# **GS-R4840NV**

## 36 W NEGATIVE SWITCHING REGULATOR

| Туре       | V <sub>in</sub> | V <sub>out</sub> | l <sub>out</sub> |

|------------|-----------------|------------------|------------------|

| GS-R4840NV | -40 to -60 V    | -22 to -60 V     | -600 mA          |

### **FEATURES**

- Digital input for voltage selection

- Short-circuit protection

- Overvoltage protection

- Thermal protection

- Softstart

- Fault signal indication output

- High efficiency (>80%)

### **DESCRIPTION**

The GS-R4840NV is a negative input, negative output switching voltage regulator that provides up to 36W output power without input-output isolation.

The output voltage is programmable by input logic signals that allow 64 steps (6 bit) of regulated output, from -22 to -60V.

## **ELECTRICAL CHARACTERISTICS** (T<sub>amb</sub> = 25°C unless otherwise specified)

| Symbol           | Parameter                             | Test Conditions                                                             | Min   | Тур | Max    | Unit |

|------------------|---------------------------------------|-----------------------------------------------------------------------------|-------|-----|--------|------|

| Vi               | Input Voltage                         | V <sub>O</sub> = -22 to -60V<br>I <sub>O</sub> = -10 to -600mA              | -40   | -48 | -60    | V    |

| Vir              | Input Ripple Voltage                  | $V_i = -40 \text{ to } -60 \text{V}$ $I_0 = -600 \text{mA}$                 |       |     | 20     | mVpp |

| Vo               | Output Voltage                        | $V_i = -40 \text{ to } -60 \text{V}$ $I_0 = -10 \text{ to } -600 \text{mA}$ | -22   |     | -60    | ٧    |

| Vor              | Output Ripple<br>Voltage              | V <sub>0</sub> = -22 to -60V<br>I <sub>0</sub> = -600mA                     |       | 4   | 10     | mVpp |

| Voov             | Output Overvoltage<br>Protection      | Vi = -40 to -60V<br>I <sub>O</sub> = -10 to -600mA                          | Vo+5% |     | Vo+10% | V    |

| lo               | Output Current                        | Vi = -40 to -60V<br>V <sub>0</sub> = -22 to -60V                            | -10   |     | -600   | mA   |

| lol              | Current Limit                         | V <sub>i</sub> = -40 to -60V<br>Overload Condition                          |       |     | -900   | mA   |

| losc             | Output Average<br>Short Circ. Current | $V_i = -40 \text{ to } -60 \text{V}$                                        |       |     | -80    | mA   |

| fs               | Switching Frequency                   |                                                                             |       | 100 |        | kHz  |

| η                | Efficiency                            | $V_i = -48V$ $I_O = -600mA$ $V_O = -48V$                                    | 80    | 82  |        | %    |

| Rth              | Thermal Resistance                    | Case to Ambient                                                             |       | 4   |        | °C/W |

| T <sub>cop</sub> | Operating Case<br>Temperature Range   |                                                                             | 0     |     | +85    | °C   |

| Tstg             | Storage<br>Temperature Range          |                                                                             | -20   |     | +105   | °C   |

December 1993 1/3

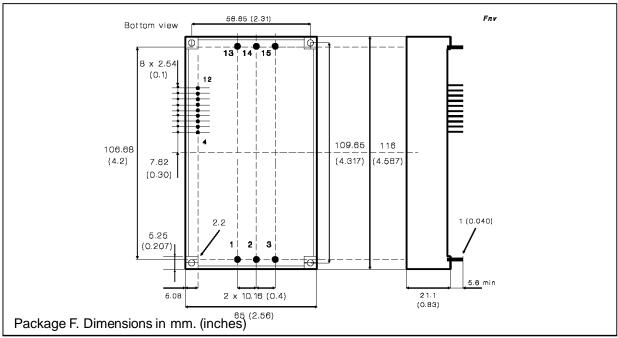

## CONNECTION DIAGRAM AND MECHANICAL DATA

## **PIN DESCRIPTION**

| Pin | Function  | Description                                                                                                                                                                                                                                                        |  |  |

|-----|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1   | -Vin      | Negative input voltage.                                                                                                                                                                                                                                            |  |  |

| 2   | Inhibit/  | Remote Inhibit/Enable logically compatible with CMOS or open collector TTL. The converter is OFF (Inhibit) when this pin is unconnected or the voltage applied is in the range of 2 to 5V (referred to GND). The converter is ON (Enable) for a control voltage in |  |  |

|     | Enable    | the range of 0 to 0.8V maximum.                                                                                                                                                                                                                                    |  |  |

| 3   | GND IN    | Return for input voltage source and +5V logic supply voltage. Internally connected to pin 15.                                                                                                                                                                      |  |  |

| 4   | +5V IN    | +5V logic supply voltage. Maximum voltage must not exceed 7V.                                                                                                                                                                                                      |  |  |

| 5   | DB0       | Data bit 0 (LSB).                                                                                                                                                                                                                                                  |  |  |

| 6   | DB1       | Data bit 1.                                                                                                                                                                                                                                                        |  |  |

| 7   | DB2       | Data bit 2.                                                                                                                                                                                                                                                        |  |  |

| 8   | DB3       | Data bit 3.                                                                                                                                                                                                                                                        |  |  |

| 9   | DB4       | Data bit 4.                                                                                                                                                                                                                                                        |  |  |

| 10  | DB5       | Data bit 5 (MSB).                                                                                                                                                                                                                                                  |  |  |

| 11  | <u>cs</u> | Chip select. An active low input control which is the device enable input terminal.                                                                                                                                                                                |  |  |

| 12  | WR        | Write control. An active low control which enables the microprocessor to write data to the DAC.                                                                                                                                                                    |  |  |

| 13  | -Vout     | Negative output voltage.                                                                                                                                                                                                                                           |  |  |

| 14  | FAULT     | FAULT indication output (referred to GND). The FAULT signal is high (TTL compatible level) when:  - the INHIBIT is ON (high) - an output overload is present (Vo < 18V typ.) - an overtemperature is present - an overvoltage is present (Vo > Vo+5%)              |  |  |

| 15  | GND OUT   | Return for output voltage source. Internally connected to pin 3.                                                                                                                                                                                                   |  |  |

Note: Case internally connected to Ground.

#### **USER NOTES**

#### **Digital Information**

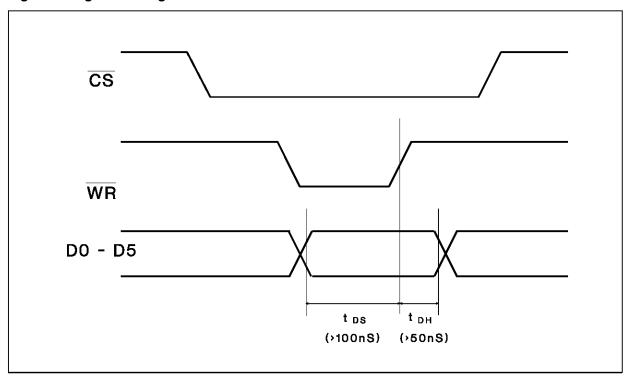

The GS-R4840NV accepts 6 bit binary at the data inputs DB0 to DB5. Data are transferred when CS is low and during the rising edge of WR signal.

tDS and tDH have to be 100ns and 50ns minimum respectively (see fig. 1).

Figure 1 - Signals Timing.

Information furnished is believed to be accurate and reliable. However, SGS-THOMSON Microelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of SGS-THOMSON Microelectronics. Specification mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. SGS-THOMSON Microelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of SGS-THOMSON Microelectronics.

© 1994 SGS-THOMSON Microelectronics - All Rights Reserved

SGS-THOMSON Microelectronics GROUP OF COMPANIES

Australia - Brazil - France - Germany - Hong Kong - Italy - Japan - Korea - Malaysia - Malta - Morocco - The Netherlands - Singapore - Spain - Sweden - Switzerland - Taiwan - Thailand - United Kingdom - U.S.A.