#### CMOS 4-BIT MICROCONTROLLER

## TMP47C233AN, TMP47C433AN

The 47C233A / 433A are the high speed and high performance 4-bit single chip microcomputers based on the TLCS-47 CMOS series with D / A converter (pulse width modulation) outputs and A/D converter input, and are suitable application in digital tuning systems for TV sets.

| PART No.    | ROM          | RAM         | PACKAGE | PIGGYBACK    |

|-------------|--------------|-------------|---------|--------------|

| TMP47C233AN | 2048 × 8-bit | 128 × 4-bit | SDIP42  | T14D47503345 |

| TMP47C433AN | 4096 × 8-bit | 256 x 4-bit | 301742  | TMP47C933AE  |

#### **FEATURES**

- ◆4-bit single chip microcomputer

- ◆Instruction execution time: 1.9 us(at 4.2 MHz)

- ♦90 basic instructions

- ◆ Table look up instructions

- ◆5-bit to 8-bit data conversion instruction

- ◆Subroutine nesting: 15 levels max.

- ◆5 interrupt sources (External: 2, Internal: 3)

All sources have independent latches each, and multiple interrupt control is available.

- ◆1/O port (36 pins)

- Input 2 ports 5 pins

- Output 2 ports 8 pins

- 1/O 6 ports 23 pins

- ◆Interval Timer

- ◆Two 12-bit Timer / Counters

Timer, event counter, and pulse width measurement mode

- ◆D/A converter (Pulse width modulation) outputs

- 14-bit resolution 1 channel

- 6-bit resolution 3 channels

- ◆3-bit A / D converter input 1 channel

Auto frequency control signal (S-shaped curve) detection

◆ High current outputs

LED direct drive capability (typ. 20 mA x 8 bits)

- ♦ Hold function

- Battery / Capacitor back up

- ◆Real Time Emulator: BM47217A

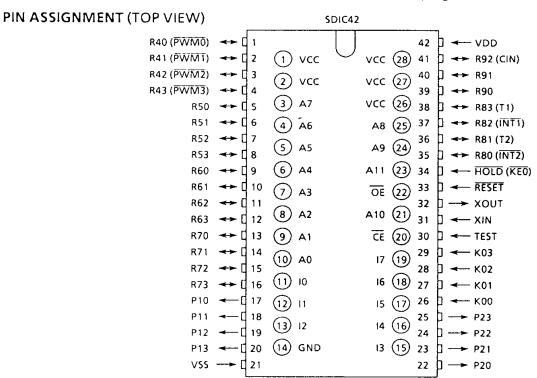

### PIN ASSIGNMENT (TOP VIEW)

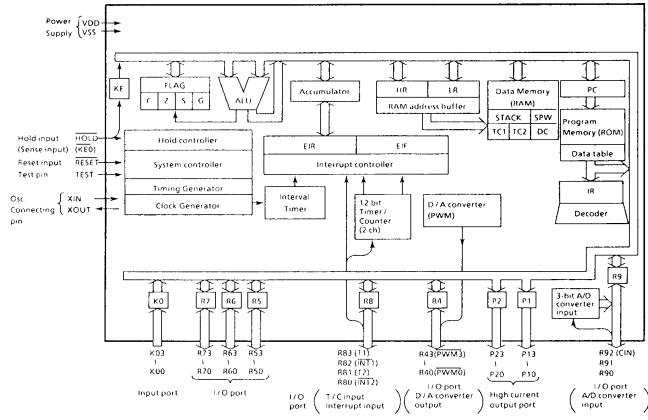

## **BLOCK DIAGRAM**

5-178

# PIN FUNCTION

| PIN NAME                  | Input / Output | FUNCT                                                                                        | TIONS                            |

|---------------------------|----------------|----------------------------------------------------------------------------------------------|----------------------------------|

| K03 - K00                 | Input          | 4 - bit input port                                                                           |                                  |

| P13 - P10                 | Output         | 4 - bit output port with latch. 8 - bit data are output by the 5 - bit to 8 - b              | oit data conversion instruction  |

| P23 - P20                 |                | (OUTB @HL).                                                                                  |                                  |

| R43 (PWM3)<br>-R41 (PWM1) | I/O (Output)   | 4 - bit I / O port with latch. When used as input port                                       | 6 - bit D / A converter output   |

| R40 (PWM0)                | 17 G (GG(pat)  | or D/A converter outputs pins, the latch must be set to "1"                                  | 14 - bit D / A converter output  |

| R53 - R50                 |                | 4 - bit I / O port with latch.                                                               |                                  |

| R63 - R60                 | 1/0            | When used as input port, the latch must be<br>Every bit data is possible to be set, clear ar |                                  |

| R73 - R70                 |                | register indirect addressing.                                                                |                                  |

| R83 (T1)                  |                | 4 - bit I / O port with latch.                                                               | Timer / Counter 1 external input |

| R82 ( <del>INT1</del> )   |                | When used as input port, external                                                            | External interrupt 1 input       |

| R81 (T2)                  | I/O (Input)    | interrupt input pin, or Timer / Counter external input pin, the latch must be set            | Timer / Counter 2 external input |

| R80 (ĪNT2)                |                | to "1".                                                                                      | External interrupt 2 input       |

| R92 (CIN)                 | I / O(Input)   | 3 - bit I / O port with latch.  When used as input port or serial port,                      | 3-bit A/D converter input        |

| R91 - R90                 | 1/0            | the latch must be set to "1".                                                                |                                  |

| XIN                       | Input          | Resonator connecting pin.                                                                    |                                  |

| хоит                      | Output         | For inputting external clock, XIN is used as                                                 | nd XOUT is opened.               |

| RESET                     | Input          | Reset signal input                                                                           |                                  |

| HOLD (KEO)                | Input (Input)  | Hold request / release signal input                                                          | Sense input                      |

| TEST                      | Input          | Test pin for out - going test. Be opened or                                                  | fixed to low level.              |

| VDD                       | Power supply   | + SV                                                                                         |                                  |

| VSS                       |                | 0V (GND)                                                                                     |                                  |

#### OPERATIONAL DESCRIPTION

Concerning the 47C233A / 433A, the configuration and functions of hardwares are described.

As the description is porvided with priority on those parts—differing from the 47C200A/400A, the technical data sheets for the 47C200A / 400A—shall also be referred to.

The 47C233A / 433A have no serial interface, differing from the 47C200A / 400A.

#### 1 SYSTEM CONFIGURATION

- (1) I / O Ports

- (2) A / D Converter (Comparator) input

- (3) D/A Converter (Pulse Width Modulation) output

#### 2 PERIPHERAL HARDWARE FUNCTION

#### 2.1 I/O Ports

The 47C233A / 433A have 10 I/O ports (36 pins) each as follows:

(i) K0 ; 4 - bit input ② P1, P2 ; 4 - bit output

3 R4 ; 4 - bit input / output (shared by pulse with modulation output)

4 R6 ; 4-bit input / output (Note)

\$ R5, R7 ; 4-bit input/output

6 R8 ; 4 - bit input / output (shared by external interrupt input and timer / counter

input)

R9 ; 3 - bit input / output (shared by A / D converter input: R92 pin)

KE ; 1 - bit sense input (shared by hold request / release signal input)

Note. Port R6 becomes a tri-state output buffer when the I/O circuit code: PF is selected.

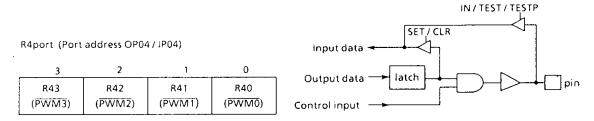

## (1) Port R4 (R43-R40)

This is a 4-bit I/O port with latch. The latch should be set to "1" when the port is used as an input port. The latch is initial to "1" during reset.

It is R4 port common to PWM output. The latch should be set to "1" when PWM is used as an output port.

Figure 2-1. Port R4

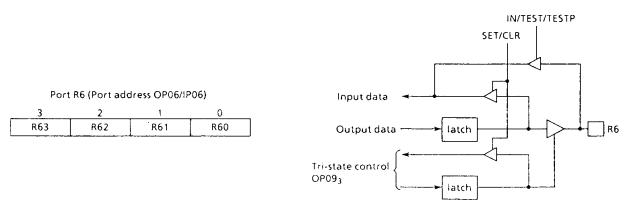

## (2) Port R6 (R63-R60)

The 4-bit I/O port with latch. The output buffers become a tri-state output buffer when the I/O circuit code: PF is selected, and the state of them is simultaneously controlled by the port. Controlling the Tri-state is performed by MSB of the port address OP09. When the data of the MSB of the OP09 are "0", the output buffers are high-impedance state. The MSB of the OP09 is initialized to "0" during reset, the output latch should be set to "1" when the port is used as output port. The output buffers should be set to high-impedance when the port is used as input port.

Example: Outputs the immediate data "5" to the R6 port.

SET %0P09, 3 ; OP09<sub>3</sub>←1 (Output buffer is on)

OUT #5, %OP06 ; Port R6←5

Figure 2-2. Port R6

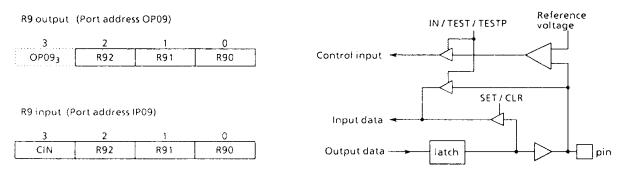

## (3) Port R9 (R92-R90)

This is a 3-bit I/O port with latch. The latch should be set to "1" when the port is used as an input port. The latch is initial to "1" during reset.

R92 (CIN) pin can also be used for A/D convertor (comparator) input for AFC (Auto Frequency Control) signal detection. R92 input is ordinary digital input which is read from bit 2 of IP09. CIN input is comparator input read from bit 3 of IP09 and uses the programmable 3-bit D/A convertor output as the reference voltage.

Figure 2-3. Port R9

#### Note. About OP093

When I/O circuit code: PF is selected, this bit functions for R6 port tri-state control. The output buffer is set to high impedance when the data is "0". When code: PC is selected, the R6 port is set for open drain output and the OUT/SET/CLR instruction for OP093 becomes ineffective.

| Port            |                 | Port                                                           |                        |                         | Input/    | Input / Output instruction | tion                   |                           |                            |

|-----------------|-----------------|----------------------------------------------------------------|------------------------|-------------------------|-----------|----------------------------|------------------------|---------------------------|----------------------------|

| address (**)    | Input (IP**)    | Output (OP**)                                                  | IN %p, A<br>IN %p, @HL | OUT A, %p<br>OUT @HL,%p | OUT #k,%p | OUTB @HL                   | SET %p, b<br>CLR %p, b | TEST %p, b<br>TESTP %p, b | SET @L<br>CLR @L<br>TEST@L |

| <sup>н</sup> 00 | K0 input port   |                                                                | 0                      | 0                       | ()        |                            |                        | 0                         | ı                          |

| 5               | P1 output latch | P1 output port                                                 | 0                      | 0                       | 0         | 0                          |                        | 0                         | 1                          |

| 05              | P2 output latch | P2 output port                                                 | 0                      | 0                       | 0         | (Note 2)                   | 0                      | 0                         | Į                          |

| 03              |                 |                                                                | 1                      | ı                       | 1         | ı                          |                        | ı                         | 1                          |

| 04              | R4 input port   | R4 output port                                                 | $\bigcirc$             | 0                       | 0         | i                          | 0                      | 0                         | ()                         |

| 02              | R5 input port   | R5 output port                                                 | 0                      | 0                       | ()        | ı                          | 0                      | 0                         | ()                         |

| 90              | R6 input port   | R6 output port                                                 | 0                      | 0                       | 0         | ŀ                          | 0                      | ·                         | О                          |

| 07              | R7 input port   | R7 output port                                                 | 0                      | 0                       | · ()      | ı                          | 0                      | - C                       | ) ()                       |

| 80              | R8 input port   | R8 output port                                                 | 0                      | 0                       | O         | ļ                          | 0                      | 0                         | · 1                        |

| 60              | R9 input port   | R9 output port (Note 3)                                        | 0                      | 0                       | 0         | ı                          | 0                      | 0                         | ı                          |

| 0<br>V          |                 |                                                                |                        | ı                       | 1         | 1                          | ı                      | ı                         | ı                          |

| 08              |                 |                                                                | 1                      | ı                       | ı         | 1                          | ı                      | ı                         | 1                          |

| 8               |                 |                                                                | 1                      | 1                       | ı         | ı                          | ı                      | ı                         | i                          |

| 00              |                 |                                                                | 1                      | ı                       | 1         | ı                          | ı                      | i                         | ı                          |

| 0E              | Hold status     |                                                                | 0                      | ı                       | ı         | Ì                          | ı                      | 0                         | i                          |

| 90              |                 |                                                                | ı                      | ļ                       | ı         | i                          | I                      | 1                         | ı                          |

| 10H             | Undefined       | Hold operating mode control                                    |                        | 0                       | 1         |                            | ı                      |                           | -                          |

| =               | Undefined       | 1                                                              | i                      | 1                       | ı         | 1                          | ı                      | ı                         | ı                          |

| 12              | Undefined       | A/D converter input control                                    | ı                      | 0                       | ı         | 1                          | ı                      | i                         | i                          |

| 13              | Undefined       |                                                                | ı                      | ı                       | 1         | 1                          | ı                      | ı                         | ı                          |

| 14              | Undefined       |                                                                | 1                      | ı                       | ı         | 1                          | ı                      | ı                         | 1                          |

| 15              | Undefined       |                                                                | ı                      | 1                       | ı         | ı                          | ı                      | ı                         | ı                          |

| 16              | Undefined       | -                                                              | ı                      | ı                       | I         | 1                          | i                      | ı                         | i                          |

| 17              | Undefined       | PWM buffer selector                                            | 1                      | 0                       | ı         | ı                          | ı                      | 1                         | ı                          |

| ₩.              | Undefined       | PWM data transfer buffer                                       | 1                      | 0                       | ı         | ı                          | ı                      | ı                         | i                          |

| 19              | Undefined       | Interval Timer interrupt control                               | ŀ                      | 0                       | 1         | ı                          | i                      | ı                         | ł                          |

| 1 <b>A</b>      | Undefined       |                                                                | 1                      | 1                       | i         | ı                          | ļ                      | ı                         | ı                          |

| 18              | Undefined       |                                                                | ı                      | I                       | ı         | í                          | ı                      | ı                         | ŀ                          |

| 7               | Undefined       | Timer / Counter 1 control                                      | 1                      | 0                       | ı         | ı                          | ı                      | 1                         | ı                          |

| 0               | Undefined       | Timer / Counter 2 control                                      | i                      | 0                       | ı         | ı                          | ı                      | ı                         | í                          |

| Ħ,              | Undefined       | -                                                              | ı                      | ı                       | ı         | 1                          | 1                      | 1                         |                            |

| <u>"</u>        | Undefined       |                                                                | -                      |                         | 1         | _                          | 1.                     | 1                         | ı                          |

| Notes.          | 1. "            | " means the reserved state. Unavailable for the user programs. | ograms.                |                         |           |                            |                        |                           |                            |

Table 2-1. Port Address Assignments and Available I / O Instructions

IFO circuit code: Controlling the tri-state (R6 port) is performed by MSB of the port address OP09, when IFO circuit code select PF.

The 5 - bit to 8 - bit data conversion instruction [OUTB @HL], automatic access to ports P1 and P2.

5-182

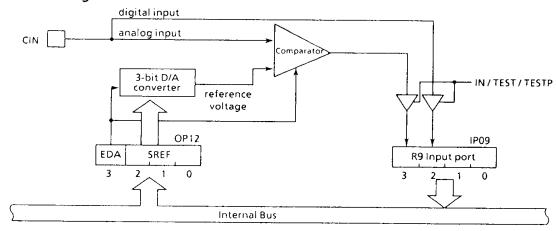

# 2.2 3-bit A/D Converter (Comparator) Input

Comparator input consists of a comparator and a 3-bit D/A converter. AFC input voltage can be detected in 8 steps by sensing bit 3 of IP09 while changing the reference voltage (D/A converter output voltage) with the command register (OP12).

R92 pin is also used for comparator input. Bit 2 is used to set R92 pin for ordinary digital input.

The comparator is disabled and bit 3 is set to "0" during reset. The latch should be set to "1" when R92 pin is used for comparator input and digital input.

## 2.2.1 Circuit Configuration

Figure 2-4. Comparator input Circuit

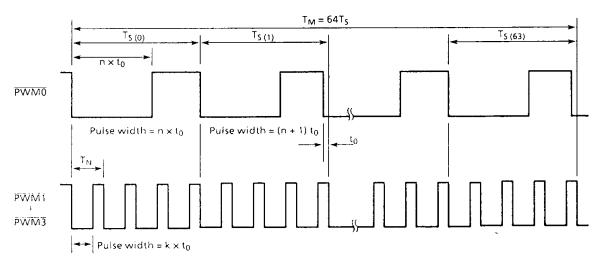

# 2.2.2 Control of Comparator Input

The reference voltage of the comparator is set using the lower 3 bits of the command register. Table 2-2 shows the reference voltage at  $V_{DD} = 5V$ .

Comparator input control command register (Port address OP12)

Figure 2-5. Control Command Register

| 1          | 1 | 1    | 5.00         |

|------------|---|------|--------------|

| Table 2-2. |   | Refe | ence Voltage |

OP12

0 0

1 0

0

0 0

0

0

1 0

1

1 0

0

0

reference voltage [V]

0.62

1.25

1.87

2.50

3.12

3.75

4.37

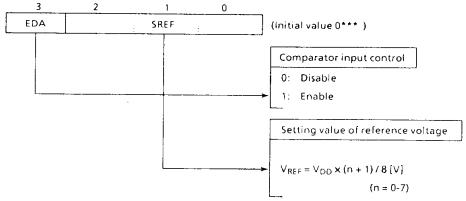

### 2.3 D/A converter (PWM) output

The 47C233A/433A have four channels built-in D/A converter (PWM) outputs. PWM output can easily be obtained by connecting an external low pass filter.

PWM outputs data are multiplex to the R4 port. When the R4 (PWM) port is used for PWM output, the corresponding bits of R4 output latch should be set to "1". The output buffer is set to high impedance during reset and so must be set to ON status by instruction (refer to section 2-1 I/O ports). PWM output is controlled by the buffer selector (OP17) and the data transfer buffer (OP18). PWM data written to the data transfer buffer can be sent to the PWM data latch by writing "CH" to the buffer selector, and PWM output switches switch to PWM output. PWM data transferred to the PWM data latch remain intact until overwritten. Resetting and holding clear the buffer selector, data transfer buffer and PWM data latch to "0" (PWM output is "high" level).

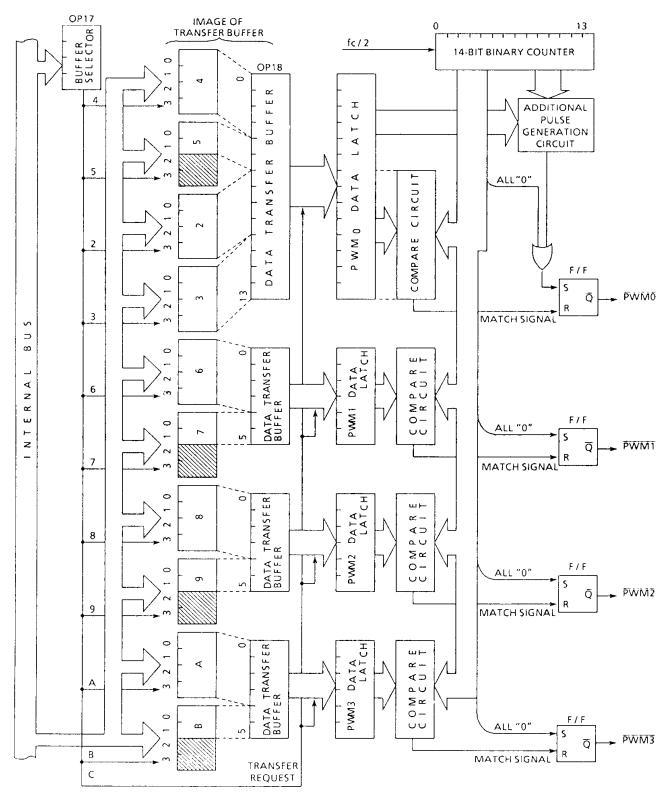

## 2.3.1 Configuration of PWM circuit

Configuration of PWM circuit shown in Figure 2-7.

## 2.3.2 Output waveform of PWM circuit

#### (1) PWM0 output

$\overline{PWM0}$  is a PWM output controlled by 14 bits data. The basic period of the  $\overline{PWM0}$  is  $T_M = 2^{15}$  / fc. The higher 8 bits of 14 bits data are used to control the pulse width of the pulse output with the period of  $T_S = T_M$  / 64, which is the sub - period of the  $\overline{PWM0}$ . When the 8 bits data are decimal n (0  $\leq$  n  $\leq$  255), this pulse width becomes n  $\times$  t<sub>0</sub>, where t<sub>0</sub> = 2 / fc.

The lower 6 bits of 14 bits data are used to control the generation of an additional  $t_0$  wide pulse in each  $T_5$  period. When the 6 bits data are decimal m (0  $\leq$  m  $\leq$  63), the additional pulse is generated in each of m periods out of 64 periods contained in a  $T_M$  period. The relationship between the 6 bits data and the position of  $T_5$  period where the additional pulse is generated is shown in Table 2-3.

#### (2) PWM1-PWM3 output

Each of PWM1 to PWM3 is a PWM output controlled by 6 bits data. The period of them is  $T_N = 27$ /fc. When the 6 bits data are decimal k (0 < k < 63), the pulse width becomes k × t<sub>0</sub>. The waveform is also illustrated in Figure 2-6.

Figure 2-6. PWM Output Waveform (It is shown to the additional pulse T<sub>S (1)</sub> and T<sub>S (63)</sub> of the PWMO)

Figure 2-7. Pulse Width Modulation Circuit

| Bit position of 6 bits data | Relative position of Ts where the output pulse is generated (No. i of $T_{S(i)}$ is listed) |

|-----------------------------|---------------------------------------------------------------------------------------------|

| Bit 0                       | 32                                                                                          |

| Bit 1                       | 16, 48                                                                                      |

| Bit 2                       | 8, 24, 40, 56                                                                               |

| Bit 3                       | 4, 12, 20, 28, 36, 44, 52, 60                                                               |

| Bit 4                       | 2, 6, 10, 14, 18, 22, 26, 30,, 58, 62                                                       |

| Bit 5                       | 1, 3, 5, 7, 9, 11, 13, 15, 17,, 59, 61, 63                                                  |

Note. When the corresponding bit is "1", it is output.

Table 2-3. Correspondence between 6 bits data and the additional pulse generated Ts periods

## 2.3.3 Control of PWM circuit (Data transfer)

PWM output is controlled by writting output data to a data transfer buffer (OP18). For writing, the output data are divided using the buffer selector (OP17). Buffer numbers are assigned to the data transfer buffers for these divided data, after which the data are written as shown in Table 2-4.

- ① The number of the transfer buffer to which the data are to be written is written to the buffer selector (OP17).

- (2) The corresponding PWM data are written to the transfer buffer (OP18).

- 3 Operations 1 and 2 are repeated, continuously writing data to the transfer buffer.

- (4) When all of the output data have been written, "CH" is written to the buffer selector.

While the output data are being written to the transfer buffer, the previously written data are being output. For  $\overline{PWM0}$  output, switching to  $\overline{PWM}$  output occurs at a maximum of  $2^{15}$  / fc [sec] (at 4MHz, 8192µs) after "CH" is written to the buffer selector. For  $\overline{PWM1}$  through  $\overline{PWM3}$  output data switching, this requires  $2^9$  / fc [sec] (at 4MHz, 128µs).

| Buffer Number<br>(OP17) | Correspondence t<br>(OP18)  | o bit |    | Mode     | PWM Output     |

|-------------------------|-----------------------------|-------|----|----------|----------------|

| 2                       | Bit of PWM0 transfer buffer | 9 -   | 6  | Write    | Preceding data |

|                         | Bit of PWM0 transfer buffer | 13 -  | 10 | Write    | Preceding data |

| 4                       | Bit of PWM0 transfer buffer | 3 -   | 0  | Write    | Preceding data |

| 5                       | Bit of PWM0 transfer buffer | 5 -   | 4  | Write    | Preceding data |

| 6 7                     | Bit of PWM1 transfer buffer | 3 -   | 0  | Write    | Preceding data |

|                         | Bit of PWM1 transfer buffer | 5 -   | 4  | Write    | Preceding data |

| 8                       | Bit of PWM2 transfer buffer | 3 -   | 0  | Write    | Preceding data |

|                         | Bit of PWM2 transfer buffer | 5 -   | 4  | Write    | Preceding data |

| A                       | Bit of PWM3 transfer buffer | 3 -   | 0  | Write    | Preceding data |

| B                       | Bit of PWM3 transfer buffer | 5 -   |    | Write    | Preceding data |

| C                       | None                        | ····· |    | Transfer | Present data   |

Table 2-4. The bit and buffer number of data transfer buffer

### **ELECTRICAL CHARACTERISTICS**

ABSOLUTE MAXIMUM RATINGS

$(V_{SS} = 0V)$

| PARAMETER                       | SYMBOL             | PINS                                            | RATING                         | UNIT  |

|---------------------------------|--------------------|-------------------------------------------------|--------------------------------|-------|

| Supply Voltage                  | V <sub>DD</sub>    |                                                 | - 0.5 to 7                     | V     |

| Input Voltage                   | ViN                |                                                 | - 0.5 to V <sub>DD</sub> + 0.5 | V     |

| Output Voltage                  | Vouti              | Except sink open drain pin, but include R92 pin | - 0.5 to V <sub>DD</sub> + 0.5 |       |

|                                 | V <sub>OUT2</sub>  | Sink open drain pin except R92 pin              | – 0.5 to 10                    | \ \ \ |

|                                 | louti              | Ports P1, P2                                    | 30                             |       |

| Output Current (Per 1 pin)      | loutz              | Ports R5, R7, R8, R9                            | 3.2                            | mA    |

| Output Current (Total)          | ΣΙ <sub>ΟυΤ1</sub> | Ports P1, P2                                    | 120                            | mA    |

| Power Dissipation [Topr = 70°C] | PD                 |                                                 | 600                            | mW    |

| Soldering Temperature (Time)    | T <sub>slei</sub>  |                                                 | 260 (10 sec)                   | °C    |

| Storage Temperature             | T <sub>stg</sub>   |                                                 | - 55 to 125                    | °C    |

| Operating Temperature           | Topr               |                                                 | – 30 to 70                     | °C    |

RECOMMENDED OPERATING CONDITIONS

$(V_{SS} = 0V, T_{opr} = -30 \text{ to } 70^{\circ}\text{C})$

| PARAMETER          | SYMBOL            | PINS                    | CONDITIONS             | Min.                   | Max.                   | UNIT  |

|--------------------|-------------------|-------------------------|------------------------|------------------------|------------------------|-------|

| Supply Voltage     |                   |                         | in the Normal mode     | 4.5                    | 6.0                    |       |

| supply voltage     | V <sub>DD</sub>   |                         | in the HOLD mode       | 2.0                    | 6.0                    | \ \ \ |

|                    | V <sub>1611</sub> | Except Hysteresis Input | V > 4 EV               | V <sub>DD</sub> × 0.7  |                        |       |

| Input High Voltage | V <sub>II12</sub> | Hysteresis Input        | V <sub>DD</sub> ≥ 4.5V | V <sub>DD</sub> × 0.75 | V <sub>DD</sub>        | V     |

|                    | V <sub>IH3</sub>  |                         | V <sub>DD</sub> < 4.5V | $V_{DD} \times 0.9$    |                        |       |

|                    | V <sub>IL1</sub>  | Except Hysteresis Input | V <sub>DD</sub> ≥ 4.5V |                        | $V_{DD} \times 0.3$    |       |

| Input Low Voltage  | V <sub>IL2</sub>  | Hysteresis Input        | V DO ₩ 4.3V            | 0                      | V <sub>DD</sub> × 0.25 | v     |

|                    | V <sub>IL3</sub>  |                         | V <sub>DD</sub> < 4.5V |                        | V <sub>DD</sub> × 0.1  |       |

| Clock Frequency    | fc                |                         |                        | 0.4                    | 4.2                    | MHz   |

Note . Input Voltage  $V_{IH3}$ ,  $V_{IL3}$  : in the HOLD mode.

D.C. CHARACTERISTICS

$(V_{SS} = 0V, T_{opr} = -30 \text{ to } 70^{\circ}\text{C})$

| PARAMETER                             | SYMBOL            | PINS                                  | CONDITIONS                                      | Min. | Тур. | Max. | UNIT |

|---------------------------------------|-------------------|---------------------------------------|-------------------------------------------------|------|------|------|------|

| Hysteresis Voltage                    | V <sub>HS</sub>   | Hysteresis Input                      |                                                 | _    | 0.7  | -    | ٧    |

| Input Current                         | l <sub>W1</sub>   | Port KO, TEST<br>RESET, HÖLD          | V <sub>DD</sub> = 5.5V,                         | _    | _    | ± 2  | μА   |

|                                       | I <sub>IN2</sub>  | Port R (open drain)                   | V <sub>IN</sub> = 5.5V / 0V                     |      |      |      |      |

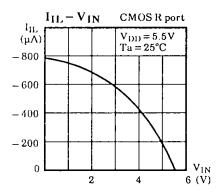

| Input Low Current                     | l <sub>iL</sub>   | Port R (push-pull)                    | $V_{DD} = 5.5V, V_{IN} = 0.4V$                  | _    | _    | - 2  | mA   |

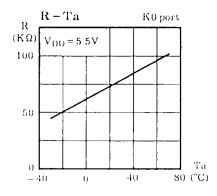

| Input Resistance                      | R <sub>IN1</sub>  | Port K0 with pull-up / pull-down      |                                                 | 30   | 70   | 150  | ΚΩ   |

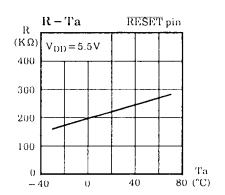

| mput Resistance                       | R <sub>INi2</sub> | RESET                                 |                                                 | 100  | 220  | 450  |      |

| Output Leakage<br>Current             | lio               | Tri-state port<br>Port R (open drain) | V <sub>DD</sub> = 5.5V, V <sub>OUT</sub> = 5.5V | -    | -    | 2    | μА   |

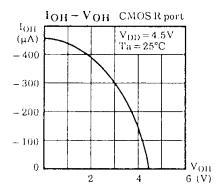

| Output High Voltage                   | V <sub>ОН1</sub>  | Ports P, R (push-pull)                | $V_{DD} = 4.5V$ , $I_{OH} = -200\mu A$          | 2.4  | _    | _    | V    |

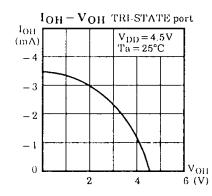

| output mg/, voitage                   | V <sub>OH2</sub>  | Port R (Tri-state)                    | $V_{DD} = 4.5V$ , $I_{OH} = -0.7mA$             | 4.1  | _    | _    |      |

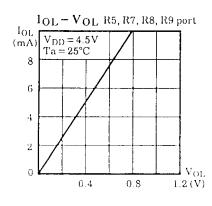

| Output Low Voltage                    | V <sub>OL1</sub>  | Ports R5, R7 to R9                    | V <sub>DD</sub> = 4.5V, I <sub>OL</sub> = 1.6mA |      |      |      |      |

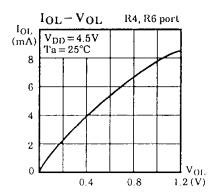

| output tow vortage                    | V <sub>OL2</sub>  | Ports R4, R6                          | $V_{DD} = 4.5V$ , $I_{OL} = 0.7mA$              | ] -  | _    | 0.4  | \ \  |

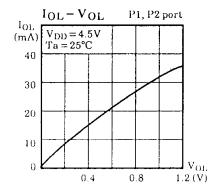

| Output Low Current                    | loL               | Port P                                | $V_{DD} = 4.5V, V_{OL} = 1.0V$                  | -    | 20   | _    | mA   |

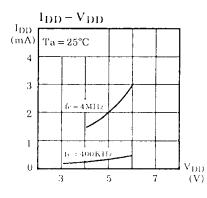

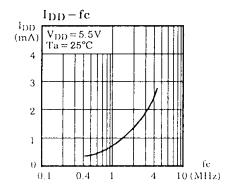

| Supply Current<br>(in the Nomal mode) | l <sub>DD</sub>   |                                       | V <sub>DD</sub> = 5.5V, fc = 4MHz               | -    | 3    | 6    | mΑ   |

| Supply Current<br>(in the HOLD mode)  | <sup>1</sup> рон  |                                       | V <sub>DO</sub> = 5.5V                          | _    | 0.5  | 10   | μА   |

Note 1. Typ. values show those at  $T_{opr} = 25^{\circ}C$ ,  $V_{DD} = 5V$ .

Note 2. Input Current I<sub>IN1</sub>: The current through resistor is not included, when the pull-up /

pull-down resistor is contained.

Note 3. Supply Current :  $V_{IN} = 5.3V / 0.2V$

The KO port is open when the pull-up / pull-down resistor is

contained. The Voltage applied to the R port is within the valid

range VIL or VIH.

A / D CONVERTER CHARACTERISTICS  $(V_{SS} = 0V, V_{DD} = 4.5 \text{ to } 6.0V, T_{opr} = -30 \text{ to } 70^{\circ}\text{C})$

| PARAMETER              | SYMBOL | PINS | CONDITIONS | Min. | Тур. | Max.            | UNIT |

|------------------------|--------|------|------------|------|------|-----------------|------|

| Analog Input Voltage   | VAIN   | CIN  |            | Vss  | _    | V <sub>DD</sub> | ٧    |

| A / D Conversion Error | _      |      |            | _    | _    | ± 1/4           | LSB  |

A.C. CHARACTERISTICS

$(V_{SS} = 0V, V_{DD} = 4.5 \text{ to } 6.0V, T_{opr} = -30 \text{ to } 70^{\circ}\text{C})$

| PARAMETER                    | SYMBOL           | CONDITIONS                   | Min. | Тур. | Max. | UNIT |

|------------------------------|------------------|------------------------------|------|------|------|------|

| Instruction Cycle Time       | t <sub>cy</sub>  |                              | 1.9  | -    | 20   | μs   |

| High level Clock Pulse Width | twch             | For external clock operation | 80   |      | _    | ns   |

| Low level Clock Pulse Width  | t <sub>WCL</sub> | To reaction cross operation  |      |      |      | '''  |

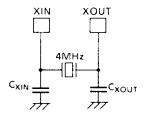

### RECOMMENDED OSCILLATING CONDITIONS

$(V_{SS} = 0V, V_{DD} = 4.5 \text{ to } 6.0V, T_{opr} = -30 \text{ to } 70^{\circ}\text{C})$

(1) 4MHz

Ceramic Resonator

CSA4.00MG (MURATA) **KBR-4.00MS**

(KYOCERA)

$C_{XIN} = C_{XOUT} = 30pF$  $C_{XIN} = C_{XOUT} = 30pF$

Crystal Oscillator

204B-6F 4.0000 (TOYOCOM)

$C_{XIN} = C_{XOUT} = 20pF$

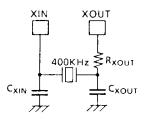

(2) 400KHz

Ceramic Resonator

KBR-400B

CSB400B

(MURATA)

(KYOCERA)

$C_{X1N} = C_{XOUT} = 220pF$ ,

$R_{XOUT} = 6.8K\Omega$

$C_{XIN} = C_{XOUT} = 100pF$ ,

$R_{XOUT} = 10K\Omega$

#### TYPICAL CHARACTERISTICS

# Input / Output Circuitry

- (1) Control pins

- I/O circuitries of the 47C233A / 433A control pins are similar to that of the 47C200A / 400A.

- (2) 1/O ports

The I/O circuitries of the 47C233A / 433A I/O ports are shown below, any one of the circuitries can be chosen by a code (PC, PF) as a mask option.

| PORT           | 1/0    | input/Output CIRO | CUITRY and CODE        | REMARKS                                                                                    |

|----------------|--------|-------------------|------------------------|--------------------------------------------------------------------------------------------|

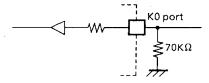

| к0             | Input  | R <sub>IN</sub>   | l•w-□<br>\$            | pull - down resistor $R_{IN} = 70KΩ (typ.)$ $R = 1KΩ (typ.)$                               |

| P1<br>P2       | Output | PC Initial "Hi-Z" | PF Initial"High" OVDD  | Sink open drain<br>or<br>Push-pull output<br>High current<br>I <sub>OL</sub> = 20mA (typ.) |

| R5             | I/O    | Initial "Hi-Z"    | Initial "Low" OVDD     | Sink open drain or Push-pull output $R = 1K\Omega \ (typ.)$                                |

| R6             | 1/0    | PC R              | PF OVDD OVDD OVDD OVDD | Sink open drain or Tri-state Initial "Hi-Z" $R=1K\Omega$ (typ.)                            |

| R4<br>R7<br>R8 | 1/0    | R4, R7            | R8                     | Sink open drain<br>Initial "Hi-Z"<br>Hysteresis input<br>(Port R8)<br>R = 1KΩ (typ.)       |

| R9             | 1/0    | R92               | R91, R90               | Sink open drain<br>Initial "Hi-Z"<br>Comparator input<br>(R92 pin)<br>R = 1KΩ (typ.)       |

This Page Intentionally Left Blank

### CMOS 4-BIT MICROCONTROLLER

## **TMP47C933AE**

The 47C933A, which is equipped with an EPROM as program memory, is a piggyback type evaluator chip used for development and operational confirmation of the 47C233A/433A application systems (programs). The 47C933A is pin compatible with the 47C233A/433A which are mask-programed ROM devices.

### PIN FUNCTION (Top of the package)

| PIN NAME | Input / Output | FUNCTIONS                     |  |  |

|----------|----------------|-------------------------------|--|--|

| A11 ~ A0 | Output         | Program memory address output |  |  |

| 17 ~ 10  | Input          | Program memory data input     |  |  |

| ČĒ       | Output         | Chip enable signal output     |  |  |

| ŌĒ       |                | Output enable signal output   |  |  |

| vcc      | Power supply   | + 5V (connected with VDD)     |  |  |

| GND      | rower supply   | 0V (connected with VSS)       |  |  |

# A.C. CHARACTERISTICS

| PARAMETER          | SYMBOL          | CONDITIONS                             | Min. | Тур. | Max. | UNIT |

|--------------------|-----------------|----------------------------------------|------|------|------|------|

| Address Delay Time | t <sub>AD</sub> | $V_{SS} = 0V$ , $V_{DD} = 4.5$ to 6.0V | -    | _    | 150  | ns   |

| Data Setup Time    | t <sub>IS</sub> | $C_L = 100 pF$ Topr = -30 to 70°C      | 150  | -    | -    | ns   |

| Data Hold Time     | t <sub>iH</sub> |                                        | 50   | -    | -    | ns   |

#### **NOTES FOR USE**

#### (1) Program memory

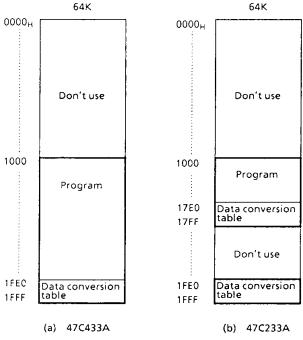

The program area are as shown in Figure 1. When this chip is used as evaluator of the 47C233A, data conversion table for [OUTB @HL] instruction must be allocated at two areas and they must be the same contents as shown in Figure 1.

Figure 1. Program area

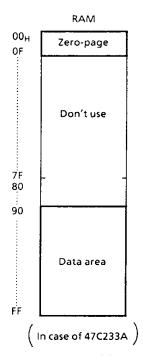

Figure 2. RAM addressing

#### (2) Data memory

The 47C933A contains  $256 \times 4$ -bit (equivalent to 47C433A) data memory. When the 47C933A is used as evaluator of the 47C233A, programming should be performed assuming that the RAM is assigned to addresses  $00\sim0$ F<sub>H</sub> and  $90\sim$ FF<sub>H</sub> as show in Figure 2 by considering the application software evaluation.

### (3) I/O ports

Input/Output circuitries of I/O ports in the 47C933A are similar to the code PC of the 47C233A/433A. When this chip is used as evaluator with other I/O code, it is nacessary to provide the external resistors.

Figure 3. External circuitry

Note. Caution is required when using the 47C933A as a code PF evaluator. The follwing ports of the 47C933A differ from those of the 47C233A/433A (code PF).

- ① Ports P1 and P2 are not push-pull output (initial "High").

- Port R5 is not push-pull output (initial "Low").

- ③ Port R6 is not tristate output (initial "Hi-Z").