# OC-48/STM-16 Framer with VC - POSIC2GV

#### **Features**

- OC-48/STS-48/STM-16, OC-12/STS-12/STM-4, OC-3/STS3/STM-1 rates, concatenated and non-concat-

- Complies with ITU-Standards G.707/Y.1322 and G.783<sup>[1,2]</sup>

- Complies with Bellcore GR253 rev.1, 1997<sup>[3]</sup>

- Channelized operation: supports 16xOC-3 and 4xOC-12 within OC-48 stream

- Supports TUG3 mapping in SDH mode

- Virtual concatenation enables secure and dedicated bandwidth provisioning<sup>[4]</sup>

- · Up to 16 channels

- From 50-Mbps to 1.2-Gbps bandwidth per channel

- STS-1 and STS-3c granularity

- Full duplex mapping of ATM cells over SONET/SDH

- Complies with ITU-Standards I 432.2<sup>[5,6,7]</sup>

- · Full duplex mapping of packet-over-SONET/SDH: IETF RFC 1619/1662/2615 (HDLC/PPP)[8,9,10]

- Generic Framing Procedure (GFP) per ANSI T1X1.5<sup>[11,12,13]</sup> Protocol Encapsulator/Decapsulator delineates GFP frames with length-CRC frame construct

- GFP 268r1

- User-programmable encapsulation

- User-programmable clear channel transport

- User-programmable SONET/SDH bypass

- Programmable frame tagging engine for packet preclassification enables such features as

- MPLS label lookup and tagging

- · PPP: LCP and NCP tagging

- PPP control packets optionally sent to host CPU interface

- MAC/layer 3 address look up and tagging.

- Programmable A1A2 processing bypass in Rx direction with frame sync input

- · Complete section overhead (SOH), line overhead (LOH), and path overhead (POH) processing

- · APS extraction, CPU interrupt generation, and programmable insertion of APS byte

- Line side APS port interface

- Provision for protection switching on SONET/SDH port

- Programmable PRBS generator and receiver

- Serial port to access line/section data communication channel (DCC) and voice communication channel (VCC)

- Full duplex OIF-SPI (POS-PHY)/UTOPIA level 3 interface<sup>[14,15]</sup>

- · 16-bit/32-bit host CPU interface bus

- JTAG and boundary scan

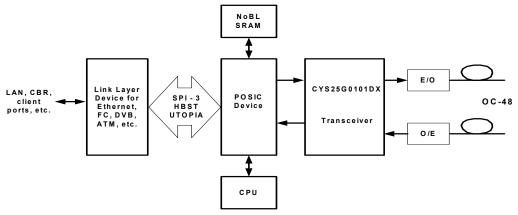

- Glueless interface with Cypress CYS25G0101DX OC-48 PHY

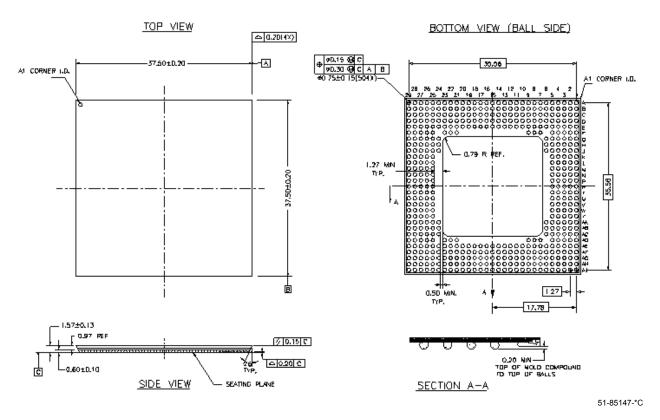

- 0.18-um CMOS, 504-pin BGA package

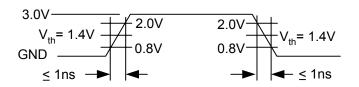

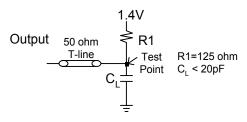

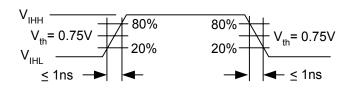

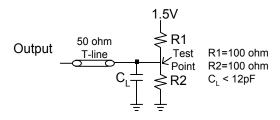

- +1.8V for core, +3.3V for LVTTL I/O, +1.5V/+3.3V for HSTL/LVPECL I/O supply, and +0.75V/2.0V reference

#### **Applications**

- · Multi-service nodes

- · ATM switches and routers

- · Packet routers and multiservice routers

- SONET/SDH/Add-Drop Mux for packet/data applications

- · SONET/SDH/ATM/POS test equipment

#### Notes:

- 1. ITU-T Recommendation G.707. "Network Node Interface for the Synchronous Digital Hierarchy." 1996.

- 2. ITU-T Recommendation G.783. "Characteristics of Synchronous Digital Hierarchy (SDH) Equipment Functional Blocks." 2000.

- 3. Bellcore Publication GR-253-Core. "Synchronous Optical Network (SONET) Transport Systems: Common Generic Criteria." 1997.

- Jones, N., Lucent Microelectronics, and C. Murton, Nortel Networks. "Extending PPP over SONET/DSH with Virtual Concatenation, High-Order and Low-Order payloads." Internet Draft. June 2000.

- ITÚ-T Recommendation I.432.3. "B-ISDN User-Network Interface—Physical Layer Specification: 1544 kbit/s and 2048 kbit/s Operation." 1999

- American National Standards Institute. "Synchronous Optical Network (SONET)—Basic Description Including Multiplex Structure, Rates and Formats." ANSI T1.105-1995

- American National Standards Institute. "Synchronous Optical Network (SONET)—Payload Mappings." ANSI T1.105.02–1998.

Simpson, W. "PPP over SONET/SDH." RFC 1619. May 1994.

Simpson, W., ed. "PPP in HDLC-like Framing," RFC 1662. *Daydreamer*. July 1994.

Malis, A. and W. Simpson. "PPP over SONET/SDH," RFC 2615. June 1999.

- 11. Hernandez-Valencia, E., Lucent Technologies. "A Generic Frame Format for Data over SONET (DoS)." March 2000.

- 12. Gorshe, C. and Steven. T1X1.5/99-204, T1 105.02. Draft Text for Mapping IEEE 802.3 Ethernet MAC Frames to SONET Payload. July 1999.

- 13. Hernandez-Valencia, E., Lucent Technologies. T1X1.5/2000-209. "Generic Framing Procedure (GFP) Specification." October 9-13, 2000.

- 14. ATM Forum, Technical Committee. UUTOPIA 3 Physical Layer Interface." Af-phy-0136.000. November 1999. 15. Can, R. and R. Tuck. "System Packet Interface Level 3 (SPÍ-3): OC-48 System Interface for Physical and Link-Layer Devices." OIF-SPI3-01.0. June 2000.

Figure 1. POSIC2GVC System Application Diagram

#### Overview

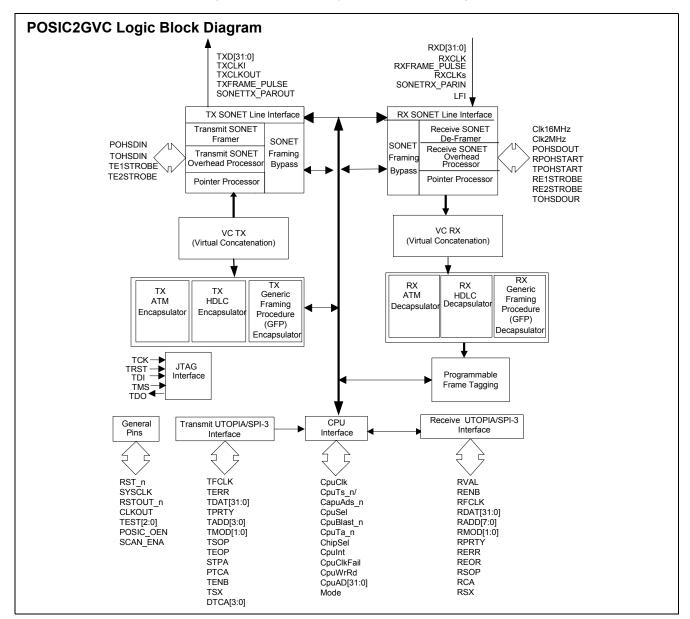

The CY7C9536B (POSIC2GVC™) is a highly integrated SONET/SDH framer device for transport of ATM and IP packets over SONET/SDH links. It features special functions and architecture to support next-generation optical networking protocols for both SONET/SDH and direct data-over-fiber networks. OIF-SPI (POS-PHY) level 3, UTOPIA level 3 and High-Bandwidth Synchronous Transfer (HBST) interfaces are provided on the system side.

POSIC2GVC performs complete SOH, LOH, and POH processing. Complete access to all overhead bytes is provided through register access via the host CPU interface. Access to selected overhead bytes are also available through serial port. Optional frame sync input and Transport Overhead (TOH) bypass enables better interface with STS-1 switched streams.

The virtual concatenation feature, with up to 16 channels, enables provisioning of secure, dedicated and right-sized bandwidth for Ethernet or ATM transport. Up to 16 virtual channels can be created with STS-1 or STS-3c granularity. Bandwidth from 50 Mbps to 1.2 Gbps can be allocated per channel.

POSIC2GVC supports packet over SONET/SDH as PPP in HDLC-like frame as per IETF rfc 1619/1662/2615 (PPP). POSIC2GVC also supports full duplex ATM over SONET/SDH transport in compliance with ITU I432.2.

POSIC2GVC supports the new generation Generic Framing Procedure (GFP) protocol encapsulation/Decapsulation over SONET/SDH. This protocol engine features wire rate framing, frame delineation and deframing with length-CRC pair header construct. Optional payload scrambling/descrambling and payload FCS are also provided.

Clear channel mode enables transport of any raw byte streams on selected virtual channels, while the rest of the channels are transporting data through any one of encapsulation/decapsulation engines.

The Programmable Frame Tagging Engine enables wire rate tagging of packets/frames. For new generation networking features such as MPLS, this engine can be programmed to tag based on existence/lack of specific label/field values, in the first 64 bytes of each packet. This way, packets are tagged for a variety of conditions, all programmable by the user, enabling sorting of packets in the incoming data stream and buffering packets accordingly. In a PPP application, control packets can optionally be sent over the host CPU interface directly.

SONET/SDH bypass mode allows use of this device for data transport in non SONET/SDH point-to-point and mesh optical networks.

#### **Transmit**

In the transmit direction, packets are received from the system side, encapsulated/framed and mapped into the SONET/SDH payload. Finally the TOH is added and SONET/SDH frames are passed onto the fiber side/line side interface on a parallel bus.

The system side interface can be programmed either as OIF-SPI level 3, or UTOPIA level 3 or HBST modes. In the UTOPIA mode, ATM cells can be received either in 54- (8-bit interface) or 56- (8-bit and 32-bit interfaces) bytes format. The sixth byte carries the channel number of the cell. In case of packets, the interface can be programmed as OIF-SPI level 3

or HBST operations. In these cases, the first data transfer always carry the channel number.

POSIC2GVC supports three basic types of encapsulation, namely (i) ATM, (ii) HDLC frame, and (iii) GFP (frames with length-CRC pair header construct based delineation). Clear channel or transparent mode (no encapsulation) is also supported. While in operation, only one type of encapsulation can be enabled for all VC channels. Some or all of the VC channels can be programmed as clear channels. For Clear Channels, the encapsulator engine will bypass the encapsulation and pass the packets without any processing to the next block

Encapsulated packets are transferred to the Virtual Concatenation (VC) block along with the channel number. The VC block rearranges the packet/frame flow to support the bandwidth allocation for virtual channels. Bandwidth is assigned by allocating a programmed number of SPEs to each channel. The VC block keeps track of the SPE under construction by the SONET/SDH framer block and transfers the packets meant for a given channel to the SONET framer. Since POSIC2GVC does not have a packet storage memory on-chip, a channel bandwidth balanced packet flow is expected from the system side. To enable such a balanced transfer, POSIC2GVC has internal FIFO of 512 bytes per channel. The status of FIFO is provided through pins to the link layer.

Finally, the SONET/SDH framer inserts the packet /cells into the SONET/SDH frame. All overhead bytes are added. All alarm bits and status bits are inserted based on the status of incoming frames as well as programming done by the host CPU. The scrambler meets relevant standards and can optionally be disabled. Frames are finally sent out on the fiber side interface. If programmed to do so, the SONET/SDH framer can be bypassed and encapsulated packets/frames can be sent directly to the fiber-side interface.

#### Receive

In the receive direction, SONET/SDH frames are received from the fiber side. Data packets/frames are extracted from the payload and passed onto the selected decapsulator engine after compensation for differential delay, in case of virtual concatenation. If the SONET/SDH framer is bypassed, the incoming data stream is directly passed over to the decapsulator engine. Data packets/frames are then decapsulated and sent to the Programmable Frame Tagging Engine. They are then analyzed and tagged before sent out to the system side via the OIF-SPI level 3, UTOPIA or HBST interface. Tagging of frames is optional.

SONET/SDH frames entering from the fiber side are synchronized and the frame boundary is identified with A1A2 bytes. Frames can be optionally synchronized with Frame\_Sync\_Input to identify the boundary. Descrambling is performed to retrieve scrambled frames. Complete processing of all overhead bytes, Section, Line and Path, is performed and all alarm bits are verified and alarms are raised as programmed. Full access to all overhead bytes is provided through register access. Access to selected overhead bytes is also provided through serial bus. The SONET/SDH deframing can be entirely bypassed.

The extracted payload is transferred to the VC block where it is reorganized to compensate for any differential delay encountered in the network from the virtual concatenation

channel. For this purpose, up to 256 frames are stored in external memory. The VC block then passes the payload stream to the selected decapsulator engine.

The selected decapsulator engine delineates the payload stream, decapsulates and extracts packets/cells from the stream. Descrambling of packets/cells is optional. The packets/cells are then sent out to the programmable Frame Tagging Engine.

The Frame Tagging Engine optionally tags the packet/cell as programmed. The packet/cell is then transferred to the link layer device, through the System Interface (OIF-SPI/UTOPIA level 3, or HBST), with an additional eight bits of information. Four bits specify the VC channel and the other four bits specify the tag.

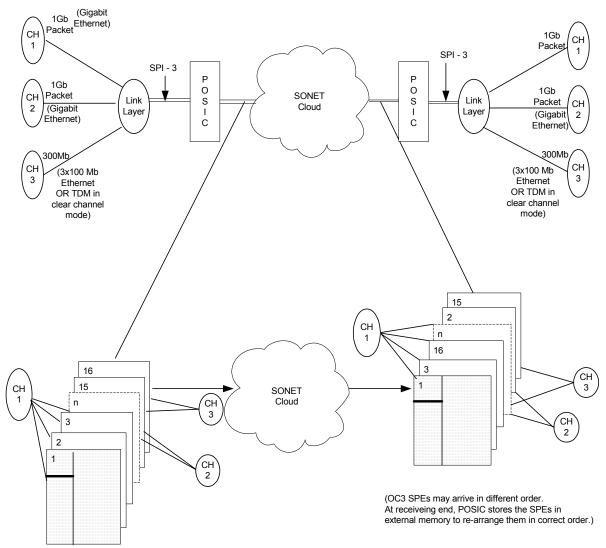

### **Virtual Concatenation**

Virtual concatenation creates multiple virtual payloads of different sizes within the incoming SONET/SDH frame, effectively creating multiple channels of different bandwidth.

The advantages of VC are:

- · Efficient and dedicated bandwidth allocation.

- Compatibility with TDM access infrastructure. Virtually concatenated channels can coexist with aware and nonaware Network Elements on the same shared access.

- Independence from upper layer data protocol/frame format.

- Fine granularity channels are extensible and easily provisionable.

POSIC2GVC supports VC for all types of packets/frames/protocols it transports on SONET/SDH. Up to 16 channels can be created using STS1/VC-3, STS3c/VC-4, STS12c/VC4-4c and STS24c/VC4-8c. POSIC2GVC also supports non-virtually concatenated channels such as STS3c and STS12c. *Table 1* shows a list of virtually concatenated channel bandwidth supported by POSIC2GVC.

Virtual concatenation requires specific overhead processing capabilities only at the path terminating equipment. It remains transparent at the intermediate nodes in the network. It is possible therefore that two or more different SPEs, virtually bonded to create a channel, travel through different routes in the network. Hence, they can arrive at the destination in the order different from the order at the point of origination. Delay encountered in arrival of two virtually concatenated SPEs in a frame is called differential delay. To compensate for differential delay, the SPE received earlier need to be stored until the particular SPE, which is previous in the order but faces longer travel time, arrives at the terminating node. POSIC2GVC can store up to 256 SONET/SDH frames in external memory, which can compensate for ±16 ms of differential delay. For differential delay higher than that, POSIC2GVC raises an alarm.

Table 1. Virtual Concatenated Channel Bandwidth<sup>[16]</sup>

| VC 2 40/CTC 4 40/17]                  | ( FO Mbas)   |

|---------------------------------------|--------------|

| VC-3-1v/STS-1-1v <sup>[17]</sup>      | (~50 Mbps)   |

| VC-3-2v/STS-1-2v                      | (~100 Mbps)  |

| VC-3-3v/STS-1-3v                      | (~150 Mbps)  |

| VC-3-4v/STS-1-4v                      | (~200 Mbps)  |

| VC-3-5v/STS-1-5v                      | (~250 Mbps)  |

| VC-3-6v/STS-1-6v                      | (~300 Mbps)  |

| VC-3-7v/STS-1-7v                      | (~350 Mbps)  |

| VC-3-8v/STS-1-8v                      | (~400 Mbps)  |

| VC-4-1v/STS-3c-1v <sup>[17]</sup>     | (~150 Mbps)  |

| VC-4-2v/STS-3c-2v                     | (~300 Mbps)  |

| VC-4-3v/STS-3c-3v                     | (~450 Mbps)  |

| VC-4-4v/STS-3c-4v                     | (~600 Mbps)  |

| VC-4-5v/STS-3c-5v                     | (~750 Mbps)  |

| VC-4-6v/STS-3c-6v                     | (~900 Mbps)  |

| VC-4-7v/STS-3c-7v                     | (~1.05 Gbps) |

| VC-4-8v/STS-3c-8v                     | (~1.2 Gbps)  |

| VC-4-4c-1v/STS-12c-1v <sup>[17]</sup> | (~600 Mbps)  |

| VC-4-4c-2v/STS-12c-2v                 | (~1.2 Gbps)  |

| VC4-8c-1v/STS-24c-1v <sup>[17]</sup>  | (~1.2Gbps)   |

| ·                                     | •            |

#### Notes:

16. All VC mode channel configurations require a SYSCLK frequency of 133.33 MHz.

17. Please refer to device manual for allowed combinations of Virtual Channels using STSX-1v/VCX-1v granularity.

Figure 2. Explanation of Virtual Concatenation

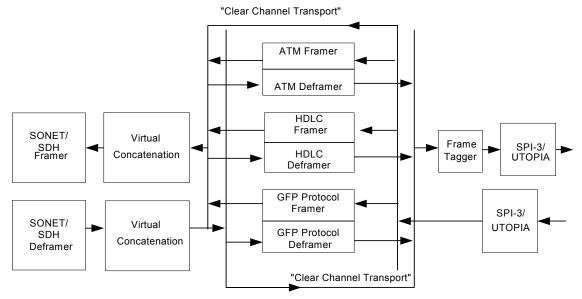

### **Generic Frame Encapsulation/Decapsulation**

POSIC2GVC supports a variety of protocols/packets/frames to transport over a SONET/SDH link. For clarity of reference, in this document, framing of packets/cells into these protocols is called "encapsulation," and the engine performing encapsulation is called an "encapsulator." Similarly, deframing is called "decapsulation," and the engine performing decapsulation is called a "decapsulator."

Three different encapsulator and decapsulator engines are integrated into POSIC2GVC.

The ATM encapsulator computes and adds the HEC field, scrambles the cells and passes on to the VC block. In case of underflow, ATM encapsulator also creates programmable idle cells.

The ATM decapsulator checks for HEC and integrity of the cell. It descrambles the cells, isolates and discards idle cells and passes ATM cells to the Programmable Frame Tagging Engine.

HDLC encapsulator performs Asynchronous Control Character Mapping (ACCM), stuffing, flag sequence insertion and scrambling. Optionally, up to 16 bytes of header is inserted ahead of the packet while framing the packet. The host CPU can program this 16-byte header through register programing. Such programmable header insertion enables encapsulation of PPP, frame relay or other protocol.

The HDLC decapsulator descrambles the incoming byte stream and searches the flag sequence. Upon finding the boundary, decapsulator performs destuffing and ACCM demapping before passing the packets to the Programmable Frame Tagging Engine.

The Generic Framing Procedure (GFP) Encapsulator/Decapsulator supports delineation based on length-CRC pair header construct. In the transmit direction, it computes a 16-bit header CRC based on 2-byte length value received from the link layer device. The length and CRC fields are inserted as header of the frame ahead of the packet. Scrambling of the payload and 32-bit payload CRC computation and insertion are optional.

### **Protocol/Frame Types**

- 1) Only one framer/deframer active

- 2) Selected VC channels can be declared "clear channel transport"

Figure 3. Protocol Framers

In the receive direction, GFP frames are delineated based on the length-CRC construct pair header, integrity verified, payload extracted, optionally descrambled and sent to the Programmable Frame Tagging Engine.

Any selected VC channel can be programmed to become a 'clear channel'. The encapsulator and decapsulator remain in transparent mode for the clear channel and data passes through without any modification. This feature can be used to transport any raw data streams on a portion of bandwidth while the rest of the bandwidth is utilized for protocol traffic.

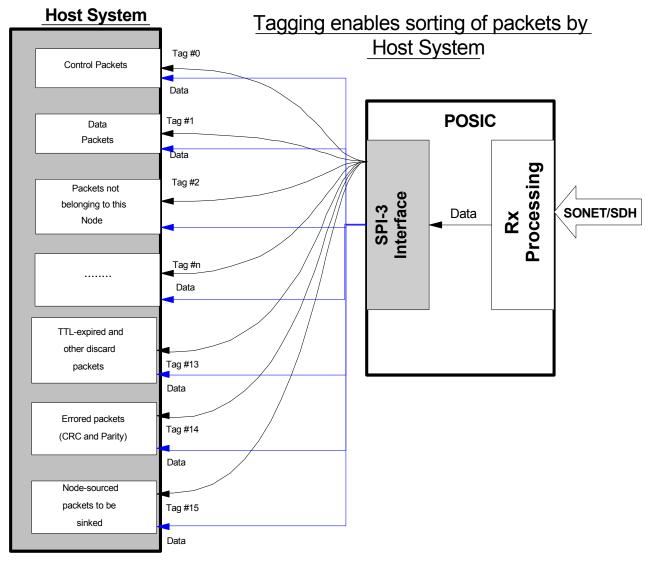

### **Programmable Frame Tagging Engine**

The Programmable Frame Tagging Engine provides preclassification of the packets/frames at the wire rate. This helps in utilizing the link layer device more efficiently.

The Programmable Frame Tagging Engine enables the user to perform preclassification of all the incoming packets into one of the 16 possible categories. Since each channel can have up to 16 different categories, and up to 16 virtual concatenated channels are possible, this engine supports up to 256 different categories. For classification, two-pass comparison can be specified. For each comparison a field of up to six bytes can be selected within the first 64 bytes of the packet and compared with up to 16 programmed values. The comparison is on a bit by bit basis and any bit comparison can be masked with a user programmable mask register. A four-bit tag is attached to the cell/packet, based on the match. Host CPU can program these parameters through register programming.

The following drawing demonstrates one possible combination of classification with the help of the Programmable Frame Tagging Engine.

The following functions can be achieved with the help of the Programmable Frame Tagging Engine:

- Incoming packet analysis to parse packets/frames/cells at wire speed.

- User-programmable routing of control packets to CPU for processing.

- Incoming frames tagged based on bits (such as congestion) in incoming packets.

- User-programmable offset to locate Ethernet and other frames within DOS and other proprietary MAN networking protocols to allow MPLS processing.

#### **SONET/SDH Bypass**

POSIC2GVC supports the SONET/SDH framer/deframer bypass mode. Host CPU can program such bypass. In this mode, the data frames/packets, encapsulated by one of the encapsulators, will be transmitted transparently through VC and SONET/SDH blocks to the fiber side and vice versa.

#### System Interface

The system interface is programmable. For application in an ATM system, POSIC2GVC system interface can be programmed to be PHY side interface as per UTOPIA level 3 specifications.

For variable length packets, POSIC2GVC system interface can be programmed to be OIF-SPI level 3. ATM cells can also be transferred over OIF-SPI level 3 bus.

System interface can be programmed in HBST mode. In this case, a separate set of address pins are supported on the system side. This mode supports high-speed burst access.

# System Memory at

Figure 4. Frame Tagging Engine Data Sorting Diagram

#### **CPU Interface**

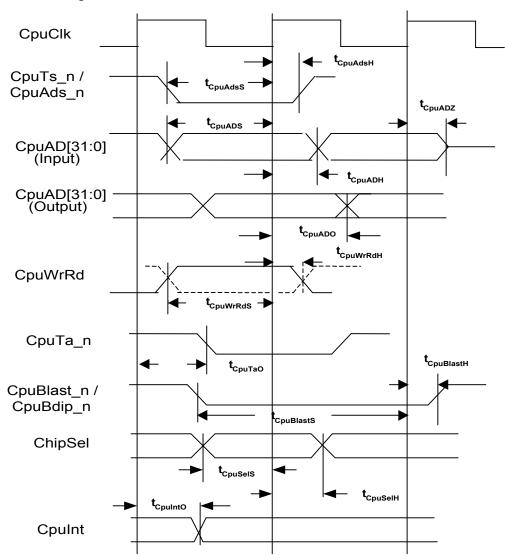

POSIC2GVC can interface with 16-bit or 32-bit CPU. The CPU interface can be pin configured to be compatible with Motorola or Intel bus interface. The CPU interface provides access to all registers of POSIC2GVC, collates all interrupt generated by various blocks and also supports control packet transfers.

#### **Line Interface**

The line interface/fiber side interface is configurable as 8 bit, 16-bit or 32-bit depending on the clock frequency and data rate. The options shown in *Table 2* are available.

**Table 2. Configuration Options**

| Bus Width | Clock Frequency | Line Rate    |

|-----------|-----------------|--------------|

| 8 bits    | 19.44 MHz       | OC-3/STM-1   |

| 8 bits    | 77.76 MHz       | OC-12/STM-4  |

| 16 bits   | 38.88 MHz       | OC-12/STM-4  |

| 16 bits   | 155.52 MHz      | OC-48/STM-16 |

| 32 bits   | 77.76 MHz       | OC-48/STM-16 |

#### **Clock Source**

The transmit clock can be programmed to be one of the following sources:

- · Received clock supplied by the PHY

- · External transmit clock source.

### **APS Port**

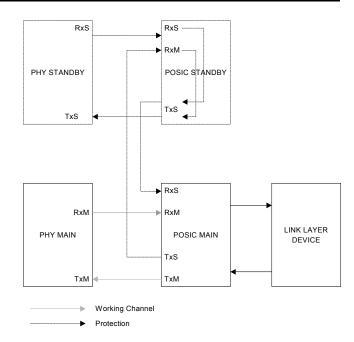

POSIC2GVC provides a 16-bit APS port for 1+1 protection. The support of a main and standby PHY interface connectivity allows several different APS implementation options using POSIC2GVC.

#### **Multi-Framer APS Implementation**

Two POSIC2GVC devices can be connected to two different transceivers, optics and fibers. POSIC2GVC enables protection switching with only one device being main and connected to link layer. The standby POSIC2GVC device is connected to the main POSIC2GVC device and it is controlled by host CPU. POSIC2GVC provides APS byte information to the host CPU. The host CPU is expected to take a protection switching decision and provide necessary instructions to both POSIC2GVC devices.

In case of protection switching, in the transmit direction, the main POSIC2GVC will perform all other operations as programmed, except some of the line and section processing of SONET/SDH framing. The main POSIC2GVC device will then pass on the SPEs to the standby device through the APS port. The standby device will then perform the rest of the line and section processing and transport SONET/SDH frames over standby fiber.

Similarly, in case of protection switched mode, on the receive side, the standby device will process some of the line and section overhead and transfer the frames to main device through the APS port. The main device will perform the rest of the processing in the receive side.

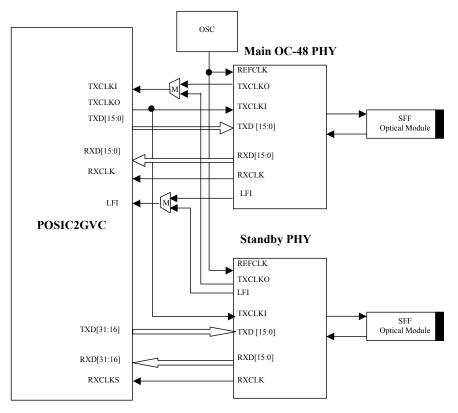

#### **Single Framer APS Implementation**

A main and slave PHY device can be interfaced directly to the main and APS ports of a single POSIC2GVC device. In this case, the main PHY is connected to the main line interface and the standby PHY is connected to the APS port.

Figure 5. POSIC2GVC APS Implementation using Two POSIC Devices

In the POSIC2GVC transmit path, SONET/SDH data is bridged across the main and APS ports (per linear 1+1 APS requirements). When protection switching, POSIC2GVC can be programmed to switch line inputs from the main receive port to the APS receive port, or vice versa.

This APS scheme provides solely optical/PHY link level protection.

Figure 6. POSIC2GVC APS Implementation Using a Single POSIC Device

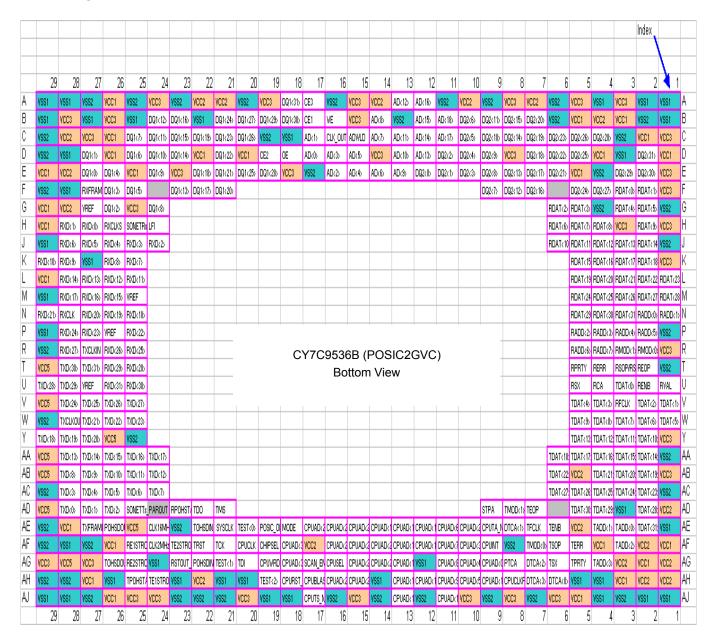

### **Pin Configuration**

# **Pin Description**

| Signal Name         | I/O   | Pad Type              | Pins | JTAG | Pin Description                                                                                                                                                                                                                                                |

|---------------------|-------|-----------------------|------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Line Interface Sign | als   |                       |      |      |                                                                                                                                                                                                                                                                |

| RXFRAME_PULSE       | I     | HSTL/LVTTL<br>/LVPECL | 1    | N    | Optional frame pulse input for line interface. Active HIGH.                                                                                                                                                                                                    |

| TXFRAME_PULSE       | 0     | HSTL/LVTTL            | 1    | N    | Frame pulse output for line interface. Active HIGH.                                                                                                                                                                                                            |

| RXD[31:0]           | I     | HSTL/LVTTL<br>/LVPECL | 32   | N    | <b>32-bit single ended receive data bus for SONET/SDH link</b> . This bus can be configured as two 16-bit buses in APS operation.                                                                                                                              |

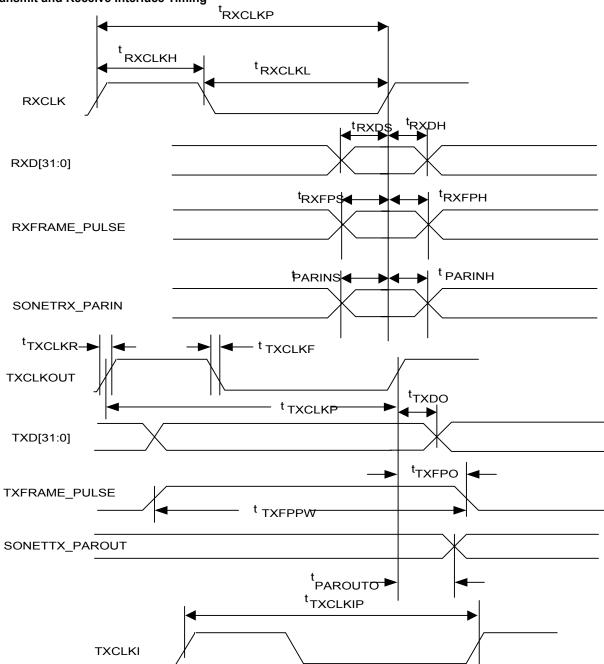

| RXCLK               | I     | HSTL/LVTTL<br>/LVPECL | 1    | N    | Receive clock input from the PHY device for line interface.                                                                                                                                                                                                    |

| RXCLKs              | I     | HSTL/LVTTL<br>/LVPECL | 1    | N    | Receive clock input from the Slave PHY device for SONET/SDH link to support APS.                                                                                                                                                                               |

| TXCLKOUT            | 0     | HSTL/LVTTL            | 1    | N    | <b>Transmit Clock to physical layer device for line interface</b> . This will be RXCLK or the TXCLKI based on the clock selection in the SONET Tx block register. During loopback this is same as the RXCLK.                                                   |

| TXCLKI              | I     | HSTL/LVTTL<br>/LVPECL | 1    | N    | Input transmit clock from physical layer device for line interface.                                                                                                                                                                                            |

| TXD[31:0]           | 0     | HSTL/LVTTL            | 32   | N    | <b>32-bit single ended transmit data bus for line interface</b> . This bus can be configured as two 16-bit buses in APS operation.                                                                                                                             |

| SONETTX_PAROU<br>T  | 0     | HSTL/LVTTL            | 1    | N    | <b>SONET Tx Parity Output</b> . Can be ODD/EVEN parity, as programmed in the SONET/SDH Tx block register.                                                                                                                                                      |

| SONETRX_PARIN       | _     | HSTL/LVTTL<br>/LVPECL | 1    | N    | <b>SONET Rx Parity Input</b> . Can be ODD/EVEN parity, as programmed in the SONET/SDH Rx block register.                                                                                                                                                       |

| LFI_n               | _     | LVTTL                 | 1    | Υ    | Line fault indicator. When LOW, this signal indicates that the PHY has detected Loss of Optical signal on the SONET/SDH link.                                                                                                                                  |

| Overhead Bytes A    | ccess | —Serial Ports         |      |      |                                                                                                                                                                                                                                                                |

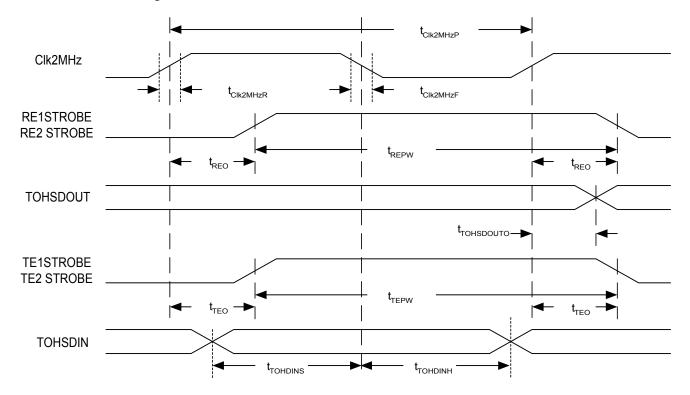

| Clk2MHz             | 0     | LVTTL                 | 1    | Υ    | <b>TOH Serial Port Clock Output</b> . TOHDout is clocked out on rising edge of this clock and TOHDin is latched-in with falling edge of this clock. The frequency is 2.048 MHz, derived from SysClk.                                                           |

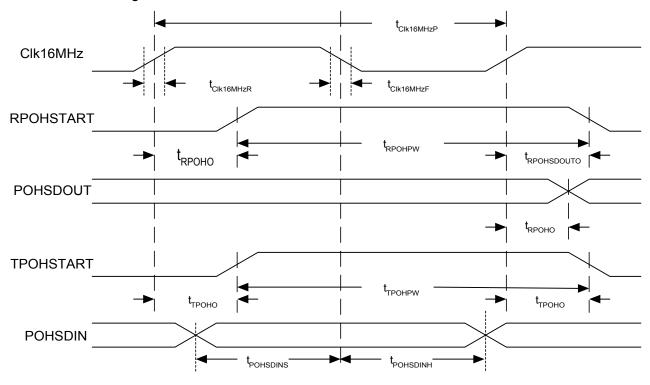

| Clk16MHz            | 0     | LVTTL                 | 1    | Y    | <b>POH Serial Port Clock Output</b> . POHDout is clocked out on rising edge of this clock and POHDin is latched-in with falling edge of this clock. The frequency is 16.625 MHz, derived from SysClk                                                           |

| TE1STROBE           | 0     | LVTTL                 | 1    | Y    | <b>Transmit E1 Strobe</b> . Transmit TOH serial port data start indication. Active HIGH pulse generated once in every 125 ms. Indicates the first bit of E1 Byte.                                                                                              |

| TE2STROBE           | 0     | LVTTL                 | 1    | Υ    | <b>Transmit E2 Strobe</b> . Active HIGH pulse generated once in every 125 ms. Indicates the first bit of E2 Byte.                                                                                                                                              |

| TPOHSTART           | 0     | LVTTL                 | 1    | Υ    | <b>Transmit POH Serial Port Data Start Indication</b> . Active HIGH pulse generated once in every 125 ms.                                                                                                                                                      |

| TOHSDIN             | I     | LVTTL                 | 1    | Υ    | Transport over head serial port data input.                                                                                                                                                                                                                    |

| POHSDIN             | ı     | LVTTL                 | 1    | Υ    | Path over head serial port data input.                                                                                                                                                                                                                         |

| RE1STROBE           | 0     | LVTTL                 | 1    | Υ    | Receive E1 Strobe. Receive TOH serial port data start indication. Active HIGH pulse generated once in every 125 ms. Indicates that the POSIC2GVC expects the first bit of the first byte of E1 should accompany the next clock edge. MSB is transmitted first. |

| RE2STROBE           | 0     | LVTTL                 | 1    | Υ    | <b>Receive E2 Strobe</b> . Active HIGH pulse generated once in every 125 ms. Indicates that the POSIC2GVC expects the first bit of the first byte of E2 should accompany the next clock edge. MSB is transmitted first                                         |

| RPOHSTART           | 0     | LVTTL                 | 1    | Υ    | Receive POH Serial Port Data Start Indication. Active HIGH pulse generated once in every 125 ms. Indicates that the POSIC2GVC expects the first bit of the first byte of RPOH should accompany the                                                             |

|                     |       |                       |      |      | next clock edge.                                                                                                                                                                                                                                               |

| Signal Name                                                                                                                          | I/O | Pad Type | Pins | JTAG | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------|-----|----------|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| POHSDOUT                                                                                                                             | 0   | LVTTL    | 1    | Υ    | Path over head serial port data output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| System Interface (OIF-SPI level 3/UTOPIA level 3/HBST) signals (in this section, POS = OIF - SPI Level 3, ATM = Utopia level 3 mode) |     |          |      |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

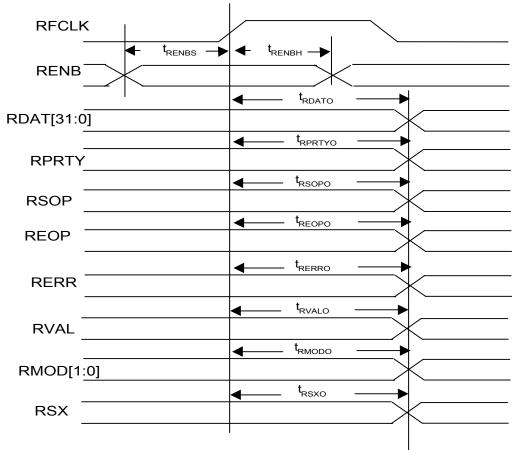

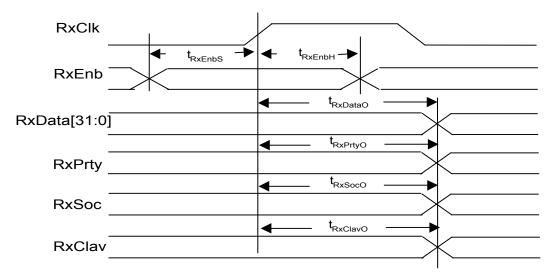

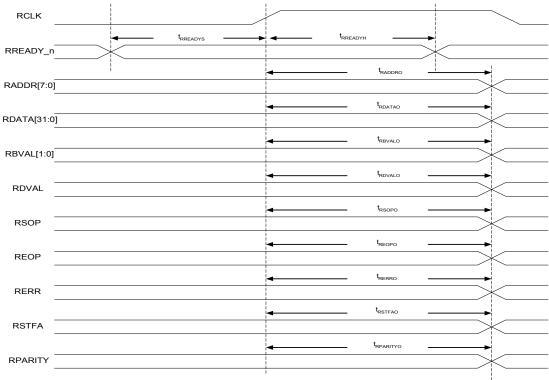

| RVAL                                                                                                                                 | 0   | LVTTL    | 1    | N    | POS: Receive Data Valid (RVAL) signal. RVAL indicates the validity of receive data signals. RVAL will transition LOW when receive FIFO is empty or at the end of a packet. When RVAL is HIGH, the RDAT[31:0], RPRTY, RMOD[1:0], RSOP, REOP, and RERR signals are valid. When RVAL is LOW, the RDAT[31:0], RPRTY, RMOD[1:0], RSOP, REOP, and RERR signals are invalid and must be disregarded. HBST: Receive Data Valid (RDVAL) signal. The RDATA, RBVAL, RSOP, REOP, RERR, and RADDR are valid when this signal is active.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| RENB                                                                                                                                 | I   | LVTTL    | 1    | N    | POS: Receive Read Enable (RENB) signal. The RENB signal is used to control the flow of data from the receive FIFOs. During data transfer, RVAL must be monitored as it will indicate if the RDAT[31:0], RPRTY, MOD[1:0], RSOP, REOP, RERR and RSX are valid. The system may deassert RENB at anytime if it is unable to accept data from POSIC2GVC. When RENB is sampled LOW by POSIC2GVC, a read is performed from the receive FIFO and the RDAT[31:0], RPRTY, RMOD[1:0], RSOP, REOP, RERR, RSX and RVAL signals are updated on the following rising edge of RFCLK. When RENB is sampled HIGH by POSIC2GVC, a read is not performed and the RDAT[31:0], RPRTY, RMOD[1:0], RSOP, REOP, RERR, RSX and RVAL signals will not updated. ATM: Enable data transfers (RxENb*) signal Enables port selection. HBST: Receive Data Ready (RREADY_n) signal Active LOW signal, indicates ready to accept data. The device will send valid data 2 clocks after the assertion of this signal. |  |  |  |  |

| RFCLK                                                                                                                                | I   | LVTTL    | 1    | N    | POS: Receive FIFO Write Clock (RFCLK). RFCLK is used to synchronize data transfer transactions between the LINK Layer device and the POSIC2GVC. RFCLK may cycle at a rate up to 100 MHz. ATM: Transfer/interface clock (RxClk) HBST: Receive Clock (RCLK). Max 104 MHz Receive Clock for level-3 operation. All signals are latched out on the rising edge of this clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| Signal Name | I/O | Pad Type |    | JTAG | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------|-----|----------|----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RDAT[31:0]  | 0   | LVTTL    | 32 | N    | POS: Receive Packet Data Bus (RDAT[31:0]) The RDAT[31:0] bus carries the packet octets that are read from the receive FIFO and the in-band port address of the selected receive FIFO. RDAT[31:0] is considered valid only when RVAL is asserted. Given the defined data structure, bit 31 is received first and bit 0 is received last.  ATM: Receive Cell Data Bus (RxData[31:0]) The RDAT[31:0] bus carries the Cell octets that are read from the receive FIFO. RDAT[31:0] is considered valid only when RENB is asserted. Given the defined data structure, bit 31 is received first and bit 0 is received last RDAT[31:0] is updated on the rising edge of RCLK. This bus is big-endian in format.  HBST: Receive Data Bus (RDATA[31:0]) 32-bit Data Bus, the data is valid when RDVAL signal is active.                               |

| RADD[7:0]   | 0   | LVTTL    | 8  | N    | HBST: Receive Port Address (RADDR[7:0]). When RDVAL signal is active, this address on this bus indicates port address in RADDR[3:0] and tag value in RADDR[7:4]. In single-channel mode all 8 bits will contain the tag value. RADDR is considered valid only when RDVAL is asserted                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| RMOD[1:0]   | 0   | LVTTL    | 2  | N    | POS: Receive Word Modulo (RMOD[1:0]) signal. RMOD[1:0] indicates the number of valid bytes of data in RDAT[31:0]. The RMOD bus should always be all zero, except during the last double-word transfer of a packet on RDAT[31:0]. When REOP is asserted, the number of valid packet data bytes on RDAT[31:0] is specified by RMOD[1:0] RMOD[1:0] = "00" RDAT[31:0] valid RMOD[1:0] = "01" RDAT[31:8] valid RMOD[1:0] = "10" RDAT[31:16] valid RMOD[1:0] = "11" RDAT[31:24] valid RMOD[1:0] is considered valid only when RVAL is asserted. In 16-bit mode, only RMOD[0] is valid. RMOD[0] = "1" RDAT[15:8] valid (16-bit mode) RMOD[0] = "0" RDAT[15:0] valid (16-bit mode) HBST: Receive Data Byte Valid (RBVAL[1:0]) signals. This indicates the number of bytes data bytes valid on the RDATA bus, 00 = 4 bytes valid, 11 = 1 byte valid. |

| RPRTY       | 0   | LVTTL    | 1  | N    | POS: Receive Parity (RPRTY) signal. The receive parity (RPRTY) signal indicates the parity calculated over the RDAT bus. RPRTY supports both odd and even parity. ATM: Receive Parity (RxPrty) signal. Data bus odd parity. HBST: Receive bus parity (RPARITY) signal. Receive bus parity, Even/Odd parity calculated on the data bus alone or on all the bus signals (RDATA, RADDR, RDVAL, RBVAL, RSOP, REOP, RERR).                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Signal Name | I/O | Pad Type | Pins | JTAG | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------|-----|----------|------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RERR        | 0   | LVTTL    | 1    | N    | POS: Receive error indicator (RERR) signal. RERR is used to indicate that the current packet is aborted and should be discarded. RERR shall only be asserted when REOP is asserted. Conditions that can cause RERR to be set may be, but are not limited to, FIFO overflow, abort sequence detection and FCS error. RERR is considered valid only when RVAL is asserted. HBST: Receive error indicator (RERR) signal. A HIGH indicates the current packet or cell has error.                                                                                                                                                                         |

| REOP        |     | LVTTL    | 1    | N    | POS: Receive End Of Packet (REOP) signal. REOP is used to delineate the packet boundaries on the RDAT bus. When REOP is HIGH, the end of the packet is present on the RDAT bus. REOP is required to be present at the end of every packet and is considered valid only when RVAL is asserted. HBST: End of Packet/cell (REOP) signal. A high indicates the end of packet or cell.                                                                                                                                                                                                                                                                    |

| RSOP/RSOC   | 0   | LVTTL    | 1    | N    | POS: Receive Start of Packet (RSOP) signal. RSOP is used to delineate the packet boundaries on the RDAT bus. When RSOP is HIGH, the start of the packet is present on the RDAT bus. RSOP is required to be present at the start of every packet and is considered valid when RVAL is asserted. ATM: Receive start of cell (RxSOC). This signal marks the start of a cell structure on the RxData bus. The first word of the cell structure is present on the RxData[31:0] bus when RxSOC is HIGH. RxSOC is updated on the rising edge of RxClk. HBST: Receive Start of Packet/cell (RSOP) signal. A HIGH indicates start of packet or start of cell. |

| RCA         | 0   | LVTTL    | 1    | N    | ATM: UTOPIA Receive Cell Available (RxClav). RxClav will be asserted, whenever a minimum of 1 cell of data is available in the Receive FIFO. HBST: Receive FIFO available (RSTFA) signal. RSTFA indicates when data is available in the receive FIFO. RSTFA will be asserted, whenever receive FIFO has at least predefined number of bytes to be read (the number of bytes is user programmable). RSTFA is updated on the rising edge of RCLK.                                                                                                                                                                                                      |

| RSX         | 0   | LVTTL    | 1    | N    | POS: Receive start of transfer signal. RSX indicates when the in-band port address is present on the RDAT bus. When RSX is HIGH and RVAL is LOW, the value of RDAT[7:0] is the address of the receive FIFO to be selected by POSIC2GVC. Subsequent data transfers on the RDAT bus will be from the port as specified by the in band address.                                                                                                                                                                                                                                                                                                         |

| Signal Name | I/O | Pad Type | Pins | JTAG | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------|-----|----------|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

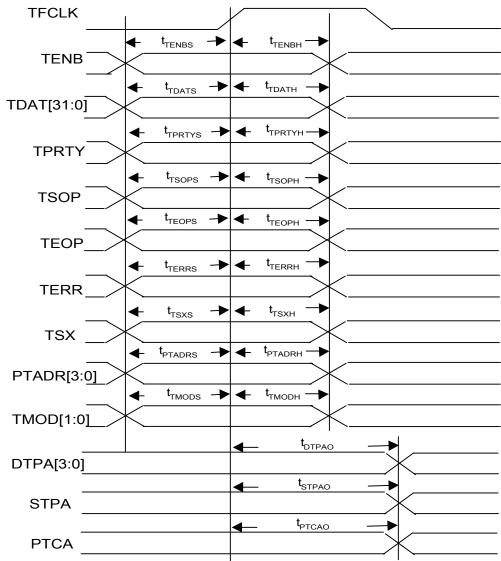

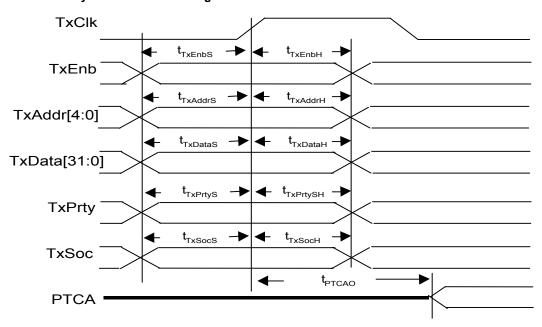

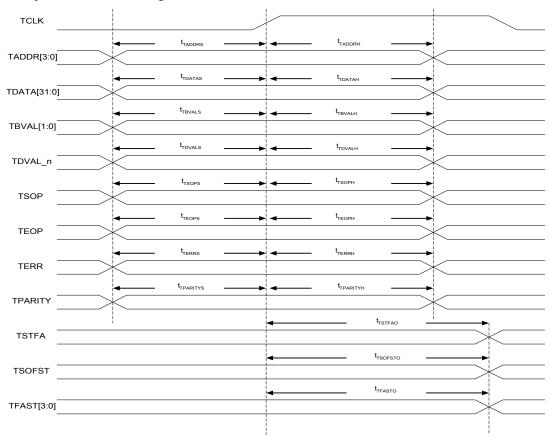

| TFCLK       | I   | LVTTL    | 1    | N    | POS: Transmit FIFO Write Clock (TFCLK). TFCLK is used to synchronize data transfer transactions between the LINK Layer device and POSIC2GVC. TFCLK may cycle at a rate up to 100 MHz. ATM: Transfer/interface clock (TxClk). HBST: Transmit Clock (TCLK). Max 104 MHz Transmit Clock for level-3 operation. All transmit signals are sampled on rising edge of the clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| TERR        | I   | LVTTL    | 1    | N    | POS: Transmit Error Indicator (TERR) signal. TERR is used to indicate that the current packet should be aborted. When TERR is set HIGH, the current packet is aborted. TERR should only be asserted when TEOP is asserted. HBST: Transmit Error Indicator (TERR) signal. A HIGH indicates the current packet or cell has error.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| TENB        | I   | LVTTL    | 1    | N    | POS: Transmit Write Enable (TENB) signal. The TENB signal is used to control the flow of data to the transmit FIFOs. When TENB is HIGH, the TDAT, TMOD, TSOP, TEOP, and TERR signals are invalid and are ignored by POSIC2GVC. The TSX signal is valid and is processed by POSIC2GVC when TENB is HIGH. When TENB is LOW, the TDAT, TMOD, TSOP, TEOP and TERR signals are valid and are processed by POSIC2GVC. Also, the TSX signal is ignored by POSIC2GVC when TENB is LOW. ATM: Transmit write enable (TxEnb*). This signal is an active LOW input which is used to initiate writes to the transmit FIFOs. When TxEnb* is sampled HIGH, the information sampled on the TxData, TxPrty, and TxSOC signals are invalid. When TxEnb* is sampled LOW, the information sampled on the TxData, TxPrty, and TxSOC signals are valid and are written into the transmit FIFO. TxEnb* is sampled on the rising edge of TxClk. HBST: Transmit Data Valid (TDVAL_n) signal. The TDVAL_n signal is used to control the flow of data to the transmit FIFOs. When TDVAL_n is HIGH, the TDATA, TBVAL, TSOP, TADDR, TSOP, TEOP, and TERR signals are valid and are processed by POSIC2GVC. |

| Signal Name | I/O | Pad Type | Pins | JTAG | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------|-----|----------|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TDAT[31:0]  | I   |          | 32   | N    | POS: Transmit Packet Data Bus (TDAT) bus. This bus carries the packet octets that are written to the selected transmit FIFO and the in-band port address to select the desired transmit FIFO. The TDAT bus is considered valid only when TENB is simultaneously asserted. Data is transmitted in big endian order on TDAT[31:0]. Given the defined data structure, bit 31 is transmitted first and bit 0 is transmitted last. ATM: Transmit Data Bus (TxData) bus. This data bus carries the ATM cell. Data on this bus is valid only if TxEnb* is HIGH. TxData[31:0] is three-stated if TxEnb* is LOW. TxData[31:0] is updated on the rising edge of TxClk. HBST: Transmit Data Bus (TDATA) bus. 32-bit Data bus. The data is valid when TDVAL_n signal is active. |

| TPRTY       | ı   | LVTTL    | 1    | N    | POS: Transmit bus parity (TPRTY) signal. The transmit parity (TPRTY) signal indicates the parity calculated over the TDAT bus. TPRTY is considered valid only when TENB is asserted. TPRTY is supported for both even and odd parity. ATM: Transmit bus parity (TxPrty). This signal indicates the parity on the TxData bus. A parity error is indicated by a status bit and a maskable interrupt. TxPrty is considered valid only when TxEnb* is simultaneously asserted. TxPrty is sampled on the rising edge of TxClk. HBST: Transmit bus parity (TPARITY) signal. Even/Odd parity calculated on the data bus alone or on all the bus signals (TDATA, TADDR, TDVAL_n, TBVAL, TSOP, TEOP, and TERR).                                                              |

| TADD[3:0]   | I   | LVTTL    | 4    | N    | POS: Transmit address bus (PTADR) bus. Address driven by Link layer to poll and select the appropriate POSIC2GVC channel (port). The value for the Transmit and Receive portions of a channel should be identical. Address 31 indicates a null port. ATM: Transmit address bus (TxAddr) bus. Address of POSIC2GVC channel being selected. HBST: Port Address (TADDR) bus. Address driven by the Link Layer to indicate the port address of current data transfer.                                                                                                                                                                                                                                                                                                   |

| Signal Name | I/O | Pad Type |   | JTAG | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------|-----|----------|---|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TMOD[1:0]   | I   | LVTTL    | 2 | N    | POS: Transmit Word Modulo (TMOD[1:0]) signal. TMOD[1:0] indicates the number of valid bytes of data in TDAT[31:0]. The TMOD bus should always be all zero, except during the last double-word transfer of a packet on TDAT[31:0]. When TEOP is asserted, the number of valid packet data bytes on TDAT[31:0] is specified by TMOD[1:0]. TMOD[1:0] = "00" TDAT[31:0] valid TMOD[1:0] = "01" TDAT[31:8] valid TMOD[1:0] = "10" TDAT[31:16] valid TMOD[1:0] = "11" TDAT[31:24] valid In 16-bit mode, only TMOD[0] is valid. TMOD[0] = "1" TDAT[15:8] valid (16-bit mode) TMOD[0] = "0" TDAT[15:0] valid (16-bit mode) HBST: Transmit byte valid (TBVAL[1:0]) signals. This indicates the number of bytes data bytes on the TDATA bus, 00 = 4 bytes valid, 11 = 1 byte valid.                                                                                  |

| TSOP        | ı   | LVTTL    | 1 | N    | POS: Transmit Start of Packet (TSOP) signal. TSOP is used to delineate the packet boundaries on the TDAT bus. When TSOP is HIGH, the start of the packet is present on the TDAT bus. TSOP is required to be present at the beginning of every packet and is considered valid only when TENB is asserted. ATM: Transmit start of cell (TxSOC) signal. This signal marks the start of a cell structure on the TxData bus. TxSOC must be present for each cell. TxSOC is considered valid only when TxEnb* is simultaneously asserted. TxSOC is sampled on the rising edge of TxClk. HBST: Transmit Start of Packet (TSOP) signal. A high indicates the start of packet or start of cell.                                                                                                                                                                     |

| TEOP        | 1   | LVTTL    | 1 | N    | POS: Transmit End of Packet (TEOP) signal. TEOP is used to delineate the packet boundaries on the TDAT bus. When TEOP is HIGH, the end of the packet is present on the TDAT bus. TEOP is required to be present at the end of every packet and is considered valid only when TENB is asserted. HBST: Transmit End of Packet (TEOP) signal. A HIGH indicates the end of packet or end of cell.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| DTCA[3:0]   | 0   | LVTTL    | 4 | N    | POS: Transmit Packet Available (DTPA) bus. This signal provides direct status indication the fill status of the transmit FIFO. Note that, regardless of what fill level TPA is set to indicate "full" at, the transmit packet processor can store 256 bytes of data. When DTPA transitions HIGH, it indicates that the transmit FIFO has enough room to store a configurable number of data bytes. This transition level is selected in the CPU programmable registers. When TPA transitions LOW, it indicates that the transmit FIFO is either full or near full as specified by the CPU programmable registers. DTPA is updated on the rising edge of TFCLK. HBST: Polled FIFO available Status (TFAST) bus. When the signal TSOFST is active, the status of channels 0,4,8,12 is given first followed by 1,5,9,13 and 2,6,10,14 and the last 3,7,11,15. |

| Signal Name | I/O | Pad Type | Pins | JTAG | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------|-----|----------|------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STPA        | 0   | LVTTL    | 1    | N    | POS: Selected Channel Transmit Packet Available (STPA) signal. STPA transitions HIGH when a predefined minimum number of bytes are available in the selected transmit FIFO. Once HIGH, STPA indicates that transmit FIFO is not full. When STPA transitions LOW, it optionally indicates that transmit FIFO is full or near full (user programmable). STPA always provides status indication for the selected channel in order to avoid FIFO overflows while polling is performed. STPA is three-stated when TENB is deasserted in the previous cycle. STPA is also deasserted when either the null-port address (0x1F) or an address not matching the POSIC2GVC address is presented on the TADR[3:0] signals when TENB is sampled HIGH (has been de-asserted during the previous clock cycle). STPA is mandatory only if packet-level transfer mode is supported. It is not be driven in byte-level mode. ATM: There is no corresponding pin definition in ATM mode, however, this pin will output the same signal as STPA in POS mode HBST: FIFO Available Status (TSTFA) signal. FIFO available status of the selected port is reflected on this pin two clocks after detecting the port address when the TDVAL signal is active.                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| PTCA        | 0   | LVTTL    | 1    | N    | POS: Polled-Port Transmit Packet Available (PTPA) signal. PTPA transitions HIGH when a predefined (user-programmable) minimum number of bytes are available in the polled transmit FIFO. Once HIGH, PTPA indicates that the transmit FIFO is not full. When PTPA transitions LOW, it optionally indicates that transmit FIFO is full or near full (user-programmable). PTPA allows polling the POSIC2GVC channel selected by TADR[3:0] when TENB is asserted. PTPA is driven by a POSIC2GVC when its address is polled by TADR[3:0]. POSIC2GVC will three-state PTPA when either the null-port address (0x1F) or an address not matching POSIC2GVC is provided on TADR[3:0]. PTPA is mandatory only if in packet-level transfer mode. It will not be driven in byte-level mode. ATM: UTOPIA Transmit Cell Available (TxClav) The TxClav signal indicates when a cell is available in the transmit FIFO for the port polled by TxAddr[3:0] when TxEnb* is asserted. When HIGH, TxClav indicates that the corresponding transmit FIFO is not full and a complete cell may be written. When TxClav goes LOW, it can be configured to indicate either that the corresponding transmit FIFO is near full or that the corresponding transmit FIFO is full. TxClav is three-stated when either the null-Port address (0x1F) or an address not matching the address space set is latched from the TxAddr[4:0] inputs when TxEnb* is HIGH. TxClav is updated on the rising edge of TxClk. HBST: FIFO Available status on TFAST bus (TSOFST) signal. Active HIGH pulse indicates the start of FIFO available status on TFAST bus. This signal is repeated once in every four clocks. |

| TSX         | I   | LVTTL    | 1    | N    | POS: Transmit Start of Transfer (TSX) signal. TSX indicates inband port address on the TDAT bus. When TENB is HIGH and TSX is asserted (HIGH), the value of TADR[3:0] is the address of transmit FIFO selected. TSX is valid only when TENB is deasserted.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Signal Name        | I/O   | Pad Type       |       | JTAG | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------------|-------|----------------|-------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Memory Interface f | or Vi | rtual Concaten | ation | •    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

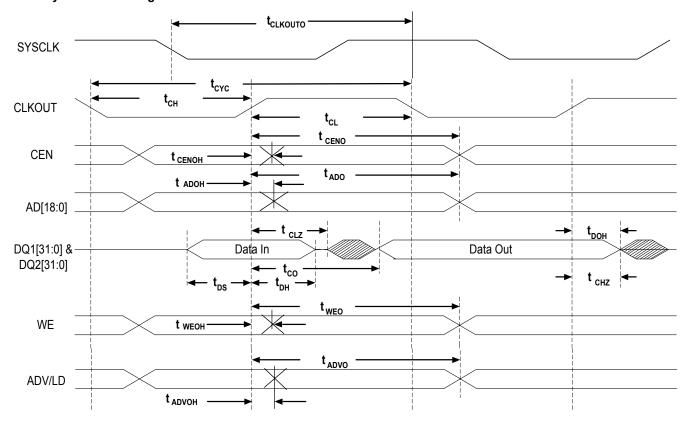

| AD [18:0]          | 0     | LVTTL          | 19    | N    | Synchronous Address Inputs Used to address up to six 512k x 36 NoBL™ SRAMs. Sampled at the rising edge of the CLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| WE                 |       | LVTTL          | 1     | N    | Synchronous Write Enable Input, active LOW. This must be sampled on the rising edge of CLK if CEN is active LOW. This signal must be asserted LOW to initiate a write sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| ADV/LD             | 0     | LVTTL          | 1     | N    | Synchronous Advance/Load Input This pin is used to advance the on-chip (SRAM's) address counter or load a new address. When HIGH (and CEN is asserted LOW) the internal burst counter of SRAM is advanced. When LOW, a new address is loaded into the SRAM for an access. After being deselected, ADV/LD should be driven LOW in order to load a new address.                                                                                                                                                                                                                                                                                                                      |

| CE1                | 0     | LVTTL          | 1     | N    | Synchronous Chip Enable 1, active LOW. Sampled on the rising edge of CLK. Used to select/deselect first bank of the NoBL memory.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |