## 74ABT245 **Octal Bi-Directional Transceiver with 3-STATE Outputs**

#### **General Description**

## **Features**

- Bidirectional non-inverting buffers

- A and B output sink capability of 64 mA, source capability of 32 mA

- Guaranteed output skew

- Guaranteed multiple output switching specifications

- Output switching specified for both 50 pF and 250 pF loads

- Guaranteed simultaneous switching, noise level and dynamic threshold performance

- Guaranteed latchup protection

- High impedance glitch-free bus loading during entire power up and power down cycle

- Non-destructive hot insertion capability

- Disable time is less than enable time to avoid bus contention

#### **Ordering Code:**

| FAIRCH<br>SEMICONDL<br>74ABT24<br>Octal Bi-                                                                                                                   | ICTOR™                                                                                                                                                                         | al Transcei                                                                                                                                                                                                                                   | September 1991<br>Revised November 1999<br>Ver with 3-STATE Outputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

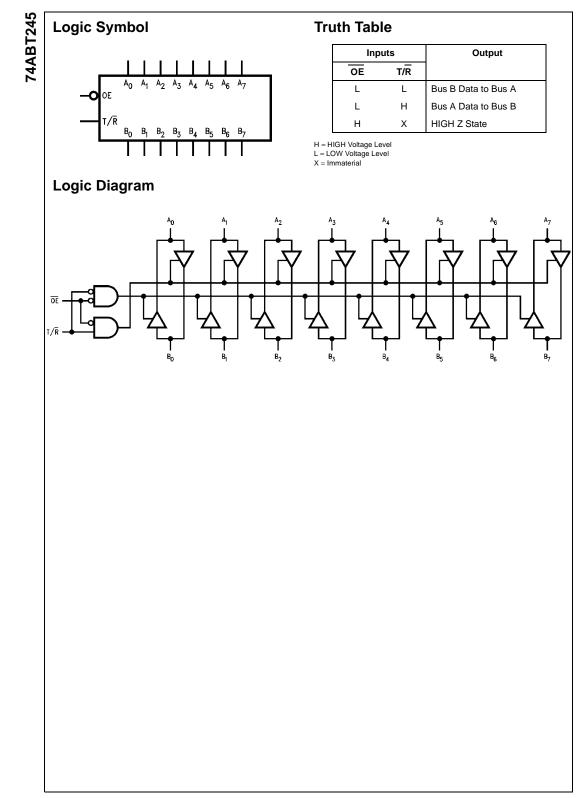

| ers with 3-STATE c<br>applications. Curre<br>the A and B ports. T<br>mines the direction<br>transceiver. Transm<br>Ports to B Ports; R<br>B Ports to A Ports. | ns eight non-invert<br>nutputs and is inten<br>nt sinking capabilit<br>The Transmit/Rece<br>of data flow thro<br>nit (active HIGH) e<br>eceive (active LOW<br>The Output Enabl | ing bidirectional buff-<br>ided for bus-oriented<br>y is $64 \text{ mA on both}$<br>ive $(T/\overline{R})$ input deter-<br>ugh the bidirectional<br>anables data from A<br>V) enables data from<br>e input, when HIGH,<br>ng them in a HIGH Z | <ul> <li>Features</li> <li>Bidirectional non-inverting buffers</li> <li>A and B output sink capability of 64 mA, source capability of 32 mA</li> <li>Guaranteed output skew</li> <li>Guaranteed multiple output switching specifications</li> <li>Output switching specified for both 50 pF and 250 pF loads</li> <li>Guaranteed simultaneous switching, noise level and dynamic threshold performance</li> <li>Guaranteed latchup protection</li> <li>High impedance glitch-free bus loading during entire power up and power down cycle</li> <li>Non-destructive hot insertion capability</li> <li>Disable time is less than enable time to avoid bus contention</li> </ul> |  |  |  |  |  |

| Ordering Co                                                                                                                                                   | ode:                                                                                                                                                                           |                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

|                                                                                                                                                               | Package Number                                                                                                                                                                 |                                                                                                                                                                                                                                               | Packade Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

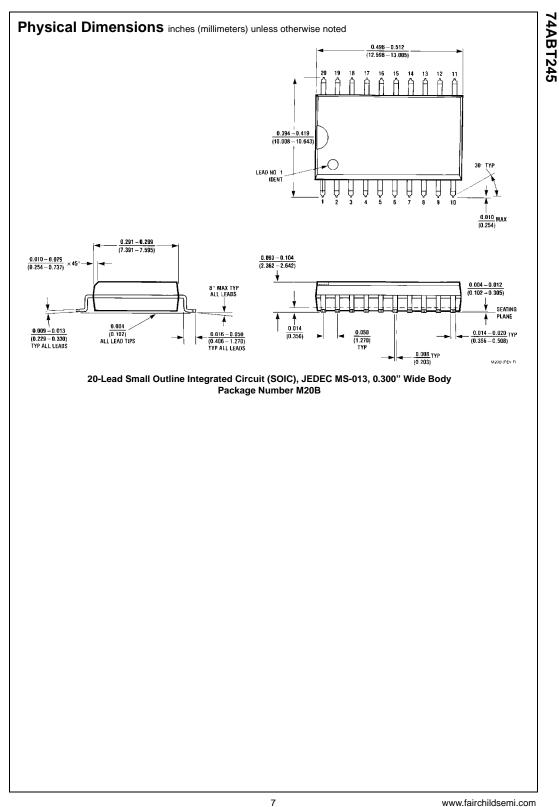

| 74ABT245CSC                                                                                                                                                   | M20B                                                                                                                                                                           |                                                                                                                                                                                                                                               | Integrated Circuit (SOIC), JEDEC MS-013, 0.300" Wide Body                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

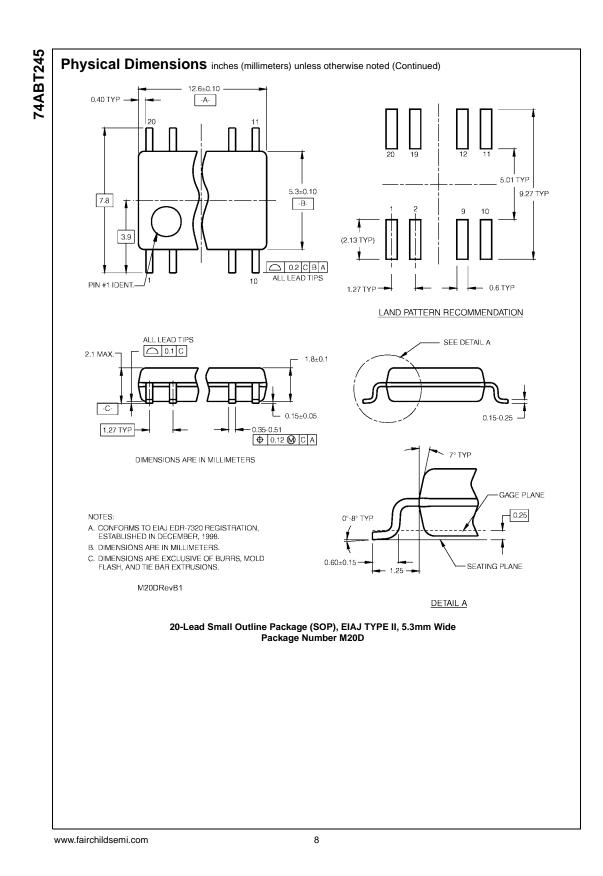

| 74ABT245CSJ                                                                                                                                                   | M20D                                                                                                                                                                           |                                                                                                                                                                                                                                               | Package (SOP), EIAJ TYPE II, 5.3mm Wide                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

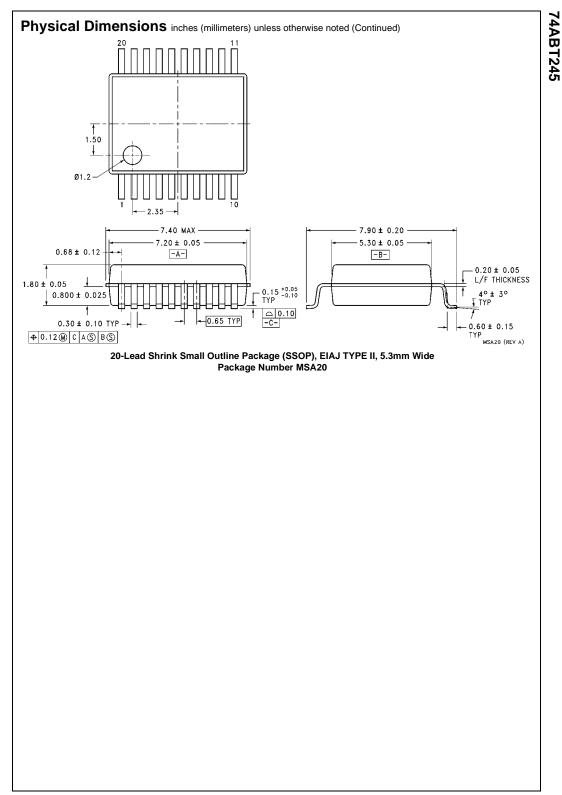

| 74ABT245CMSA                                                                                                                                                  | MSA20                                                                                                                                                                          | 20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300" Wide Body<br>20-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide<br>20-Lead Shrink Small Outline Package (SSOP), EIAJ TYPE II, 5.3mm Wide                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

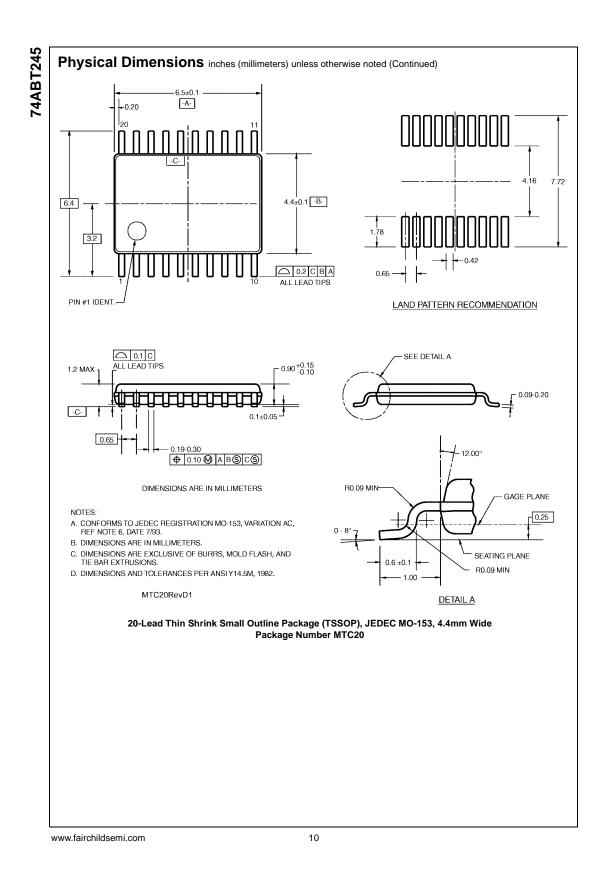

|                                                                                                                                                               | MTC20                                                                                                                                                                          | 20-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

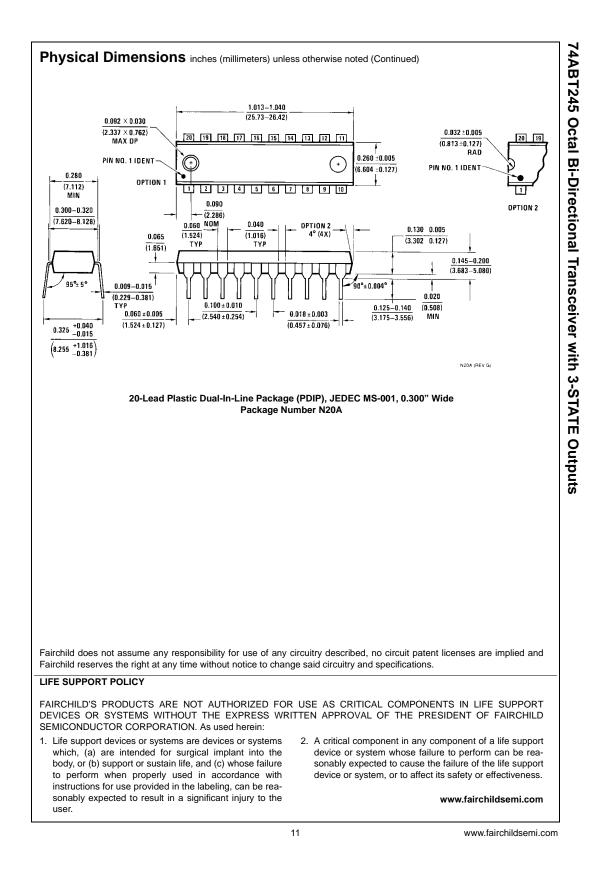

| 74ABT245CMTC<br>74ABT245CPC                                                                                                                                   | 111020                                                                                                                                                                         |                                                                                                                                                                                                                                               | n-Line Package (PDIP), JEDEC MS-001, 0.300" Wide                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

Device also available in Tape and Reel. Specify by appending suffix letter "X" to the ordering code.

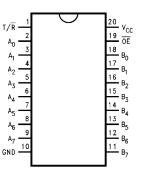

#### **Connection Diagram**

#### **Pin Descriptions**

| Pin Names                      | Description                      |

|--------------------------------|----------------------------------|

| OE                             | Output Enable Input (Active LOW) |

| T/R                            | Transmit/Receive Input           |

| A <sub>0</sub> -A <sub>7</sub> | Side A Inputs or 3-STATE Outputs |

| B <sub>0</sub> -B <sub>7</sub> | Side B Inputs or 3-STATE Outputs |

© 1999 Fairchild Semiconductor Corporation DS010945

www.fairchildsemi.com

2

#### Absolute Maximum Ratings(Note 1)

|                                      | _                                    |

|--------------------------------------|--------------------------------------|

| Storage Temperature                  | $-65^{\circ}C$ to $+150^{\circ}C$    |

| Ambient Temperature under Bias       | $-55^{\circ}C$ to $+125^{\circ}C$    |

| Junction Temperature under Bias      | $-55^{\circ}C$ to $+150^{\circ}C$    |

| $V_{CC}$ Pin Potential to Ground Pin | -0.5V to +7.0V                       |

| Input Voltage (Note 2)               | -0.5V to +7.0V                       |

| Input Current (Note 2)               | -30 mA to +5.0 mA                    |

| Voltage Applied to Any Output        |                                      |

| in the Disabled or                   |                                      |

| Power-off State                      | -0.5V to 5.5V                        |

| in the HIGH State                    | -0.5V to V <sub>CC</sub>             |

| Current Applied to Output            |                                      |

| in LOW State (Max)                   | twice the rated I <sub>OL</sub> (mA) |

| DC Latchup Source Current            | –500 mA                              |

| Over Voltage Latchup (I/O)           | 10V                                  |

|                                      |                                      |

# Recommended Operating Conditions

| Free Air Ambient Temperature<br>Supply Voltage  | -40°C to +85°C<br>+4.5V to +5.5V |

|-------------------------------------------------|----------------------------------|

| Minimum Input Edge Rate ( $\Delta V/\Delta t$ ) |                                  |

| Data Input                                      | 50 mV/ns                         |

| Enable Input                                    | 20 mV/ns                         |

Note 1: Absolute maximum ratings are values beyond which the device may be damaged or have its useful life impaired. Functional operation under these conditions is not implied.

Note 2: Either voltage limit or current limit is sufficient to protect inputs

## **DC Electrical Characteristics**

| Symbol                             | Parameter                              | Min  | Тур | Max    | Units | V <sub>cc</sub> | Conditions                                                                                           |

|------------------------------------|----------------------------------------|------|-----|--------|-------|-----------------|------------------------------------------------------------------------------------------------------|

| V <sub>IH</sub>                    | Input HIGH Voltage                     | 2.0  |     |        | V     |                 | Recognized HIGH Signal                                                                               |

| V <sub>IL</sub>                    | Input LOW Voltage                      |      |     | 0.8    | V     |                 | Recognized LOW Signal                                                                                |

| V <sub>CD</sub>                    | Input Clamp Diode Voltage              |      |     | -1.2   | V     | Min             | $I_{IN} = -18 \text{ mA} (\overline{OE}, T/\overline{R})$                                            |

| V <sub>ОН</sub>                    | Output HIGH Voltage                    | 2.5  |     |        | V     | Min             | $I_{OH} = -3 \text{ mA} (A_n, B_n)$                                                                  |

|                                    |                                        | 2.0  |     |        | V     | Min             | $I_{OH} = -32 \text{ mA} (A_n, B_n)$                                                                 |

| V <sub>OL</sub>                    | Output LOW Voltage                     |      |     | 0.55   | V     | Min             | $I_{OL} = 64 \text{ mA} (A_n, B_n)$                                                                  |

| IIH                                | Input HIGH Current                     |      |     | 1<br>1 | μΑ    | Max             | $V_{IN} = 2.7V (\overline{OE}, T/\overline{R})$<br>$V_{IN} = V_{CC} (\overline{OE}, T/\overline{R})$ |

| I <sub>BVI</sub>                   | Input HIGH Current Breakdown Test      |      |     | 7      | μΑ    | Max             | $V_{IN} = 7.0V (\overline{OE}, T/R)$                                                                 |

| BVIT                               | Input HIGH Current Breakdown Test (I/C | D)   |     | 100    | μA    | Max             | $V_{IN} = 5.5V (A_n, B_n)$                                                                           |

| IIL                                | Input LOW Current                      |      |     | -1     |       |                 | $V_{IN} = 0.5V (\overline{OE}, T/\overline{R})$                                                      |

|                                    |                                        |      |     | -1     | μA    | Max             | $V_{IN} = 0.0V (\overline{OE}, T/\overline{R})$                                                      |

| V <sub>ID</sub>                    | Input Leakage Test                     | 4.75 |     |        | V     | 0.0             | I <sub>ID</sub> = 1.9 μA (OE, T/R)<br>All Other Pins Grounded                                        |

| I <sub>IH</sub> + I <sub>OZH</sub> | Output Leakage Current                 |      |     | 10     | μA    | 0-5.5V          | $V_{OUT} = 2.7V (A_n, B_n); \overline{OE} = 2.0V$                                                    |

| I <sub>IL</sub> + I <sub>OZL</sub> | Output Leakage Current                 |      |     | -10    | μΑ    | 0-5.5V          | $V_{OUT} = 0.5V (A_n, B_n); \overline{OE} = 2.0V$                                                    |

| l <sub>os</sub>                    | Output Short-Circuit Current           | -100 |     | -275   | mA    | Max             | $V_{OUT} = 0.0V (A_n, B_n)$                                                                          |

| I <sub>CEX</sub>                   | Output HIGH Leakage Current            |      |     | 50     | μA    | Max             | $V_{OUT} = V_{CC} (A_n, B_n)$                                                                        |

| I <sub>ZZ</sub>                    | Bus Drainage Test                      |      |     | 100    | μΑ    | 0.0             | V <sub>OUT</sub> = 5.5V (A <sub>n</sub> , B <sub>n</sub> );<br>All Others GND                        |

| I <sub>ССН</sub>                   | Power Supply Current                   |      |     | 50     | μA    | Max             | All Outputs HIGH                                                                                     |

| I <sub>CCL</sub>                   | Power Supply Current                   |      |     | 30     | mA    | Max             | All Outputs LOW                                                                                      |

| I <sub>CCZ</sub>                   | Power Supply Current                   |      |     | 50     | μΑ    | Max             | $\overline{OE} = V_{CC}, T/\overline{R} = GND \text{ or } V_{CC};$<br>All Other GND or $V_{CC}$      |

| ICCT                               | Additional Outputs Enabled             | ł    |     | 2.5    | mA    |                 | $V_{I} = V_{CC} - 2.1V$                                                                              |

|                                    | I <sub>CC</sub> /Input Outputs 3-STAT  | E    |     | 2.5    | mA    | Max             | $\overline{OE}$ , T/ $\overline{R}$ V <sub>I</sub> = V <sub>CC</sub> - 2.1V                          |

|                                    | Outputs 3-STAT                         | E    |     | 50     | μΑ    |                 | Data Input $V_I = V_{CC} - 2.1V$                                                                     |

|                                    |                                        |      |     |        |       |                 | All Others at $V_{CC}$ or GND.                                                                       |

| ICCD                               | Dynamic I <sub>CC</sub> No Load        |      |     | 0.1    | mA/   | Max             | Outputs Open                                                                                         |

|                                    |                                        |      |     |        | MHz   | iviax           | $\overline{OE} = GND, T/R = GND \text{ or } V_{CC}$                                                  |

|                                    |                                        |      |     |        |       |                 | One Bit Toggling, 50% Duty Cyc                                                                       |

## **DC Electrical Characteristics**

#### (SOIC package) Conditions Symbol Parameter Min Тур Max Units $v_{cc}$ $\textbf{C}_{\textbf{L}}=\textbf{50}~\textbf{pF},~\textbf{R}_{\textbf{L}}=\textbf{500}\boldsymbol{\Omega}$ V<sub>OLP</sub> Quiet Output Maximum Dynamic VOL 07 1.0 V 5.0 $T_A = 25^{\circ}C$ (Note 3) Quiet Output Minimum Dynamic V<sub>OL</sub> $T_A = 25^{\circ}C$ (Note 3) V<sub>OLV</sub> -1.3-1.0V 5.0 Minimum HIGH Level Dynamic Output Voltage $T_A = 25^{\circ}C$ (Note 5) V<sub>OHV</sub> 2.7 3.1 ٧ 5.0 $V_{\text{IHD}}$ Minimum HIGH Level Dynamic Input Voltage V 5.0 $T_A = 25^{\circ}C$ (Note 4) 2.0 1.7 VILD Maximum LOW Level Dynamic Input Voltage 0.9 0.6 ٧ 5.0 $T_A = 25^{\circ}C$ (Note 4)

Note 3: Max number of outputs defined as (n). n-1 data inputs are driven 0V to 3V. One output at LOW. Guaranteed, but not tested.

Note 4: Max number of data inputs (n) switching. n-1 inputs switching 0V to 3V. Input-under-test switching: 3V to threshold (V<sub>ILD</sub>), 0V to threshold (V<sub>ILD</sub>). Guaranteed, but not tested.

Note 5: Max number of outputs defined as (n). n - 1 data inputs are driven 0V to 3V. One output HIGH. Guaranteed, but not tested.

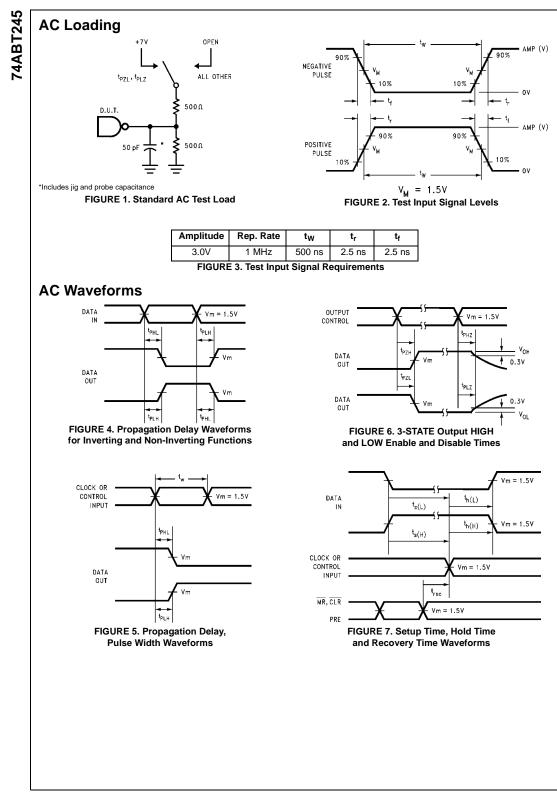

# AC Electrical Characteristics

| Symbol           | Parameter         |     | T <sub>A</sub> = +25°C<br>V <sub>CC</sub> = +5V<br>C <sub>L</sub> = 50 pF |     |     | $T_{A} = -55^{\circ}C \text{ to } +125^{\circ}C$ $V_{CC} = 4.5V - 5.5V$ $C_{L} = 50 \text{ pF}$ |     | $T_{A} = -40^{\circ}C \text{ to } +85^{\circ}C$ $V_{CC} = 4.5V - 5.5V$ $C_{L} = 50 \text{ pF}$ |    |

|------------------|-------------------|-----|---------------------------------------------------------------------------|-----|-----|-------------------------------------------------------------------------------------------------|-----|------------------------------------------------------------------------------------------------|----|

|                  |                   | Min | Тур                                                                       | Max | Min | Max                                                                                             | Min | Max                                                                                            |    |

| t <sub>PLH</sub> | Propagation Delay | 1.0 | 2.1                                                                       | 3.6 | 1.0 | 4.8                                                                                             | 1.0 | 3.6                                                                                            |    |

| t <sub>PHL</sub> | Data to Outputs   | 1.0 | 2.4                                                                       | 3.6 | 1.0 | 4.8                                                                                             | 1.0 | 3.6                                                                                            | ns |

| t <sub>PZH</sub> | Output Enable     | 1.5 | 3.2                                                                       | 6.0 | 1.0 | 6.7                                                                                             | 1.5 | 6.0                                                                                            |    |

| t <sub>PZL</sub> | Time              | 1.5 | 3.7                                                                       | 6.0 | 2.0 | 7.5                                                                                             | 1.5 | 6.0                                                                                            | ns |

| t <sub>PHZ</sub> | Output Disable    | 1.0 | 3.6                                                                       | 6.1 | 1.7 | 7.4                                                                                             | 1.0 | 6.1                                                                                            |    |

| t <sub>PLZ</sub> | Time              | 1.0 | 3.3                                                                       | 5.6 | 1.7 | 6.5                                                                                             | 1.0 | 5.6                                                                                            | ns |

#### **Extended AC Electrical Characteristics**

#### (SOIC package)

| Symbol              | Parameter            | $-40^{\circ}C \text{ to } +85^{\circ}C$ $V_{CC} = 4.5V-5.5V$ $C_{L} = 50 \text{ pF}$ 8 Outputs Switching<br>(Note 6) |     | $T_{A} = -40^{\circ}C \text{ to } +85^{\circ}C$ $V_{CC} = 4.5V - 5.5V$ $C_{L} = 250 \text{ pF}$ 1 Output Switching<br>(Note 7) |                   | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$ $V_{CC} = 4.5V - 5.5V$ $C_L = 250 \text{ pF}$ 8 Outputs Switching<br>(Note 8) |        | Units  |     |  |

|---------------------|----------------------|----------------------------------------------------------------------------------------------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------|--------|--------|-----|--|

|                     |                      | Min                                                                                                                  | Тур | Max                                                                                                                            | Min               | Max                                                                                                                         | Min    | Max    | 1   |  |

| f <sub>TOGGLE</sub> | Max Toggle Frequency |                                                                                                                      | 100 |                                                                                                                                |                   |                                                                                                                             |        |        | MHz |  |

| t <sub>PLH</sub>    | Propagation Delay    | 1.5                                                                                                                  |     | 5.0                                                                                                                            | 1.5               | 6.0                                                                                                                         | 2.5    | 8.5    | ns  |  |

| t <sub>PHL</sub>    | Data to Outputs      | 1.5                                                                                                                  |     | 5.0                                                                                                                            | 1.5               | 6.0                                                                                                                         | 2.5    | 8.5    | 115 |  |

| t <sub>PZH</sub>    | Output Enable Time   | 1.5                                                                                                                  |     | 6.5                                                                                                                            | 2.5               | 7.5                                                                                                                         | 2.5    | 9.5    | ns  |  |

| t <sub>PZL</sub>    |                      | 1.5                                                                                                                  |     | 6.5                                                                                                                            | 2.5               | 7.5                                                                                                                         | 2.5    | 11.0   | 115 |  |

| t <sub>PHZ</sub>    | Output Disable Time  | 1.0                                                                                                                  |     | 6.5                                                                                                                            | (Note 9) (Note 9) |                                                                                                                             | oto Q) | 200    |     |  |

| t <sub>PLZ</sub>    |                      | 1.0                                                                                                                  |     | 5.6                                                                                                                            | (14               | 010 3)                                                                                                                      | (1)    | JIC 3) | ns  |  |

Note 6: This specification is guaranteed but not tested. The limits apply to propagation delays for all paths described switching in phase (i.e., all LOW-to-HIGH, HIGH-to-LOW, etc.).

Note 7: This specification is guaranteed but not tested. The limits represent propagation delay with 250 pF load capacitors in place of the 50 pF load capacitors in the standard AC load. This specification pertains to single output switching only.

**Note 8:** This specification is guaranteed but not tested. The limits represent propagation delays for all paths described switching in phase

(i.e., all LOW-to-HIGH, HIGH-to-LOW, etc.) with 250 pF load capacitors in place of the 50 pF load capacitors in the standard AC load.

Note 9: The 3-STATE delays are dominated by the RC network (500Ω, 250 pF) on the output and have been excluded from the datasheet.

www.fairchildsemi.com

| Symbol                         | Parameter                                  | $T_{A} = -40^{\circ}C \text{ to } +85^{\circ}C$ $V_{CC} = 4.5V - 5.5V$ $C_{L} = 50 \text{ pF}$ 8 Outputs Switching<br>(Note 12)<br>Max | $T_{A} = -40^{\circ}C \text{ to } +85^{\circ}C$ $V_{CC} = 4.5V-5.5V$ $C_{L} = 250 \text{ pF}$ 8 Outputs Switching<br>(Note 13)<br>Max | Units |

|--------------------------------|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-------|

| t <sub>OSHL</sub><br>(Note 10) | Pin to Pin Skew<br>HL Transitions          | 1.3                                                                                                                                    | 2.3                                                                                                                                   | ns    |

| t <sub>OSLH</sub><br>(Note 10) | Pin to Pin Skew<br>LH Transitions          | 1.0                                                                                                                                    | 1.8                                                                                                                                   | ns    |

| t <sub>PS</sub><br>(Note 14)   | Duty Cycle<br>LH–HL Skew                   | 2.0                                                                                                                                    | 3.5                                                                                                                                   | ns    |

| t <sub>OST</sub><br>(Note 10)  | Pin to Pin Skew<br>LH/HL Transitions       | 2.0                                                                                                                                    | 3.5                                                                                                                                   | ns    |

| t <sub>PV</sub><br>(Note 11)   | Device to Device Skew<br>LH/HL Transitions | 2.0                                                                                                                                    | 3.5                                                                                                                                   | ns    |

d as the absolute value of the difference between the a ion delays for any two s uts of the same devi  $The specification applies to any outputs switching HIGH-to-LOW (t_{OSHL}), LOW-to-HIGH (t_{OSLH}), or any combination switching LOW-to-HIGH and/or to-HIGH (t_{OSLH}), transfer to the trans$

HIGH-to-LOW ( $t_{OST}$ ). The specification is guaranteed but not tested.

Note 11: Propagation delay variation for a given set of conditions (i.e., temperature and V<sub>CC</sub>) from device to device. This specification is guaranteed but not tested.

Note 12: This specification is guaranteed but not tested. The limits apply to propagation delays for all paths described switching in phase (i.e., all LOW-to-HIGH, HIGH-to-LOW, etc.)

Note 13: These specifications guaranteed but not tested. The limits represent propagation delays with 250 pF load capacitors in place of the 50 pF load capacitors in the standard AC load.

Note 14: This describes the difference between the delay of the LOW-to-HIGH and the HIGH-to-LOW transition on the same pin. It is measured across all the outputs (drivers) on the same chip, the worst (largest delta) number is the guaranteed specification. This specification is guaranteed but not tested.

#### Capacitance

| Symbol                     | Symbol Parameter  |      | Units | Conditions<br>T <sub>A</sub> = 25°C           |

|----------------------------|-------------------|------|-------|-----------------------------------------------|

| C <sub>IN</sub>            | Input Capacitance | 5.0  | pF    | $V_{CC} = 0V (\overline{OE}, T/\overline{R})$ |

| C <sub>I/O</sub> (Note 15) | I/O Capacitance   | 11.0 | pF    | $V_{CC} = 5.0V (A_n, B_n)$                    |

Note 15:  $C_{I/O}$  is measured at frequency f = 1 MHz, per MIL-STD-883, Method 3012.

www.fairchildsemi.com

74ABT245

www.fairchildsemi.com

6

www.fairchildsemi.com

9