# 80C186/80C188

# **CMOS High-Integration 16-Bit Microprocessors**

#### **DISTINCTIVE CHARACTERISTICS**

- Operation Modes Include

- ---Enhanced mode with

- · DRAM Refresh Control Unit

- · Power-save mode

- —Compatible Mode

- NMOS 80186/80188 pin-for-pin replacement for non-numerics applications

- Integrated Feature Set

- -Enhanced 80C86/C88 CPU

- —Clock generator

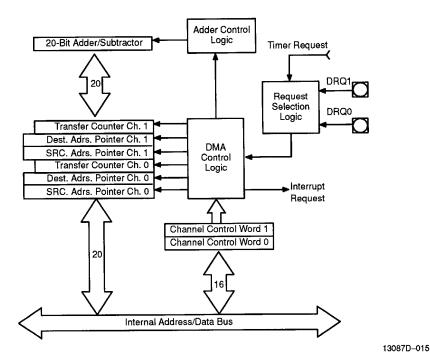

- -Two independent DMA channels

- —Programmable interrupt controller

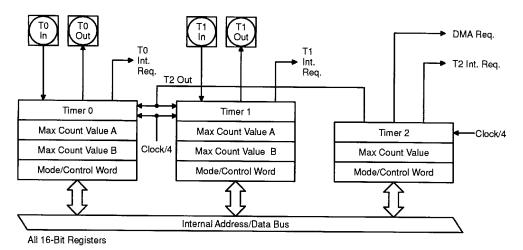

- -Three programmable 16-bit timers

- --- Dynamic RAM refresh control unit

- Programmable memory and peripheral chip select logic

- -Programmable wait-state generator

- -Local bus controller

- ---Power-save mode

- System-level testing support (high-impedance test mode)

- Available in 25-MHz, 20-MHz, 16-MHz, 12.5-MHz, and 10-MHz versions

- Direct addressing capability to 1-Mbyte of memory and 64-Kbyte I/O

- Fully static CMOS design

- Completely object code compatible with all existing 8086/8088 software. Has ten additional instructions over 8086/8088.

- Complete system development

- —There are many vendors making support tools for the 80C186/C188. Software tools for the NMOS 80186/80188 can be used for the 80C186/C188 as can the NMOS emulators

- Available in

- -68-Pin Plastic Leaded Chip Carrier (PLCC)

- -80-Pin Thin Quad Flat Pack (TQFP)

- -80-Pin Plastic Quad Flat Pack (PQFP)

- In Trimmed/Formed Configuration

## **GENERAL DESCRIPTION**

The 80C186/C188 is a CMOS high-integration microprocessor. It has features that are new to the 80186/80188 Family, which include a DRAM refresh control unit, and power-save mode. When used in "compatible" mode, the 80C186/C188 is 100% pin-for-pin compatible with the NMOS 80186/80188

(except for 8087 applications). The Enhanced mode of operation allows the full feature set of the 80C186/C188 to be used. The 80C186/80C188 is upward compatible with 8086 and 8088 software and fully compatible with 80186 and 80188 software.

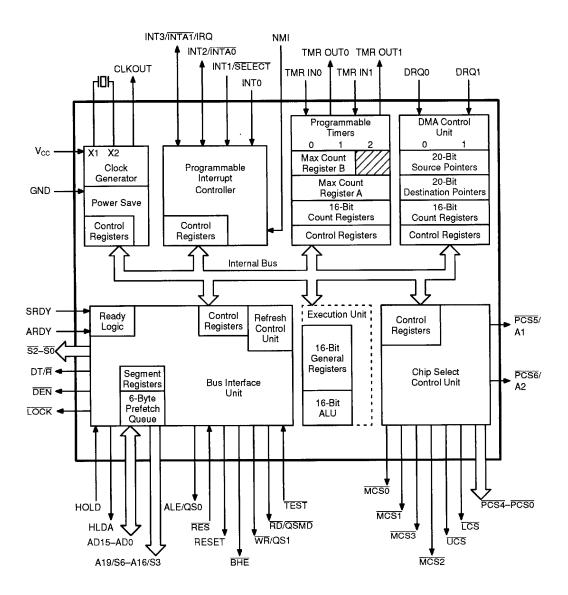

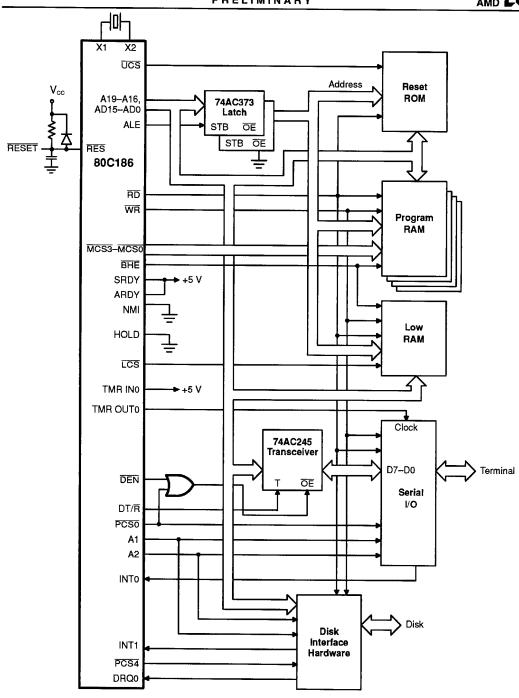

# 80C186 BLOCK DIAGRAM

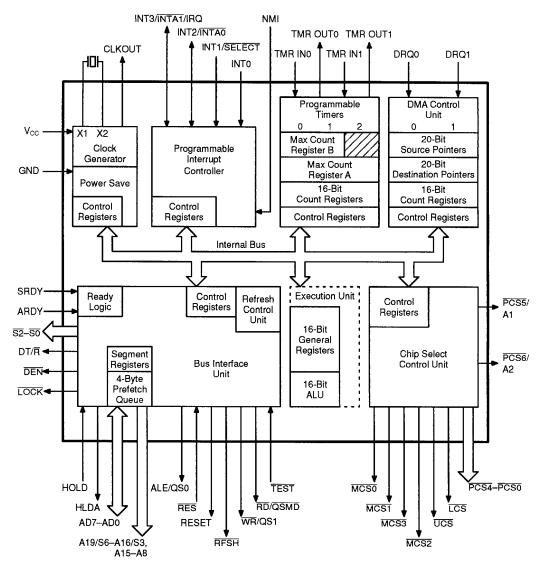

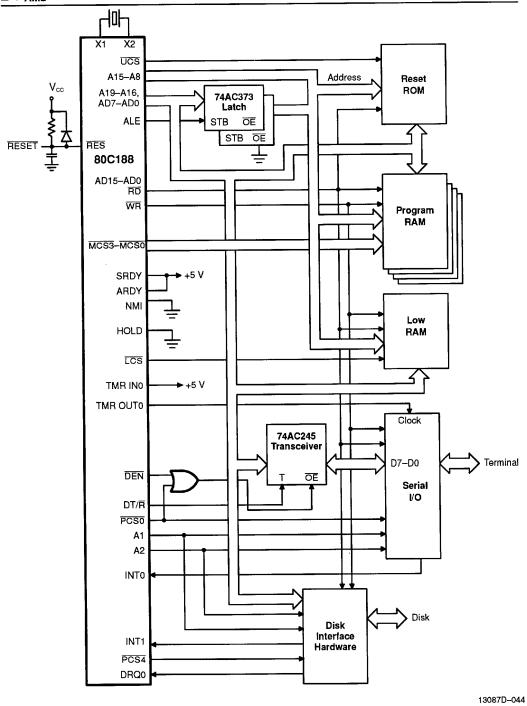

# 80C188 BLOCK DIAGRAM

13088B-001

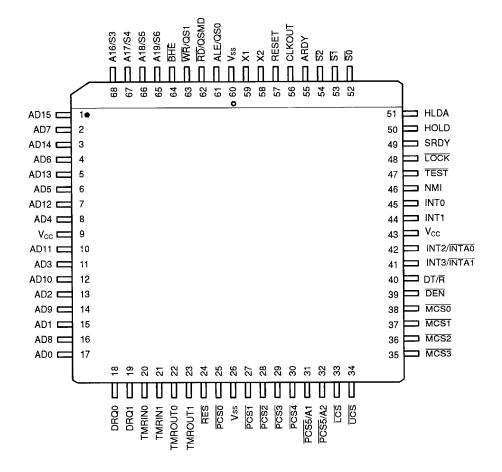

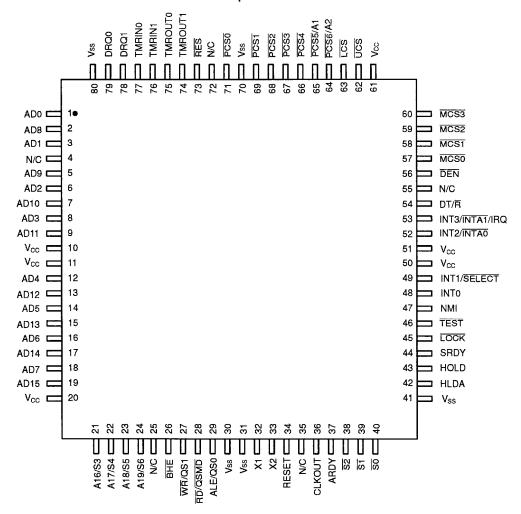

# **80C186 CONNECTION DIAGRAMS**

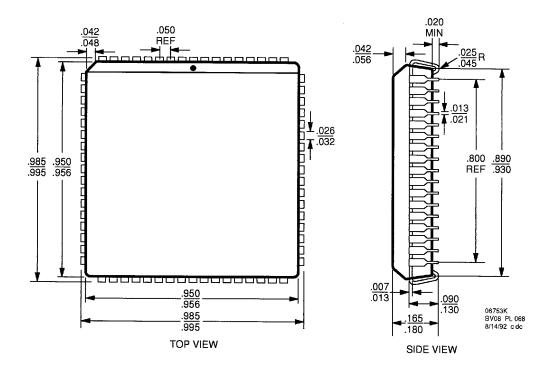

# 68-Pin Plastic Leaded Chip Carrier (PL 068)

#### Note:

Pin One marked for orientation purposes only.

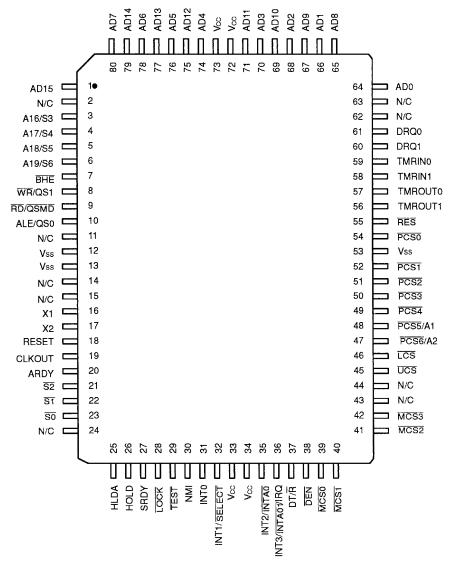

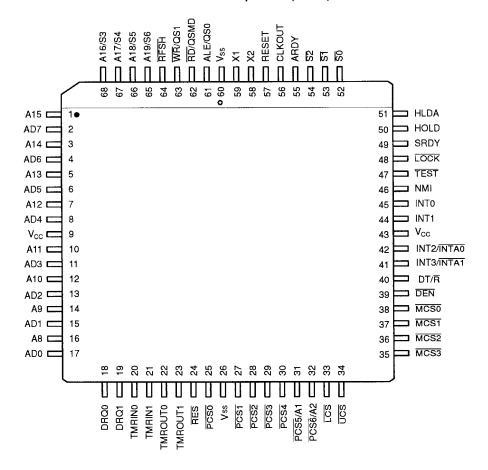

# 80C186 CONNECTION DIAGRAMS (continued)

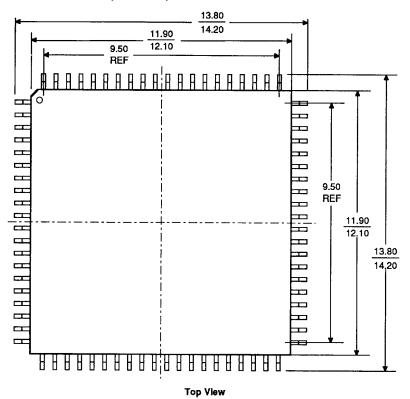

# 80-Pin Plastic Quad Flat Pack (PQR 80)

#### Notes:

- 1. Pin 1 is marked for orientation purposes only.

- 2. N/C = Not connected.

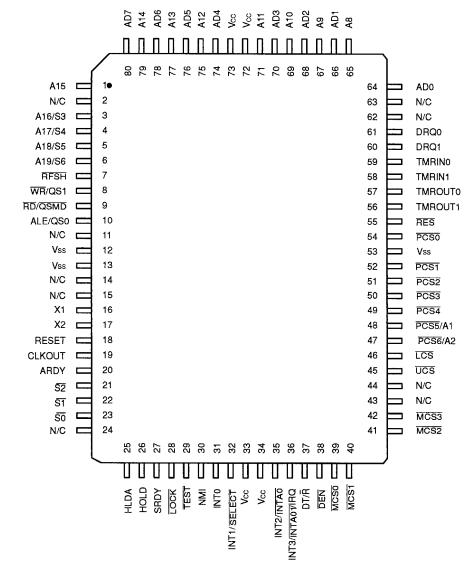

# 80C186 CONNECTION DIAGRAMS (continued)

#### 80-Pin Thin Quad Flat Pack **Top View**

1.Pin 1 is marked for orientation purposes only.

2. N/C = Not connected.

0257525 0049573 198 📟

80C186 PIN DESIGNATIONS (sorted by Pin Name)

| 80C186 PIN DESIGNATIONS (sorted by Pin N |            |          | Pin Number |                           |                  |            |          |              |                   |

|------------------------------------------|------------|----------|------------|---------------------------|------------------|------------|----------|--------------|-------------------|

| Pin Name                                 | Pin Number |          |            | Code                      | Pin Name         |            |          |              | Code              |

| PLCCPQFP TQFP                            |            |          | PLCC       | PQFP                      | TQFP             |            |          |              |                   |

| A19/S6<br>A18/S5                         | 65<br>66   | 6<br>5   | 24<br>23   |                           | MCS0             | 38         | 39       | 57           | I/O, HA(1), R(PU) |

| A17/S4                                   | 67         | 4        | 23         | O, HA(Z), R(Z)            | MCS1             | 37         | 40       | 58           | I/O, HA(1), R(PU) |

| A16/S3                                   | 68         | 3        | 21         |                           | MCS2             | 36         | 41       | 59           | O, HA(1), R(PU)   |

| AD15                                     | 1          | 1        | 19         |                           | MCS3             | 35         | 42       | 60           | O, HA(1), R(PU)   |

| AD14                                     | 3          | 79       | 17         |                           | NMI              | 46         | 30       | 47           | I, S(E)           |

| AD13<br>AD12                             | 5<br>7     | 77<br>75 | 15<br>13   | -                         | PCS5/A1          | 31         | 48       | 65           | O, HA(X), R(1)    |

| AD11                                     | 10         | 71       | 9          |                           | PCS6/A2          | 32         | 47       | 64           | O, HA(X), R(1)    |

| AD10                                     | 12         | 69       | 7          |                           | PCS4             | 30         | 49       | 66           | -, (,,(,          |

| AD9                                      | 14         | 67       | 5          |                           | PCS3             | 29         | 50       | 67           |                   |

| AD8                                      | 16         | 65       | 2          | I/O, S(L), HA(Z), R(Z)    | PCS2             | 28         | 51       | 68           | O, HA(1), R(1)    |

| AD7                                      | 2          | 80       | 18         | , - (-), (-), (-)         | PCS1             | 27         | 52       | 69           |                   |

| AD6                                      | 4          | 78       | 16         |                           | PCS0             | 25         | 54       | 71           |                   |

| AD5<br>AD4                               | 6<br>8     | 76       | 14<br>12   |                           | RD/QSMD          | 62         | 9        | 28           | I/O, HA(Z), R(PU) |

| AD3                                      | 11         | 74<br>70 | 8          |                           | RES              | 24         | 55       | 73           | I, S(L)           |

| AD2                                      | 13         | 68       | 6          |                           | RESET            | 57         | 18       | 34           | O, HA(A)          |

| AD1                                      | 15         | 66       | 3          |                           |                  | 54, 53, 52 |          |              |                   |

| AD0                                      | 17         | 64       | 1          |                           |                  |            |          |              | . ( ). ( )        |

| ALE/QS0                                  | 61         | 10       | 29         | O, HA(0), R(0)            | SRDY             | 49         | 27       | 44           | I, S(L)           |

| ARDY                                     | 55         | 20       | 37         | l, <b>A</b> (L)           |                  | 47         | 29       | 46           | I, R(PU)          |

| BHE                                      | 64         | 7        | 26         | O, HA(Z), R(Z)            | TMRIN0<br>TMRIN1 | 20<br>21   | 59<br>58 | 77<br>76     | I, S(E)           |

| CLKOUT                                   | 56         | 19       | 36         | O, HA(A), R(A)            | TMROUTO          | 22         | 57       | 75           |                   |

| DEN                                      | 39         | 38       | 56         | O, HA(Z), R(Z)            | TMROUT1          | 23         | 56       | 74           | O, HA(A), R(1)    |

| DRQ0, DRQ1                               | 18, 19     | 61, 60   | 79, 78     | l, S(L)                   | ucs              | 34         | 45       | 62           | I/O, HA(1), R(PU) |

| DT/A                                     | 40         | 37       | 54         | O, HA(Z), R(Z)            |                  | 9          | 33       | 61, 10       |                   |

| HOLD                                     | 50         | 26       | 43         | I, S(L)                   | V <sub>CC</sub>  | 43<br>-    | 34<br>72 | 51, 11<br>50 | 1                 |

| HLDA                                     | 51         | 25       | 42         | O, HA(A), R(0)            |                  | _          | 73       | 20           |                   |

| INT0                                     | 45         | 31       | 48         | I, A(E, L)                | WR/QS1           | 63         | 8        | 27           | O, HA(Z), R(Z)    |

| INT1/SELECT                              | 44         | 32       | 49         | I, A(E, L)                |                  | 26         | 12       | 30, 70       |                   |

| INT2/INTAO                               | 42         | 35       | 52         | I/O, A(E, L), HA(X), R(Z) | V <sub>ss</sub>  | 60<br>—    | 13<br>53 | 31, 80<br>41 | '                 |

| INT3/INTA1/IRQ                           | 41         | 36       | 53         | I/O, A(E, L), HA(X), R(Z) | X1               | 59         | 16       | 32           | i                 |

| <u>cs</u>                                | 33         | 46       | 63         | I/O, HA(1), R(PU)         | X2               | 58         | 17       | 33           | 0                 |

| LOCK                                     | 48         | 28       | 45         | O, HA(Z), R(PU)           | 1,,,,            |            |          |              |                   |

On the PQFP package, the following pins are N/C (No Connect): 2, 11, 14, 15, 24, 43, 44, 62, and 63. On the TQFP package, the following pins are N/C (No Connect): 4, 25, 35, 55, and 72.

# **Key to Pin Description Codes**

Symbol

| Symbol | Description                                                                                                                      |

|--------|----------------------------------------------------------------------------------------------------------------------------------|

| l I    | Input Only                                                                                                                       |

| 0      | Output Only                                                                                                                      |

| 1/0    | Input or Output (depending on situation)                                                                                         |

| S(x)   | Synchronous: Setup and Hold times must be met for proper operation.  S(E) = Edge Sensitive  S(L) = Level Sensitive               |

| A(x)   | Asynchronous: Setup and Hold times guarantee signal recognition by the processor.  A(E) = Edge Sensitive  A(L) = Level Sensitive |

| HA(x) | Hold Acknowledge: Pin state while processor is in the Hold Acknowledge state.  HA(1) = Internally driven to V <sub>CC</sub> HA(0) = Internally driven to V <sub>SS</sub> HA(Z) = Internally floated  HA(A) = Remains active  HA(X) = Retains current state                        |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R(x)  | Reset: Pin state while the processor's RES line is held Low externally.  R(1) = Internally driven to V <sub>CC</sub> R(0) = Internally driven to V <sub>SS</sub> R(Z) = Internally floated  R(A) = Remains Active  R(PU) = Weak internal pull-up  R(PD) = Weak internal pull-down |

Description

🕶 0257525 0849574 024 🖼 .

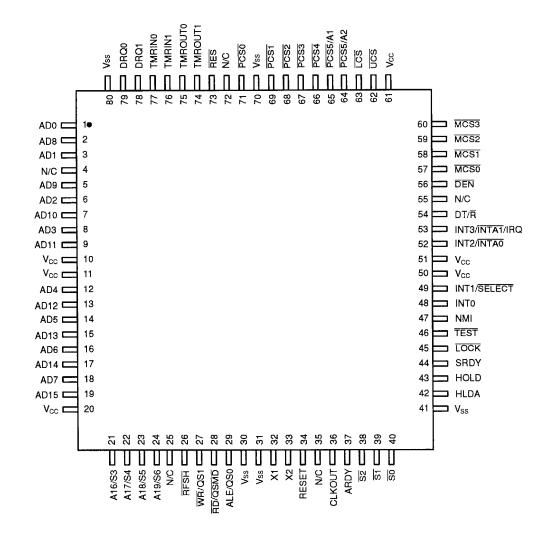

# 80C188 CONNECTION DIAGRAMS

#### 68-Pin Plastic Leaded Chip Carrier (PL 068)

**Note:**Pin One marked for orientation purposes only.

🖿 0257525 0049575 T60 🖿

# 80C188 CONNECTION DIAGRAMS (continued)

#### 80-Pin Plastic Quad Flat Pack (PQR 80)

#### Notes:

1. Pin 1 is marked for orientation purposes only.

2. N/C = Not connected.

■ 0257525 0049576 9T7 **■**

# 80C188 CONNECTION DIAGRAMS (continued)

#### 80-Pin Thin Quad Flat Pack Top View

#### Notes

1.Pin 1 is marked for orientation purposes only. 2. N/C = Not connected.

**■** 0257525 0049577 833 **■**

80C186/80C188 Microprocessors

10

# 80C188 PIN DESIGNATIONS (sorted by Pin Name)

|                        | Pin Number           |                      | ber              |                           |                                      | Pin Number           |                      |                      |                                       |

|------------------------|----------------------|----------------------|------------------|---------------------------|--------------------------------------|----------------------|----------------------|----------------------|---------------------------------------|

| Pin Name               | PLCC                 | PQFP                 | TQFP             | Code                      | Pin Name                             | PLCC                 | PQFP                 | TQFP                 | Code                                  |

| A19/S6                 | 65                   | 6                    | 24               |                           | MCS1                                 | 37                   | 40                   | 58                   | O, HA(1), R(PU)                       |

| A18/S5<br>A17/S4       | 66<br>67             | 5<br>4               | 23<br>22         | O, HA(Z), R(Z)            | MCS2                                 | 36                   | 41                   | 59                   | O, HA(1), R(PU)                       |

| A16/S3                 | 68                   | 3                    | 21               |                           | MCS3                                 | 35                   | 42                   | 60                   | O, HA(1), R(PU)                       |

| A15<br>A14             | 1                    | 1<br>79              | 19<br>17         |                           | NMI                                  | 46                   | 30                   | 47                   | I, S(E)                               |

| A13                    | 5                    | 77                   | 15               |                           | PCS5/A1                              | 31                   | 48                   | 65                   | O, HA(X), R(1)                        |

| A12                    | 7                    | 75                   | 13               |                           | PCS6/A2                              | 32                   | 47                   | 64                   | O, HA(X), R(1)                        |

| A11<br>A10<br>A9<br>A8 | 10<br>12<br>14<br>16 | 71<br>69<br>67<br>65 | 9<br>7<br>5<br>2 |                           | PCS4<br>PCS3<br>PCS2<br>PCS1<br>PCS0 | 30<br>29<br>28<br>27 | 49<br>50<br>51<br>52 | 66<br>67<br>68<br>69 | O, HA(1), R(1)                        |

| A7<br>A6               | 2                    | 80<br>78             | 18<br>16         | I/O, S(L), HA(Z), R(Z)    | RD/QSMD                              | 25<br>62             | 54<br>9              | 71                   | LO LIAGO DIDIO                        |

| A5                     | 6                    | 76                   | 14               |                           | RES                                  |                      |                      | 28                   | I/O, HA(Z), R(PU)                     |

| A4                     | 8                    | 74                   | 12               |                           |                                      | 24                   | 55                   | 73                   | I, S(L)                               |

| A3<br>A2               | 11<br>13             | 70<br>68             | 8                |                           | RESET                                | 57                   | 18                   | 34                   | O, HA(A)                              |

| A2<br>A2               | 15                   | 66                   | 3                |                           | RFSH                                 | 64                   | 7                    | 26                   | HA(Z), R(Z)                           |

| <b>A</b> 0             | 17                   | 64                   | 1                |                           | <u>S2–S0</u>                         |                      | <u> </u>             | 38, 39, 40           | · · · · · · · · · · · · · · · · · · · |

| ALE/QS0                | 61                   | 10                   | 29               | O, HA(0), R(0)            | SRDY                                 | 49                   | 27                   | 44                   | I, S(L)                               |

| ARDY                   | 55                   | 20                   | 37               | I, A(L)                   | TEST                                 | 47                   | 29                   | 46                   | I, R(PU)                              |

| CLKOUT                 | 56                   | 19                   | 36               | O, HA(A), R(A)            | TMRIN1<br>TMRIN0                     | 20<br>21             | 59<br>58             | 76<br>77             | I, S(E)                               |

| DEN                    | 39                   | 38                   | 56               | O, HA(Z), R(Z)            | TMROUT1                              | 22                   | 57                   | 74                   |                                       |

| DRQ0, DRQ1             | 18, 19               | 61, 60               | 79, 78           | I, S(L)                   | TMROUTO                              | 23                   | 56                   | 75                   | O, HA(A), R(1)                        |

| DT/R                   | 40                   | 37                   | 54               | O, HA(Z), R(Z)            | UCS                                  | 34                   | 45                   | 62                   | I/O, HA(1), R(PU)                     |

| HOLD                   | 50                   | 26                   | 43               | I, S(L)                   |                                      | 9                    | 33                   | 61, 10               |                                       |

| HLDA                   | 51                   | 25                   | 42               | O, HA(A), R(0)            | V <sub>CC</sub>                      | 43<br>               | 34<br>72             | 51, 11<br>50         | I                                     |

| INT0                   | 45                   | 31                   | 48               | I, A(E, L)                |                                      |                      | 73                   | 20                   |                                       |

| INT1/SELECT            | 44                   | 32                   | 49               | I, A(E, L)                | WR/QS1                               | 63                   | 8                    | 27                   | O, HA(Z), R(Z)                        |

| INT2/INTAO             | 42                   | 35                   | 52               | I/O, A(E, L), HA(X), R(Z) |                                      | 26                   | 12                   | 30, 70               |                                       |

| INT3/INTA1/IRQ         | 41                   | 36                   | 53               | I/O, A(E, L), HA(X), R(Z) | V <sub>ss</sub>                      | 60<br>_              | 13<br>53             | 31, 80<br>41         |                                       |

| LCS                    | 33                   | 46                   | 63               | I/O, HA(1), R(PU)         | X1                                   | 59                   | 16                   | 32                   | 1                                     |

| LOCK                   | 48                   | 28                   | 45               | O, HA(Z), R(PU)           | X2                                   | 58                   | 17                   | 33                   | 0                                     |

| MCS0                   | 38                   | 39                   | 57               | O, HA(1), R(PU)           | L'\-                                 | 30                   | L ''                 | 1 33                 | L Y                                   |

On PQFP package the following pins are N/C (No Connect): 2, 11, 14, 15, 24, 43, 44, 62, and 63. On TQFP package the following pins are N/C (No Connect): 4, 25, 35, 55, 72.

# **Key to Pin Description Codes**

| Symbol | Description                                                                                                                     |  |

|--------|---------------------------------------------------------------------------------------------------------------------------------|--|

| 1      | Input Only                                                                                                                      |  |

| 0      | Output Only                                                                                                                     |  |

| 1/0    | Input or Output (depending on situation)                                                                                        |  |

| S(x)   | Synchronous: Setup and Hold times must be met for proper operation.  S(E) = Edge Sensitive S(L) = Level Sensitive               |  |

| A(x)   | Asynchronous: Setup and Hold times guarantee signal recognition by the processor.  A(E) = Edge Sensitive A(L) = Level Sensitive |  |

| N257525 | 0049578 | フファ |  |

|---------|---------|-----|--|

|         | 0121210 | rr  |  |

| Symbol | Description                                                                                                                                                                                                                                                                              |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HA(x)  | Hold Acknowledge: Pin state while processor is in the Hold Acknowledge state. $HA(1) = \text{Internally driven to } V_{CC} \\ HA(0) = \text{Internally driven to } V_{SS} \\ HA(Z) = \text{Internally floated} \\ HA(A) = \text{Remains active} \\ HA(X) = \text{Retains current state}$ |

| ∏(x)   | Reset: Pin state while the processor's RES line is held Low externally.  R(1) = Internally driven to V <sub>CC</sub> R(0) = Internally driven to V <sub>SS</sub> R(Z) = Internally floated  R(A) = Remains Active  R(PU) = Weak internal pull-up  R(PD) = Weak internal pull-down        |

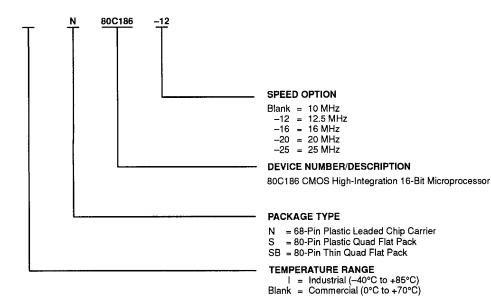

# 80C186 ORDERING INFORMATION

#### **Commodity Products**

AMD® commodity products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of the elements below.

| Valid Combinations |                         |  |  |  |

|--------------------|-------------------------|--|--|--|

|                    | N80C186, IN80C186       |  |  |  |

|                    | N80C186-12, IN80C186-12 |  |  |  |

| PLCC               | N80C186-16, IN80C186-16 |  |  |  |

| -                  | N80C186-20, IN80C186-20 |  |  |  |

|                    | N80C186-25              |  |  |  |

|            | S80C186    |

|------------|------------|

| PQFP       | S80C186-12 |

| Trimmed    | S80C186-16 |

| and Formed | S80C186-20 |

|            | S80C186-25 |

|      | SB80C186    |

|------|-------------|

|      | SB80C186-12 |

| TQFP | SB80C186-16 |

|      | SB80C18620  |

|      | SB80C186-25 |

#### **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations and to check on newly released combinations.

**■** 0257525 0049579 606 **■**

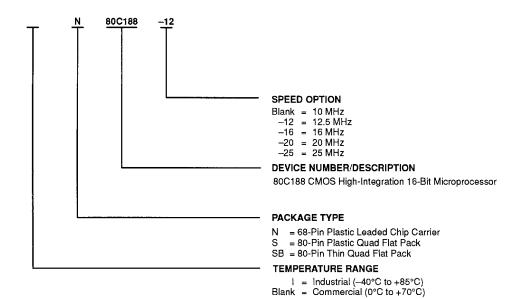

# **80C188 ORDERING INFORMATION**

# **Commodity Products**

AMD commodity products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of the elements below.

| Valid Combinations |                         |  |  |

|--------------------|-------------------------|--|--|

|                    | N80C188, IN80C188       |  |  |

|                    | N80C188-12, IN80C188-12 |  |  |

| PLCC               | N80C188-16, IN80C188-16 |  |  |

| . 200              | N80C188-20, IN80C188-20 |  |  |

|                    | N80C188-25              |  |  |

|                       | \$80C188   |

|-----------------------|------------|

| POFP                  | S80C188-12 |

| Trimmed<br>and Formed | S80C188-16 |

|                       | S80C188-20 |

|                       | S80C188-25 |

| TQFP | SB80C188    |

|------|-------------|

|      | SB80C188-12 |

|      | SB80C188-16 |

|      | SB80C188-20 |

|      | SB80C188-25 |

### **Valid Combinations**

Valid Combinations list configurations are planned to be supported in volume for this device. Consult the local AMD sales office to confirm the availability of specific valid combinations and to check on newly released combinations.

0257525 0049580 328

# **PIN DESCRIPTIONS**

#### A19/S6, A18/S5, A17/S4, A16/S3 Address Bus Outputs (Outputs)

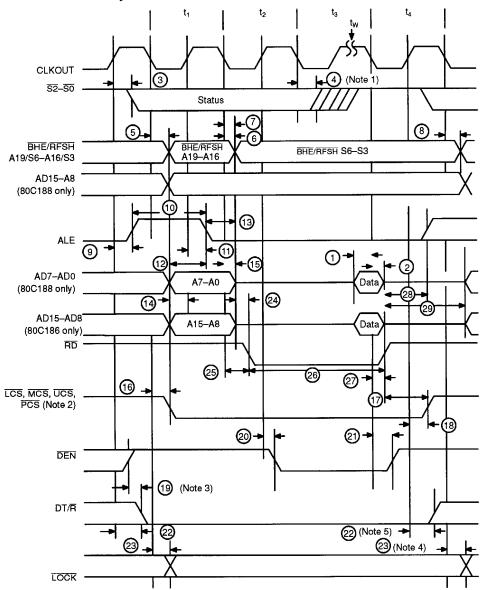

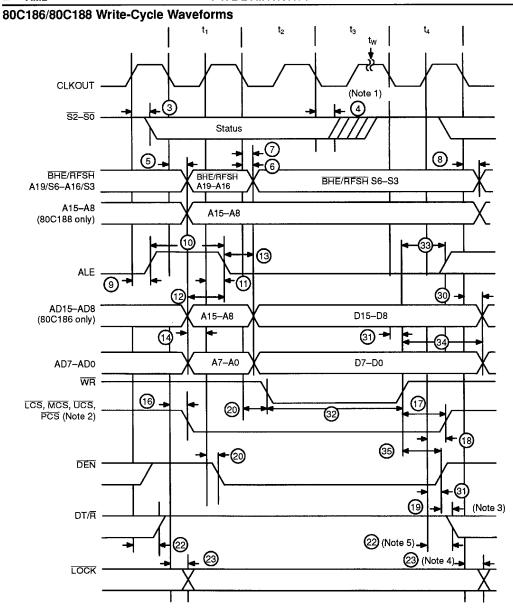

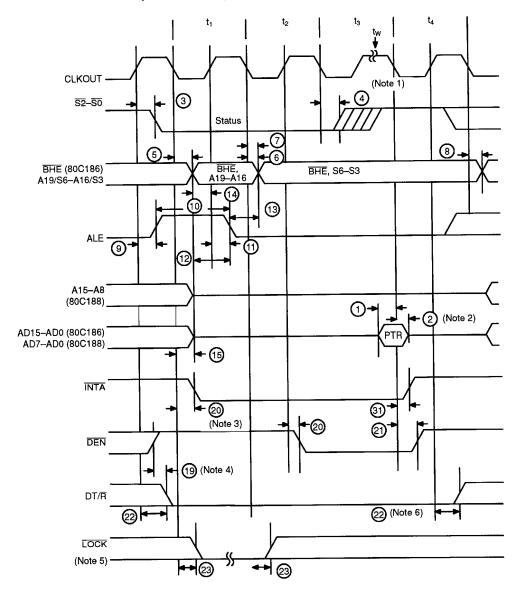

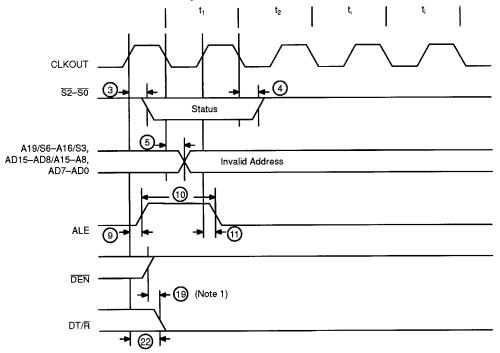

Address Bus Outputs (19–16) and Bus Cycle Status (6–3) indicate the four most significant address bits during T1. These signals are active High.

During T2, T3, TW, and T4, the S6 pin is Low to indicate a CPU-initiated bus cycle, or High to indicate a DMA-initiated bus cycle. During the same T states, S3, S4, and S5 are always Low. These outputs are floated during bus HOLD or RESET.

### A15-A8 (80C188 only) Address-Only Bus (Outputs)

Address-Only Bus (15–8) contains valid addresses from T1–T4. The bus is active High. These outputs are floated during a bus HOLD or RESET.

# AD7-AD0 (80C188 only) Address/Data Bus (Inputs/Outputs)

Address/Data Bus (7–0) signals constitute the time multiplexed memory or I/O address (T1) and data (T2, T3, TW, and T4) bus. The bus is active High. These pins are floated during bus HOLD or RESET.

# AD15-AD0 (80C186 only) Address/Data Bus (Inputs/Outputs)

Address/Data Bus (15–0) signals constitute the time multiplexed memory or I/O address (T1) and data (T2, T3, TW, and T4) bus. The bus is active High. A0 is analogous to  $\overline{\rm BHE}$  for the lower byte of the data bus, pins D7–D0. It is Low during T1 when a byte is to be transferred onto the lower portion of the bus in memory or I/O operations. These pins are floated during a bus HOLD or RESET.

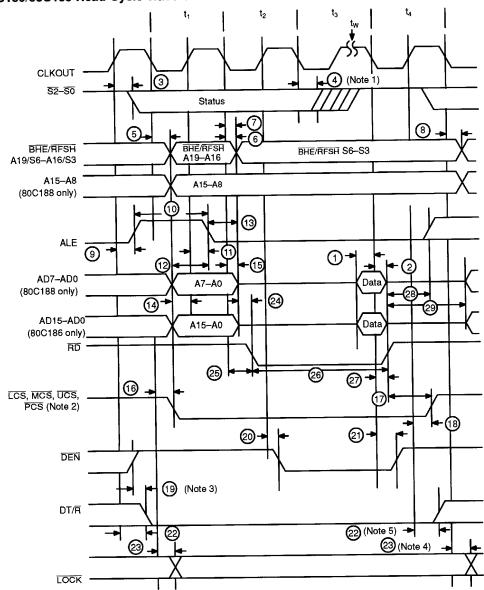

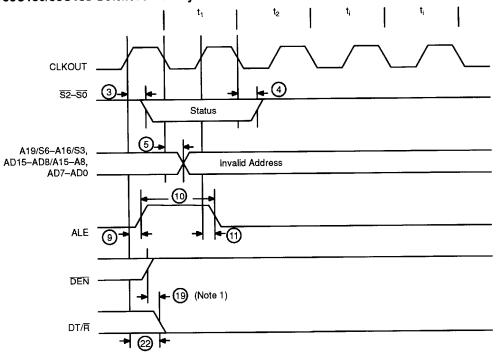

#### ALE/QS0

#### Address Latch Enable/Queue Status (Output)

Address Latch Enable/Queue Status 0 is provided by the 80C186/C188 to latch the address. ALE is active High, with addresses guaranteed to be valid on the trailing edge.

#### **ARDY**

### Asynchronous Ready (Input)

Asynchronous Ready informs the 80C186/C188 that the addressed memory space or I/O device will complete a data transfer. The ARDY pin accepts a rising edge that is asynchronous to CLKOUT and is active High. The falling edge of ARDY must be synchronized to the 80C186/C188 clock. Connecting ARDY High always asserts the ready condition to the CPU. If this line is unused, it should be tied Low to yield control to the SRDY pin.

# BHE (80C186 only) Bus High Enable (Output)

The BHE (Bus High Enable) signal is analogous to A0 in that it is used to enable data on to the most significant half of the data bus, pins D15–D8. BHE is Low during T1 when the upper byte is transferred and remains Low through T3 and TW. BHE does not need to be latched. BHE floats during HOLD or RESET.

In Enhanced Mode, BHE is also used to signify DRAM refresh cycles. A refresh cycle is indicated by both BHE and A0 being High.

#### **BHE** and A0 Encodings

| BHE<br>Function | A0<br>Value | Value                                              |

|-----------------|-------------|----------------------------------------------------|

| 0               | 0           | Word Transfer                                      |

| 0               | 1           | Byte Transfer on upper half of data<br>bus (D8-D1) |

| 1               | 0           | Byte Transfer on lower half of data<br>bus (D7–D0) |

| 1               | 1           | Refresh                                            |

#### **CLKOUT**

#### **Clock Output (Output)**

Clock Output provides the system with a 50% duty cycle waveform. All device pin timings are specified relative to CLKOUT. CLKOUT is active during RESET and bus HOLD.

## **DEN**

#### **Data Enable (Output)**

Data Enable is provided as a data bus transceiver output enable.  $\overline{\text{DEN}}$  is active Low during each memory and I/O access (including 80C187 access).  $\overline{\text{DEN}}$  is High whenever DT/ $\overline{\text{R}}$  changes state.  $\overline{\text{DEN}}$  floats during a bus HOLD or RESET.

### DRQ0-DRQ1

#### **DMA Requests (Inputs)**

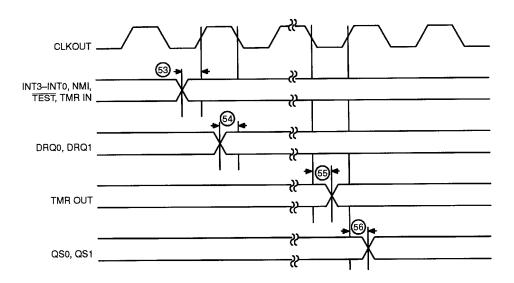

DMA Request is asserted High by an external device when it is ready for DMA Channel 0 or 1 to perform a transfer. These signals are level triggered and internally synchronized.

#### DT/R

#### Data Transmit/Receive (Output)

Data Transmit/Receive controls the direction of data flow through an external data bus transceiver. When Low, data is transferred to the 80C186/C188. When High, the 80C186/C188 place write data on the data bus.  $DT/\overline{R}$  floats during a bus HOLD or RESET.

🖿 0257525 0049581 264 🖿

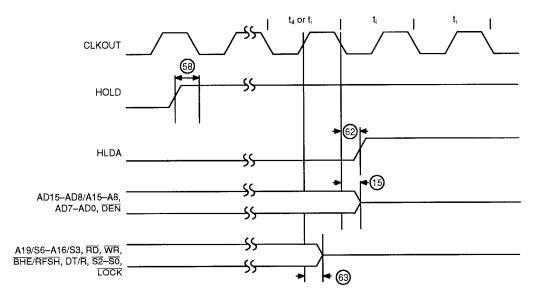

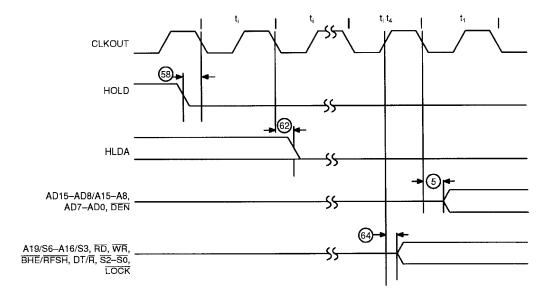

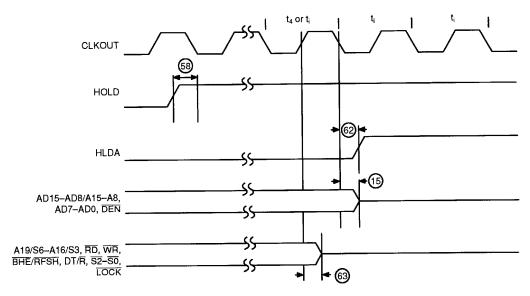

# HOLD, HLDA

#### (Input, Output)

HOLD indicates that another bus master is requesting the local bus. The HOLD input is active High. The 80C186/C188 generate HLDA (High) in response to a HOLD request. Simultaneous with the issuance of HLDA, the 80C186/C188 will float the local bus and control lines. After HOLD is detected as being Low, the 80C186/C188 lower HLDA. When the 80C186/80C188 needs to run another bus cycle, it will again drive the local bus and control lines.

In Enhanced Mode, HLDA goes Low when a DRAM refresh cycle is pending in the 80C186/C188 and an external bus master has control of the bus. It will be up to the external master to relinquish the bus by lowering HOLD so that the 80C186/C188 may execute the refresh cycle.

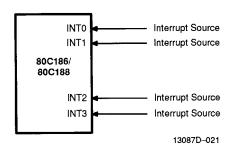

# INTO, INT1/SELECT, INT2/INTAO, INT3/INTA1/IRQ

# Maskable Interrupt Requests (Inputs, Input/Output)

Maskable Interrupt Requests can be requested by activating one of these pins. When configured as inputs, these pins are active High. Interrupt Requests are synchronized internally. INT2 and INT3 may be configured to provide active-Low interrupt-acknowledge output signals. All interrupt inputs may be configured to be either edge or level triggered. To ensure recognition, all interrupt requests must remain active until the interrupt is acknowledged. When Slave Mode is selected, the function of these pins changes (see the Interrupt Controller section of this data sheet).

#### **LCS**

#### Lower Memory Chip Select (Output/Input)

Lower Memory Chip Select is active Low whenever a memory reference is made to the defined lower portion (1K–256K) of memory.  $\overline{\text{LCS}}$  does not float during bus HOLD. The address range activating  $\overline{\text{LCS}}$  is software programmable.

UCS and LCS are sampled upon the rising edge of RES. If both pins are held Low, the 80C186/C188 enter ONCE mode. In ONCE mode all pins assume a high-impedance state and remain so until a subsequent RESET. LCS has a weak internal pull-up that is active only during RESET to ensure that the 80C186/C188 does not enter ONCE mode inadvertently.

# LOCK

#### Lock (Output)

LOCK output indicates that other system bus masters are not to gain control of the system bus. LOCK is active Low. The LOCK signal is requested by the LOCK prefix instruction and is activated at the beginning of the first

data cycle associated with the instruction immediately following the LOCK prefix. It remains active until the completion of that instruction. No instruction prefetching will occur while LOCK is asserted. LOCK has an internal pull-up that is active during bus HOLD or RESET.

## MCS0, MCS1, MCS2, MCS3 Mid-Range Memory Chip Select (Output/Inputs, Outputs)

Mid-Range Memory Chip Select signals are active Low when a memory reference is made to the defined midrange portion of memory (8K–512K). These lines do not float during bus HOLD. The address ranges activating MCS3–MCS0 are software programmable.

In Enhanced Mode, MCS0 and MCS3 become dummy inputs to maintain compatibility. They should be treated as inputs and tied High/Low when in Enhanced Mode.

MCS0 and MCS1 have weak internal pull-ups that are active during RESET.

#### NMI

#### Non-Maskable Interrupt (Input)

The Non-Maskable Interrupt input causes a Type 2 interrupt. An NMI transition from Low to High is latched and synchronized internally, and initiates the interrupt at the next instruction boundary. NMI must be asserted for at least one CLKOUT period. The Non-Maskable Interrupt cannot be avoided by programming.

### PCS5/A1

# Peripheral Chip Select 5 or Latched A1 (Output)

Peripheral Chip Select 5 or Latched A1 may be programmed to provide a sixth peripheral chip select, or to provide an internally latched A1 signal. The address range activating PCS5 is software programmable. When programmed to provide latched A1 rather than PCS5, this pin will retain the previously latched value of A1 during a bus HOLD. A1 is active High. PCS5/A1 does not float during bus HOLD.

#### PCS6/A2

# Peripheral Chip Select 6 or Latched A2 (Output)

Peripheral Chip Select 6 or Latched A2 may be programmed to provide a seventh peripheral chip select, or to provide an internally latched A2 signal. The address range activating PCS6 is software programmable. When programmed to provide latched A2 rather than PCS6, this pin retains the previously latched value of A2 during a bus HOLD. A2 is active High. PCS6/A2 does not float during bus HOLD.

#### PCS4-PCS0

#### Peripheral Chip Select Signals (Outputs)

Peripheral Chip Select signals (4–0) are active Low when a reference is made to the defined peripheral area

(64-Kbyte I/O or 1-Mbyte memory space). These lines do not float during bus HOLD. The address ranges activating PCS4-PCS0 are software programmable.

$\overline{S2}$  may be used as a logical memory or I/O indicator, and  $\overline{S1}$  as a DT/ $\overline{R}$  indicator.

#### RD/QSMD

#### Read Strobe (Output/Input)

Read Strobe is an active Low signal, which indicates that the 80C186/C188 is performing a memory or I/O read cycle. It is guaranteed not to go Low before the A/D bus is floated. An internal pull-up ensures that  $\overline{\text{RD}}/\overline{\text{QS}}$ - $\overline{\text{MD}}$  is High during RESET. Following RESET, the pin is sampled to determine whether the 80C186/C188 is to provide ALE,  $\overline{\text{RD}}$ , and  $\overline{\text{WR}}$ , or queue status information. To enable Queue Status Mode,  $\overline{\text{RD}}$  must be connected to GND.  $\overline{\text{RD}}$  floats during bus HOLD.

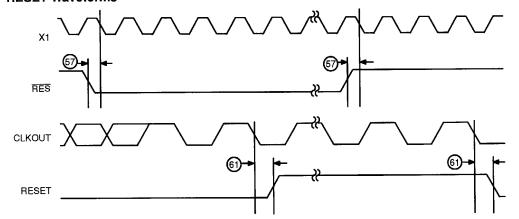

## RES

#### **RESET (Input)**

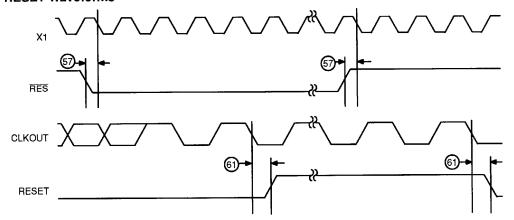

An active  $\overline{\text{RES}}$  causes the 80C186/C188 to immediately terminate its present activity, clear the internal logic, and enter a dormant state. This signal may be asynchronous to the 80C186/C188 clock. The 80C186/C188 begins fetching instructions approximately  $6^{1}/2$  clock cycles after  $\overline{\text{RES}}$  is returned High. For proper initialization,  $V_{\infty}$  must be within specifications and the clock signal must be stable for more than four clocks with  $\overline{\text{RES}}$  held Low.  $\overline{\text{RES}}$  is internally synchronized. This input is provided with a Schmitt-trigger to facilitate power-on  $\overline{\text{RES}}$  generation via an RC network.

#### RESET

## System Reset (Output)

RESET output indicates that the 80C186/C188 CPU is being reset and can be used as a system reset. It is active High, synchronized with the processor clock, and lasts an integer number of clock periods corresponding to the length of the RES signal. RESET goes inactive two clockout periods after RES goes inactive. When tied to the TEST pin, RESET forces the 80C186/ 80C188 into enhanced mode. RESET is not floated during bus HOLD.

#### RFSH (80C188 only) Refresh (Output)

In compatible mode, RFSH is High. In enhanced mode, RFSH is asserted Low to signify a refresh bus cycle. The RFSH output pin floats during bus HOLD or RESET, regardless of operating mode.

# <u>52</u>–<u>50</u>

#### **Bus Cycle Status (Outputs)**

Bus cycle status  $\overline{\text{S2}}\overline{-\text{S0}}$  are encoded to provide bustransaction information.

The status pins float during HOLD/HLDA.

#### 80C186/C188 Bus Cycle Status Information

| <u>S2</u> | <u>81</u> | <u>50</u> | Bus Cycle Initiated    |

|-----------|-----------|-----------|------------------------|

| 0         | 0         | 0         | Interrupt Acknowledge  |

| 0         | 0         | 1         | Read I/O               |

| 0         | 1         | 0         | Write I/O              |

| 0         | 1         | 1         | Halt                   |

| 1         | 0         | 0         | Instruction Fetch      |

| 1         | 0         | 1         | Read Data from Memory  |

| 1         | 1         | 0         | Write Data to Memory   |

| 1         | 1         | 1         | Passive (no bus cycle) |

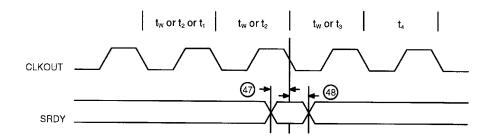

#### SRDY

#### Synchronous Ready (Input)

Synchronous Ready informs the 80C186/C188 that the addressed memory space or I/O device will complete a data transfer. The SRDY pin accepts an active-High input synchronized to CLKOUT. The use of SRDY allows a relaxed system timing over ARDY. This is accomplished by elimination of the one-half clock cycle required to internally synchronize the ARDY input signal. Connecting SRDY High always asserts the ready condition to the CPU. If this line is unused, it should be tied Low to yield control to the ARDY pin.

#### TEST

# Test (Input)

The TEST pin is sampled during and after reset to determine whether the 80C186/C188 is to enter Compatible or Enhanced Mode. Enhanced Mode requires TEST to be High on the rising edge of RES and Low four CLKOUT cycles later. Any other combination places the 80C186/C188 in Compatible Mode. During power-up, active RES is required to configure TEST as an input. A weak internal pull-up ensures a High state when the pin is not driven. This pin is examined by the WAIT instruction. If the TEST input is High when WAIT execution begins, instruction execution will suspend. TEST resampled every five clocks until it goes Low, at which time execution resumes. If interrupts are enabled while the 80C186/C188 is waiting for TEST, interrupts will be serviced.

#### TMR INO, TMR IN1 Timer Inputs (Inputs)

Timer inputs are used either as clock or control signals, depending upon the programmed timer mode. These inputs are active High (or Low-to-High transitions are counted) and internally synchronized. Timer inputs must

**257525 0049583 037**

be tied High when not being used as clock or retrigger inputs.

# TMR OUT0, TMR OUT1 Timer Outputs (Outputs)

Timer outputs are used to provide single pulse or continuous waveform generation, depending upon the timer mode selected. These outputs are not floated during a bus HOLD.

## **UCS**

#### Upper Memory Chip Select (Output/Input)

Upper Memory Chip Select is an active Low output whenever a memory reference is made to the defined upper portion (1K–256K block) of memory. UCS does not float during bus HOLD. The address range activating UCS is software programmable.

UCS and LCS are sampled upon the rising edge of RES. If both pins are held Low, the 80C186/C188 enters ONCE Mode. In ONCE Mode, all pins assume a high-impedance state and remain so until a subsequent RESET. UCS has a weak internal pull-up that is active during RESET to ensure that the 80C186/C188 does not enter ONCE Mode inadvertently.

# V<sub>CC</sub> Power Supply (Inputs)

System power: +5-V power supply.

# V<sub>SS</sub> Ground (Inputs) System ground.

#### WR/QS1

#### Write Strobe/Queue Status 1 (Output)

Write Strobe/Queue Status 1 indicates that the data on the bus is to be written into a memory or an I/O device. It is active Low and floats during bus HOLD or RESET. When the 80C186/C188 is in Queue Status Mode, the ALE/QS0 and  $\overline{WR}/QS1$  pins provide information about processor/instruction queue interaction.

| QS1 | QS0 | Queue Operation                          |

|-----|-----|------------------------------------------|

| 0   | 0   | No queue operation                       |

| 0   | 1   | First opcode byte fetched from the queue |

| 1   | 1   | Subsequent byte fetched from the queue   |

| 1   | 0   | Empty the queue                          |

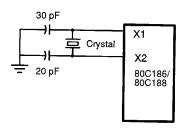

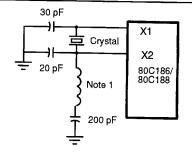

# X1, X2 Crystal Inputs (Input/Output)

Crystal inputs X1 and X2 provide external connections for a fundamental mode or third overtone parallel resonant crystal for the internal oscillator. X1 can connect to an external clock instead of a crystal. In this case, minimize the capacitance on X2. The input or oscillator frequency is internally divided by two to generate the clock signal (CLKOUT).

# **FUNCTIONAL DESCRIPTION**

#### Introduction

The following Functional Description describes the base architecture of the 80C186/C188. The 80C186/80C188 is a very high integration 16-bit microprocessor. It combines 15–20 of the most common microprocessor system components onto one chip. The 80C186/80C188 is object code compatible with the 8086/8088 microprocessors and adds 10 new instruction types to the 8086/8088 instruction set.

The 80C186/C188 has two major modes of operation, Compatible and Enhanced. In Compatible Mode the 80C186/C188 is completely compatible with the NMOS 80186/80188, with the exception of 8087 support. The Enhanced Mode adds two new features to the system design: power-save control, and dynamic RAM refresh.

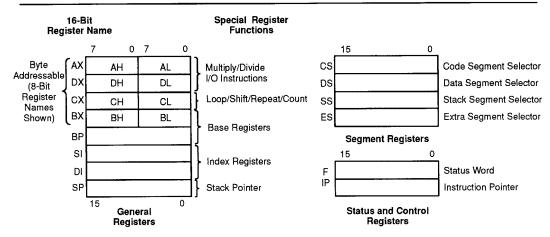

#### 80C186/C188 Base Architecture

The 8086, 8088, 80186, and 80188 Family all contain the same basic set of registers, instructions, and addressing modes. The 80C186/C188 processor is upward compatible with the 8086 and 8088 CPUs.

#### **Register Set**

The 80C186/C188 base architecture has fourteen registers, as shown in Figure 1. These registers are grouped into the following categories.

#### General Registers

Eight 16-bit general purpose registers may be used for arithmetic and logical operands. Four of these (AX, BX,

CX, and DX) can be used as 16-bit registers or split into pairs of separate 8-bit registers.

#### Segment Registers

Four 16-bit special-purpose registers select, at any given time, the segments of memory that are immediately addressable for code, stack, and data. (For usage, refer to Memory Organization.)

#### Base and Index Registers

Four of the general-purpose registers may also be used to determine offset addresses of operands in memory. These registers may contain base addresses or indexes to particular locations within a segment. The addressing mode selects the specific registers for operand and address calculations.

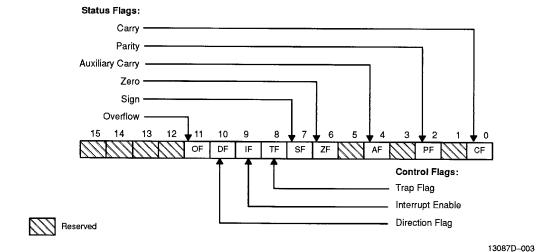

#### Status and Control Registers

Two 16-bit special-purpose registers record or alter certain aspects of the 80C186/C188 processor state. These are the Instruction Pointer Register, which contains the offset address of the next sequential instruction to be executed, and the Status Word Register, which contains status and control flag bits (see Figures 1 and 2).

#### Status Word Description

The Status Word records specific characteristics of the result of logical and arithmetic instructions (bits 0, 2, 4, 6, 7, and 11) and controls the operation of the 80C186/C188 within a given operating mode (bits 8, 9, and 10). The Status Word Register is 16-bits wide. The function of the Status Word bits is shown in Table 1.

Figure 1. 80C186/C188 Register Set

13087D-002

■ 0257525 0049585 90T ■

Table 1. Status Word Bit Functions

| Bit<br>Position | Name | Function                                                                                                                                   |

|-----------------|------|--------------------------------------------------------------------------------------------------------------------------------------------|

| 0               | CF   | Carry Flag—Set on high-order bit carry or borrow; cleared otherwise.                                                                       |

| 2               | PF   | Parity Flag—Set if low-order 8 bits of result contain an even number of 1 bits; cleared otherwise.                                         |

| 4               | AF   | Auxiliary Carry—Set on carry from or borrow to the low order four bits of the general purpose register AL; cleared otherwise.              |

| 6               | ZF   | Zero Flag—Set if result is 0; cleared otherwise.                                                                                           |

| 7               | SF   | Sign Flag—Set equal to high-order bit of result (0 if positive, 1 if negative).                                                            |

| 8               | TF   | Single-Step Flag—Once set, a single-step interrupt occurs after the next instruction executes. TF is cleared by the single-step interrupt. |

| 9               | lF   | Interrupt-Enable Flag—When set, maskable interrupts cause the CPU to transfer control to an interrupt vector specified location.           |

| 10              | DF   | Direction Flag—Causes string instructions to auto decrement the appropriate index register when set. Clearing DF causes auto-increment.    |

| 11              | OF   | Overflow Flag—Set if the signed result cannot be expressed within the number of bits in the destination operand; cleared otherwise.        |

Figure 2. Status Word Format

#### **Instruction Set**

The instruction set is divided into seven categories: data transfer, arithmetic, shift/rotate/logical, string manipulation, control transfer, high-level instructions, and processor control. These categories are summarized in 80C186/C188 Instruction Set section.

The 80C186/C188 instruction can reference anywhere from zero to several operands. An operand can reside in a register, in the instruction itself, or in memory. Specific

operand addressing modes are discussed later in this data sheet.

### **Memory Organization**

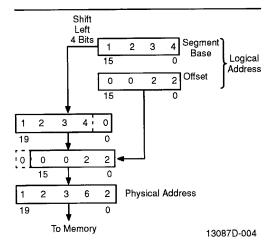

Memory is organized in sets of segments. Each segment is a linear contiguous sequence of up to 64K (2<sup>16</sup>) 8-bit bytes. Memory is addressed using a two-component address (a pointer) that consists of a 16-bit base segment and a 16-bit offset. The 16-bit base values are contained in one of four internal segment registers (code, data, stack, extra). The physical

0257525 0049586 846

address is calculated by shifting the base value LEFT by 4 bits and adding the 16-bit offset value to yield a 20-bit physical address (see Figure 3). This allows for a 1-Mb physical address size.

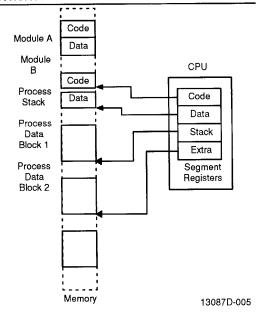

All instructions that address operands in memory must specify the base segment and the 16-bit offset value. For speed and compact instruction encoding, the segment register used for physical address generation is implied by the addressing mode used (see Table 2). These rules follow the way programs are written (see Figure 4) as independent modules that require areas for code and data, a stack, and access to external data areas.

Special segment override instruction prefixes allow the implicit segment register selection rules to be overridden for special cases. The stack, data, and extra segments may coincide for simple programs.

#### Note:

To access operands that do not reside in one of the four immediately available segments, a full 32-bit pointer can be used to reload both the base (segment) and offset values.

Figure 3. Two-Component Address

Figure 4. Segmented Memory Helps Structure Software

#### 80C186/C188 Instruction Set

#### General Purpose

| MOV   | Move byte or word            |

|-------|------------------------------|

| PUSH  | Push word onto stack         |

| POP   | Pop word off stack           |

| PUSHA | Push all registers on stack  |

| POPA  | Pop all registers from stack |

| SCAS  | Scan byte or word string     |

| LODS  | Load byte or word string     |

| XCHG  | Exchange byte or word        |

| XLAT  | Translate byte               |

|       |                              |

**Table 2. Segment Register Selection Rules**

| Memory Reference<br>Needed | Segment Register<br>Used | Implicit Segment Selection Rule                                                           |

|----------------------------|--------------------------|-------------------------------------------------------------------------------------------|

| Instructions               | Code (CS)                | Instruction prefetch and immediate data.                                                  |

| Local Data                 | Data (DS)                | All other data references.                                                                |

| Stack                      | Stack (SS)               | All stack pushes and pops; any memory references that use BP Register as a base register. |

| External Data (Global)     | Extra (ES)               | All string instruction references that use the DI register as an index.                   |

**0257525 0049587 782**

|     | • |

|-----|---|

| AMD | 4 |

| Input/Output   |                                                                |                 |                                                                                   |

|----------------|----------------------------------------------------------------|-----------------|-----------------------------------------------------------------------------------|

|                |                                                                | REPNE/REPNZ     | Repeat while not equal/not zero                                                   |

| IN             | Input byte or word                                             | Logicals        |                                                                                   |

| OUT            | Output byte or word                                            | NOT             | "NOT" byte or word                                                                |

| Address Object | t                                                              | AND             | "AND" byte or word                                                                |

| LEA            | Load effective address                                         | OR              | "Inclusive or" byte or word                                                       |

| LDS            | Load pointer using DS                                          | XOR             | "Exclusive or" byte or word                                                       |

| LES            | Load pointer using ES                                          | TEST            | "Test" byte or word                                                               |

| Flag Transfer  |                                                                | Shifts          |                                                                                   |

| LAHF           | Load AH register from flags                                    | SHL/SAL         | Shift logical/arithmetic left byte or word                                        |

| SAHF           | Store AH register in flags                                     | SHR             | Shift logical right byte or word                                                  |

| PUSHF          | Push flags onto stack                                          | SAR             |                                                                                   |

| POPF           | Pop flags off stack                                            |                 | Shift arithmetic right byte or word                                               |

| Addition       |                                                                | Rotates         | Batata Iadi bata a sa sa d                                                        |

| ADD            | Add byte or word                                               | ROL             | Rotate left byte or word                                                          |

| ADC            | Add byte or word with carry                                    | ROR<br>RCL      | Rotate right byte or word                                                         |

| INC            | Increment byte or word by 1                                    | RCR             | Rotate through carry left byte or word<br>Rotate through carry right byte or word |

| AAA            | ASCII adjust for addition                                      | Flag Operation  |                                                                                   |

| DAA            | Decimal adjust for addition                                    | STC             |                                                                                   |

| Subtraction    | Desirial adjust for addition                                   | CLC             | Set carry flag                                                                    |

| SUB            | Cubirasi buta ar ward                                          | CMC             | Clear carry flag  Complement carry flag                                           |

| SBB            | Subtract byte or word                                          | STD             | Set direction flag                                                                |

| DEC            | Subtract byte or word with borrow  Decrement byte or word by 1 | CLD             | Clear direction flag                                                              |

| NEG            | Negate byte or word                                            | STI             | Set interrupt-enable flag                                                         |

| CMP            | Compare byte or word                                           | CLI             | Clear interrupt-enable flag                                                       |

| AAS            | · · · · · ·                                                    |                 | •                                                                                 |

| DAS            | ASCII adjust for subtraction  Decimal adjust for subtraction   | External Synch  |                                                                                   |

| Multiplication | Decimal adjust for subtraction                                 | HLT             | Halt until interrupt or reset                                                     |

| MUL            | Multiply byte or word unsigned                                 | WAIT            | Wait for TEST pin active                                                          |

| IMUL           | Integer multiply byte or word                                  | ESC             | Escape to extension processor                                                     |

| AAM            | ASCII adjust for multiply                                      | LOCK            | Lock bus during next instruction                                                  |

| Division       | Acon adjust for multiply                                       | No Operation    |                                                                                   |

| DIV            | Divide byte or word unsigned                                   | NOP             | No operation                                                                      |

| IDIV           | Integer divide byte or word                                    | High Level Inst | ructions                                                                          |

| AAD            | ASCII adjust for division                                      | ENTER           | Format stack for procedure entry                                                  |

| CBW            | Convert byte or word                                           | LEAVE           | Restore stack for procedure exit                                                  |

| CWD            | Convert word to doubleword                                     | BOUND           | Detects values outside prescribed                                                 |

| MOVS           | Move byte or word string                                       |                 | range                                                                             |

| INS            | Input bytes or word string                                     | Conditional Tra | ansfers                                                                           |

| OUTS           | Output bytes or word string                                    | JA/JNBE         | Jump if above/not below nor equal                                                 |

| CMPS           | Compare byte or word string                                    | JAE/JNB         | Jump if above or equal/not below                                                  |

| STOS           | Store byte or word string                                      | JB/JNAE         | Jump if below/not above nor equal                                                 |

| REP            | Repeat                                                         | JBE/JNA         | Jump if below or equal/not above                                                  |

| NEF            |                                                                |                 |                                                                                   |

80C186/80C188 Microprocessors

#### PRELIMINARY

JE/JZ

Jump if equal/zero

JG/JNLE

Jump if greater/not less nor equal

JGE/JNL

Jump if greater or equal/not less

JL/JNGE

Jump if less/not greater nor equal

JLE/JNG

Jump if less or equal/not greater

JNC

Jump if not carry

JNE/JNZ

Jump if not equal/not zero

JNO

Jump if not overflow

JNP/JPO Jump if not parity/parity odd

JNS Jump if not sign

JO Jump if overflow

JP/JPE Jump if parity/parity even

JS Jump if sign

**Unconditional Transfers**

CALL Call procedure

RET Return from procedure

JMP Jump

**Iteration Controls**

LOOP Loop

LOOPE/

LOOPZ

Loop if equal/zero

LOOPNE/

LOOPNZ

Loop if not equal/not zero Jump if register CX = 0

JCXZ

Interrupts

Interrupt

INT INTO

Interrupt if overflow

IRET

Interrupt return

#### **Addressing Modes**

The 80C186/C188 provides eight categories of addressing modes to specify operands. Two addressing modes are provided for instructions that operate on register or immediate operands:

- 1. Register Operand Mode: The operand is located in one of the 8- or 16-bit registers.

- Immediate Operand Mode: The operand is included in the instruction.

Six modes are provided to specify the location of an operand in a memory segment. A memory operand address consists of two 16-bit components: a segment base and an offset. The segment base is supplied by a 16-bit segment register either implicitly chosen by the addressing mode or explicitly chosen by a segment override prefix. The offset, also called the effective

address, is calculated by summing any combination of the following three address elements:

- the displacement (an 8- or 16-bit immediate value contained in the instruction):

- the base (contents of either the BX or BP base registers); and,

- the index (contents of either the SI or DI index registers).

Any carry out from the 16-bit addition is ignored. Eightbit displacements are sign-extended to 16-bit values.

Combinations of these three address elements define the six memory addressing modes, described below.

- Direct Mode: The operand's offset is contained in the instruction as an 8- or 16-bit displacement element

- Register Indirect Mode: The operand's offset is in one of the registers SI, DI, BX, or BP.

- Based Mode: The operand's offset is the sum of an 8- or 16-bit displacement and the contents of a base register (BX or BP).

- Indexed Mode: The operand's offset is the sum of an 8- or 16-bit displacement and the contents of an index register (SI or DI).

- Based Indexed Mode: The operand's offset is the sum of the contents of a base register and an index register.

- Based Index Mode with Displacement: The operand's offset is the sum of a base register's contents, an index register's contents, and an 8- or 16-bit displacement.

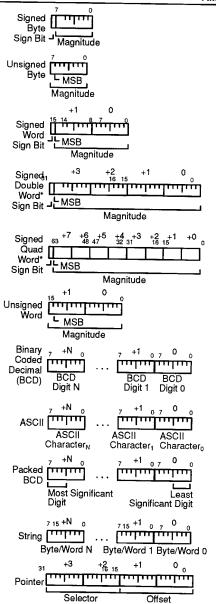

#### **Data Types**

The 80C186/C188 directly supports the following data types:

- Integer: A signed binary numeric value contained in an 8-bit byte or a 16-bit word. All operations assume a two's complement representation.

- Ordinal: An unsigned binary numeric value contained in an 8-bit byte or a 16-bit word.

- Pointer: A 16- or 32-bit quantity, composed of a 16-bit offset component or a 16-bit segment base component in addition to a 16-bit offset component.

- String: A contiguous sequence of bytes or words.

A string may contain 1 to 64 Kbytes.

- ASCII: A byte representation of alphanumeric and control characters using the ASCII standard of character representation.

- BCD: A byte (unpacked) representation of the decimal digits 0-9.

**■** 0257525 0049589 555 **■**

Packed BCD: A byte (packed) representation of two decimal digits (0-9). One digit is stored in each nibble (4 bits) of the byte.

In general, individual data elements must fit within defined segment limits. Figure 5 graphically represents the data types supported by the 80C186/C188.

# I/O Space

The I/O space consists of 64K 8-bit or 32K 16-bit ports. Separate instructions address the I/O space with either an 8-bit port address specified in the instruction, or a 16-bit port address in the DX register. 8-bit port addresses are zero-extended such that A15—A8 are Low. I/O port addresses 00F8(H) through 00FF(H) are reserved.

#### Interrupts

An interrupt transfers execution to a new program location. The old program address (CS:IP) and machine state (Status Word) are saved on the stack to allow resumption of the interrupted program. Interrupts fall into three classes: hardware initiated, INT instructions, and instruction exceptions. Hardware-initiated interrupts occur in response to an external input and are classified as non-maskable or maskable.

Programs may cause an interrupt with an INT instruction. Instruction exceptions occur when an unusual condition that prevents further instruction processing is detected while attempting to execute an instruction.

13087D-006

Figure 5. 80C186/C188 Supported Data Types

**■** 0257525 0049590 277 **■**

exception points to the instruction immediately following the instruction causing the exception.

A table containing up to 256 pointers defines the proper interrupt service routine for each interrupt. Interrupts 0-31, some of which are used for instruction exceptions, are reserved. Table 3 shows the 80C186/C188 predefined types and default priority levels. For each interrupt, an 8-bit vector must be supplied to the 80C186/C188, which identifies the appropriate table entry. Exceptions supply the interrupt vector internally. In addition, internal peripherals and non-cascaded external interrupts generate their own vectors through the internal interrupt controller. INT instructions contain or imply the vector and allow access to all 256 interrupts. Maskable hardware-initiated interrupts supply the 8-bit vector to the CPU during an interrupt acknowledge bus sequence. Non-maskable hardware interrupts use a predefined internally supplied vector.

# Interrupt Sources

The 80C186/C188 can service interrupts generated by software or hardware. The software interrupts are generated by specific instructions (INT, ESC, unused OP, etc.) or the results of conditions specified by instructions (array bounds check, INTO, DIV, IDIV, etc.). All interrupt sources are serviced by an indirect call through an element of a vector table. This vector table is indexed by using the interrupt vector type (Table 3), multiplied by four. All hardware-generated interrupts are sampled at the end of each instruction. Thus, the software interrupts begin service first. Once the service routine is entered and interrupts are enabled, any hardware source of sufficient priority can interrupt the service routine in progress.

Those pre-defined 80C186/C188 interrupts that cannot be masked by programming are described below.

#### Divide Error Exception (Type 0)

Generated when a DIV or IDIV instruction quotient cannot be expressed in the number of bits in the destination.

## Single-Step Interrupt (Type 1)

Generated after most instructions if the TF (single step) flag in the status word is set. This interrupt allows programs to execute one instruction at a time. Interrupts are not be generated after prefix instructions (e.g., REP), instructions that modify segment registers (e.g., POP DS), or the WAIT instruction. Vectoring to the single-step interrupt service routine clears the TF bit. An IRET instruction in the interrupt service routine restores the TF bit to logic 1 and transfers control to the next instruction to be single-stepped.

# Non-Maskable Interrupt-NMI (Type 2)

An external interrupt source that is serviced regardless of the state of the IF (interrupt enable flag) bit. No external interrupt acknowledge sequence is performed. The IF bit is cleared at the beginning of a NMI interrupt to prevent maskable interrupts from being serviced. A typical use of NMI would be to activate a power failure routine.

#### **Breakpoint Interrupt (Type 3)**

A 1-byte version of the INT instructions. It uses 12 (OCH) as an index into the service routine address table (because it is a Type 3 interrupt).

#### INTO Detected Overflow Exception (Type 4)

Generated during an INTO instruction if the 0F bit is set.

#### Array BOUNDS Exception (Type 5)

Generated during a BOUND instruction if the array index is outside the array bounds. The array bounds are located in memory at a location indicated by one of the instruction operands. The other operand indicates the value of the index to be checked.

#### **Unused Opcode Exception (Type 6)**

Generated if execution is attempted on undefined opcodes.

#### **ESCAPE Opcode Exception**

Generated if execution is attempted of ESC opcodes (D8-DFH). The 80C186/C188 does not check the escape opcode trap bit. ESC traps occur in both compatible and enhanced operating modes. The return address of this exception will point to the ESC instruction causing the exception. If a segment override prefix preceded the ESC instruction, the return address will point to the segment override prefix.

#### Note

All numerics coprocessor opcodes cause a trap. The 80C186/C188 does not support the numerics interface.

#### **Hardware Interrupts**

Hardware-generated interrupts are divided into two groups: maskable interrupts and non-maskable interrupts. The 80C186/C188 provides maskable hardware interrupt request pins INT3-INT0. In addition, maskable interrupts may be generated by the 80C186/C188 integrated DMA controller and the integrated timer unit. The vector types for these interrupts is shown in Table 3. Software enables these inputs by setting the interrupt enable flag bit (IF) in the Status Word. The interrupt controller is discussed in the peripheral section of this data sheet.

Further maskable interrupts are disabled while servicing an interrupt because the IF bit is reset as part of the response to an interrupt or exception. The saved Status Word will reflect the enable status of the processor prior

to the interrupt. The interrupt flag will remain zero unless specifically set. The interrupt return instruction restores the Status Word, thereby restoring the original status of IF (interrupt-enable flag) bit. If the interrupt return re-enables interrupts and another interrupt is pending, the 80C186/188 will immediately services the highest-priority interrupt pending (i.e., no instructions of the main line program are executed).

power-up to ensure proper device initialization. RES forces the 80C186/C188 to terminate all execution and local bus activity. No instruction or bus activity occurs as long as  $\overline{\text{RES}}$  is active. After  $\overline{\text{RES}}$  becomes inactive and an internal processing interval elapses, the 80C186/C188 begins execution with the instruction at physical location FFFF0(H). RES also sets some registers to predefined values as shown in Table 4.

#### Initialization and Processor Reset

Processor initialization or startup is accomplished by driving the  $\overline{\text{RES}}$  input pin Low.  $\overline{\text{RES}}$  must be Low during

Table 3. 80C186/C188 Interrupt Vectors

| Interrupt Name                   | Vector<br>Type | Vector<br>Address | Default<br>Priority | Related<br>Instructions | Applicable<br>Notes |

|----------------------------------|----------------|-------------------|---------------------|-------------------------|---------------------|

| Divide Error Exception           | 0              | 00H               | 1                   | DIV, IDIV               | 1                   |

| Single-Step Interrupt            | 1              | 04H               | 1A                  | All                     | 2                   |

| Non-Maskable Interrupt (NMI)     | 2              | 08H               | 1                   | All                     |                     |

| Breakpoint Interrupt             | 3              | OCH               | 1                   | INT                     | 1                   |

| INTO Detected Overflow Exception | 4              | 10H               | 1                   | INTO                    | 1                   |

| Array Bounds Exception           | 5              | 14H               | 1 1                 | BOUND                   | 1                   |

| Unused Opcode Exception          | 6              | 18H               | 1                   | Undefined<br>Opcodes    | 1                   |

| ESC Opcode Exception             | 7              | 1CH               | 1                   | ESC Opcodes             | 1, 3                |

| Timer 0 Interrupt                | 8              | 20H               | 2A                  |                         | 4                   |

| Timer 1 Interrupt                | 18             | 48H               | 2B                  |                         | 4, 5                |

| Timer 2 Interrupt                | 19             | 4CH               | 2C                  |                         | 4, 5                |

| Reserved                         | 9              | 24H               | 3                   |                         | 7,0                 |

| DMA 0 Interrupt                  | 10             | 28H               | 4                   |                         | 5                   |

| DMA 1 Interrupt                  | 11             | 2CH               | 5                   |                         | 5                   |

| INT0 Interrupt                   | 12             | 30H               | 6                   |                         |                     |

| INT1 Interrupt                   | 13             | 34H               | 7                   |                         |                     |

| INT2 Interrupt                   | 14             | 38H               | 8                   |                         |                     |

| INT3 Interrupt                   | 15             | 3CH               | 9                   |                         |                     |

| Reserved                         | 16, 17         | 40H, 44H          | <del>-</del>        |                         |                     |

| Reserved                         | 20–31          | 50H 7CH           |                     |                         |                     |

#### Notes:

Default priorities for the interrupt sources are used only if the user does not program each source to a unique priority level. 1. Generated as a result of an instruction execution.

- Performed in the same manner as 8086/8088.

- An ESC opcode will cause a trap regardless of the 80C186/C188 operating mode. The 80C186/C188 are not directly compatible with the 80188 in this respect. The instruction set of the numerics coprocessor cannot be executed.

All three timers constitute one source of request to the interrupt controller. As such, they share the same priority level with

- respect to other interrupt sources. However, the timers have a defined priority order among themselves (2A > 2B > 2C).

- 5. The vector type numbers of these sources are programmable in Slave Mode.

0257525 0049592 04T **=**

#### Table 4. 80C186/C188 Initial Register State after RESET

| Status Word         | F002(H) |

|---------------------|---------|

| Instruction Pointer | 0000(H) |

| Code Segment        | FFFF(H) |

| Data Segment        | 0000(H) |

| Extra Segment       | 0000(H) |

| Stack Segment       | 0000(H) |

| Relocation Register | 20FF(H) |

| UMCS                | FFFB(H) |

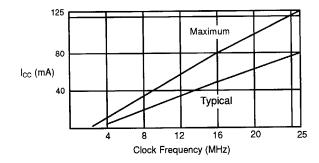

# 80C186/C188 CLOCK GENERATOR

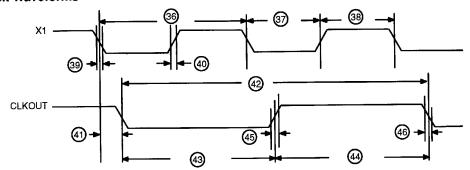

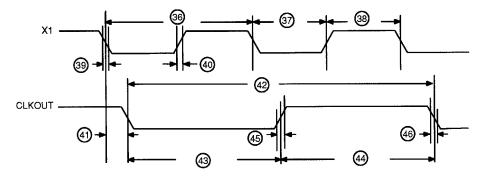

The 80C186/C188 provide an on-chip clock generator for both internal and external clock generation. The clock generator features a crystal oscillator, a divide-bytwo counter, synchronous and asynchronous ready inputs, and reset circuitry.

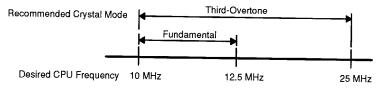

#### Oscillator

The oscillator circuit of the 80C186/C188 is designed to be used either with a parallel resonant fundamental or third-overtone mode crystal, depending upon the frequency range of the application, as shown in Figure 6(c). This is used as the time base for the 80C186/C188. The crystal frequency chosen should be twice the required processor frequency. Use of an LC or RC circuit is not recommended.

The output of the oscillator is not directly available outside the 80C186/C188. The two recommended crystal configurations are shown in Figure 6(a and b). When used in third-overtone mode, the tank circuit shown in Figure 6(b) is recommended for stable operation. The sum of the stray capacitances and loading capacitors should equal the values shown. It is advisable to limit stray capacitance between the X1 and X2 pins to less than 10 pF. While a fundamental-mode circuit requires approximately 1 ms for start-up, the third-overtone arrangement may require 1 ms to 3 ms to stabilize.

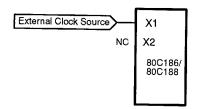

Alternately, the oscillator may be driven from an external source, as shown in Figure 6(d). The configuration shown in Figure 6(e) is not recommended.

The following parameters should be used when choosing a crystal:

Temperature Range: 0°C to 70°C

ESR (Equivalent Series Resistance): 40 ohms max

C0 (Shunt Capacitance of Crystal): 7.0 pF max

C1 (Load Capacitance): 20 pF ±2 pF

Drive Level: 1 mW max

#### **Clock Generator**

The 80C186/C188 clock generator provides the 50%-duty cycle processor clock for the 80C186/80C188. It does this by dividing the oscillator output by two, forming the symmetrical clock. If an external oscillator is used, the state of the clock generator changes on the falling edge of the oscillator signal. The CLKOUT pin provides the processor clock signal for use outside the 80C186/C188. This may be used to drive other system components. All timings are referenced to the output clock.

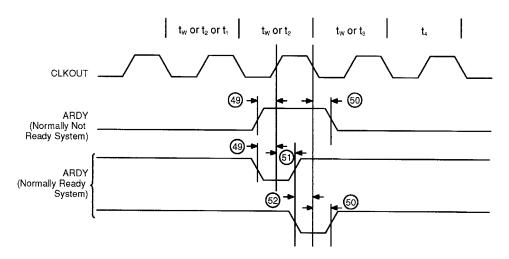

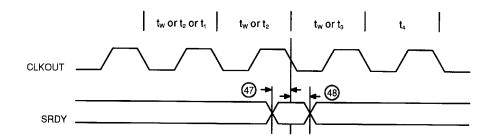

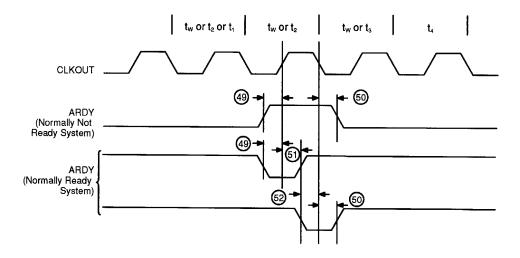

# **READY Synchronization**

The 80C186/C188 provide both synchronous and asynchronous ready inputs. Asynchronous ready synchronization is accomplished by circuitry that samples ARDY in the middle of T2 and again in the middle of each TW until ARDY is sampled High. One-half CLKOUT cycle of resolution time is used for full synchronization of a rising ARDY signal. A High-to-Low transition on ARDY may be used as an indication of the not-ready condition, but it must be performed synchronously to CLKOUT, either in the middle of T2 or TW, or at the falling edge of TW.

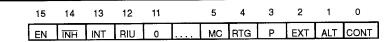

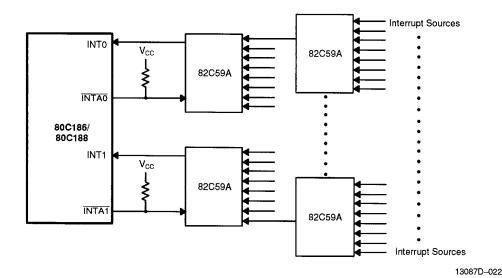

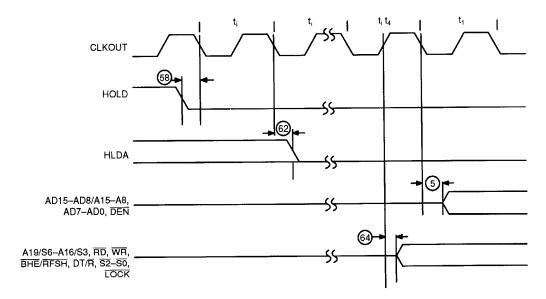

A second ready input (SRDY) is provided to interface with externally synchronized ready signals. This input is sampled at the end of T2 and again at the end of each TW until it is sampled High. By using this input rather than the asynchronous ready input, the half-clock cycle resolution time penalty is eliminated. This input must satisfy set-up and hold times to guarantee proper operation of the circuit.