**Features**

- D3/D4 or ESF framing and SLC-96 compatible

- 2 frame elastic buffer with 32 µsec jitter buffer

- Insertion and detection of A, B,C,D bits. Signalling freeze, optional debounce

- Selectable B8ZS, jammed bit (ZCS) or no zero code suppression

- Yellow alarm and blue alarm signal capabilities

- Bipolar violation count, FT error count, CRC error count

- Selectable robbed bit signalling

- Frame and superframe sync. signals, Tx and Rx

- AMI encoding and decoding

- Per channel, overall, and remote loop around

- Digital phase detector between T1 line & ST-**BUS**

- One uncommitted scan point and drive point

- Pin compatible with MT8977 and MT8979

- ST-BUS compatible

### **Applications**

- DS1/ESF digital trunk interfaces

- Computer to PBX interfaces (DMI and CPI)

- High speed computer to computer data links

May 1995 ISSUE 9

### **Ordering Information**

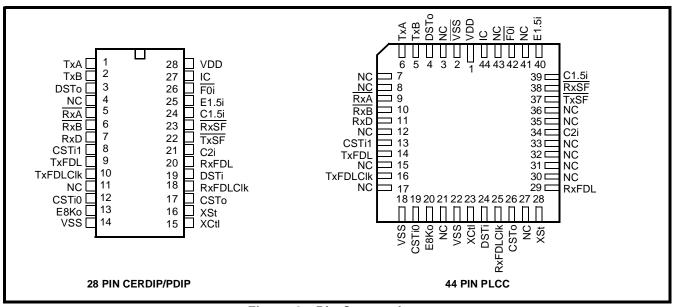

MT8976AC 28 Pin Ceramic DIP MT8976AE 28 Pin Plastic DIP MT8976AP 44 Pin PLCC -40°C to 85°C

### Description

The MT8976 is Mitel's second generation T1 interface solution. The MT8976 meets the Extended Super Frame format (ESF), the current D3/D4 format and is compatible with SLC-96 systems.

The MT8976 interfaces to DS1 1.544 Mbit/sec digital trunk.

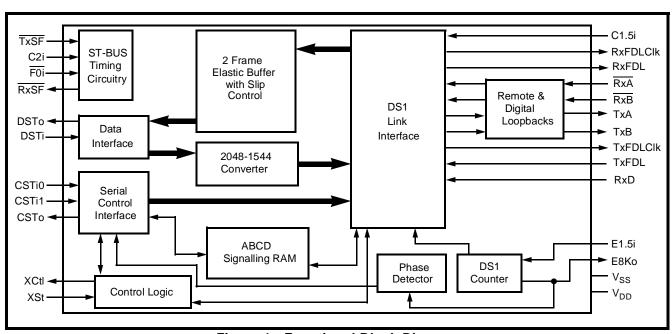

Figure 1 - Functional Block Diagram

Figure 2 - Pin Connections

### **Pin Description**

| Р   | in # | Name     | Description                                                                                                                                                                                                                    |

|-----|------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DIP | PLCC | Name     | Description                                                                                                                                                                                                                    |

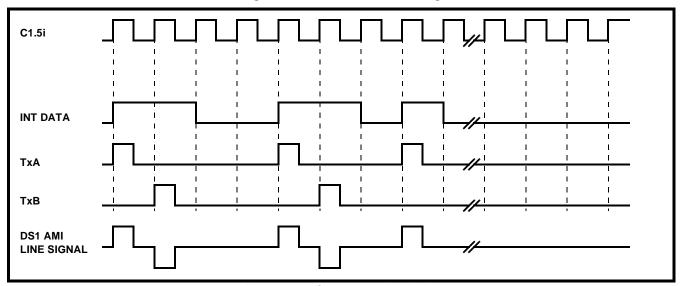

| 1   | 2    | TxA      | <b>Transmit A Output</b> . Unipolar output that can be used in conjunction with TxB and external line driver circuitry to generate the bipolar DS1 signal.                                                                     |

| 2   | 3    | ТхВ      | <b>Transmit B Output.</b> Unipolar output that can be used in conjunction with TxA and external line driver circuitry to generate the bipolar DS1 signal.                                                                      |

| 3   | 5    | DSTo     | <b>Data ST-BUS Output.</b> A 2048 kbit/s serial output stream which contains the 24 PCM or data channels received from the DS1 line.                                                                                           |

| 4   | 4    | NC       | No Connection.                                                                                                                                                                                                                 |

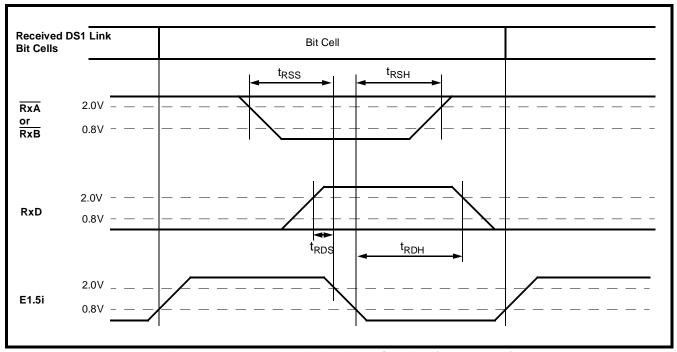

| 5   | 9    | RxA      | Receive A Complementary Input. Accepts a unipolar split phase signal decoded externally from the received DS1 bipolar signal. This input, in conjunction with RxB, detects bipolar violations in the received signal.          |

| 6   | 10   | RxB      | Receive B Complementary Input. Accepts a unipolar split phase signal decoded externally from the received DS1 bipolar signal. This input, in conjunction with RxA, detects bipolar violations in the received signal.          |

| 7   | 11   | RxD      | Receive Data Input. Unipolar RZ data signal decoded from the received DS1 signal. Generally the signals input at RxA and RxB are combined externally with a NAND gate and the resulting composite signal is input at this pin. |

| 8   | 13   | CSTi1    | Control ST-BUS Input #1. A 2048 kbit/s serial control stream which carries 24 per-<br>channel control words.                                                                                                                   |

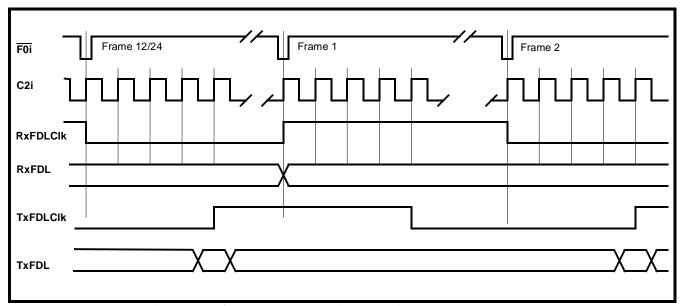

| 9   | 14   | TxFDL    | <b>Transmit Facility Data Link (Input).</b> A 4 kHz serial input stream that is multiplexed into the FDL position in the ESF mode, or the $F_s$ pattern when in SLC-96 mode. It is clocked in on the rising edge of TxFDLClk.  |

| 10  | 16   | TxFDLClk | <b>Transmit Facility Data Link Clock (Output).</b> A 4 kHz clock used to clock in the FDL data.                                                                                                                                |

| 11  |      | NC       | No connection.                                                                                                                                                                                                                 |

### **Pin Description (Continued)**

| Pi  | in #            | Name            | Description                                                                                                                                                                                                                                                                                                             |

|-----|-----------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DIP | PLCC            |                 | Доостірногі.                                                                                                                                                                                                                                                                                                            |

| 12  | 19              | CSTi0           | <b>Control ST-BUS Input #0.</b> A 2048 kbit/s serial control stream that contains 24 per channel control words and two master control words.                                                                                                                                                                            |

| 13  | 20              | E8Ko            | <b>Extracted 8 kHz Output.</b> The E1.5i clock is internally divided by 193 to produce an 8 kHz clock which is aligned with the received DS1 frame and output at this pin. The8 kHz signal is derived from C1.5 in Digital Loopback mode.                                                                               |

| 14  | 6,<br>18,<br>22 | V <sub>SS</sub> | System Ground.                                                                                                                                                                                                                                                                                                          |

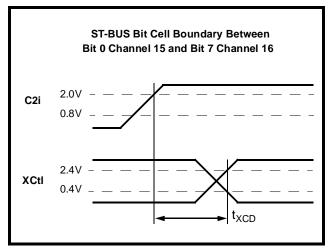

| 15  | 23              | XCtI            | <b>External Control (Output).</b> This is an uncommitted external output pin which is set or reset via bit 3 in Master Control Word 1 on CSTi0. The state of XCtl is updated once per frame.                                                                                                                            |

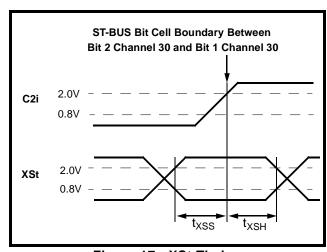

| 16  | 24              | XSt             | <b>External Status (Schmitt Trigger Input).</b> The state of this pin is sampled once per frame and the status is reported in bit 5 of Master Status Word 2 on CSTo.                                                                                                                                                    |

| 17  | 26              | CSTo            | Control ST-BUS Output. This is a 2048 kbit/s serial control stream which provides the 24 per-channel status words, and two master status words.                                                                                                                                                                         |

| 18  | 27              | RxFDLClk        | <b>Receive Facility Data Link Clock (Output).</b> A 4 kHz clock signal used to clock out FDL information. The data is clocked out on the rising edge of RxFDLClk.                                                                                                                                                       |

| 19  | 28              | DSTi            | <b>Data ST-BUS Input.</b> This pin accepts a 2048 kbit/s serial stream which contains the 24 PCM or data channels to be transmitted on the T1 trunk.                                                                                                                                                                    |

| 20  | 29              | RxFDL           | <b>Received Facility Data Link (Output).</b> A 4 kHz serial output stream that is demultiplexed from the FDL in ESF mode, or the received F <sub>S</sub> bit pattern in SLC-96 mode. It is clocked out on the rising edge of RxFDLClk.                                                                                  |

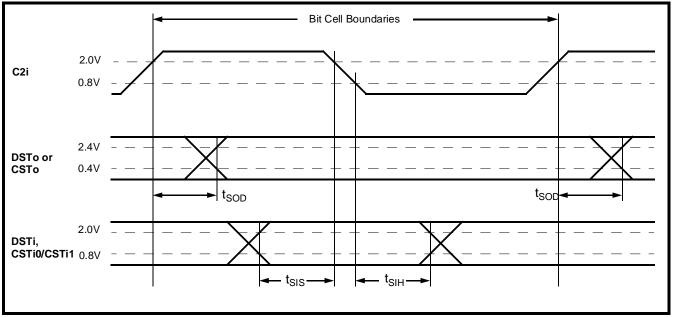

| 21  | 34              | C2i             | 2.048 MHz Clock Input. This is the master clock used for clocking serial data into DSTi, CSTi0 and CSTi1. It is also used to clock serial data out of CSTo and DSTo.                                                                                                                                                    |

| 22  | 37              | TxSF            | <b>Transmit Superframe Pulse Input.</b> A low going pulse applied at this pin will make the next transmit frame the first frame of a superframe. The device will free run if this pin is held high.                                                                                                                     |

| 23  | 38              | RxSF            | Received Superframe Pulse Output. A pulse output on this pin designates that the next frame of data on the ST-BUS is from frame 1 of the received superframe. The period is 12 frames long in D3/D4 modes and 24 frames in ESF mode. Pulses are output only when the device is synchronized to the received DS1 signal. |

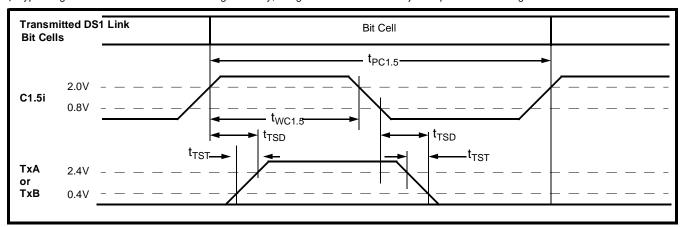

| 24  | 39              | C1.5i           | <b>1.544 MHz Clock Input</b> . This is the DS1 transmit clock and is used to output data on TxA and TxB. It must be phase-locked to C2i. Data is clocked out on the rising edge of C1.5i.                                                                                                                               |

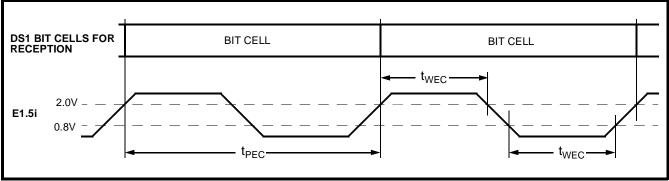

| 25  | 40              | E1.5i           | <b>1.544 MHz Extracted Clock (Input).</b> This clock which is extracted from the received data is used to clock in data at RxA, RxB and RxD. The falling edge of the is nominally aligned with the center of the received bit on RxD, RxA and RxB.                                                                      |

| 26  | 42              | F0i             | <b>Frame Pulse Input.</b> This is the frame synchronization signal which defines the beginning of the 32 channel ST-BUS frame.                                                                                                                                                                                          |

| 27  | 44              | IC              | Internal Connection. Tied to V <sub>SS</sub> for normal operation.                                                                                                                                                                                                                                                      |

| 28  | 1               | $V_{DD}$        | Positive Power Supply Input. +5V ± 5%.                                                                                                                                                                                                                                                                                  |

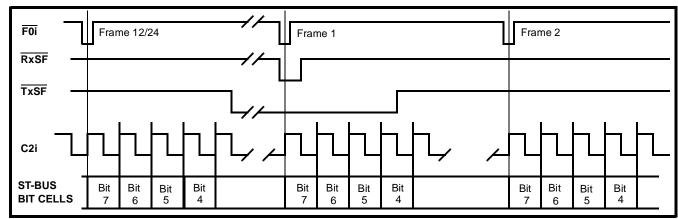

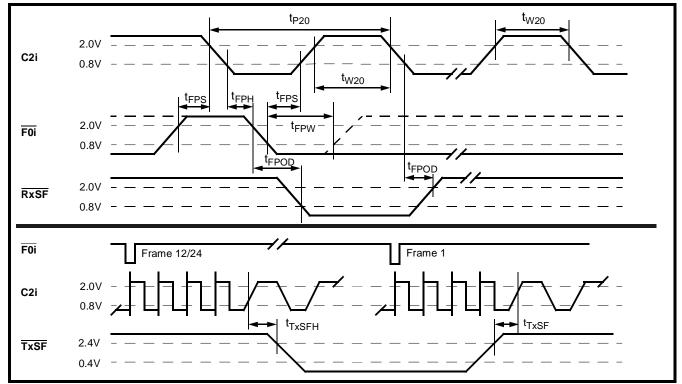

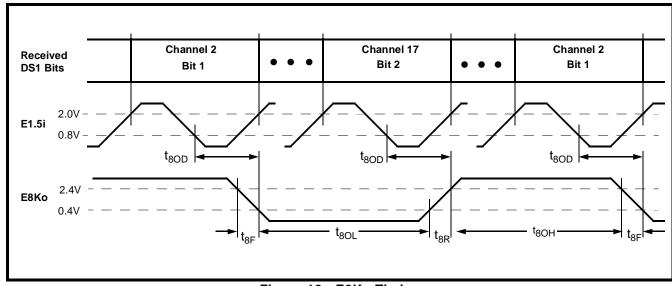

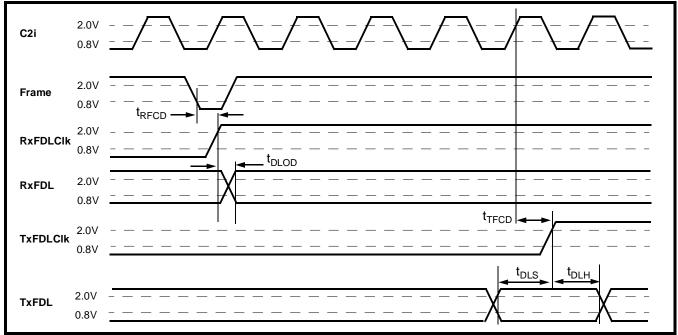

### **Functional Timing Diagrams**

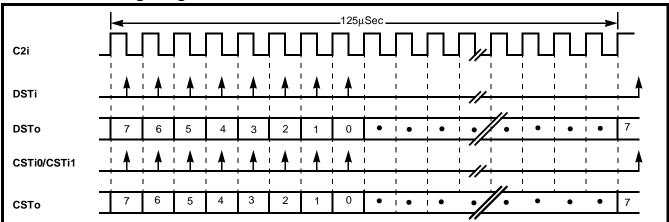

Figure 3 - ST-BUS Timing

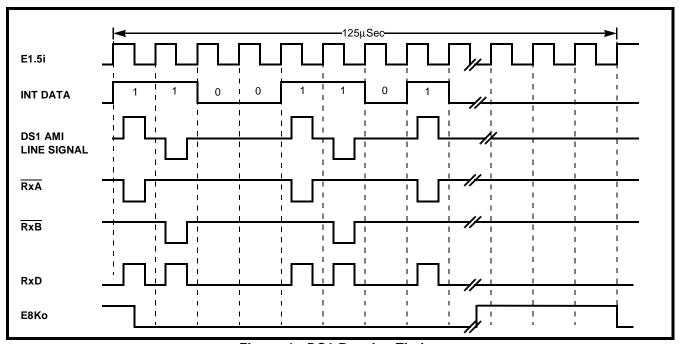

Figure 4 - DS1 Receive Timing

Figure 5 - DS1 Transmit Timing

|    |   | _  |

|----|---|----|

| 31 |   | 24 |

| 30 |   | 23 |

| 29 |   | 22 |

| 28 | Х |    |

| 27 |   | 21 |

| 26 |   | 20 |

| 25 |   | 19 |

| 24 | × |    |

| 23 |   | 18 |

| 22 |   | 17 |

| 21 |   | 16 |

| 20 | × |    |

| 19 |   | 15 |

| 18 |   | 14 |

| 17 |   | 13 |

| 16 | × |    |

| 15 |   | 12 |

| 14 |   | 7  |

| 13 |   | 10 |

| 12 | × |    |

| 11 |   | 6  |

| 10 |   | 8  |

| 6  |   | 7  |

| 8  | × |    |

| 7  |   | 9  |

| 9  |   | 2  |

| 2  |   | 4  |

| 4  | × |    |

| 3  |   | 3  |

| 2  |   | 2  |

| _  |   | -  |

| 0  | × |    |

|    |   |    |

# ST-BUS CHANNEL VERSUS DS1 CHANNEL TRANSMITTED

| 27 28 29 30 31 | × | 21 22 23 24 |

|----------------|---|-------------|

| 24 25 26       | X | 19 20       |

| 22 23 2        |   | 17 18       |

| 19 20 21       | × | 15 16       |

| 17 18          |   | 13 14       |

| 15 16          | × | 12          |

| 13 14          |   | 10 11       |

| 11 12          | × | 6           |

| 9 10           |   | 8 2         |

| 8 /            | × | 9           |

| 9              |   | 2           |

| 4              | × | 4           |

| 2 3            |   | 2 3         |

| 0              | × | 1           |

| DSTo           |   | DS1         |

### ST-BUS CHANNEL VERSUS DS1 CHANNEL RECEIVED

| 31         | O S         | 7 \ \ |      |

|------------|-------------|-------|------|

| 30<br>C    | S S         | 1     | 24   |

| 29<br>P.C. |             | 1     | 23   |

| 28<br>PC   |             |       | 22   |

| 27         |             |       | .,   |

|            | C N         |       | _    |

|            |             | _     | 0 21 |

| t 25       |             | 1     | 9 20 |

|            |             | 1     | 19   |

| 23         |             |       |      |

|            |             | 1     | 18   |

|            | . S         | _     | 17   |

| 20<br>P.C. | S           | 7     | 16   |

| 6          |             |       |      |

| 18<br>P.C. | C ⊆         | 1     | 15   |

| 17<br>P.C. | S<br>S<br>S | 1     | 14   |

| 16<br>P.C. | S           | 1     | 13   |

| 15<br>MC   | ×           |       |      |

| 4 D        | . S         | 1     | 12   |

| 13<br>PC   |             | 1     | 11   |

| 12<br>PC   | S<br>S      | 1     | 10   |

| 7          | : ×         |       |      |

| 10<br>P.C. | . S         | 1     | 6    |

| 9<br>C     | ) N         | 1     | 8    |

| 8<br>C     | ) S         | -     | 7    |

| 7          | ×           |       |      |

| 9 G        | ) S         | 1     | 9    |

| 5<br>PC    | ) S         | -     | 2    |

| 4 G        | N N         | -     | 4    |

| ď          | ×           |       |      |

| 2 G        | C S         | -     | 3    |

| + G        |             | -     | 2    |

| 0 G        |             | 1     | 1    |

| сѕтіо      |             |       | DS1  |

PCCW =PER CHANNEL CONTROL WORD MCW1/2 =MASTER CONTROL WORD 1/2

# ST-BUS CHANNEL VERSUS DS1 CHANNEL CONTROLLED

|                                |          |          |        |     |          |        |     |        |        |          |    | ŀ |         | ŀ       |             |         |        |        |   |        |    |    |   |    |    |    |    |    |    |    | I  |

|--------------------------------|----------|----------|--------|-----|----------|--------|-----|--------|--------|----------|----|---|---------|---------|-------------|---------|--------|--------|---|--------|----|----|---|----|----|----|----|----|----|----|----|

| CST11                          | 0        | _        | 7      |     | 4        | 2      | 9   |        | 00     | 9        | 0  | _ | 12 1    | 13 14   | 4           | 16      | 3 17   | 18     |   | 20     | 2  | 22 |   | 24 | 25 | 26 |    | 28 | 29 | 30 |    |

|                                | <u>В</u> | PC<br>PC | S      | 3   | PC PC    | S<br>S | SC. | 7 F    | ς<br>π | ς<br>P   |    |   | PC<br>P | PC<br>P |             |         | S C    |        |   |        | PC |    |   | S  | ВС | ВС | 27 | S  | S  | S  | 31 |

|                                | Š        | S        | CW CW  | ×   | CW CW CW | Š      | CW  | ں<br>× | CW CW  | Ω<br>≥   | ×  |   | CW CW   |         | C<br>C<br>C | ×<br>CM | ∑<br>^ | C<br>V | × | Š      | Š  | Š  | × | S  | S  | CW | ×  | Š  | S  | Š  | ×  |

|                                | 2        | 7        | 2      |     | 2        | 7      | 2   |        | 7      | 2        | ٥. |   | 2       | 2       | 5           | 2       |        |        |   | 2      | 7  | 7  |   | 7  | 2  | 2  |    | 2  | 2  | 2  |    |

| DS1                            | 1        | 2        | 3      |     | 4        | 2      | 9   |        | 2 8    | 8 9      | 6  | 1 | 10 11   | 1 12    | 2           | 13      | 3 14   | 15     |   | 16     | 17 | 18 |   | 19 | 20 | 21 |    | 22 | 23 | 24 |    |

| PCCW =PER CHANNEL CONTROL WORD | =PER     | CHA      | NNEL ( | CON | rrol     | WOR    | ٥   |        |        |          |    |   |         |         |             |         |        |        |   |        |    |    |   |    |    |    |    |    |    |    |    |

|                                |          |          |        |     |          |        |     |        | (      | ()<br>() |    |   |         | 0       | 9           |         |        | į      | ( | (<br>( |    | ,  |   |    |    |    |    |    |    |    |    |

# ST-BUS CHANNEL VERSUS DS1 CHANNEL CONTROLLED

| 31<br>MS<br>W2                                                         |          |

|------------------------------------------------------------------------|----------|

| % CS ×                                                                 | 24       |

| 28 29<br>PCS PCS F<br>W W                                              | 23       |

| 28<br>V W                                                              | 22       |

| × ×                                                                    |          |

| 26<br>PCS                                                              | 21       |

| 25<br>∨ ×                                                              | 20       |

| PCS W                                                                  | 19       |

| × 23                                                                   |          |

| 22<br>PCS<br>W                                                         | 18       |

| 21<br>V<br>W                                                           | 17       |

| 20<br>PCS F                                                            | 16       |

| <del>6</del> ×                                                         |          |

| 18<br>V V                                                              | 15       |

| 17<br>W                                                                | 14       |

| 16<br>W W                                                              | 13       |

| 15<br>MS<br>W1                                                         |          |

| PCS ×                                                                  | 12       |

| 13<br>W                                                                | 11       |

| 12 13 14 15 16 17 18 PCS PCS PCS WW WW W W W W W W W W W W W W W W W W | 10 11 12 |

| 5 ×                                                                    |          |

| 10<br>W W                                                              | 6        |

| 9<br>PCS<br>₩                                                          | 8        |

| 8 9 10 11 W W W W                                                      | 7        |

| r×                                                                     |          |

| e<br>PCS<br>W                                                          | 9        |

| 5<br>W                                                                 | 2        |

| 4 S S                                                                  | 4        |

| ნ <mark>გ</mark> ≷                                                     |          |

| 2<br>PCS                                                               | 3        |

| 1 2 PCS PCS W                                                          | 2        |

| 0 1 2 3 4 5 6<br>PCS PCS PCS PS PCS PCS PCS<br>W W W W W W             | 1        |

| CSTo                                                                   | DS1      |

PCSW =PER CHANNEL STATUS WORD PSW =PHASE STATUS WORD MSW =MASTER STATUS WORD

Figure 6 - ST-BUS Channel Allocations

ST-BUS VERSUS DS1 CHANNEL STATUS

### X=UNUSED CHANNEL

### **Functional Description**

The MT8976 provides a simple interface to a bidirectional DS1 link. All of the formatting and signalling insertion and detection is done by the device. Various programmable options in the device include: ESF, D3/D4, or SLC-96 mode, common channel or robbed bit signalling, zero code suppression, alarms, and local and remote loop back. All data and control information is communicated to the MT8976 via 2048 kbit/s serial streams conforming to Mitel's ST-BUS format.

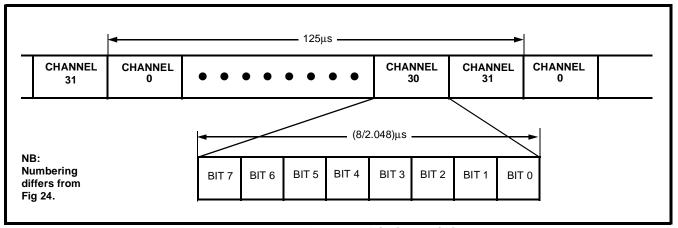

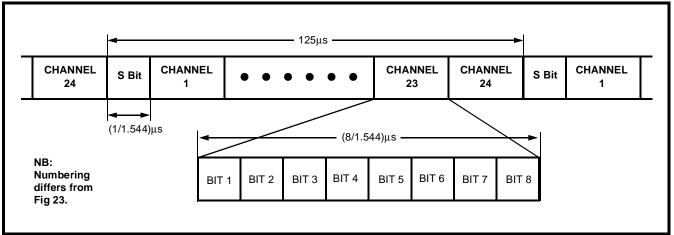

The ST-BUS is a TDM serial bus that operates at 2048 kbits/s. The serial streams are divided into 125 µsec frames that are made up of 32 8 bit channels. A serial stream that is made up of these 32 8 bit channels is known as an ST-BUS stream, and one of these 64 kbit/s channels is known as an ST-BUS channel.

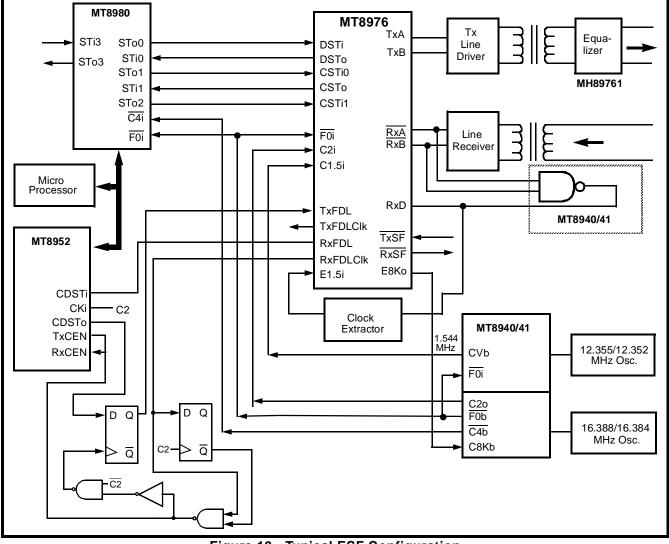

The system side of the MT8976 is made up of STBUS inputs and outputs, i.e., control inputs and outputs (CSTi/o) and data inputs and outputs (DSTi/o). These signals are functionally represented in Figure 3. The line side of the device is made up of the split phase inputs and outputs that can be interfaced to an external bipolar receiver and transmitter. Functional transmit and receive timing is shown in Figures 4 and 5.

Data for transmission on the DS1 line is clocked serially into the device at the DSTi pin. The DSTi pin accepts a 32 channel time division multiplexed STBUS stream. Data is clocked in with the falling edge of the C2i clock. ST-BUS frame boundaries are defined by the frame pulse applied at the F0i pin. Only 24 of the available 32 channels on the ST-BUS serial stream are actually transmitted on the DS1 side. The unused 8 channels are ignored by the device.

Data received from the DS1 line is clocked out of the device in a similar manner at the DSTo pin. Data is clocked out on the rising edge of the C2i clock. Only 24 of the 32 channels output by the device contain the information from the DS1 line. The DSTo pin is, however, actively driven during the unused channel timeslots. Figure 6 shows the correspondence between the DS1 channels and the ST-BUS channels.

All control and monitoring of the device is accomplished through two ST-BUS serial control inputs and one serial control output. Control ST-BUS input number 0 (CSTi0) accepts an ST-BUS serial stream which contains the 24 per channel control words and two master control words. The per

channel control words relate directly to the 24 information channels output on the DS1 side. The master control words affect operation of the whole device. Control ST-BUS input number 1 (CSTi1) accepts an ST-BUS stream containing the A, B, C and D signalling bits. The relationship between the CSTi channels and the controlled DS0 channels is shown in Figure 6. Status and signalling information is received from the device via the control ST-BUS output (CSTo). This serial output stream contains two master status words, 24 per channel status words and one Phase Status Word. Figure 6 shows the correspondence between the received DS1 channels and the status words. Detailed information on the operation of the control interface is presented below.

### **Programmable Features**

The main features in the device are programmed through two master control words which occupy channels 15 and 31 in Control ST-BUS input stream number 0 (CSTi0). These two eight bit words are used to:

- Select the different operating modes of the device ESF, D3/D4 or SLC-96.

- Activate the features that are needed in a certain application; common channel signalling, zero code suppression, signalling debounce, etc.

- Turn on in service alarms, diagnostic loop arounds, and the external control function.

Tables 1 and 2 contain a complete explanation of the function of the different bits in Master Control Words 1 and 2.

### **Major Operating Modes**

The major operating modes of the device are enabled by bits 2 and 4 of Master Control Word 2. The Extended Superframe(ESF) mode is enabled when bit 4 is set high. Bit 2 has no effect in this mode. The ESF mode enables the transmission of the S bit pattern shown in Table 3. This includes the frame/superframe pattern, the CRC-6, and the Facility Data Link (FDL). The device generates the frame/multiframe pattern and calculates the CRC for each superframe. The data clocked into the device on the TxFDL pin is incorporated into the FDL. ESF mode will also insert A, B, C and D signalling bits into the 24 frame multiframe. The DS1 frame begins after approximately 25 periods of the C1.5i clock from the F0i frame pulse.

During synchronization the receiver locks to the incoming frame, calculates the CRC and compares it

| Bit | Name       | Description                                                                                                                                                                                                                                                        |

|-----|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | Debounce   | When set the received A, B, C and D signalling bits are reported directly in the per channel status words output at CSTo. When clear, the signalling bits are debounced for 6 to 9 ms before they are placed on CSTo.                                              |

| 6   | TSPZCS     | <b>Transparent Zero Code Suppression.</b> When this bit is set, no zero code suppression is implemented.                                                                                                                                                           |

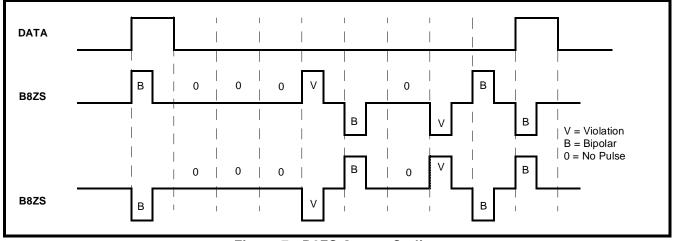

| 5   | B8ZS       | <b>Binary Eight Zero Suppression.</b> When this bit is set, B8ZS zero code suppression is enabled. When clear, bit 7 in data channels containing all zeros is forced high before being transmitted on the DS1 side. This bit is inactive if the TSPZCS bit is set. |

| 4   | 8KHSel     | <b>8 kHz Output Select.</b> When set, the E8Ko pin is held high. When clear, the E8Ko generates an 8 kHz output derived from the E1.5i or C1.5 clock (see Pin Description for E8Ko).                                                                               |

| 3   | XCtI       | External Control Pin. When set, the XCtl pin is held high. When clear, XCtl is held low.                                                                                                                                                                           |

| 2   | ESFYLW     | <b>ESF Yellow Alarm.</b> Valid only in ESF mode. When set, a sequence of eight 1's followed by eight 0's is sent in the FDL bit positions. When clear, the FDL bit contains data input at the TxFDL pin.                                                           |

| 1   | Robbed bit | When this bit is set, robbed bit signalling is disabled on all DS0 transmit channels. When clear, A, B, C and D signalling bit insertion in bit 8 for all DS0 transmit channels in every 6 <sup>th</sup> frame is enabled.                                         |

| 0   | YLALR      | <b>Yellow Alarm.</b> When set, bit 2 of all DS1 channels is set low. When clear, bit 2 operates normally.                                                                                                                                                          |

Table 1. Master Control Word 1 (Channel 15, CSTi0)

to the CRC received in the next multiframe. The device will not declare itself to be in synchronization unless a valid framing pattern in the S-bit is detected and a correct CRC is received. The CRC check in this case provides protection against false framing. The CRC check can be turned off by setting bit 1 in Master Control Word 2.

The device can be forced to resynchronize itself. If Bit 3 in Master Control Word 2 is set for one frame and then subsequently reset, the device will start to search for a new frame position. The decision to reframe is made by the user's system processor on the basis of the status conditions detected in the received master status words. This may include consideration of the number of errors in the received CRC in conjunction with an indication of the presence of a mimic. When the device attains synchronization the mimic bit in Master Status Word 1 is set if the device found another possible candidate when it was searching for the framing pattern.

Note that the device will resynchronize automatically if the errors in the terminal framing pattern ( $F_T$  or FPS) exceed the threshold set with bit 0 in Master Control Word 2.

Standard D3/D4 framing is enabled when bit 4 of Master Control Word 2 is reset (logic 0). In this mode the device searches for and inserts the framing pattern shown in Table 4. This mode only supports AB bit signalling, and does not contain a CRC check.

The CRC/MIMIC bit in Master Control Word 2, when set high, allows the device to synchronize in the presence of a mimic. If this bit is reset, the device will not synchronize in the presence of a mimic (Also, refer to section on Framing algorithm).

In the D3/D4 mode the device can also be made compatible with SLC-96 by setting bit two of Master Control Word 2. This allows the user to insert and extract the signalling framing pattern on the DS1 bit stream using the FDL input and output pins. The user must format this 4 kbits of information externally to meet all of the requirements of the SLC-96 specification (see Table 5). The device multiplexes and demultiplexes this information into the proper position. This mode of operation can also be used for any other application that uses all or part of the signalling framing pattern. As long as the serial stream clocked into the TxFDL contains two proper sets of consecutive synchronization bits (as shown in Table 5 for frames 1 to 24), the device will be able to insert and extract the A, B signalling bits. The TxSF pin should be held high in this mode. Superframe boundaries cannot be defined by a pulse on this input. The RXSF output functions normally and indicates the superframe boundaries based on the synchronization pattern in the FS received bit position.

### **Zero Code Suppression**

The combination of bits 5 and 6 in Master Control Word 1 allow one of three zero code suppression

| Bit | Name      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | RMLOOP    | <b>Remote Loopback.</b> When set, the data received at RxA and RxB is looped back to TxB and TxA respectively. The data is clocked into the device with E1.5i. The device still monitors the received data and outputs it at DSTo. The device operates normally when the bit is clear.                                                                                                                                                                                                                                                                      |

| 6   | DGLOOP    | <b>Digital Loopback.</b> When <u>set</u> , the <u>data</u> input on DSTi is looped around to DSTo. The normal received data on RxA, RxB and RxD is ignored. However, the data input at DSTi is still transmitted on TxA and TxB. The device frames up on the looped data using the C1.5i clock.                                                                                                                                                                                                                                                             |

| 5   | ALL1'S    | <b>All One's Alarm.</b> When set, the chip transmits an unframed all 1's signal on TxA and TxB.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 4   | ESF/D4    | <b>ESF/D4 Select.</b> When set, the device is in ESF mode. When clear, the device is in D3/D4 mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3   | ReFR      | <b>Reframe.</b> If set for at least one frame and then cleared, the chip will begin to search for a new frame position. Only the change from high to low will cause a reframe, not a continuous low level.                                                                                                                                                                                                                                                                                                                                                  |

| 2   | SLC-96    | <b>SLC-96 Mode Select.</b> The chip is in SLC-96 mode when this bit is set. This enables input and output of the $F_S$ bit pattern using the same pins as the facility data link in ESF mode. The chip will use the same framing algorithm as D3/D4 mode. The user must insert the valid $F_S$ bits in 2 out of 6 superframes to allow the receiver to find superframe sync, and the transmitter to insert A and B bits in every $6^{th}$ frame. The SLC-96 FDL completely replaces the $F_S$ pattern in the outgoing S bit position. Inactive in ESF mode. |

| 1   | CRC/MIMIC | In ESF mode, when set, the chip disregards the CRC calculation during synchronization. When clear, the device will check for a correct CRC before going into synchronization. In D3/D4 mode, when set, the device will synchronize on the first correct S-bit pattern detected. When this bit is clear, the device will not synchronize if it has detected more than one candidate for the frame alignment pattern (i.e., a mimic).                                                                                                                         |

| 0   | Maint.    | <b>Maintenance Mode.</b> When set, the device will declare itself out-of-sync if 4 out of 12 consecutive $F_T$ bits are in error. When clear, the out-of-sync threshold is 2 errors in 4 $F_T$ bits. In this mode, four consecutive bits following an errored $F_T$ bit are examined.                                                                                                                                                                                                                                                                       |

Table 2. Master Control Word 2 (Channel 31, CSTi0)

schemes to be selected. The three choices are: none, binary 8 zero suppression (B8ZS), or jammed bit (bit 7 forced high). No zero code suppression allows the device to interface with systems that have already applied some form of zero code suppression to the data input on DSTi. B8ZS zero code suppression replaces all strings of 8 zeros with a known bit pattern and a specific pattern of bipolar violations. This bit pattern and violation pattern is shown in Figure 7. The receiver monitors the received bit pattern and the bipolar violation pattern and replaces all matching strings with 8 zeros.

### **Loopback Modes**

Remote and digital loopback modes are enabled by bits 6 and 7 in Master Control Word 2. These modes can be used for diagnostics in locating the source of a fault condition. Remote loop around loops back data received at RxA and RxB back out on TxA and TxB, thus effectively sending the received DS1 data back to the far end unaltered so that the transmission line can be tested. The received signal is still monitored with the appropriate received channels on the DS1 side made available in the proper format at DSTo.

The digital loop around mode diverts the data received at DSTi back out the DSTo pin. Data received on DSTi is, however, still transmitted out via TxA and TxB. This loop back mode can be used to test the near end interface equipment when there is no transmission line or when there is a suspected failure of the line.

The all one's transmit alarm (also known as the blue alarm or the keep alive signal) can be activated in conjunction with the digital loop around so that the transmission line sends an all 1's signal while the normal data is looped back locally.

The MT8976 also has a per channel loopback mode. See Table 6 and the following section for more information.

### **Per Channel Control Features**

In addition to the two master control words in CSTi0 there are also 24 Per Channel Control Words. These control words only affect individual DS0 channels. The correspondence between the channels on CSTi0 and the affected DS0 channel is shown in Fig. 6.

| Frame # | FPS | FDL | CRC | Signalling <sup>†</sup> |

|---------|-----|-----|-----|-------------------------|

| 1       |     | X   |     |                         |

| 2       |     |     | CB1 |                         |

| 3       |     | Х   |     |                         |

| 4       | 0   |     |     |                         |

| 5       |     | Χ   |     |                         |

| 6       |     |     | CB2 | Α                       |

| 7       |     | Х   |     |                         |

| 8       | 0   |     |     |                         |

| 9       |     | Х   |     |                         |

| 10      |     |     | CB3 |                         |

| 11      |     | Х   |     |                         |

| 12      | 1   |     |     | В                       |

| 13      |     | Х   |     |                         |

| 14      |     |     | CB4 |                         |

| 15      |     | Х   |     |                         |

| 16      | 0   |     |     |                         |

| 17      |     | Х   |     |                         |

| 18      |     |     | CB5 | С                       |

| 19      |     | Х   |     |                         |

| 20      | 1   |     |     |                         |

| 21      |     | Х   |     |                         |

| 22      |     |     | CB6 |                         |

| 23      |     | Х   |     |                         |

| 24      | 1   |     |     | D                       |

Table 3. ESF Frame Pattern

† These signalling bits are only valid if the robbed bit signalling is active.

| Frame # | F <sub>T</sub> | F <sub>S</sub> | Signalling <sup>†</sup> |

|---------|----------------|----------------|-------------------------|

| 1       | 1              |                |                         |

| 2       |                | 0              |                         |

| 3       | 0              |                |                         |

| 4       |                | 0              |                         |

| 5       | 1              |                |                         |

| 6       |                | 1              | Α                       |

| 7       | 0              |                |                         |

| 8       |                | 1              |                         |

| 9       | 1              |                |                         |

| 10      |                | 1              |                         |

| 11      | 0              |                |                         |

| 12      |                | 0              | В                       |

Table 4. D3/D4 Framer

Each control word has three bits that enable robbed bit signalling, DS0 channel loopback and inversion of the DS0 channel. A full description of each of the bits is provided in Table 6.

### **Transmit Signalling Bits**

Control ST-BUS input number 1 (CSTi1) contains 24 additional per channel control words. These 24 ST-BUS channels contain the A, B, C and D signalling bits that the device uses at transmit time. The position of these 24 per channel control words in the ST-BUS is shown in Figure 6 and the position of the ABCD signalling bits is shown in Table 7. Even

though the device only inserts the signalling information in every 6th DS1 frame this information must be input every ST-BUS frame.

Robbed bit signalling can be disabled for all channels on the DS1 link by bit 1 of Master Control Word 1. It can also be disabled on a per channel basis by bit 0 in the Per Channel Control Word 1.

### **Operating Status Information**

Status Information regarding the operation of the device is output serially via the Control ST-BUS output (CSTo). The CSTo serial stream contains Master Status Words 1 and 2, 24 Per Channel Status Words, and a Phase Status Word. The Master Status Words contain all of the information needed to determine the state of the interface and how well it is operating. The information provided includes frame and super frame synchronization, slip, bipolar violation counter, alarms, CRC error count,  $F_T$  error count, synchronization pattern mimic and a phase status word. Tables 8 and 9 give a description of each of the bits in Master Status Words 1 and 2, and Table 10 gives a description of the Phase Status Word.

### **Alarm Detection**

The device detects the yellow alarm for both D3/D4 frame format and ESF format. The D3/D4 yellow alarm will be activated if a '0' is received in bit position 2 of every DS0 channel for 600 msec. It will be released in 200 msec after the contents of the bit change. The alarm is detectable in the presence of errors on the line. The ESF yellow alarm will become active when the device has detected a string of eight 0's followed by eight 1's in the facility data link. It is not detectable in the presence of errors on the line. This means that the ESF yellow alarm will drop out for relatively short periods of time, so the system will have to integrate the ESF yellow alarm. The blue alarm signal, in Master Status Word 2, will also drop out if there are errors on the line.

### **Mimic Detection**

The mimic bit in Master Status Word 1 will be set if, during synchronization, a frame alignment pattern ( $F_T$  or FPS bit pattern) was observed in more than one position, i.e., if more than one candidate for the frame synchronization position was observed. It will be reset when the device resynchronizes. The mimic bit, the terminal framing error bit and the CRC error counter can be used separately or together to decide if the receiver should be forced to reframe.

<sup>†</sup> These signalling bits are only valid if the robbed bit signalling is active.

| Frame<br># | F <sub>T</sub> | F <sub>S</sub> † | Notes             | Frame<br># | F <sub>T</sub> | F <sub>S</sub> † | Notes            |

|------------|----------------|------------------|-------------------|------------|----------------|------------------|------------------|

| 1          | 1              |                  |                   | 37         | 1              |                  |                  |

| 2          |                | 0                |                   | 38         |                | Х                |                  |

| 3          | 0              |                  |                   | 39         | 0              |                  |                  |

| 4          |                | 0                |                   | 40         |                | Х                |                  |

| 5          | 1              |                  |                   | 41         | 1              |                  | X = Concentrator |

| 6          |                | 0                |                   | 42         |                | Χ                | Field Bits       |

| 7          | 0              |                  |                   | 43         | 0              |                  |                  |

| 8          |                | 1                |                   | 44         |                | Χ                |                  |

| 9          | 1              |                  |                   | 45         | 1              |                  |                  |

| 10         |                | 1                |                   | 46         |                | Х                |                  |

| 11         | 0              |                  | Resynchronization | 47         | 0              |                  |                  |

| 12         |                | 1                | Data              | 48         |                | S                |                  |

| 13         | 1              |                  | Bits              | 49         | 1              |                  |                  |

| 14         |                | 0                | Dits              | 50         |                | S                | S = Spoiler Bits |

| 15         | 0              |                  |                   | 51         | 0              |                  |                  |

| 16         |                | 0                |                   | 52         |                | S                |                  |

| 17         | 1              |                  |                   | 53         | 1              |                  |                  |

| 18         |                | 0                |                   | 54         |                | С                |                  |

| 19         | 0              |                  |                   | 55         | 0              |                  | C = Maintenance  |

| 20         |                | 1                |                   | 56         |                | С                | Field            |

| 21         | 1              |                  |                   | 57         | 1              |                  | Bits             |

| 22         |                | 1                |                   | 58         |                | С                |                  |

| 23         | 0              |                  |                   | 59         | 0              |                  |                  |

| 24         |                | 1                |                   | 60         |                | Α                | A = Alarm Field  |

| 25         | 1              |                  |                   | 61         | 1              |                  | Bits             |

| 26         |                | Х                |                   | 62         |                | Α                |                  |

| 27         | 0              |                  |                   | 63         | 0              |                  |                  |

| 28         |                | Х                |                   | 64         |                | L                |                  |

| 29         | 1              |                  |                   | 65         | 1              |                  |                  |

| 30         |                | Х                | X = Concentrator  | 66         |                | L                | L = Line Switch  |

| 31         | 0              |                  | Field Bits        | 67         | 0              |                  | Field Bits       |

| 32         |                | Х                |                   | 68         |                | L                |                  |

| 33         | 1              |                  |                   | 69         | 1              |                  |                  |

| 34         |                | Х                |                   | 70         |                | L                |                  |

| 35         | 0              |                  |                   | 71         | 0              |                  | S = Spoiler Bits |

| 36         |                | Χ                |                   | 72         |                | S                | 3 = Spoiler Dits |

Table 5. SLC-96 Framing Pattern

<sup>†</sup> Note: The F<sub>S</sub> pattern has to be supplied by the user.

Figure 7 - B8ZS Output Coding

### **Bipolar Violation Counter**

The Bipolar Violation bit in Master Status Word 1 will toggle after 256 violations have been detected in the received signal. It has a maximum refresh time of 96 ms. This means that the bit can not change state faster than once every 96 ms. For example, if there are 256 violations in 80 ms the BPV bit will not change state until 96 ms. Any more errors in that extra 16 ms are not counted. If there are 256 errors in 200 ms then the BPV bit will change state after 200 ms. In practical terms this puts an upper limit on the error rate that can be calculated from the BPV information, but this rate (1.7 X 10<sup>-3</sup>) is well above any normal operating condition.

Bits 4 and 3 also provide bipolar violations information. Bit 4 will change state after 128 violations. Bit 3 changes state after 64 bipolar violations. These bits are refreshed independently and are not subject to the 96ms refresh rate described above.

### **DS1/ST-BUS Phase Difference**

An indication of the phase difference between the ST-BUS and the DS1 frame can be ascertained from the information provided by the eight bit Phase Status Word and the Frame Count bit. Channel three on CSTo contains the Phase Status Word. Bits 7-3 in this word indicate the number of ST-BUS channels between the ST-BUS frame pulse and the rising edge of the E8Ko signal. The remaining three bits provide one bit resolution within the channel count indicated by bits 7-3. The frame count bit in Master Status Word 2 is the ninth and most significant bit of the phase status word. It will toggle

when the phase status word increments above channel 31, bit 7 or decrements below channel 0, bit 0. The E8Ko signal has a specific relationship with received DS1 frame. The rising edge of E8Ko occurs during bit 2, channel 17 of the received DS1 frame. The Phase Status Word in conjunction with the frame count bit, can be used to monitor the phase relationship between the received DS1 frame and the local ST-BUS frame.

The local 2.048 MHz ST-BUS clock must be phase-locked to the 1.544 MHz clock extracted from the received data. When the two clocks are not phase-locked, the input data rate on the DS1 side will differ from the output data rate on the ST-BUS side. If the average input data rate is higher than the average output data rate, the channel count and bit count in the phase status word will be seen to decrease over time, indicating that the E8Ko rising edge, and therefore, the DS1 frame boundary is moving with respect to the ST-BUS frame pulse. Conversely, a lower average input data rate will result in an increase in the phase reading.

In an application where it is necessary to minimize jitter transfer from the received clock to the local system clock, a phase lock loop with a relatively large time constant can be implemented using information provided by the phase status word. In such a system, the local 2.048 MHz clock is derived from a precision VCO. Frequency corrections are made on the basis of the average trend observed in the phase status word. For example, if the channel count in the phase status word is seen to increase over time, the feedback applied to the VCO is used to decrease the system clock frequency until a reversal in the trend is observed.

| Bit | Name     | Description                                                                                                                                                                                                                                                                                 |

|-----|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-3 | IC       | Internal Connections. Must be kept at 0 for normal operation                                                                                                                                                                                                                                |

| 2   | Polarity | When set, the applicable channel is not inverted on the transmit or the receive side of the device. When clear, all the bits within the applicable channel are inverted both on transmit and receive side.                                                                                  |

| 1   | Loop     | Per Channel Loopback. When set, the received DS0 channel is replaced with the transmitted DS0 channel. Only one DS0 channel may be looped back in this manner at a time. The transmitted DS0 channel remains unaffected. When clear the transmit and receive DS0 sections operate normally. |

| 0   | Data     | <b>Data Channel Enable.</b> When set, robbed bit signalling for the applicable channel is disabled. When clear, every 6th DS1 frame is available for robbed bit signalling. This feature is enabled only if bit 1 in Master Control Word is low.                                            |

Table 6. Per Channel Control Word 1 Input at CSTi0

| Bit | Name   | Description                                                                                                                                                                             |

|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-4 | Unused | Keep at 0 for normal operation                                                                                                                                                          |

| 3 2 | A<br>B | These are the 4 signalling bits inserted in the appropriate channels of the DS1 stream being output from the chip, when in ESF mode. In D3/D4 modes where there are only two signalling |

| 1-0 | C, D   | bits, the values of C and D are ignored.                                                                                                                                                |

Table 7. Per Channel Control Word 2 Input at CSTi1

| Bit | Name   | Description                                                                                                                                                                                              |

|-----|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | YLALR  | <b>Yellow Alarm Indication.</b> This bit is set when the chip is receiving a 0 in bit position 2 of every DS0 channel.                                                                                   |

| 6   | MIMIC  | This bit is set if the frame search algorithm found more than one possible frame candidate when it went into frame synchronization.                                                                      |

| 5   | ERR    | <b>Terminal Framing Bit Error.</b> The state of this bit changes every time the chip detects 4 errors in the F <sub>T</sub> or FPS bit pattern. The bit will not change state more than once every 96ms. |

| 4   | ESFYLW | <b>ESF Yellow Alarm.</b> This bit is set when the device has observed a sequence of eight one's and eight 0's in the FDL bit positions.                                                                  |

| 3   | MFSYNC | <b>Multiframe Synchronization.</b> This bit is cleared when D3/D4 multiframe synchronization has been achieved. Applicable only in D3/D4 and SLC-96 modes.                                               |

| 2   | BPV    | <b>Bipolar Violation Count.</b> The state of this bit changes every time the device counts 256 bipolar violations.                                                                                       |

| 1   | SLIP   | Slip Indication. This bit changes state every time the elastic buffer in the device performs a controlled slip.                                                                                          |

| 0   | SYN    | <b>Synchronization.</b> This bit is set when the device has not achieved synchronization. The bit is clear when the device has synchronized to the received DS1 data stream.                             |

Table 8. Master Status Word 1 (Channel 15, CSTo)

| Bit | Name   | Description                                                                                                                                                                                                                                                                                                                           |

|-----|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | BIAIm  | <b>Blue Alarm.</b> This bit is set if the receiver has detected two frames of 1's and an out of frame condition. It is reset by any 250 microsecond interval that contains a zero.                                                                                                                                                    |

| 6   | FrCnt  | <b>Frame Count.</b> This is the ninth and most significant bit of the "Phase Status Word" (see Table 10). If the phase status word is incrementing, this bit will toggle when the phase reading exceeds channel 31, bit 7. If the phase word is decrementing, then this bit will toggle when the reading goes below channel 0, bit 0. |

| 5   | XSt    | <b>External Status.</b> This bit reflects the state of the external status pin (XSt). The state of the XSt pin is sampled once per frame.                                                                                                                                                                                             |

| 4-3 | BPVCnt | <b>Bipolar Violation Count.</b> These two bits change state every 128 and every 64 bipolar violations respectively.                                                                                                                                                                                                                   |

| 2-0 | CRCCNT | <b>CRC Error Count.</b> These three bits count received CRC errors. The counter will reset to zero when it reaches terminal count. Valid only in ESF mode.                                                                                                                                                                            |

Table 9. Master Status Word 2 (Channel 31, CSTo)

| Bit | Name       | Description                                                                                                                         |  |  |  |  |  |  |  |

|-----|------------|-------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 7-3 | ChannelCnt | <b>Channel Count.</b> These five bits indicate the ST-BUS channel count between the ST-BUS frame pulse and the rising edge of E8Ko. |  |  |  |  |  |  |  |

| 2-0 | BitCnt     | Bit Count. These three bits provide one bit resolution within the channel count described above.                                    |  |  |  |  |  |  |  |

Table 10. Phase Status Word (Channel 3, CSTo)

| Bit | Name   | Description                                                                                         |  |  |  |  |  |  |

|-----|--------|-----------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 7-4 | Unused | Unused Bits. Will be output as 0's.                                                                 |  |  |  |  |  |  |

| 3   | Α      | These are the 4 signalling bits as extracted from the received DS1 bit stream.                      |  |  |  |  |  |  |

| 2   | В      | The bits are debounced for 6 to 9 ms if the debounce feature is enabled via bit 7 in Master Control |  |  |  |  |  |  |

| 1   | С      | Word 1.                                                                                             |  |  |  |  |  |  |

| 0   | D      |                                                                                                     |  |  |  |  |  |  |

Table 11. Per Channel Status Word Output on CSTo

The elastic buffer in the MT8976 permits the device to handle eight channels of jitter/wander (see description of elastic buffer in the next section). In order to prevent slips from occurring, the frequency corrections would have to be implemented such that the deviation in the phase status word is limited to eight channels peak to peak. It is possible to use a

more sophisticated protocol, which would center the elastic buffer and permit more jitter/wander to be handled. However, for most applications, the eight channels of jitter/wander tolerance is acceptable.

### **Received Signalling Bits**

The A, B, C and D signalling bits are output from the device in the 24 Per Channel Status Words. Their location in the serial steam output at CSTo is shown in Figure 6 and the bit positions are shown in Table 11. The internal debouncing of the signalling bits can be turned on or off by Master Control Word 1. In ESF mode, A, B, C and D bits are valid. Even though the signalling bits are only received once every six frames the device stores the information so that it is available on the ST-BUS every frame. The ST-BUS will always contain the most recent signalling bits. The state of the signalling bits is frozen if synchronization is lost.

In D3/D4 mode, only the A and B bits are valid. The state of the signalling bits is frozen when terminal frame synchronization is lost. The freeze is disabled when the device regains terminal frame synchronization. The signalling bits may go through a random transition stage until the device attains multiframe synchronization.

### Clock and Framing Signals

The MT8976 requires one 2.048 MHz clock (C2i) and an 8 kHz framing signal for the ST-BUS side. Figure 12 illustrates the relationship between the two signals. The framing signal is used to delimit individual 32 channel ST-BUS frames.

The DS1 side requires two clocks. A 1.544 MHz clock used for transmit (C1.5i), and a 1.544 MHz clock extracted from the DS1 line signal and applied at E1.5i pin to clock in the received data.

The C2i and C1.5i clock must be phase-locked together. There must be 193 clock cycles of C1.5i for every 256 clock cycles of C2i. At the slave end of the link, the C2i and C1.5i must be phase locked to the extracted E1.5i clock.

The clock applied at E1.5i is internally divided down by 193 and aligned with the DS1 frame. The resulting 8 kHz clock is output at the E8Ko pin. This signal can be used as a reference for phase locking the C2i and C1.5i clocks to the extracted 1.544 MHz clock.

### **DS1** Line Interface

### **Transmit Interface**

The interface to the DS1 line is made up of two unipolar outputs, TxA and TxB, which can be used to drive a bipolar transmitter circuit. The output signal

on TxA and TxB corresponds to the positive and negative bipolar pulses required for the Alternate Mark Inversion signal on the T1 line. The relationship between the signal output at TxA and TxB and the AMI signal is illustrated in Figure 5. For transmission over twisted pair wire, the AMI signal has to be equalized and transformer coupled to the line.

### **Receiver Interface**

The receiver circuitry is made up of three pins RxA, RxB and RxD. The bipolar alternate mark inversion signal from the DS-1 line should be converted into a unipolar split phase format. The resulting signals are clocked into the device at RxA and RxB. The signals are also NANDED together and input at RxD.

In special applications where the detection of bipolar violations is not required, it is possible to clock NRZ data directly into RxD. In this case, the RxA and RxB pins should be tied high.

Data is clocked into RxA, RxB and RxD with the falling edge of the E1.5i clock. This clock signal is extracted from the received data. The relationship between the received signals and the extracted clock is shown in Figure 4.

### **Elastic Buffer**

The MT8976 has a two frame elastic buffer which absorbs jitter in the received DS1 signal. The buffer is also used in the rate conversion between the 1.544 Mbit/s DS1 rate and the 2.048 Mbit/s ST-BUS data rate.

The received data is written into the elastic buffer with the extracted 1.544 MHz clock. The data is read out of the buffer on the ST-BUS side with the system 2.048 MHz clock. The maximum delay through the buffer is 1.3 ST-BUS frames (i.e., 42 ST-BUS channels). The minimum delay required to avoid bus contention in the buffer memory is two ST-BUS channels.

Under normal operating conditions, the system C2i clock is phase locked to the extracted E1.5i clock using external circuitry. If the two clocks are not phase-locked, then the rate at which the data is being written into the device on the DS1 side may differ from the rate at which it is being read out on the ST-BUS side. The buffer circuit will perform a controlled slip if the throughput delay conditions described above are violated. For example, if the data on the DS1 side is being written in at a rate slower than what it is being read out on the ST-BUS side, the delay between the received DS1 write

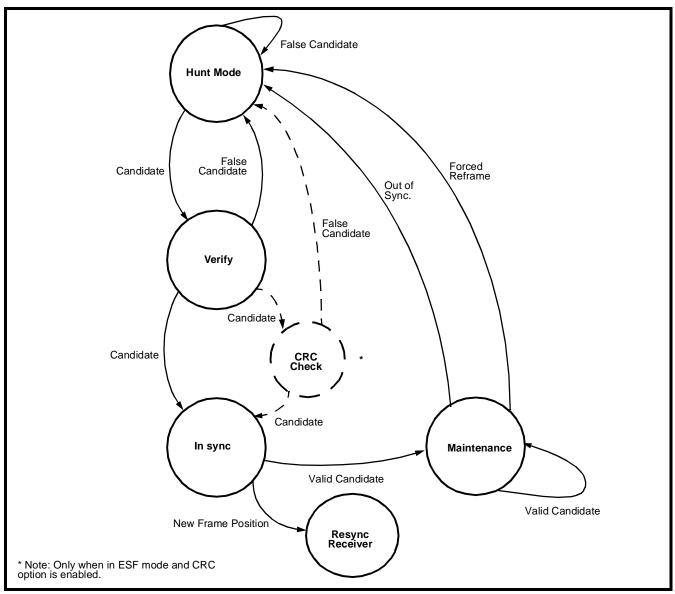

Figure 8 - Off-Line Framer State Diagram

pointer and the ST-BUS read pointer will begin to decrease over time. When this delay approaches the minimum two channel threshold, the buffer will perform a controlled slip, which will reset the internal ST-BUS read pointers so that there is exactly 34 channels delay between the two pointers. This will result in some ST-BUS channels containing information output in the previous frame. Repetition of up to one DS1 frame of information is possible.

Conversely, if the data on the DS1 side is being written into the buffer at a rate faster than that at which it is being read out on the ST-BUS side, the delay between the DS1 frame and the ST-BUS frame will increase over time. A controlled slip will be performed when the throughput delay exceeds 42 ST-BUS channels. This slip will reset the internal ST-BUS counters so that there is a 10 channel delay between the DS1 write pointer and the ST-BUS read

pointer, resulting in loss of up to one frame of received DS1 data.

Note that when the device performs a controlled slip, the ST-BUS address pointers are repositioned so that there is either a 10 channel or a 34 channel delay between the input DS1 frame and the output ST-BUS frame. Since the buffer performs a controlled slip only if the delay exceeds 42 channels or is less than 2 channels, there is an 8 channel hysteresis built into the slip mechanism. The device can, therefore, absorb 8 channels or 32.5µs of jitter in the received signal.

There is no loss of frame sync, multiframe sync or any errors in the signalling bits when the device performs a slip. The information on the FDL pins in ESF or SLC-96 mode will, however, undergo slips at the same time.

### Framing Algorithm

In ESF mode, the framer searches for a correct FPS pattern. Figure 8 shows a state diagram of the framing algorithm. The dotted lines show which feature can be switched in and out depending upon the operating mode of the device.

When the device is operating in the D3/D4 format, the framer searches for the F<sub>T</sub> pattern, i.e., a repeating 1010... pattern in a specific bit position every alternate frame. It will synchronize to this pattern and declare valid terminal synchronization by clearing bit 0 in Master Status Word 1. The device will subsequently initiate a search for the F<sub>S</sub> pattern to locate the signalling frames (see Table 4). When a correct F<sub>S</sub> pattern has been located, bit 3 in Master Status Word 1 is cleared indicating that the device has achieved multiframe synchronization.

Note: the device will remain in terminal frame synchronization even if no F<sub>S</sub> pattern can be located.

In D3/D4 format, when the CRC/MIMIC bit in Master Control Word 1 is cleared, the device will not go into synchronization if more than one bit position in the frame has a repeating 1010.... pattern, i.e., if more than one candidate for the terminal framing position is located. The framer will continue to search until only one terminal framing pattern candidate is discovered. It is, therefore, possible that the device may not synchronize at all in the presence of PCM code sequences (e.g., sequences generated by some types of test signals), which contain mimics of the terminal framing pattern.

Setting CRC/MIMIC bit high will force the framer to synchronize to the first terminal framing pattern detected. In standard D3/D4 applications, the user's system software should monitor the multiframe synchronization state indicated by bit 3 in Master Status Word 1. Failure of the device to achieve multiframe synchronization within 4.5ms of terminal frame synchronization, is an indication that the device has framed up to a terminal framing pattern mimic and should be forced to reframe.

One of the main features of the framer is that it performs its function "off line". That is, the framer repositions the receive circuit only when it has detected a valid frame position. When the framer exits maintenance mode the receive counters remain where they are until the framer has found a new frame position. This means that if the user forces a reframe when the device was really in the right place, there will not be any disturbance in the circuit

because the framer has no effect on the receiver until it has found synchronization. The out of synchronization criterion can be controlled by bit 0 in Master Control Word 2. This bit changes the out of frame conditions for the maintenance state.

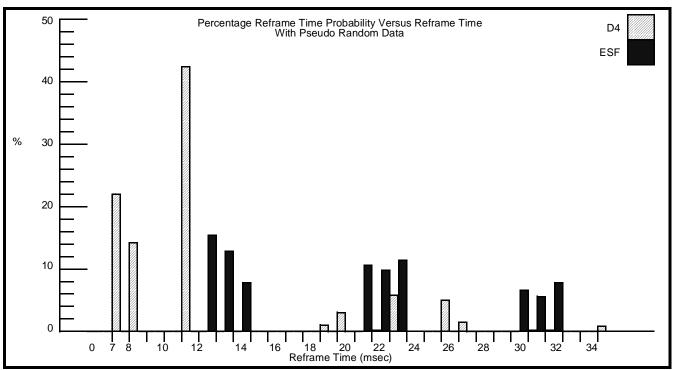

The out of sync threshhold can be changed from 2 out of 4 errors in  $F_T$  (or FPS) to 4 out of 12 errors in  $F_T$  (or FPS). The average reframe time is 24 ms for ESF mode, and 12ms for D3/D4 modes.

Figure 9 is a bar graph which shows the probability of achieving frame synchronization at a specific time. The chart shows the results for ESF mode with CRC check, and D3/D4 modes of operation. The average reframe time with random data is 24 ms for ESF, and 13 msec. D3/D4 modes. The probability of a reframe time of 35 ms or less is 88% for ESF mode, and 97% for D3/D4 modes. In ESF mode it is recommended that the CRC check be enabled unless the line has a high error rate. With the CRC check disabled the average reframe time is greater because the framer must also check for mimics.

### **Applications**

Figure 10 shows the external components that are required in a typical ESF application. The MT8980 is used to control and monitor the device as well as switch data to DSTi and DSTo. The MT8952, the HDLC protocol controller, is shown in this application to illustrate how the data on the FDL could be used. The digital phase-locked loop, the MT8940/41, provides all the clocks necessary to make a functional interface. The clock input to the MT8976 at E1.5i is extracted from the received data signal with an external circuit. The E1.5i clock is internally divided by 193 to obtain an 8 kHz clock, which is output at E8Ko. The MT8940/41 uses this 8 kHz signal to provide a phase locked 2.048 MHz clock for the ST-BUS interface and a 1.544 MHz clock for the DS1 transmit side. Using the 8 kHz signal as a reference for the MT8940/41 DPLL effectively filters out the high frequency jitter in the extracted clock. Thus the C2 and C1.5 clocks generated by the MT8940/41 will have significantly lower jitter than would be the case if the extracted 1.5 MHz clock was used as a reference directly.

An external line driver circuit is required in order to interface the device to twisted pair cabling. The split phase unipolar signals output by the MT8976 at TxA and TxB are used by the line driver circuit to generate a bipolar AMI signal. The line driver is transformer coupled to an equalization circuit and the DS1 line. Equalization of the transmitted signal is required to meet the specifications for crossconnect

Figure 9 - Reframe Time

Figure 10 - Typical ESF Configuration

compatible equipment (see ANSI T1.102 and AT & T Technical Advisory #34). On the receive side the bipolar line signal is converted into a unipolar format by the line receiver circuit. The resulting split phase signals are input at the RxA and RxB pins on the MT8976. The signals are combined together to produce a composite return to zero signal, which is clocked into the device at RxD. An uncommitted nand gate in the MT8940/41 can be used for this purpose.

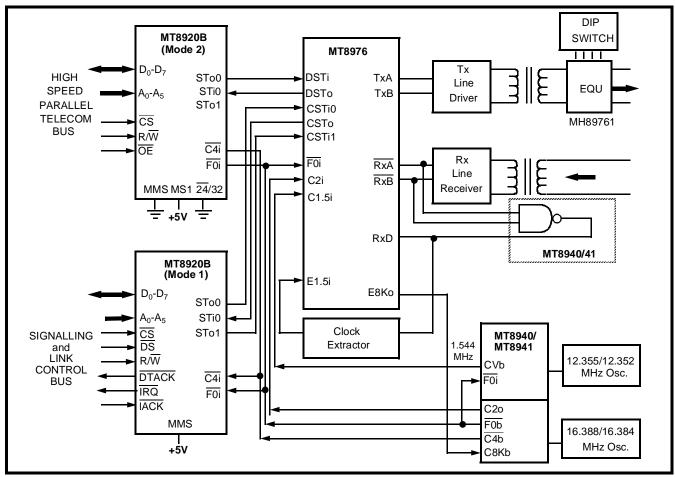

The MT8976 can be interfaced to a high speed parallel bus or to a microprocessor using the MT8920B Parallel Access Circuit (STPA). Figure 11 shows the MT8976 interfaced to a parallel bus structure using two STPA's operating in modes 1 and 2.

The first STPA operating in mode 2 (MMS=0, MS1=1, 24/32=0), routes data and/or voice information between the parallel telecom bus and the T1 or CEPT link via DSTi and DSTo. The second STPA, operating in mode 1 (MMS = 1 ) provides access from the signalling and link control bus to the MT8976 status and control channels. All signalling and link functions may be controlled easily through

the STPA transmit RAM's Tx0, Tx1, while status information is read at receive RAM Rx0. In addition, interrupts can be set up to notify the system in case of slips, loss of sync, alarms, violations, etc.

Mitel also manufactures a thick film hybrid device, the MH89760/760B, which incorporates the line driver, receiver and clock extractor circuitry. A second SIP hybrid, the MH89761, provides the necessary equalization circuitry to condition the signal for transmission up to 655 feet over 22 AWG twisted pair.

Note: the configurations shown in Figures 10 and 11 using the MT8940/41 may not meet specific jitter performance requirements. A more sophisticated PLL or line interface unit with transmit jitter attenuator may be required for applications designed to meet specific standards.

Figure 11 - Using the MT8976 in a Parallel Bus Environment

### **Absolute Maximum Ratings\***

|   | Parameter                                      | Symbol          | Min                  | Max                  | Units |

|---|------------------------------------------------|-----------------|----------------------|----------------------|-------|

| 1 | Power Supplies with respect to V <sub>SS</sub> | $V_{DD}$        | -0.3                 | 7                    | V     |

| 2 | Voltage on any pin other than supplies         |                 | V <sub>SS</sub> -0.3 | V <sub>DD</sub> +0.3 | V     |

| 3 | Current at any pin other than supplies         |                 |                      | 40                   | mA    |

| 4 | Storage Temperature                            | T <sub>ST</sub> | -55                  | 125                  | °C    |

| 5 | Package Power Dissipation                      | Р               |                      | 800                  | mW    |