# 1K x 8 Dual-Port Static RAM

### **Features**

- · True Dual-Ported memory cells which allow simultaneous reads of the same memory location

- 1K x 8 organization

- 0.65-micron CMOS for optimum speed/power

- High-speed access: 15 ns

- Low operating power: I<sub>CC</sub> = 110 mA (max.)

- Fully asynchronous operation

- · Automatic power-down

- Master CY7C130/CY7C131 easily expands data bus width to 16 or more bits using slave CY7C140/CY7C141

- BUSY output flag on CY7C130/CY7C131; BUSY input on CY7C140/CY7C141

- · INT flag for port-to-port communication

- Available in 48-pin DIP (CY7C130/140), 52-pin PLCC, 52-Pin TQFP.

- · Pb-Free packages available

### **Functional Description**

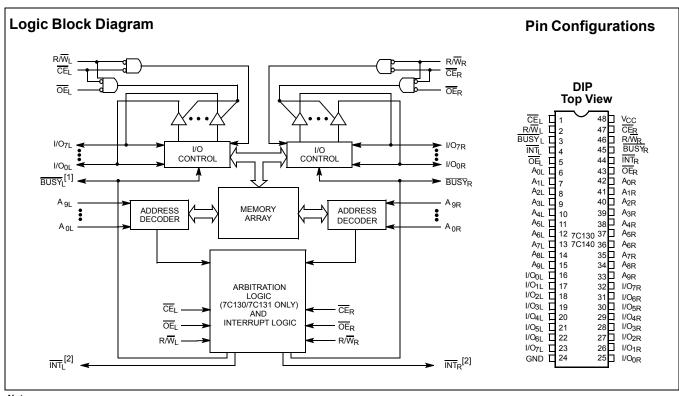

The CY7C130/CY7C131/CY7C140 and CY7C141 are high-speed CMOS 1K by 8 dual-port static RAMs. Two ports are provided permitting independent access to any location in memory. The CY7C130/ CY7C131 can be utilized as either a standalone 8-bit dual-port static RAM or as a master dual-port RAM in conjunction with the CY7C140/CY7C141 slave dual-port device in systems requiring 16-bit or greater word widths. It is the solution to applications requiring shared or buffered data, such as cache memory for DSP, bit-slice, or multiprocessor designs.

Each port has independent control pins; chip enable  $(\overline{CE})$ , write enable  $(R/\overline{W})$ , and output enable  $(\overline{OE})$ . Two flags are provided on each port, BUSY and INT. BUSY signals that the port is trying to access the same location currently being accessed by the other port. INT is an interrupt flag indicating that data has been placed in a unique location (3FF for the left port and 3FE for the right port). An automatic power-down feature is controlled independently on each port by the chip enable (CE) pins.

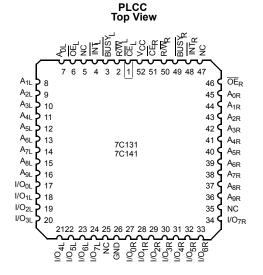

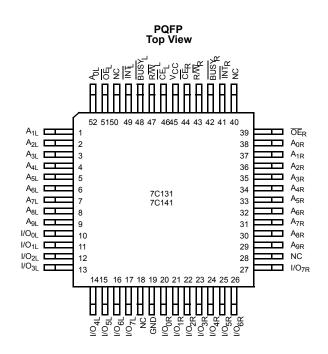

The CY7C130 and CY7C140 are available in 48-pin DIP. The CY7C131 and CY7C141 are available in 52-pin PLCC, 52-pin Pb-free PLCC, 52-pin PQFP and 52-pin Pb-free PQFP.

- CY7C130/CY7C131 (Master): <u>BUSY</u> is open drain output and requires pull-up resistor CY7C140/CY7C141 (Slave): BUSY is input.

- 2. Open drain outputs: pull-up resistor required.

### Pin Configuration (continued)

### **Pin Definitions**

| Left Port                                | Right Port                               | Description           |

|------------------------------------------|------------------------------------------|-----------------------|

| CEL                                      | CE <sub>R</sub>                          | Chip Enable           |

| $R/\overline{W}_L$                       | R/W <sub>R</sub>                         | Read/Write Enable     |

| ŌĒL                                      | ŌĒ <sub>R</sub>                          | Output Enable         |

| A <sub>0L</sub> -A <sub>11/12L</sub>     | A <sub>0R</sub> -A <sub>11/12R</sub>     | Address               |

| I/O <sub>0L</sub> –I/O <sub>15/17L</sub> | I/O <sub>0R</sub> -I/O <sub>15/17R</sub> | Data Bus Input/Output |

| ĪNT <sub>L</sub>                         | ĪNT <sub>R</sub>                         | Interrupt Flag        |

| BUSYL                                    | BUSY <sub>R</sub>                        | Busy Flag             |

| V <sub>CC</sub>                          |                                          | Power                 |

| GND                                      |                                          | Ground                |

### **Selection Guide**

|                     |           | 7C131-15 <sup>[3]</sup><br>7C141-15 | 7C131-25 <sup>[3]</sup><br>7C141-25 | 7C130-30<br>7C131-30<br>7C140-30<br>7C141-30 | 7C130-35<br>7C131-35<br>7C140-35<br>7C141-35 | 7C130-45<br>7C131-45<br>7C140-45<br>7C141-45 | 7C130-55<br>7C131-55<br>7C140-55<br>7C141-55 | Unit |

|---------------------|-----------|-------------------------------------|-------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|------|

| Maximum Access Time |           | 15                                  | 25                                  | 30                                           | 35                                           | 45                                           | 55                                           | ns   |

| Maximum Operating   | Com'l/Ind | 190                                 | 170                                 | 170                                          | 120                                          | 120                                          | 110                                          | mA   |

| Current             | Military  |                                     |                                     |                                              | 170                                          | 170                                          | 120                                          |      |

| Maximum Standby     | Com'l/Ind | 75                                  | 65                                  | 65                                           | 45                                           | 45                                           | 35                                           | mA   |

| Current             | Military  |                                     |                                     |                                              | 65                                           | 65                                           | 45                                           |      |

Shaded areas contain preliminary information.

### Note

3. 15 and 25-ns version available only in PLCC/PQFP packages.

### Maximum Ratings<sup>[4]</sup>

| Static Discharge Voltage       | . >2001V |

|--------------------------------|----------|

| (per MIL-STD-883, Method 3015) |          |

| Latch-Up Current               | >200 mA  |

### **Operating Range**

| Range                   | Ambient<br>Temperature | V <sub>cc</sub> |

|-------------------------|------------------------|-----------------|

| Commercial              | 0°C to +70°C           | 5V ± 10%        |

| Industrial              | –40°C to +85°C         | 5V ± 10%        |

| Military <sup>[5]</sup> | –55°C to +125°C        | 5V ± 10%        |

### Electrical Characteristics Over the Operating Range<sup>[6]</sup>

|                  |                                                   |                                                                                     |        | 7C130-30 <sup>[3]</sup> 7C131-25,30 7C131-15 <sup>[3]</sup> 7C140-30 7C141-25,30 |      | 7C130-35,45<br>7C131-35,45<br>7C140-35,45<br>7C141-35,45 |      | 7C131-55   |      |            |      |      |

|------------------|---------------------------------------------------|-------------------------------------------------------------------------------------|--------|----------------------------------------------------------------------------------|------|----------------------------------------------------------|------|------------|------|------------|------|------|

| Parameter        | Description                                       | Test Condition                                                                      | ns     | Min.                                                                             | Max. | Min.                                                     | Max. | Min.       | Max. | Min.       | Max. | Unit |

| V <sub>OH</sub>  | Output HIGH<br>Voltage                            | V <sub>CC</sub> = Min., I <sub>OH</sub> = -                                         | 4.0 mA | 2.4                                                                              |      | 2.4                                                      |      | 2.4        |      | 2.4        |      | V    |

| V <sub>OL</sub>  | Output LOW                                        | I <sub>OL</sub> = 4.0 mA                                                            |        |                                                                                  | 0.4  |                                                          | 0.4  |            | 0.4  |            | 0.4  | V    |

|                  | Voltage                                           | I <sub>OL</sub> = 16.0 mA <sup>[7]</sup>                                            |        |                                                                                  | 0.5  |                                                          | 0.5  |            | 0.5  |            | 0.5  |      |

| V <sub>IH</sub>  | Input HIGH Voltage                                |                                                                                     |        | 2.2                                                                              |      | 2.2                                                      |      | 2.2        |      | 2.2        |      | V    |

| V <sub>IL</sub>  | Input LOW Voltage                                 |                                                                                     |        |                                                                                  | 0.8  |                                                          | 8.0  |            | 8.0  |            | 0.8  | V    |

| I <sub>IX</sub>  | Input Leakage<br>Current                          | $GND \leq V_I \leq V_CC$                                                            |        | <b>–</b> 5                                                                       | +5   | <b>–</b> 5                                               | +5   | <b>–</b> 5 | +5   | <b>–</b> 5 | +5   | μА   |

| I <sub>OZ</sub>  | Output Leakage<br>Current                         | GND ≤ V <sub>O</sub> ≤ V <sub>CC</sub> ,<br>Output Disabled                         |        | <b>–</b> 5                                                                       | +5   | <b>-</b> 5                                               | +5   | <b>–</b> 5 | +5   | <b>-</b> 5 | +5   | μА   |

| I <sub>OS</sub>  | Output Short<br>Circuit Current <sup>[8, 9]</sup> | V <sub>CC</sub> = Max.,<br>V <sub>OUT</sub> = GND                                   |        |                                                                                  | -350 |                                                          | -350 |            | -350 |            | -350 | mA   |

| I <sub>CC</sub>  | V <sub>CC</sub> Operating                         | CE = V <sub>II</sub> ,                                                              | Com'l  |                                                                                  | 190  |                                                          | 170  |            | 120  |            | 110  | mA   |

|                  | Supply Current                                    | Outputs Open,<br>f = f <sub>MAX</sub> <sup>[10]</sup>                               | Mil    |                                                                                  |      |                                                          |      |            | 170  |            | 120  |      |

| I <sub>SB1</sub> | Standby Current                                   | CE <sub>L</sub> and CE <sub>B</sub> >                                               | Com'l  |                                                                                  | 75   |                                                          | 65   |            | 45   |            | 35   | mA   |

|                  | Both Ports,<br>TTL Inputs                         | $V_{IH}$ , $f = f_{MAX}$ <sup>[10]</sup>                                            | Mil    |                                                                                  |      |                                                          |      |            | 65   |            | 45   |      |

| I <sub>SB2</sub> | Standby Current                                   | $\overline{CE}_L$ or $\overline{CE}_R \ge V_{IH}$ ,                                 | Com'l  |                                                                                  | 135  |                                                          | 115  |            | 90   |            | 75   | mA   |

|                  | One Port,<br>TTL Inputs                           | Active Port Outputs<br>Open,<br>f = f <sub>MAX</sub> <sup>[10]</sup>                | Mil    |                                                                                  |      |                                                          |      |            | 115  |            | 90   |      |

| I <sub>SB3</sub> | Standby Current                                   | Both Ports CE <sub>L</sub> and                                                      | Com'l  |                                                                                  | 15   |                                                          | 15   |            | 15   |            | 15   | mA   |

|                  | Both Ports,<br>CMOS Inputs                        | $CE_R \ge V_{CC} - 0.2V,$ $V_{IN} \ge V_{CC} - 0.2V$ or $V_{IN} \le 0.2V$ , $f = 0$ | Mil    |                                                                                  |      |                                                          |      |            | 15   |            | 15   |      |

Shaded areas contain preliminary information.

### Note

- 4. The Voltage on any input or I/O pin cannot exceed the power pin during power-up.

- 5. T<sub>A</sub> is the "instant on" case temperature

- 6. See the last page of this specification for Group A subgroup testing information.

- BUSY and INT pins only.

- 8. Duration of the short circuit should not exceed 30 seconds.

- 9. This parameter is guaranteed but not tested.

- 10. At f = f<sub>MAX</sub>, address and data inputs are cycling at the maximum frequency of read cycle of 1/t<sub>RC</sub> and using AC Test Waveforms input levels of GND to 3V.

### Electrical Characteristics Over the Operating Range<sup>[6]</sup> (continued)

|                  |                          |                                                                                                                                                                                                                                                                                                      |       |      | 1-15 <sup>[3]</sup><br>I1-15 | 7C131<br>7C14 | 0-30 <sup>[3]</sup><br>-25,30<br>I0-30<br>-25,30 | 7C13 <sup>2</sup><br>7C140 | 0-35,45<br>1-35,45<br>0-35,45<br>1-35,45 | 7C13 | 80-55<br>81-55<br>80-55<br>81-55 |      |

|------------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|------------------------------|---------------|--------------------------------------------------|----------------------------|------------------------------------------|------|----------------------------------|------|

| Parameter        | Description              | Test Condition                                                                                                                                                                                                                                                                                       | ns    | Min. | Max.                         | Min.          | Max.                                             | Min.                       | Max.                                     | Min. | Max.                             | Unit |

| I <sub>SB4</sub> | Standby Current          | One Port CE <sub>L</sub> or                                                                                                                                                                                                                                                                          | Com'l |      | 125                          |               | 105                                              |                            | 85                                       |      | 70                               | mA   |

|                  | One Port,<br>CMOS Inputs | $\begin{split} & \text{CE}_{\text{R}} \geq \text{V}_{\text{CC}} - 0.2\text{V}, \\ & \text{V}_{\text{IN}} \geq \text{V}_{\text{CC}} - 0.2\text{V} \\ & \text{or V}_{\text{IN}} \leq 0.2\text{V}, \\ & \text{Active Port Outputs} \\ & \text{Open}, \\ & \text{f} = f_{\text{MAX}}^{[10]} \end{split}$ | Mil   |      |                              |               |                                                  |                            | 105                                      |      | 85                               |      |

## Capacitance<sup>[9]</sup>

| Parameter        | Description        | Test Conditions                         | Max. | Unit |

|------------------|--------------------|-----------------------------------------|------|------|

| C <sub>IN</sub>  | Input Capacitance  | $T_A = 25^{\circ}C, f = 1 \text{ MHz},$ | 15   | pF   |

| C <sub>OUT</sub> | Output Capacitance | $V_{CC} = 5.0V$                         | 10   | pF   |

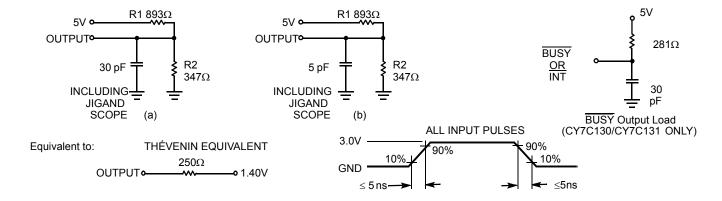

### **AC Test Loads and Waveforms**

## Switching Characteristics Over the Operating Range<sup>[6, 11]</sup>

|                   |                                          |          | 1-15 <sup>[3]</sup><br>41-15 | 7C1:<br>7C1 | 0-25 <sup>[3]</sup><br>31-25<br>40-25<br>41-25 | 7C1:<br>7C1 | 30-30<br>31-30<br>40-30<br>41-30 |      |

|-------------------|------------------------------------------|----------|------------------------------|-------------|------------------------------------------------|-------------|----------------------------------|------|

| Parameter         | Description                              | Min.     | Max.                         | Min.        | Max.                                           | Min.        | Max.                             | Unit |

| READ CYCL         | Ē                                        | ·        |                              |             |                                                |             |                                  |      |

| t <sub>RC</sub>   | Read Cycle Time                          | 15       |                              | 25          |                                                | 30          |                                  | ns   |

| t <sub>AA</sub>   | Address to Data Valid <sup>[12]</sup>    |          | 15                           |             | 25                                             |             | 30                               | ns   |

| t <sub>OHA</sub>  | Data Hold from Address Change            | 0        |                              | 0           |                                                | 0           |                                  | ns   |

| t <sub>ACE</sub>  | CE LOW to Data Valid <sup>[12]</sup>     |          | 15                           |             | 25                                             |             | 30                               | ns   |

| t <sub>DOE</sub>  | OE LOW to Data Valid <sup>[12]</sup>     |          | 10                           |             | 15                                             |             | 20                               | ns   |

| t <sub>LZOE</sub> | OE LOW to Low Z <sup>[9, 13, 14]</sup>   | 3        |                              | 3           |                                                | 3           |                                  | ns   |

| t <sub>HZOE</sub> | OE HIGH to High Z <sup>[9, 13, 14]</sup> |          | 10                           |             | 15                                             |             | 15                               | ns   |

| t <sub>LZCE</sub> | CE LOW to Low Z <sup>[9, 13, 14]</sup>   | 3        |                              | 5           |                                                | 5           |                                  | ns   |

| t <sub>HZCE</sub> | CE HIGH to High Z <sup>[9, 13, 14]</sup> |          | 10                           |             | 15                                             |             | 15                               | ns   |

| t <sub>PU</sub>   | CE LOW to Power-Up <sup>[9]</sup>        | 0        |                              | 0           |                                                | 0           |                                  | ns   |

| t <sub>PD</sub>   | CE HIGH to Power-Down <sup>[9]</sup>     |          | 15                           |             | 25                                             |             | 25                               | ns   |

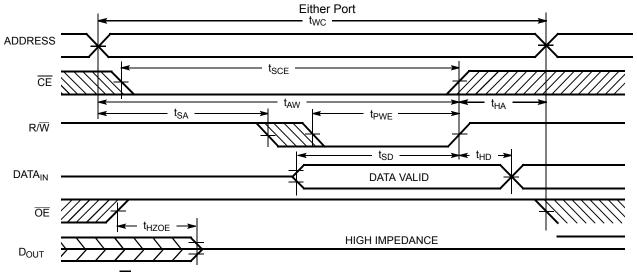

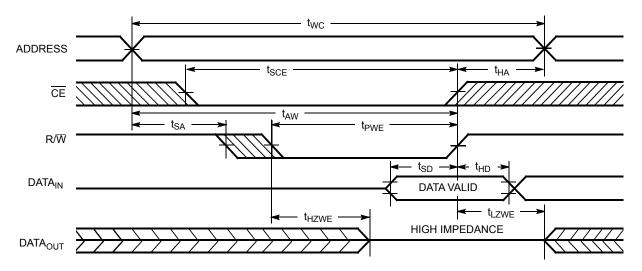

| WRITE CYC         | LE <sup>[15]</sup>                       | <u>'</u> | I                            | 1           |                                                |             |                                  | .1   |

| t <sub>WC</sub>   | Write Cycle Time                         | 15       |                              | 25          |                                                | 30          |                                  | ns   |

| t <sub>SCE</sub>  | CE LOW to Write End                      | 12       |                              | 20          |                                                | 25          |                                  | ns   |

| t <sub>AW</sub>   | Address Set-Up to Write End              | 12       |                              | 20          |                                                | 25          |                                  | ns   |

| t <sub>HA</sub>   | Address Hold from Write End              | 2        |                              | 2           |                                                | 2           |                                  | ns   |

| t <sub>SA</sub>   | Address Set-Up to Write Start            | 0        |                              | 0           |                                                | 0           |                                  | ns   |

| t <sub>PWE</sub>  | R/W Pulse Width                          | 12       |                              | 15          |                                                | 25          |                                  | ns   |

| t <sub>SD</sub>   | Data Set-Up to Write End                 | 10       |                              | 15          |                                                | 15          |                                  | ns   |

| t <sub>HD</sub>   | Data Hold from Write End                 | 0        |                              | 0           |                                                | 0           |                                  | ns   |

| t <sub>HZWE</sub> | R/W LOW to High Z <sup>[14]</sup>        |          | 10                           |             | 15                                             |             | 15                               | ns   |

| t <sub>LZWE</sub> | R/W HIGH to Low Z <sup>[14]</sup>        | 0        |                              | 0           |                                                | 0           |                                  | ns   |

|                   | ntain preliminary information.           |          |                              | 1           | 1                                              | 1           | 1                                |      |

Shaded areas contain preliminary information.

<sup>11.</sup> Test conditions assume signal transition times of 5 ns or less, timing reference levels of 1.5V, input pulse levels of 0 to 3.0V and output loading of the specified I<sub>OL</sub>/I<sub>OH,</sub> and 30-pF load capacitance.

12. AC Test Conditions use V<sub>OH</sub> = 1.6V and V<sub>OL</sub> = 1.4V.

<sup>12.</sup> AC lest Conditions use V<sub>OH</sub> = 1.6V and V<sub>OL</sub> = 1.4V.

13. At any given temperature and voltage condition for any given device, t<sub>HZCE</sub> is less than t<sub>LZCE</sub> and t<sub>HZOE</sub> is less than t<sub>LZOE</sub>.

14. t<sub>LZCE</sub>, t<sub>LZWE</sub>, t<sub>HZOE</sub>, t<sub>HZOE</sub>, t<sub>HZCE</sub> and t<sub>HZWE</sub> are tested with C<sub>L</sub> = 5<u>pF</u> as in part (b) <u>of</u> AC Test Loads. Transition is measured ±500 mV from steady state voltage.

15. The internal write time of the memory is defined by the overlap of CS LOW and R/W LOW. Both signals must be low to initiate a write and either signal can terminate a write by going high. The data input set-up and hold timing should be referenced to the rising edge of the signal that terminates the write.

# Switching Characteristics Over the Operating Range $^{[6,\ 11]}$ (continued)

|                                 |                                                 | 7C13<br>7C1 | 7C131-15 <sup>[3]</sup><br>7C141-15 |      | 0-25 <sup>[3]</sup><br>31-25<br>40-25<br>41-25 | 7C130-30<br>7C131-30<br>7C140-30<br>7C141-30 |         |      |  |

|---------------------------------|-------------------------------------------------|-------------|-------------------------------------|------|------------------------------------------------|----------------------------------------------|---------|------|--|

| Parameter                       | Description                                     | Min.        | Max.                                | Min. | Max.                                           | Min.                                         | Max.    | Unit |  |

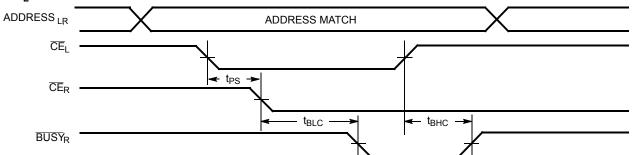

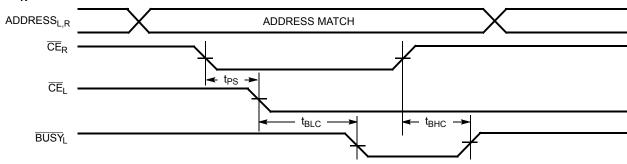

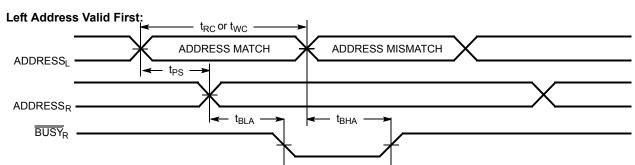

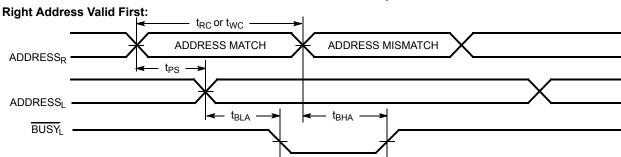

| BUSY/INTER                      | RRUPT TIMING                                    |             |                                     |      |                                                |                                              |         |      |  |

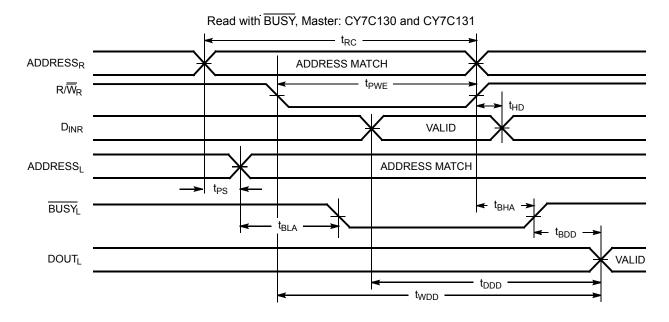

| t <sub>BLA</sub>                | BUSY LOW from Address Match                     |             | 15                                  |      | 20                                             |                                              | 20      | ns   |  |

| t <sub>BHA</sub>                | BUSY HIGH from Address Mismatch <sup>[16]</sup> |             | 15                                  |      | 20                                             |                                              | 20      | ns   |  |

| t <sub>BLC</sub>                | BUSY LOW from CE LOW                            |             | 15                                  |      | 20                                             |                                              | 20      | ns   |  |

| t <sub>BHC</sub>                | BUSY HIGH from CE HIGH <sup>[16]</sup>          |             | 15                                  |      | 20                                             |                                              | 20      | ns   |  |

| t <sub>PS</sub>                 | Port Set Up for Priority                        | 5           |                                     | 5    |                                                | 5                                            |         | ns   |  |

| t <sub>WB</sub> <sup>[17]</sup> | R/W LOW after BUSY LOW                          | 0           |                                     | 0    |                                                | 0                                            |         | ns   |  |

| t <sub>WH</sub>                 | R/W HIGH after BUSY HIGH                        | 13          |                                     | 20   |                                                | 30                                           |         | ns   |  |

| t <sub>BDD</sub>                | BUSY HIGH to Valid Data                         |             | 15                                  |      | 25                                             |                                              | 30      | ns   |  |

| t <sub>DDD</sub>                | Write Data Valid to Read Data Valid             |             | Note 18                             |      | Note 18                                        |                                              | Note 18 | ns   |  |

| t <sub>WDD</sub>                | Write Pulse to Data Delay                       |             | Note 18                             |      | Note 18                                        |                                              | Note 18 | ns   |  |

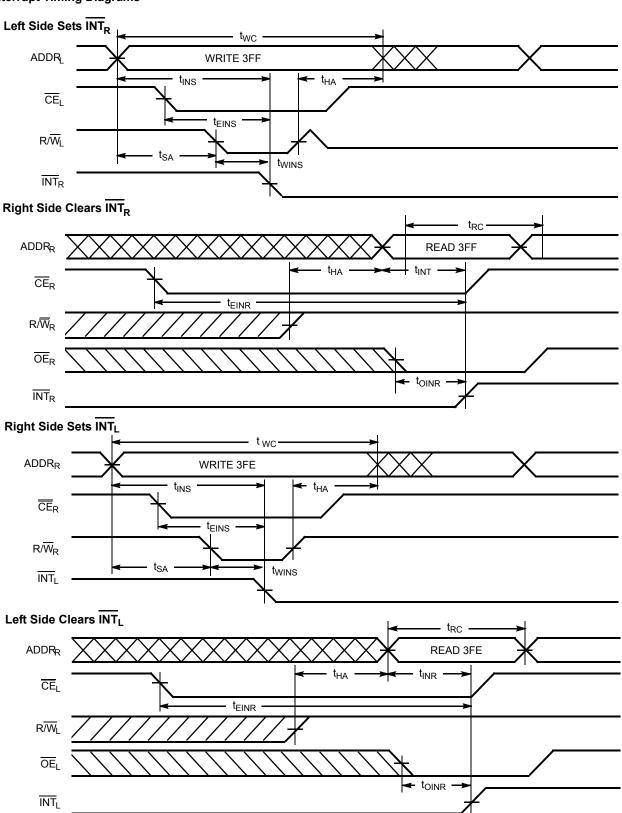

| INTERRUPT                       | TIMING                                          | •           |                                     |      |                                                |                                              |         |      |  |

| t <sub>WINS</sub>               | R/W to INTERRUPT Set Time                       |             | 15                                  |      | 25                                             |                                              | 25      | ns   |  |

| t <sub>EINS</sub>               | CE to INTERRUPT Set Time                        |             | 15                                  |      | 25                                             |                                              | 25      | ns   |  |

| t <sub>INS</sub>                | Address to INTERRUPT Set Time                   |             | 15                                  |      | 25                                             |                                              | 25      | ns   |  |

| t <sub>OINR</sub>               | OE to INTERRUPT Reset Time <sup>[16]</sup>      |             | 15                                  |      | 25                                             |                                              | 25      | ns   |  |

| t <sub>EINR</sub>               | CE to INTERRUPT Reset Time <sup>[16]</sup>      |             | 15                                  |      | 25                                             |                                              | 25      | ns   |  |

| t <sub>INR</sub>                | Address to INTERRUPT Reset Time <sup>[16]</sup> |             | 15                                  |      | 25                                             |                                              | 25      | ns   |  |

|                                 | tain preliminary information                    |             |                                     |      |                                                |                                              |         |      |  |

Shaded areas contain preliminary information.

## Switching Characteristics Over the Operating Range<sup>[6,11]</sup>

|                   |                                          | 7C1:<br>7C1 | 7C130-35<br>7C131-35<br>7C140-35<br>7C141-35 |      | 7C130-45<br>7C131-45<br>7C140-45<br>7C141-45 |      | 7C130-55<br>7C131-55<br>7C140-55<br>7C141-55 |      |

|-------------------|------------------------------------------|-------------|----------------------------------------------|------|----------------------------------------------|------|----------------------------------------------|------|

| Parameter         | Description                              | Min.        | Max.                                         | Min. | Max.                                         | Min. | Max.                                         | Unit |

| READ CYCL         | E                                        |             |                                              |      |                                              |      |                                              | •    |

| t <sub>RC</sub>   | Read Cycle Time                          | 35          |                                              | 45   |                                              | 55   |                                              | ns   |

| t <sub>AA</sub>   | Address to Data Valid <sup>[12]</sup>    |             | 35                                           |      | 45                                           |      | 55                                           | ns   |

| t <sub>OHA</sub>  | Data Hold from Address Change            | 0           |                                              | 0    |                                              | 0    |                                              | ns   |

| t <sub>ACE</sub>  | CE LOW to Data Valid <sup>[12]</sup>     |             | 35                                           |      | 45                                           |      | 55                                           | ns   |

| t <sub>DOE</sub>  | OE LOW to Data Valid <sup>[12]</sup>     |             | 20                                           |      | 25                                           |      | 25                                           | ns   |

| t <sub>LZOE</sub> | OE LOW to Low Z <sup>[9, 13, 14]</sup>   | 3           |                                              | 3    |                                              | 3    |                                              | ns   |

| t <sub>HZOE</sub> | OE HIGH to High Z <sup>[9, 13, 14]</sup> |             | 20                                           |      | 20                                           |      | 25                                           | ns   |

| t <sub>LZCE</sub> | CE LOW to Low Z <sup>[9, 13, 14]</sup>   | 5           |                                              | 5    |                                              | 5    |                                              | ns   |

<sup>16.</sup> These parameters are measured from the input signal changing, until the output pin goes to a high-impedance state.

<sup>17.</sup> CY7C140/CY7C141 only.

<sup>18. &</sup>lt;u>A write</u> operation on Port A, where Port A has priority, leaves the data on Port B's outputs undisturbed until one access time after one of the following: BUSY on Port B goes HIGH.

<u>Port B's address is toggled.</u>

<u>CE for Port B is toggled.</u>

R/W for Port B is toggled during valid read.

# $\textbf{Switching Characteristics} \ \, \text{Over the Operating Range}^{[6,11]} \ \, \text{(continued)}$

|                                 |                                                 | 7C13 | 30-35<br>31-35<br>40-35<br>41-35 | 7C13<br>7C13<br>7C14<br>7C14 | 1-45<br>0-45 | 7C13 | 30-55<br>31-55<br>40-55<br>41-55 |      |

|---------------------------------|-------------------------------------------------|------|----------------------------------|------------------------------|--------------|------|----------------------------------|------|

| Parameter                       | Description                                     | Min. | Max.                             | Min.                         | Max.         | Min. | Max.                             | Unit |

| t <sub>HZCE</sub>               | CE HIGH to High Z <sup>[9, 13, 14]</sup>        |      | 20                               |                              | 20           |      | 25                               | ns   |

| t <sub>PU</sub>                 | CE LOW to Power-Up <sup>[9]</sup>               | 0    |                                  | 0                            |              | 0    |                                  | ns   |

| t <sub>PD</sub>                 | CE HIGH to Power-Down <sup>[9]</sup>            |      | 35                               |                              | 35           |      | 35                               | ns   |

| WRITE CYC                       | L <b>E</b> <sup>[15]</sup>                      |      |                                  |                              |              |      |                                  |      |

| t <sub>WC</sub>                 | Write Cycle Time                                | 35   |                                  | 45                           |              | 55   |                                  | ns   |

| t <sub>SCE</sub>                | CE LOW to Write End                             | 30   |                                  | 35                           |              | 40   |                                  | ns   |

| t <sub>AW</sub>                 | Address Set-Up to Write End                     | 30   |                                  | 35                           |              | 40   |                                  | ns   |

| t <sub>HA</sub>                 | Address Hold from Write End                     | 2    |                                  | 2                            |              | 2    |                                  | ns   |

| t <sub>SA</sub>                 | Address Set-Up to Write Start                   | 0    |                                  | 0                            |              | 0    |                                  | ns   |

| t <sub>PWE</sub>                | R/W Pulse Width                                 | 25   |                                  | 30                           |              | 30   |                                  | ns   |

| t <sub>SD</sub>                 | Data Set-Up to Write End                        | 15   |                                  | 20                           |              | 20   |                                  | ns   |

| t <sub>HD</sub>                 | Data Hold from Write End                        | 0    |                                  | 0                            |              | 0    |                                  | ns   |

| t <sub>HZWE</sub>               | $R/\overline{W}$ LOW to High $Z^{[14]}$         |      | 20                               |                              | 20           |      | 25                               | ns   |

| t <sub>LZWE</sub>               | $R/\overline{W}$ HIGH to Low $Z^{[14]}$         | 0    |                                  | 0                            |              | 0    |                                  | ns   |

| BUSY/INTER                      | RRUPT TIMING                                    |      |                                  |                              |              |      |                                  |      |

| t <sub>BLA</sub>                | BUSY LOW from Address Match                     |      | 20                               |                              | 25           |      | 30                               | ns   |

| t <sub>BHA</sub>                | BUSY HIGH from Address Mismatch <sup>[16]</sup> |      | 20                               |                              | 25           |      | 30                               | ns   |

| t <sub>BLC</sub>                | BUSY LOW from CE LOW                            |      | 20                               |                              | 25           |      | 30                               | ns   |

| t <sub>BHC</sub>                | BUSY HIGH from CE HIGH <sup>[16]</sup>          |      | 20                               |                              | 25           |      | 30                               | ns   |

| t <sub>PS</sub>                 | Port Set Up for Priority                        | 5    |                                  | 5                            |              | 5    |                                  | ns   |

| t <sub>WB</sub> <sup>[17]</sup> | R/W LOW after BUSY LOW                          | 0    |                                  | 0                            |              | 0    |                                  | ns   |

| t <sub>WH</sub>                 | R/W HIGH after BUSY HIGH                        | 30   |                                  | 35                           |              | 35   |                                  | ns   |

| t <sub>BDD</sub>                | BUSY HIGH to Valid Data                         |      | 35                               |                              | 45           |      | 45                               | ns   |

| t <sub>DDD</sub>                | Write Data Valid to Read Data Valid             |      | Note<br>18                       |                              | Note<br>18   |      | Note<br>18                       | ns   |

| t <sub>WDD</sub>                | Write Pulse to Data Delay                       |      | Note<br>18                       |                              | Note<br>18   |      | Note<br>18                       | ns   |

| INTERRUPT                       | TIMING                                          |      | <u>.</u>                         |                              | 1            | 1    |                                  | 1    |

| t <sub>WINS</sub>               | R/W to INTERRUPT Set Time                       |      | 25                               |                              | 35           |      | 45                               | ns   |

| t <sub>EINS</sub>               | CE to INTERRUPT Set Time                        |      | 25                               |                              | 35           |      | 45                               | ns   |

| t <sub>INS</sub>                | Address to INTERRUPT Set Time                   |      | 25                               |                              | 35           |      | 45                               | ns   |

| t <sub>OINR</sub>               | OE to INTERRUPT Reset Time <sup>[16]</sup>      |      | 25                               |                              | 35           |      | 45                               | ns   |

| t <sub>EINR</sub>               | CE to INTERRUPT Reset Time <sup>[16]</sup>      |      | 25                               |                              | 35           |      | 45                               | ns   |

| t <sub>INR</sub>                | Address to INTERRUPT Reset Time <sup>[16]</sup> |      | 25                               |                              | 35           |      | 45                               | ns   |

## **Switching Waveforms**

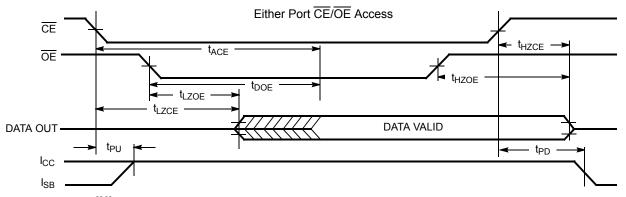

**Read Cycle No. 1**<sup>[19, 20]</sup>

# Either Port Address Access $t_{RC}$ **ADDRESS** DATA OUT PREVIOUS DATAVALID DATA VALID

## **Read Cycle No. 2**<sup>[19, 21]</sup>

Read Cycle No. 3<sup>[20]</sup>

- 19. R/W is HIGH for read cycle.

- 20. Device is continuously selected,  $\overline{\text{CE}} = \text{V}_{\text{IL}}$  and  $\overline{\text{OE}} = \text{V}_{\text{IL}}$ . 21. Address valid prior to or coincident with  $\overline{\text{CE}}$  transition LOW.

Write Cycle No. 1 (OE Three-States Data I/Os—Either Port[15, 22]

Write Cycle No. 2 (R/ $\overline{W}$  Three-States Data I/Os—Either Port)<sup>[16, 23]</sup>

Notes:

22. If  $\overline{OE}$  is LOW during a R $\overline{W}$  controlled write cycle, the write pulse width must be the larger of  $t_{PWE}$  or  $t_{HZWE} + t_{SD}$  to allow the data I/O pins to enter high impedance and for data to be placed on the bus for the required  $t_{SD}$ .

23. If the  $\overline{CE}$  LOW transition occurs simultaneously with or after the R/ $\overline{W}$  LOW transition, the outputs remain in the high-impedance state.

### **Busy Timing Diagram No. 1 (CE Arbitration)**

## **CE**<sub>L</sub> Valid First:

## CE<sub>R</sub> Valid First:

### **Busy Timing Diagram No. 2 (Address Arbitration)**

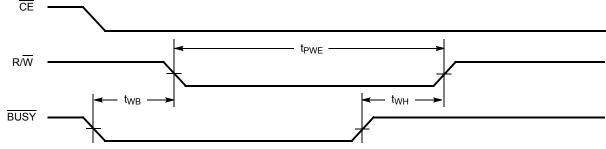

**Busy Timing Diagram No. 3**

Write with BUSY (Slave:CY7C140/CY7C141)

**Interrupt Timing Diagrams**

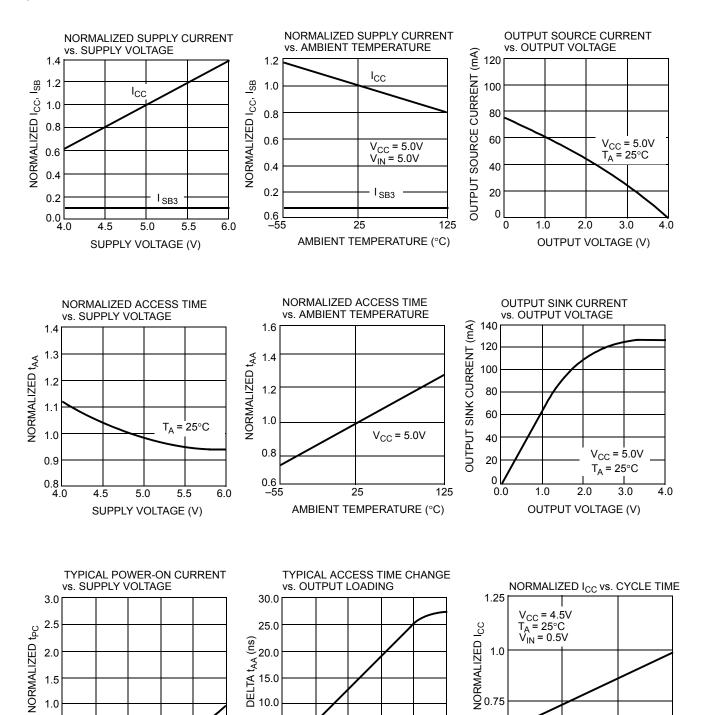

### Typical DC and AC Characteristics

$V_{CC} = 4.5V$

T<sub>A</sub> = 25°C

600 CAPACITANCE (pF)

800 1000

0.50

5.0

0

200

400

5.0

3.0

SUPPLY VOLTAGE (V)

2.0

1.0

0.5

30

CYCLE FREQUENCY (MHz)

# **Ordering Information**

| Speed<br>(ns) | Ordering Code | Package<br>Name | Package Type                                | Operating<br>Range |  |

|---------------|---------------|-----------------|---------------------------------------------|--------------------|--|

| 30            | CY7C130-30PC  | P25             | 48-Lead (600-Mil) Molded DIP                | Commercial         |  |

|               | CY7C130-30PI  | P25             | 48-Lead (600-Mil) Molded DIP                | Industrial         |  |

| 35            | CY7C130-35PC  | P25             | 48-Lead (600-Mil) Molded DIP                | Commercial         |  |

|               | CY7C130-35PI  | P25             | 48-Lead (600-Mil) Molded DIP                | Industrial         |  |

|               | CY7C130-35DMB | D26             | 48-Lead (600-Mil) Sidebraze DIP             | Military           |  |

| 45            | CY7C130-45PC  | P25             | 48-Lead (600-Mil) Molded DIP                | Commercial         |  |

|               | CY7C130-45PI  | P25             | 48-Lead (600-Mil) Molded DIP                | Industrial         |  |

|               | CY7C130-45DMB | D26             | 48-Lead (600-Mil) Sidebraze DIP             | Military           |  |

| 55            | CY7C130-55PC  | P25             | 48-Lead (600-Mil) Molded DIP                | Commercial         |  |

|               | CY7C130-55PI  | P25             | 48-Lead (600-Mil) Molded DIP                | Industrial         |  |

|               | CY7C130-55DMB | D26             | 48-Lead (600-Mil) Sidebraze DIP             | Military           |  |

| 15            | CY7C131-15JC  | J69             | 52-Lead Plastic Leaded Chip Carrier         | Commercial         |  |

|               | CY7C131-15JXC | J69             | 52-Lead Pb-Free Plastic Leaded Chip Carrier |                    |  |

|               | CY7C131-15NC  | N52             | 52-Pin Plastic Quad Flatpack                |                    |  |

|               | CY7C131-15JI  | J69             | 52-Lead Plastic Leaded Chip Carrier         | Industrial         |  |

|               | CY7C131-15JXI | J69             | 52-Lead Pb-Free Plastic Leaded Chip Carrier |                    |  |

| 25            | CY7C131-25JC  | J69             | 52-Lead Plastic Leaded Chip Carrier         | Commercial         |  |

|               | CY7C131-25JXC | J69             | 52-Lead Pb-Free Plastic Leaded Chip Carrier |                    |  |

|               | CY7C131-25NC  | N52             | 52-Pin Plastic Quad Flatpack                |                    |  |

|               | CY7C131-25NXC | N52             | 52-Pin Pb-Free Plastic Quad Flatpack        |                    |  |

|               | CY7C131-25JI  | J69             | 52-Lead Plastic Leaded Chip Carrier         | Industrial         |  |

|               | CY7C131-25NI  | N52             | 52-Pin Plastic Quad Flatpack                |                    |  |

| 30            | CY7C131-30JC  | J69             | 52-Lead Plastic Leaded Chip Carrier         | Commercial         |  |

|               | CY7C131-30NC  | N52             | 52-Pin Plastic Quad Flatpack                |                    |  |

|               | CY7C131-30JI  | J69             | 52-Lead Plastic Leaded Chip Carrier         | Industrial         |  |

| 35            | CY7C131-35JC  | J69             | 52-Lead Plastic Leaded Chip Carrier         | Commercial         |  |

|               | CY7C131-35NC  | N52             | 52-Pin Plastic Quad Flatpack                |                    |  |

|               | CY7C131-35JI  | J69             | 52-Lead Plastic Leaded Chip Carrier         | Industrial         |  |

|               | CY7C131-35NI  | N52             | 52-Pin Plastic Quad Flatpack                |                    |  |

| 45            | CY7C131-45JC  | J69             | 52-Lead Plastic Leaded Chip Carrier         | Commercial         |  |

|               | CY7C131-45NC  | N52             | 52-Pin Plastic Quad Flatpack                |                    |  |

|               | CY7C131-45JI  | J69             | 52-Lead Plastic Leaded Chip Carrier         | Industrial         |  |

|               | CY7C131-45NI  | N52             | 52-Pin Plastic Quad Flatpack                |                    |  |

| 55            | CY7C131-55JC  | J69             | 52-Lead Plastic Leaded Chip Carrier         | Commercial         |  |

|               | CY7C131-55JXC | J69             | 52-Lead Pb-Free Plastic Leaded Chip Carrier |                    |  |

|               | CY7C131-55NC  | N52             | 52-Pin Plastic Quad Flatpack                |                    |  |

|               | CY7C131-55NXC | N52             | 52-Pin Pb-Free Plastic Quad Flatpack        |                    |  |

|               | CY7C131-55JI  | J69             | 52-Lead Plastic Leaded Chip Carrier         | Industrial         |  |

|               | CY7C131-55JXI | J69             | 52-Lead Pb-Free Plastic Leaded Chip Carrier | 1                  |  |

|               | CY7C131-55NI  | N52             | 52-Pin Plastic Quad Flatpack                | 7                  |  |

Document #: 38-06002 Rev. \*D

# Ordering Information (continued)

| Speed<br>(ns) | Ordering Code | Package<br>Name | Package Type                                | Operating<br>Range |

|---------------|---------------|-----------------|---------------------------------------------|--------------------|

| 30            | CY7C140-30PC  | P25             | 48-Lead (600-Mil) Molded DIP                | Commercial         |

|               | CY7C140-30PI  | P25             | 48-Lead (600-Mil) Molded DIP                | Industrial         |

| 35            | CY7C140-35PC  | P25             | 48-Lead (600-Mil) Molded DIP                | Commercial         |

|               | CY7C140-35PI  | P25             | 48-Lead (600-Mil) Molded DIP                | Industrial         |

|               | CY7C140-35DMB | D26             | 48-Lead (600-Mil) Sidebraze DIP             | Military           |

| 45            | CY7C140-45PC  | P25             | 48-Lead (600-Mil) Molded DIP                | Commercial         |

|               | CY7C140-45PI  | P25             | 48-Lead (600-Mil) Molded DIP                | Industrial         |

|               | CY7C140-45DMB | D26             | 48-Lead (600-Mil) Sidebraze DIP             | Military           |

| 55            | CY7C140-55PC  | P25             | 48-Lead (600-Mil) Molded DIP                | Commercial         |

|               | CY7C140-55PI  | P25             | 48-Lead (600-Mil) Molded DIP                | Industrial         |

|               | CY7C140-55DMB | D26             | 48-Lead (600-Mil) Sidebraze DIP             | Military           |

| 15            | CY7C141-15JC  | J69             | 52-Lead Plastic Leaded Chip Carrier         | Commercial         |

|               | CY7C141-15NC  | N52             | 52-Pin Plastic Quad Flatpack                |                    |

| 25            | CY7C141-25JC  | J69             | 52-Lead Plastic Leaded Chip Carrier         | Commercial         |

|               | CY7C141-25JXC | J69             | 52-Lead Pb-Free Plastic Leaded Chip Carrier |                    |

|               | CY7C141-25NC  | N52             | 52-Pin Plastic Quad Flatpack                |                    |

|               | CY7C141-25JI  | J69             | 52-Lead Plastic Leaded Chip Carrier         | Industrial         |

|               | CY7C141-25NI  | N52             | 52-Pin Plastic Quad Flatpack                | 7                  |

| 30            | CY7C141-30JC  | J69             | 52-Lead Plastic Leaded Chip Carrier         | Commercial         |

|               | CY7C141-30NC  | N52             | 52-Pin Plastic Quad Flatpack                |                    |

|               | CY7C141-30JI  | J69             | 52-Lead Plastic Leaded Chip Carrier         | Industrial         |

| 35            | CY7C141-35JC  | J69             | 52-Lead Plastic Leaded Chip Carrier         | Commercial         |

|               | CY7C141-35NC  | N52             | 52-Pin Plastic Quad Flatpack                | 7                  |

|               | CY7C141-35JI  | J69             | 52-Lead Plastic Leaded Chip Carrier         | Industrial         |

|               | CY7C141-35NI  | N52             | 52-Pin Plastic Quad Flatpack                | 7                  |

| 45            | CY7C141-45JC  | J69             | 52-Lead Plastic Leaded Chip Carrier         | Commercial         |

|               | CY7C141-45NC  | N52             | 52-Pin Plastic Quad Flatpack                | 7                  |

|               | CY7C141-45JI  | J69             | 52-Lead Plastic Leaded Chip Carrier         | Industrial         |

|               | CY7C141-45NI  | N52             | 52-Pin Plastic Quad Flatpack                |                    |

| 55            | CY7C141-55JC  | J69             | 52-Lead Plastic Leaded Chip Carrier         | Commercial         |

|               | CY7C141-55NC  | N52             | 52-Pin Plastic Quad Flatpack                |                    |

|               | CY7C141-55JI  | J69             | 52-Lead Plastic Leaded Chip Carrier         | Industrial         |

|               | CY7C141-55NI  | N52             | 52-Pin Plastic Quad Flatpack                |                    |

## **MILITARY SPECIFICATIONS**

## **Group A Subgroup Testing**

### **DC Characteristics**

| Parameter            | Subgroups |

|----------------------|-----------|

| V <sub>OH</sub>      | 1, 2, 3   |

| V <sub>OL</sub>      | 1, 2, 3   |

| V <sub>IH</sub>      | 1, 2, 3   |

| V <sub>IL</sub> Max. | 1, 2, 3   |

| I <sub>IX</sub>      | 1, 2, 3   |

| l <sub>OZ</sub>      | 1, 2, 3   |

| I <sub>CC</sub>      | 1, 2, 3   |

| I <sub>SB1</sub>     | 1, 2, 3   |

| I <sub>SB2</sub>     | 1, 2, 3   |

| I <sub>SB3</sub>     | 1, 2, 3   |

| I <sub>SB4</sub>     | 1, 2, 3   |

# **Switching Characteristics**

| Parameter                       | Subgroups       |

|---------------------------------|-----------------|

| READ CYCLE                      |                 |

| t <sub>RC</sub>                 | 7, 8, 9, 10, 11 |

| t <sub>AA</sub>                 | 7, 8, 9, 10, 11 |

| t <sub>ACE</sub>                | 7, 8, 9, 10, 11 |

| t <sub>DOE</sub>                | 7, 8, 9, 10, 11 |

| WRITE CYCLE                     |                 |

| $t_WC$                          | 7, 8, 9, 10, 11 |

| t <sub>SCE</sub>                | 7, 8, 9, 10, 11 |

| $t_AW$                          | 7, 8, 9, 10, 11 |

| t <sub>HA</sub>                 | 7, 8, 9, 10, 11 |

| t <sub>SA</sub>                 | 7, 8, 9, 10, 11 |

| t <sub>PWE</sub>                | 7, 8, 9, 10, 11 |

| t <sub>SD</sub>                 | 7, 8, 9, 10, 11 |

| t <sub>HD</sub>                 | 7, 8, 9, 10, 11 |

| BUSY/INTERRUPT TIMING           |                 |

| $t_BLA$                         | 7, 8, 9, 10, 11 |

| t <sub>BHA</sub>                | 7, 8, 9, 10, 11 |

| t <sub>BLC</sub>                | 7, 8, 9, 10, 11 |

| t <sub>BHC</sub>                | 7, 8, 9, 10, 11 |

| t <sub>PS</sub>                 | 7, 8, 9, 10, 11 |

| $t_{WINS}$                      | 7, 8, 9, 10, 11 |

| t <sub>EINS</sub>               | 7, 8, 9, 10, 11 |

| t <sub>INS</sub>                | 7, 8, 9, 10, 11 |

| t <sub>OINR</sub>               | 7, 8, 9, 10, 11 |

| t <sub>EINR</sub>               | 7, 8, 9, 10, 11 |

| $t_INR$                         | 7, 8, 9, 10, 11 |

| BUSY TIMING                     |                 |

| t <sub>WB</sub> <sup>[24]</sup> | 7, 8, 9, 10, 11 |

| $t_WH$                          | 7, 8, 9, 10, 11 |

| t <sub>BDD</sub>                | 7, 8, 9, 10, 11 |

**Note:** 24. CY7C140/CY7C141 only.

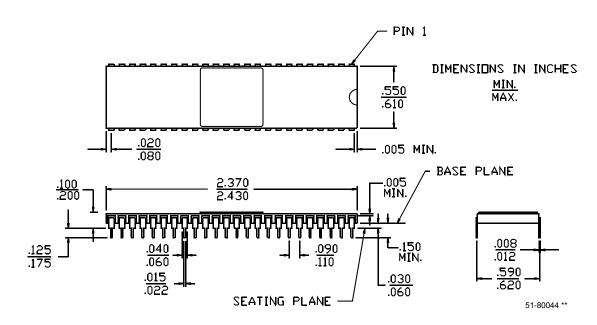

## **Package Diagrams**

### 48-Lead (600-Mil) Sidebraze DIP D26 MIL-STD-1835 D-14 Config. C

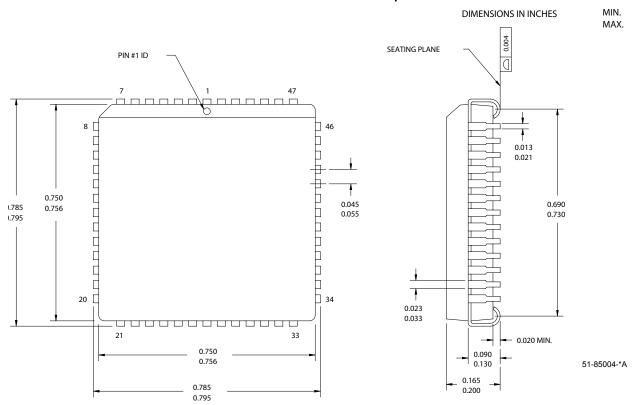

### 52-Lead Plastic Leaded Chip Carrier J69 52-Lead Pb-Free Plastic Leaded Chip Carrier J69

### Package Diagrams (continued)

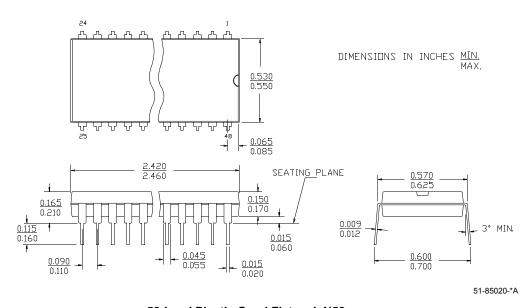

### 48-Lead (600-Mil) Molded DIP P25

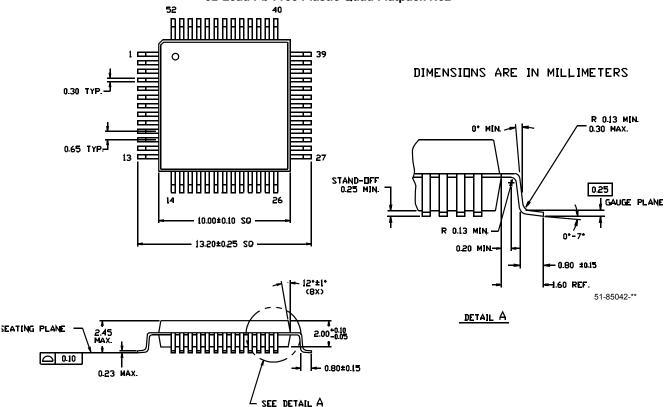

### 52-Lead Plastic Quad Flatpack N52 52-Lead Pb-Free Plastic Quad Flatpack N52

All products and company names mentioned in this document may be the trademarks of their respective holders.

# **Document History Page**

| REV. | ECN NO. | Issue<br>Date | Orig. of<br>Change | Description of Change                                                                                 |

|------|---------|---------------|--------------------|-------------------------------------------------------------------------------------------------------|

| **   | 110169  | 09/29/01      | SZV                | Change from Spec number: 38-00027 to 38-06002                                                         |

| *A   | 122255  | 12/26/02      | RBI                | Power up requirements added to Maximum Ratings Information                                            |

| *B   | 236751  | See ECN       | YDT                | Removed cross information from features section                                                       |

| *C   | 325936  | See ECN       | RUY                | Added pin definitions table, 52-pin PQFP package diagram and Pb-free information                      |

| *D   | 393153  | See ECN       | YIM                | Added CY7C131-15JI to ordering information Added Pb-Free parts to ordering information: CY7C131-15JXI |