3501 ED BLUESTEIN BLVD., AUSTIN, TEXAS 78721

## MC146823

## **Advance Information**

#### **CMOS PARALLEL INTERFACE**

The MC146823 CMOS parallel interface (CPI) provides a universal means of interfacing external signals with the MC146805E2 CMOS microprocessor and other multiplexed bus microprocessors. The unique MOTEL circuit on-chip allows direct interfacing to most industry CMOS microprocessors, as well as many NMOS MPUs.

The MC146823 CPI includes three bidirectional 8-bit ports or 24 I/O pins. Each I/O line may be separately established as an input or an output under program control via data direction registers associated with each port. Using the bit change and test instructions of the MC146805E2, each individual I/O pin can be separately accessed. All port registers are read/write bytes to accommodate read-modify-write instructions. Features include:

- 24 Individually Programmed I/O Pins

- MOTEL Circuit for Bus Compatibility with Many Microprocessors

- Multiplexed Bus Compatibility with: MC146805E2, MC6801, MC6803, and Competitive Microprocessors

- Data Direction Registers for Ports A, B, and C

- Four Port C I/O Pins May Be Used as Control Lines for: Four Interrupt Inputs Input Byte Latch Output Pulse Handshake Activity

- 15 Registers Addressed as Memory Locations

- Handshake Control Logic for Input and Output Peripheral Operation

- Interrupt Output Pin

- Reset Input to Clear Interrupts and Initialize Internal Registers

- 3.0 Volt to 5.5 Volt Operating VDD

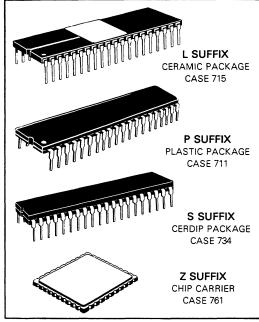

#### **ORDERING INFORMATION**

$(T_A = 0$ °C to +70°C)

| Package Type                     | Order Number |

|----------------------------------|--------------|

| Plastic - P Suffix               | MC146823P    |

| Ceramic (Side Brazed) — L Suffix | MC146823L    |

| Cerdip - S Suffix                | MC146823S    |

| Chip Carrier — Z Suffix          | MC146823Z    |

## **CMOS**

(HIGH-DENSITY HIGH-PERFORMANCE SILICON-GATE)

#### PARALLEL INTERFACE

| PIN                                                                                  | ASSIGNMENT          |  |  |  |  |  |

|--------------------------------------------------------------------------------------|---------------------|--|--|--|--|--|

| PC2 <b>I</b> 1                                                                       | 40 V <sub>DD</sub>  |  |  |  |  |  |

| PC1 <b>[</b> 2                                                                       | 39 <b>1</b> PC3     |  |  |  |  |  |

| PC0 <b>□</b> 3                                                                       | 38 DPC4/CA1         |  |  |  |  |  |

| PA0 <b>1</b> 4                                                                       | 37 <b>p</b> PC5/CA2 |  |  |  |  |  |

| PA1 <b>[</b> 5                                                                       | 36 PC6/CB1          |  |  |  |  |  |

| PA2 <b>[</b> 6                                                                       | 35 <b>1</b> PC7/CB2 |  |  |  |  |  |

| PA3 <b>[</b> 7                                                                       | 34 🗖 РВО            |  |  |  |  |  |

| PA4 <b>[</b> 8                                                                       | 33 <b>T</b> PB1     |  |  |  |  |  |

| PA5 <b>[</b> 9                                                                       | 32 <b>1</b> PB2     |  |  |  |  |  |

| PA6 <b>[</b> 10                                                                      | 31 <b>1</b> PB3     |  |  |  |  |  |

| · PA7 <b>[</b> 11                                                                    | 30 <b>1</b> PB4     |  |  |  |  |  |

| AD0 <b>[</b> 12                                                                      | 29 <b>1</b> PB5     |  |  |  |  |  |

| AD1 <b>[</b> 13                                                                      | 28 <b>1</b> PB6     |  |  |  |  |  |

| AD2 <b>[</b> 14                                                                      | 27 <b>1</b> PB7     |  |  |  |  |  |

| AD3 <b>[</b> 15                                                                      | 26 🗖 ĪRQ            |  |  |  |  |  |

| AD4 <b>[</b> 16                                                                      | 25 RESET            |  |  |  |  |  |

| AD5 <b>[</b> 17                                                                      | 24 <b>D</b> DS      |  |  |  |  |  |

| AD6 <b>[</b> 18                                                                      | 23 <b>□</b> R/₩     |  |  |  |  |  |

| AD7 <b>[</b> 19                                                                      | 22 <b>1</b> AS      |  |  |  |  |  |

| V <sub>SS</sub> <b>I</b> 20                                                          | 21 D CE             |  |  |  |  |  |

| Pin assignments are the same for both the dual-in-<br>line and chip carrier package. |                     |  |  |  |  |  |

## MAXIMUM RATINGS (Voltages reference to VSS)

| Ratings                                     | Symbol           | Value                            | Unit |

|---------------------------------------------|------------------|----------------------------------|------|

| Supply Voltage                              | V <sub>DD</sub>  | -0.3 to +8.0                     | V    |

| All Input Voltages                          | Vin              | $V_{SS} = 0.5$ to $V_{DD} + 0.5$ | V    |

| Current Drain per Pin Excluding VDD and VSS | ı                | 10                               | mA   |

| Operating Temperature Range                 | TA               | 0 to +70                         | °C   |

| Storage Temperature Range                   | T <sub>stg</sub> | -55 to +150                      | °C   |

## THERMAL CHARACTERISTICS

| Characteristics    | Symbol        | Value | Unit |

|--------------------|---------------|-------|------|

| Thermal Resistance |               |       |      |

| Cera <b>m</b> ic   | $\theta_{JA}$ | 50    | °C/W |

| Plastic            |               | 100   |      |

| Cerdip             |               | 60    |      |

| Chip Carrier       |               | TBD   |      |

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high-impedance circuit. For proper operation it is recommended that  $V_{in}$  and  $V_{out}$  be constrained to the range  $V_{SS} \ge (V_{in}$  or  $V_{out}) \ge V_{DD}$ . Leakage currents are reduced and reliability of operation is enhanced if unused inputs are tied to an appropriate logic voltage level (e.g., either  $V_{SS}$  or  $V_{DD}$ ).

## DC ELECTRICAL CHARACTERISTICS (VDD=5 Vdc ±10%, VSS=0 Vdc, TA=0°C to 70°C, unless otherwise noted)

| Parameter                                                               | Symbol           | Min                   | Max    | Unit |

|-------------------------------------------------------------------------|------------------|-----------------------|--------|------|

| Output Voltage (I <sub>Load</sub> ≤10 μA)                               | VOL              | _                     | 0.1    | V    |

|                                                                         | ∨он              | V <sub>DD</sub> = 0.1 | _      | V    |

| Output High Voltage                                                     |                  |                       |        |      |

| $(I_{Load} = -1.6 \text{ mA}) \text{ AD0-AD7}$                          | ∨он              | 4.1                   | VDD    |      |

| (I <sub>Load</sub> = -0.2 mA) PA0-PA7, PC0-PC7                          | ∨он              | 4.1                   | VDD    | V    |

| $(I_{Load} = -0.36 \text{ mA}) \text{ PB0-PB7}$                         | ∨он              | 4.1                   | VDD    |      |

| Output Low Voltage                                                      |                  |                       |        |      |

| (I <sub>Load</sub> = 1.6 mA) AD0-AD7, PB0-PB7                           | VOL              | Vss                   | 0.4    |      |

| (I <sub>Load</sub> =0.8 mA) <u>PA0-PA7</u> , PC0-PC7                    | VOL              | Vss                   | 0.4    | V    |

| (I <sub>Load</sub> =1.0 mA) IRQ                                         | VOL              | V <sub>SS</sub>       | 0.4    |      |

| Input High Voltage, AD0-AD7, AS, DS, R/W, CE, PA0-PA7, PB0-PB7, PC0-PC7 | VIH              | V <sub>DD</sub> - 2.0 | VDD    | V    |

| RESET                                                                   | VIH              | V <sub>DD</sub> = 0.8 | VDD    |      |

| Input Low Voltage (All Inputs)                                          | VIL              | V <sub>SS</sub>       | 0.8    | ٧    |

| Quiescent Current - No dc Loads                                         |                  |                       |        |      |

| (All Ports Programmed as Inputs, All Inputs= V <sub>DD</sub> - 0.2 V)   | IDD              | _                     | 160    | μΑ   |

| Total Supply Current                                                    |                  |                       |        |      |

| (All Ports Programmed as Inputs, $CE = V_{1L}$ , $t_{CYC} = 1 \mu s$ )  | IDD              | _                     | 3.0    | mΑ   |

| Input Current, CE, AS, R/W, DS, RESET                                   | lin              | _                     | ± 1.0  | μΑ   |

| Hi-Z State Leakage, AD0-AD7, PA0-PA7, PB0-PB7, PC0-PC7                  | <sup> </sup> TSL | _                     | ± 10.0 | μΑ   |

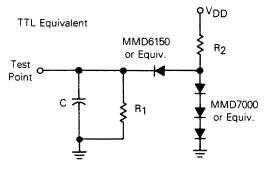

## **EQUIVALENT TEST LOADS**

CMOS Equivalent

| Pin              | R1    | R2    | С      |

|------------------|-------|-------|--------|

| AD0-AD7          | 2.55k | 2.0k  | 130 pF |

| PA0-PA7, PC0-PC7 | 20.0k | 4.32k | 50 pF  |

| PB0-PB7          | 11.5k | 2.1k  | 50 pF  |

**MOTOROLA** Semiconductor Products Inc.

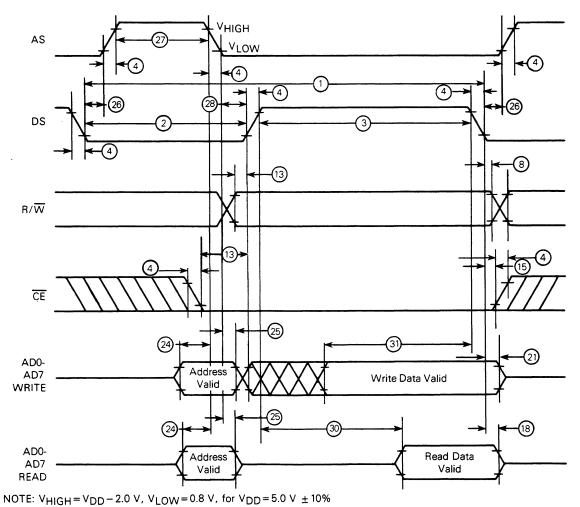

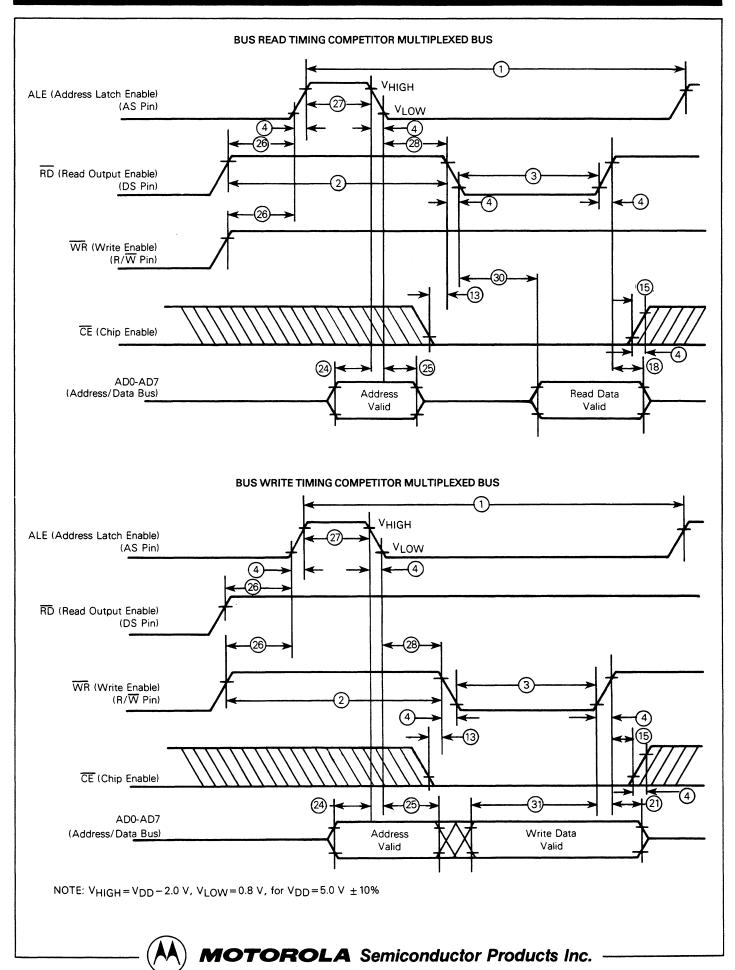

**BUS TIMING** ( $V_{DD}$ =5 Vdc  $\pm$  10%,  $V_{SS}$ =0 Vdc,  $T_A$ =0° to 70°C, unless otherwise noted)

| ldent.<br>Number | Characteristics                                             | Symbol                          | Min  | Max | Unit |

|------------------|-------------------------------------------------------------|---------------------------------|------|-----|------|

| 1                | Cycle Time                                                  | tcyc                            | 1000 | dc  | ns   |

| 2                | Pulse Width, DS/E Low or RD/WR High                         | PWEL                            | 300  | _   | ns   |

| 3                | Pulse Width, DS/E High or RD/WR Low                         | PWEH                            | 325  | -   | ns   |

| 4                | Input Rise and Fall Time                                    | t <sub>r</sub> , t <sub>f</sub> | _    | 30  | ns   |

| 8                | R/W Hold Time                                               | tRWH                            | 10   | _   | ns   |

| 13               | $R/\overline{W}$ and $\overline{CE}$ Setup Time Before DS/E | tRWS                            | 25   | -   | ns   |

| 15               | Chip Enable Hold Time                                       | tCH                             | 0    | _   | ns   |

| 18               | Read Data Hold Time                                         | tDHR                            | 10   | 100 | ns   |

| 21               | Write Data Hold Time                                        | tDHW                            | 0    | _   | ns   |

| 24               | Muxed Address Valid Time to AS/ALE Fall                     | tASL                            | 25   | _   | ns   |

| 25               | Muxed Address Hold Time                                     | <sup>t</sup> AHL                | 20   | _   | ns   |

| 26               | Delay Time DS/E to AS/ALE Rise                              | †ASD                            | 60   | _   | ns   |

| 27               | Pulse Width, AS/ALE High                                    | PWASH                           | 170  | -   | ns   |

| 28               | Delay Time, AS/ALE to DS/E Rise                             | †ASED                           | 60   | _   | ns   |

| 30               | Peripheral Output Data Delay Time from DS/E or RD           | <sup>t</sup> DDR                | 20   | 240 | ns   |

| 31               | Peripheral Data Setup Time                                  | tDSW                            | 220  | -   | ns   |

NOTE: Designations E, ALE,  $\overline{\text{RD}}$ , and  $\overline{\text{WR}}$  refer to signals from alternative microprocessor signals.

## **BUS TIMING DIAGRAM**

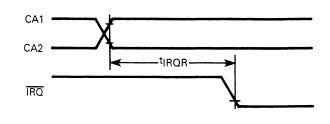

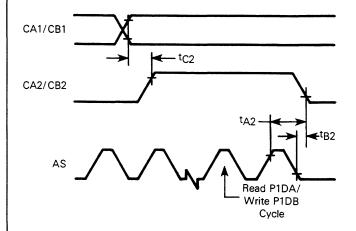

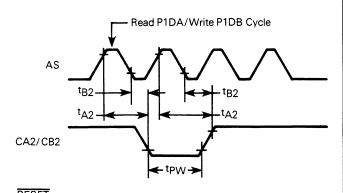

## **CONTROL TIMING** ( $V_{DD}$ =5.0 Vdc $\pm$ 10%, $V_{SS}$ =0 Vdc, $T_{A}$ =0°C to 70°C)

| Parameter                                                             | Symbol            | Min | Max | Unit |

|-----------------------------------------------------------------------|-------------------|-----|-----|------|

| Interrupt Response (Input Modes 1 and 3)                              | <sup>‡</sup> IRQR | TBD | _   | μS   |

| Delay, CA1 (CB1) Active Transition to CA2 (CB2) High (Output Mode 0)  | t <sub>C2</sub>   | TBD | _   | μS   |

| Delay, CA2 Transition from Positive Edge of AS (Output Modes 0 and 1) | t <sub>A2</sub>   | TBD | _   | μS   |

| Delay, CB2 Transition from Negative Edge of AS (Output Modes 0 and 1) | t <sub>B2</sub>   | TBD | _   | μS   |

| CA2/CB2 Pulse Width (Output Mode 1)                                   | tpW               | TBD | TBD | ns   |

| Delay, V <sub>DD</sub> Rise to RESET High                             | <sup>t</sup> RLH  | TBD | _   | μS   |

| Pulse Width, RESET                                                    | t <sub>RW</sub>   | TBD | _   | ns   |

TBD = To be determined.

#### **CONTROL TIMING DIAGRAMS**

## IRQ RESPONSE (INPUT MODES 1 AND 3)

CA2/CB2 DELAY (OUTPUT MODE 0)

#### CA2/CB2 DELAY (OUTPUT MODE 1)

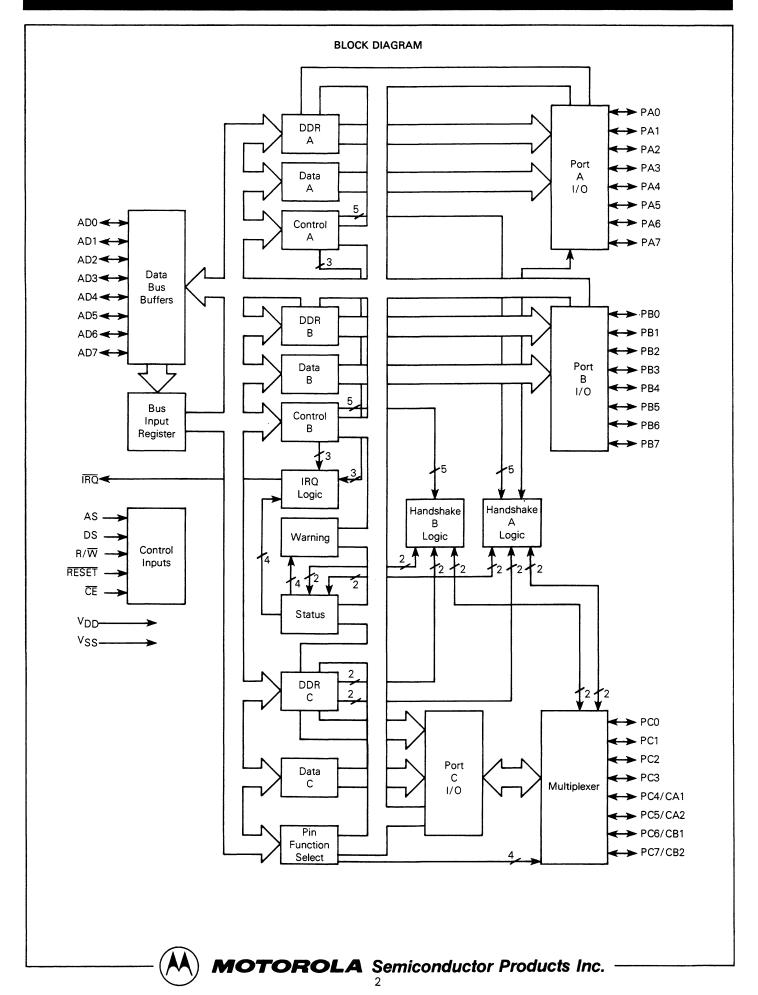

#### GENERAL DESCRIPTION

The MC146823, CMOS parallel interface (CPI), contains 24 individual bidirectional I/O lines configured in three 8-bit ports. The 15 internal registers, which control the mode of operation and contain the status of the port pins, are accessed via an 8-bit multiplexed address/data bus. The lower four address bits (AD0-AD3) of the multiplexed address bus determine which register is to be accessed (see Figure 1). The four address bits (AD4, AD5, AD6, and AD7) must be separately decoded to position this memory map within each 256 byte address space available via the 8-bit multiplexed address bus. For more detailed information refer to REGISTER DESCRIPTION.

FIGURE 1 - REGISTER ADDRESS MAP

| 0 | Port A Data, Clear CA1 Interrupt        | P1DA |

|---|-----------------------------------------|------|

| 1 | Port A Data, Clear CA2 Interrupt        | P2DA |

| 2 | Port A Data                             | PDA  |

| 3 | Port B Data                             | PDB  |

| 4 | Port C Data                             | PDC  |

| 5 | Not Used                                | _    |

| 6 | Data Direction Register for Port A      | DDRA |

| 7 | Data Direction Register for Port B      | DDRB |

| 8 | Data Direction Register for Port C      | DDRC |

| 9 | Control Register for Port A             | CRA  |

| Α | Control Register for Port B             | CRB  |

| В | Pin Function Select Register for Port C | FSR  |

| С | Port B Data, Clear CB1 Interrupt        | P1DB |

| D | Port B Data, Clear CB2 Interrupt        | P2DB |

| Ε | Handshake/Interrupt Status Register     | HSR  |

| F | Handshake Over-Run Warning Register     | HWR  |

The CPI is implemented with the MOTEL circuit which allows direct interface with either of the two major multiplexed microprocessor bus types. A detailed description of the MOTEL circuit is provided in the **MOTEL** section.

Three data direction registers (DDRs), one for each port, determine which pins are outputs and which are inputs. A logic zero on a DDR bit configures its associated pin as an input; and a logic one configures the pin as an output. Upon reset, the DDRs are cleared to logic zero to configure all port pins as inputs.

Actual port data may be read or written via the port data registers (PDA, PDB, and PDC). Ports A and B each have two additional data registers (P1DA and P2DA — P1DB and P2DB) which are used to clear the associated handshake/interrupt status register bits (HSA1 and HSA2 — HSB1 and HSB2), respectively. Port A may also be configured as an 8-bit latch when used with CA1. Reset has no effect on the contents of the port data registers. Users are advised to initialize the port data registers before changing any port pin to an output.

Four pins on port C (PC4/CA1, PC5/CA2, PC6/CB1, and PC7/CB2) may additionally be programmed as handshake lines for ports A and B via the port C function select register (FSR). Both ports A and B have one input-only line and one bidirectional handshake line each associated with them. The handshake lines may be programmed to perform a variety of tasks such as interrupt requests, setting flags, latching data, and data transfer requests and/or acknowledgements. The handshake functions are programmed via control registers A and B (CRA and CRB). Additional information may be found in PIN DESCRIPTIONS, REGISTER DESCRIPTION, or HANDSHAKE OPERATION.

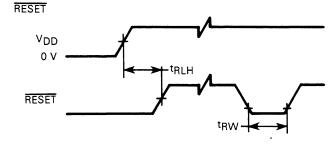

#### **MOTEL**

The MOTEL circuit is a concept that permits the MC146823 to be directly interfaced with different types of multiplexed bus microprocessors without any additional external logic. For a more detailed description of the multiplexed bus, see MULTIPLEXED BIDIRECTIONAL ADDRESS/DATA BUS (AD0-AD7). Most multiplexed microprocessors use one of two synchronous buses to interface peripherals. One bus was originated by Motorola in the MC6803 and the other by Intel in the 8085.

The MOTEL circuit (for MOTorola and intEL bus) is built into peripheral and memory ICs to permit direct connection to either type of bus. A functional diagram of the MOTEL circuit is shown in Figure 2.

FIGURE 2 - FUNCTIONAL DIAGRAM OF MOTEL CIRCUIT

The microprocessor type is automatically selected by the MOTEL circuit through latching the state of the DS/ $\overline{RD}$  pin with AS/ALE. Since DS is always low during AS and  $\overline{RD}$  is always high during ALE, the latch automatically indicates with which type microprocessor bus it is interfaced.

#### PIN DESCRIPTIONS

The following paragraphs contain a brief description of the input and output pins. References (if applicable) are given to other paragraphs that contain more detail about the function being performed.

# MULTIPLEXED BIDIRECTIONAL ADDRESS/DATA BUS (AD0-AD7)

Multiplexed bus processors save pins by presenting the address during the first portion of the bus cycle and using the same pins during the second portion of the bus cycle for data. Address-then-data multiplexing does not slow the access time of the MC146823 since the bus reversal from address to data is occurring during the internal register access time.

The address must be valid tasl prior to the fall of AS/ALE at which time the MC146823 latches the address present on the AD0-AD3 pins. Valid write data must be presented and held stable during the latter portion of the DS or  $\overline{\text{WR}}$  pulses. In a read cycle, the MC146823 outputs eight bits of data during the latter portion of the DS or  $\overline{\text{RD}}$  pulses, then ceases driving the bus (returns the output drivers to high impedance) tDHR hold time after DS falls in the Motorola case of MOTEL or  $\overline{\text{RD}}$  rises in the other case.

#### ADDRESS STROBE (AS)

The address strobe input pulse serves to demultiplex the bus. The falling edge of AS or ALE causes the addresses AD0-AD3 to be latched within the MC146823. The automatic MOTEL circuit in the MC146823 also latches the state of the DS pin with the falling edge of AS or ALE.

### DATA STROBE OR READ (DS)

The DS input pin has two interpretations via the MOTEL circuit. When generated by a Motorola microprocessor, DS is a positive pulse during the latter portion of the bus cycle, and is variously called DS (data strobe), E (enable), or phase 2 (phase 2 clock). During read cycles, DS or  $\overline{\text{RD}}$  signifies the time that the CPI is to drive the bidirectional bus. In write cycles, the trailing edge of DS or rising edge of  $\overline{\text{WR}}$  causes the parallel interface to latch the written data present on the bidirectional bus.

The second MOTEL interpretation of DS is that of  $\overline{\text{RD}}$ , MEMR, or I/OR originating from the competitor's microprocessor. In this case, DS identifies the time period when the parallel interface drives the bus with read data. This interpretation of DS is also the same as an output-enable signal on a typical memory.

The MOTEL circuit, within the MC146823, latches the state of the DS pin on the falling edge of AS/ALE. When the Motorola mode of MOTEL is desired DS must be low during AS/ALE, which is the case with the Motorola multiplexed bus microprocessors. To insure the competitor mode of MOTEL, the DS pin must remain high during the time AS/ALE is high.

#### READ/WRITE (R/W)

The MOTEL circuit treats the  $R/\overline{W}$  input pin in one of two ways. First, when a Motorola microprocessor is connected,  $R/\overline{W}$  is a level which indicates whether the current cycle is a read or write. A read cycle is indicated with a high level on  $R/\overline{W}$  while DS is high, whereas a write cycle is a low on  $R/\overline{W}$  while DS is high.

The second interpretation of R/ $\overline{W}$  is as a negative write pulse,  $\overline{WR}$ ,  $\overline{MEMW}$ , and  $\overline{I}/\overline{OW}$  from competitor's microprocessors. The MOTEL circuit in this mode gives the R/ $\overline{W}$  pin the same meaning as the write ( $\overline{W}$ ) pulse on many generic RAMs

### CHIP ENABLE (CE)

The  $\overline{\text{CE}}$  input signal must be asserted (low) for the bus cycle in which the MC146823 is to be accessed.  $\overline{\text{CE}}$  is not latched and must be stable prior to and during DS (in the Motorola case of MOTEL) and prior to and during  $\overline{\text{RD}}$  and  $\overline{\text{WR}}$  (in the other MOTEL case). Bus cycles which take place without asserting  $\overline{\text{CE}}$  cause no actions to take place within the MC146823. When  $\overline{\text{CE}}$  is high, the multiplexed bus output is in a high-impedance state.

When  $\overline{\text{CE}}$  is high, all data, DS, and R/ $\overline{\text{W}}$  inputs from the microprocessor are disconnected within the MC146823. This permits the MC146823 to be isolated from a powered-down microprocessor.

#### RESET (RESET)

The RESET input pin is an active-low line that is used to restore all register bits, except the port data register bits, to logical zeros. After reset, all port lines are configured as inputs and no interrupt or handshake lines are enabled.

## INTERRUPT REQUEST (IRQ)

The  $\overline{\text{IRQ}}$  output line is an open-drain active-low signal that may be used to interrupt the microprocessor with a service request. The "open-drain" output allows this and other interrupt request lines to be wire ORed with a pullup resistor. The  $\overline{\text{IRQ}}$  line is low when bit 7 of the status register is high. Bit 7 (IRQF) of the handshake/interrupt status register (HSR) is set if any enabled handshake transition occurs; and its associated control register bit is set to allow interrupts. Refer to INTERRUPT DESCRIPTION or HANDSHAKE OPERATION for additional information.

## PORT A, BIDIRECTIONAL I/O LINES (PA0-PA7)

Each line of port A, PA0-PA7, is individually programmable as either an input or output via its data direction register (DDRA). An I/O pin is an input when its corresponding DDR bit is a logic zero and an output when the DDR bit is a logic one. See Figure 3 for typical I/O circuitry and Table 1 for I/O operation.

There are three data registers associated with port A: PDA, P1DA, and P2DA. P1DA and P2DA are accessed when certain handshake activity is desired. See **HANDSHAKE OPERATION** for more information.

Data written to the port A data register, PDA, is latched into the port A output latch regardless of the state of the DDRA. Data written to P1DA or P2DA is ignored and has no affect upon the output data latch or the I/O lines. An MPU read of port bits programmed as outputs reflect the last value written to the PDA register. Port A pins programmed as inputs may be latched via the handshake line PC4/CA1 (see

#### FIGURE 3 - TYPICAL PORT I/O CIRCUITRY Data Direction Register Bit Latched To 1/0 Output Output And Pin Data Bit From CPU Dutpu<sup>r</sup> Reg. Bit Input 1/0 Pin

TABLE 1 - PORT DATA REGISTER ACCESSES (ALL PORTS)

| R/W | DDR<br>Bit | Results                                                                   |

|-----|------------|---------------------------------------------------------------------------|

| 0   | 0          | The I/O pin is in input mode. Data is written into the output data latch. |

| 0   | 1          | Data is written into the output data latch and output to the I/O pin.     |

| 1   | 0          | The state of the I/O pin is read.                                         |

| 1   | 1          | The I/O pin is in an output mode. The output data latch is read.          |

HANDSHAKE OPERATION) and latched input data may be read via any of the three port A data registers. If the port A input latch feature is not enabled, an MPU read of any port A data register reflects the current status of the port A input pins if the corresponding DDRA bits equal zero. Reset has no effect upon the contents of the port A data register; however, all pins will be placed in the input mode (all DDRA bits forced to equal zero) and all handshake lines will be disabled.

#### PORT B BIDIRECTIONAL I/O LINES (PB0-PB7)

Each line of port B, PB0-PB7, is individually programmable as either an input or an output via its data direction register (DDRB). An I/O pin is an input when its corresponding DDR bit is a logic zero and an output when the DDR bit is a logic one.

There are three data registers associated with port B: PDB, P1DB, and P2DB. PDB is used for simple port B data reads and writes. P1DB and P2DB are accessed when certain handshake activity is desired. See **HANDSHAKE OPERATION** for more information.

Data written to PDB or P1DB data register is latched into the port B output latch regardless of the state of the DDRB. An MPU read of port bits programmed as outputs reflect the last value written to a port B data register. An MPU read of any port B register reflects the current status of the input pins whose DDRB bits equal zero. Reset has no effect upon the contents of the port B data register; however, all pins will be placed in the input mode (all DDRB bits forced to equal zero) and all handshake lines will be disabled.

### PORT C, BIDIRECTIONAL I/O LINES (PC0-PC3)

Each line of port C, PCO-PC3, is individually programmable as either an input or an output via its data direction register (DDRC). An I/O pin is an input when its corresponding DDR bit is a logic zero and an output when the DDR bit is a logic one. Port C data register (PDC) is used for simple port C data reads and writes.

Data written into PDC is latched into the port C data latch regardless of the state of the DDRC. An MPU read of port C bits programmed as outputs reflect the last value written to the PDC register. An MPU read of the port C register reflects the current status of the corresponding input pins whose DDRC bits equal zero. Reset has no effect upon the contents of the port C data register; however, all pins will be placed in the input mode (all DDRC bits forced to equal zero) and all handshake lines will be disabled.

## PORT C BIDIRECTIONAL I/O LINE OR PORT A INPUT HANDSHAKE LINE (PC4/CA1)

This line may be programmed as either a simple port C I/O line or as a handshake line for port A via the port C function select register (FSR). If programmed as a port C I/O pin, PC4/CA1 performs as described in the PC0-PC3 pin description. If programmed as a port A handshake line, PC4/CA1 performs as described in HANDSHAKE OPERATION.

## PORT C BIDIRECTIONAL I/O LINE OR PORT A BIDIRECTIONAL HANDSHAKE LINE (PC5/CA2)

This line may be programmed as either a simple port C I/O line or as a handshake line for port A via the port C function select register (FSR). If programmed as a port C I/O pin, PC5/CA2 performs as described in the PC0-PC3 pin description. If programmed as a port A handshake line, PC5/CA2 performs as described in **HANDSHAKE OPERATION**.

## PORT C BIDIRECTIONAL I/O LINE OR PORT B INPUT HANDSHAKE LINE (PC6/CB1)

This line may be programmed as either a simple port C I/O line or as a handshake line for port B via the port C function select register (FSR). If programmed as a port C I/O pin, PC6/CB1 performs as described in the PC0-PC3 pin description. If programmed as a port B handshake line, PC6/CB1 performs as described in HANDSHAKE OPERATION.

MOTOROLA Semiconductor Products Inc.

## PORT C BIDIRECTIONAL I/O LINE OR PORT B BIDIRECTIONAL HANDSHAKE LINE (PC7/CB2)

This line may be programmed as either a simple port C I/O line or as a handshake line for port B via the port C function select register (FSR). If programmed as a port C I/O line, PC7/CB2 performs as described in the PC0-PC3 pin description. If programmed as a port B handshake line, PC7/CB2 performs as described in HANDSHAKE OPERATION.

#### HANDSHAKE OPERATION

Up to four port C pins can be configured as handshake lines for ports A and B (one input-only and one bidirectional line for each port) via the port C function select register (FSR). The direction of data flow for the two bidirectional handshake lines (CA2 and CB2) is determined by bits 5 and 7, respectively, of the port C data direction register (DDRC). Actual handshake operation is defined by the appropriate port control register (CRA or CRB).

The control registers allow each handshake line to be programmed to operate in one of four modes. CA2 and CB2 each have four input and four output modes. For detailed information, see Tables 2 and 3.

A summary of the handshake modes is given in the input and output sections that follow. All handshake activity is disabled by reset.

#### **INPUT**

Handshake lines programmed as inputs operate in any of four different modes as defined by the control registers (see Table 2). A bit in the handshake/interrupt status register (HSR) is set to a logic one on an active transition of any handshake line programmed as an input. Modes 0 and 1 define a negative transition as active; modes 2 and 3 define a positive transition as active. If modes 1 or 3 are selected on any input handshake line then the active transition of that line results in the IRQF bit of the HSR being set to a logic one and causes the interrupt line (IRQ) to go low. IRQ is released by clearing the HSR bits that are input handshake lines which have interrupts enabled.

If an active transition occurs while the associated HSR bit is set to a logic one, the corresponding bit in the handshake warning register (HWR) is set to a logic one indicating that service of at least one active transition was missed. An HWR bit is cleared to a logic zero by first accessing the appropriate port data register, to clear the appropriate HSR status bit, followed by a read of the HWR.

TABLE 2 - INPUT HANDSHAKE MODES

| Mode | Control<br>Register Bits* | Active<br>Edge | Status Bit<br>In HSR     | ĪRQ Pin                                                   |

|------|---------------------------|----------------|--------------------------|-----------------------------------------------------------|

| 0    | 00                        | – Edge         | Set high on active edge. | Disabled                                                  |

| 1    | 01                        | – Edge         | Set high on active edge. | Goes low when corresponding status flag in HSR goes high. |

| 2    | 10                        | + Edge         | Set high on active edge. | Disabled                                                  |

| 3    | 11                        | + Edge         | Set high on active edge. | Goes low when corresponding status flag in HSR goes high. |

<sup>\*</sup>Cleared to logic zero on reset.

TABLE 3 — OUTPUT HANDSHAKE LINES (CA2 AND CB2 ONLY)

| Mode | Control<br>Register<br>CRA(B)<br>Bits<br>3 and 4* | Handshake Line Set High                                                        | Handshake Line Cleared Low                                                                                                     | Default<br>Level |

|------|---------------------------------------------------|--------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|------------------|

| 0    | 00                                                | Handshake set high on active transition of CA1 input.                          | Read of P1DA or a read of P2DA while HSA1 is cleared.                                                                          | High             |

|      |                                                   | Handshake set high on active transition of CB1 input.                          | Write of port B P1DB or write of P2DB while HSB1 is cleared.                                                                   |                  |

| 1    | 01                                                | High on the first positive (negative) transition of AS while CA2 (CB2) is low. | Low on the first positive (negative) transition on AS following a read (write) of port A(B) data registers P1DA(B) or P2DA(B). | High             |

| 2    | 10                                                | Never                                                                          | Always                                                                                                                         | Low              |

| 3    | 11                                                | Always                                                                         | Never                                                                                                                          | High             |

<sup>\*</sup>Cleared to logic zero on reset.

#### INPUT LATCH

Port A input-only handshake line (PC4/CA1) can be programmed to function as a latch enable for port A input data via CA1 LE (bit 2 of CRA). If CA1 LE is programmed to a logic one, an active transition of PC4/CA1 will latch the current status of the port A input pins into all three port A data registers (PDA, P1DA, and P2DA). When CA1 LE is enabled, port A and PC4/CA1 function as an 8-bit transparent latch; that is, if the HSA1 bit in the HSR is a logic zero then a read of any port A register reflects the current state of the port A input pins and corresponding bits of the output data latch for port A output pins. If HSA1 is a logic one, a read of any port A data register reflects the state of the port A input pins when HSA1 was set and the corresponding bits of the port A output data latch for port A output pins.

Further transitions of PC4/CA1 result only in setting the HWA1 bit in the HWR and do not relatch data into the port A registers. Latched data is released only by clearing HSA1 in the HSR to a logic zero (HSA1 is cleared by reading P1DA).

#### **OUTPUT**

Each bidirectional handshake line programmed as an output by the DDRC operates in one of four modes as described in Table 3. Modes 2 and 3 force the output handshake line to reflect the state of bit 4 in the appropriate control register.

In modes 0 and 1, PC5/CA2 is forced low during the cycle following a read of P1DA or a read of P2DA while HSA1 is cleared. PC7/CB2 is forced low during the cycle following a write to P1DB or a write to P2DB while HSB1 is cleared. Because of these differences, port A is the preferred input port and port B is the preferred output port.

In mode 0, PC5/CA2 (PC7/CB2) is set high by an active transition of PC4/CA1 (PC6/CB1). In mode 1, PC5/CA2 (PC7/CB2) is set high in the cycle following the cycle in which PC5/CA2 (PC7/CB2) goes low. Mode 1 forces a low-going pulse on PC5/CA2 (PC7/CB2) following a read (write) of P1DA (P1DB) or P2DA (P2DB) that is approximately one cycle time wide.

When entering an output handshake mode for the first time after a reset, the handshake line outputs the default level as listed in Table 3.

#### INTERRUPT DESCRIPTION

The MC146823 allows an MPU interrupt request ( $\overline{\text{IRQ}}$  low) via the input handshake lines. The input handshake line, operating in modes 1 or 3 as defined by the control registers

(CRA and CRB), causes  $\overline{\text{IRQ}}$  to go low when IRQF (interrupt flag) in the HSR is set to a logic one.  $\overline{\text{IRQ}}$  is released when IRQF is cleared. See **Handshake/Interrupt Status Register** under **REGISTER DESCRIPTION** for additional information.

#### REGISTER DESCRIPTION

The MC146823 has 15 registers (see Figure 1) which define the mode of operation and status of the port pins. The following paragraphs describe these registers.

#### Register Names:

Control Register A (CRA) Control Register B (CRB)

#### Register Addresses:

\$9 (CRA) \$A (CRB)

#### Register Bits:

|     | 7 | 6 | 5 | 4 3         | 2         | 1 0         |

|-----|---|---|---|-------------|-----------|-------------|

| \$9 | Х | х | Х | CA2<br>Mode | CA1<br>LE | CA1<br>Mode |

| \$A | × | х | × | CB2<br>Mode | х         | CB1<br>Mode |

#### Purpose:

These two registers control the handshake and interrupt activity for those pins defined as handshake lines by the port C function select register (FSR).

#### Description:

CA2 and CB2 are programmed as inputs or outputs via the associated DDRC bits. Each handshake line is controlled by two mode bits. Bit 2 of CRA enables the Port A latch for an active CA1 transition. Table 2 describes the input handshake modes (CA1, CB1, CA2, CB2) and Table 3 describes the output handshake modes for CA2 and CB2.

#### Register Names:

Port A Data Registers (PDA, P1DA, P2DA)

#### Register Addresses:

\$2 (PDA), \$0 (P1DA), \$1 (P2DA)

#### Register Bits:

| 7     | 6     | 5     | 4     | _ 3   | 2     | 1     | 0     |

|-------|-------|-------|-------|-------|-------|-------|-------|

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

#### Purpose:

These three registers serve different purposes. PDA is used to read input data and latch data written to the port A output pins. P1DA and P2DA are used to read input data and to affect handshake and status activity for PC4/CA1 and PC5/CA2. If enabled, port A input data may be latched into the three port A data registers on an active PC4/CA1 transition as described in HANDSHAKE OPERATION.

#### Description:

Data written into PDA is latched into the port A output latch (see Figure 3) regardless of the state of DDRA. Output pins, as defined by DDRA, assume the logic levels of the corresponding bits in the PDA output latch. The PDA output latch allows the user to read the state of the port A output data. If the input latch is not enabled, a read of any port A data register reflects the current state of the port A input pins as defined by DDRA and the contents of the output latch for output pins. Writes into P1DA or P2DA have no effect upon the output pins or the output data latch. Users are recommended to initialize the port A output latch before changing any pin to an output via the DDRA.

MPU accesses of P1DA or P2DA are primarily used to affect handshake and status activity. A summary of the effects on the status and warning bits of port A data register accesses is given in Table 4. For more information, see HANDSHAKE OPERATION and Control Register A (CRA) under REGISTER DESCRIPTION. Reset has no effect upon the contents of any port A data register.

#### Register Names:

Port B Data Registers (PDB, P1DB, P2DB)

#### Register Addresses:

\$3 (PDB), \$C(P1DB), \$D (P2DB)

#### Register Bits:

| 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|-------|-------|-------|-------|-------|-------|-------|-------|

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

#### Purpose:

These three registers serve different purposes. The Port B data registers are used to read input data and to latch data written to the port B output pins. Writes to PDB and P1DB affect the contents of the output data latch while writes to P2DB do not affect the output data latch. P1DB and P2DB accesses additionally affect handshake and status activity for PC6/CB1 and PC7/CB2.

#### Description:

Data written into PDB and P1DB port B registers is latched into the port B output latch (see Figure 3) regardless of the state of DDRB. Output pins, as defined by DDRB, assume the logic levels of the corresponding bits in the port B output latch. Reads of any port B data registers reflect the contents of the output data latch for output pins and the current state of the input pins (as determined by DDRB). Users are recommended to initialize the port B output latch before changing any pin to an output via the DDRB.

MPU accesses of P1DB or P2DB are primarily used to affect handshake and status activity. A summary of the effects on status and warning register bits of port B data register accesses is given in Table 5. For more information, see HANDSHAKE OPERATION or Control Register B (CRB) under REGISTER DESCRIPTION. Reset has no effect upon the contents of any port B data register.

TABLE 4 — SUMMARY OF EFFECTS ON HANDSHAKE STATUS, WARNING BITS, AND OUTPUT LATCH BY PORT A DATA REGISTER ACCESSES

| Register |                                     |                                |                                                              | Outpu | t Latch |

|----------|-------------------------------------|--------------------------------|--------------------------------------------------------------|-------|---------|

| Accessed | HSR Bit                             | HWR Bit                        | Handshake Reaction                                           | Read  | Write   |

| PDA      | None                                | None                           | None                                                         | Yes   | Yes     |

| P1DA     | HSA1 cleared<br>to a logic<br>zero. | HWA1 loaded into buffer latch. | CA2 goes low if output modes 0 or 1 are selected in the CRA. | Yes   | No      |

| P2DA     | HSA2 cleared<br>to a logic<br>zero. | HWA2 loaded into buffer latch. | CA2 goes low if output modes 0 or 1 are selected in the CRA. | Yes   | No      |

## TABLE 5 — SUMMARY OF EFFECTS ON HANDSHAKE STATUS, WARNING BITS, AND OUTPUT LATCH BY PORT B DATA REGISTER ACCESSES

| Register |                                     |                                |                                                              | Output | Latch |

|----------|-------------------------------------|--------------------------------|--------------------------------------------------------------|--------|-------|

| Accessed | HSR Bit                             | HWR Bit                        | Handshake Reaction                                           | Read   | Write |

| PDB      | None                                | None                           | None                                                         | Yes    | Yes   |

| P1DB     | HSB1 cleared<br>to a logic<br>zero. | HWB1 loaded into buffer latch. | CB2 goes low if output modes 0 or 1 are selected in the CRB. | Yes    | Yes   |

| P2DB     | HSB2 cleared<br>to a logic<br>zero. | HWA2 loaded into buffer latch. | CB2 goes low if output modes 0 or 1 are selected in CRB.     | Yes    | No    |

### Register Name:

Port C Data Register (PDC)

#### Register Address:

\$4

#### Register Bits:

| 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|-------|-------|-------|-------|-------|-------|-------|-------|

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

#### Purpose:

The port C data register (PDC) is used to read input data and to latch data written to the output pins.

#### Description:

Data is written into the port C output latch (see Figure 3) regardless of the state of DDRC. Any port C pin defined as a handshake line by the port C function select register (FSR) is not affected by PDC. Output pins, as defined by DDRC, assume logic levels of the corresponding bits in the port C output latch. A read of PDC reflects the contents of the output latch for output pins and the current state of the input pins (as reflected in the DDRC). Reset has no effect upon the contents of PDC. Users are recommended to initialize the port C output data latch before changing any pin to an output via the DDRC.

## Register Name:

Data Direction Register for Port A (B) (C)

#### Register Address:

\$6 (\$7) (\$8)

#### Register Bits:

| 7_    | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|-------|-------|-------|-------|-------|-------|-------|-------|

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

#### Purpose:

Each of the three data direction registers (DDRA, DDRB, and DDRC) define the direction of data flow of the port pins for ports A<sub>J</sub> B, and C.

#### Description:

A logic zero in a DDR bit places the corresponding port pin in the input mode. A logic one in a DDR bit places the corresponding pin in the output mode. Any port C pins defined as bidirectional handshake lines also use the port C DDR (DDRC). Input-only handshake lines are not affected by DDRC. Reset clears all DDR bits to logic zero configuring all port pins as inputs. The DDRs have no write-inhibit control over the port data output latches. Data may be written to the port data registers even though the pins are configured as inputs.

#### Register Name:

Port C Pin Function Select Register (FSR)

#### Register Address:

\$В

#### Register Bits:

| 7    | 6    | 5    | 4    | 3  | 2  | 1  | 0  |  |

|------|------|------|------|----|----|----|----|--|

| CFB2 | CFB1 | CFA2 | CFA1 | XX | XX | XX | XX |  |

#### Purpose:

The port C pin function select register defines whether the multifunction port C pins are to operate as "normal" port C lines or as handshake lines.

## Description:

A logic zero in any FSR bit defines the corresponding port C pin as a "normal" I/O pin. A logic one in any valid FSR bit defines the corresponding port C pin as a handshake line. Pins defined as handshake lines function according to the contents of control register A (CRA) or control register B (CRB). The port C data direction register (DDRC) is valid regardless of FSR contents for all pins except PC4/CA1 and PC6/CB1. Transitions on port C pins not defined as handshake pins do not effect the handshake/interrupt status register. Reset clears all FSR bits to a logic zero. Users are recommended to initialize the data direction and control registers before modifying the FSR.

#### Register Name:

Handshake/Interrupt Status Register (HSR)

#### Register Address:

\$E

#### Register Bits:

| 7    | 6  | _ 5 | 4  | 3    | 2    | 1    | 0    |

|------|----|-----|----|------|------|------|------|

| IRQF | XX | XX  | XX | HSB2 | HSA2 | HSB1 | HSA1 |

#### Purpose:

The handshake interrupt status register is a read-only flag register that may be used during a polling routine to determine if any enabled input handshake transition, as defined by the control register (CRA and CRB), has occurred.

### Description:

If an enabled input handshake transition occurs then the appropriate HSR bit (HSB2, HSA2, HSB1, or HSA1) is set. The IRQ flag bit (bit 7, IRQF) is set when one or more of the HSR bits 0-3 and their corresponding control register bits are set to a logic one as shown in the following equation:

The numbers in ( ) indicate which bit in the control register enables the interrupt.

Handshake/interrupt status register bits are cleared by accessing the appropriate port data register. The following table lists the HSR bit and the port data register that must be accessed to clear the bit.

| To Clear | Access   |

|----------|----------|

| HSR Bit  | Register |

| HSB2     | P2DB     |

| HSA2     | P2DA     |

| HSB1     | P1DB     |

| HSA1     | P1DA     |

Reset clears all handshake/interrupt status register bits to a logic zero.

#### Register Name:

Handshake Warning Register (HWR)

#### Register Address:

\$F

#### Register Bits:

| 7  | 6  | 5  | 4  | 3    | 2    | 1    | 0    |  |

|----|----|----|----|------|------|------|------|--|

| XX | XX | XX | XX | HWB2 | HWA2 | HWB1 | HWA1 |  |

#### Purpose:

The warning register is a read-only flag register that may be used to determine if a second attempt to set a handshake/interrupt status register bit has been made before the original had been serviced.

#### Description:

Each bit in the handshake/interrupt status register, except IRQF, has a corresponding bit in the handshake warning register. If an attempt is made to set a bit in the handshake/interrupt status register that is already set, then the corresponding bit in the handshake warning register is also set. An attempt is the occurrence of any enabled input handshake transition as defined by the control registers.

A handshake warning register bit is cleared by first reading the appropriate data register then reading the handshake warning register. Reading the data register (either P1DA, P2DA, P1DB, or P2DB) loads a buffer latch with the proper bit in the handshake warning register (HWA1, HWA2, HWB1, and HWB2, respectively). The next read of the handshake warning register clears the appropriate bit without affecting the other three handshake warning register bits. The upper four bits, HWR4-HWR7, always read as logic zeros. If a port data register is not read before reading the handshake warning register, then the handshake warning register bits will remain unaffected. Reset clears all HWR bits to a logic zero.

Recommended status register handling sequence:

1. Read status register

(User determines which if any enabled handshake transition occurred)

2. Read/write port data indicated by status register

(Clears associated status bit and latches appropriate warning register bit in the buffer latch) (Latched warning bit is cleared and the remaining bits are unaf-

3. Read warning register

fected)

Motorola reserves the right to make changes to any products herein to improve reliability, function or design. Motorola does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others.

**MOTOROLA** Semiconductor Products Inc. -

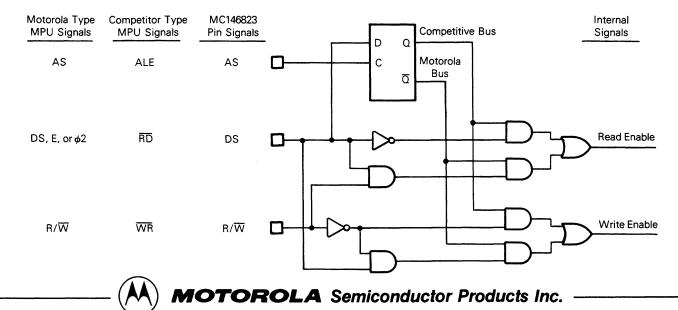

#### TYPICAL INTERFACING

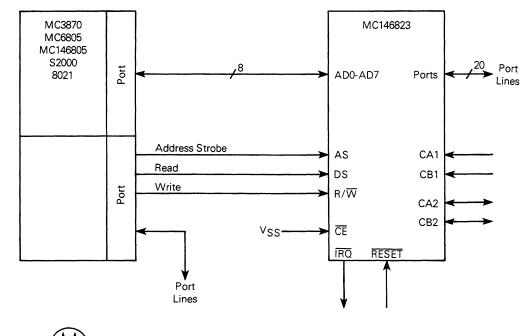

The MC146823 is best suited for use with microprocessors which generate an address-then-data-multiplexed bus. Figure 4 shows the MC146823 in a typical CMOS system that uses the MC146805E2 CMOS MPU. Other multiplexed microprocessors can be used as easily.

A single-chip microcomputer (MCU) may be interfaced with 11 port lines as shown in Figure 5. This interface also requires some software overhead to gain up to 13 additional I/O lines and the MC146823 handshake lines.

#### FIGURE 4 — A TYPICAL CMOS MICROPROCESSOR SYSTEM

#### FIGURE 5 - MC146823 INTERFACED WITH THE PORTS OF A TYPICAL SINGLE-CHIP MICROCOMPUTER

**OTOROLA** Semiconductor Products Inc.

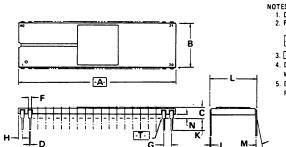

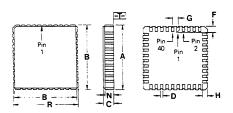

#### PACKAGE DIMENSIONS

- NOTES:

1. DIMENSION A: IS DATUM.

2. POSITIONAL TOLERANCE FOR LEADS:

## ⊕ 0.25 (0.010) ⊚ T A⊚

- 3. T. IS SEATING PLANE.

- 4. DIMENSION "L" TO CENTER OF LEADS WHEN FORMED PARALLEL.

| 5. | DIMENSIONING AND TOLERANCING |

|----|------------------------------|

|    | PER ANSI Y14.5, 1973.        |

#### **L SUFFIX**

CERAMIC PACKAGE

CASE 715-05

|     | MILLIMETERS |       | INCHES    |       |

|-----|-------------|-------|-----------|-------|

| DIM | MIN         | MAX   | MIN       | MAX   |

| A   | 50.29       | 51.31 | 1.980     | 2.020 |

| В   | 14.63       | 15.49 | 0.576     | 0.610 |

| C   | 3.05        | 4.32  | 0.120     | 0.170 |

| D   | 0.38        | 0.53  | 0.015     | 0.021 |

| F   | 0.76        | 1.40  | 0.030     | 0.055 |

| G   | 254 BSC     |       | 0.100 BSC |       |

| J   | 0.20        | 0.33  | 0.008     | 0.013 |

| K   | 2.54        | 4.19  | 0.100     | 0.165 |

| L   | 14.99       | 15.65 | 0.590     | 0.616 |

| M   | -           | 100   | -         | 100   |

| N   | 1.02        | 1.52  | O DAD     | 0.060 |

NOTES:

1. POSITIONAL TOLERANCE OF LEADS (D), SHALL BE WITHIN 0.25 mm (0.010) AT MAXIMUM MATERIAL CONDITION, IN RELATION TO SEATING PLANE AND EACH OTHER.

2. DIMENSION L TO CENTER OF LEADS WHEN FORMED PARALLEL.

3. DIMENSION B DOES NOT INCLUDE MOLD FLASH.

P SUFFIX PLASTIC PACKAGE

CASE 711-01

|     | MILLIMETERS |       | INCHES    |       |

|-----|-------------|-------|-----------|-------|

| DIM | MIN         | MAX   | MIN       | MAX   |

| A   | 51.69       | 52.45 | 2.035     | 2.065 |

| 8   | 13.72       | 14.22 | 0.540     | 0.560 |

| C   | 3.94        | 5.08  | 0.155     | 0.200 |

| 0   | 0.36        | 0.56  | 0.014     | 0.022 |

| F   | 1.02        | 1.52  | 0.040     | 0.060 |

| G   | 2.54 BSC    |       | 0.100 BSC |       |

| H   | 1.65        | 2.16  | 0.065     | 0.085 |

| J   | 0.20        | 0.38  | 0.008     | 0.015 |

| K   | 2.92        | 3.43  | 0.115     | 0.135 |

| L   | 15.24 BSC   |       | 0.600 BSC |       |

| M   | 90          | 150   | 00        | 150   |

| N   | 0.51        | 1.02  | 0.020     | 0.040 |

#### NOTES:

- DIMENSION-A-IS DATUM.

POSITIONAL TOLERANCE

FOR LEADS:

| + | <b>♦</b> 0.25 (0.010) <b>△</b> | T | A ⊛ |

|---|--------------------------------|---|-----|

|---|--------------------------------|---|-----|

- IS SEATING PLANE.

DIMENSION L TO CENTER OF LEADS WHEN FORMED

- PARALLEL.

DIMENSION A AND B

INCLUDES MENISCUS.

### S SUFFIX

CERDIP PACKAGE

CASE 734-03

|     | MILLIMETERS |       | MILLIMETERS INCHES |       |

|-----|-------------|-------|--------------------|-------|

| DIM | MIN         | MAX   | MIN                | MAX   |

| Α   | 51.31       | 53.24 | 2.020              | 2.096 |

| В   | 12.70       | 15.49 | 0.500              | 0.610 |

| C   | 4.06        | 5.84  | 0.160              | 0.230 |

| 0   | 0.38        | 0.56  | 0.015              | 0.022 |

| F   | 1.27        | 1.65  | 0.050              | 0.065 |

| G   | 2.54 BSC    |       | 0.100 BSC          |       |

| J   | 0.20        | 0.30  | 0.008              | 0.012 |

| K   | 3.18        | 4.06  | 0.125              | 0.160 |

| ī   | 15.24 BSC   |       | 0.600 BSC          |       |

| M   | 50          | 150   | 50                 | 150   |

| N   | 0.51        | 1.27  | 0.020              | 0.050 |

#### NOTES:

- 1. DIMENSIONS A & R ARE DATUMS.

- 2. T-IS GAUGE PLANE.

- 2. [-II]S GAUGE PLANE.

3. POSITIONAL TOLERANCE FOR TERMINALS (D): 40 PLACES:

□ □ 0.25 (0.010)

DIMENSIONING AND TOLERANCING PER ANSI Y14.5, 1973.

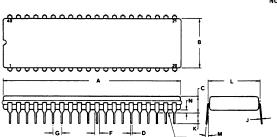

## **Z SUFFIX**

40-PIN CHIP CARRIER

CASE 761-01

|     | MILLIMETERS |       | INCHES |       |

|-----|-------------|-------|--------|-------|

| DIM | MIN         | MAX   | MIN    | MAX   |

| Α   | 11.94       | 12.57 | 0.470  | 0.495 |

| В   | 11.05       | 11.30 | 0.435  | 0.445 |

| C   | 1.60        | 2.08  | 0.063  | 0.082 |

| D   | 0.33        | 0.69  | 0.013  | 0.027 |

| F   | 1.07        | 1.47  | 0.042  | 0.058 |

| G   | 1.02 BSC    |       | 0.040  | BSC   |

| Н   | 0.84        | 1.19  | 0.033  | 0.047 |

| N   | 1.27        | 1.79  | 0.050  | 0.070 |

| R   | 11.94       | 12.57 | 0.470  | 0.495 |

## **MOTOROLA** Semiconductor Products Inc.

3501 ED BLUESTEIN BLVD., AUSTIN, TEXAS 78721 ● A SUBSIDIARY OF MOTOROLA INC.