May 2000

MM145453 Liquid Crystal Display Driver

# MM145453 Liquid Crystal Display Driver General Description

The MM145453 is a monolithic integrated circuit utilizing CMOS metal gate, low threshold enhancement mode devices. The chip can drive up to 33 LCD segments and can be paralleled to increase this number. The chip is capable of driving a  $4\frac{1}{2}$  digit 7-segment display with minimal interface between the display and the data source.

The MM145453 stores display data in latches after it is clocked in, and holds the data until new display data is received.

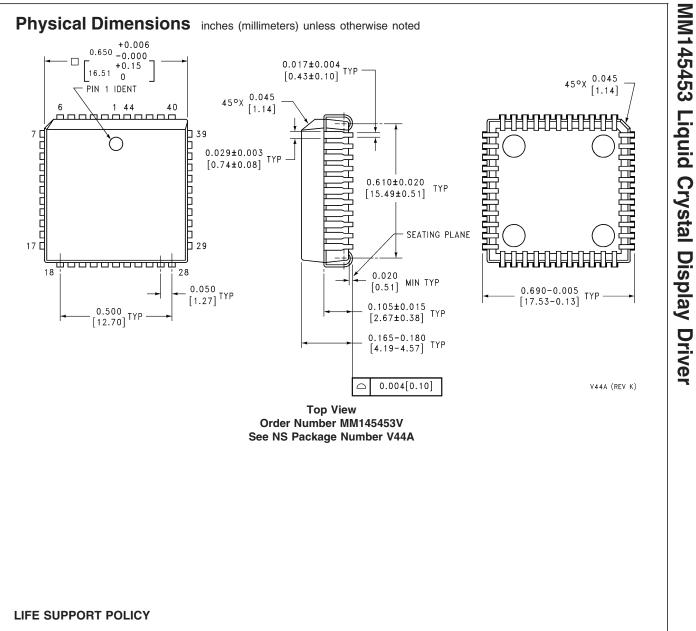

The MM145453 is available in a molded 44 pin surface mount PLCC package. The MM145453 is pin out and functionally compatible with the MC145453.

#### Features

- Serial Data Input

- Wide Power Supply operation

- TTL Compatibility

- Up to 33 LCD Segments

- Alphanumeric or Bar Graph capability

- Cascaded operation capability

- Pin Compatible with MC145453

#### **Applications**

- COPS<sup>™</sup> or microprocessor displays

- Industrial control indicator

- Digital clock, thermometer, counter, voltmeter

- Instrumentation displays

- Remote displays

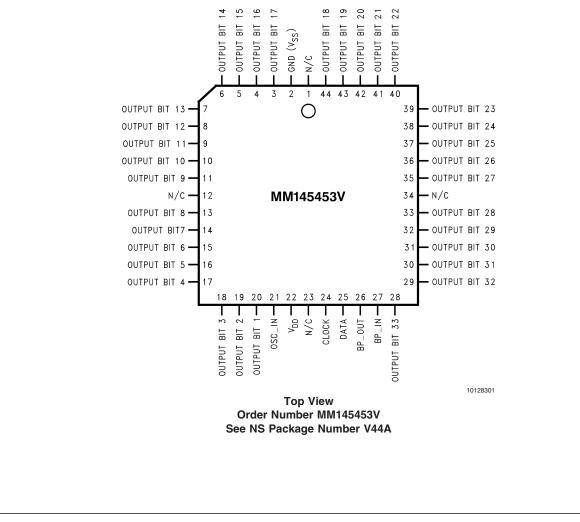

### **Connection Diagram**

#### Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| -0.3V to +10V   |

|-----------------|

|                 |

| -65°C to +150°C |

| 350mW           |

| 300mW           |

|                 |

| Junction Temperature |

|----------------------|

| Lead Temperature     |

| (Soldering, 10s)     |

# Recommended Operating Conditions

+150°C

300°C

| V <sub>DD</sub>       | 3V to 10V     |

|-----------------------|---------------|

| Operating Temperature | –40°C to 85°C |

#### **Electrical Characteristics**

The following specifications apply for  $T_A$  within operation range,  $V_{DD} = 3.0V$  to 10V,  $V_{SS} = 0V$ , unless otherwise specified.

| Parameter                               | Conditions                                             | Min  | Typical | Max   | Units |

|-----------------------------------------|--------------------------------------------------------|------|---------|-------|-------|

| Supply Voltage, V <sub>DD</sub>         |                                                        | 3    |         | 10    | V     |

| Average Supply Current, I <sub>DD</sub> | All Outputs Open, Clock=Gnd,                           |      |         |       |       |

|                                         | Data=Gnd,OSC=Gnd, BP_IN @ 32Hz                         |      |         |       |       |

|                                         | $V_{DD} = 5V$                                          |      |         | 10    | μA    |

|                                         | V <sub>DD</sub> = 10V                                  |      |         | 40    | μA    |

| Input Logical '0' Voltage, VIL          | V <sub>DD</sub> = 3V                                   |      |         | 0.4   | V     |

|                                         | $V_{DD} = 5V$                                          |      |         | 0.8   | V     |

|                                         | V <sub>DD</sub> = 10V                                  |      |         | 0.8   | V     |

| Input Logical '1' Voltage, VIH          | V <sub>DD</sub> = 3V                                   | 2.0  |         |       | V     |

|                                         | V <sub>DD</sub> = 5V                                   | 2.0  |         |       | V     |

|                                         | V <sub>DD</sub> = 10V                                  | 8.0  |         |       | V     |

| Segment Sink Current, I <sub>OL</sub>   | $V_{DD}$ = 3V, $V_{OUT}$ = 0.3V                        | -20  | -40     |       | μΑ    |

| Segment Source Current, I <sub>OH</sub> | V <sub>DD</sub> = 3V, V <sub>OUT</sub> = 2.7V          | 20   | 40      |       | μΑ    |

| Backplane Out Sink Current,             | $V_{DD}$ = 3V, $V_{OUT}$ = 0.3V                        | -320 | -500    |       | μA    |

| I <sub>OL</sub>                         |                                                        | -520 | -500    |       |       |

| Backplane Out Source                    | $V_{DD}$ = 3V, $V_{OUT}$ = 2.7V                        | 320  | 500     |       | μA    |

| Current, I <sub>OH</sub>                |                                                        | 520  | 000     |       | μ/ τ  |

| Segment Output Offset                   | Segment Load = 250pF (Note 2)                          |      |         | +/-50 | mV    |

| Voltage                                 |                                                        |      |         |       |       |

| Backplane Output Offset                 | Backplane Load = 8750pF (Note 2)                       |      |         | +/-50 | mV    |

| Voltage                                 |                                                        |      |         |       |       |

| Backplane Out Frequency                 | $R_{OSC_{IN}} = 50 k\Omega, C_{OSC_{IN}} = 0.01 \mu F$ |      | 75      |       | Hz    |

| Clock Input Frequency, $f_{CLOCK}$      | V <sub>DD</sub> = 3V (Notes 2, 3)                      |      |         | 500   | kHz   |

|                                         | V <sub>DD</sub> = 5V (Note 2)                          |      |         | 750   | kHz   |

|                                         | V <sub>DD</sub> = 10V (Note 2)                         |      |         | 1.0   | MHz   |

| Clock Input Duty Cycle                  |                                                        | 40   |         | 60    | %     |

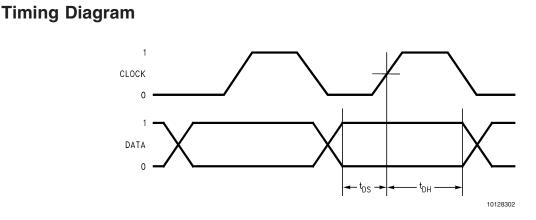

| Data Input Set-Up Time, t <sub>DS</sub> |                                                        | 300  |         |       | ns    |

| Data Input Hold Time, t <sub>DH</sub>   |                                                        | 300  |         |       | ns    |

Note 1: "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. They are not meant to imply that the devices should be operated at these limits. The table of "Electrical Characteristics" specifies conditions of device operation.

Note 2: This parameter is guaranteed (but not production tested) over the operating temperature range and the operating supply voltage range. Not to be used in Q.A. testing.

Note 3: AC input waveform for test purposes:  $t_f \le 20ns$ ,  $t_f \le 20ns$ ,  $f_{CLOCK} = 500kHz$ , Duty Cycle = 50% ±10%

Note 4: Clock input rise time  $(t_r)$  and fall time  $(t_f)$  must not exceed 300ns

www.national.com

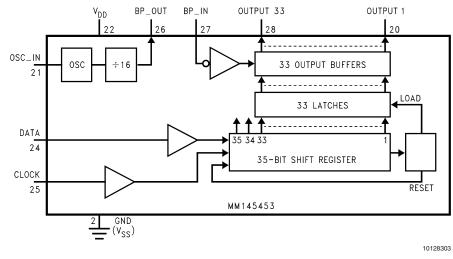

## **Block Diagram**

# **Applications Information**

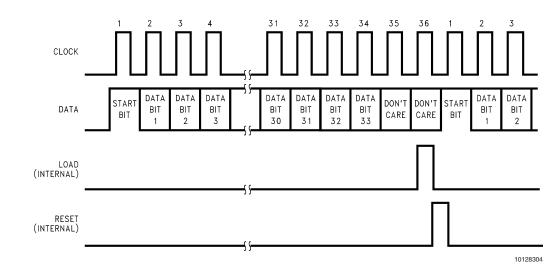

The MM145453 is specifically designed to operate 4½ digit 7-segment displays with minimal interface with the display and data source. Serial data transfer from the data source to the display driver is accomplished with 2 signals, serial Data and Clock. Using a format of a leading "1" followed by the 33 data bits and 2 trailing don't care bits, allows data transfer without the need of an additional Data Load signal. Since the MM145453 does not contain a character generator, the formatting of the segment information must be done prior to inputting the data to the MM145453. The transfer of the 33 data bits is complete at the falling edge of the 36th clock cycle, thus providing non-multiplexed, direct drive to the display. Outputs change only if the serial data bits differ from the previous time.

*Figure 3* shows the data input format. A single start bit of logical '1' precedes the 33 bits of segment data for a total of 34 bits that need to be defined and clocked in. After the 34 bits are clocked in, 2 additional clock cycles are required. At the 36th clock cycle an internal LOAD signal is generated synchronously with the rising edge of the Clock In signal, which loads the 33 bits of segment data in the shift register into the latches. At the falling edge of the 36th clock cycle an

internal RESET signal is generated which clears all the shift registers for the next set of data. The shift registers are static master-slave configuration. There is no clear for the master portion of the first shift register, thus allowing continuous operation. The data during the 35th and 36th clock cycles is "don't care", but setting data to logical '0' for these two clock cycles is the preferred format.

The data input bits map directly to the segment output pins and the display. The MM145453 does not have any format restrictions, as all outputs are controllable.

The MM145453 has an internal oscillator which can generate the required clock signal to drive the LCD back plane. The frequency of the internal oscillator is set by a pull-up resistor ( $R_{OSC\_IN}$ ) connected from the OSC\_IN pin to  $V_{DD}$ , and a capacitor ( $C_{OSC\_IN}$ ) connected from the OSC\_IN pin to Ground. Due to the current sink limitations of the OSC\_IN circuitry, the lowest recommended resistor value for setting the oscillator frequency is 9k $\Omega$ . It will typically take 2 to 4 RC time constants to charge the OSC\_IN pin from near 0V to within 1V of  $V_{DD}$  which is the high threshold voltage point for the OSC\_IN circuitry. An approximate calculation of  $f_{OSC}$  is:

$f_{OSC} = 1 / (l\eta(V_{DD}/1V) X R_{OSC_IN} X C_{OSC_IN})$

# **MM145453**

#### Applications Information (Continued)

A  $R_{OSC\_IN}$  resistor value of  $50 k\Omega$  with a  $C_{OSC\_IN}$  capacitor value of  $0.01 \mu F$  and a  $V_{DD}$  value of 5.00V would produce a typical oscillator frequency ( $f_{OSC}$ ) of about 1200Hz. The  $f_{OSC}$  signal is divided by 16 before it is presented at the BP\_OUT pin. For this example the approximate BP\_OUT frequency will be  $f_{OSC}/16$ , or about 75Hz.

The BP\_IN pin of the MM145453 can be used with an externally supplied signal, provided it has a duty cycle of 50%. Any deviation from a precise 50% duty cycle will result

#### **Input Data Format**

in an offset voltage on the LCD. The use of an external clock allows synchronizing the display drive with AC power, other internal clocks, or DVM integration time to reduce interference from the display. When using an external clock for the back plane drive the internal oscillator should be disabled by connecting the OSC\_IN pin directly to ground. This will prevent possible internal oscillations, and reduce device dissipation.

The MM145453 is a pin out variation of the MM5453. For additional applications information please refer to the MM5453 data sheet.

FIGURE 3.

www.national.com

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### **BANNED SUBSTANCE COMPLIANCE**

National Semiconductor certifies that the products and packing materials meet the provisions of the Customer Products Stewardship Specification (CSP-9-111C2) and the Banned Substances and Materials of Interest Specification (CSP-9-111S2) and contain no "Banned Substances" as defined in CSP-9-111S2.

www.national.com

National Semiconductor Americas Customer Support Center Email: new.feedback@nsc.com Tel: 1-800-272-9959

National Semiconductor Europe Customer Support Center Fax: +49 (0) 180-530 85 86 Email: europe.support@nsc.com Deutsch Tel: +49 (0) 69 9508 6208 English Tel: +44 (0) 870 24 0 2171 Français Tel: +33 (0) 1 41 91 8790 National Semiconductor Asia Pacific Customer Support Center Email: ap.support@nsc.com National Semiconductor Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.