# HD64570 SCA

Serial Communications Adaptor

User's Manual

**HITACHI**

ADE-602-035B Rev. 3.0 August 28, 1998 Hitachi Company or Division

# **Cautions**

- 1. Hitachi neither warrants nor grants licenses of any rights of Hitachi's or any third party's patent, copyright, trademark, or other intellectual property rights for information contained in this document. Hitachi bears no responsibility for problems that may arise with third party's rights, including intellectual property rights, in connection with use of the information contained in this document.

- 2. Products and product specifications may be subject to change without notice. Confirm that you have received the latest product standards or specifications before final design, purchase or use.

- 3. Hitachi makes every attempt to ensure that its products are of high quality and reliability. However, contact Hitachi's sales office before using the product in an application that demands especially high quality and reliability or where its failure or malfunction may directly threaten human life or cause risk of bodily injury, such as aerospace, aeronautics, nuclear power, combustion control, transportation, traffic, safety equipment or medical equipment for life support.

- 4. Design your application so that the product is used within the ranges guaranteed by Hitachi particularly for maximum rating, operating supply voltage range, heat radiation characteristics, installation conditions and other characteristics. Hitachi bears no responsibility for failure or damage when used beyond the guaranteed ranges. Even within the guaranteed ranges, consider normally foreseeable failure rates or failure modes in semiconductor devices and employ systemic measures such as fail-safes, so that the equipment incorporating Hitachi product does not cause bodily injury, fire or other consequential damage due to operation of the Hitachi product.

- 5. This product is not designed to be radiation resistant.

- 6. No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without written approval from Hitachi.

- 7. Contact Hitachi's sales office for any questions regarding this document or Hitachi semiconductor products.

# **Preface**

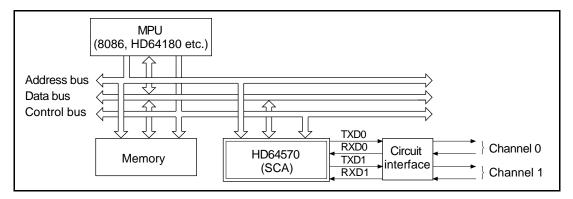

The HD64570 serial communications adaptor (SCA) peripheral chip enables a host microprocessor to perform asynchronous, byte-synchronous, or bit-synchronous serial communication. Its two full-duplex, multiprotocol serial channels support a wide variety of protocols, including frame relay, LAPB, LAPD, bisync, and TMDDCMP. Its built-in direct memory access controller (DMAC) is equipped with a 32-stage FIFO and can execute chained-block transfers. Due to its DMAC and 16-bit bus interface, the SCA supports serial data transfer rates up to 12 Mbits/s without monopolizing the bus, even in full-duplex communication. Other on-chip features of the SCA, including four types of MPU interfaces, a bus arbiter, timers, and an interrupt controller, provide added functionality in a wide range of applications, such as frame relay exchanges/system multiplexes, private branch exchanges, computer networks, workstations, ISDN terminals, and facsimile.

<sup>TM</sup>DDCMP is a trademark of Digital Equipment Corporation.

Rev. 0, 07/98, page i of 11

# **Changes in the Revised Edition**

The following tables list the main differences between this revision and the previous edition (ADE-602-035A). (2nd edition) The changes are marked with stars (\*) in the text.

### **Changes in the Specifications**

| Specifications | Modifications                                                                          |

|----------------|----------------------------------------------------------------------------------------|

| WTR SCA added  | A chip with Wide Temperature Range (–40 to 85°C) has been added to the product lineup. |

### Changes in the Text

| Page    | Title                                                              | Modifications                                       |

|---------|--------------------------------------------------------------------|-----------------------------------------------------|

| 1, 2, 3 | 1.2 Features,                                                      | A chip with Wide Temperature Range                  |

|         | Table 3.1 Maximum data transfer rate supply voltage product lineup | (-40 to 85°C) has been added to the product lineup. |

Rev. 0, 07/98, page i of 11

# How to Use This Manual

This user's manual describes the functions, performance, and usage of the HD64570 serial communications adaptor (SCA) as a general-purpose communications control chip.

This manual consists of eleven chapters and an appendix.

#### — Section 1 Overview

This section outlines the functions, performance, and internal structure of the SCA.

#### - Section 2 Pin Arrangements and Functions

This section shows the pin arrangements and lists the functions of each pin.

#### — Section 3 System Controller

This section describes the operating modes of the chip (reset mode, normal operating mode, system stop mode), the bus arbiter functions, and the bus interface needed for interfacing with a host MPU.

### — Section 4 Interrupt Controller

This section describes the SCA's interrupt control logic, on-chip interrupt sources, vector output (fixed and modified vectoring), and acknowledge cycle.

#### — Section 5 MSCI (Multiprotocol Serial Communication Interface)

This section gives a general description of the asynchronous, byte-synchronous, and bit-synchronous communication protocols supported by the built-in multiprotocol serial communication interfaces (MSCI channels 0 and 1) that implement the main functions of the SCA, and shows the register settings for various communication functions.

#### — Section 6 DMAC (DMA Controller)

This section explains the single- and chained-block transfer modes supported by the built-in direct memory access controller (DMAC channels 0 to 3). Internal register functions and settings are also described.

#### — Section 7 Timers

This section explains operating modes and register settings of the built-in timers (channels 0 to 3), which generate internal interrupts.

#### — Section 8 Wait Controller

This section describes the built-in wait controller, which inserts wait states during memory access to one of three physical address spaces. Details about the associated internal registers and WAIT pin are also provided.

Rev. 0, 07/98, page iii of 11

#### — Section 9 Application Examples

This section shows examples of software routines and circuits in some typical applications of the SCA.

### — Section 10 Electrical Specifications

This section lists the SCA's electrical characteristics (absolute maximum ratings, DC characteristics, AC characteristics) and provides timing diagrams.

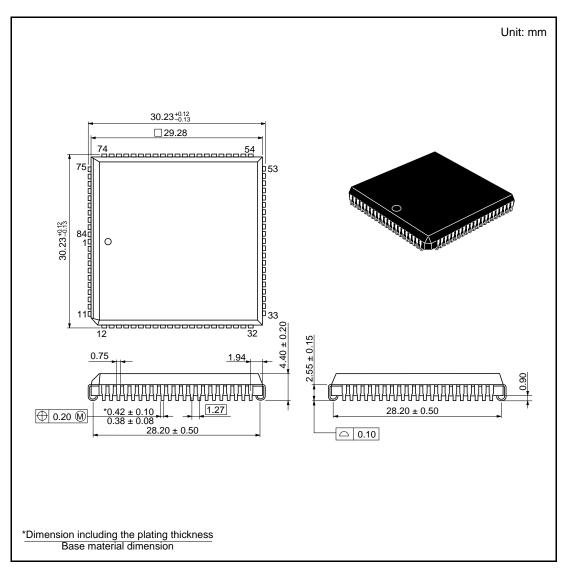

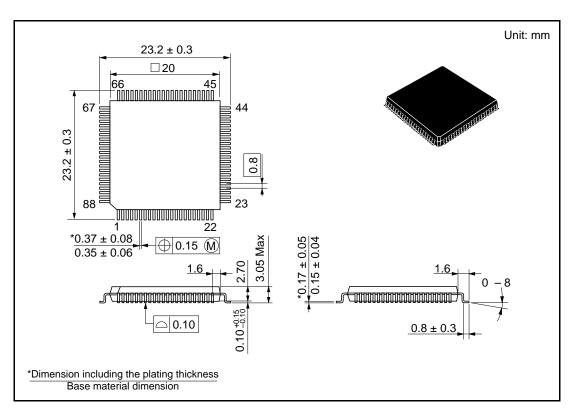

### - Section 11 Package Dimensions

This section shows the dimensions of the SCA package.

### - Appendices Descriptor and Register Tables

These tables list the names and bits of the descriptors used in DMA transfer, and the names, addresses, and bits of all SCA registers.

Rev. 0, 07/98, page iv of 11

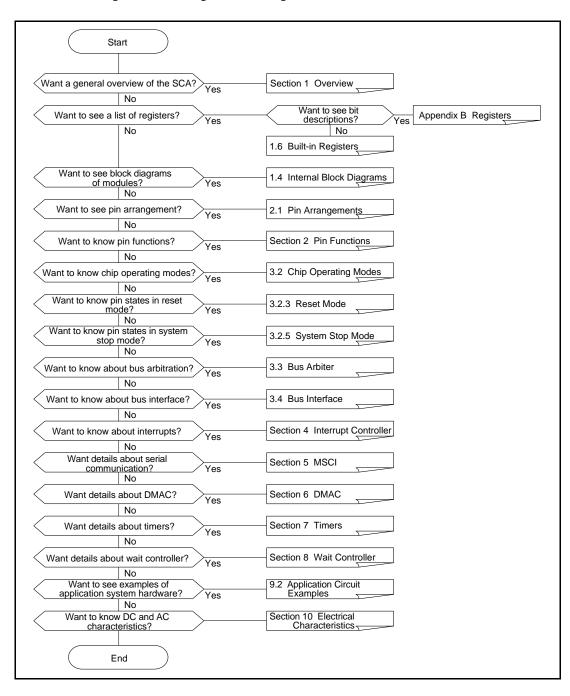

Use the following flowchart as a guide to reading this manual.

Rev. 0, 07/98, page v of 11

# Contents

| Secti | on 1     | Overview                                              | 1  |

|-------|----------|-------------------------------------------------------|----|

| 1.1   | Overvi   | ew                                                    | 1  |

| 1.2   | Feature  | S                                                     | 1  |

| 1.3   | Basic F  | Functions                                             | 2  |

| 1.4   | Block I  | Diagram                                               | 4  |

| 1.5   | Protoco  | ol Support                                            | 8  |

|       | 1.5.1    | Asynchronous Mode                                     | 8  |

|       | 1.5.2    | Byte-Synchronous Mode                                 | 9  |

|       | 1.5.3    | Bit-Synchronous Mode                                  | 9  |

| 1.6   | Built-In | n Registers                                           | 10 |

|       | 1.6.1    | Low-Power Mode Control Registers                      | 10 |

|       | 1.6.2    | Interrupt Control Registers                           | 10 |

|       | 1.6.3    | MSCI Registers                                        | 11 |

|       | 1.6.4    | DMAC Registers common to channels 0 to 3              | 12 |

|       | 1.6.5    | DMA Registers provided separately for channels 0 to 3 | 13 |

|       | 1.6.6    | Timer Registers                                       | 15 |

|       | 1.6.7    | Wait Controller Registers                             | 15 |

| 1.7   | Genera   | l Description of Functions                            | 16 |

|       | 1.7.1    | Operating Modes of Serial Section                     | 16 |

|       | 1.7.2    | Transmission Formats                                  | 16 |

|       | 1.7.3    | Transmission Error Detection                          | 18 |

|       | 1.7.4    | Transmission Codes                                    | 19 |

|       | 1.7.5    | Transmit/Receive Clock Selection                      | 20 |

|       | 1.7.6    | Maximum Bit Rates                                     | 22 |

|       | 1.7.7    | Transmitter                                           | 23 |

|       | 1.7.8    | Receiver                                              | 24 |

|       | 1.7.9    | DMAC                                                  | 26 |

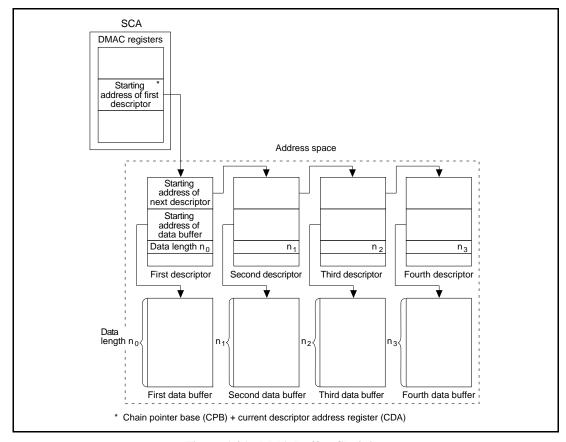

|       | 1.7.10   | DMA Buffer Chaining                                   | 33 |

|       | 1.7.11   | Descriptor Structure                                  | 34 |

|       | 1.7.12   | Bus Arbiter                                           | 35 |

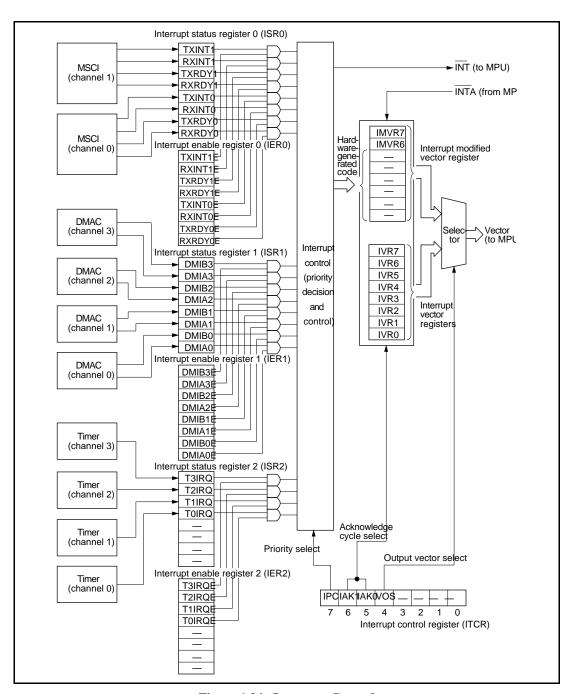

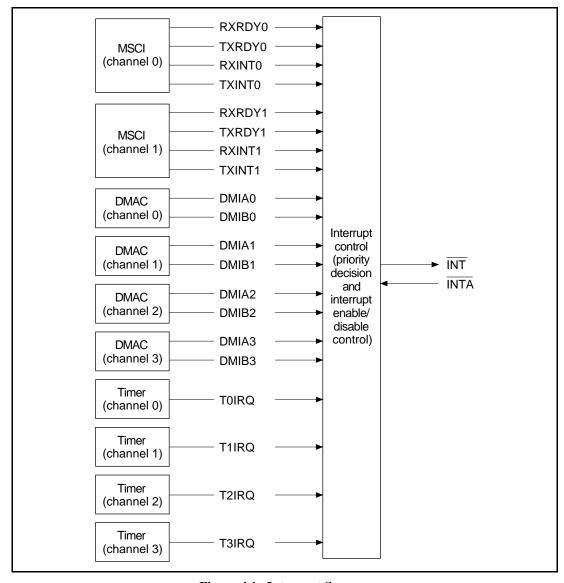

|       | 1.7.13   | Interrupt Control                                     | 36 |

|       | 1.7.14   | Timers                                                | 40 |

|       | 1.7.15   | Wait Controller                                       | 40 |

| Secti | on 2     | Pin Arrangements and Functions                        | 41 |

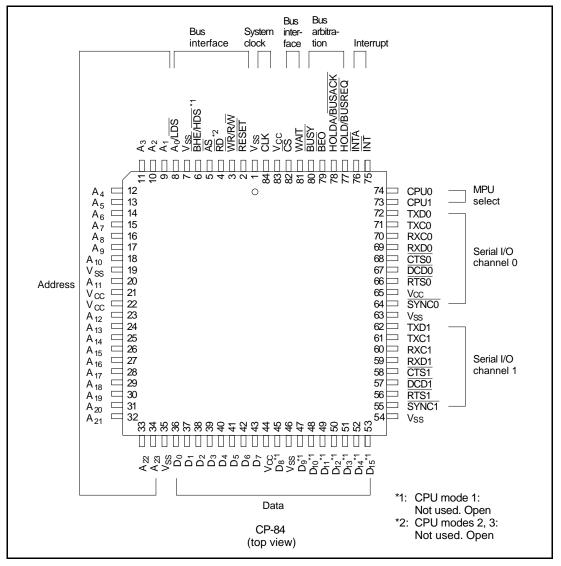

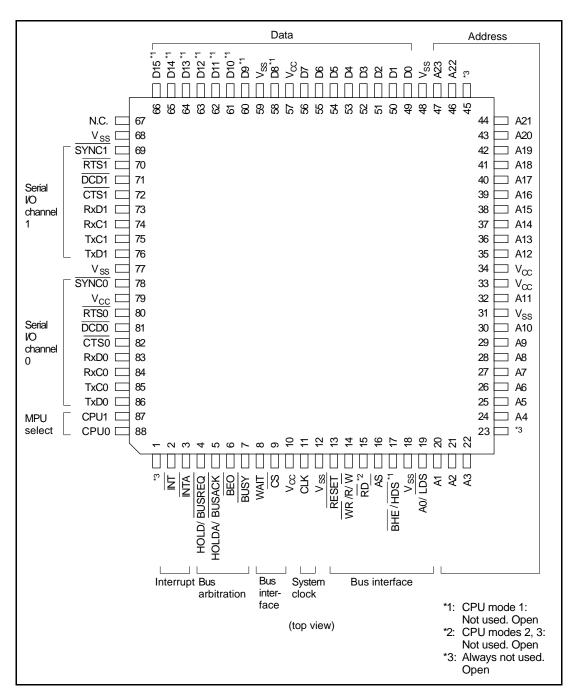

| 2.1   | Pin Arr  | rangements                                            |    |

| 2.2   | Pin Fur  | nctions                                               | 43 |

Rev. 0, 07/98, page i of 11

| Secti  | on 3      | System Controller                                   | 55  |

|--------|-----------|-----------------------------------------------------|-----|

| 3.1    | Overvi    | ew                                                  | 55  |

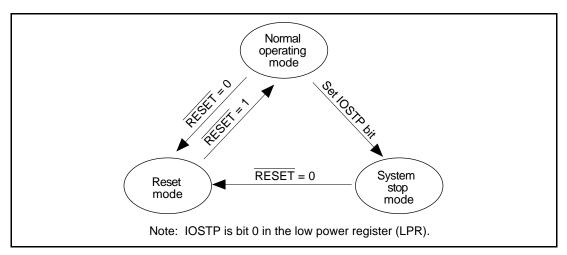

| 3.2    | Chip O    | perating Modes                                      | 55  |

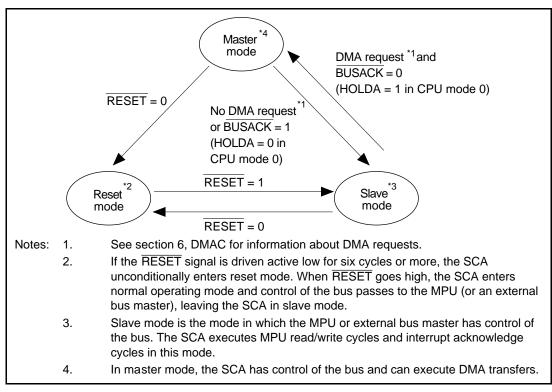

|        | 3.2.1     | SCA Operating Modes                                 | 55  |

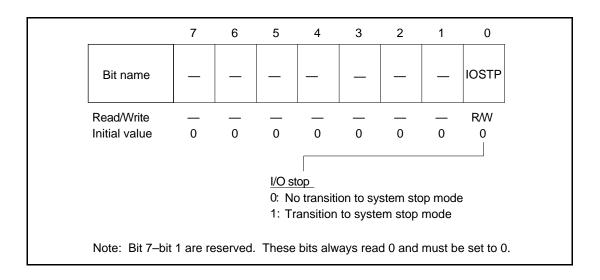

|        | 3.2.2     | Low-Power Register (LPR)                            | 57  |

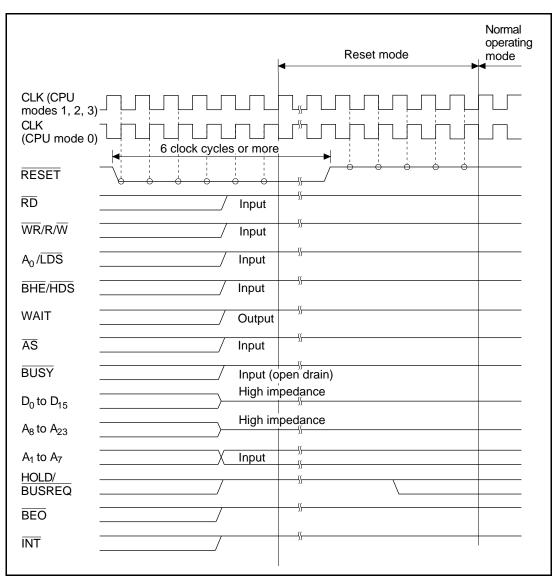

|        | 3.2.3     | Reset Mode                                          | 58  |

|        | 3.2.4     | Normal Operating Mode                               | 60  |

|        | 3.2.5     | System Stop Mode                                    | 60  |

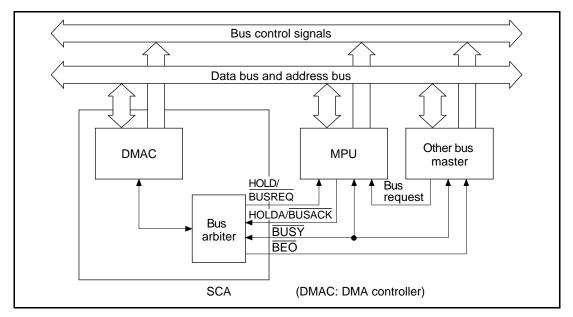

| 3.3    | Bus Ar    | biter                                               | 63  |

|        | 3.3.1     | Overview                                            | 63  |

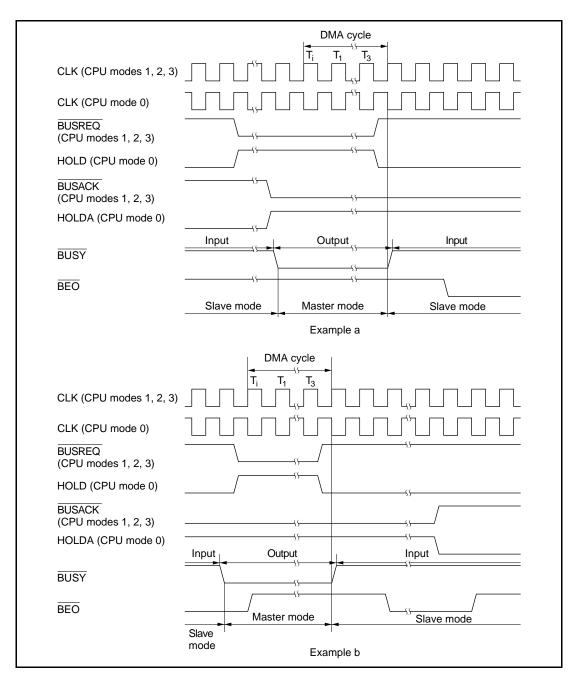

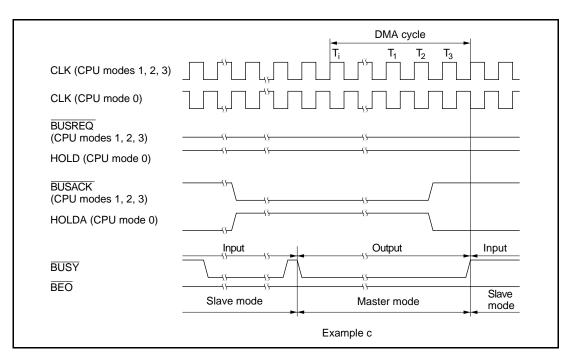

|        | 3.3.2     | Timing for Passing Bus Control                      | 64  |

|        | 3.3.3     | Bus Control Passing                                 | 65  |

| 3.4    | Bus Int   | erface                                              | 70  |

|        | 3.4.1     | Overview                                            | 70  |

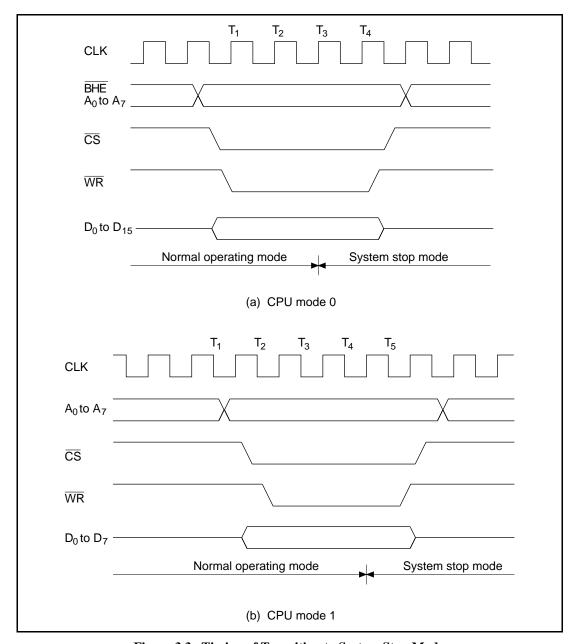

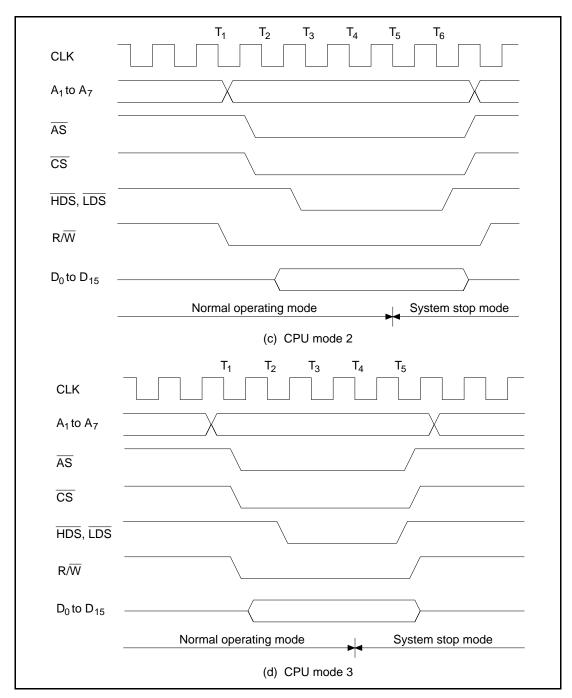

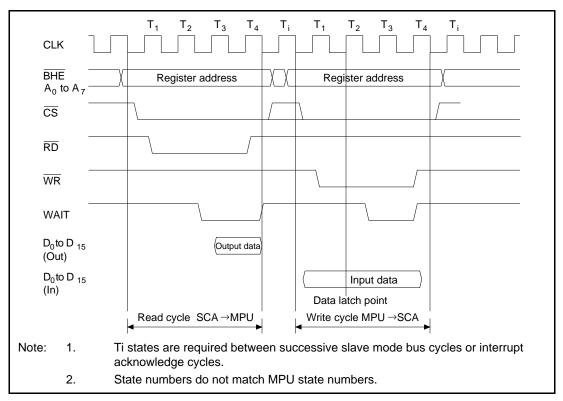

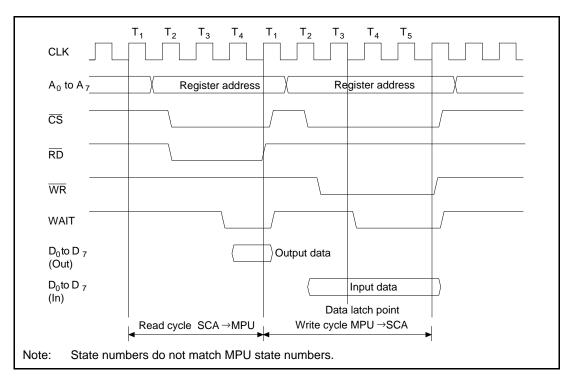

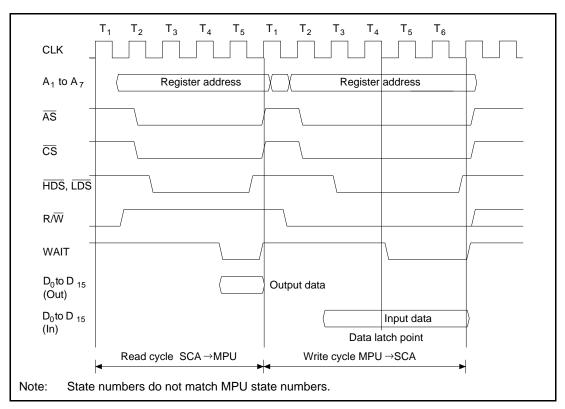

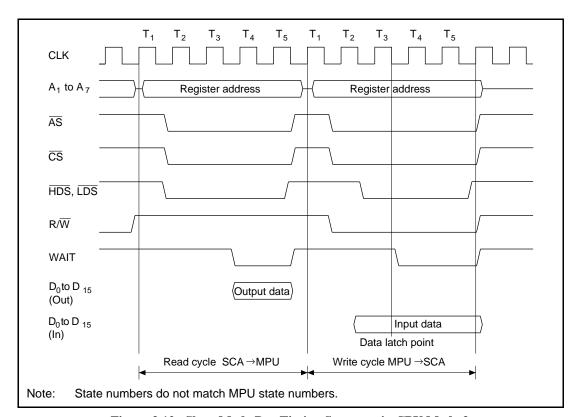

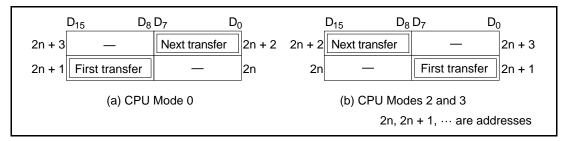

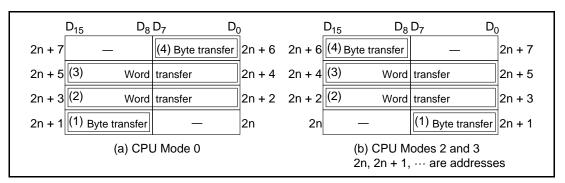

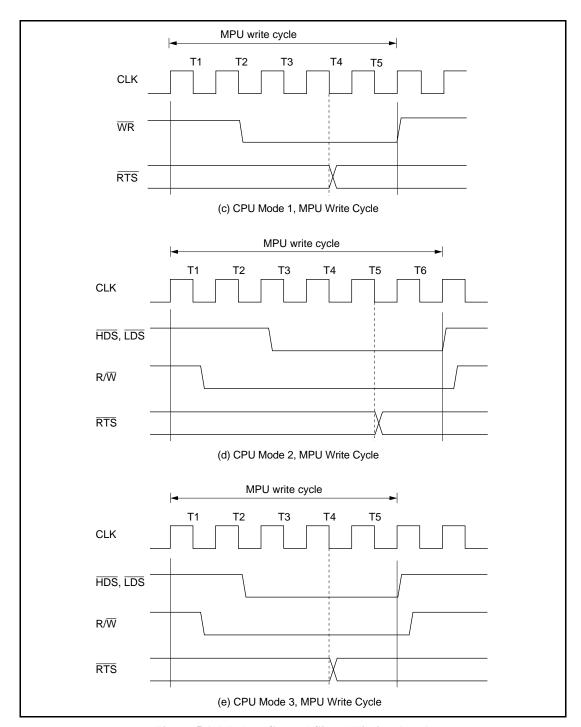

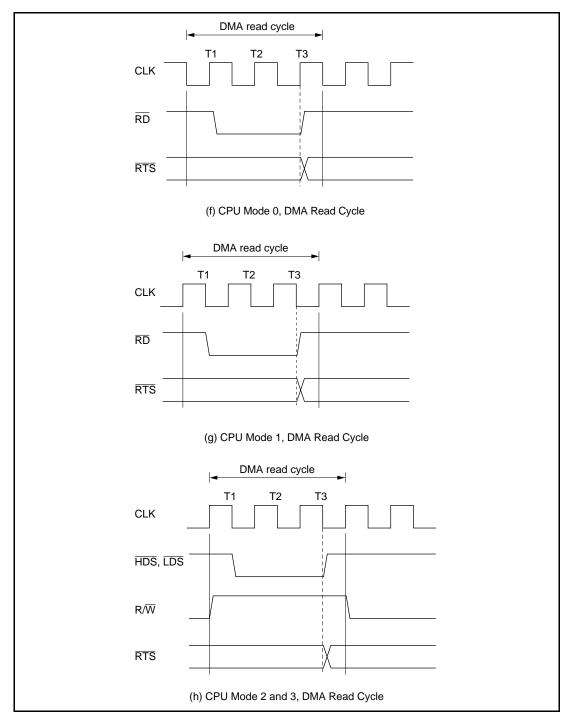

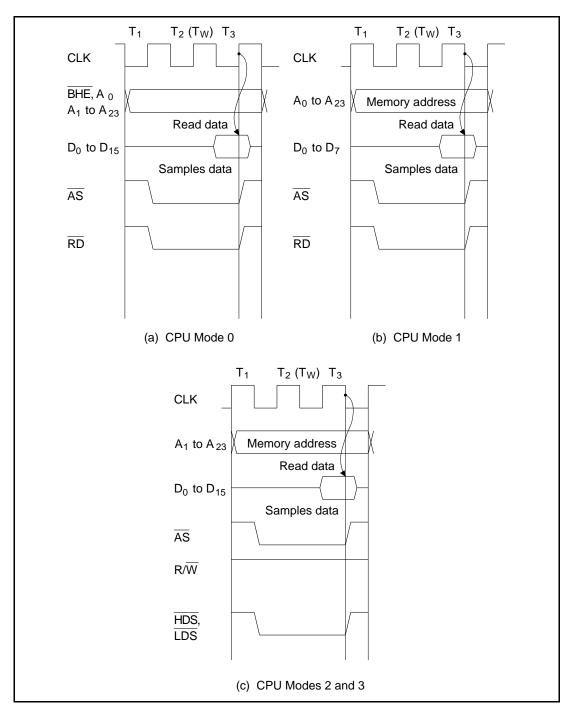

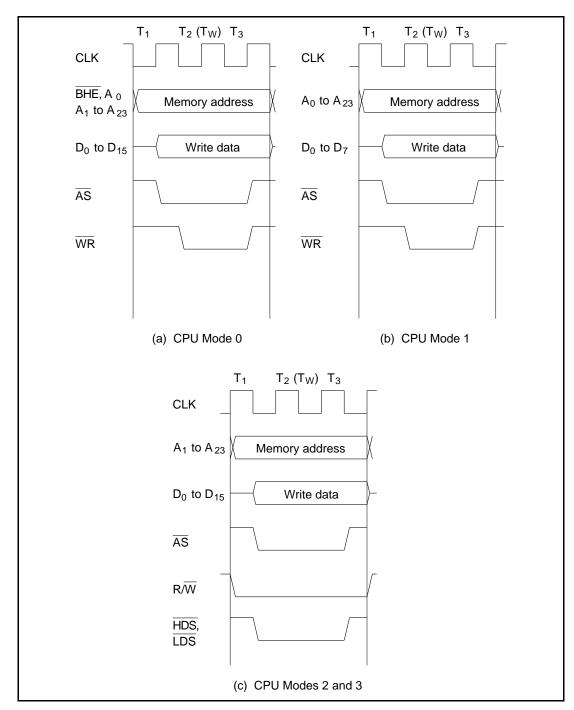

|        | 3.4.2     | Slave Mode Bus Cycle                                | 71  |

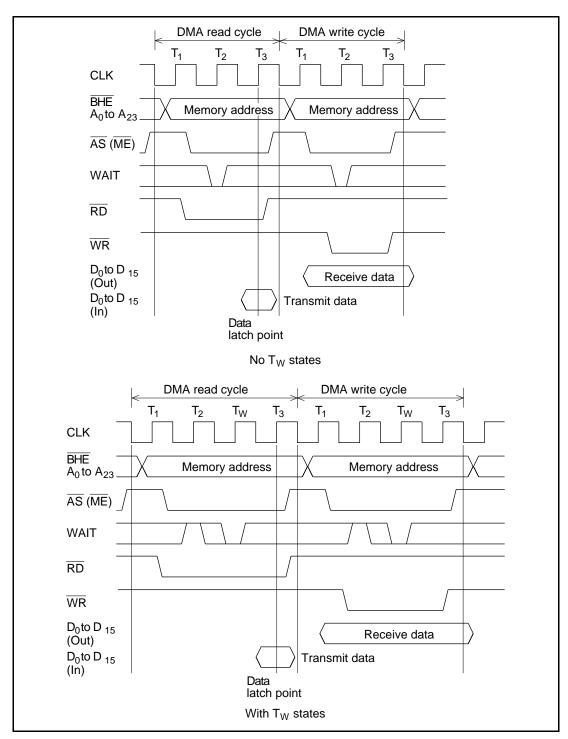

|        | 3.4.3     | Master Mode Bus Cycle                               | 76  |

|        |           |                                                     |     |

| Secti  | on 4      | Interrupt Controller                                | 81  |

| 4.1    | Overvi    | ew                                                  | 81  |

| 4.2    | Registe   | ers                                                 | 83  |

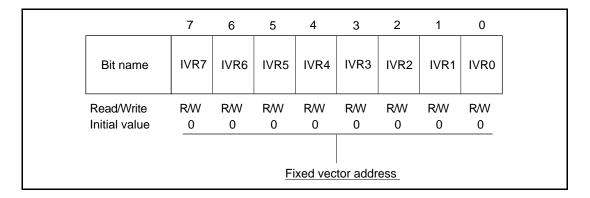

|        | 4.2.1     | Interrupt Vector Register (IVR)                     | 83  |

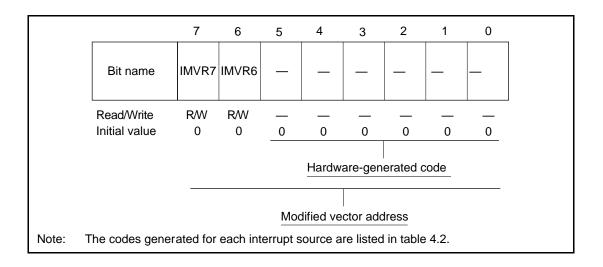

|        | 4.2.2     | Interrupt Modified Vector Register (IMVR)           | 83  |

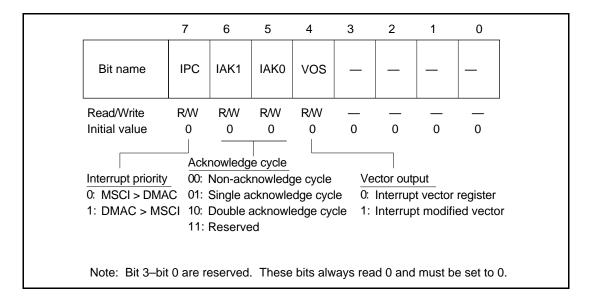

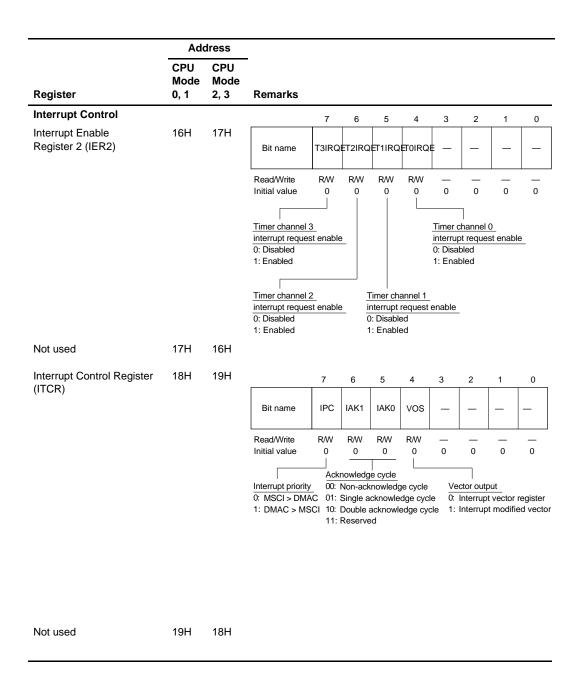

|        | 4.2.3     | Interrupt Control Register (ITCR)                   | 84  |

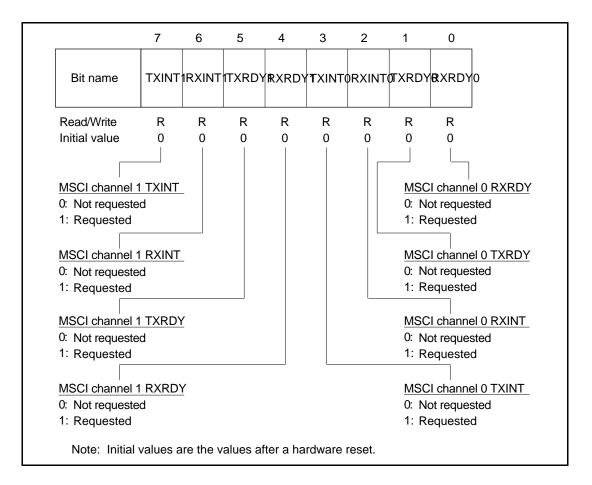

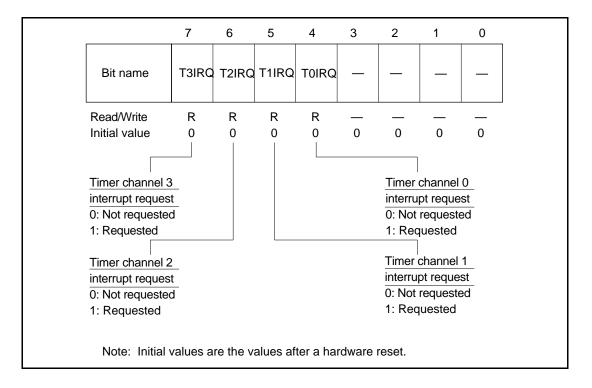

|        | 4.2.4     | Interrupt Status Register 0 (ISR0)                  | 86  |

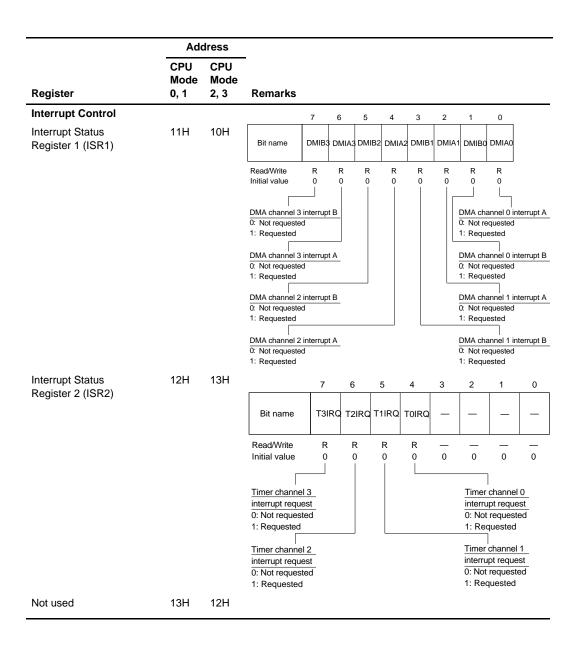

|        | 4.2.5     | Interrupt Status Register 1 (ISR1)                  | 88  |

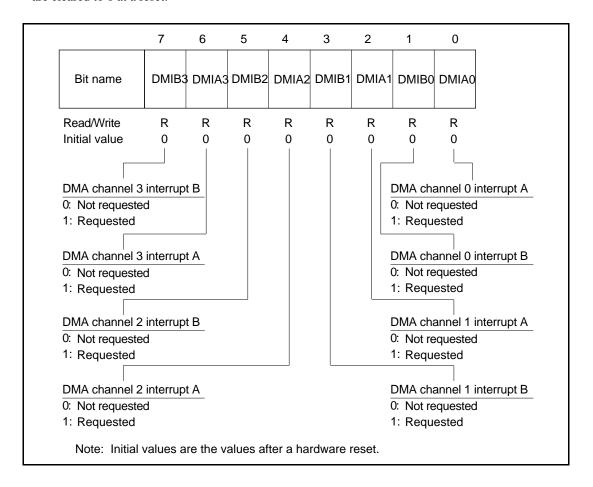

|        | 4.2.6     | Interrupt Status Register 2 (ISR2)                  | 90  |

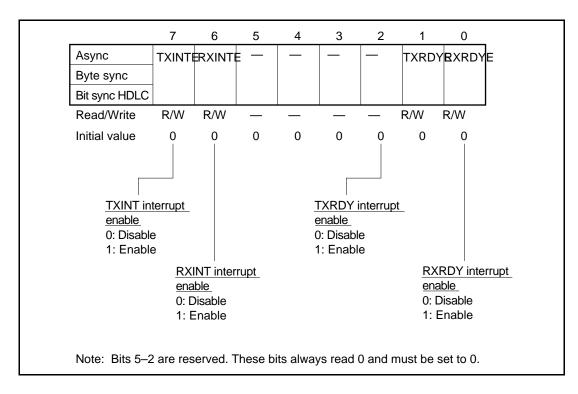

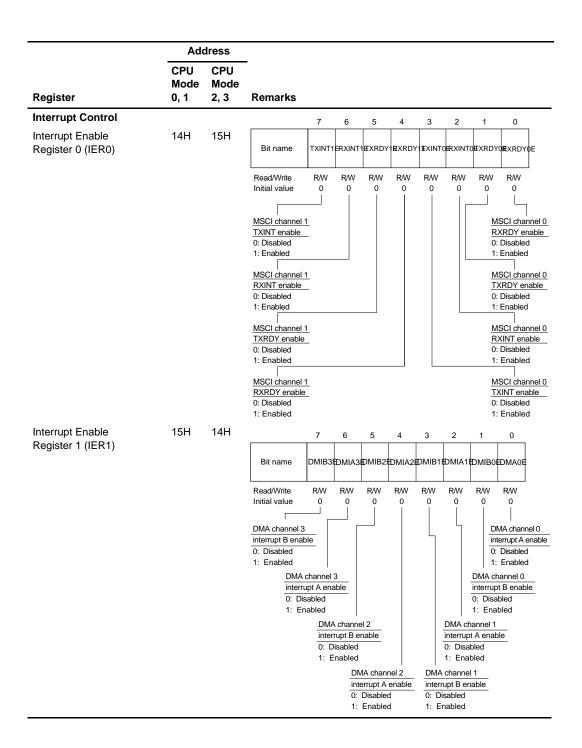

|        | 4.2.7     | Interrupt Enable Register 0 (IER0)                  | 92  |

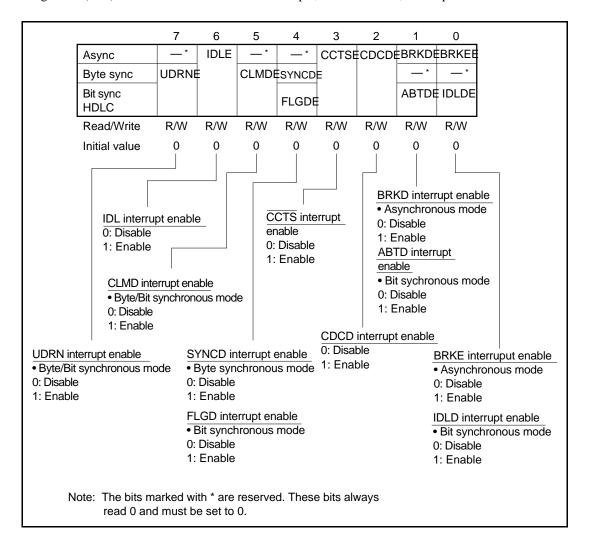

|        | 4.2.8     | Interrupt Enable Register 1 (IER1)                  | 94  |

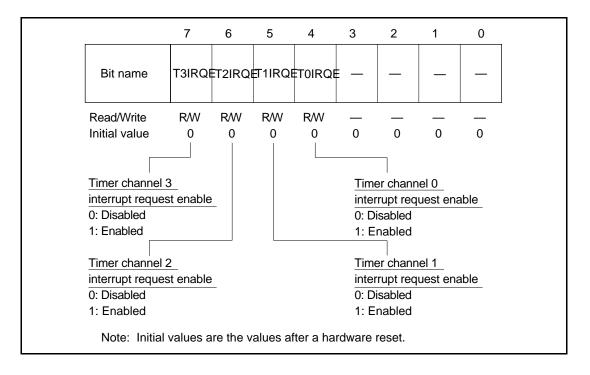

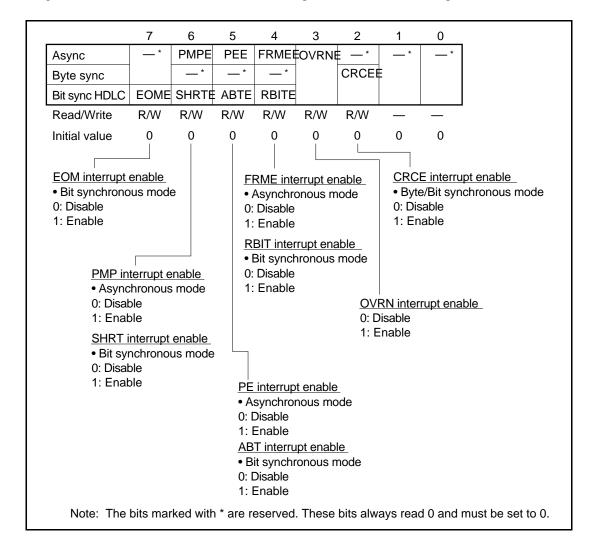

|        | 4.2.9     | Interrupt Enable Register 2 (IER2)                  | 96  |

| 4.3    | Vector    | Output                                              | 98  |

| 4.4    |           | wledge Cycle                                        | 98  |

| 4.5    |           | pt Sources and Vector Addresses                     |     |

|        |           |                                                     |     |

| Secti  | on 5      | Multiprotocol Serial Communication Interface (MSCI) | 101 |

| 5.1    | Overvi    | ew                                                  | 101 |

|        | 5.1.1     | Functions                                           | 101 |

|        | 5.1.2     | Configuration and Operation                         | 103 |

| 5.2    | Registe   | ers                                                 | 104 |

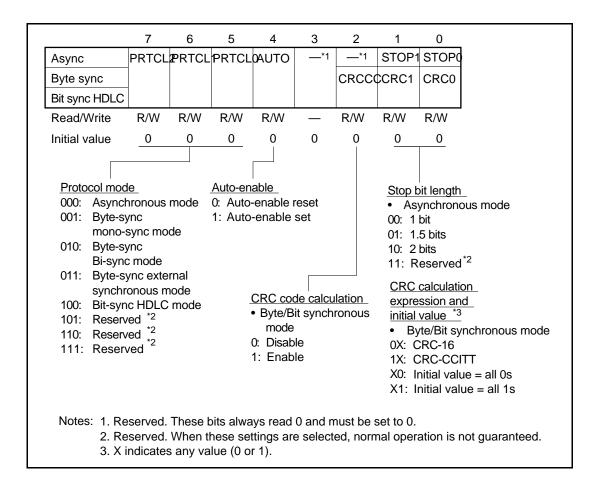

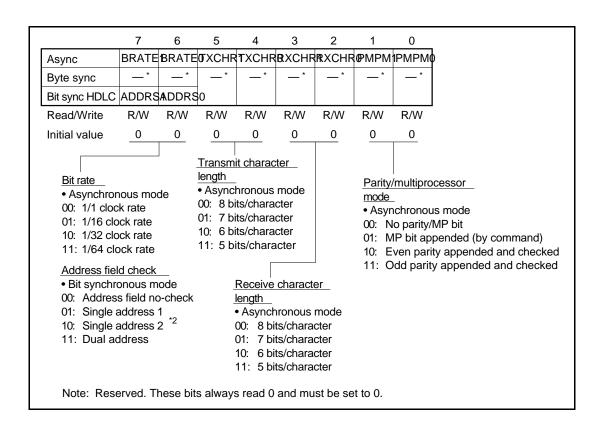

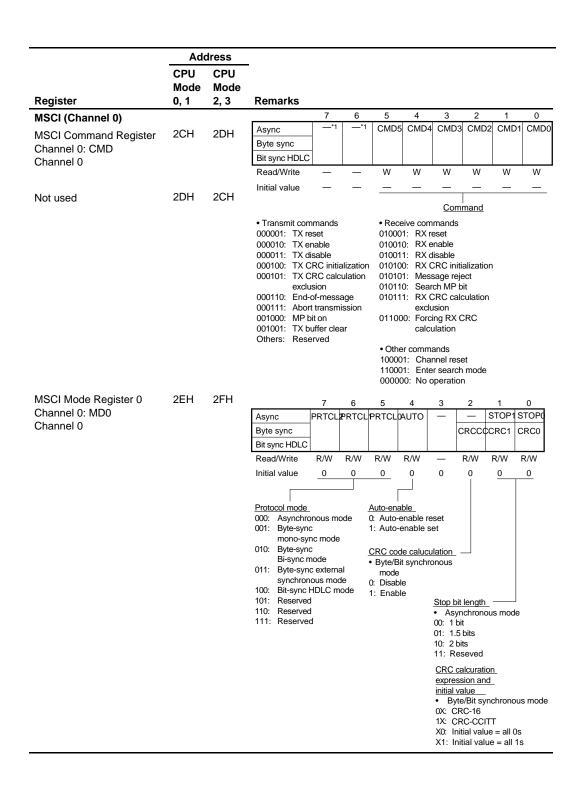

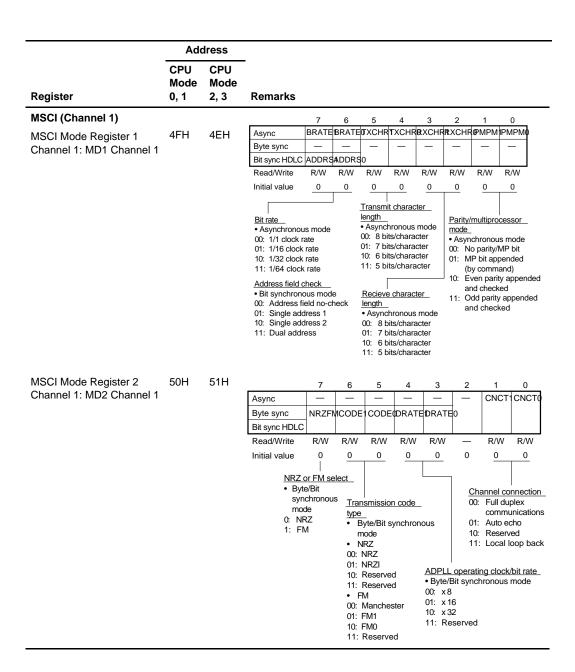

|        | 5.2.1     | MSCI Mode Register 0 (MD0)                          | 105 |

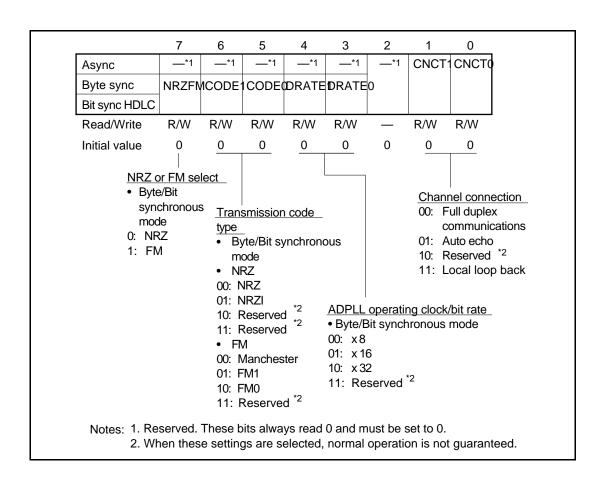

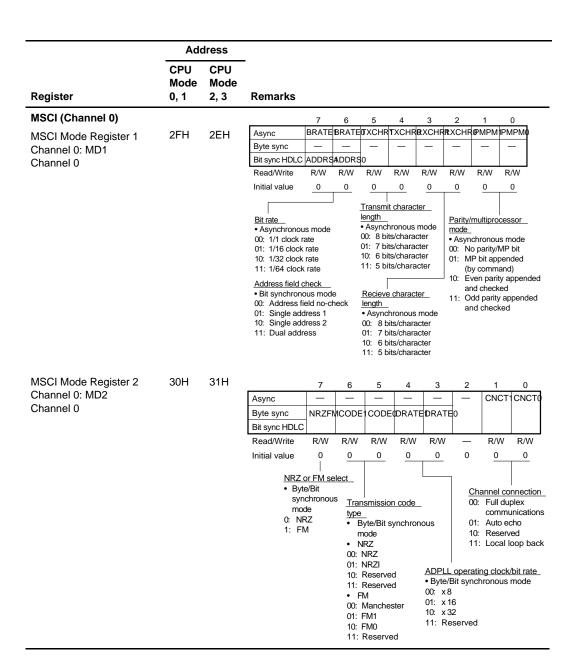

|        | 5.2.2     | MSCI Mode Register 1 (MD1)                          | 112 |

|        | 5.2.3     | MSCI Mode Register 2 (MD2)                          | 115 |

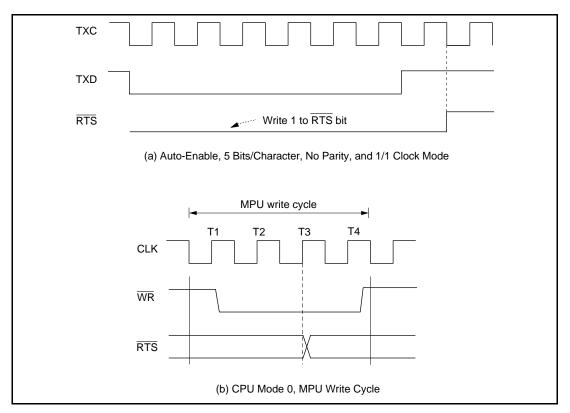

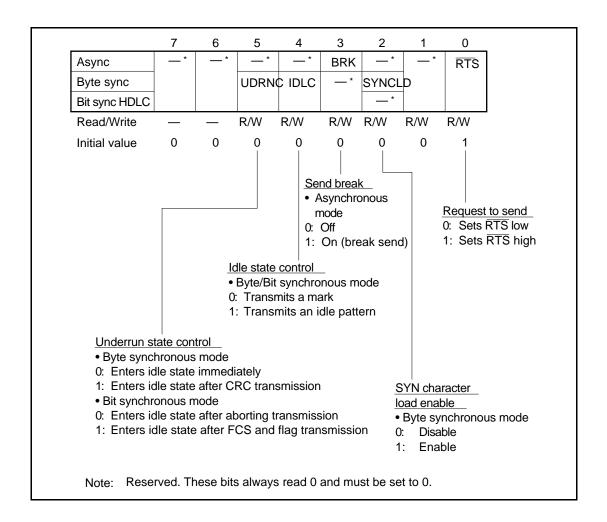

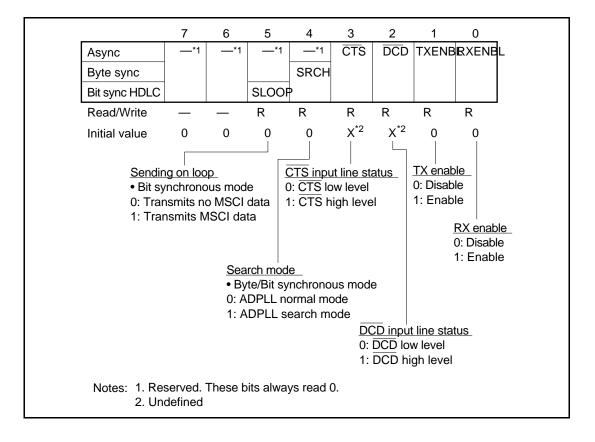

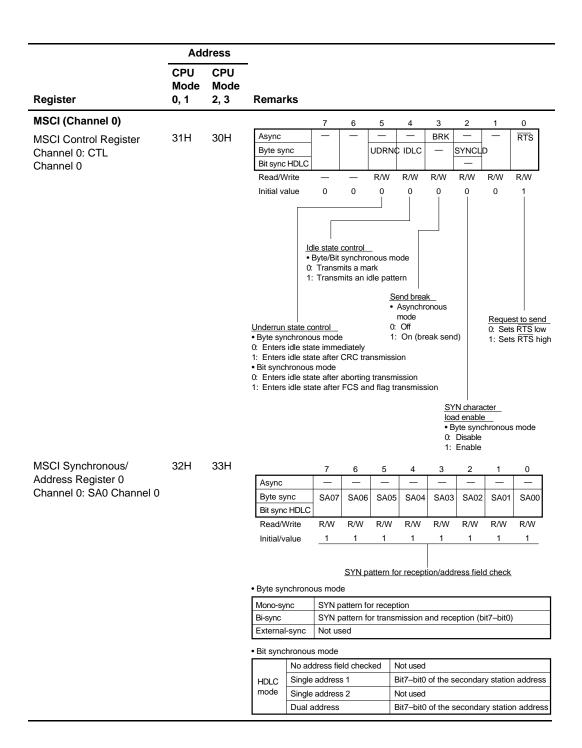

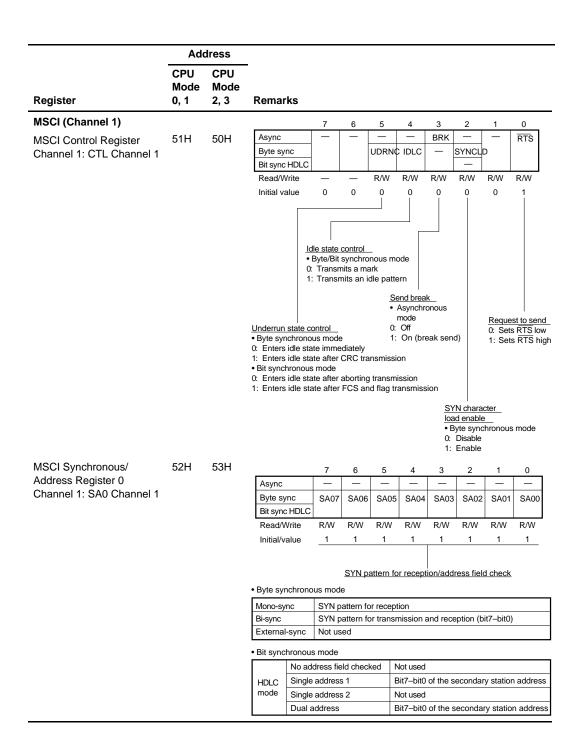

|        | 5.2.4     | MSCI Control Register (CTL)                         | 118 |

| Rev. ( | 0, 07/98, | page i of 11                                        |     |

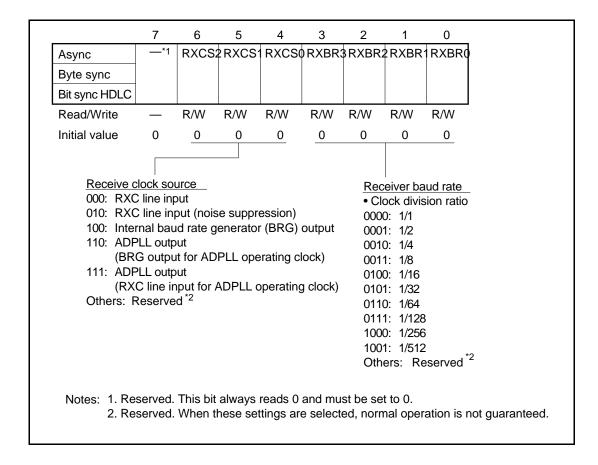

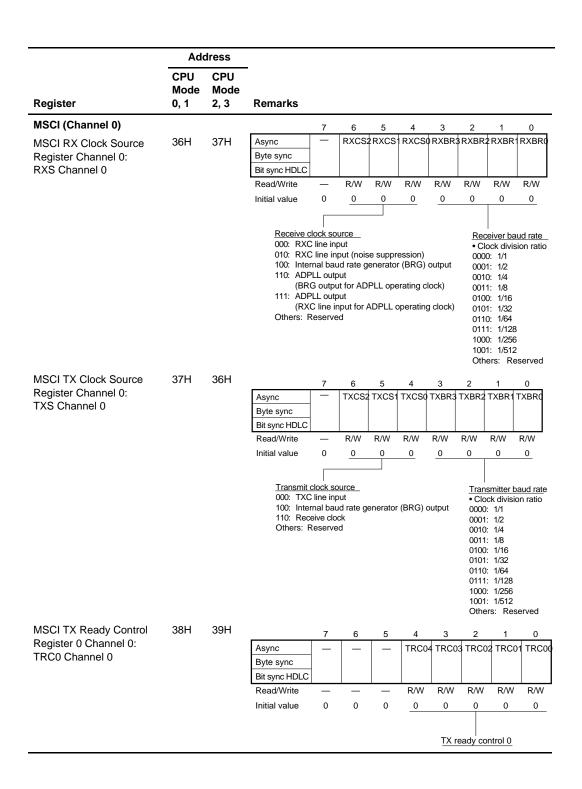

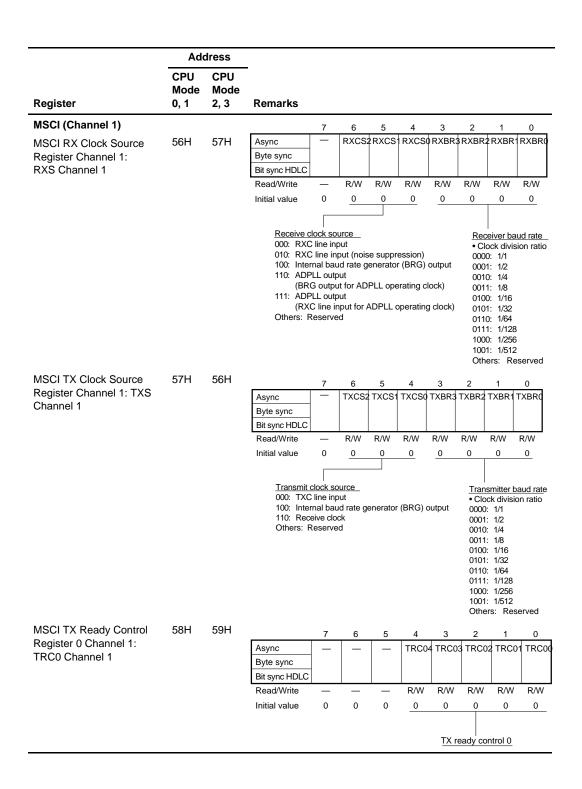

|     | 5.2.5  | MSCI RX Clock Source Register (RXS)          | 121 |

|-----|--------|----------------------------------------------|-----|

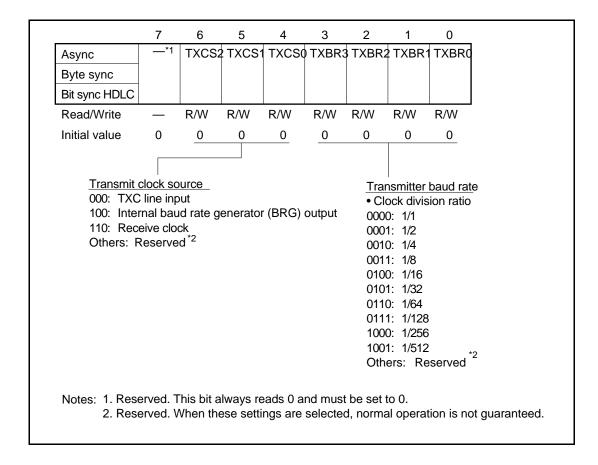

|     | 5.2.6  | MSCI TX Clock Source Register (TXS)          | 123 |

|     | 5.2.7  | MSCI Time Constant Register (TMC)            | 125 |

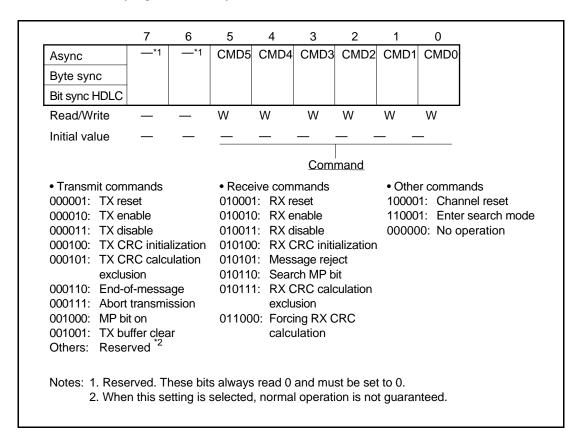

|     | 5.2.8  | MSCI Command Register (CMD)                  | 126 |

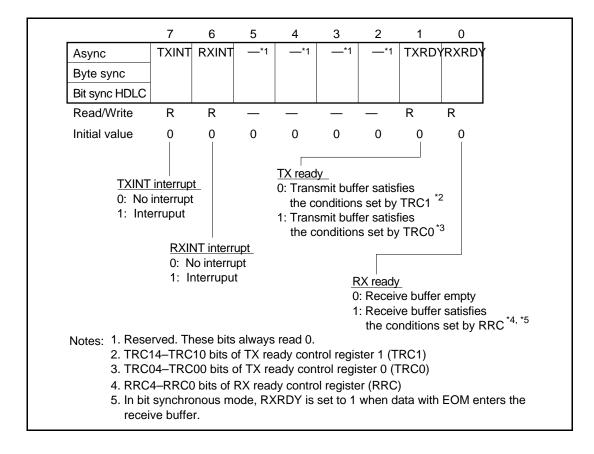

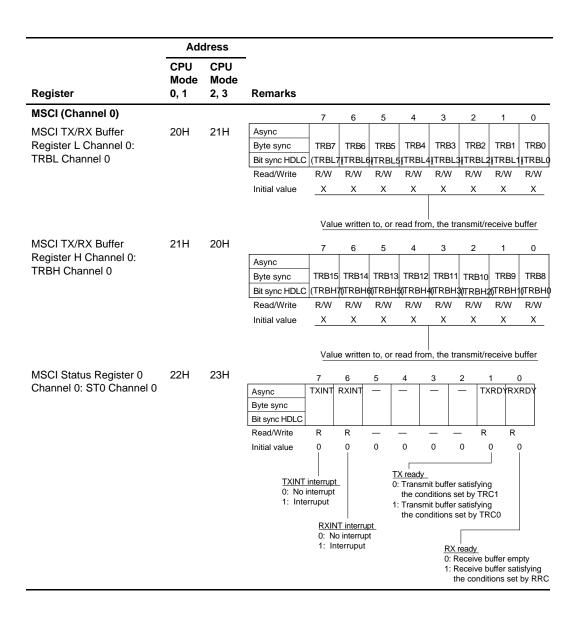

|     | 5.2.9  | MSCI Status Register 0 (ST0)                 | 131 |

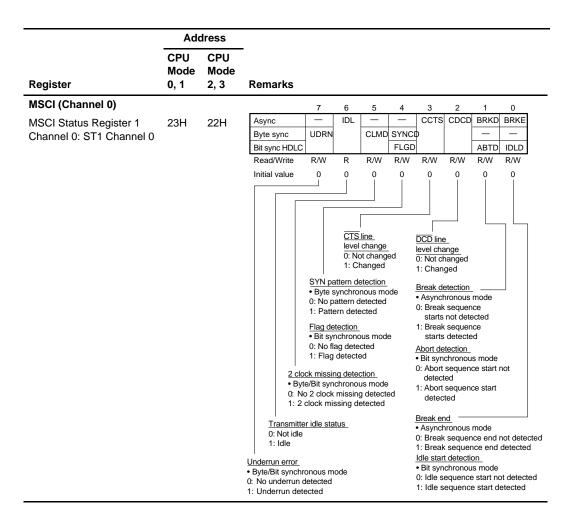

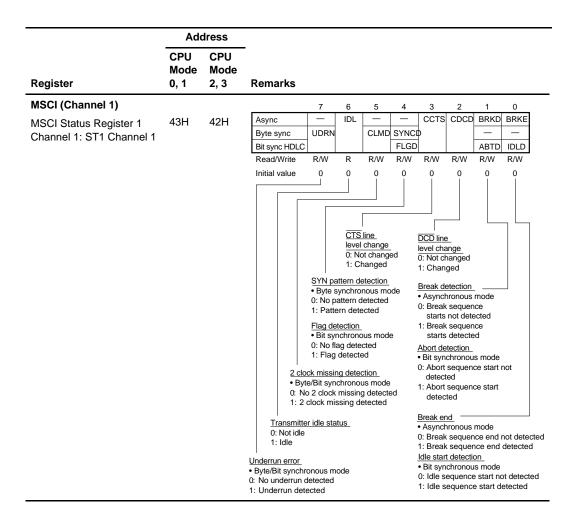

|     | 5.2.10 | MSCI Status Register 1 (ST1)                 | 136 |

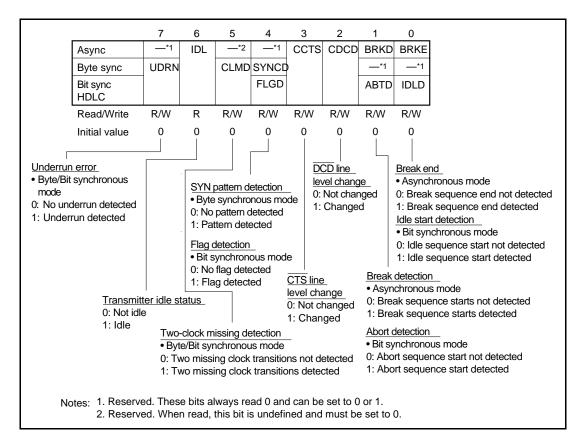

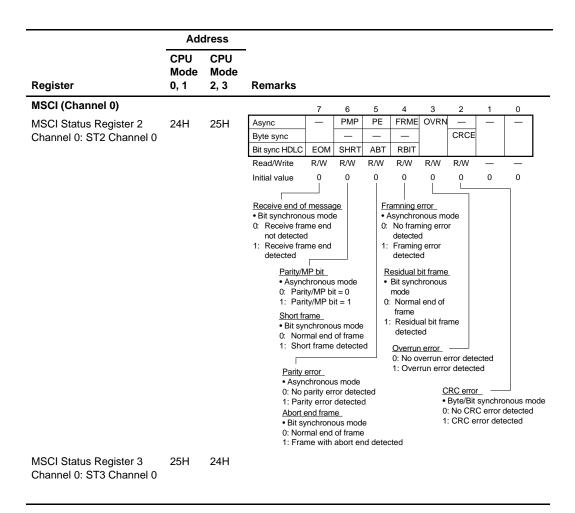

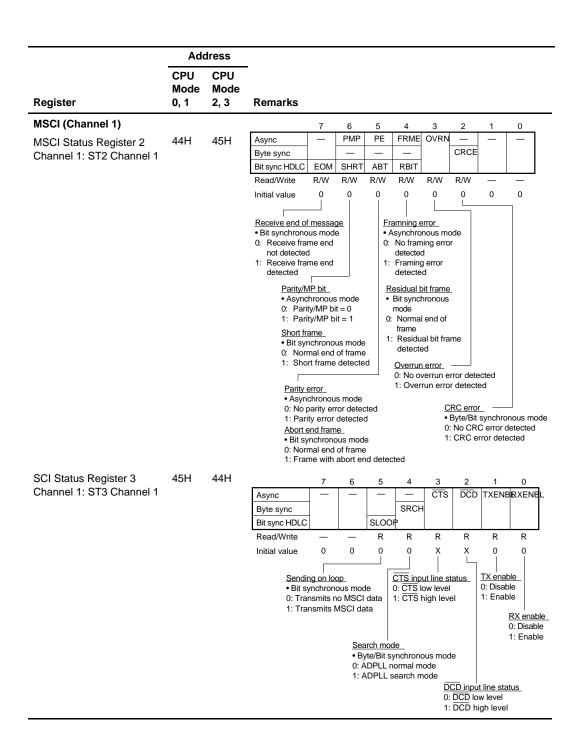

|     | 5.2.11 | MSCI Status Register 2 (ST2)                 | 139 |

|     | 5.2.12 | MSCI Status Register 3 (ST3)                 | 145 |

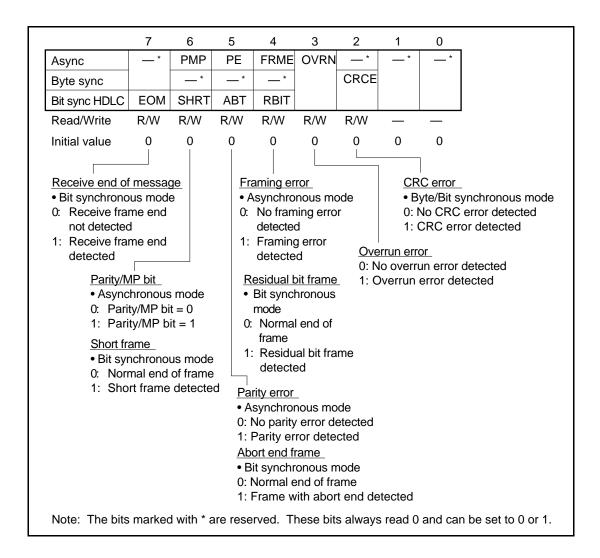

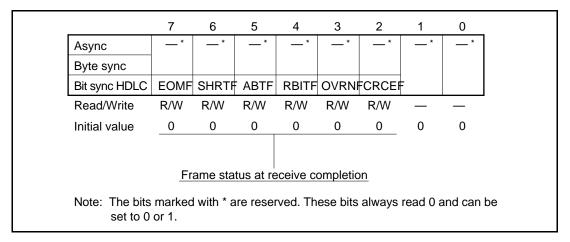

|     | 5.2.13 | MSCI Frame Status Register (FST)             | 147 |

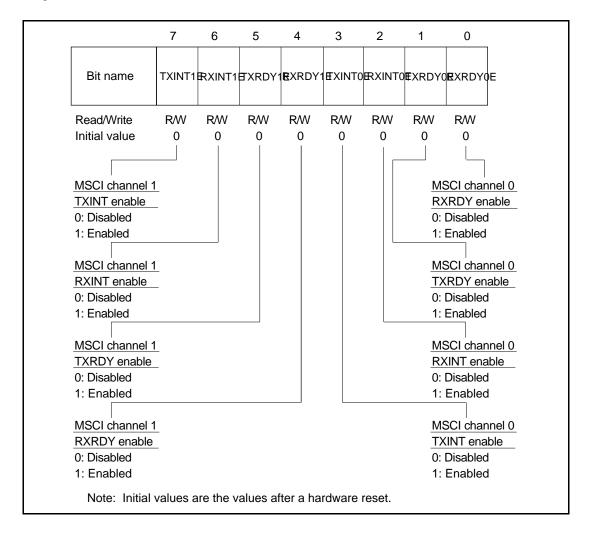

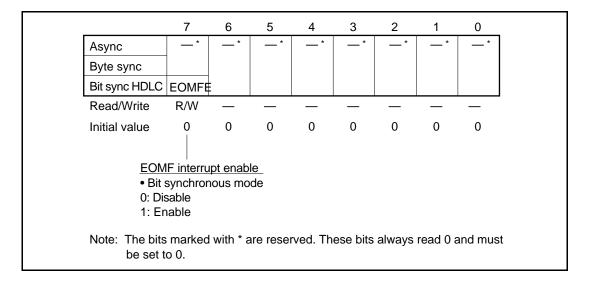

|     | 5.2.14 | MSCI Interrupt Enable Register 0 (IE0)       | 149 |

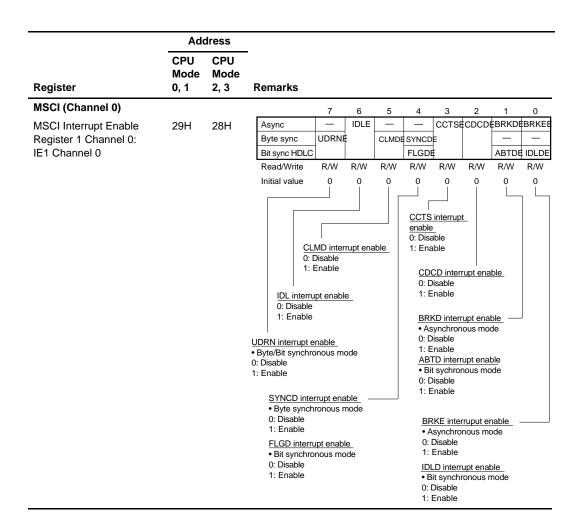

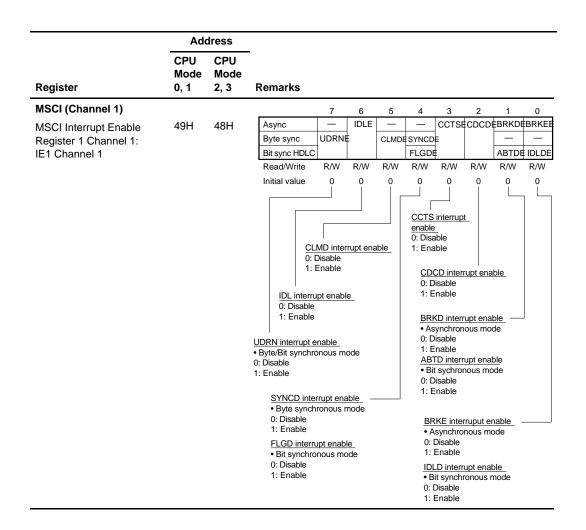

|     | 5.2.15 | MSCI Interrupt Enable Register 1 (IE1)       | 151 |

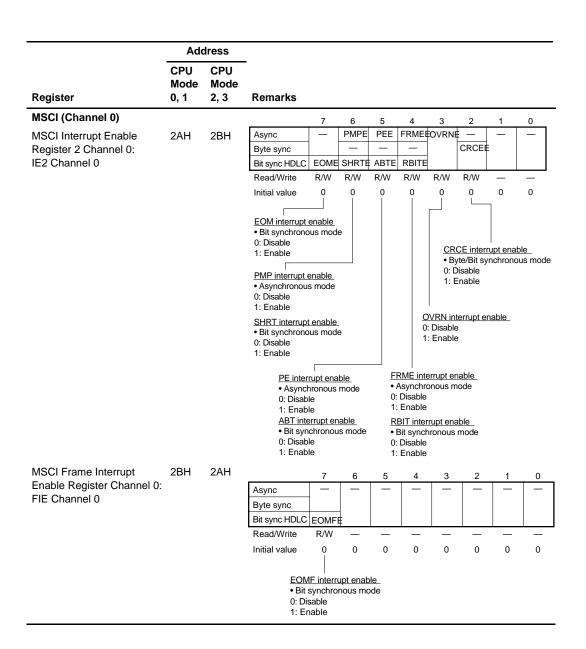

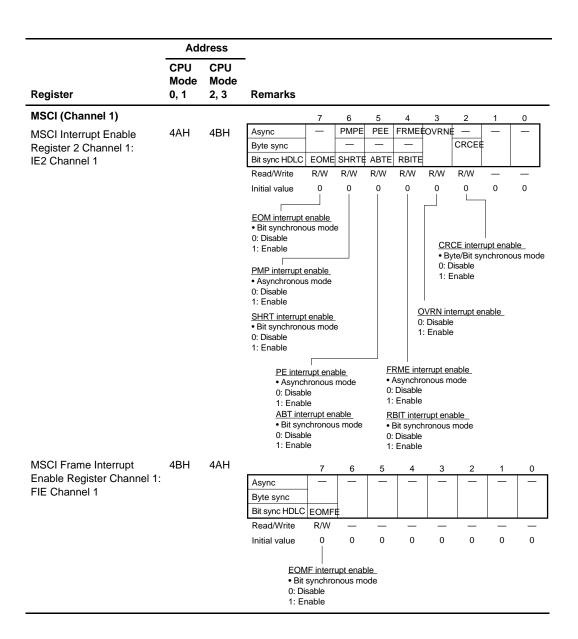

|     | 5.2.16 | MSCI Interrupt Enable Register 2 (IE2)       | 154 |

|     | 5.2.17 | MSCI Frame Interrupt Enable Register (FIE)   | 157 |

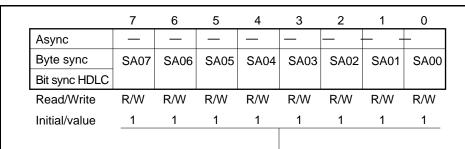

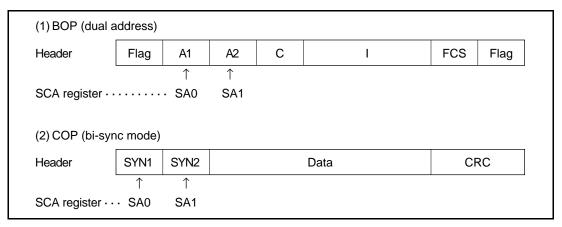

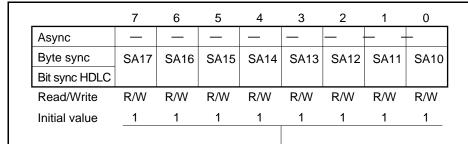

|     | 5.2.18 | MSCI Synchronous/Address Register 0 (SA0)    | 158 |

|     | 5.2.19 | MSCI Synchronous/Address Register 1 (SA1)    | 160 |

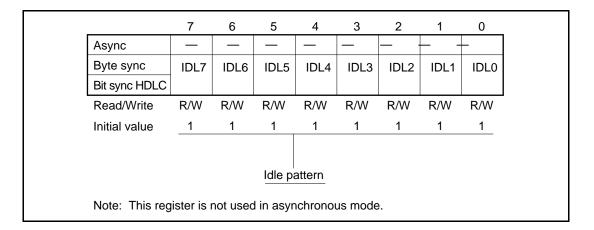

|     | 5.2.20 | MSCI Idle Pattern Register (IDL)             | 162 |

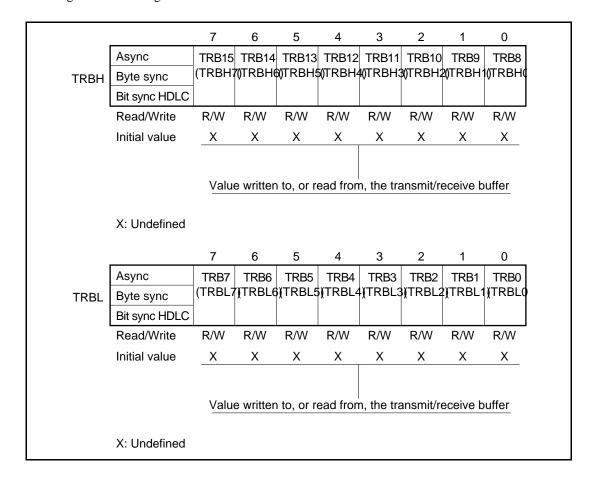

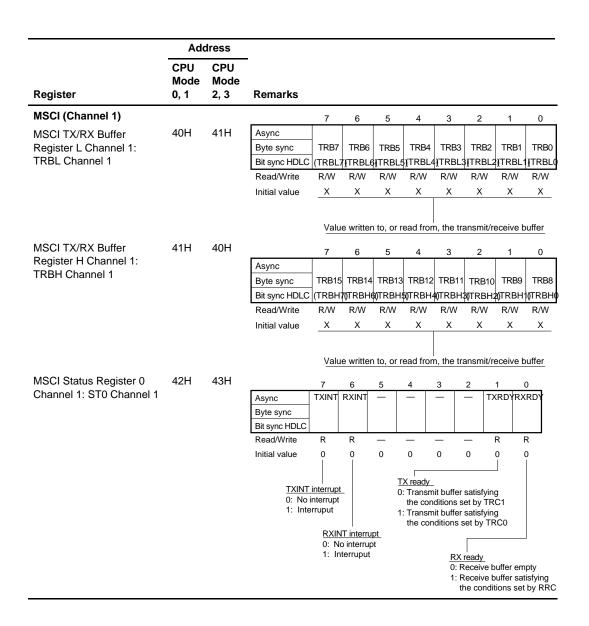

|     | 5.2.21 | MSCI TX/RX Buffer Register (TRB: TRBH, TRBL) | 163 |

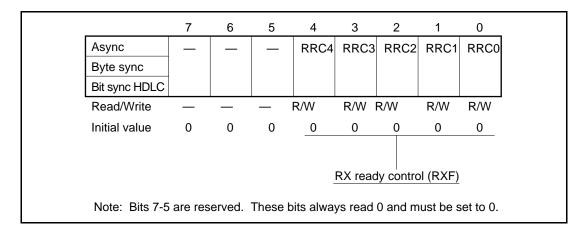

|     | 5.2.22 | MSCI RX Ready Control Register (RRC)         | 168 |

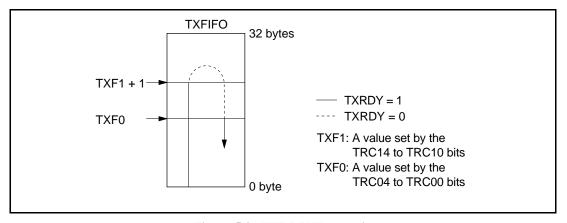

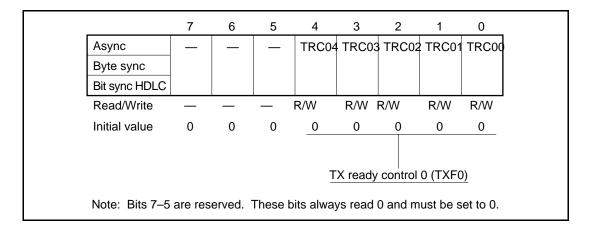

|     | 5.2.23 | MSCI TX Ready Control Register 0 (TRC0)      | 169 |

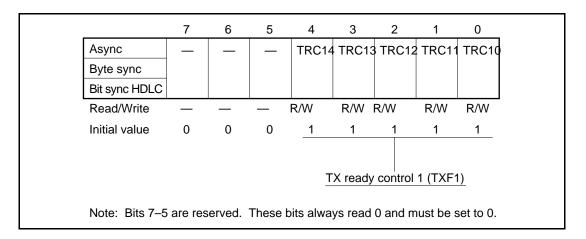

|     | 5.2.24 | MSCI TX Ready Control Register 1 (TRC1)      | 170 |

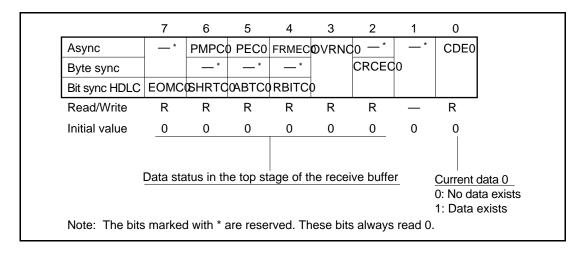

|     | 5.2.25 | MSCI Current Status Register 0 (CST0)        | 171 |

|     |        | MSCI Current Status Register 1 (CST1)        |     |

| 5.3 | Operat | ion                                          | 174 |

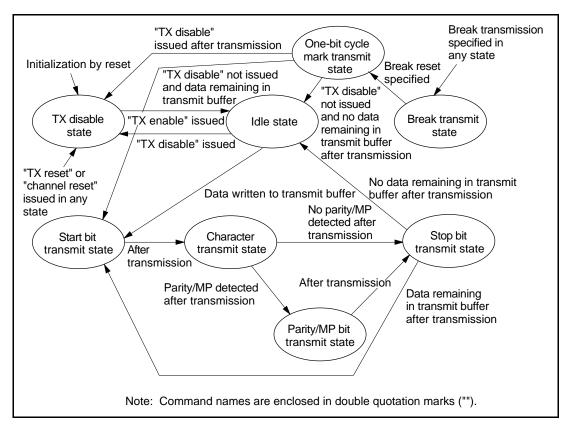

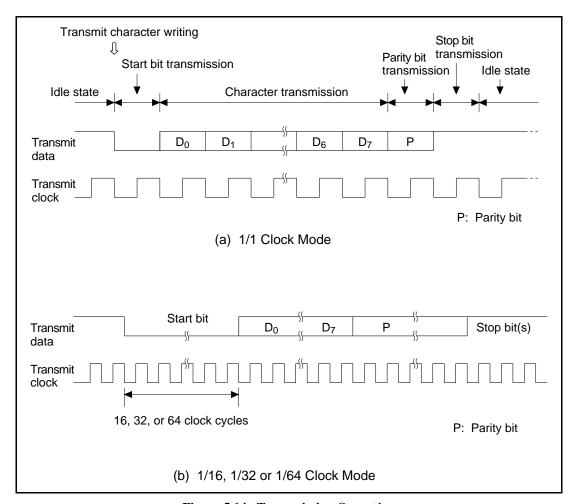

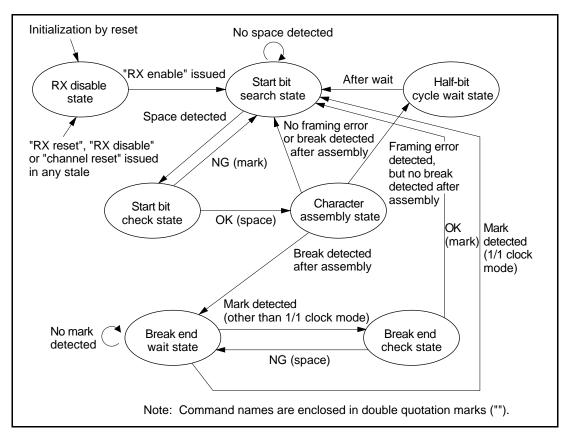

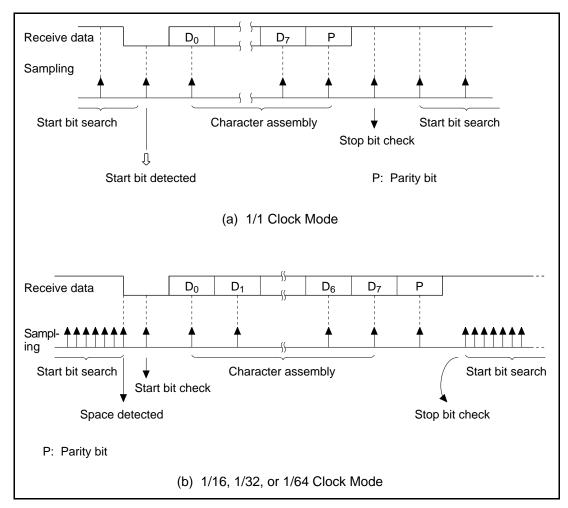

|     | 5.3.1  | Asynchronous Mode                            | 174 |

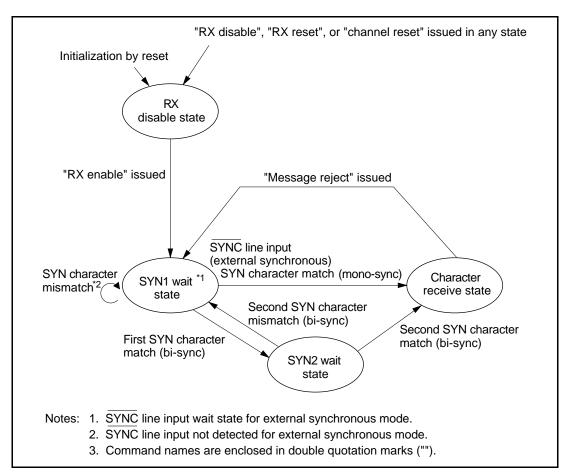

|     | 5.3.2  | Byte Synchronous Mode                        | 190 |

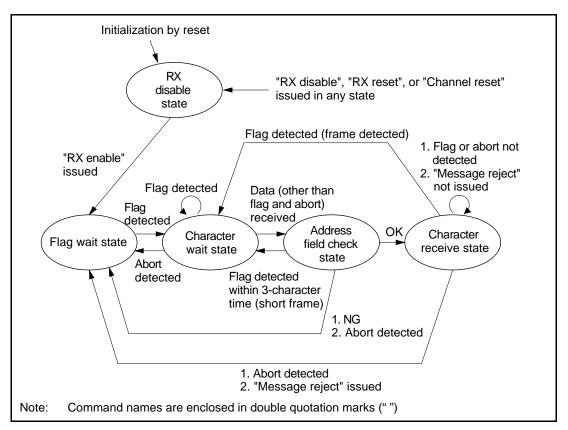

|     | 5.3.3  | Bit Synchronous Mode                         |     |

| 5.4 | Transn | nit/Receive Clock Sources                    | 206 |

|     | 5.4.1  | Overview                                     | 206 |

|     | 5.4.2  | Transmit Clock Sources                       | 208 |

|     | 5.4.3  | Receive Clock Sources                        | 209 |

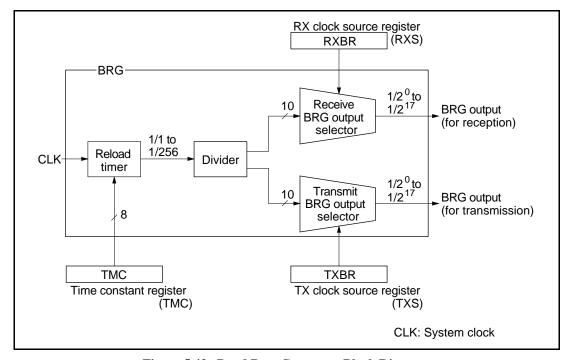

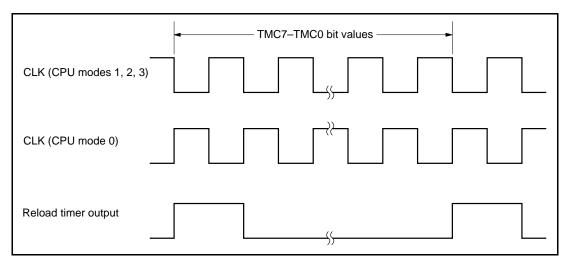

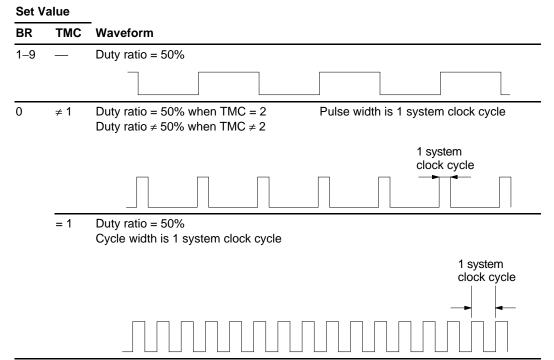

|     | 5.4.4  | Baud Rate Generator                          | 210 |

|     | 5.4.5  | ADPLL                                        | 210 |

| 5.5 | ADPL   | L                                            |     |

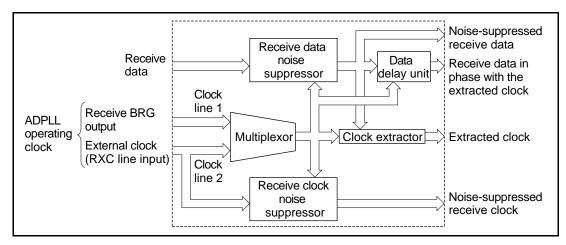

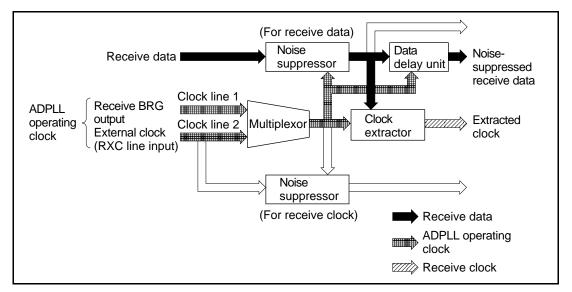

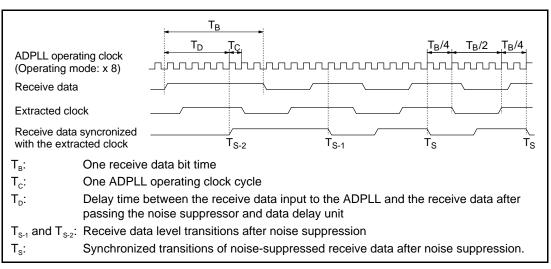

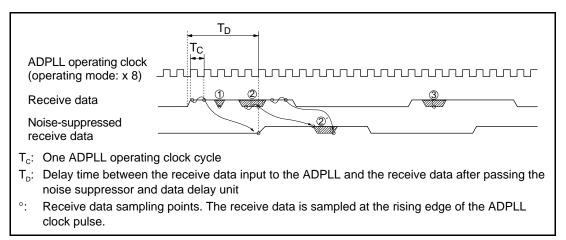

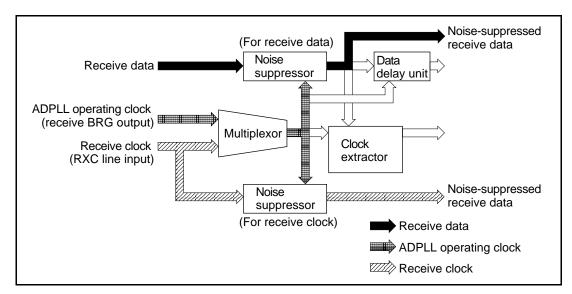

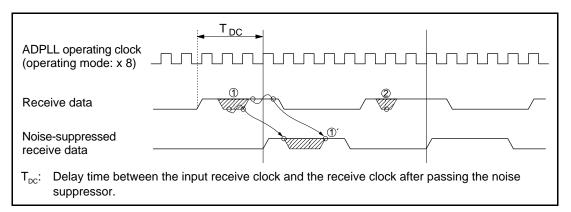

|     | 5.5.1  | Overview                                     | 211 |

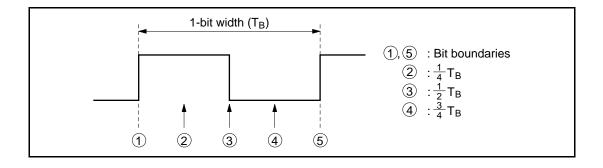

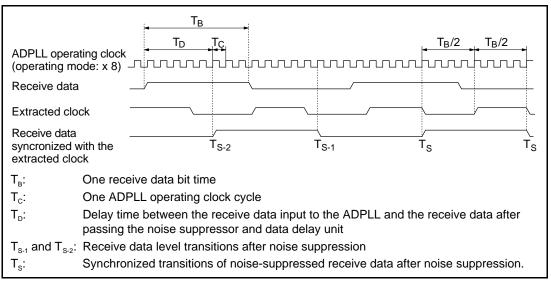

|     | 5.5.2  | Operation                                    | 214 |

|     | 5.5.3  | Notes on Usage                               | 220 |

| 5.6 | Baud F | Rate Generator                               |     |

|     | 5.6.1  | Overview                                     |     |

|     | 5.6.2  | Functions                                    |     |

|     | 5.6.3  | Register Set Values and Bit Rates            |     |

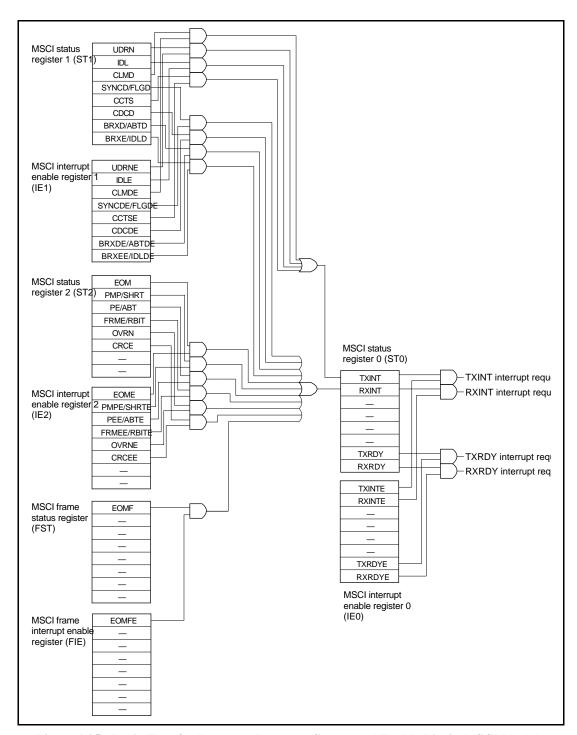

| 5.7 |        | pts                                          |     |

|     | 5.7.1  | Interrupt Types and Sources                  |     |

|     | 5.7.2  | Interrupt Clear                              | 234 |

Rev. 0, 07/98, page ii of 11

|      | 5.7.3   | Interrupt Enable Conditions                                          | 237 |

|------|---------|----------------------------------------------------------------------|-----|

| 5.8  | Reset ( | Operation                                                            | 237 |

|      |         |                                                                      |     |

| Sect | ion 6   | Direct Memory Access Controller (DMAC)                               | 239 |

| 6.1  | Overvi  | ew                                                                   | 239 |

|      | 6.1.1   | Functions                                                            | 239 |

|      | 6.1.2   | Configuration and Operation                                          | 240 |

| 6.2  | Registe | ers                                                                  | 241 |

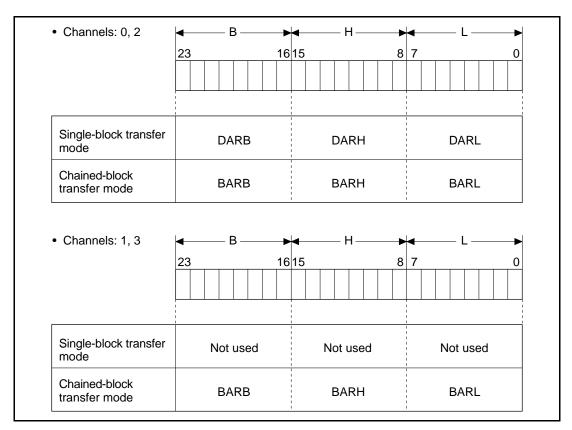

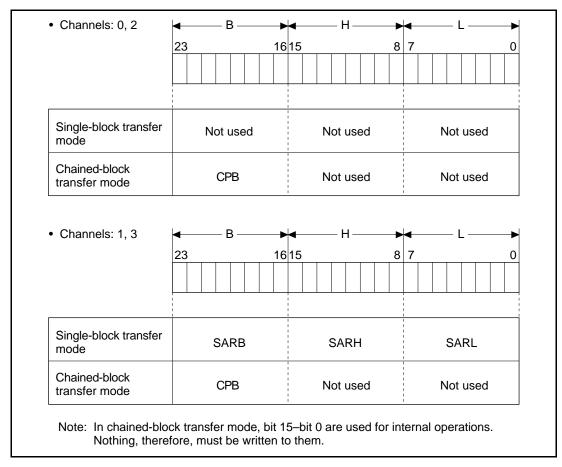

|      | 6.2.1   | Channels 0, 2: Destination Address Register (DAR: DARL, DARH, DARB)/ |     |

|      |         | Buffer Address Register (BAR: BARL, BARH, BARB)                      |     |

|      |         | Channels 1, 3: Buffer Address Register (BAR: BARL, BARH, BARB)       | 241 |

|      | 6.2.2   | Channels 0, 2: Chain Pointer Base (CPB)                              |     |

|      |         | Channels 1, 3: Source Address Register (SAR: SARL, SARH, SARB)/      |     |

|      |         | Chain Pointer Base (CPB)                                             | 242 |

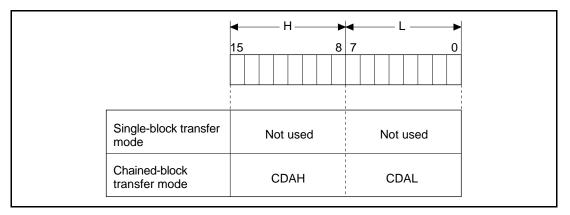

|      | 6.2.3   | Current Descriptor Address Register (CDA: CDAL, CDAH)                | 244 |

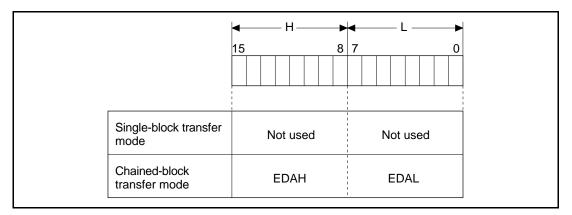

|      | 6.2.4   | Error Descriptor Address Register (EDA: EDAL, EDAH)                  | 245 |

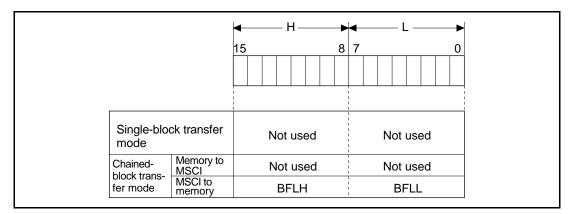

|      | 6.2.5   | Receive Buffer Length Register (BFL: BFLL, BFLH)                     | 246 |

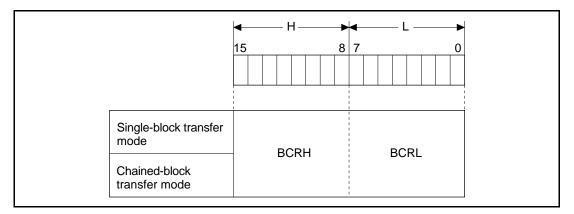

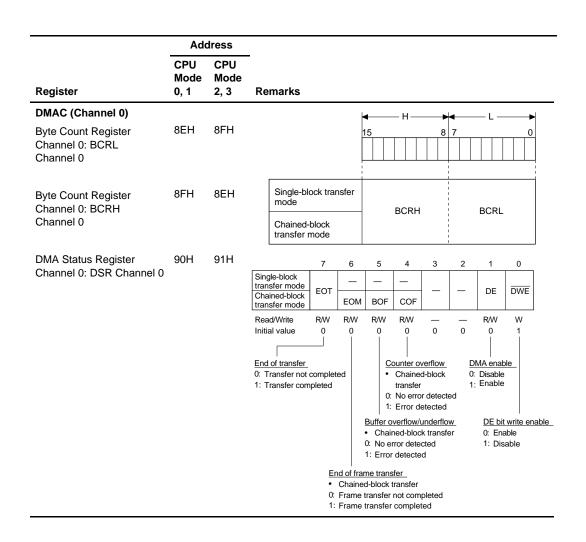

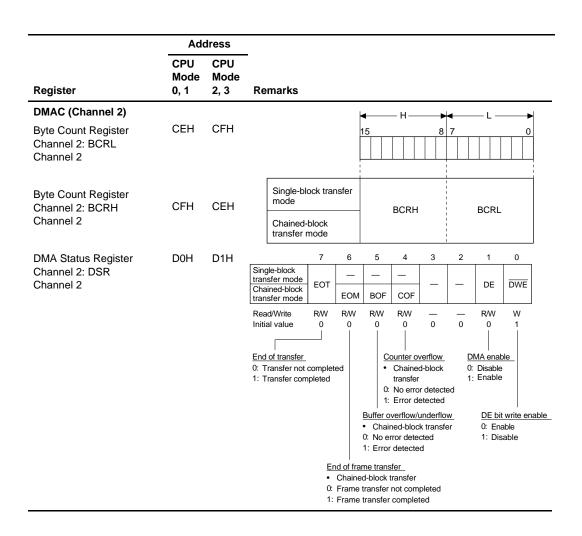

|      | 6.2.6   | Byte Count Register (BCR: BCRL, BCRH)                                | 247 |

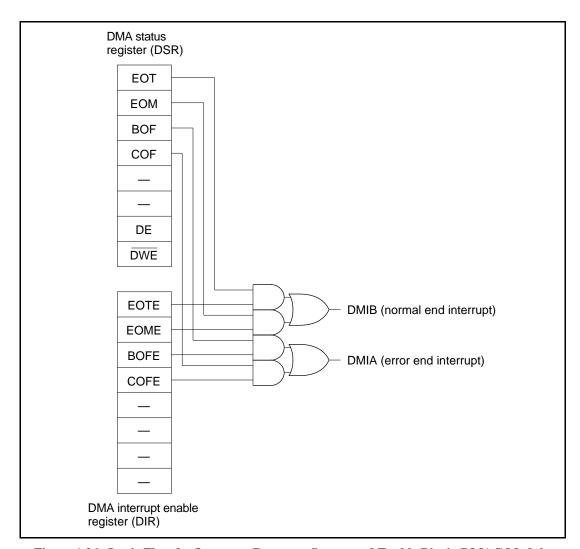

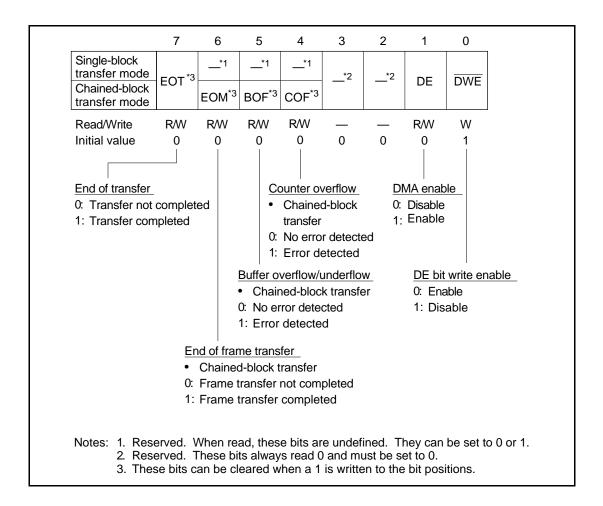

|      | 6.2.7   | DMA Status Register (DSR)                                            | 248 |

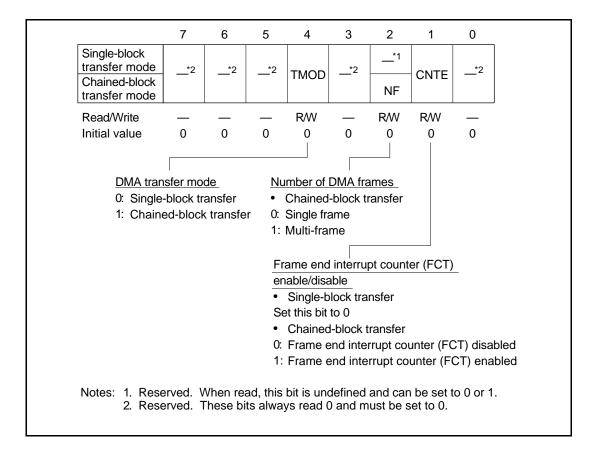

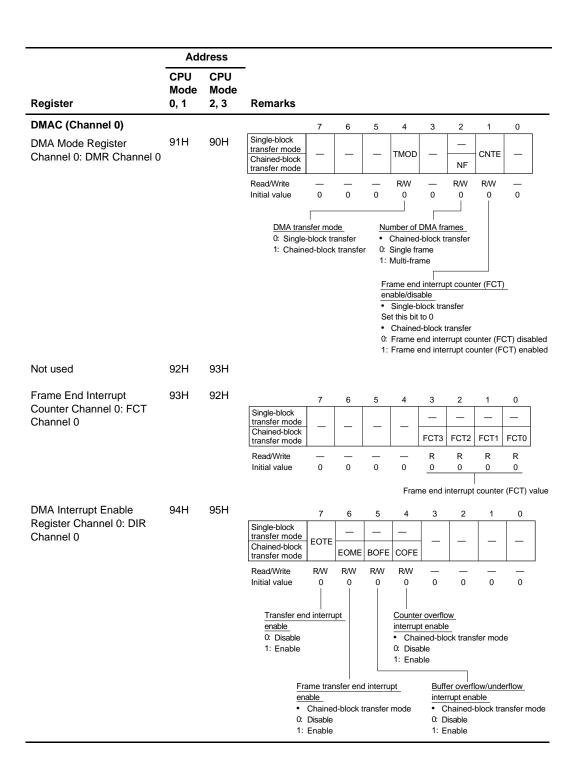

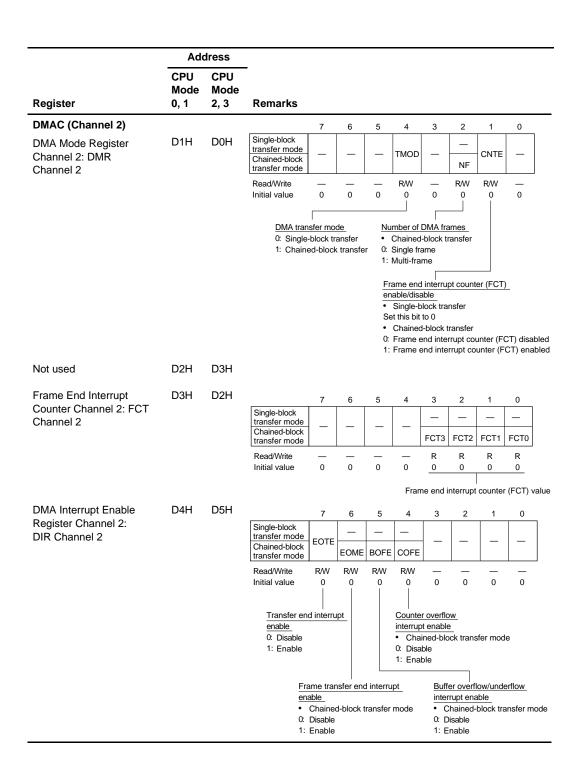

|      | 6.2.8   | DMA Mode Register (DMR)                                              | 251 |

|      | 6.2.9   | Frame End Interrupt Counter (FCT)                                    | 253 |

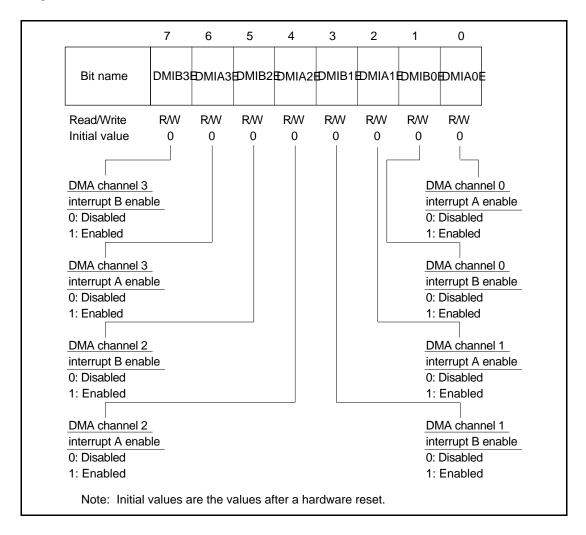

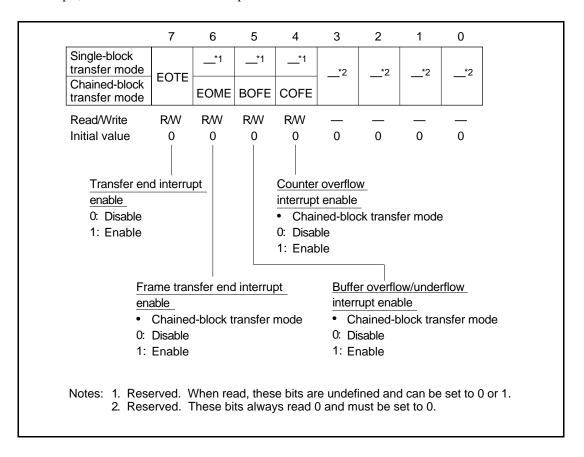

|      | 6.2.10  | DMA Interrupt Enable Register (DIR)                                  | 254 |

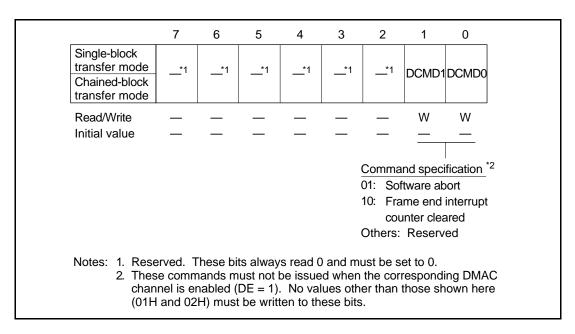

|      | 6.2.11  | DMA Command Register (DCR)                                           | 256 |

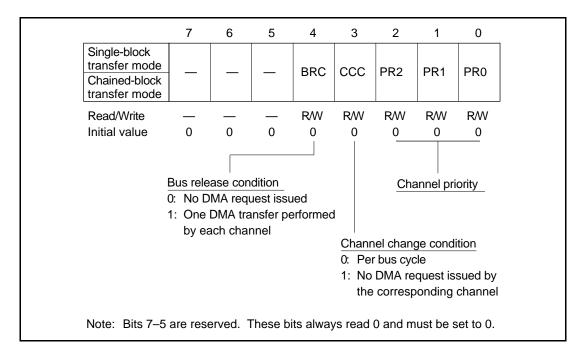

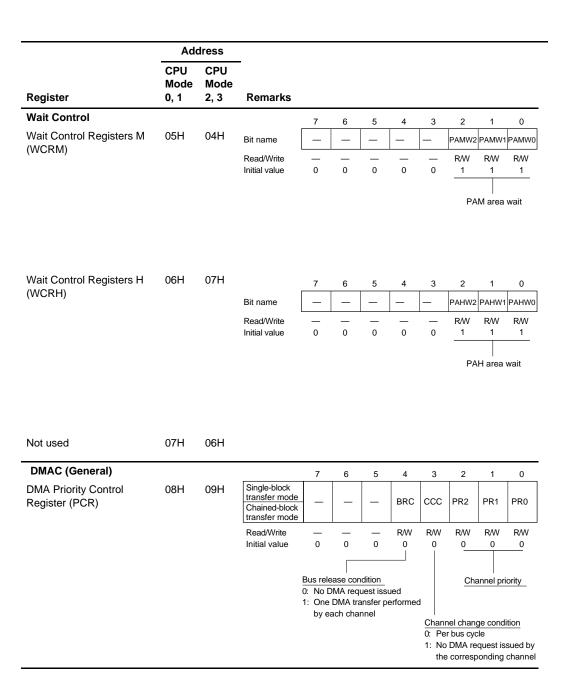

|      | 6.2.12  | DMA Priority Control Register (PCR)                                  | 258 |

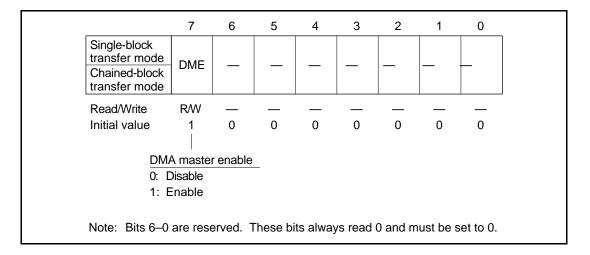

|      | 6.2.13  | DMA Master Enable Register (DMER)                                    | 260 |

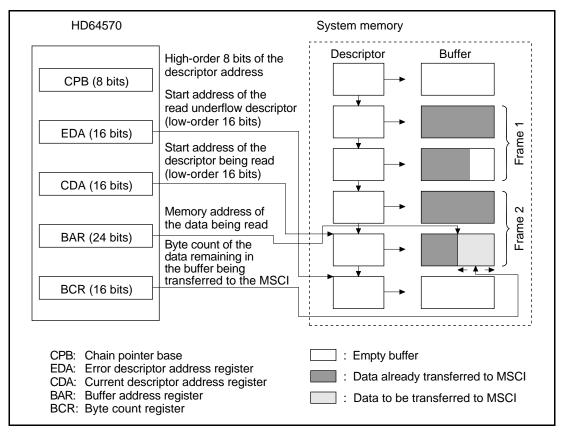

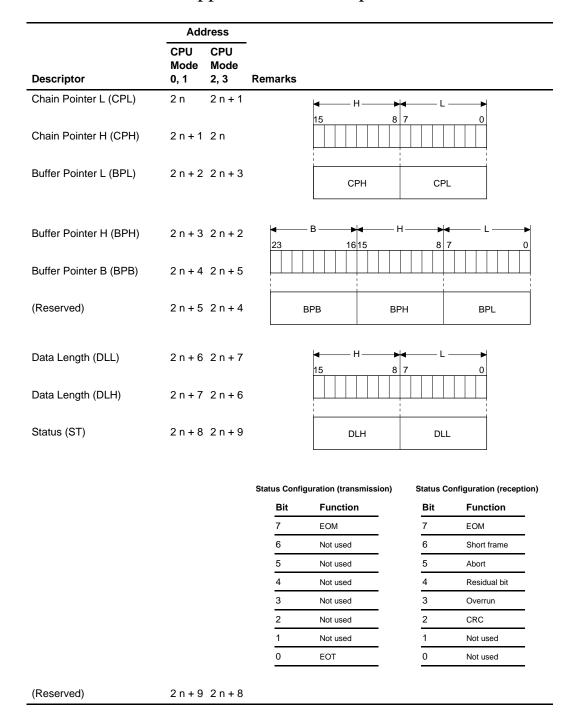

| 6.3  | Descrip | otors                                                                | 261 |

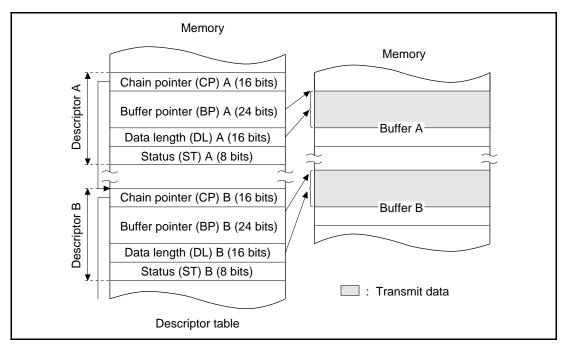

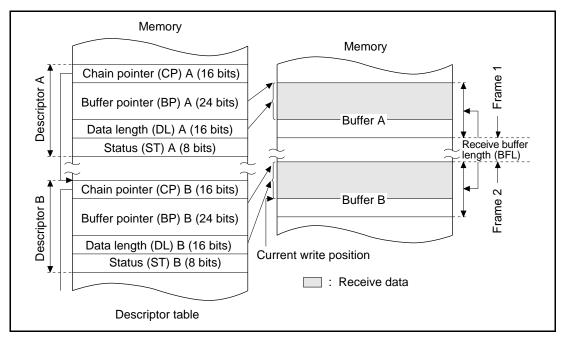

|      | 6.3.1   | Memory-to-MSCI Chained-Block Transfer Mode (Transmission)            | 261 |

|      | 6.3.2   | MSCI-to-Memory Chained-Block Transfer Mode (Reception)               | 263 |

| 6.4  | Operat  | ing Modes                                                            | 265 |

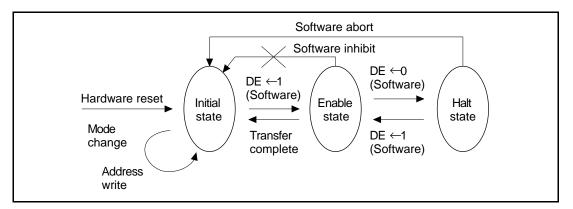

|      | 6.4.1   | Overview                                                             | 265 |

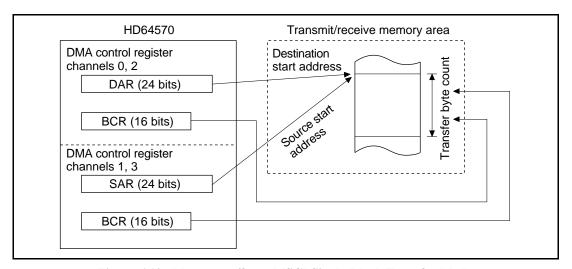

|      | 6.4.2   | Memory-to/from-MSCI Single-Block Transfer Mode                       | 267 |

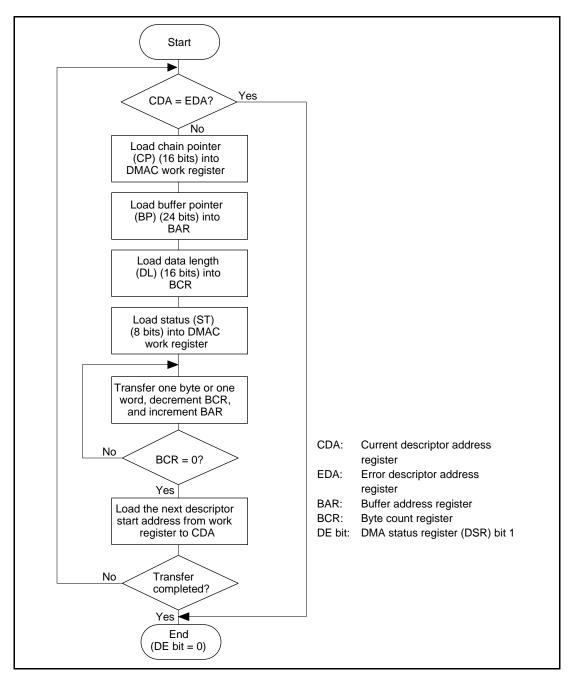

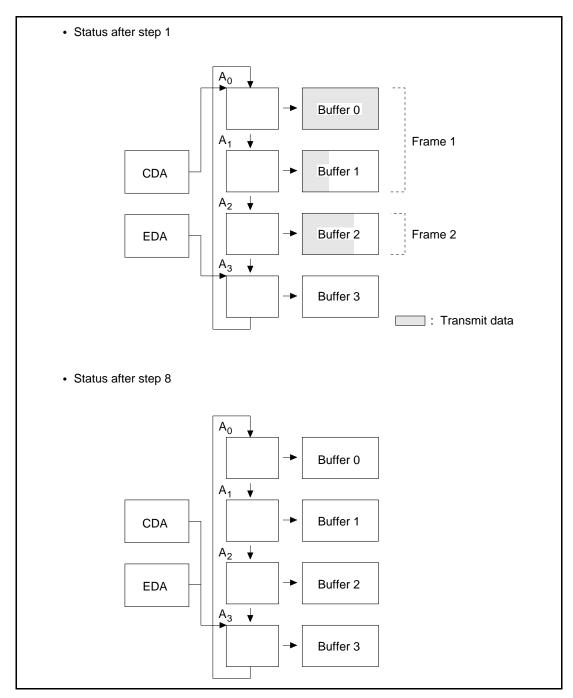

|      | 6.4.3   | Memory-to-MSCI Chained-Block Transfer Mode                           | 271 |

|      | 6.4.4   | MSCI-to-Memory Chained-Block Transfer Mode                           | 285 |

|      | 6.4.5   | DMAC Characteristics                                                 | 299 |

| 6.5  | Interru | pts                                                                  | 300 |

| 6.6  |         | Operation                                                            |     |

| 6.7  | Precau  | tions                                                                | 301 |

| ~    | . –     |                                                                      |     |

|      | ion 7   | Timer                                                                |     |

| 7.1  |         | ew                                                                   |     |

|      | 7.1.1   | Functions                                                            |     |

|      | 7.1.2   | Configuration and Operation                                          |     |

| 7.2  | _       | ers                                                                  | 304 |

| _    | 0 07/00 |                                                                      |     |

Rev. 0, 07/98, page iv of 11

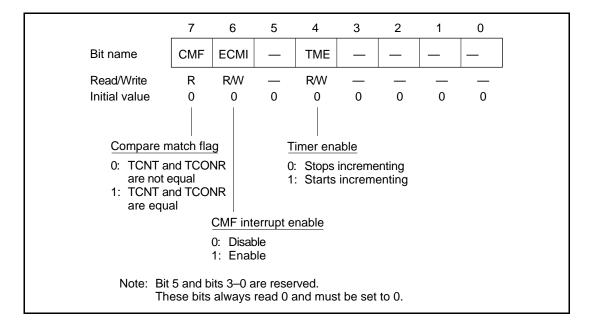

|      | 7.2.1    | Timer up-counter (TCNT: TCNTH, TCNTL)                   | 304  |

|------|----------|---------------------------------------------------------|------|

|      | 7.2.2    | Timer Constant Register (TCONR: TCONRH, TCONRL)         | 305  |

|      | 7.2.3    | Timer Control/Status Register (TCSR)                    | 306  |

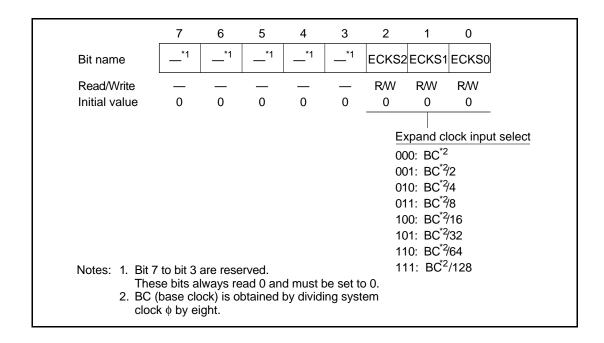

|      | 7.2.4    | Timer Expand Prescale Register (TEPR)                   | 307  |

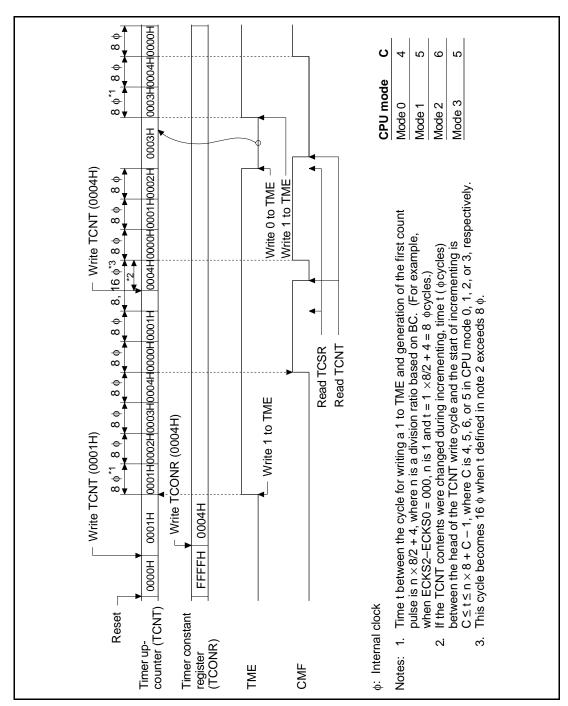

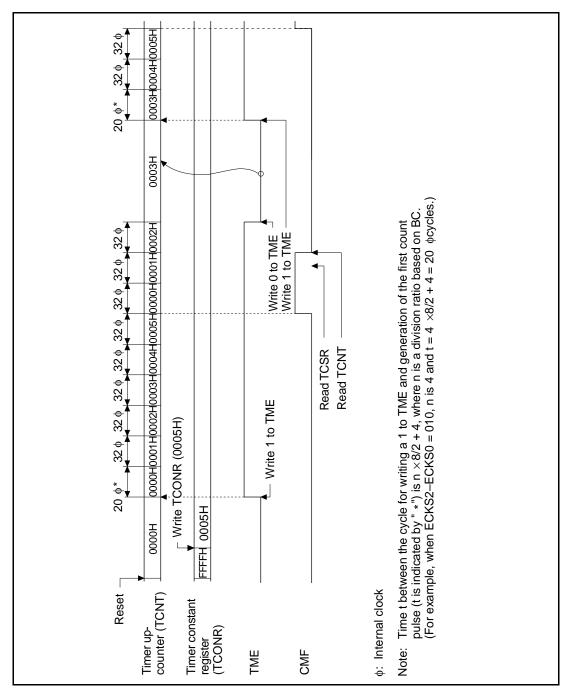

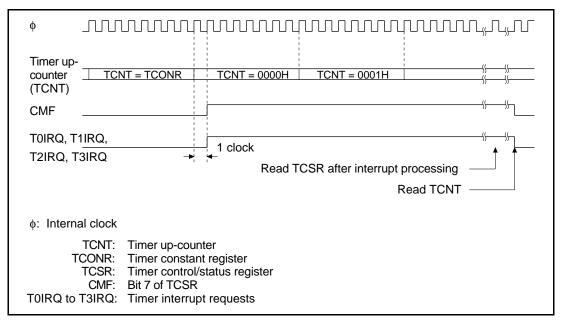

| 7.3  | Operat   | ion Timing                                              | 308  |

|      | 7.3.1    | Timer Increment Timing                                  | 308  |

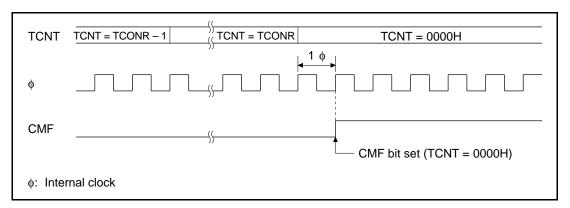

|      | 7.3.2    | Output Timing                                           | 311  |

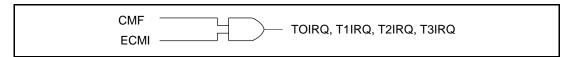

| 7.4  | Interru  | pt                                                      | 311  |

| 7.5  | Operat   | ion in System Stop Mode                                 | 312  |

| 7.6  | Reset C  | Operation                                               | 312  |

| 7.7  | Precau   | tions                                                   | 313  |

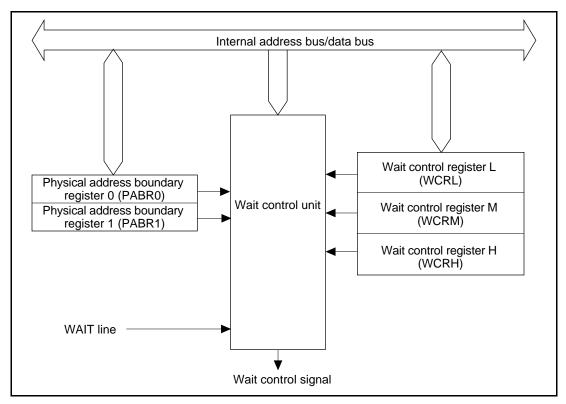

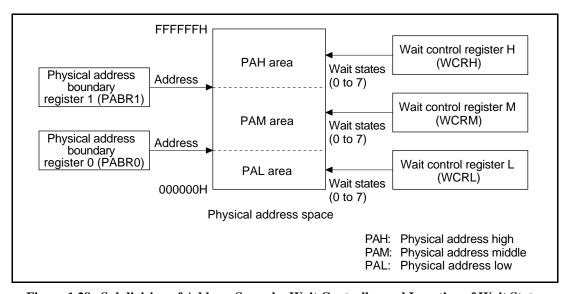

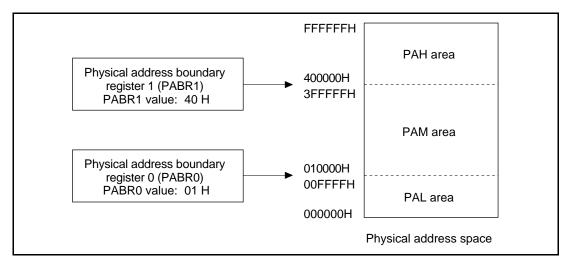

| Sect | ion 8    | Wait Controller                                         | 315  |

| 8.1  | Overvi   | ew                                                      | 315  |

|      | 8.1.1    | Functions                                               | 315  |

|      | 8.1.2    | Configuration and Operation                             | 315  |

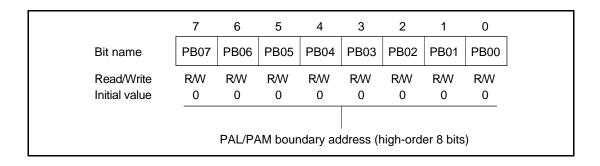

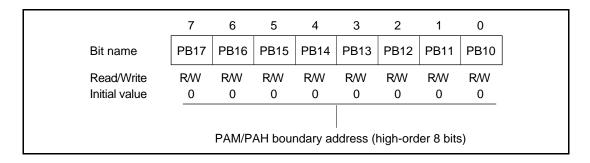

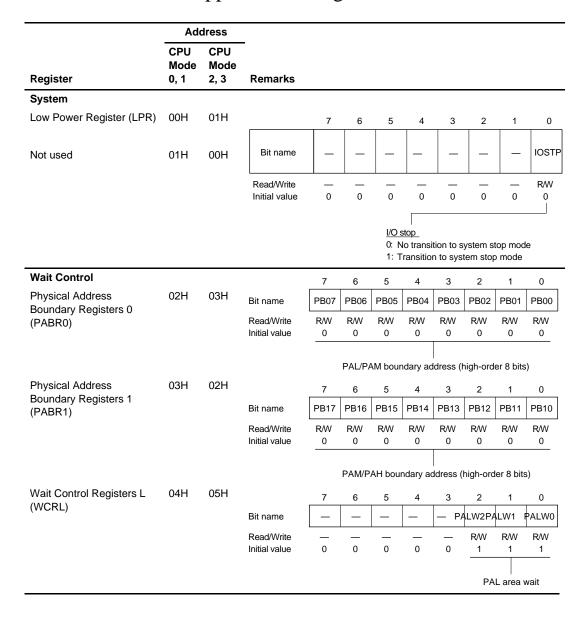

| 8.2  | Registe  | ers                                                     | 316  |

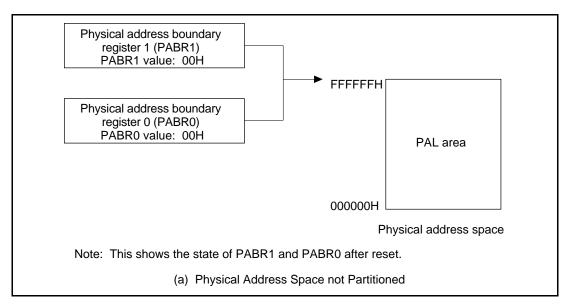

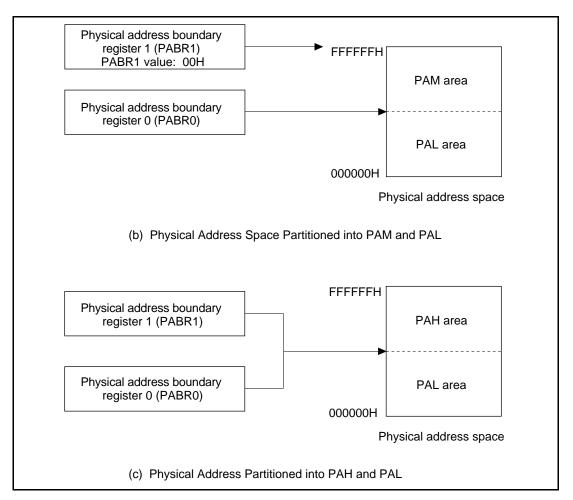

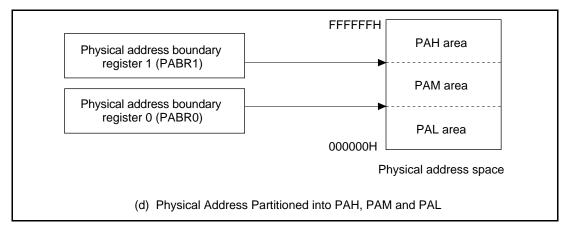

|      | 8.2.1    | Physical Address Boundary Registers 0, 1 (PABR0, PABR1) | 316  |

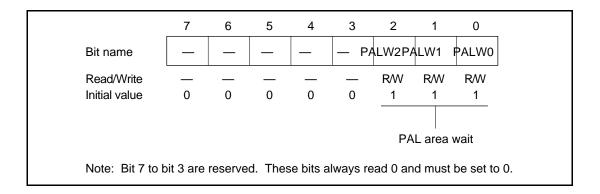

|      | 8.2.2    | Wait Control Registers L, M, H (WCRL, WCRM, WCRH)       | 321  |

| 8.3  | Operat   | ion                                                     | 324  |

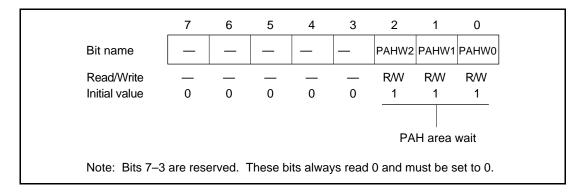

|      | 8.3.1    | Wait State Insertion Using the WAIT Line                | 324  |

|      | 8.3.2    | Wait State Insertion Using the Register                 | 325  |

| 8.4  | Operat   | ion in System Stop Mode                                 | 325  |

| 8.5  | Reset C  | Operation                                               | 325  |

| 8.6  | Precau   | tions                                                   | 325  |

| Sect | ion 9    | Application Examples                                    | 327  |

| 9.1  | Applica  | ation Examples                                          | 327  |

|      | 9.1.1    | Serial Data Transfer by MPU and DMAC                    | 327  |

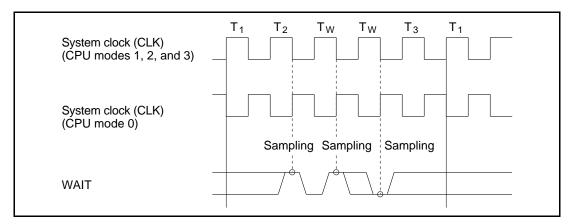

|      | 9.1.2    | Transmission by Programmed I/O (Bi-Sync Mode)           | 328  |

|      | 9.1.3    | Reception by Programmed I/O (Bi-Sync Mode)              | 331  |

|      | 9.1.4    | Transmission in DMA Chained-Block Transfer Mode         |      |

|      |          | (Bit Synchronous HDLC Mode)                             | 334  |

|      | 9.1.5    | Reception in DMA Chained-Block Transfer Mode            |      |

|      |          | (Bit Synchronous HDLC Mode)                             | 336  |

| 9.2  | Applica  | ation Circuits                                          | 338  |

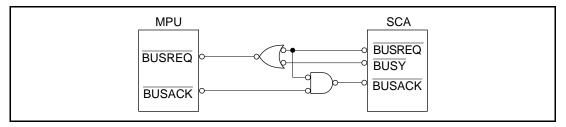

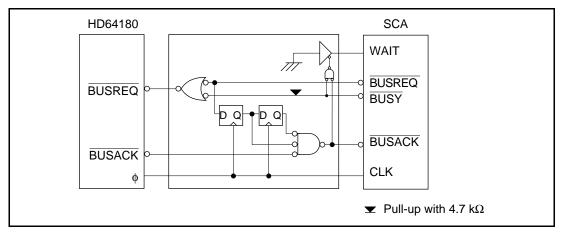

|      | 9.2.1    | System Configuration Example                            | 338  |

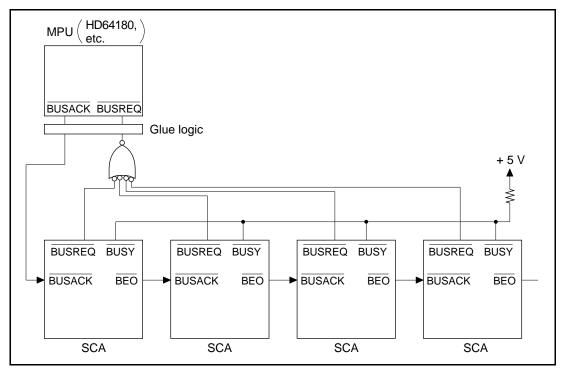

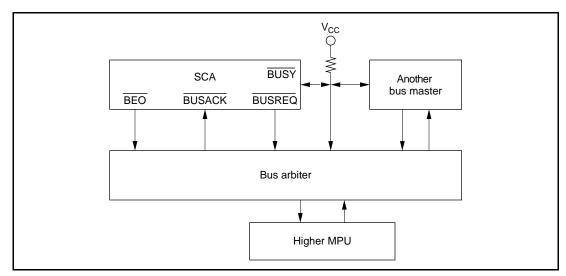

|      | 9.2.2    | Bus Arbitration Block                                   | 338  |

| Sect | ion 10   | Electrical Characteristics                              | 341  |

| 10.1 | Electric | cal Characteristics of HD64570CP and HD64570F           | 341  |

|      | 10.1.1   | Absolute Maximum Ratings                                | 341  |

|      |          | DC Characteristics                                      | 3/12 |

Rev. 0, 07/98, page v of 11

|       | 10.1.3   | AC Characteristics                               | 343 |

|-------|----------|--------------------------------------------------|-----|

| 10.2  | Electric | al Characteristics of HD64570CP16 and HD64570F16 | 353 |

|       | 10.2.1   | Absolute Maximum Ratings                         | 353 |

|       | 10.2.2   | DC Characteristics                               | 354 |

|       | 10.2.3   | AC Characteristics                               | 355 |

| 10.3  | Electric | al Characteristics of HD64570CP8I and HD64570F8I | 365 |

|       | 10.3.1   | Absolute Maximum Ratings                         | 365 |

|       | 10.3.2   | DC Characteristics                               | 366 |

|       | 10.3.3   | AC Characteristics                               | 367 |

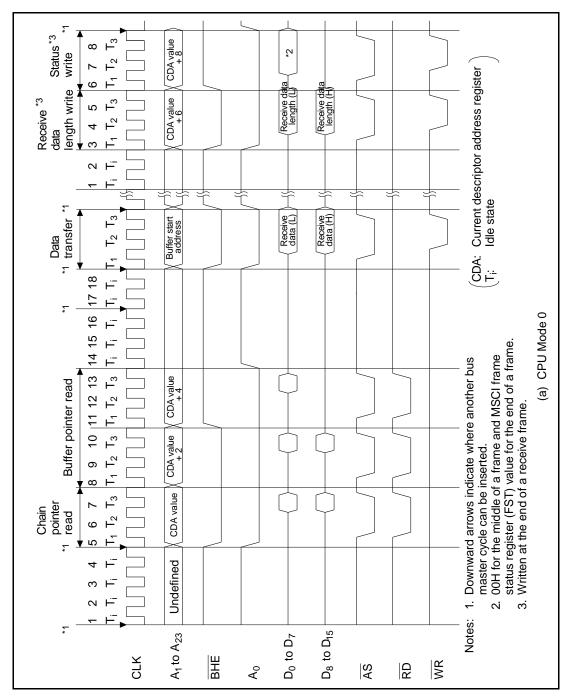

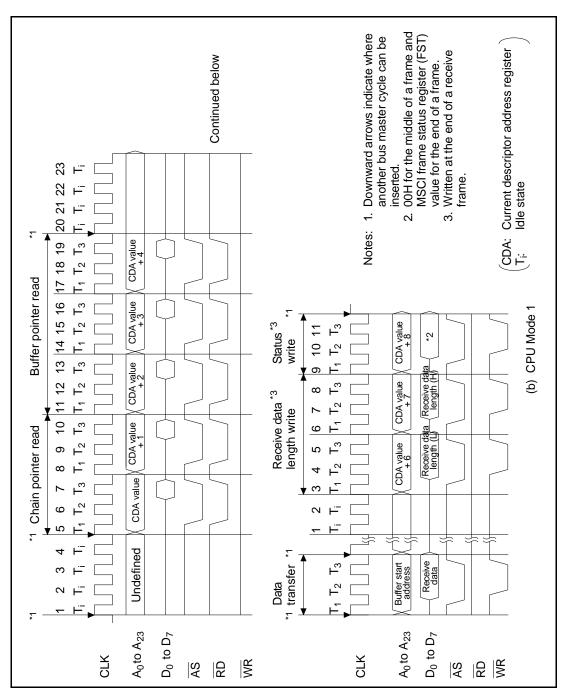

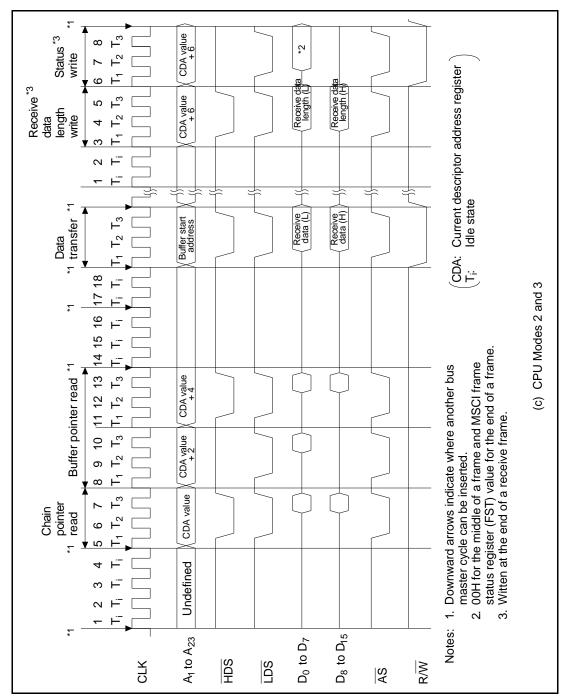

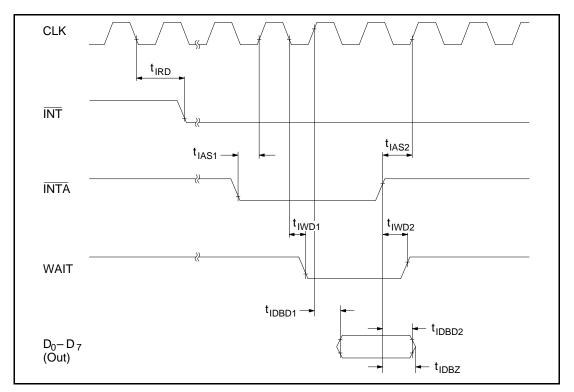

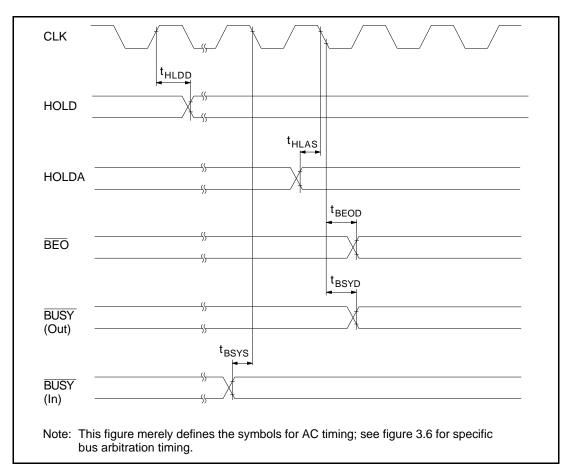

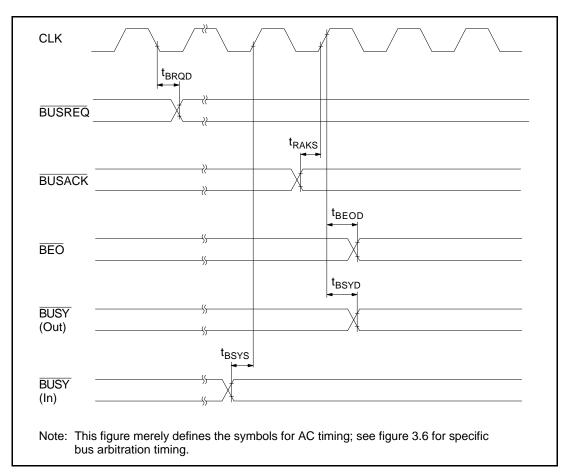

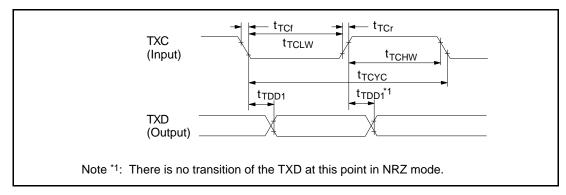

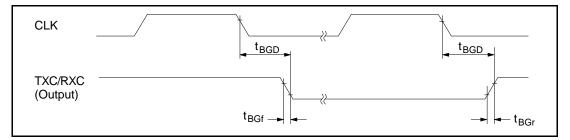

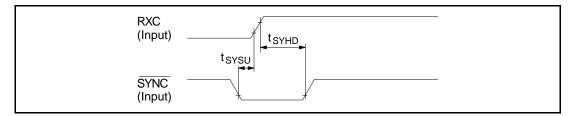

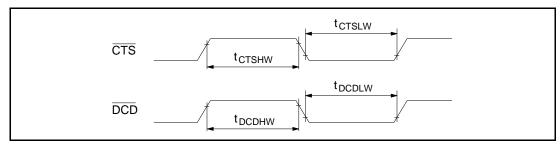

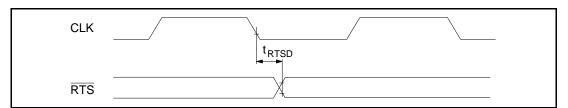

| 10.4  | Timing   | Diagrams                                         | 377 |

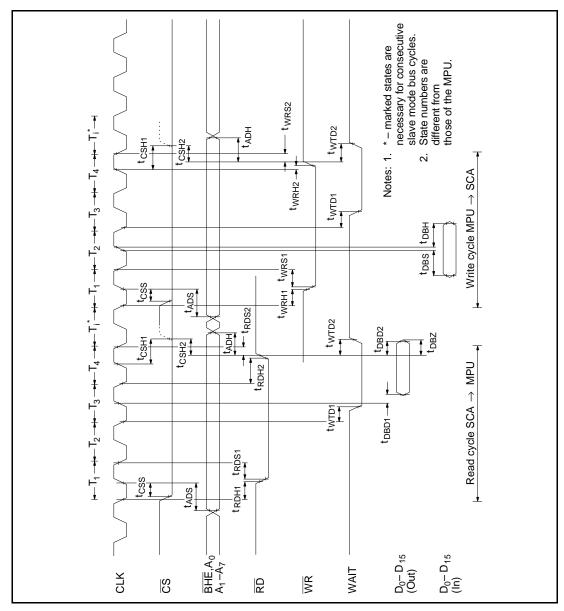

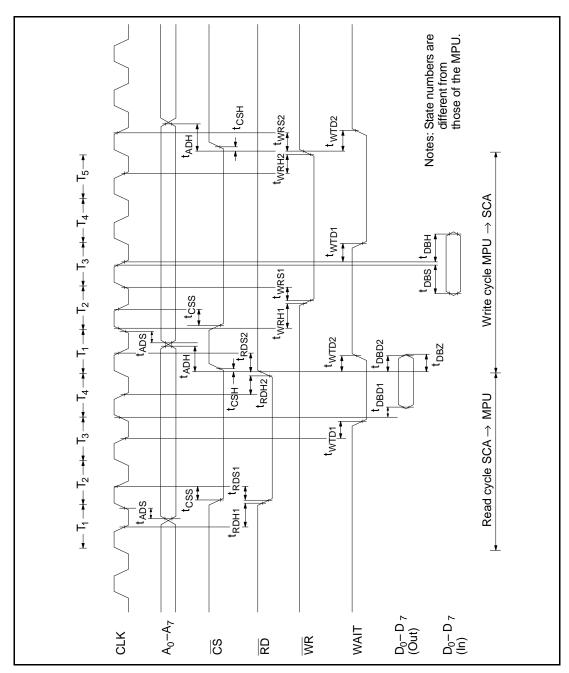

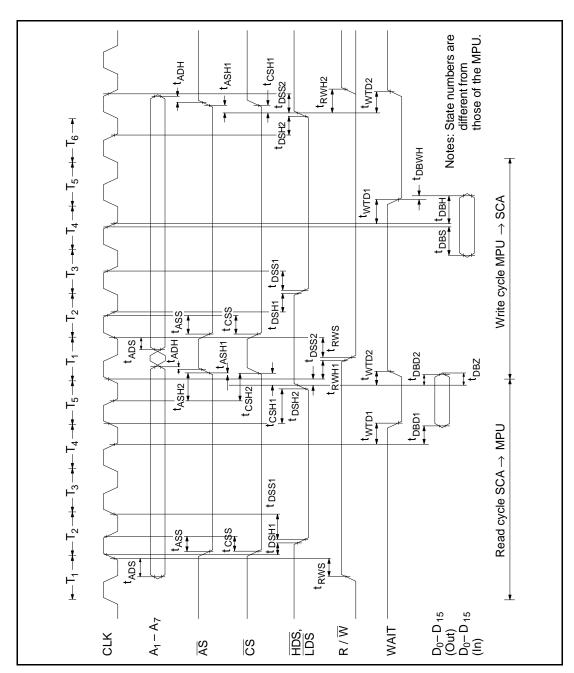

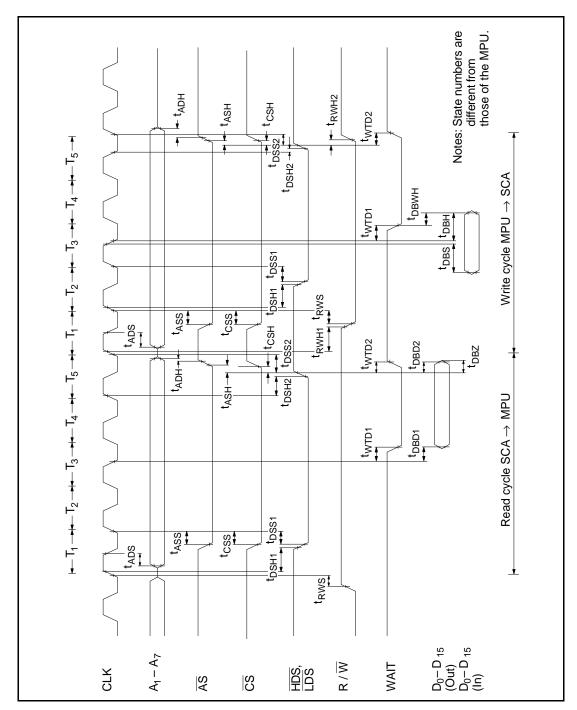

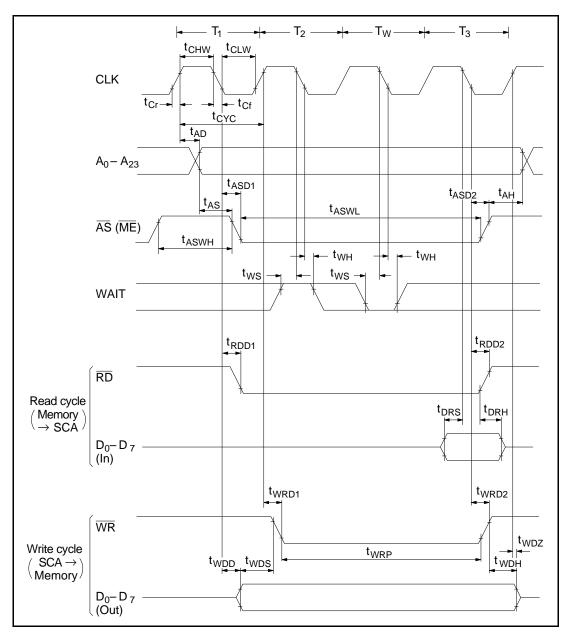

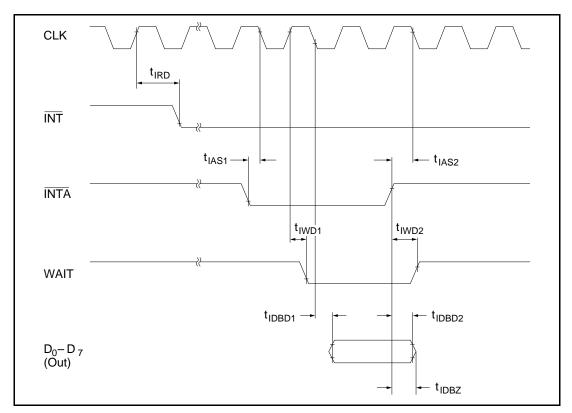

|       | 10.4.1   | Slave Mode Bus Timing                            | 377 |

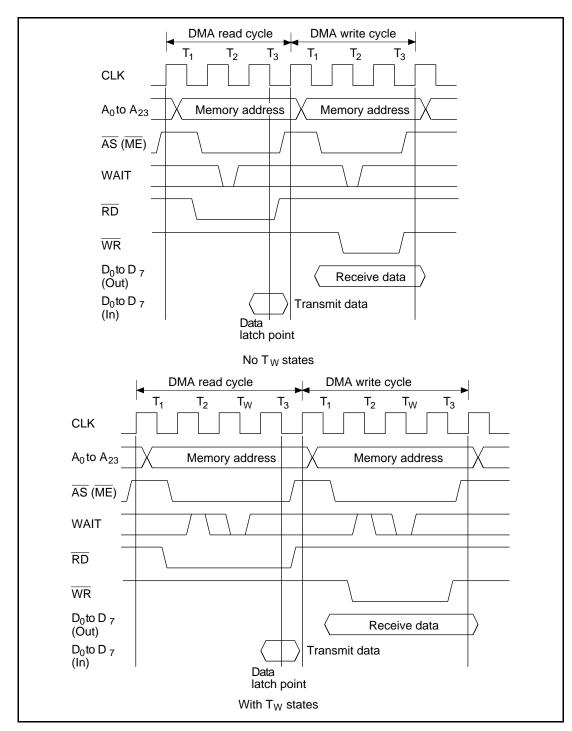

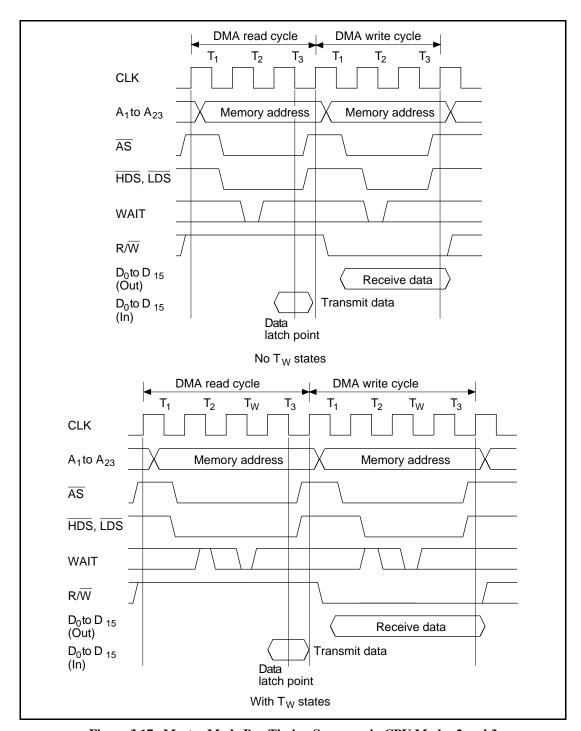

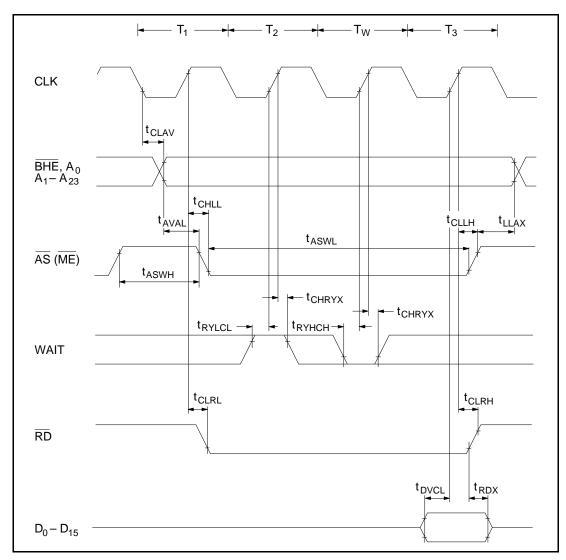

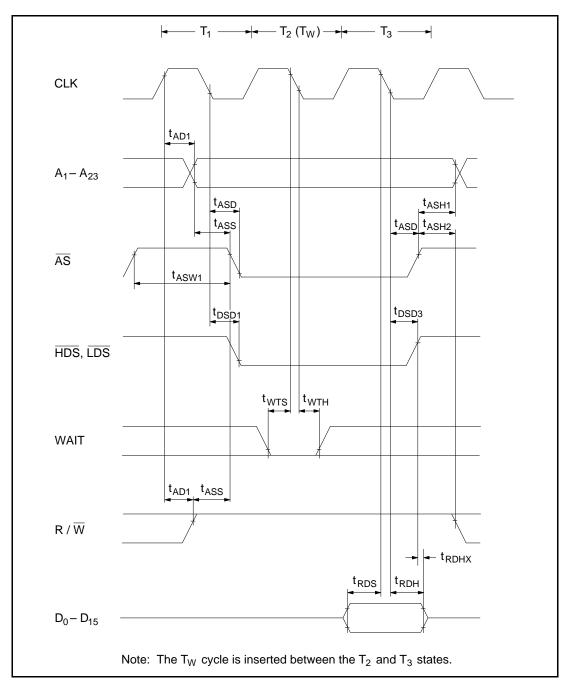

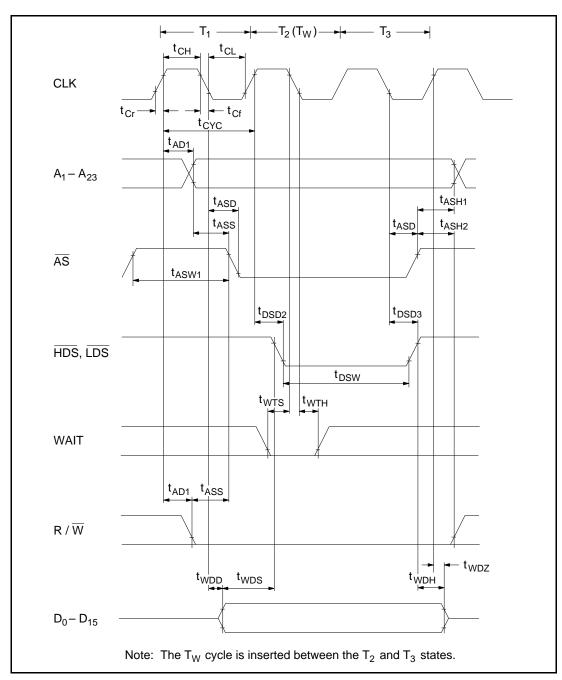

|       | 10.4.2   | Master Mode Bus Timing                           | 381 |

| Secti | on 11    | Package Dimensions                               | 393 |

| Appe  | ndix A   | Descriptors                                      | 395 |

| Appe  | ndix B   | Registers                                        | 396 |

Rev. 0, 07/98, page vi of 11

# Section 1 Overview

#### 1.1 Overview

The HD64570 serial communications adaptor (SCA) converts parallel data to serial data for communication with other devices. Its two independent, full-duplex transceivers support both synchronous (bit-synchronous or byte-synchronous) and asynchronous communication. Extensive protocol functions are provided.

The SCA chip provides FIFO transmit and receive buffers with 32 stages each and a four-channel direct memory access controller (DMAC) with chained-block transfer facilities, enabling high-speed transfer of data between SCA and memory. A built-in bus arbiter and 16-bit bus interface support high-performance system designs.

#### 1.2 Features

- Data transfer rate: 50 bits/s to 7.1 Mbits/s (f = 10 MHz),

50 bits/s to 12 Mbits/s (f = 16.7 MHz)

50 bits/s to 5.7 Mbits/s (f = 8 MHz)\*

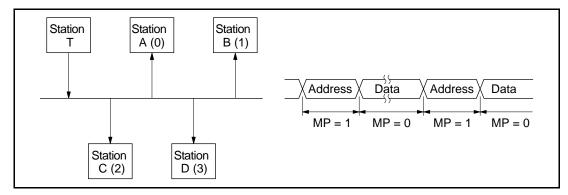

- Protocol support

- Asynchronous (ASYNC): 5 to 8 bits + parity

- Byte synchronous (COP): bisync, X.21, DDCMP, etc.

- Bit synchronous (BOP): frame relay, HDLC, ™SDLC, X.25 link level (LAPB), LAPD etc.

- Highly efficient data transfer: two 32-byte FIFOs (transmit/receive) per channel

- Error detection: parity (asynchronous)

CRC-16, CRC-CCITT (byte- and bit-synchronous)

TMSDLC is a trademark of International Business Machine.

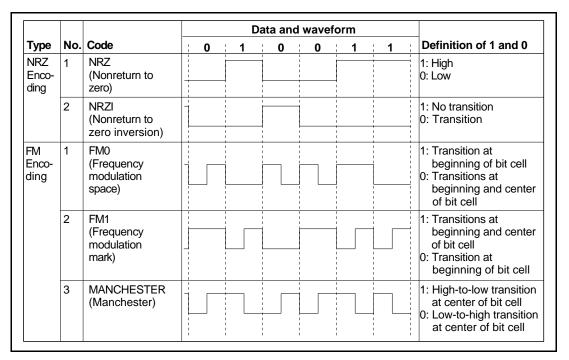

Transmission codes: NRZ, NRZI, FM0, FM1, Manchester

Operating modes: normal operating mode (full-duplex), auto echo, local loop back DMA transfer: on-chip DMAC with four channels and chained-block transfer capability

Address space: 16 Mbytes

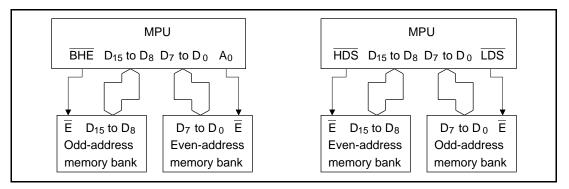

Bus interface: connects to 64180-, 8086-, and 68000-system 8-/16-bit MPU buses

Timers: time-out detection, etc.

Power supply:  $5 \text{ V} \pm 10\% \text{ (-20 to } 75^{\circ}\text{C)} \text{ for } 10\text{-MHz chip,}$

5 V  $\pm$  5% (0 to 70°C) for 16.7-MHz chip 5 V  $\pm$  10% (-40 to 85°C) for 8-MHz chip\*

Rev. 0, 07/98, page 1 of 453

# **1.3** Basic Functions

**Table 1.1** Major Functions of the SCA

| Item                                                |                              | Specification                                                                                                                                                                                                                                      |

|-----------------------------------------------------|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MSCI (multiprotocol serial communication interface) | Maximum data transfer rate   | 7.1 Mbits/s (f = 10 MHz) 12 Mbits/s (f = 16.7 MHz) 5.7 Mbits/s (f = 8 MHz)*                                                                                                                                                                        |

|                                                     | Number of channels           | 2                                                                                                                                                                                                                                                  |

|                                                     | Operating modes              | Normal operating mode (full duplex) Auto echo mode Local loop back mode                                                                                                                                                                            |

|                                                     | Protocol functions           | Asynchronous: 5 to 8 bits, parity (odd, even, or none) Byte synchronous: mono-sync, bi-sync, or external synchronization Bit synchronous: HDLC mode                                                                                                |

|                                                     | Error detection              | Five types (parity error, framing error, CRC error, overrun error, underrun error)                                                                                                                                                                 |

|                                                     | Transmission codes           | Five types (NRZ, NRZI, FM0, FM1, Manchester)                                                                                                                                                                                                       |

|                                                     | FIFO                         | Transmit—32 bytes/receive—32 bytes                                                                                                                                                                                                                 |

|                                                     | Clock sources                | Internal clock sources:  1. On-chip baud rate generators can generate arbitrary baud rates (independent transmit/receive baud rate generators are provided for each channel)  2. On-chip digital PLL (independent ADPLLs for each receive channel) |

|                                                     |                              | External clock                                                                                                                                                                                                                                     |

|                                                     | Modem control                | CTS, RTS, DCD                                                                                                                                                                                                                                      |

|                                                     | ADPLL (Advanced digital PLL) | On-chip advanced digital PLLs:  1. For extraction of clock signals  2. For suppressing noise in received data and clock signals                                                                                                                    |

|                                                     | Baud rate generator          | On-chip (independent transmit and receive baud rate generators for each channel)                                                                                                                                                                   |

| Bus interface                                       | MPU modes                    | Four externally selectable modes:  1. 8086-system 16-bit MPU 2. 64180-system 8-bit MPU 3. 68000-system 16-bit MPUI 4. 68000-system 16-bit MPUII                                                                                                    |

|                                                     | Data bus width               | 8 or 16 bits                                                                                                                                                                                                                                       |

|                                                     | Data bas wiatii              | 0 0. 10 0.10                                                                                                                                                                                                                                       |

Rev. 0, 07/98, page 2 of 453

Table 1.1

Major Functions of the SCA (cont)

| Item                                        |                   |                   | Specification                                                                                                                               | 1                                                                   |                               |  |

|---------------------------------------------|-------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|-------------------------------|--|

| DMAC<br>(direct memory<br>access controller |                   | of channels       | 4                                                                                                                                           |                                                                     |                               |  |

|                                             | Transfer          | r modes           | DMA transfer                                                                                                                                | between memory and on-                                              | chip MSCI:                    |  |

|                                             |                   |                   | synchronous                                                                                                                                 | ck transfer (asynchronous,<br>modes)<br>lock transfer (bit-synchron |                               |  |

|                                             | Minimur<br>cycle  | m transfer        | 3 clocks                                                                                                                                    |                                                                     |                               |  |

| Timers                                      | Number            | of channels       | 4                                                                                                                                           |                                                                     |                               |  |

|                                             | Counter           | length            | 16 bits                                                                                                                                     |                                                                     |                               |  |

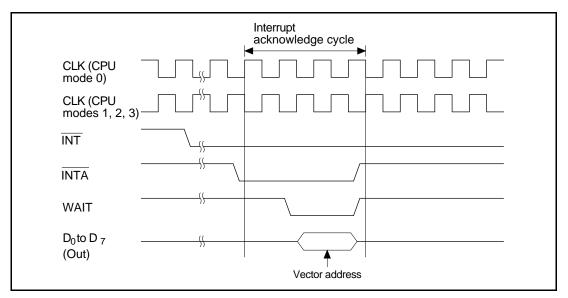

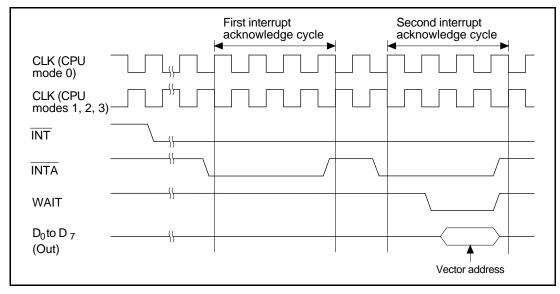

| Interrupt controlle                         | er Acknow         | ledge cycle       | Programmabl                                                                                                                                 | e:                                                                  |                               |  |

|                                             |                   |                   | •                                                                                                                                           | wledge cycle<br>nowledge cycle<br>knowledge cycle                   |                               |  |

|                                             | Vector o          | output mode       |                                                                                                                                             | e:<br>or output mode<br>ector output mode                           |                               |  |

| Wait state contro                           | ller              |                   | On-chip (register programmable, or external line control)                                                                                   |                                                                     |                               |  |

| Bus arbiter                                 |                   |                   | On-chip (can be daisy-chained)                                                                                                              |                                                                     |                               |  |

| Low-power mode                              | 9                 |                   | System stop mode supported                                                                                                                  |                                                                     |                               |  |

| Maximum system                              | n clock rate      |                   | 10 MHz or 16.7 MHz                                                                                                                          |                                                                     |                               |  |

| Signal level                                |                   |                   | TTL-compatible TTL-compatible                                                                                                               |                                                                     |                               |  |

| Supply voltage                              |                   |                   | +5 V $\pm$ 10% (–20 to 75°C) for 10-MHz chip<br>+5 V $\pm$ 5% (0 to 70°C) for 16.7-MHz chip<br>+5 V $\pm$ 10% (–40 to 85°C) for 8-MHz chip* |                                                                     |                               |  |

| Process                                     |                   |                   | CMOS                                                                                                                                        |                                                                     |                               |  |

| Package                                     |                   |                   | leaded chip ca                                                                                                                              | o QFJ (PLCC) (quad flat j-le<br>arrier))<br>QFP (quad flat package) | eaded package (plastic        |  |

| Product lineup                              | Туре              | Product<br>Number | Maximum<br>Operating<br>Frequency                                                                                                           |                                                                     | Package                       |  |

|                                             | SCA               | HD64570CF         | 2 10 MHz                                                                                                                                    | +5 V $\pm$ 10% (–20 to 75°C)                                        | (PLCC))                       |  |

|                                             | LP-t-O            | HD64570F          | 24040 7 144                                                                                                                                 | . 5 \ / 1 50 /                                                      | FP-88 (88-pin QFP)            |  |

|                                             | High Speed<br>SCA |                   | P1616.7 MHz                                                                                                                                 | +5 V ±5%<br>(0 to 70°C)                                             | CP-84 (84-pin QFJ<br>(PLCC))  |  |

|                                             | WITD CCA          | HD64570F1         |                                                                                                                                             | .E.V.  400/                                                         | FP-88 (88-pin QFP)            |  |

|                                             | WTR SCA           | HD64570CF         |                                                                                                                                             | +5 V ±10%<br>(-40 to 85°C)                                          | CP-84 (84-pin QFJ<br>(PLCC))* |  |

|                                             |                   | HD64570F8         | 81                                                                                                                                          |                                                                     | FP-88 (88-pin QFP)*           |  |

Rev. 0, 07/98, page 3 of 453

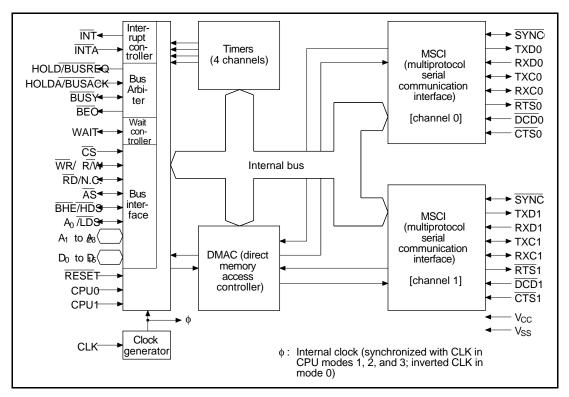

# 1.4 Block Diagram

Figure 1.1 Block Diagram of SCA

Rev. 0, 07/98, page 4 of 453

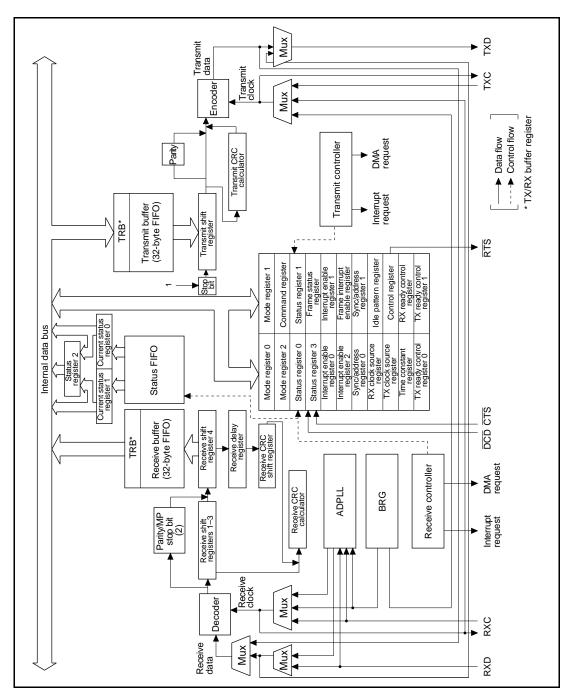

Figure 1.2 MSCI Block Diagram

Rev. 0, 07/98, page 5 of 453

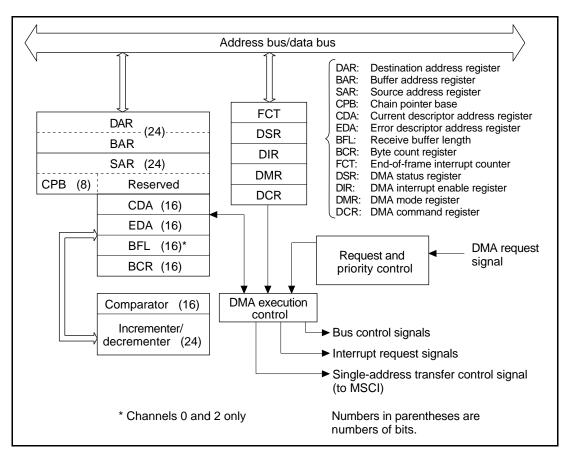

Figure 1.3 DMAC Block Diagram (one channel)

Rev. 0, 07/98, page 6 of 453

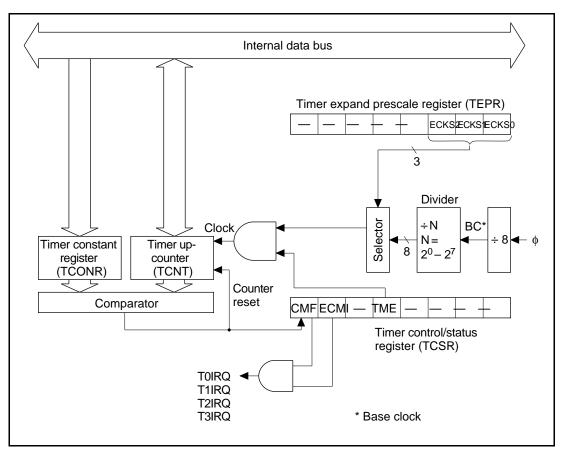

Figure 1.4 Timer Block Diagram

Rev. 0, 07/98, page 7 of 453

Figure 1.5 Wait Controller Block Diagram

# 1.5 Protocol Support

# 1.5.1 Asynchronous Mode

| Item                   | Description                                   |

|------------------------|-----------------------------------------------|

| Character length       | 5 to 8 bits                                   |

| Parity                 | Odd or even parity or no parity               |

| Stop bits              | 1, 1.5, or 2                                  |

| Transmit/receive clock | 1x, 16x, 32x, or 64x mode                     |

| Error detection        | Parity errors, overrun errors, framing errors |

| Break signal           | Can generate break signal of arbitrary length |

| Break detection        | Detects beginning and end of break            |

| Multiprocessor support | By MP bit                                     |

|                        |                                               |

Rev. 0, 07/98, page 8 of 453

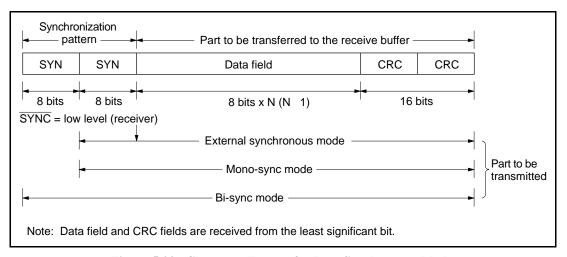

# 1.5.2 Byte-Synchronous Mode

| Item                     | Description                                        |

|--------------------------|----------------------------------------------------|

| Character length         | 8 bits                                             |

| Error control            | Generates and checks CRC codes (CRC-16, CRC-CCITT) |

| Synchronous characters   | 1 or 2 characters                                  |

| External synchronization | Supported                                          |

| Synchronization          | Can transmit, detect and delete SYN character      |

| Underrun                 | Idle, or CRC + idle output                         |

| Idle                     | Mark or SYN character output                       |

| Error detection          | CRC error, overrun error, underrun error           |

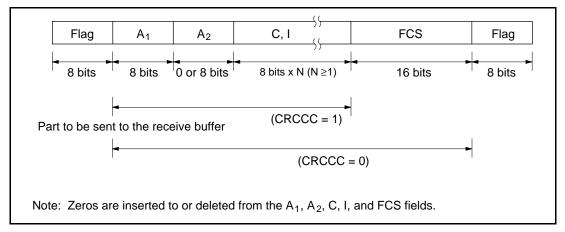

# 1.5.3 Bit-Synchronous Mode

| Item              | Description                                                                    |

|-------------------|--------------------------------------------------------------------------------|

| Character length  | 8 bits                                                                         |

| Error control     | Generates and checks CRC codes (CRC-16, CRC-CCITT)                             |

| Bit pattern       | Detects and generates flag, abort, and idle                                    |

| Frame subdivision | Detects subdivision flag (single flag) between frames                          |

| Address field     | Four address field checks (can recognize group addresses and global addresses) |

| End of frame      | When EOM is received                                                           |

| Data input/output | Zero insert/delete                                                             |

| Residual bits     | Detects residual bit frames                                                    |

| Short frame       | Detects short (invalid) frames                                                 |

| Underrun          | Abort + idle, or FCS + flag + idle                                             |

| Idle              | Mark or flag                                                                   |

|                   |                                                                                |

Rev. 0, 07/98, page 9 of 453

# 1.6 Built-In Registers

# 1.6.1 Low-Power Mode Control Registers

| Register Name      | Symbol |     | CPU Modes<br>2 & 3 | Initial Value at Hardware Res |   |   |   |   |   |   | lese | t<br>Read/<br>Write |

|--------------------|--------|-----|--------------------|-------------------------------|---|---|---|---|---|---|------|---------------------|

|                    |        |     |                    | MSB LSB                       |   |   |   |   |   |   |      |                     |

| Low power register | LPR    | 00H | 01H                | 0                             | 0 | 0 | 0 | 0 | 0 | 0 | 0    | R/W                 |

# 1.6.2 Interrupt Control Registers

|                                    |        |           |           | Initial Value at Hardware Reset |   |   |   |   |   |    | t<br>Read/<br>Write |     |

|------------------------------------|--------|-----------|-----------|---------------------------------|---|---|---|---|---|----|---------------------|-----|

| Register Name                      | Symbol | Channel 0 | Channel 1 | MSB                             |   |   |   |   |   | LS | SB                  | _   |

| Interrupt vector register          | IVR    | 1AH       | 1BH       | 0                               | 0 | 0 | 0 | 0 | 0 | 0  | 0                   | R/W |

| Interrupt modified vector register | IMVR   | 1CH       | 1DH       | 0                               | 0 | 0 | 0 | 0 | 0 | 0  | 0                   | R/W |

| Interrupt control register         | ITCR   | 18H       | 19H       | 0                               | 0 | 0 | 0 | 0 | 0 | 0  | 0                   | R/W |

| Interrupt status register 0        | ISR0   | 10H       | 11H       | 0                               | 0 | 0 | 0 | 0 | 0 | 0  | 0                   | R   |

| Interrupt status register 1        | ISR1   | 11H       | 10H       | 0                               | 0 | 0 | 0 | 0 | 0 | 0  | 0                   | R   |

| Interrupt status register 2        | ISR2   | 12H       | 13H       | 0                               | 0 | 0 | 0 | 0 | 0 | 0  | 0                   | R   |

| Interrupt enable register 0        | IER0   | 14H       | 15H       | 0                               | 0 | 0 | 0 | 0 | 0 | 0  | 0                   | R/W |

| Interrupt enable register 1        | IER1   | 15H       | 14H       | 0                               | 0 | 0 | 0 | 0 | 0 | 0  | 0                   | R/W |

| Interrupt enable register 2        | IER2   | 16H       | 17H       | 0                               | 0 | 0 | 0 | 0 | 0 | 0  | 0                   | R/W |

Rev. 0, 07/98, page 10 of 453

### 1.6.3 MSCI Registers (1)

|                                 |        | CPU Mode  | _         | lni       | tial      | Valu | ue a | t Re | set | *1 | Read/<br>Write* <sup>2</sup> |                |    |     |

|---------------------------------|--------|-----------|-----------|-----------|-----------|------|------|------|-----|----|------------------------------|----------------|----|-----|

| Register Name                   | Symbol | Channel 0 | Channel 1 | Channel 0 | Channel 1 | MS   | SB   |      |     |    |                              | L              | SB | _   |

| Mode register 0                 | MD0    | 2EH       | 4EH       | 2FH       | 4FH       | 0    | 0    | 0    | 0   | 0  | 0                            | 0              | 0  | R/W |

| Mode register 1                 | MD1    | 2FH       | 4FH       | 2EM       | 4EH       | 0    | 0    | 0    | 0   | 0  | 0                            | 0              | 0  | R/W |

| Mode register 2                 | MD2    | 30H       | 50H       | 31H       | 51H       | 0    | 0    | 0    | 0   | 0  | 0                            | 0              | 0  | R/W |

| Control register                | CTL    | 31H       | 51H       | 30H       | 50H       | 0    | 0    | 0    | 0   | 0  | 0                            | 0              | 1  | R/W |

| RX clock source register        | RXS    | 36H       | 56H       | 37H       | 57H       | 0    | 0    | 0    | 0   | 0  | 0                            | 0              | 0  | R/W |

| TX clock source register        | TXS    | 37H       | 57H       | 36H       | 56H       | 0    | 0    | 0    | 0   | 0  | 0                            | 0              | 0  | R/W |

| Time constant register          | TMC    | 35H       | 55H       | 34H       | 54H       | 0    | 0    | 0    | 0   | 0  | 0                            | 0              | 1  | R/W |

| Command register                | CMD    | 2CH       | 4CH       | 2DH       | 4DH       |      |      |      |     |    |                              |                |    | W   |

| Status register 0               | ST0    | 22H       | 42H       | 23H       | 43H       | 0    | 0    | 0    | 0   | 0  | 0                            | 0              | 0  | R   |

| Status register 1               | ST1    | 23H       | 43H       | 22H       | 42H       | 0    | 0    | 0    | 0   | 0  | 0                            | 0              | 0  | R/W |

| Status register 2               | ST2    | 24H       | 44H       | 25H       | 45H       | 0    | 0    | 0    | 0   | 0  | 0                            | 0              | 0  | R/W |

| Status register 3               | ST3    | 25H       | 45H       | 24H       | 44H       | 0    | 0    | 0    | 0   | ×  | ×*                           | <sup>3</sup> 0 | 0  | R   |

| Frame status register           | FST    | 26H       | 46H       | 27H       | 47H       | 0    | 0    | 0    | 0   | 0  | 0                            | 0              | 0  | R/W |

| Interrupt enable register 0     | IE0    | 28H       | 48H       | 29H       | 49H       | 0    | 0    | 0    | 0   | 0  | 0                            | 0              | 0  | R/W |

| Interrupt enable register 1     | IE1    | 29H       | 49H       | 28H       | 48H       | 0    | 0    | 0    | 0   | 0  | 0                            | 0              | 0  | R/W |

| Interrupt enable register 2     | IE2    | 2AH       | 4AH       | 2BH       | 4BH       | 0    | 0    | 0    | 0   | 0  | 0                            | 0              | 0  | R/W |

| Frame interrupt enable register | FIE    | 2BH       | 4BH       | 2AH       | 4AH       | 0    | 0    | 0    | 0   | 0  | 0                            | 0              | 0  | R/W |

| Sync/address register 0         | SA0    | 32H       | 52H       | 33H       | 53H       | 1    | 1    | 1    | 1   | 1  | 1                            | 1              | 1  | R/W |

| Sync/address register 1         | SA1    | 33H       | 53H       | 32H       | 52H       | 1    | 1    | 1    | 1   | 1  | 1                            | 1              | 1  | R/W |

| Idle pattern register           | IDL    | 34H       | 54H       | 35H       | 55H       | 1    | 1    | 1    | 1   | 1  | 1                            | 1              | 1  | R/W |

- Notes: 1. These initial values apply after a hardware reset or execution of a channel reset command. Some registers are also initialized to these values by the RX reset command or TX reset command. See section 5.2, Registers, for details.

- 2. The functions of some bits vary depending on the operating mode (asynchronous, byte synchronous, or bit synchronous). See the register descriptions starting in section 5.2.1.

- 3. When bits 3 and 2 of status register 3 (ST3) are read, the logic level of the  $\overline{\text{CTS}}$  and  $\overline{\text{DCD}}$  lines are read.

Rev. 0, 07/98, page 11 of 453

### 1.6.3 MSCI Registers (2)

|                             |        |           | Ad        |           |           |                |   |   |   |   |   |    |       |

|-----------------------------|--------|-----------|-----------|-----------|-----------|----------------|---|---|---|---|---|----|-------|

|                             |        | CPU Mo    | des 0 & 1 | CPU Mo    | In        | Read/W<br>rite |   |   |   |   |   |    |       |

| Register Name               | Symbol | Channel 0 | Channel 1 | Channel 0 | Channel 1 | MSB            |   |   |   |   | L | SB | _     |

| TX/RX buffer register       | TRBL   | 20H       | 40H       | 21H       | 41H       | ××             | × | × | × | × | × | ×  | R/W*3 |

|                             | TRBH   | 21H       | 41H       | 20H       | 40H       | ××             | × | × | × | × | × | ×  | R/W*3 |

| RX ready control register   | RRC    | ЗАН       | 5AH       | 3BH       | 5BH       | 0 0            | 0 | 0 | 0 | 0 | 0 | 0  | R/W   |

| TX ready control register ( | TRC0   | 38H       | 58H       | 39H       | 59H       | 0 0            | 0 | 0 | 0 | 0 | 0 | 0  | R/W   |

| TX ready control register   | 1 TRC1 | 39H       | 59H       | 38H       | 58H       | 0 0            | 0 | 1 | 1 | 1 | 1 | 1  | R/W   |

| Current status register 0   | CST0   | 3CH       | 5CH       | 3DH       | 5DH       | 0 0            | 0 | 0 | 0 | 0 | 0 | 0  | R/W   |

| Current status register 1   | CST1   | 3DH       | 5DH       | 3CH       | 5CH       | 0 0            | 0 | 0 | 0 | 0 | 0 | 0  | R/W   |

- Notes: 1. These initial values apply after a hardware reset or execution of a channel reset command. Some registers are also initialized to these values by the RX reset command or TX reset command. See section 5.2, Registers, for details.

- 2. The functions of some bits vary depending on the operating mode (asynchronous, byte synchronous, or bit synchronous). See the register descriptions starting in section 5.2.1.

- 3. The TX/RX buffer register (TRBL, TRBH) acts as the receive buffer register for the received character when read, and as the transmit buffer register for the transmitted character when written.

### 1.6.4 DMAC Registers Common to Channels 0 to 3

|                               |        | Add                | dress           | _   |                    |   |   |   |   |               |    |     |  |  |  |  |

|-------------------------------|--------|--------------------|-----------------|-----|--------------------|---|---|---|---|---------------|----|-----|--|--|--|--|

|                               |        | CPU Modes<br>0 & 1 | CPU Modes 2 & 3 | lni | Initial Value at H |   |   |   |   | ardware Reset |    |     |  |  |  |  |

| Register Name                 | Symbol |                    |                 | MS  | SB                 |   |   |   |   | L             | SB | -   |  |  |  |  |

| DMA priority control register | IPCR   | 08H                | 09H             | 0   | 0                  | 0 | 0 | 0 | 0 | 0             | 0  | R/W |  |  |  |  |

| DMA master enable register    | DMER   | 09H                | 08H             | 1   | 0                  | 0 | 0 | 0 | 0 | 0             | 0  | R/W |  |  |  |  |

Note: Use byte access to read and write PCR and DMER. These registers cannot be accessed by word access.

Rev. 0, 07/98, page 12 of 453

# 1.6.5 DMA Registers Provided Separately for Channels 0 to 3

|                                                                             |                | Address |                                 |                |                |                |                |                |                |    |   |                |   |   |   |   |     |

|-----------------------------------------------------------------------------|----------------|---------|---------------------------------|----------------|----------------|----------------|----------------|----------------|----------------|----|---|----------------|---|---|---|---|-----|

|                                                                             |                | (       | CPU Modes 0 & 1 CPU Modes 2 & 3 |                |                |                |                |                | & 3            | _  |   | Read/<br>Write |   |   |   |   |     |

| Register<br>Name                                                            | Symbol         |         | Chan-<br>nel 1                  | Chan-<br>nel 2 | Chan-<br>nel 3 | Chan-<br>nel 0 | Chan-<br>nel 1 | Chan-<br>nel 2 | Chan-<br>nel 3 |    |   |                |   |   |   |   | -   |

| Destination<br>address<br>register L<br>(buffer<br>address<br>register L)*1 | DARL<br>(BARL) | 80H     | A0H                             | C0H            | E0H            | 81H            | A1H            | C1H            | E1H            | ×× | × | ×              | × | × | × | × | R/W |

| Destination<br>address<br>register H<br>(buffer<br>address<br>register H)*1 | DARH<br>(BARH) | 81H     | A1H                             | C1H            | E1H            | 80H            | A0H            | C0H            | E0H            | ×× | × | ×              | × | × | × | × | R/W |

| Destination<br>address<br>register B<br>(buffer<br>address<br>register B)*1 | DARB<br>(BARB) | 82H     | A2H                             | C2H            | E2H            | 83H            | АЗН            | C3H            | E3H            | ×× | × | ×              | × | × | × | × | R/W |

| Source<br>address<br>register L*2                                           | SARL           | _       | A4H                             | _              | E4H            | _              | A5H            | _              | E5H            | ×× | × | ×              | × | × | × | × | R/W |

| Source<br>address<br>register H*2                                           | SARH           | _       | A5H                             | _              | E5H            | _              | A4H            | _              | E4H            | ×× | × | ×              | × | × | × | × | R/W |

| Source<br>address<br>register B<br>(chain pointer<br>base)*1                | SARB<br>(CPB)  | 86H     | A6H                             | C6H            | E6H            | 87H            | А7Н            | C7H            | E7H            | ×× | × | ×              | × | × | × | × | R/W |

| Current<br>descriptor<br>address<br>register L                              | CDAL           | 88H     | A8H                             | C8H            | E8H            | 89H            | А9Н            | C9H            | Е9Н            | ×× | × | ×              | × | × | × | × | R/W |

(x: undefined)

- Notes: 1. Parentheses indicate registers with different functions in single-block transfer mode and chained-block transfer mode. The name in parentheses applies in chained-block transfer mode. See the register descriptions for details.

- 2. These registers are not used in chained-block transfer mode. Avoid writing to these registers in chained-block transfer mode.

Rev. 0, 07/98, page 13 of 453

# 1.6.5 DMA Registers Provided Separately for Channels 0 to 3 (cont)

|                                                |        | Address                         |                |                |                |                |                |                |                |    | _  |   |   |   |              |    |    |                |

|------------------------------------------------|--------|---------------------------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----|----|---|---|---|--------------|----|----|----------------|

|                                                |        | CPU Modes 0 & 1 CPU Modes 2 & 3 |                |                |                |                |                |                |                |    |    |   |   |   | lue a<br>Res |    |    | Read/<br>Write |

| Register<br>Name                               | Symbol |                                 | Chan-<br>nel 1 | Chan-<br>nel 2 | Chan-<br>nel 3 | Chan-<br>nel 0 | Chan-<br>nel 1 | Chan-<br>nel 2 | Chan-<br>nel 3 |    |    |   |   |   |              |    |    | _              |

|                                                |        |                                 |                |                |                |                |                |                |                | MS | SB |   |   |   |              | LS | SB |                |

| Current<br>descriptor<br>address<br>register H | CDAH   | 89H                             | А9Н            | C9H            | E9H            | 88H            | А8Н            | C8H            | E8H            | ×  | ×  | × | × | × | ×            | ×  | ×  | R/W            |

| Error<br>descriptor<br>address<br>register L   | EDAL   | 8AH                             | AAH            | CAH            | EAH            | 8BH            | ABH            | CBH            | EBH            | ×  | ×  | × | × | × | ×            | ×  | ×  | R/W            |

| Error<br>descriptor<br>address<br>register H   | EDAH   | 8BH                             | ABH            | CBH            | EBH            | 8AH            | ААН            | CAH            | EAH            | ×  | ×  | × | × | × | ×            | ×  | ×  | R/W            |

| Receive<br>buffer length<br>L*2                | BFLL   | 8CH                             | —              | ССН            | _              | 8DH            | —              | CDH            | _              | ×  | ×  | × | × | × | ×            | ×  | ×  | R/W            |

| Receive<br>buffer length<br>H*2                | BFLH   | 8DH                             | _              | CDH            | _              | 8CH            | _              | CCH            | _              | ×  | ×  | × | × | × | ×            | ×  | ×  | R/W            |

| Byte count register L                          | BCRL   | 8EH                             | AEH            | CEH            | EEH            | 8FH            | AFH            | CFH            | EFH            | ×  | ×  | × | × | × | ×            | ×  | ×  | R/W            |

| Byte count register H                          | BCRH   | 8FH                             | AFH            | CFH            | EFH            | 8EH            | AEH            | CEH            | EEH            | ×  | ×  | × | × | × | ×            | ×  | ×  | R/W            |

| DMA status register*1                          | DSR    | 90H                             | вон            | D0H            | F0H            | 91H            | В1Н            | D1H            | F1H            | 0  | 0  | 0 | 0 | 0 | 0            | 0  | 1  | R/W            |

| DMA mode register                              | DMR    | 91H                             | В1Н            | D1H            | F1H            | 90H            | ВОН            | D0H            | F0H            | 0  | 0  | 0 | 0 | 0 | 0            | 0  | 0  | R/W            |

| End-of-frame interrupt counter                 | FCT    | 93H                             | взн            | D3H            | F3H            | 92H            | B2H            | D2H            | F2H            | 0  | 0  | 0 | 0 | 0 | 0            | 0  | 0  | R              |

| DMA interrupt<br>enable<br>register            | DIR    | 94H                             | В4Н            | D4H            | F4H            | 95H            | В5Н            | D5H            | F5H            | 0  | 0  | 0 | 0 | 0 | 0            | 0  | 0  | R/W            |

| DMA<br>command<br>register                     | DCR    | 95H                             | В5Н            | D5H            | F5H            | 94H            | В4Н            | D4H            | F4H            | _  |    |   |   |   |              |    |    | W              |

(x: undefined)

Notes: 1. Some bits in the DMA status register are cleared by writing 1 to their bit positions, and one is a write-only bit. See section 6.2.7, DMA Status Register, for details.

2. These registers are used in receiving, so they are not provided for channels 1 and 3.

Rev. 0, 07/98, page 14 of 453

### 1.6.6 Timer Registers

Address CPU Modes 0 & 1 CPU Modes 2 & 3 Initial Value at **Hardware Reset** Read/ Write Register Chan- Chan- Chan- Chan- Chan- Chan- Chan-Name Symbol nel 0 nel 1 nel 2 nel 3 nel 0 nel 1 nel 2 nel 3 MSB LSB Timer up-TCNTL 60H 68H 70H 78H 61H 69H 71H 79H 0 0 0 0 0 0 0 0 R/W counter TCNTH 61H 69H 71H 79H 60H 68H 70H 78H 0 0 0 0 Timer TCONRL 62H 6AH 72H 7AH 63H 6BH 73H 7BH constant register TCONRH63H 72H 7AH 6BH 73H 7BH 62H 6AH 1 1 1 1 1 1 TCSR 74H 6DH 75H 7DH 0 0 0 0 Timer 64H 6CH 7CH 65H control/status register Timer expand TEPR 75H 74H 7CH  $0 \ \ 0 \ \ 0 \ \ 0 \ \ 0 \ \ 0 \ \ R/W$ 65H 6DH 7DH 64H 6CH prescale register

Note: The timer constant register is a write-only register that always reads as 0000H.

### 1.6.7 Wait Controller Registers

|                                      |        | CPU Modes<br>0 & 1 | CPU Modes 2 & 3 | Initial Value at Hardv |    |   |   |   |   | re F | Rese | t<br>Read/<br>Write |

|--------------------------------------|--------|--------------------|-----------------|------------------------|----|---|---|---|---|------|------|---------------------|

| Register Name                        | Symbol |                    |                 | MS                     | SB |   |   |   |   | L    | SB   | _                   |

| Physical address boundary register 0 | PABR0  | 02H                | 03H             | 0                      | 0  | 0 | 0 | 0 | 0 | 0    | 0    | R/W                 |

| Physical address boundary register 1 | PABR1  | 03H                | 02H             | 0                      | 0  | 0 | 0 | 0 | 0 | 0    | 0    | R/W                 |

| Wait control register L              | WCRL   | 04H                | 05H             | 0                      | 0  | 0 | 0 | 0 | 1 | 1    | 1    | R/W                 |

| Wait control register M              | WCRM   | 05H                | 04H             | 0                      | 0  | 0 | 0 | 0 | 1 | 1    | 1    | R/W                 |

| Wait control register H              | WCRH   | 06H                | 07H             | 0                      | 0  | 0 | 0 | 0 | 1 | 1    | 1    | R/W                 |

Rev. 0, 07/98, page 15 of 453

### 1.7 General Description of Functions

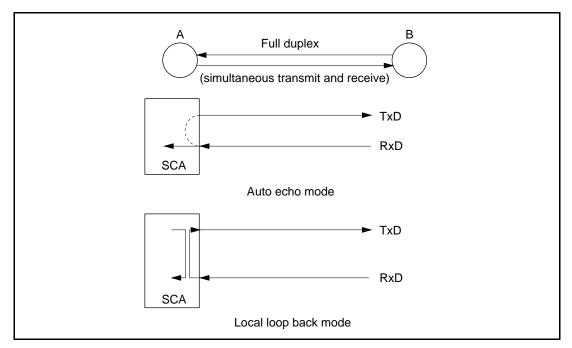

#### 1.7.1 Operating Modes of Serial Section

The normal SCA operating mode is full duplex (figure 1.6). The SCA can transmit and receive simultaneously, using two separate lines.

In auto echo mode (figure 1.6), the SCA automatically retransmits all received data. Data received on the RXD line are retransmitted on the TXD line, and received data are simultaneously input to the receiver in the SCA.

In local loop back mode (figure 1.6), transmit data supplied to the SCA are automatically transferred to the receive data buffer in the SCA. Data received on the RXD line are retransmitted on the TXD line.

Figure 1.6 Operating Modes

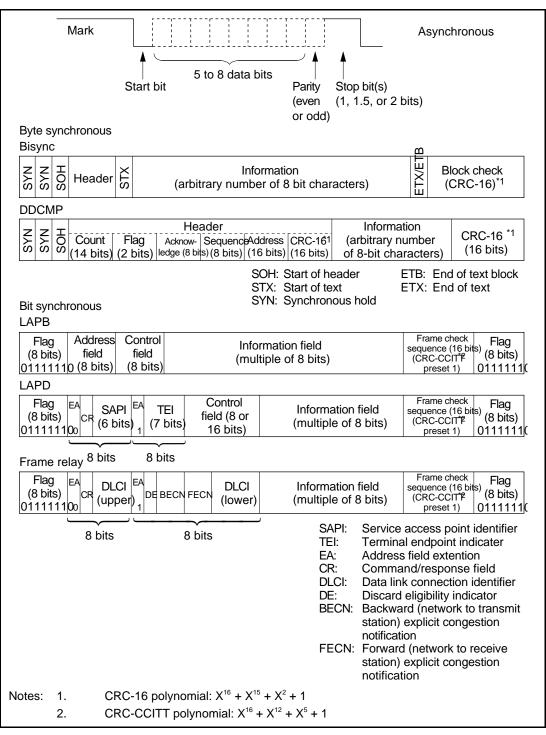

#### 1.7.2 Transmission Formats

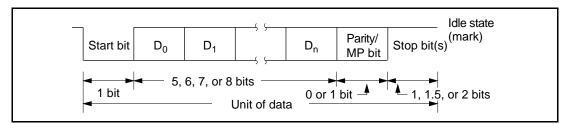

The SCA supports asynchronous, byte-synchronous (bisync, X.21, DDCMP, etc.) and bit-synchronous (frame relay, HDLC, SDLC, X.25 link level/LAPB, LAPD, etc.) protocols. Each communication mode has its own format for transmitting data (figure 1.7).

Rev. 0, 07/98, page 16 of 453

Figure 1.7 Examples of Transmission Formats

Rev. 0, 07/98, page 17 of 453

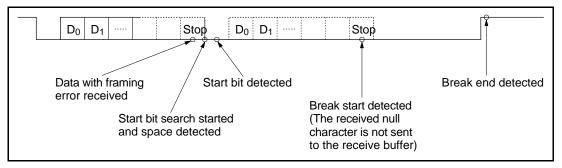

#### 1.7.3 Transmission Error Detection

The SCA flags the following transmission errors in its status registers (ST1 and ST2) to notify the host MPU:

1. Parity error (asynchronous)

This error occurs when the designated parity condition is not satisfied. It indicates that an incorrect bit (possibly the parity bit) was received.

2. Framing error (asynchronous)

This error occurs if the RXD input is low (space) in the position of the first stop bit.

3. CRC error (byte synchronous or bit synchronous)

This error occurs if the correct CRC value is not obtained, indicating that a bit error occurred on the transmission line.

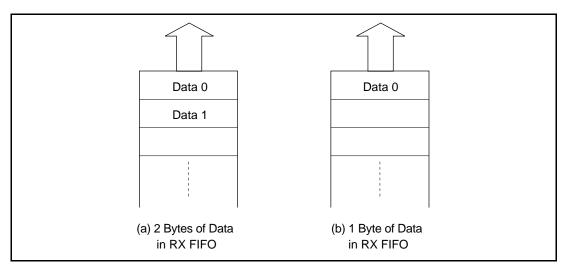

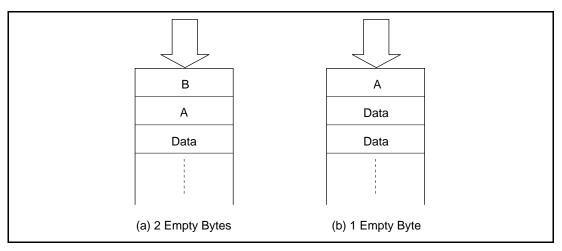

4. Overrun error (asynchronous, byte synchronous, or bit synchronous)

This error occurs if receive data are sent to the receive FIFO when the receive FIFO is full. After an overrun error, new receive data are overwritten on the last byte in the receive FIFO, destroying the preceding receive data but protecting other data already received.

5. Underrun error (byte synchronous or bit synchronous)

This error occurs if the transmit FIFO is empty after transmission of the data in the transmit shift register.

Rev. 0, 07/98, page 18 of 453

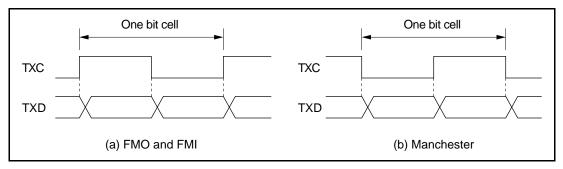

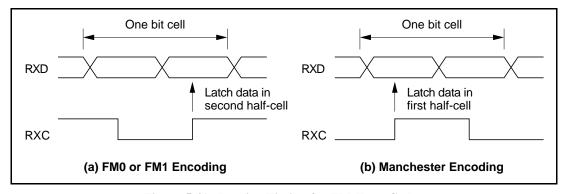

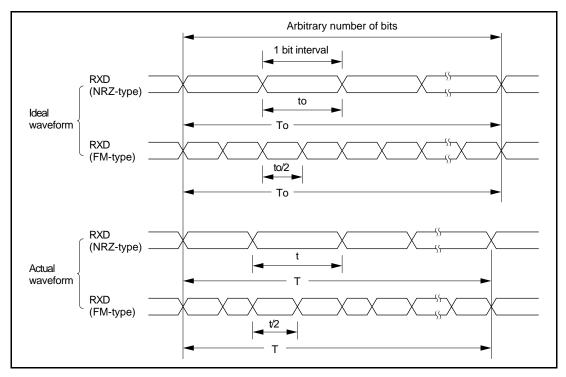

#### 1.7.4 Transmission Codes

The SCA supports five transmission codes: NRZ, NRZI, FM0, FM1, and Manchester (figure 1.8).

See figures 5.39, 5.40, and 5.41 for the timing relationships between the TX and RX clocks and each code.

Figure 1.8 Transmission Codes

Rev. 0, 07/98, page 19 of 453

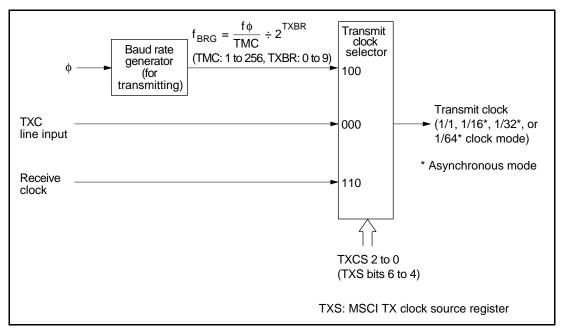

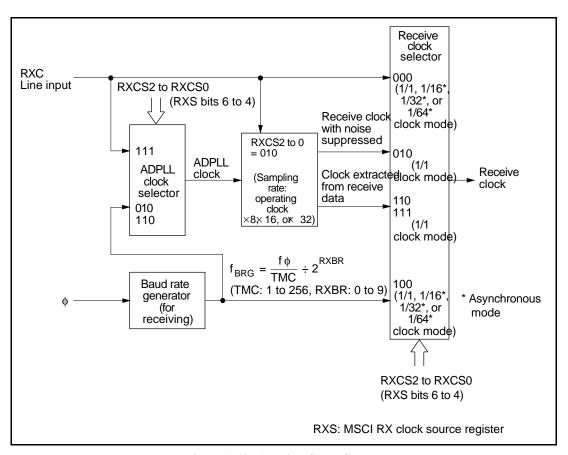

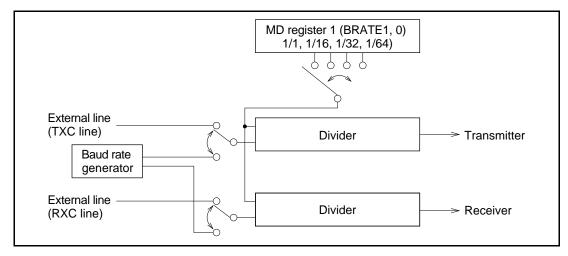

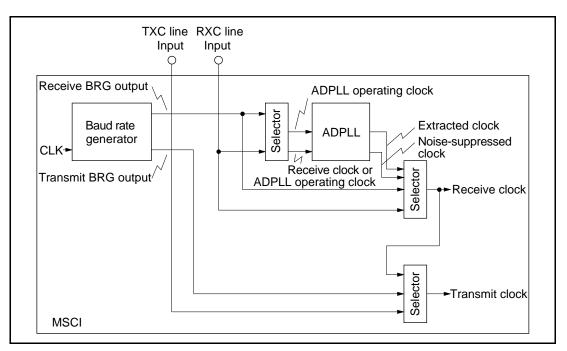

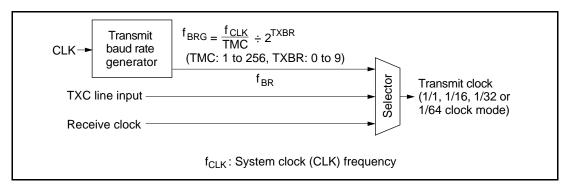

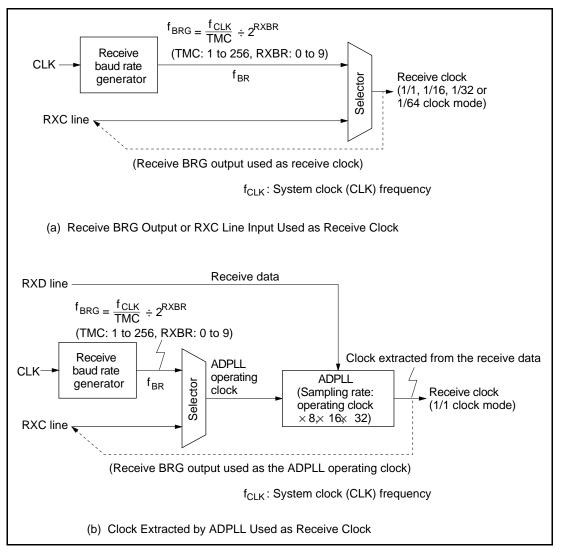

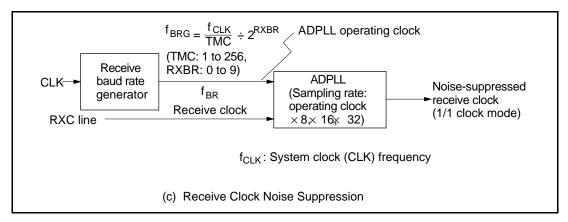

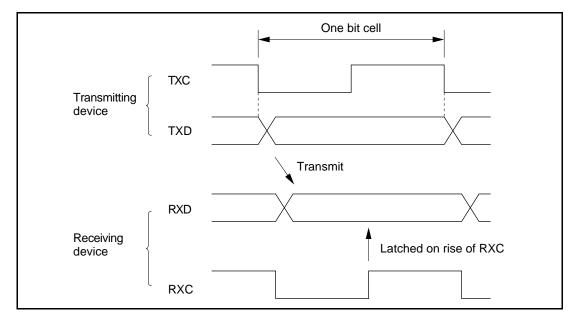

#### 1.7.5 Transmit/Receive Clock Selection

MSCI channels 0 and 1 in the SCA are full-duplex transceivers that support asynchronous, byte-synchronous, and bit-synchronous transmission formats. The transmit clock (figure 1.9) can be selected independently on each channel. The selectable clock sources include the built-in baud rate generator, external clock input, and the receive clock (figure 1.10).

Figure 1.9 Transmit Clock Source

Rev. 0, 07/98, page 20 of 453

Figure 1.10 Receive Clock Source

Rev. 0, 07/98, page 21 of 453

### 1.7.6 Maximum Bit Rates

Table 1.2 lists the maximum bit rates supported by the MSCI in the SCA (when system clock  $(f\phi) = 10 \text{ MHz}$ ).

**Table 1.2** Maximum Bit Rates

| Maximum Transfer Rate ( |

|-------------------------|

|-------------------------|

|                   |                              |                 |                     |                      | Clock Extraction                          |      |       |                                         |       |       |

|-------------------|------------------------------|-----------------|---------------------|----------------------|-------------------------------------------|------|-------|-----------------------------------------|-------|-------|

|                   |                              |                 |                     |                      | Sampling Clock:<br>External* <sup>1</sup> |      |       | Sampling Clock:<br>BRG* <sup>2, 3</sup> |       |       |

| Frequency<br>(fφ) | Protocol<br>Mode             | Clock<br>Mode*4 | External<br>Clock   | BRG                  | ×8                                        | ×16  | × 32  | × 8                                     | × 16  | × 32  |

| 10 MHz*5          | Asynchronous                 | 1/64            | 62.5k* <sup>6</sup> | 78.1k* <sup>7</sup>  | _                                         | _    | _     | _                                       | _     | _     |

|                   |                              | 1/32            | 125k* <sup>6</sup>  | 156.3k* <sup>7</sup> | _                                         | _    | _     | _                                       | _     | _     |

|                   |                              | 1/16            | 250k* <sup>6</sup>  | 312.5k* <sup>7</sup> | _                                         | _    | _     | _                                       | _     | _     |

|                   |                              | 1/1             | 4.0M* <sup>6</sup>  | 3.3M* <sup>8</sup>   | _                                         | _    | _     | _                                       | _     | _     |

|                   | Byte synchronous             | 1/1             | 7.1M* <sup>9</sup>  | 5M* <sup>7</sup>     | 2.2M                                      | 1.1M | 0.55M | 1.25M                                   | 0.62M | 0.31M |

|                   | Bit synchronous<br>HDLC mode | 1/1             | 7.1M* <sup>9</sup>  | 5M* <sup>7</sup>     | 2.2M                                      | 1.1M | 0.55M | 1.25M                                   | 0.62M | 0.31M |

| 16.7 MHz*10       | Asynchronous                 | 1/64            | 104k* <sup>6</sup>  | 130k* <sup>7</sup>   | _                                         | _    | _     | _                                       | _     | _     |

|                   |                              | 1/32            | 208k* <sup>6</sup>  | 260k* <sup>7</sup>   | _                                         | _    | _     | _                                       | _     | _     |

|                   |                              | 1/16            | 416k* <sup>6</sup>  | 521k* <sup>7</sup>   | _                                         | _    | _     | _                                       | _     | _     |

|                   |                              | 1/1             | 6.67M* <sup>6</sup> | 5.56M* <sup>8</sup>  | _                                         | _    | _     | _                                       | _     | _     |

|                   | Byte synchronous             | 1/1             | 12M* <sup>9</sup>   | 8.3M* <sup>7</sup>   | 2.2M                                      | 1.1M | 0.55M | 2.08M                                   | 1.04M | 0.52M |

|                   | Bit synchronous<br>HDLC mode | 1/1             | 12M* <sup>9</sup>   | 8.3M* <sup>7</sup>   | 2.2M                                      | 1.1M | 0.55M | 2.08M                                   | 1.04M | 0.52M |

Notes: 1. 17.6 Mbps ÷ (sampling clock multiplier)

- 2. fo ÷ (sampling clock multiplier)

- 3. Same maximum transfer rate when receive clock noise is suppressed

- 4. Depends on setting of MSCI mode register 1 (MD1)

- 5. SCA (HD64570CP, HD64570F)

- 6.  $f\phi \div 2.5 \times \text{(clock mode)}$

- 7.  $f\phi \div 2 \times (clock mode)$

- 8.  $f \phi \div 3$

- 9.  $f\phi \div 1.4 \times (clock mode)$

- 10. High-speed SCA (HD64570CP16, HD64570F16)

Rev. 0, 07/98, page 22 of 453

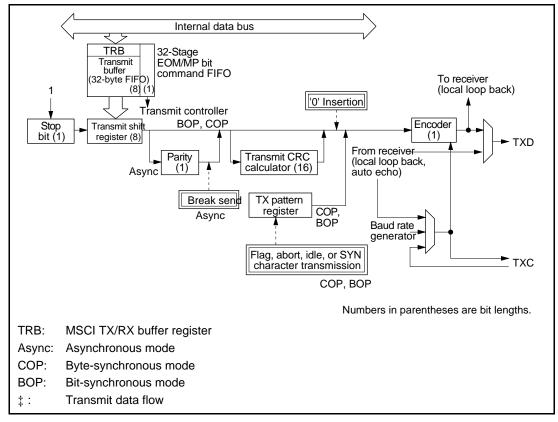

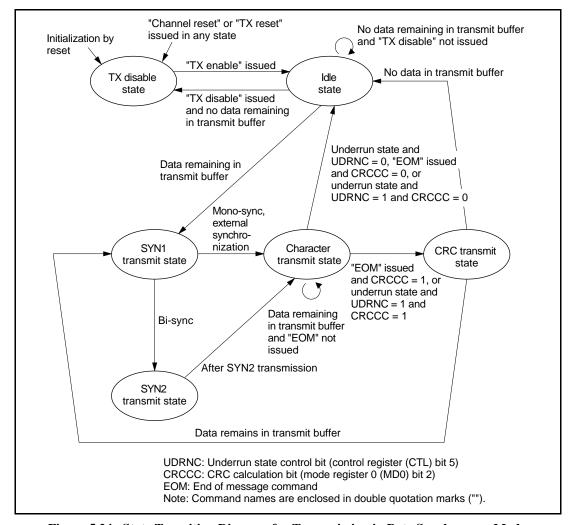

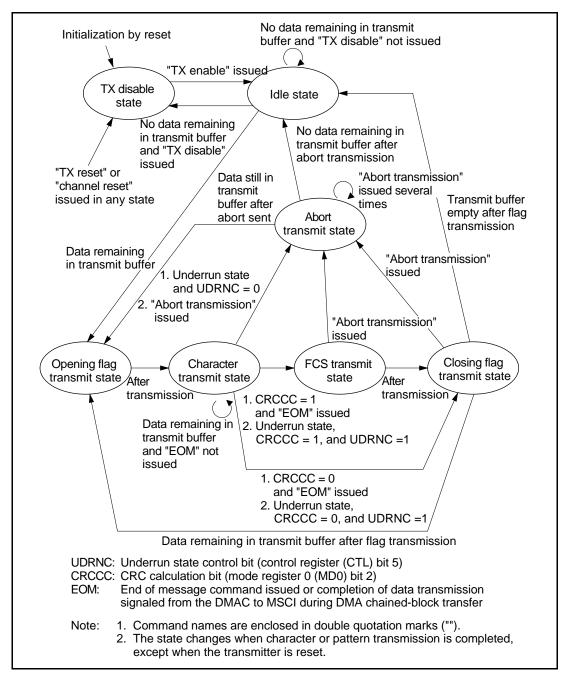

### 1.7.7 Transmitter

The transmitter (figure 1.11) loads parallel data supplied from the data bus into a transmit FIFO consisting of 32 eight-bit registers. Next, according to the selected transmission format, it moves the data into a transmit shift register which converts them to serial data. Data are transmitted LSB first.

Figure 1.11 Block Diagram of the MSCI Transmitter

Rev. 0, 07/98, page 23 of 453

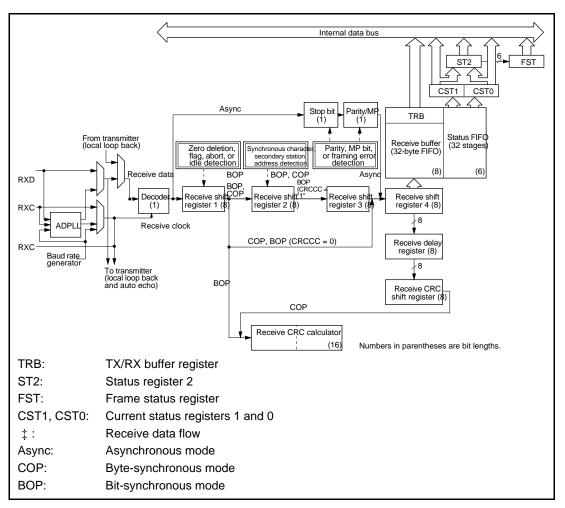

### 1.7.8 Receiver

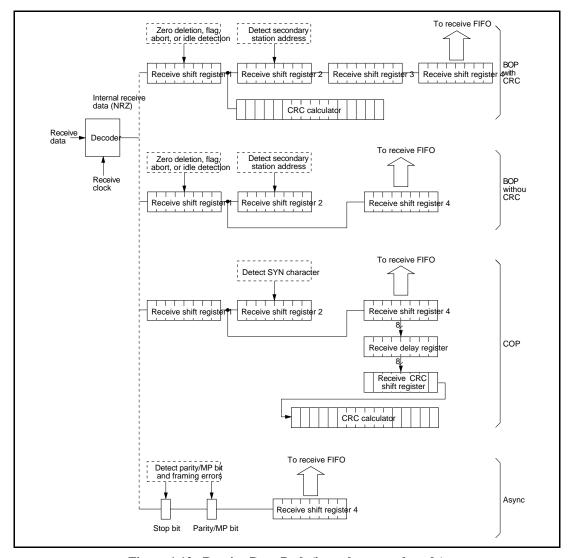

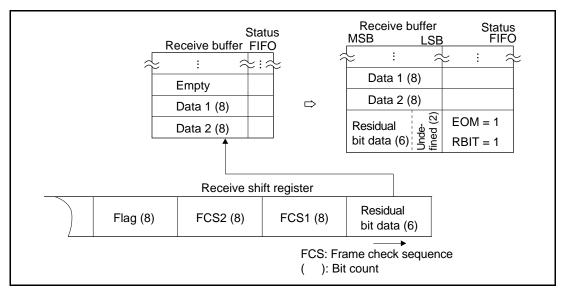

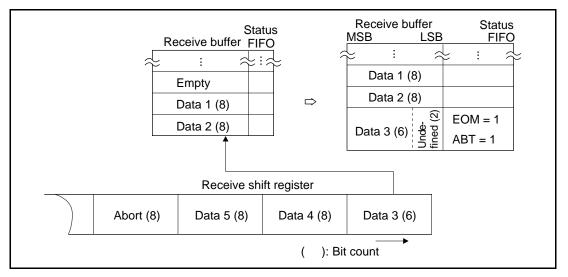

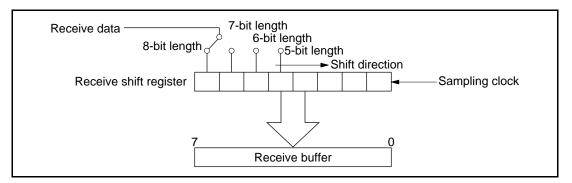

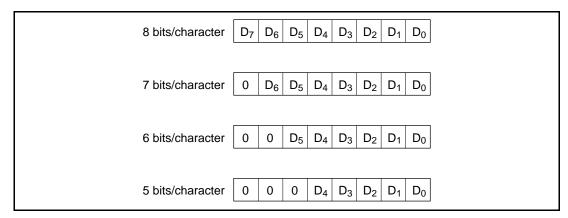

The receiver (figure 1.13) converts serial receive data into parallel data according to the selected communication format. The LSB of the data is received first. The data are shifted through a succession of receive shift registers, the last of which is the eight-bit receive shift register 4 (figure 1.12).

Figure 1.12 Receive Data Path (in each protocol mode)

Rev. 0, 07/98, page 24 of 453

Figure 1.13 Block Diagram of the MSCI Receiver

Rev. 0, 07/98, page 25 of 453

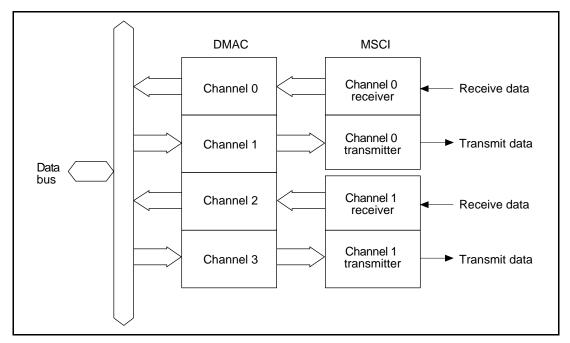

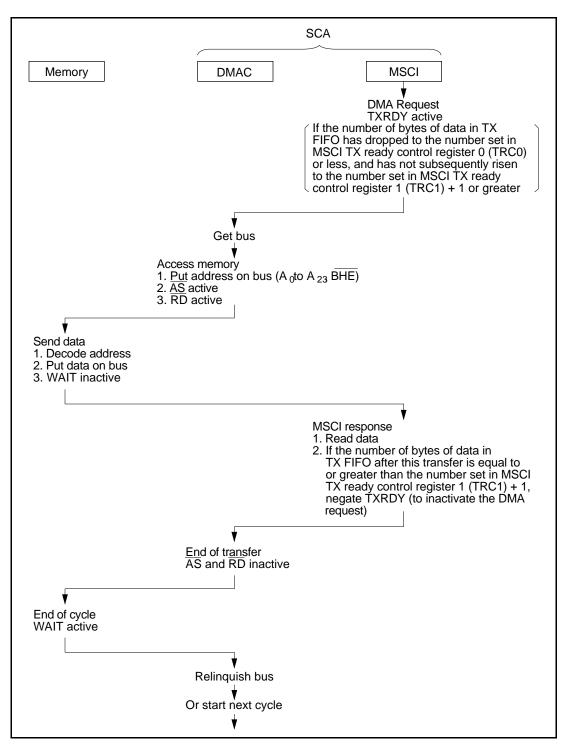

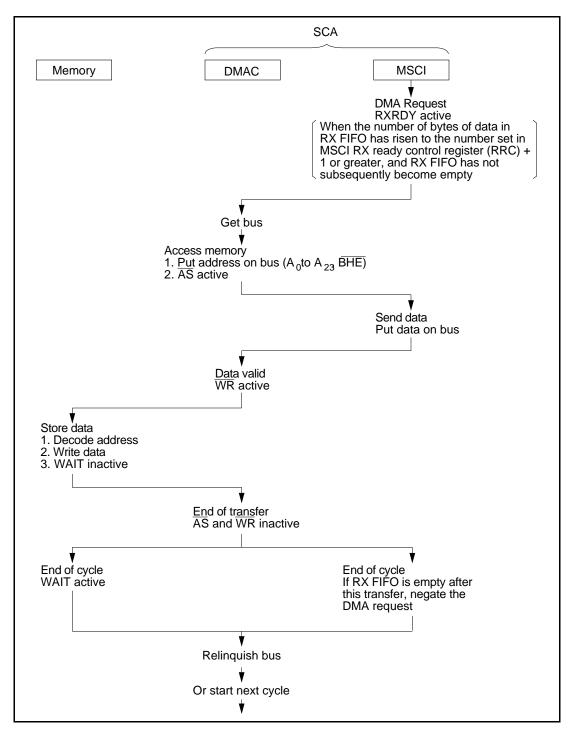

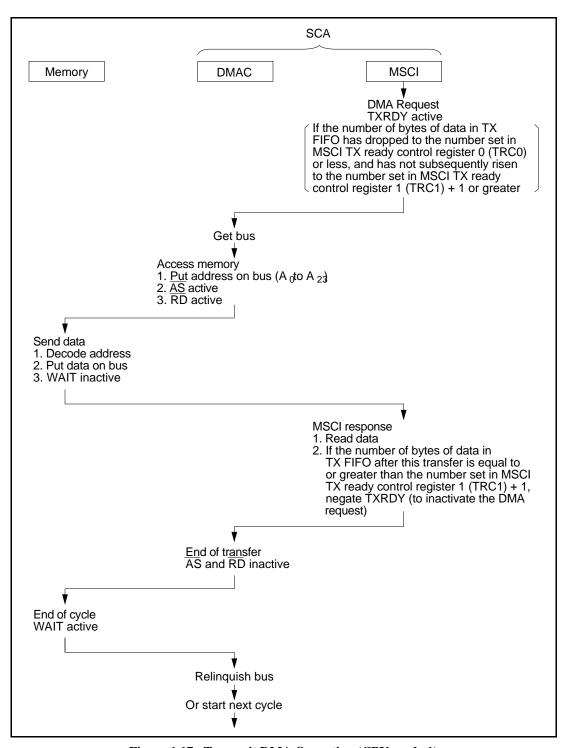

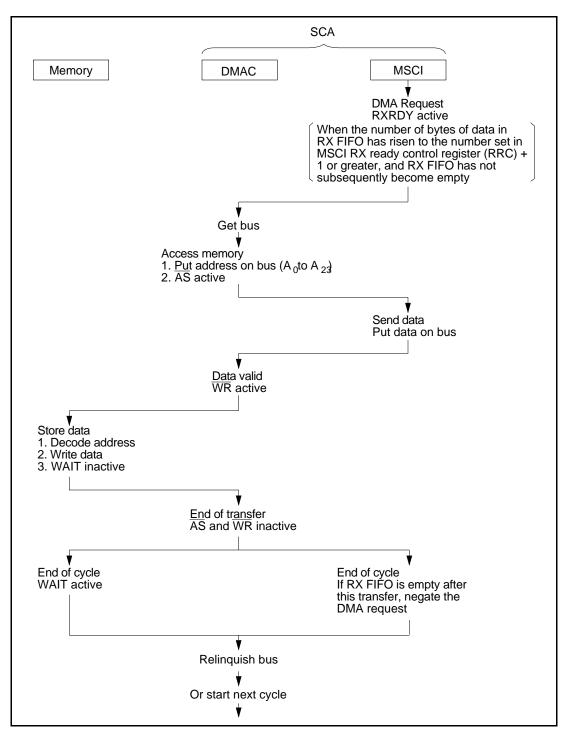

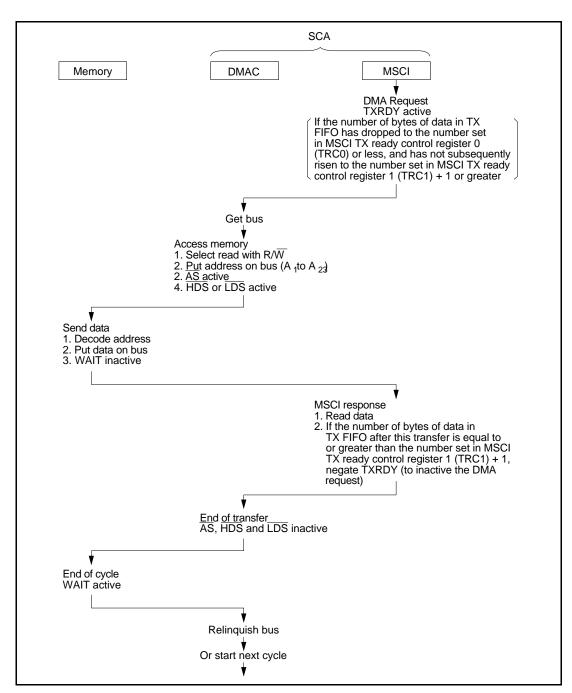

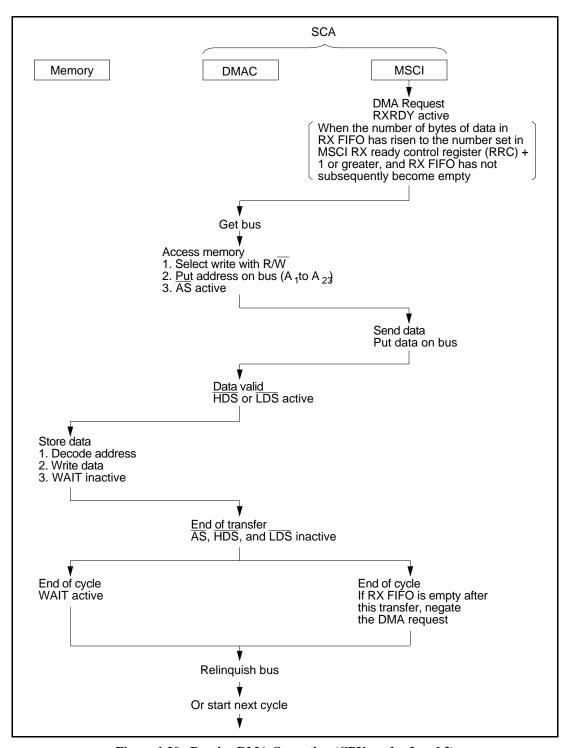

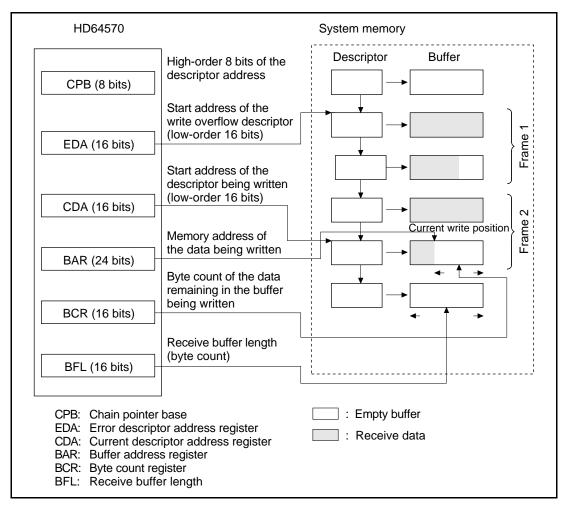

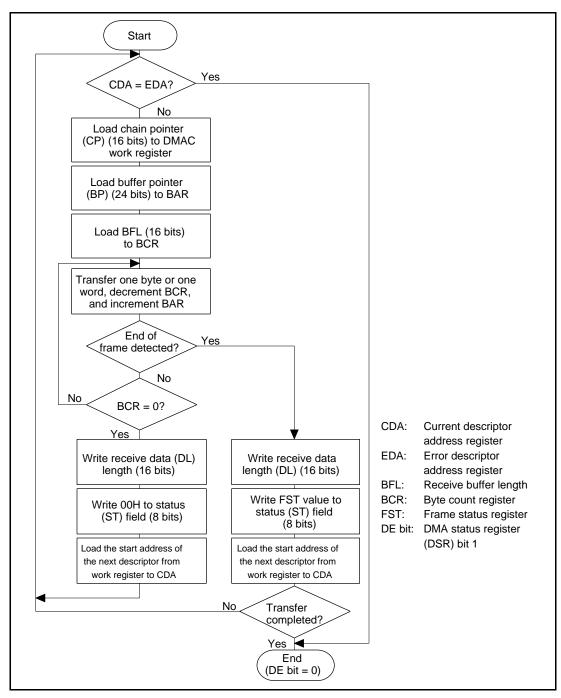

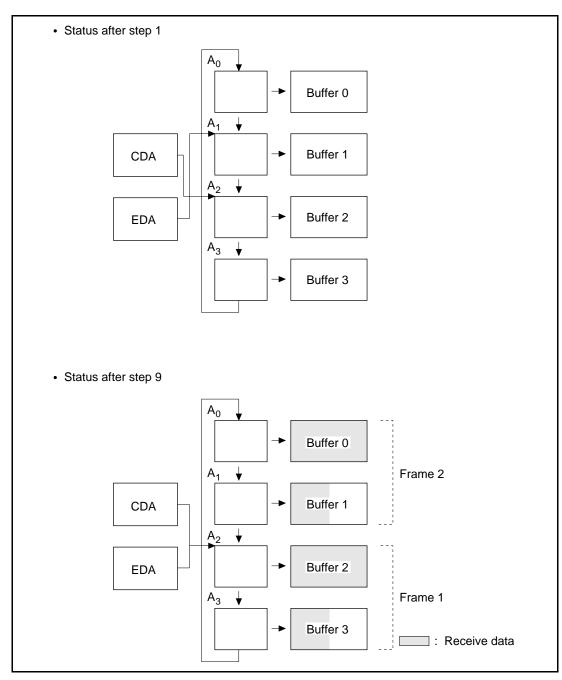

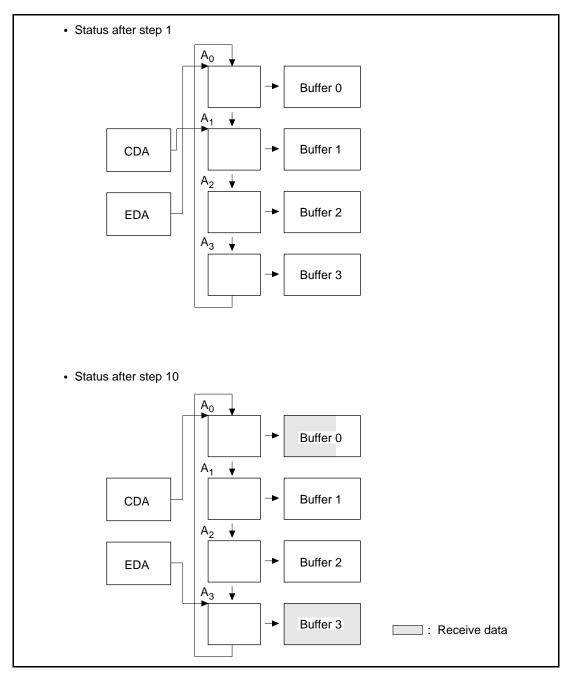

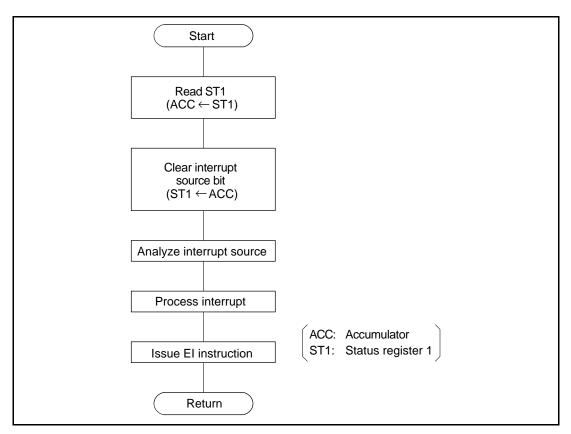

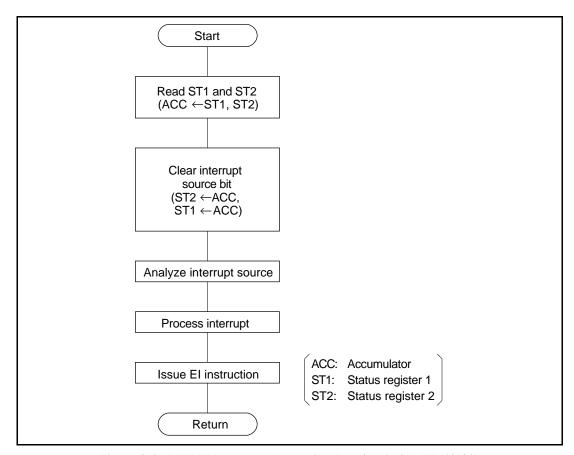

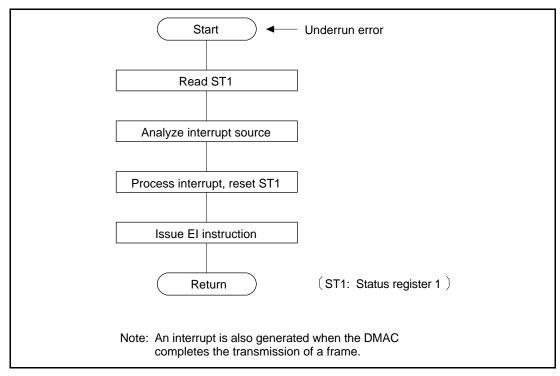

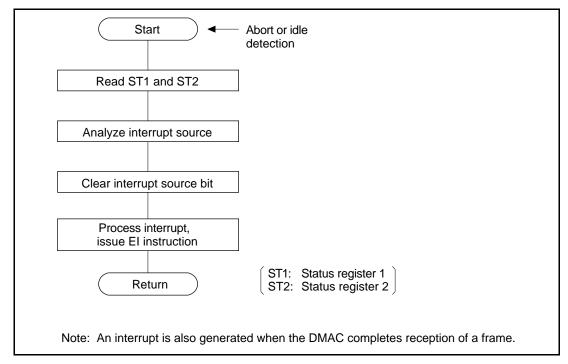

### 1.7.9 **DMAC**