CY7C43643 CY7C43663 CY7C43683

# 1K/4K/16K x36 Unidirectional Synchronous FIFO with Bus Matching

### Features

- High-speed, low-power, Unidirectional, First-in, First-out (FIFO) memories w/bus matching capabilities

- 1Kx36 (CY7C43643)

- 4Kx36 (CY7C43663)

- 16Kx36 (CY7C43683)

- 0.35-micron CMOS for optimum speed/power

- High-speed 133-MHz operation (7.5 ns read/write cycle times)

- Low power

$-I_{CC} = 100 \text{ mA}$

— I<sub>SB</sub> = 10 mA

- Fully asynchronous and simultaneous read and write operation permitted

- Mailbox bypass register for each FIFO

- Parallel and Serial Programmable Almost Full and Almost Empty flags

- Retransmit function

- Standard or FWFT mode user selectable

- Partial Reset

- Big or Little Endian format for word or byte bus sizes

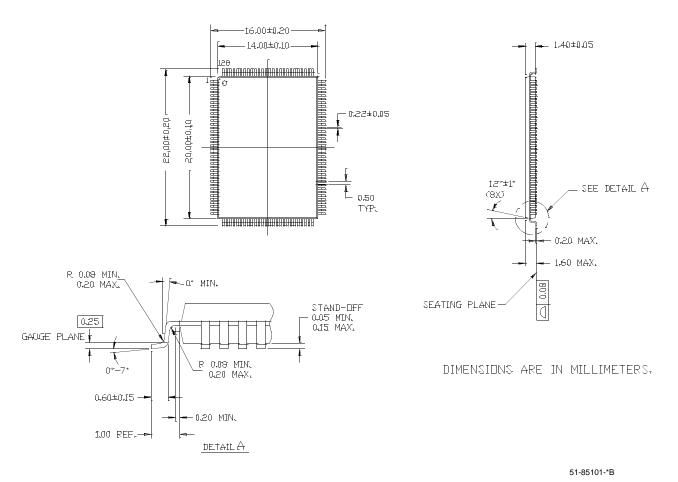

- 128-pin TQFP packaging

- · Easily expandable in width and depth

Cypress Semiconductor Corporation • Document #: 38-06021 Rev. \*B

3901 North First Street • San Jose

CA 95134 • 408-943-2600 Revised December 26, 2002

٠

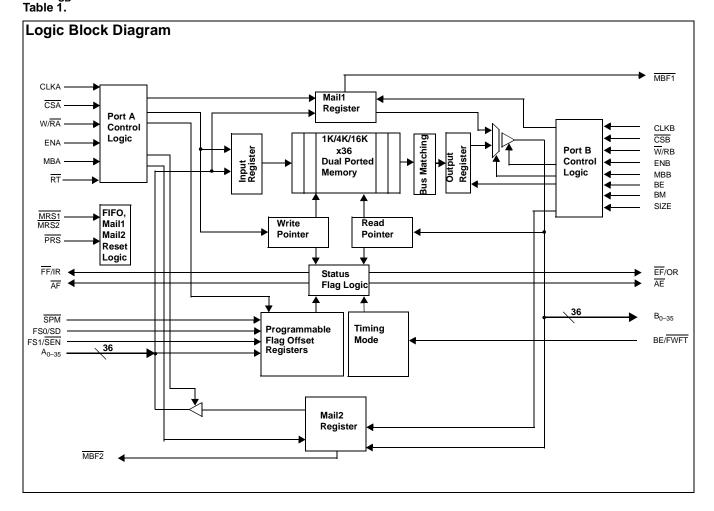

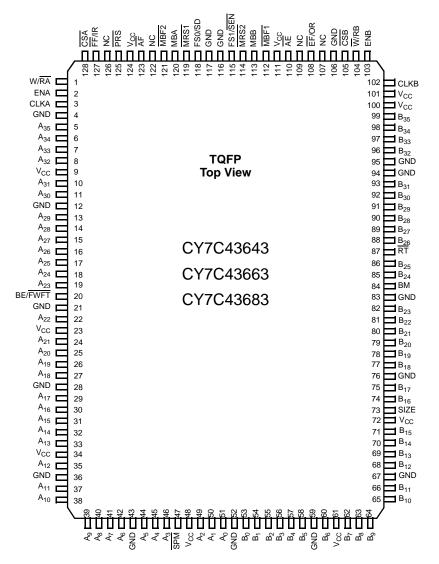

**Pin Configuration**

### **Selection Guide**

|                             |            | CY7C43643/63/83<br>-7 | CY7C43643/63/83<br>-10 | CY7C43643/63/83<br>-15 | Unit |

|-----------------------------|------------|-----------------------|------------------------|------------------------|------|

| Maximum Frequency           |            | 133                   | 100                    | 66.7                   | MHz  |

| Maximum Access Tim          | e          | 6                     | 8                      | 10                     | ns   |

| Minimum Cycle Time          |            | 7.5                   | 10                     | 15                     | ns   |

| Minimum Data or Enal        | ble Set-up | 3                     | 4                      | 5                      | ns   |

| Minimum Data or Enable Hold |            | 0                     | 0                      | 0                      | ns   |

| Maximum Flag Delay          |            | 6                     | 8                      | 8                      | ns   |

| Active Power Supply         | Commercial | 100                   | 100                    | 100                    | mA   |

| Current (I <sub>CC1</sub> ) | Industrial |                       |                        | 100                    |      |

|                             |            | CY7C43643             | CY7C43663              | CY7C4368               | 3    |

| Density                     |            | 1K x 36               | 4K x 36                | 16K x 36               |      |

| Package                     |            | 128 TQFP              | 128 TQFP               | 128 TQFF               | )    |

Document #: 38-06021 Rev. \*B

Page 2 of 29

### **Pin Definitions**

| Signal Name       | Description                                         | I/O | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------------|-----------------------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A <sub>0-35</sub> | Port A Data                                         | I   | 36-bit unidirectional data port for side A.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| ĀĒ                | Almost Empty<br>Flag (Port B)                       | 0   | <b>Programmable Almost Empty flag synchronized to CLKA</b> . It is LOW when the number of words in the FIFO2 is less than or equal to the value in the Almost Empty A offset register, X. <sup>[1]</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| ĀF                | Almost Full Flag                                    | 0   | <b>Programmable Almost Full flag synchronized to CLKA</b> . It is LOW when the number of empty locations in the FIFO is less than or equal to the value in the Almost Full A offset register, Y. <sup>[1]</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| B <sub>0-35</sub> | Port B Data                                         | 0   | 36-bit unidirectional data port for side B.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| BE/FWFT           | Big<br>Endian/First-Wor<br>d Fall-Through<br>Select | Ι   | This is a dual-purpose pin. During Master Reset, a HIGH on BE will select Big Endian operation. In this case, depending on the bus size, the most significant byte or word on Port A is transferred to Port B first. A LOW on BE will select Little Endian operation. In this case, the least significant byte or word on Port A is transferred to Port B first. A LOW on Port A is transferred to Port B first. After Master Reset, this pin selects the timing mode. A HIGH on FWFT selects CY Standard Mode, a LOW selects First-Word Fall-Through Mode. Once the timing mode has been selected, the level on FWFT must be static throughout device operation. |

| BM                | Bus Match<br>Select (Port B)                        | I   | A HIGH on this pin enables either byte or word bus width on Port B, depending on the state of SIZE. A LOW selects long-word operation. BM works with SIZE and BE to select the bus size and endian arrangement for Port B. The level of BM must be static throughout device operation.                                                                                                                                                                                                                                                                                                                                                                            |

| CLKA              | Port A Clock                                        | Ι   | <b>CLKA is a continuous clock that synchronizes all data transfers through Port A</b> and can be asynchronous or coincident to CLKB. FF/IR and AF are all synchronized to the LOW-to-HIGH transition of CLKA.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| CLKB              | Port B Clock                                        | Ι   | <b>CLKB is a continuous clock that synchronizes all data transfers through Port B</b> and can be asynchronous or coincident to CLKA. FB/IR, EF/OR, AF, and AE are all synchronized to the LOW-to-HIGH transition of CLKB.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| CSA               | Port A Chip<br>Select                               | I   | <b>CSA</b> must be LOW to enable a LOW-to HIGH transition of CLKA to read or write on Port A. The $A_{0-35}$ outputs are in the high-impedance state when CSA is HIGH.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

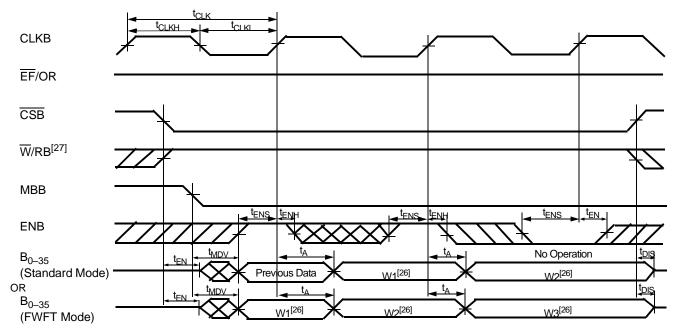

| CSB               | Port B Chip<br>Select                               | I   | <b>CSB</b> must be LOW to enable a LOW-to HIGH transition of CLKB to read or write on Port B. The $B_{0-35}$ outputs are in the high-impedance state when CSB is HIGH.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| EF/OR             | Empty/Output<br>Ready Flag<br>(Port B)              | 0   | <b>This is a dual-function pin</b> . In the CY Standard Mode, the $\overline{\text{EF}}$ function is selected. $\overline{\text{EF}}$ indicates whether or not the FIFO memory is empty. In the FWFT mode, the OR function is selected. OR indicates the presence of valid data on $A_{0-35}$ outputs, available for reading. $\overline{\text{EF}}$ /OR is synchronized to the LOW-to-HIGH transition of CLKB. <sup>[2]</sup>                                                                                                                                                                                                                                    |

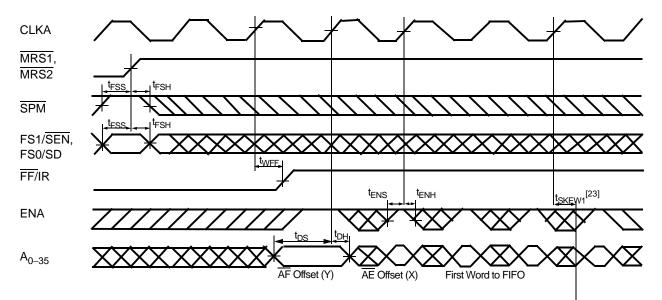

| ENA               | Port A Enable                                       | Ι   | ENA must be HIGH to enable a LOW-to-HIGH transition of CLKA to read or write data on Port A.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| ENB               | Port B Enable                                       | I   | ENB must be HIGH to enable a LOW-to-HIGH transition of CLKB to read or write data on Port B.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| FF/IR             | Port B Full/Input<br>Ready Flag                     | 0   | <b>This is a dual-function pin</b> . In the CY Standard Mode, the $\overline{FF}$ function is selected. $\overline{FF}$ indicates whether or not the FIFO memory is full. In the FWFT mode, the IR function is selected. IR indicates whether or not there is space available for writing to the FIFO memory. FF/IR is synchronized to the LOW-to-HIGH transition of CLKA.                                                                                                                                                                                                                                                                                        |

Notes:

When reading from the FIFO under FWFT, ORA/ORB signal should be included in the read logic to ensure proper operation. To read without gating the boundary flag (e.g., in bursts), use CY standard mode. When FIFO is operated at the almost empty/full boundary, there may be an uncertainty of up to three clock cycles for flag assertion and deassertion. Refer to "Designing with CY7C436xx Synchronous FIFO" application notes for more details on flag uncertainties. 1.

2.

### Pin Definitions (continued)

| Signal Name | Description                              | I/O | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------|------------------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

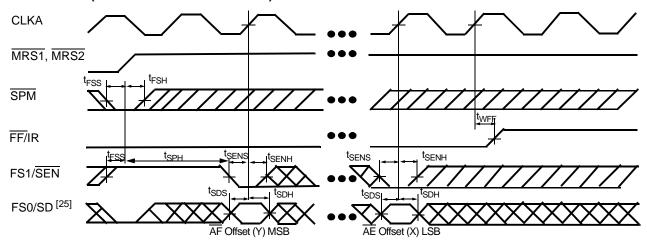

| FS1/SEN     | Flag Offset<br>Select 1/Serial<br>Enable | I   | FS1/SEN and FS0/SD are dual-purpose inputs used for flag offset register<br>programming. During Master Reset, FS1/SEN and FS0/SD, together with SPM, select<br>the flag offset programming method. Three offset register programming methods are                                                                                                                                                                                                                                                                                                                                                                                                           |

| FS0/SD      | Flag Offset<br>Select 0/Serial<br>Data   | I   | available: automatically load one of three preset values (8, 16, or 64), parallel load from<br>Port <u>A</u> , and serial load. When serial load is selected for flag offset register programming,<br>FS1/SEN is <u>used</u> as an enable synchronous to the LOW-to-HIGH transition of CLKA.<br>When FS1/SEN is LOW, a rising edge on CLKA loads the bit present on FS0/SD into<br>the X and Y registers. The number of bit writes required to program the offset registers<br>is 20 for the CY7C43643, 24 for the CY7C43663, and 28 for the CY7C43683. The first<br>bit write stores the Y-register MSB and the last bit write stores the X-register LSB. |

| MBA         | Port A Mailbox<br>Select                 | I   | A HIGH level on MBA chooses a mailbox register for a Port A read or write operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| MBB         | Port B Mailbox<br>Select                 | I   | A HIGH level on MBB chooses a mailbox register for a Port B read or write operation.<br>When a read operation is performed on Port B, a HIGH level on MBB selects data from<br>the Mail1 register for output and a LOW level selects FIFO output register data for output.<br>Data can only be written into Mail 2 register through Port B (MBB HIGH) and not into<br>the FIFO memory.                                                                                                                                                                                                                                                                     |

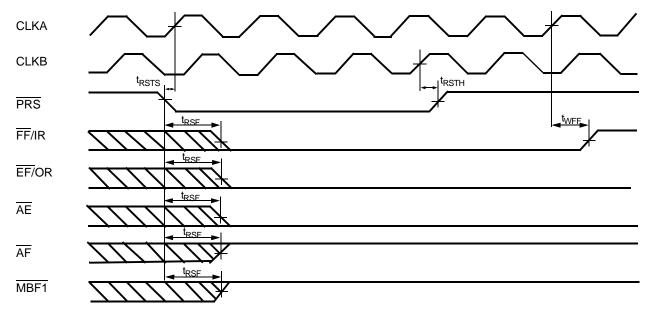

| MBF1        | Mail1 Register<br>Flag                   | 0   | <b>MBF1 is set LOW by a LOW-to-HIGH transition of CLKA</b> that writes data to the Mail1 register. Writes to the Mail1 register are inhibited while MBF1 is LOW. MBF1 is set HIGH <u>by a L</u> OW-to-HIGH transition of CLKB when a Port B read is selected and MBB is HIGH. MBF1 is set HIGH following either a Master or Partial Reset.                                                                                                                                                                                                                                                                                                                 |

| MBF2        | Mail2 Register<br>Flag                   | 0   | <b>MBF2</b> is set LOW by a LOW-to-HIGH transition of CLKB that writes data to the Mail2 register. Writes to the Mail2 register are inhibited while MBF2 is LOW. MBF2 is set HIGH by a LOW-to-HIGH transition of CLKA when a Port A read is selected and MBA is HIGH. MBF2 is set HIGH following either a Master or Partial Reset of FIFO2.                                                                                                                                                                                                                                                                                                                |

| MRS1        | Master Reset                             | I   | A LOW on this pin initializes the FIFO read and write pointers to the first location of memory and sets the Port B output register to all zeroes. A LOW pulse on MRS1 selects the programming method (serial or parallel) and one of three programmable flag default offsets. It also configures Port B for bus size and endian arrangement. Four LOW-to-HIG <u>H transitions of CLKA and four LOW-to-HIGH transitions of CLKB must occur while MRS1 is LOW.</u>                                                                                                                                                                                           |

| MRS2        | Master Reset                             | Ι   | A LOW on this pin initializes the Mail2 register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| PRS         | Partial Reset                            | Ι   | A LOW on this pin initializes the FIFO read and write pointers to the first location of memory and sets the Port B output register to all zeroes. During Partial Reset, the currently selected bus size, endian arrangement, programming method (serial or parallel), and programmable flag settings are all retained.                                                                                                                                                                                                                                                                                                                                     |

| RT          | Retransmit                               | Ι   | A LOW strobe on this pin will retransmit data on the FIFO. This is achieved by bringing the read pointer back to location zero. The user will still need to perform read operation to retransmit the data. Retransmit function applies to CY standard mode only.                                                                                                                                                                                                                                                                                                                                                                                           |

| SIZE        | Bus Size Select                          | I   | A HIGH on this pin when BM is HIGH selects byte bus (9-bit) size on Port B. A LOW on this pin when BM is HIGH selects word (18-bit) bus size. SIZE works with BM and BE to select the bus size and endian arrangement for Port B. The level of SIZE must be static throughout device operation.                                                                                                                                                                                                                                                                                                                                                            |

| SPM         | Serial<br>Programming                    | Ι   | <b>A LOW on this pin selects serial programming of partial flag offsets</b> . A HIGH on this pin selects parallel programming or default offsets (8, 16, or 64).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| W/RA        | Port A<br>Write/Read<br>Select           | I   | A HIGH selects a write operation and a LOW selects a read operation on Port A for a LOW-to-HIGH transition of CLKA. The $A_{0-35}$ outputs are in the high-impedance state when W/RA is HIGH.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| W/RB        | Port B<br>Write/Read<br>Select           | I   | A LOW selects a write operation and a HIGH selects a read operation on Port B for a LOW-to-HIGH transition of CLKB. The $B_{0-35}$ outputs are in the high-impedance state when W/RB is LOW.                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

### **Functional Description**

The CY7C436x3 is a monolithic, high-speed, low-power, CMOS Unidirectional Synchronous (clocked) FIFO memory which supports clock frequencies up to 133 MHz and has read access times as fast as 6 ns. Two independent 1K/4K/16K x 36 dual-port SRAM FIFOs on board each chip buffer data in opposite directions. FIFO data on Port B can be output in 36-bit, 18-bit, or 9-bit formats with a choice of Big or Little Endian configurations.

The CY7C436x3 is a synchronous (clocked) FIFO, meaning each port employs a synchronous interface. All data transfers through a port are gated to the LOW-to-HIGH transition of a port clock by enable signals. The clocks for each port are independent of one another and can be asynchronous or coincident. The enables for each port are arranged to provide a simple unidirectional interface between microprocessors and/or buses with synchronous control.

Communication between each port may bypass the FIFOs via two mailbox registers. The mailbox registers' width matches the selected Port B bus width. Each mailbox register has a flag (MBF1 and MBF2) to signal when new mail has been stored.

Two kinds of reset are available on the CY7C436x3: Master Reset and Partial Reset. Master Reset initializes the read and write pointers to the first location of the memory array, configures the FIFO for Big or Little Endian byte arrangement and selects serial flag programming, parallel flag programming, or one of the three possible default flag offset settings, 8, 16, or 64. The FIFO also has two Master Reset pins, MRS1 and MRS2.

Partial Reset also sets the read and write pointers to the first location of the memory. Unlike Master Reset, any settings existing prior to Partial Reset (i.e., programming method and partial flag default offsets) are retained. Partial Reset is useful since it permits flushing of the FIFO memory without changing any configuration <u>settings</u>. The FIFO has its own independent Partial Reset pin, PRS.

The CY7C436x3 have two modes of operation: In the CY Standard Mode, the first word written to an empty FIFO is deposited into the memory array. A read operation is required to access that word (along with all other words residing in memory). In the First-Word Fall-Through Mode (FWFT), the first long-word (36-bit wide) written to an empty FIFO appears automatically on the outputs, no read operation required (nevertheless, accessing subsequent words <u>does</u> necessitate a formal read request). The state of the BE/FWFT pin during FIFO operation determines the mode in use.

The FIFO has a combined Empty/Output Ready flag ( $\overline{EF}/OR$ ) and a combined Full/Input Ready flag ( $\overline{FF}/R$ ). The  $\overline{EF}$  and  $\overline{FF}$ functions are selected in the CY Standard Mode.  $\overline{EF}$  indicates whether the memory is full or not. The IR and OR functions are selected in the First-Word Fall-Through Mode. IR indicates whether or not the FIFO has available memory locations. OR shows whether the FIFO has data available for reading or not. It marks the presence of valid data on the outputs.<sup>[1]</sup>

The FIFO has a programmable Almost Empty flag ( $\overline{AE}$ ) and a programmable Almost Full flag ( $\overline{AF}$ ).  $\overline{AE}$  indicates when a selected number of words written to FIFO memory achieve a predetermined "almost empty state."  $\overline{AF}$  indicates when a selected number of words written to the memory achieve a predetermined "almost full state."<sup>[2]</sup>

IR and  $\overline{AF}$  are synchronized to the port clock that writes data into its array. OR and  $\overline{AE}$  are synchronized to the port clock that reads data from its array. Programmable offset for  $\overline{AE}$  and  $\overline{AF}$  can be loaded in parallel using Port A or in serial via the <u>SD</u> input. Three default offset settings are also provided. The  $\overline{AE}$  threshold can be <u>set</u> at 8, 16, or 64 locations from the empty boundary and  $\overline{AF}$  threshold can be set at 8, 16, or 64 locations from the full boundary. All these choices are made using the FS0 and FS1 inputs during Master Reset.

Two or more devices may be used in parallel to create wider data paths.

The CY7C436x3 are characterized for operation from 0°C to 70°C commercial, and from -40°C to 85°C industrial. Input ESD protection is greater than 2001V, and latch-up is prevented by the use of guard rings.

### Signal Description

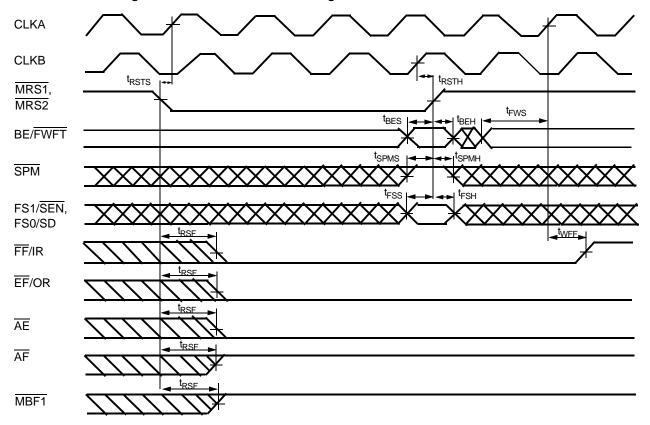

### Master Reset (MRS1, MRS2)

The FIFO memory of the CY7C436x3 undergoes a complete reset by taking its associated Master Reset (MRS1, MRS2) input LOW for at least four Port A clock (CLKA) and four Port B clock (CLKB) LOW-to-HIGH transitions. The Master Reset input can switch asynchronously to the clocks. A Master Reset initializes the internal <u>read</u> and write pointers and forces the Full/Input Ready flag (FF/IR) LOW, the Empty/Output Ready flag (EF/OR) LOW, the Almost Empty flag (AE) LOW, and the Almost Full flag (AF) HIGH. A Master Reset also forces the Mailbox flag (MBF1, MBF2) of the parallel mailbox register HIGH. After a Master Reset, the FIFO's Full/Input Ready flag is set HIGH after two clock cycles to begin normal operation. A Master Reset must be performed on the FIFO after power up, before data is written to its memory.

<u>A LOW</u>-to-HIGH transition on a FIFO Master Reset (MRS1, MRS2) input latches the value of the Big Endian (BE) input or determining the order by which bytes are transferred through Port B.

A LOW-to-HIGH transition on a FIFO reset (MRS1, MRS2) input latches the values of the Flag select (FS0, FS1) and Serial Programming Mode (SPM) inputs for choosing the Almost Full and Almost Empty offset programming method (see Almost Empty and Almost Full flag offset programming below).

### Partial Reset (PRS)

Each of the two FIFO memories of the CY7C436x3 undergoes a limited reset by taking its associated Partial Reset (PRS) input LOW for at least four Port A clock (CLKA) and four Port B clock (CLKB) LOW-to-HIGH transitions. The Partial Reset inputs can switch asynchronously to the clocks. A Partial Reset initializes the internal read and write pointers and forces the Full/Input Ready flag (FF/IR) LOW, the Empty/Output Ready flag (EF/OR) LOW, the Almost Empty flag (AE) LOW, and the Almost Full flag (AF) HIGH. A Partial Reset also forces the Mailbox flag (MBF1, MBF2) of the parallel mailbox register HIGH. After a Partial Reset, the FIFO's Full/Input Ready flag is set HIGH after two clock cycles to begin normal operation.

Whatever flag offsets, programming method (parallel or serial), and timing mode (FWFT or IDT Standard mode) are currently selected at the time a Partial Reset is initiated, those settings will remain unchanged upon completion of the reset operation. A Partial Reset may be useful in the case where

CY7C43643 CY7C43663 CY7C43683

reprogramming a FIFO following a Master Reset would be inconvenient.

### Big Endian/First-Word Fall-Through (BE/FWFT)

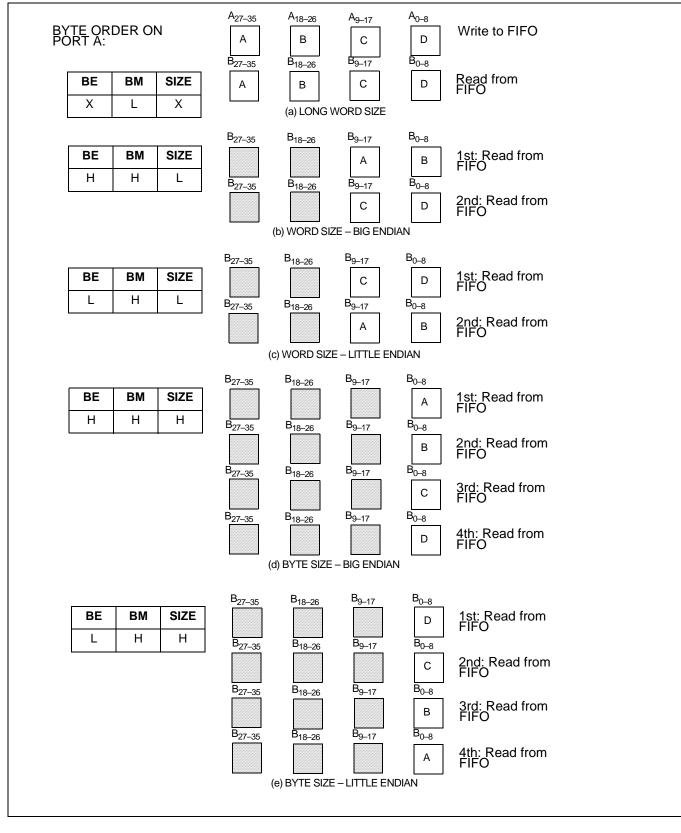

This is a dual-purpose pin. At the time of Master Reset, the BE select function is active, permitting a choice of Big or Little Endian byte arrangement for data written to or read from Port B. This selection determines the order by which bytes (or words) of data are transferred through this port. For the following illustrations, assume that a byte (or word) bus size has been selected for Port B. (Note that when Port B is configured for a long-word size, the Big Endian function has no application and the BE input is a "Don't Care."

<u>A HIGH</u> on the BE/FWFT input when the Master Reset (MRS1, MRS2) inputs go from LOW to HIGH will select a Big Endian arrangement. When data is moving in the direction from Port A to Port B, the most significant byte (word) of the long-word written to Port A will be transferred to Port B first; the least significant byte (word) of the long-word written to Port A will be transferred to Port B last.

A LOW on the BE/FWFT input when the Master Reset (MRS1, MRS2) inputs go from LOW to HIGH will select a Little Endian arrangement. When data is moving in the direction from Port A to Port B, the least significant byte (word) of the long-word written to Port A will be transferred to Port B first; the most significant byte (word) of the long-word written to Port A will be transferred to Port B last. After Master Reset, the FWFT select function is active, permitting a choice between two possible timing modes: CY Standard Mode or First-Word Fall-Through (FWFT) Mode. Once the Master Reset (MRS1, MRS2) input is HIGH, a HIGH on the BE/FWFT input at the second LOW-to-HIGH transition of CLKA will select CY Standard Mode. This mode uses the Empty Flag function (EF) to indicate whether or not there are any words present in the FIFO memory. It uses the Full Flag function (FF) to indicate whether or not the FIFO memory has any free space for writing. In CY Standard Mode, every word read from the FIFO, including the first, must be requested using a formal read operation.

Once the <u>Master</u> Reset (<u>MRS1</u>, <u>MRS2</u>) input is HIGH, a LOW on the BE/FWFT input during the next LOW-to-HIGH transition of CLKA will select FWFT Mode. This mode uses the Output Ready function (OR) to indicate whether or not there is valid data at the data outputs (B<sub>0-35</sub>). It also uses the Input Ready function (IR) to indicate whether or not the FIFO memory has any free space for writing. In the FWFT mode, the first word written to an empty FIFO goes directly to data outputs, no read request necessary. Subsequent words must be accessed by performing a formal read operation.

Following Master Reset, the level applied to the  $BE/\overline{FWFT}$  input to choose the desired timing mode must remain static throughout the FIFO operation.

#### Programming the Almost Empty and Almost Full Flags

Two registers in the CY7C436x3 are used to hold the offset values for the Almost Empty and Almost Full flags. The Port B Almost Empty flag ( $\overline{AE}$ ) offset register is labeled X. The Port A Almost Full flag ( $\overline{AF}$ ) offset register is labeled Y. The index of each register name corresponds with preset values during the reset of a FIFO, programmed in parallel using the FIFO's Port A data inputs, or programmed in serial using the Serial Data (SD) input (see *Table 2*).

To load a FIFO's Almost Empty flag and Almost Full flag offset registers with one of the three preset values listed in *Table 2*, the Serial Program Mode (SPM) and at least one of the flag-select inputs must be HIGH during the LOW-to-HIGH transition of its Master Reset input (MRS1, MRS2). For example, to load the preset value of 64 into X and Y, SPM, FS0 and FS1 must be HIGH when the FIFO reset (MRS1, MRS2) returns HIGH. When using one of the preset values for the flag offsets, the FIFO can be reset simultaneously or at different times.

To program the X and Y registers from Port A, perform a Master Reset on both FIFOs simultaneously with SPM HIGH and FS0 and FS1 LOW during the LOW-to-HIGH transition of MRS1/MRS2. After this reset is complete, the first two writes to the FIFO do not store data in RAM but load the offset registers in the order Y and X. The Port A data inputs used by the offset registers are  $(A_{0-9})$ ,  $(A_{0-11})$ , or  $(A_{0-13})$ ,for the CY7C436x3, respectively. The highest numbered input is used as the most significant bit of the binary number in each case. Valid programming values for the registers range from 0 to 1023 for the CY7C43643; 0to 4095 for the CY7C43663; 0 to 16383 for the CY7C43683. Before programming the offset register, FF/IR is set HIGH. FIFOs begin normal operation after programming is done.

To program the X and Y registers serially, initiate a Master Reset with SPM LOW, FS0/SD LOW, and FS1/SEN HIGH during the LOW-to-HIGH transition of MRS1/MRS2. After this reset is complete, the X and Y register values are loaded bit-wise through the FS0/SD input on each LOW-to-HIGH transition of CLKA that the FS1/SEN input is LOW. Twenty, twenty four, or twenty eight bit writes are needed to complete the programming for the CY7C436x3, respectively. The two registers are written in the order Y then finally X. The first-bit write stores the most significant bit of the Y register and the last-bit write stores the least significant bit of the X register. Each register value can be programmed from 0 to 1023 for the CY7C43643; 0 to 4095 for the CY7C43663; 0 to 16383 (Cy7c43683).

When the option to program the offset registers serially is chosen, the Port A Full/Input Ready (FF/IR) flag remains LOW until all register bits are written. FF/IR is set HIGH by the LOW-to-HIGH transition of CLKA after the last bit is loaded to allow normal FIFO operation.

SPM, FS0/SD, and FS1/SEN function the same way in both CY Standard and FWFT modes.

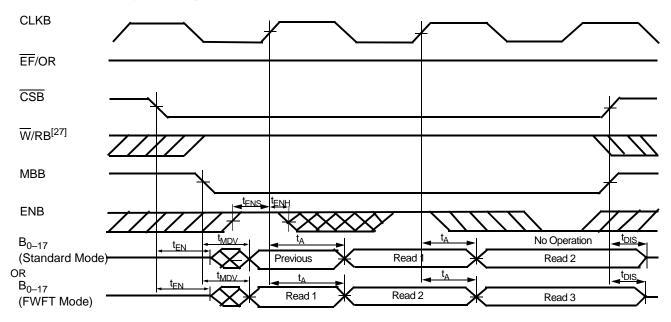

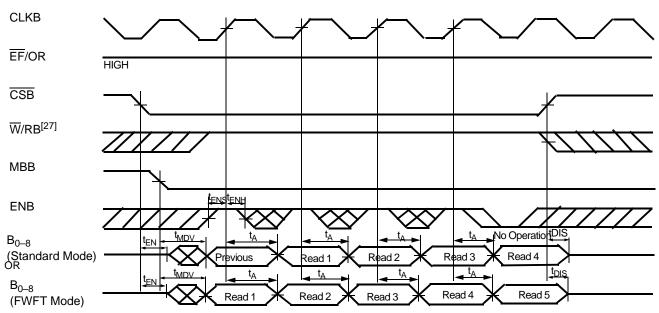

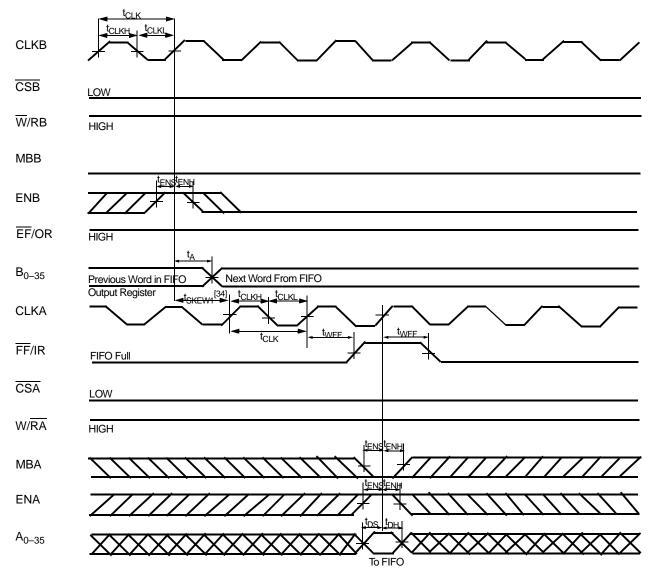

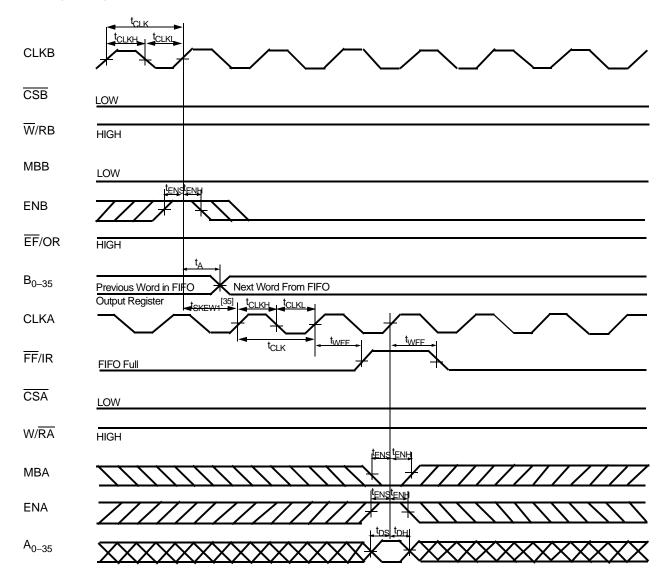

#### **FIFO Write/Read Operation**

The state of the <u>Port</u> A data ( $A_{0-35}$ ) lines is controlled by <u>Port</u> A Chip Select (CSA) and Port A Write/Read Select (W/RA). <u>The</u>  $A_{0-35}$  lines are in the high-impedance state when either CSA or W/RA is HIGH. The  $A_{0-35}$  lines are active mail 2 register outputs when both CSA and W/RA are LOW.

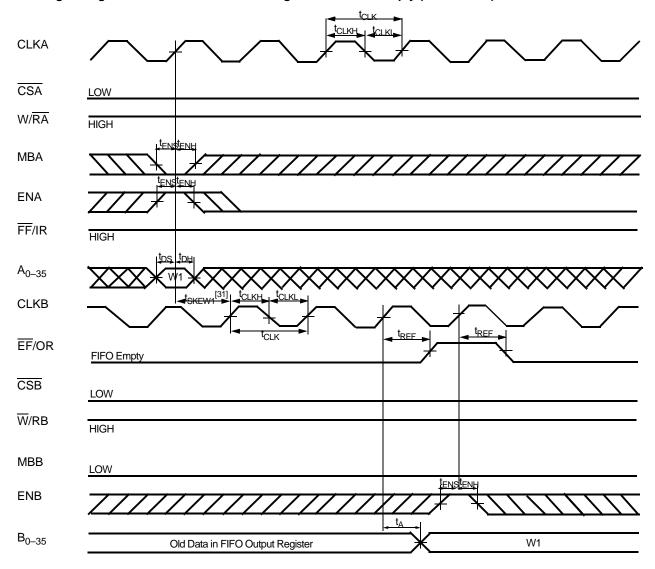

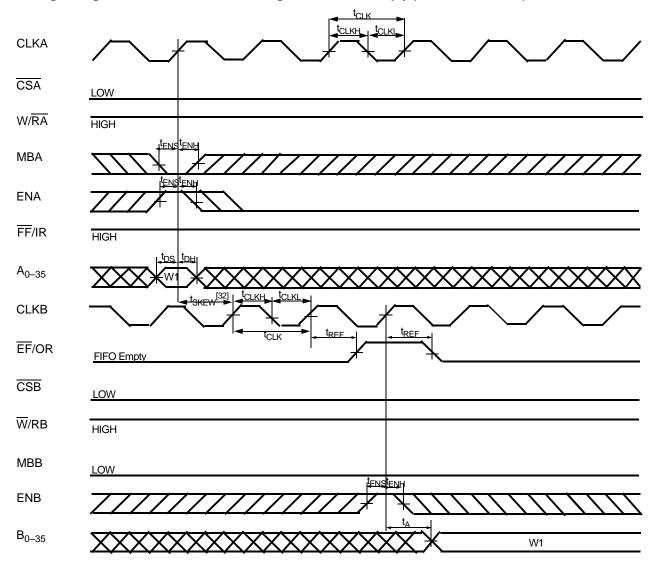

Data is loaded into the FIFO from the  $A_{0-35}$  inputs on a LOW-to-HIGH transition of CLKA when CSA is LOW, W/RA is HIGH, ENA is HIGH, MBA is LOW, and FF/IR is HIGH (see *Table 3*). FIFO writes on Port A are independent of any concurrent Port B operation.

The Port B control signals are identical to those of Port A with the exception that the Port B Write/Read Select (W/RB) is the inverse of the Port A Write/Read Select (W/RA). The state of the Port B data (B<sub>0-35</sub>) lines is controlled by the Port B Chip Select (CSB) and Port B Write/Read Select (W/RB). The B<sub>0-35</sub>

lines are in the high-impedance state when either  $\overline{\text{CSB}}$  is HIGH or W/RB is LOW. The B\_{0-35} lines are active outputs when  $\overline{\text{CSB}}$  is LOW and W/RB is HIGH.

Data is read from the FIFO to the <u>B<sub>0-35</sub></u> outputs by a LOW-to-HIGH transition of CLKB when <u>CSB</u> is LOW, W/RB is HIGH, ENB is HIGH, MBB is LOW, and EF/OR is HIGH (see *Table 4*). FIFO reads and writes on Port B are independent of any concurrent Port A operation.

The Set-up and hold time constraints to the port clocks for the port Chip Selects and Write/Read Selects are only for enabling write and read operations and are not related to high-impedance control of the data outputs. If a port enable is LOW during a clock cycle, the port's Chip Select and Write/Read Select may change states during the Set-up and hold time window of the cycle.

When operating the FIFO in FWFT Mode with the Output Ready flag LOW, the next word written is automatically sent to the FIFO's output register by the LOW-to-HIGH transition of the port clock that sets the Output Ready flag HIGH, data residing in the FIFO's memory array is clocked to the output register only when a read is selected using the port's Chip Select, Write/Read Select, Enable, and Mailbox Select.

When operating the FIFO in CY Standard Mode, regardless of whether the Empty Flag is LOW or HIGH, data residing in the FIFO's memory array is clocked to the output register only when a read is selected using the port's Chip Select, Write/Read Select, Enable, and Mailbox Select.

### Synchronized FIFO Flags

Each FIFO is synchronized to its port clock through at least two flip-flop stages. This is done to improve flag-signal reliability by reducing the probability of the metastable events when CLKA and CLKB operate asynchronously to one another. EF/OR and AE are synchronized to CLKA. FF/IR and AF are synchronized to CLKB. *Table 5* shows the relationship of each port flag to the FIFO.

### Empty/Output Ready Flags (EF/OR)

These are dual-purpose flags. In the FWFT Mode, the Output Ready (OR) function is selected. When the Output Ready flag is HIGH, new data is present in the FIFO output register. When the Output Ready flag is LOW, the previous data word is present in the FIFO output register and attempted FIFO reads are ignored.<sup>[1]</sup>

In the CY Standard Mode, the Empty Flag ( $\overline{\text{EF}}$ ) function is selected. When the Empty Flag is HIGH, data is available in the FIFO's RAM memory for reading to the output register. When the Empty Flag is LOW, the previous data word is present in the FIFO output register and attempted FIFO reads are ignored.

The Empty/Output Ready flag of a FIFO is synchronized to the port clock that reads data from its array. For both the FWFT and CY Standard modes, the FIFO read pointer is incremented each time a new word is clocked to its output register. The state machine that controls an Output Ready flag monitors a write pointer and read pointer comparator that indicates when the FIFO SRAM status is empty, or empty+1.

In FWFT Mode, from the time a word is written to a FIFO, it can be shifted to the FIFO output register in a minimum of three cycles of the Output Ready flag synchronizing clock. Therefore, an Output Ready flag is LOW if a word in memory is the next data to be sent to the FIFO output register and three cycles have not elapsed since the time the word was written. The Output Ready flag of the FIFO remains LOW until the third LOW-to-HIGH transition of the synchronizing clock occurs, simultaneously forcing the Output Ready flag HIGH and shifting the word to the FIFO output register.

In the CY Standard Mode, from the time a word is written to a FIFO, the Empty Flag will indicate the presence of data available for reading in a minimum of two cycles of the Empty Flag synchronizing clock. Therefore, an Empty Flag is LOW if a word in memory is the next data to be sent to the FIFO output register and two cycles have not elapsed since the time the word was written. The Empty Flag of the FIFO remains LOW until the second LOW-to-HIGH transition of the synchronizing clock occurs, forcing the Empty Flag HIGH; only then can data be read.

A LOW-to-HIGH transition on an Empty/Output Ready flag synchronizing clock begins the first synchronization cycle of a write if the clock transition occurs at time  $t_{SKEW1}$  or greater after the write. Otherwise, the subsequent clock cycle can be the first synchronization cycle.

### Full/Input Ready Flags (FF/IR)

This is a dual-purpose flag. In FWFT Mode, the Input Ready (IR) function is selected. In CY Standard Mode, the Full Flag (FF) function is selected. For both timing modes, when the Full/Input Ready flag is HIGH, a memory location is free in the SRAM to receive new data. No memory locations are free when the Full/Input Ready flag is LOW and attempted writes to the FIFO are ignored.

The Full/Input Ready flag of a FIFO is synchronized to the port clock that writes data to its array. For both FWFT and CY Standard modes, each time a word is written to a FIFO, its write pointer is incremented. The state machine that controls a Full/Input Ready flag monitors a write pointer and read pointer comparator that indicates when the FIFO SRAM status is full, or full–1. From the time a word is read from a FIFO, its previous memory location is ready to be written to in a minimum of two cycles of the Full/Input Ready flag synchronizing clock. Therefore, an Full/Input Ready flag is LOW if less than two cycles of the Full/Input Ready flag synchronizing clock have elapsed since the next memory write location has been read. The second LOW-to-HIGH transition on the Full/Input Ready flag synchronizing clock after the read sets the Full/Input Ready flag HIGH.

A LOW-to-HIGH transition on a Full/Input Ready flag synchronizing clock begins the first synchronization cycle of a read if the clock transition occurs at time  $t_{SKEW1}$  or greater after the read. Otherwise, the subsequent clock cycle can be the first synchronization cycle.

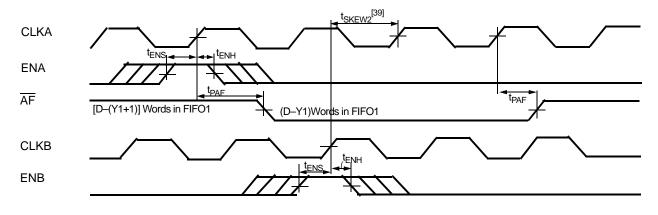

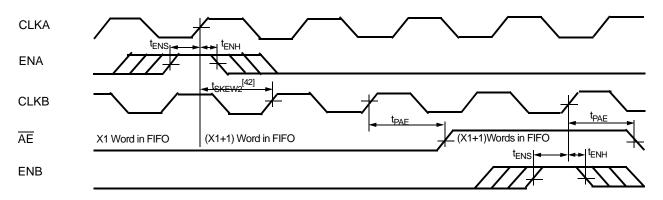

### Almost Empty Flags (AE)

The Almost Empty flag of the FIFO is synchronized to port B clock. The state machine that controls an Almost Empty flag monitors a write pointer and read pointer comparator that indicates when the FIFO SRAM status is almost empty, or almost empty+1. The Almost Empty state is defined by the contents of register X for  $\overline{AE}$ . These registers are loaded with preset values during a FIFO reset, programmed from Port A, or programmed serially (see Almost Empty flag and Almost Full flag offset programming above). An Almost Empty flag is LOW when its FIFO contains X or less words and is HIGH when its FIFO contains (X+1) or more words<sup>[2]</sup>.

Two LOW-to-HIGH transitions of the Almost Empty flag synchronizing clock are required after a FIFO write for its Almost Empty flag to reflect the new level of fill. Therefore, the Almost empty flag of a FIFO containing (X+1) or more words remains LOW if two cycles of its synchronizing clock have not elapsed since the write that filled the memory to the (X+1) level. An Almost Empty flag is set HIGH by the second LOW-to-HIGH transition of its synchronizing clock after the FIFO write that fills memory to the (X+1) level. A LOW-to-HIGH transition of an Almost Empty flag synchronizing clock begins the first synchronization cycle if it occurs at time  $t_{SKEW2}$  or greater after the write that fills the FIFO to (X+1) words. Otherwise, the subsequent synchronizing clock cycle may be the first synchronization cycle.

#### Almost Full Flags (AFA, AFB)

The Almost Full flag of the FIFO is synchronized to port A clock. The state machine that controls an Almost Full flag monitors a write pointer and read pointer comparator that indicates when the FIFO SRAM status is almost full, or almost full–1. The Almost Full state is defined by the contents of register Y for AF. These registers are loaded with preset values during a FIFO reset, programmed from Port A, or programmed serially (see Almost Empty flag and Almost Full flag offset programming above). An Almost Full flag is LOW when the number of words in its FIFO is greater than or equal to (1024–Y), (4096–Y), or (16384–Y) for the CY7C436x3 respectively. An Almost Full flag is HIGH when the number of words in its FIFO is less than or equal to [1024–(Y+1)], [4096–(Y+1)], or [16384–(Y+1)], for the CY7C436x3 respectively.<sup>[2]</sup>

Two LOW-to-HIGH transitions of the Almost Full flag synchronizing clock are required after a FIFO read for its Almost Full flag to reflect the new level of fill. Therefore, the Almost Full flag of a FIFO containing [1024/4096/16384-(Y+1)] or less words remains LOW if two cycles of its synchronizing clock have not elapsed since the read that reduced the number of words in memory to [1024/4096/16384-(Y+1)]. An Almost Full flag is set HIGH by the second LOW-to-HIGH transition of its synchronizing clock after the FIFO read that reduces the number of words in memory to [1024/4096/16384-(Y+1)]. A LOW-to-HIGH transition of an Almost Full flag synchronizing clock begins the first synchronization cycle if it occurs at time t<sub>SKEW2</sub> or greater after the read that reduces the number of words in memory to [1024/4096/16384-(Y+1)]. Otherwise, the subsequent synchronizing clock cycle may be the first synchronization cycle.

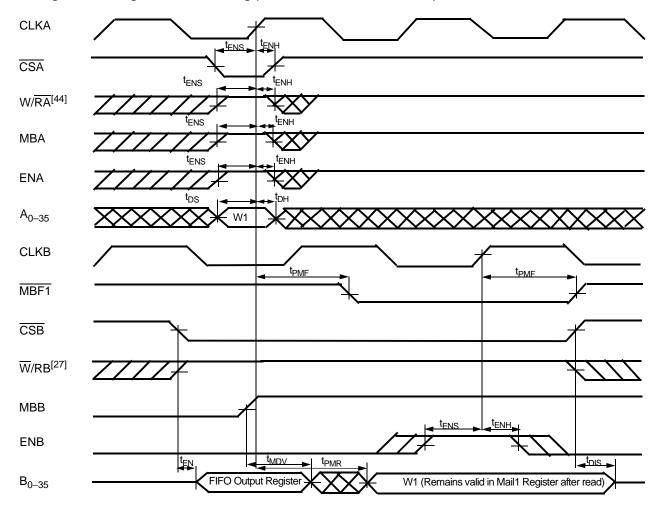

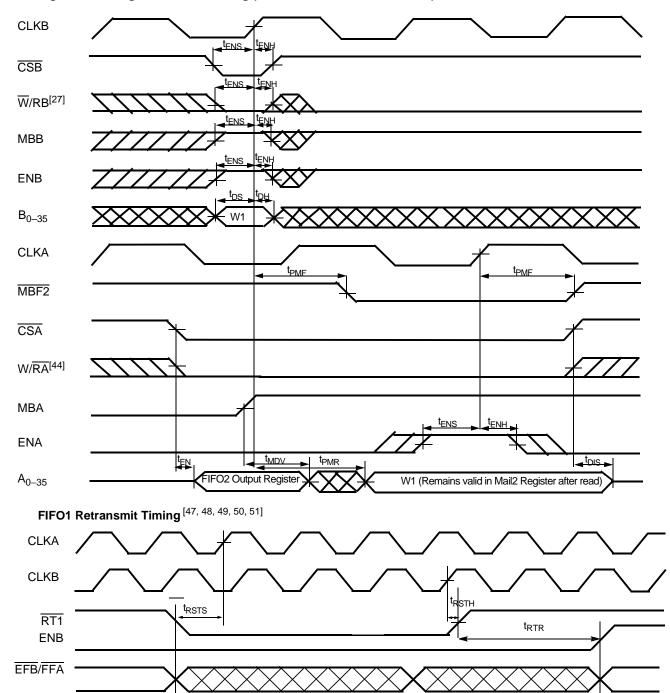

#### **Mailbox Registers**

Each FIFO has a 36-bit bypass register to pass command and control information between Port A and Port B without putting it in queue. The Mailbox Select (MBA, MBB) inputs choose between a mail register and a FIFO for a port data transfer operation. The usable width of both the Mail1 and Mail2 registers matches the selected bus size for Port B.

A LOW-to-HIGH transition on CLKA writes  $A_{0.35}$  data to the Mail1 Register when a Port A write is selected by CSA, W/RA, and ENA with MBA HIGH. If the selected Port A bus size is also 36 bits, then the usable width of the Mail1 Register employs data lines  $A_{0-35}$ . If the selected Port A bus size is 18 bits, then the usable width of the Mail1 Register employs data lines  $A_{0-17}$ . (In this case,  $A_{18-35}$  are "don't care" inputs.) If the selected Port A bus size is 9 bits, then the usable width of the Mail1 Register employs data lines  $A_{0-8}.$  (In this case,  $A_{9-35}$  are "don't care" inputs.)

A LOW-to-HIGH transition on CLKB writes  $B_{0-35}$  data to the Mail2 register when a Port B write is selected by CSB, W/RB, and ENB with MBB HIGH. If the selected Port B bus size is also 36 bits, then the usable width of the Mail2 Register employs data lines  $B_{0-35}$ . If the selected Port B bus size is 18 bits, then the usable width of the Mail2 register employs data lines  $B_{0-17}$ . (In this case,  $B_{18-35}$  are "don't care" inputs.) If the selected Port B bus size is 9 bits, then the usable width of the Mail2 register employs data lines  $B_{0-17}$ . (In this case,  $B_{18-35}$  are "don't care" inputs.) If the selected Port B bus size is 9 bits, then the usable width of the Mail2 Register employs data lines  $B_{0-8}$ . (In this case,  $B_{9-35}$  are "don't care" inputs.)

<u>Writing</u> data to a mail register sets its corresponding flag (MBF1 or MBF2) LOW. Attempted writes to a mail register are ignored while the mail flag is LOW.

When data outputs of a port are active, the data on the bus comes from the FIFO output register when the port Mailbox Select input is LOW and from the mail register when the port Mailbox Select input is HIGH.

The Mail1 Register flag ( $\overline{\text{MBF1}}$ ) is set HIGH by a LOW-to-HIG<u>H</u> transition on CLKB when a Port B read is selected by CSB,  $\overline{\text{W/RB}}$ , and ENB with MBB HIGH. For a 36-bit bus size, 36 bits of mailbox data are placed on B<sub>0-35</sub>. For an 18-bit bus size, 18 bits of mailbox data are placed on B<sub>0-17</sub>. (In this case, B<sub>18-35</sub> are indeterminate.) For a 9-bit bus size, 9 bits of mailbox data are placed on B<sub>0-8</sub>. (In this case, B<sub>9-35</sub> are indeterminate.)

The Mail2 Register flag (MBF2) is set HIGH by a LOW-to-HIGH transition on CLKA when a Port A read is selected by CSA, W/RA, and ENA with MBA HIGH.

For a 36-bit bus size, 36 bits of mailbox data are placed on  $A_{0-35}$ . For an 18-bit bus size, 18 bits of mailbox data are placed on  $A_{0-17}$ . (In this case,  $A_{18-35}$  are indeterminate.) For a 9-bit bus size, 9 bits of mailbox data are placed on  $A_{0-8}$ . (In this case,  $A_{9-35}$  are indeterminate.)

The data in a mail register remains intact after it is read and changes only when new data is written to the register. The Endian Select feature has no effect on the mailbox data.

#### **Bus Sizing**

The Port B bus can be configured in a 36-bit long-word, 18-bit word, or 9-bit byte format for data read from FIFO. The levels applied to the Port B Bus Size Select (SIZE) and the Bus Match Select (BM) determine the Port B bus size. These levels should be static throughout FIFO operation. Both bus size selections are implemented at the completion of Master Reset, by the time the Full/Input Ready flag is set HIGH.

Two different methods for sequencing data transfer are available for Port B when the bus size selection is either byte-or word-size. They are referred to as Big Endian (most significant byte first) and Little Endian (least significant byte first). The level applied to the Big Endian Select (BE) input during the LOW-to-HIGH transition of MRS1/MRS2 selects the endian method that will be active during FIFO operation. BE is a don't care input when the bus size selected for Port B is long-word. The endian method is implemented at the completion of Master Reset, by the time the Full/Input Ready flag is set HIGH.

Only 36-bit long-word data is written to or read from the two FIFO memories on the CY7C436x3. Bus-matching operations are done after data is read from the FIFO. These bus-matching

operations are not available when transferring data via mailbox registers. Furthermore, both the word- and byte-size bus selections limit the width of the data bus that can be used for mail register operations. In this case, only those byte lanes belonging to the selected word- or byte-size bus can carry mailbox data. The remaining data outputs will be indeterminate. The remaining data inputs will be don't care inputs. For example, when a word-size bus is selected, then mailbox data can be transmitted only between  $A_{0-17}$  and  $B_{0-17}$ . When a byte-size bus is selected, then mailbox data can be transmitted only between  $A_{0-8}$ .

#### **Bus-Matching FIFO Reads**

Data is read from the FIFO RAM in 36-bit long-word increments. If a long-word bus size is implemented, the entire longword immediately shifts to the FIFO output register. If byte or word size is implemented on Port B, only the first one or two bytes appear on the selected portion of the FIFO output register, with the rest of the long-word stored in auxiliary registers. In this case, subsequent FIFO reads output the rest of the long-word to the FIFO output register. When reading data from the FIFO in the byte or word format, the unused  $B_{0-35}$  outputs are indeterminate.

### Retransmit (RT)

The retransmit feature is beneficial when transferring packets of data. It enables the receipt of data to be acknowledged by the receiver and retransmitted if necessary. Retransmit function applies to CY standard mode only.

The number of 36-/18-/9-bit words written into the FIFO should be less than full depth minus 2/4/8 words between the reset of the FIFO (master or partial) and Retransmit setup. A LOW pulse on RT resets the internal read pointer to the first physical location of the FIFO. CLKA and CLKB may be free-running but ENB must be disabled during and t<sub>RTR</sub> after the retransmit pulse. With every valid read cycle after retransmit, previously accessed data is read and the read pointer is incremented until it is equal to the write pointer. Flags are governed by the relative locations of the read and write pointers and are updated during a retransmit cycle. Data written to the FIFO after activation of RT are transmitted also. The full depth of the FIFO can be repeatedly transmitted.

### Table 2. Flag Programming<sup>[2]</sup>

| SPM | FS1/SEN | FS0/SD | MRS1/MRS2  | X and Y Registers <sup>[3]</sup> |

|-----|---------|--------|------------|----------------------------------|

| н   | Н       | н      | $\uparrow$ | 64                               |

| Н   | Н       | L      | $\uparrow$ | 16                               |

| Н   | L       | н      | $\uparrow$ | 8                                |

| Н   | L       | L      | $\uparrow$ | Parallel programming via Port A  |

| L   | Н       | L      | $\uparrow$ | Serial programming via SD        |

| L   | Н       | н      | $\uparrow$ | Reserved                         |

| L   | L       | н      | $\uparrow$ | Reserved                         |

| L   | L       | L      | $\uparrow$ | Reserved                         |

#### Table 3. Port A Enable Function

| CSA | W/RA | ENA | MBA | CLKA       | A <sub>0-35</sub> Outputs | Port Function              |

|-----|------|-----|-----|------------|---------------------------|----------------------------|

| Н   | Х    | Х   | Х   | Х          | In high-impedance state   | None                       |

| L   | Н    | L   | Х   | Х          | In high-impedance state   | None                       |

| L   | Н    | Н   | L   | $\uparrow$ | In high-impedance state   | FIFO write                 |

| L   | Н    | Н   | Н   | $\uparrow$ | In high-impedance state   | Mail1 write                |

| L   | L    | L   | L   | Х          | Active, Mail2 register    | None                       |

| L   | L    | Н   | L   | $\uparrow$ | Active, Mail2 register    | None                       |

| L   | L    | L   | Н   | Х          | Active, Mail2 register    | None                       |

| L   | L    | н   | Н   | ↑          | Active, Mail2 register    | Mail2 read (set MBF2 HIGH) |

### Table 4. Port B Enable Function

| CSB | W/RB | ENB | MBB | CLKB       | B <sub>0-35</sub> Outputs    | Port Function              |

|-----|------|-----|-----|------------|------------------------------|----------------------------|

| Н   | Х    | Х   | Х   | Х          | In high-impedance state      | None                       |

| L   | L    | L   | Х   | Х          | In high-impedance state      | None                       |

| L   | L    | Н   | L   | $\uparrow$ | In high-impedance state      | None                       |

| L   | L    | Н   | Н   | $\uparrow$ | In high-impedance state      | Mail2 write                |

| L   | Н    | L   | L   | Х          | Active, FIFO output register | None                       |

| L   | Н    | Н   | L   | $\uparrow$ | Active, FIFO output register | FIFO read                  |

| L   | Н    | L   | Н   | Х          | Active, Mail1 register       | None                       |

| L   | Н    | Н   | Н   | $\uparrow$ | Active, Mail1 register       | Mail1 read (set MBF1 HIGH) |

### Table 5. FIFO Flag Operation (CY Standard and FWFT Modes)<sup>[2]</sup>

| Number of Words in      | FIFO Memory <sup>[4, 5, 6, 7]</sup> | Synchronized             | I to CLKB | Synchronized to CLKA |    |       |

|-------------------------|-------------------------------------|--------------------------|-----------|----------------------|----|-------|

| CY7C43643               | CY7C43663                           | CY7C43683                | EF/OR     | AE                   | AF | FF/IR |

| 0                       | 0                                   | 0                        | L         | L                    | Н  | Н     |

| 1 TO X1                 | 1 TO X1                             | 1 TO X1                  | Н         | L                    | Н  | Н     |

| (X1+1) to [1024–(Y1+1)] | (X1+1) to [4096–(Y1+1)]             | (X1+1) to [16384–(Y1+1)] | Н         | Н                    | Н  | Н     |

| (1024–Y1) to 1023       | (4096–Y1) to 4095                   | (16384–Y1) to 16383      | Н         | Н                    | L  | Н     |

| 1024                    | 4096                                | 16384                    | Н         | Н                    | L  | L     |

#### Notes:

3.

X register holds the offset for AE; Y register holds the offset for AF. X is the Almost Empty offset for FIFO used by AE. Y is the Almost Full offset for FIFO used by AF. Both X and Y are selected during a FIFO reset or port A 4. When a word loaded to an empty FIFO is shifted to the output register, its previous FIFO memory location is free. Data in the output register does not count as a "word in FIFO memory". Since in FWFT Mode, the first word written to an empty FIFO goes unrequested to the output register (no read operation necessary), it is not included in the <u>EI</u>FO memory count. The OR and IR functions are active during FWFT mode; the EF and FF functions are active in CY Standard Mode. 5.

6.

7.

### Table 6. Data Size for FIFO Long-Word Reads

| 9  | Size Mode <sup>[9</sup> | 9] |                    | Data Writt                                                               | en to FIFO |   |                    | Data Read          | From FIFO         |                  |

|----|-------------------------|----|--------------------|--------------------------------------------------------------------------|------------|---|--------------------|--------------------|-------------------|------------------|

| BM | SIZE                    | BE | A <sub>27-35</sub> | A <sub>27-35</sub> A <sub>18-26</sub> A <sub>9-17</sub> A <sub>0-8</sub> |            |   | B <sub>27-35</sub> | B <sub>18-26</sub> | B <sub>9–17</sub> | B <sub>0-8</sub> |

| L  | Х                       | Х  | А                  | В                                                                        | С          | D | A                  | В                  | С                 | D                |

### Table 7. Data Size for Word Reads

|    | Size Mode <sup>[9]</sup> |    |                    | Data Writt         | en to FIFO        | Read No.         | Data Read | From FIFO         |                  |

|----|--------------------------|----|--------------------|--------------------|-------------------|------------------|-----------|-------------------|------------------|

| BM | SIZE                     | BE | A <sub>27–35</sub> | A <sub>18–26</sub> | A <sub>9-17</sub> | A <sub>0-8</sub> |           | B <sub>9-17</sub> | B <sub>0-8</sub> |

| Н  | L                        | Н  | A                  | В                  | С                 | D                | 1         | A                 | В                |

|    |                          |    |                    |                    |                   |                  | 2         | С                 | D                |

| Н  | L                        | L  | A                  | В                  | С                 | D                | 1         | С                 | D                |

|    |                          |    |                    |                    |                   |                  | 2         | A                 | В                |

Table 8. Data Size for Byte Reads from FIFO

|    | Size Mode <sup>[9]</sup> |    |                    | Data Writt         | Read No.          | Data Read From<br>FIFO |   |                  |

|----|--------------------------|----|--------------------|--------------------|-------------------|------------------------|---|------------------|

| BM | SIZE                     | BE | A <sub>27-35</sub> | A <sub>18–26</sub> | A <sub>9–17</sub> | A <sub>0-8</sub>       |   | B <sub>0-8</sub> |

| Н  | Н                        | Н  | А                  | В                  | С                 | D                      | 1 | A                |

|    |                          |    |                    |                    |                   |                        | 2 | В                |

|    |                          |    |                    |                    |                   |                        | 3 | С                |

|    |                          |    |                    |                    |                   |                        | 4 | D                |

| Н  | Н                        | L  | A                  | В                  | С                 | D                      | 1 | D                |

|    |                          |    |                    |                    |                   |                        | 2 | С                |

|    |                          |    |                    |                    |                   |                        | 3 | В                |

|    |                          |    |                    |                    |                   |                        | 4 | A                |

Notes:

BE is selected at Master Reset; BM and SIZE must be static throughout device operation.

# CY7C43643 CY7C43663 CY7C43683

### Maximum Ratings<sup>[10,12]</sup>

(Above which the useful life may be impaired. For user guidelines, not tested.)

| Storage Temperature65°C to +15                                                              | 0°C |

|---------------------------------------------------------------------------------------------|-----|

| Ambient Temperature with<br>Power Applied55°C to +12                                        | 5°C |

| Supply Voltage to Ground Potential0.5V to +7                                                | .0V |

| DC Voltage Applied to Outputs<br>in High-Z State <sup>[11]</sup> 0.5V to V <sub>CC</sub> +0 |     |

| DC Input Voltage <sup>[11]</sup> 0.5V to V <sub>CC</sub> +0                                 | .5V |

### Electrical Characteristics Over the Operating Range

| Output Current into Outputs (LOW)                          | 20 mA   |

|------------------------------------------------------------|---------|

| Static Discharge Voltage<br>(per MIL-STD-883, Method 3015) | .>2001V |

| (po: 0 000,                                                |         |

Latch-up Current.....> 200 mA

### **Operating Range**

| Range      | Ambient<br>Temperature | <b>V<sub>CC<sup>[13]</sup></sub></b> |

|------------|------------------------|--------------------------------------|

| Commercial | 0°C to +70°C           | 5.0V ± 0.5V                          |

| Industrial | ∠40°C to +85°C         | 5.0V ± 0.5V                          |

|                                      |                             |                                                                                                          |       | CY7C436 |                 |      |

|--------------------------------------|-----------------------------|----------------------------------------------------------------------------------------------------------|-------|---------|-----------------|------|

| Parameter                            | Description                 | Test Conditions                                                                                          |       | Min.    | Max.            | Unit |

| V <sub>OH</sub>                      | Output HIGH Voltage         | $V_{CC} = 4.5V$ ,<br>$I_{OH} = \angle 4.0 \text{ mA}$                                                    |       | 2.4     |                 | V    |

| V <sub>OL</sub>                      | Output LOW Voltage          | $V_{CC} = 4.5V,$<br>$I_{OL} = 8.0 \text{ mA}$                                                            |       |         | 0.5             | V    |

| V <sub>IH</sub>                      | Input HIGH Voltage          |                                                                                                          |       | 2.0     | V <sub>CC</sub> | V    |

| V <sub>IL</sub>                      | Input LOW Voltage           |                                                                                                          |       | ∠0.5    | 0.8             | V    |

| I <sub>IX</sub>                      | Input Leakage Current       | V <sub>CC</sub> = Max.                                                                                   |       | ∠10     | +10             | μΑ   |

| I <sub>OZL</sub><br>I <sub>OZH</sub> | Output OFF, High-Z Current  | $\label{eq:VIH} \begin{array}{ c c } \hline \hline OE \geq V_{IH}, \\ V_{SS} < V_O < V_{CC} \end{array}$ |       | ∠10     | +10             | μΑ   |

| I <sub>CC1</sub> <sup>[14]</sup>     | Active Power Supply Current |                                                                                                          | Com'l |         | 100             | mA   |

|                                      |                             |                                                                                                          | Ind   |         | 100             | mA   |

| I <sub>SB</sub> <sup>[15]</sup>      | Average Standby Current     |                                                                                                          | Com'l |         | 10              | mA   |

|                                      |                             |                                                                                                          | Ind   |         | 10              | mA   |

### Capacitance<sup>[16]</sup>

| Parameter        | Description        | Test Conditions                         | Max. | Unit |

|------------------|--------------------|-----------------------------------------|------|------|

| C <sub>IN</sub>  | Input Capacitance  | $T_A = 25^{\circ}C, f = 1 \text{ MHz},$ | 4    | pF   |

| C <sub>OUT</sub> | Output Capacitance | $V_{CC} = 3.3V$                         | 8    | pF   |

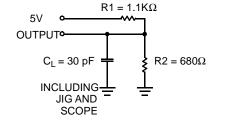

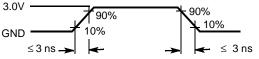

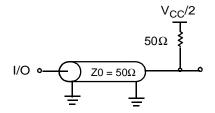

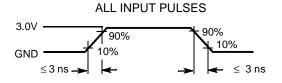

### AC Test Loads and Waveforms (-10 and -15)

# ALL INPUT PULSES

#### Notes:

- Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

The input and output voltage ratings may be exceeded provided the input and output current ratings are observed.

The Voltage on any input or I/O pin cannot exceed the power pin during power-up.

Operating V<sub>CC</sub> range for -7 speed is 5.0V ±0.25V.

Unter input input or I/O to 20.25V.

- 14. Input signals switch from 0V to 3V with a rise/fall time of less than 3 ns, clocks and clock enables switch at 20 MHz, while data inputs switch at 10 MHz. Outputs are unloaded. 15. All inputs =  $V_{CC} - 0.2V$ , except RCLK and WCLK (which are at frequency = 0 MHz). All outputs are unloaded.

- 16. Tested initially and after any design or process changes that may affect these parameters.

# AC Test Loads and Waveforms (-7)

### Switching Characteristics Over the Operating Range

|                   |                                                                                                                                                        |      | CY7C43643/<br>63/83<br>_7 |      | CY7C43643/<br>63/83<br>–10 |      | CY7C43643/<br>63/83<br>-15 |      |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------------------|------|----------------------------|------|----------------------------|------|

| Parameter         | Description                                                                                                                                            | Min. | Max.                      | Min. | Max.                       | Min. | Max.                       | Unit |

| f <sub>S</sub>    | Clock Frequency, CLKA or CLKB                                                                                                                          |      | 133                       |      | 100                        |      | 67                         | MHz  |

| t <sub>CLK</sub>  | Clock Cycle Time, CLKA or CLKB                                                                                                                         | 7.5  |                           | 10   |                            | 15   |                            | ns   |

| t <sub>CLKH</sub> | Pulse Duration, CLKA or CLKB HIGH                                                                                                                      | 3.5  |                           | 4    |                            | 6    |                            | ns   |

| t <sub>CLKL</sub> | Pulse Duration, CLKA or CLKB LOW                                                                                                                       | 3.5  |                           | 4    |                            | 6    |                            | ns   |

| t <sub>DS</sub>   | Set-up Time, $A_{0\!-\!35}$ before CLKA $\uparrow$ and $B_{0\!-\!35}$ before CLKB $\uparrow$                                                           | 3    |                           | 4    |                            | 5    |                            | ns   |

| t <sub>ENS</sub>  | Set-up T <u>ime, CS</u> A, W/RA, ENA, and MBA before<br>CLKA↑; CSB, W/RB, ENB, and MBB before<br>CLKB↑                                                 | 3    |                           | 4    |                            | 5    |                            | ns   |

| t <sub>RSTS</sub> | Set-up Time, MRS1/MRS2, PRS or RT1 LOW<br>before CLKA↑ or CLKB↑ <sup>[17]</sup>                                                                        | 2.5  |                           | 4    |                            | 5    |                            | ns   |

| t <sub>FSS</sub>  | Set-up Time, FS0 and FS1 before MRS1/MRS2<br>HIGH                                                                                                      | 6    |                           | 7    |                            | 7.5  |                            | ns   |

| t <sub>BES</sub>  | Set-up Time, BE/FWFT before MRS1/MRS2 HIGH                                                                                                             | 5    |                           | 7    |                            | 7.5  |                            | ns   |

| t <sub>SPMS</sub> | Set-up Time, SPM before MRS1/MRS2 HIGH                                                                                                                 | 5    |                           | 7    |                            | 7.5  |                            | ns   |

| t <sub>SDS</sub>  | Set-up Time, FS0/SD before CLKA↑                                                                                                                       | 3    |                           | 4    |                            | 5    |                            | ns   |

| t <sub>SENS</sub> | Set-up Time, FS1/SEN before CLKA↑                                                                                                                      | 3    |                           | 4    |                            | 5    |                            | ns   |

| t <sub>FWS</sub>  | Set-up Time, FWFT before CLKA↑                                                                                                                         | 0    |                           | 0    |                            | 0    |                            | ns   |

| t <sub>DH</sub>   | Hold Time, $A_{0-35}$ after CLKA $\uparrow$ and $B_{0-35}$ after CLKB $\uparrow$                                                                       | 0    |                           | 0    |                            | 0    |                            | ns   |

| t <sub>ENH</sub>  | Hold Tim <u>e, CSA</u> , W/RA, ENA, and MBA after<br>CLKA↑; CSB, W/RB, ENB, and MBB after CLKB↑                                                        | 0    |                           | 0    |                            | 0    |                            | ns   |

| t <sub>RSTH</sub> | Hold Time, $\overline{\text{MRS1}/\text{MRS2}}$ , $\overline{\text{PRS}}$ or $\overline{\text{RT1}}$ LOW after CLKA <sup>↑</sup> or CLKB <sup>17</sup> | 1    |                           | 2    |                            | 4    |                            | ns   |

| t <sub>FSH</sub>  | Hold Time, FS0 and FS1 after MRS1/MRS2 HIGH                                                                                                            | 1    |                           | 1    |                            | 2    |                            | ns   |

| t <sub>BEH</sub>  | Hold Time, BE/FWFT after MRS1/MRS2 HIGH                                                                                                                | 1    |                           | 1    |                            | 2    |                            | ns   |

| t <sub>SPMH</sub> | Hold Time, SPM after MRS1/MRS2 HIGH                                                                                                                    | 1    |                           | 1    |                            | 2    | 1                          | ns   |

| t <sub>SDH</sub>  | Hold Time, FS0/SD after CLKA↑                                                                                                                          |      |                           | 0    | Ī                          | 0    | 1                          | ns   |

| t <sub>SENH</sub> | Hold Time, FS1/SEN after CLKA↑                                                                                                                         | 0    |                           | 0    | Ī                          | 0    | 1                          | ns   |

| t <sub>SPH</sub>  | Hold Time, FS1/SEN HIGH after MRS1/MRS2<br>HIGH                                                                                                        | 0    |                           | 1    |                            | 2    |                            | ns   |

17. Requirement to count the clock edge as one of at least four needed to reset a FIFO.