# PRELIMINARY

# AX™ ATM-SONET/SDH Transceiver

#### **Features**

- · WAN and LAN ATM physical layer device

- Provides complete physical layer transport of ATM cells at:

- STS-3c/ STM-1 rate of 155.52 MHz

- STS-1 rate of 51.84 MHz

- Compliant with ATM Forum User Network Interface 3.1 specification

- UTOPIA ATM interface

- ATM cell processing including:

- HEC generation/verification

- Cell scrambling/descrambling

- Rate adaption/idle cell filtering

- Local Flow Control

- Cell alignment

- · SONET frame processing including:

- Compliant with Bellcore GR-253, I.432,

T1.105, and G.709 for Jitter Tolerance and Jitter Generation

- Frame generation/recovery

- SONET scrambling/descrambling

- Frequency justification/pointer processing

- Complete line interface including:

- Clock and data recovery

- Transmit timing derived from receiver or byte-rate source

- SONET compliant PLL

- -100K PECL compatible I/O

- Alarm indications including:

- Loss Of Signal

- Out Of Frame, Loss Of Frame

- Line Far End Receive Failure

- Line Alarm Indication Signal

- B1 Parity Error

- Loss Of Cell Alignment

- Loss Of Receive Data

- Controller interface for internal interrupt and configuration registers including:

- Error monitoring

- Status indication

- Device configuration

- 0.65μ Low Power CMOS

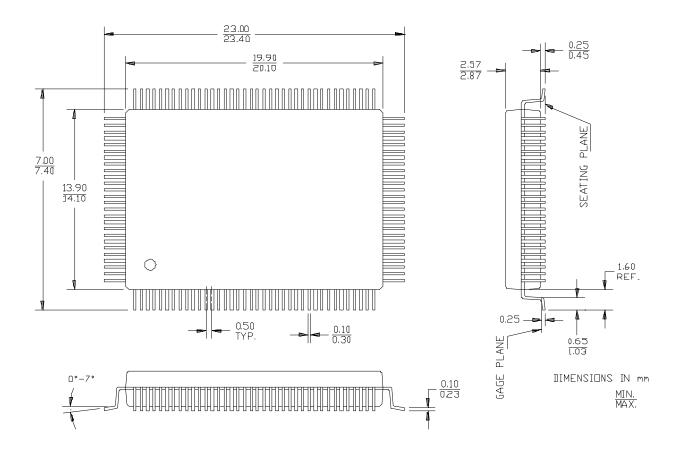

- 128-pin PQFP

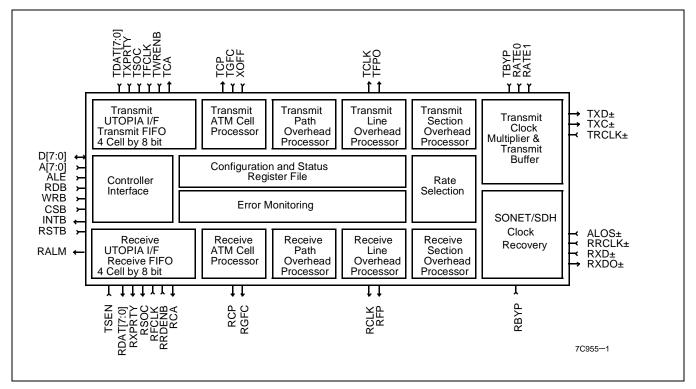

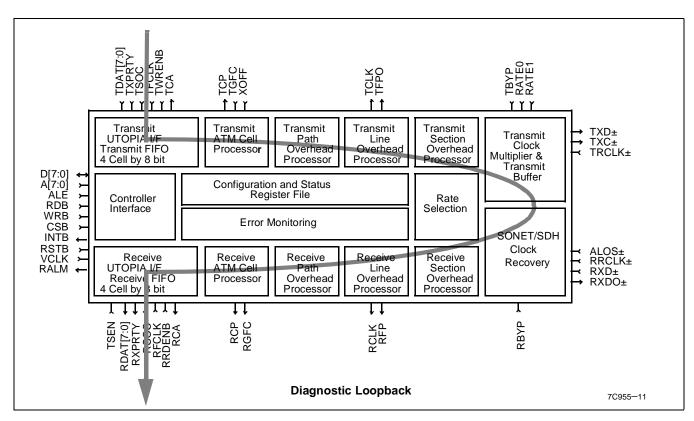

### **Functional Description**

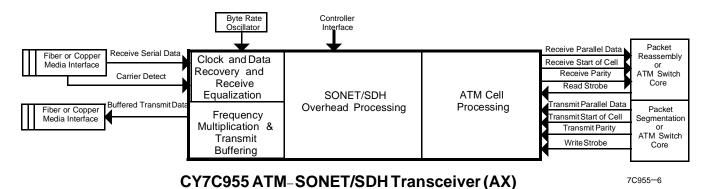

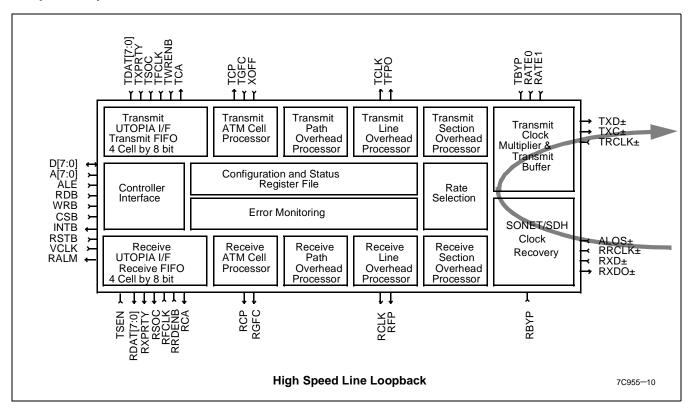

The Cypress Semiconductor CY7C955 is a Transceiver chip designed to carry ATM cells across SONET/SDH systems.

On the transmit side, ATM cells coming from the Utopia interface are being mapped into SONET/SDH frames and then serialized for transmission over fiber or twisted pair (through an optical module or an equalizer chip).

On the receive side, serial SONET/SDH datastreams coming from an optical module or an equalizer chip are being recovered by the intergrated clock and data recovery phase-locked loop, framed, processed, and presented as parallel ATM cells on the Receive Utopia Interface.

The CY7C955 can be used in a Network Interface Card (NIC) design to connect the segmentation and Reassembly (SAR) chip to the optical modules or equalizer chip.

The CY7C955 can also be used in work group or enterprise switches to connect the I/O FIFOs of the switch fabric to the optical module or equalizer in the interface boards.

The applications of the CY7C955 include adapters, switches, routers, hubs, and proprietary systems.

| TABLE OF CONTENTS           |    |

|-----------------------------|----|

| Features                    | 1  |

| Functional Description      | 1  |

| Pin Descriptions            | 2  |

| Pin Configuration           | 7  |

| Description                 | 8  |

| Transmit Section            | 8  |

| Receive Section             | 10 |

| Controller Interface (CI)   | 12 |

| Loopback Operation          | 16 |

| SONET Overhead Description  | 17 |

| CY7C955 Register Map        | 18 |

| Electrical Characteristics  | 60 |

| Capacitance                 | 61 |

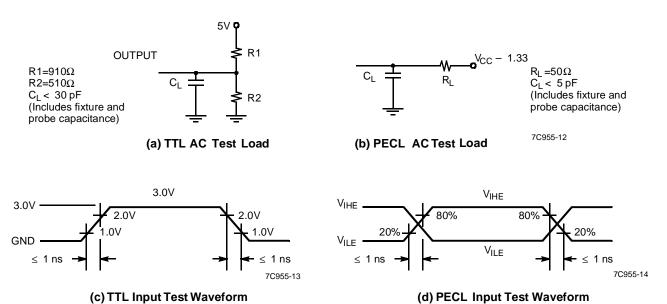

| AC Test Loads and Waveforms | 61 |

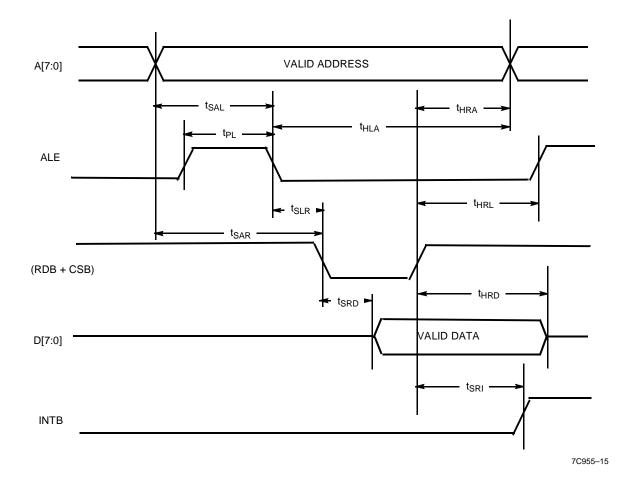

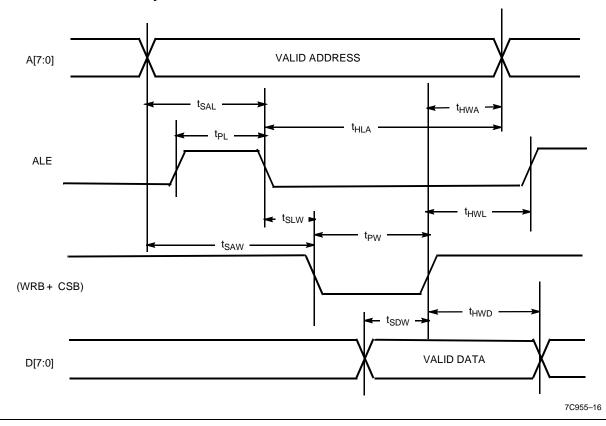

| Switching Characteristics   | 61 |

| TABLE OF CONTENTS (continued)             |    |

|-------------------------------------------|----|

| Switching Waveforms                       | 63 |

| Functional Timing Diagram                 | 69 |

| Interface Termination and Biasing Schemes | 73 |

| Filter Pin Configuration                  | 75 |

| Ordering Information                      | 76 |

| Package Diagram                           | 77 |

# **Pin Descriptions**

### CY7C955 ATM-SONET/SDH Transceiver

Transmit Utopia Interface

| Name      | Pin   | I/O   | Description                                                                                                                                                                                                                                                       |

|-----------|-------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TDAT[7:0] | 87–94 | Input | Transmit Utopia data: Byte-wide data driven from the ATM to PHY layer. TDAT[7] is the MSB.                                                                                                                                                                        |

| TPRTY     | 95    | Input | Transmit Utopia Data Parity: Data parity calculated over TDAT[7:0]. Odd parity is assumed unless the TXPTYP bit (Reg-63, bit 7) is set to even parity                                                                                                             |

| TSOC      | 96    | Input | Transmit Utopia Start of Cell: Assert TSOC HIGH when TDAT[7:0] contains the first byte of an ATM cell. If TSOC is asserted sooner than 53 writes after the previous SOC, an error condition will be generated. This input is optional after the first TSOC pulse. |

| TFCLK     | 84    | Input | Transmit Utopia Clock: Data transfer clock. Data is transferred to the AX on the rising edge of TFCLK when TWRENB is asserted (LOW).                                                                                                                              |

| TWRENB    | 85    | Input | Transmit Utopia Data Enable: Enables the TFCLK input for data transfer to the AX. This signal is active LOW.                                                                                                                                                      |

# Transmit Utopia Interface (continued)

| Name | Pin | I/O    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------|-----|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TCA  | 86  | Output | Transmit Utopia Cell Available: An active state on this signal indicates that the Transmit FIFO can accept at least N more cells (53 octets) of data where N and the active state of the signal (HIGH or LOW) are programmable through the configuration registers (Reg–63H and Reg–01H). In a special case, if Reg–63H bit2–3 is set to 00, Reg–01H, bit 3 is set to 0, and TCALEVEL0 (Reg–63H, bit 1) set to 0. TCA will behave as an active HIGH FULL indicator. |

# Transmit ATM Interface

| Name | Pin | I/O    | Description                                                                                                                                                                                                                                               |

|------|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| XOFF | 50  | Input  | Transmit Idle Cell: A HIGH state on this pin will force the ATM Cell Processor to send an IDLE cell even if there are cells to send in the Transmit FIFO. XOFF is an asynchronous input and has an integrated pull down resistor.                         |

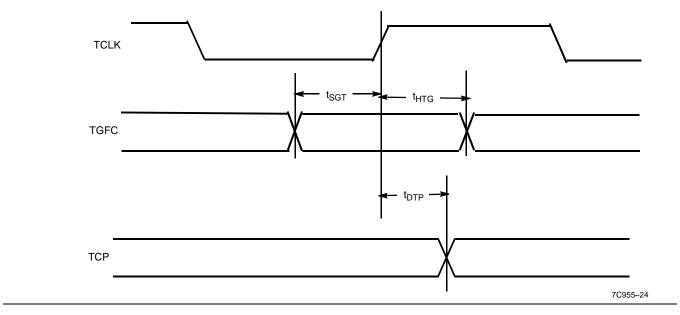

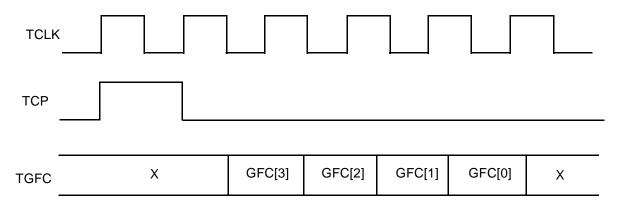

| TGFC | 52  | Input  | Transmit Generic Flow Control: This bit serial input provides the ability to overwrite the four bits of the ATM cell header GFC field. These bits may be optionally written during the four TCLK clock periods following the assertion of the TCP output. |

| TCP  | 51  | Output | Transmit Start Of GFC: This indicates that the first bit of the GFC for the next cell read from the Transmit FIFO is expected on the TGFC pin during the next rising edge of TCLK.                                                                        |

# Transmit Clock Generator

| Name           | Pin   | I/O              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------|-------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

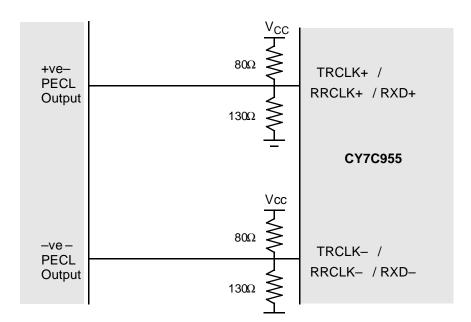

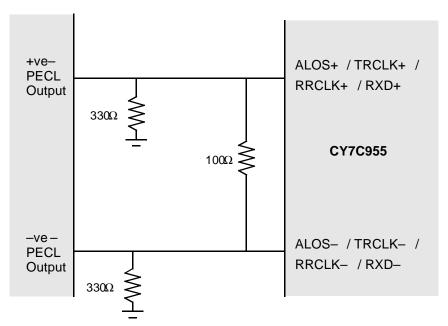

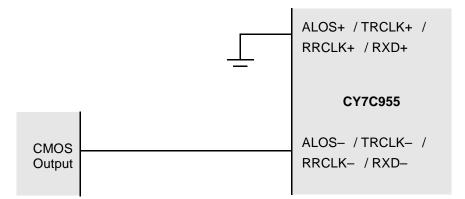

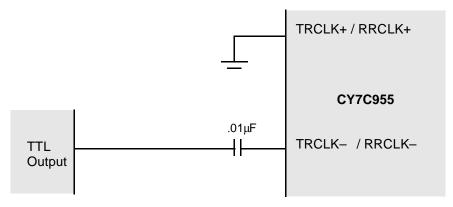

| TRCLK±         | 9–10  | Differential In  | Transmit Input Clock: Accepts either a differential PECL, or a TTL or a CMOS byte rate reference connected to TRCLK– with TRCLK+ grounded for the Transmit frequency multiplier PLL. Optionally, this input can accept also the bit rate reference when TBYP is true (held HIGH). In this mode the Transmit frequency multiplier is bypassed and the bit rate clock is used directly for transmit side clocking.                             |

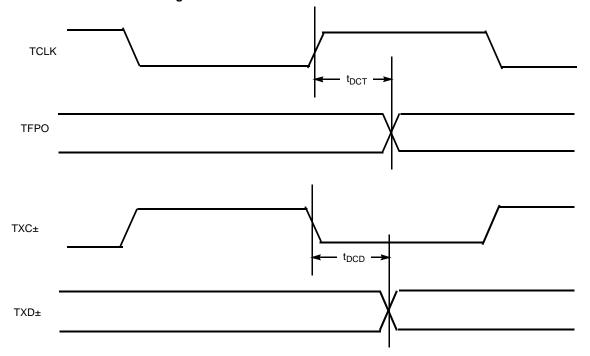

| TXC±           | 13–14 | Differential Out | Transmit Output Clock: Provides clock output for the transmit data. TXD± is updated on the falling edge of this signal. In the default setting, TXC is disabled if RATE0 is HIGH and a 51.84-MHz clock if RATE0 is LOW. XORTXC (Reg–04H, bit 6) can be used to invert the default setting such that TXC is a 155.52-MHz clock if RATE0 is HIGH and is disabled when RATE0 is LOW.                                                            |

| TXD±           | 15–16 | Differential Out | Transmit Data Output: Accepts NRZ encoded output data. This signal is updated on the falling edge of TXC±.                                                                                                                                                                                                                                                                                                                                   |

| ТВҮР           | 2     | Input            | Transmit Clock Bypass: When this input is held HIGH the transmit frequency multiplier is disabled and TRCLK± input is used directly for transmit side clocking. When this input is held LOW the transmit frequency multiplier multiplies the TRCLK± input by 8, 24, or 8/3 (depending on the TREFSEL (Reg–06H, bit 0) setting to provide the internal bit rate clock.                                                                        |

| RATE0<br>RATE1 | 97–98 | Input            | RATE: When the RATE0 input is HIGH the Transmit frequency generator and the Receive clock recovery are selected to operate at the STS–3c/STM–1 rate of 155.52 MHz. When the RATE0 pin is LOW, the Transmit frequency generator and the Receive clock recovery are selected to operate at the STS–1 rate of 51.84 MHz. RATE1 is for factory testing use only and should be tied HIGH. Both RATE0 and RATE1 have integrated pull-up resistors. |

| TCLK           | 54    | Output           | Transmit Byte Reference: Byte rate reference clock derived from the transmit line bit rate.                                                                                                                                                                                                                                                                                                                                                  |

| TFPO           | 53    | Output           | Transmit Frame Reference. This signal is an 8-kHz frame rate reference that goes HIGH during the transmission of the first A1 byte of the SONET/SDH frame. TFPO is updated by the rising edge of TCLK.                                                                                                                                                                                                                                       |

# Receive Clock Recovery

| Name | Pin   | 1/0             | Description                                                                                                                                                                                                                                              |

|------|-------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RXD± | 25–26 | Differential In | Receive Input Data: These line receiver inputs are connected to an internal Receive PLL that recovers the embedded clock and data information. The incoming data rate can be within one of two frequency ranges depending on the state of the RATE0 pin. |

# Receive Clock Recovery (continued)

| Name     | Pin    | I/O              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------|--------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RXDO±    | 22–23  | Differential Out | Receive Output Data: These differential outputs represent the retimed version of the input data stream (RXD±) in normal mode and the buffered version of the input datastream (RXD±) in bypass mode. This output pair can be used as inputs to decision feedback equalizers to correct for baseline wander. RXDO can be turned off to save power by setting RXDOD (Reg-04H, bit 7) to 1.                                                                                            |

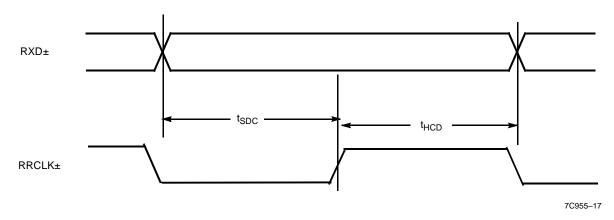

| RRCLK±   | 33–34  | Differential In  | Receive Clock: These inputs are used to clock in the differential data (RXD±) when the Receive clock recovery block is bypassed (RBYP=HIGH). If RBYP is LOW, RRCLK is multiplied by 8, 24, or 8/3 depending on the setting of RREFSEL (Reg–07H, bit 0) and use as a reference for the Receiver PLL. Refer to the section on "Interface Termination and Bias of Schemes" for connection examples to these pins.                                                                      |

| RBYP     | 41     | Input            | Receive Clock Bypass: When this input is HIGH the Receiver clock recovery block is bypassed. In this mode the device does not recover clock and data from the Receive input data stream (RXD $\pm$ ) but instead uses the RRCLK $\pm$ inputs to clock the differential data into the device. When this input is LOW the Receiver clock recovery block recovers the clock and data from the input data stream. In this mode a byte-rate clock is expected on the RRCLK $\pm$ inputs. |

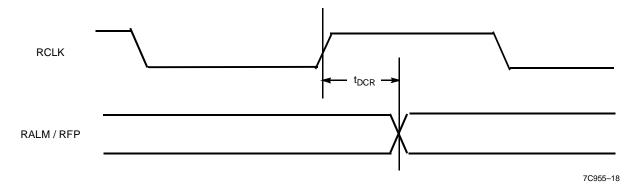

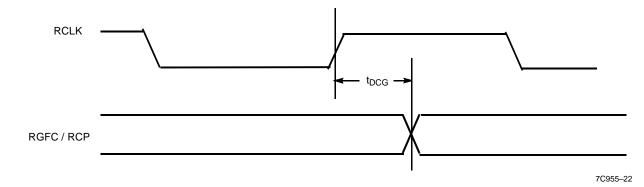

| RCLK     | 57     | Output           | Receive Byte Reference: Provides a byte-rate reference derived from the recovered bit- rate Receive clock. RALM, RCP, and RGFC are aligned with this clock.                                                                                                                                                                                                                                                                                                                         |

| RFP      | 58     | Output           | Receive Frame Reference: This output provides a frame-rate reference clock aligned to the SONET/SDH frame alignment bytes. RFP will pulse HIGH for one RCLK cycle every 125 seconds even at OOF and LOF situations.                                                                                                                                                                                                                                                                 |

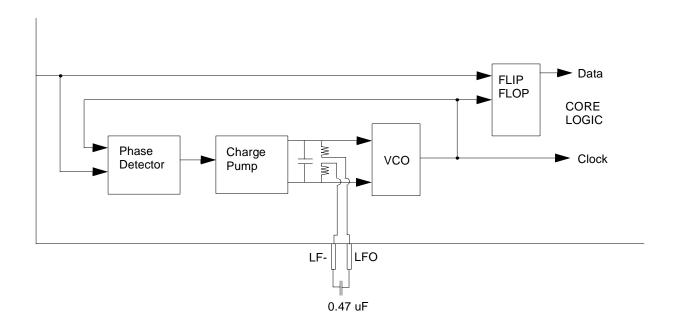

| LF+      | 42     | Input            | NC. This pin is for factory testing only.                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| LF-, LFO | 43, 44 | Input            | These are the PLL filter pins. Connect a 0.47-μF capacitor across LF– and LFO.                                                                                                                                                                                                                                                                                                                                                                                                      |

# Receive ATM Interface

| Name | Pin | I/O    | Description                                                                                                                                                                                                                                                                      |

|------|-----|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

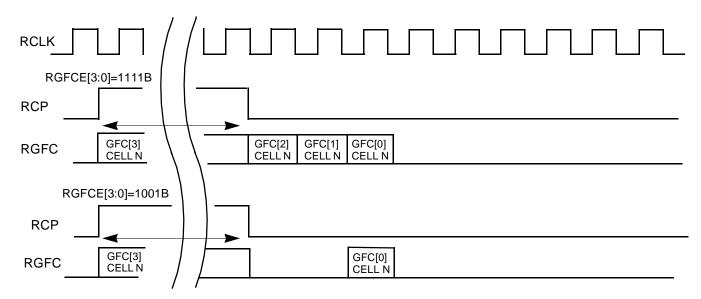

| RGFC | 59  | Output | Receive Generic Flow Control: This output provides the four bits of the current ATM cell header GFC locations at each successive RCLK pulse. The RCP output indicates the first GFC bit location. This output is forced LOW if the ATM Cell Processor has lost cell delineation. |

| RALM | 63  | Output | Receive Interrupt: This active HIGH signal is aligned with the RCLK byte-rate clock and signals the presence of LAIS, PAIS, LOS, LOF, LOP, or LCD.                                                                                                                               |

| RCP  | 60  | Output | Receive Start Of GFC: This output indicates the first bit of the GFC presented on the RGFC output. This output goes HIGH for 1 RCLK cycle 6 byte times after the corresponding cell is written into the Receive FIFO.                                                            |

# Receive Utopia Interface

| Name      | Pin No         | I/O    | Description                                                                                                                                                                                               |

|-----------|----------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

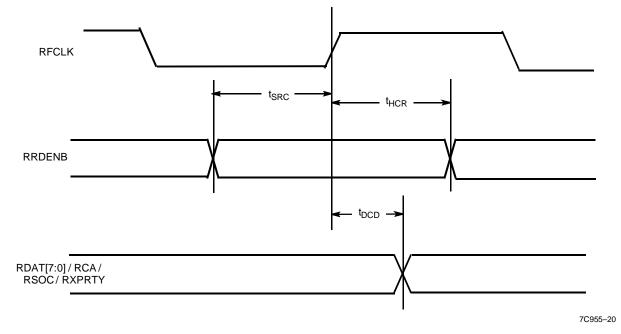

| RDAT[7:0] | 70–71<br>74–79 | Output | Receive Utopia Data: Byte-wide data driven from the PHY to ATM layer. RDAT[7] is the MSB                                                                                                                  |

| RPRTY     | 82             | Output | Receive Utopia Data Parity: Data parity calculated over RDAT[7:0]. Odd parity is assumed unless the TXPRTY bit is set to even parity by Reg–50H, bit 6.                                                   |

| RSOC      | 83             | Output | Receive Utopia Start of Cell: Asserted HIGH when RDAT[7:0] contains the first byte of an ATM cell.                                                                                                        |

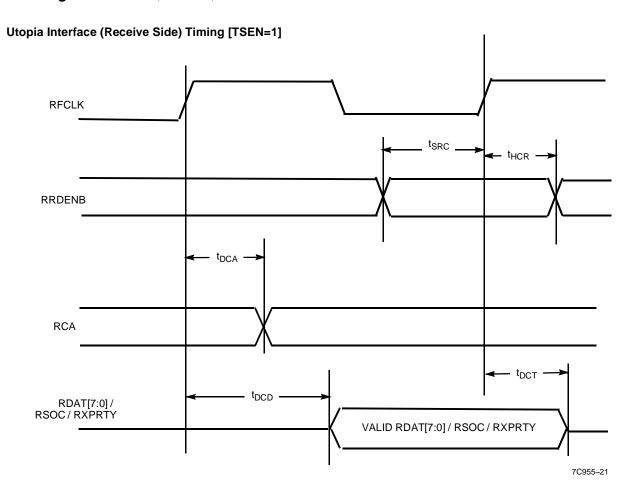

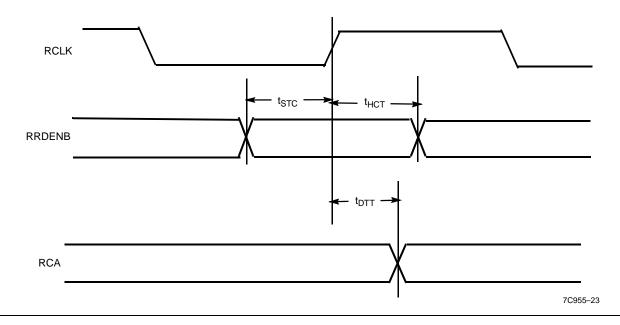

| RFCLK     | 67             | Input  | Receive Utopia Clock: Data transfer clock. Data is transferred from the AX on the rising edge of RFCLK when RRDENB is asserted (LOW).                                                                     |

| RRDENB    | 68             | Input  | Receive Utopia Enable: Enables the RFCLK input for data transfers from the AX.                                                                                                                            |

| RCA       | 69             | Output | Receive Utopia Cell Available: An active signal indicates that the Receive FIFO contains at least 1 or 4 more bytes of data. RCA is controlled by RCAINV (Reg–01H, bit 2) and RCALEVEL0 (Reg–59H, bit 2). |

# Receive Utopia Interface (continued)

| Name | Pin No | I/O   | Description                                                                                                                                                                                                                                                                                                                               |

|------|--------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TSEN | 66     | Input | Receive Output Enable: This output operates in conjunction with the RRDENB output. When TSEN is HIGH and RRDENB is HIGH the Receive UTOPIA data bus (RDAT[7:0], RPRTY, and RSOC) is three-stated. When TSEN is HIGH and RRDENB is LOW the data bus is driven with the requested data. When TSEN is LOW the data bus will not three-state. |

# Controller Interface

| Name   | Pin No             | I/O             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------|--------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D[7:0] | 110–112<br>115–118 | I/O             | Data[7:0]: Bidirectional data bus used to transfer data to and from the internal configuration, status, and error monitoring registers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| A[7:0] | 119–126            | Input           | Address[7:0]: Address bus used to select the internal register for reading or writing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| ALE    | 127                | Input           | Address Latch Enable: When this input is LOW the address is latched from the A[7:0] inputs. When this input is HIGH, the input is transparent. ALE has an integrated pull-up resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| RDB    | 105                | Input           | Read: This active LOW signal is used to read the internal register. The AX drives D[7:0] when RDB and CSB are both LOW.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| WRB    | 104                | Input           | Write: This active LOW signal is used to write the internal registers. Data is latched into the specified address register on the rising edge of WRB when CSB is LOW.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| CSB    | 100                | Input           | Select: This active LOW device select has to be enabled during register accesses.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| INTB   | 108                | Output          | Interrupt: This active LOW open drain output transitions LOW when an unmasked interrupt source is active. This output transitions HIGH when the appropriate register has been read. This interrupt signals the most critical error states of the device including Loss of Pointer, Line Alarm Indication Signal (LAIS), Line Far End Receive Failure (LFERF), Loss of Frame (LOF), Out of Frame (OOF), Loss of Signal (LOS), and many others.                                                                                                                                                                                                                      |

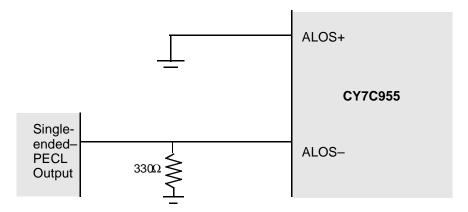

| ALOS±  | 27–28              | Differential In | Carrier Detect: This differential input controls the recovery function of the Receive PLL and can be driven by the carrier detect output from optical modules or from external transition detection circuitry. When this input is at a Logic Low, the input data stream (RXD±) is recovered normally by the Receive Clock Recovery PLL. When this input is at a Logic High, the Receive PLL no longer aligns to RXD±, but instead aligns with the RRCLK * 8 frequency and the LOS alarm register (RDOOLV) will be set. Besides differential PECL, the ALOS– input can be set to accept single ended PECL input if ALOS+ is tied to GND. ALOS- has to be decoupled. |

| RSTB   | 101                | Input           | Reset: This active LOW signal provides a device reset. This line can be pulled LOW to put the CY7C955 into the power-down mode. RSTB has an integrated pull-up resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| VCLK   | 99                 | Input           | Factory test pin. Must be LOW for normal operation. VCLK has an integrated pull-down resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

# Transmit Power

| Name  | Pin No | I/O   | Description                                                                                                                                                                                                                                    |  |

|-------|--------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| TXVDD | 12     | Power | The Transmit Pad Power supplies the TXD± outputs. TXVDD is physically isolated from the other device power pins and should be well regulated +5V DC and noise-free for good performance when driving category 5 unshielded twist pair cabling. |  |

| TAVD1 | 4      | Power | The power pin for the transmit clock synthesizer reference circuitry. TAVD1 should be connected to analog +5V.                                                                                                                                 |  |

| TAVD2 | 6      | Power | The power pin for the transmit clock synthesizer oscillator. TAVD2 should be connected to analog +5V.                                                                                                                                          |  |

| TAVD3 | 8      | Power | The power pin for the transmit PECL inputs. TAVD3 should be connected to analog +5V.                                                                                                                                                           |  |

| TVDDO | 18     | Power | Power for TXC± and RXDO±.                                                                                                                                                                                                                      |  |

# Receive Power

| Name  | Pin No | I/O   | Description                                                                                                                         |

|-------|--------|-------|-------------------------------------------------------------------------------------------------------------------------------------|

| RAVD1 | 30     | Power | The power pin for receive clock and data recovery block reference circuitry. RAVD1 should be connected to analog +5V.               |

| RAVD2 | 36     | Power | The power pin for receive clock and data recovery block active loop filter and oscillator. RAVD2 should be connected to analog +5V. |

| RAVD3 | 24     | Power | The power pin for the RXD± and ALOS± PECL inputs. RAVD3 should be connected to analog +5V.                                          |

| RAVD4 | 32     | Power | The power pin for the RRCLK± PECL inputs. RAVD4 should be connected to analog +5V.                                                  |

# Core Power

| Name             | Pin No             | I/O   | Description                                                                                                     |

|------------------|--------------------|-------|-----------------------------------------------------------------------------------------------------------------|

| V <sub>DDI</sub> | 20, 61,<br>107     | Power | The core power pins should be connected to a well decoupled +5V DC in common with $V_{\mbox{\scriptsize DDO}}.$ |

| $V_{DDO}$        | 55, 73,<br>81, 114 | Power | The pad ring power pins should be connected to a well decoupled +5V DC in common with $V_{\rm DDI}$ .           |

# Ground

| Name                   | Pin No                                                  | I/O    | Description                                                                                                                                                                                                                                                 |  |

|------------------------|---------------------------------------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| TAVS1                  | 5                                                       | Ground | The ground pin for the transmit clock synthesizer reference circuitry. TAVS1 should be connected to analog GND.                                                                                                                                             |  |

| TAVS2                  | 7                                                       | Ground | The ground pin for the transmit clock synthesizer oscillator. TAVS2 should be connected to analog GND.                                                                                                                                                      |  |

| TAVS3                  | 11                                                      | Ground | The ground pin for the transmit PECL inputs. TAVS3 should be connected to analog GND.                                                                                                                                                                       |  |

| TXV <sub>SS</sub>      | 17                                                      | Ground | The transmit pad ground is the return path for the TXC± and TXD± outputs. TXV <sub>SS</sub> is physically isolated from the other device ground pins and should be noise-free for good performance when driving category 5 unshielded twisted pair cabling. |  |

| RAVS1                  | 31                                                      | Ground | The ground pin for receive clock and data recovery block reference circuitry. RAVS1 should be connected to analog GND.                                                                                                                                      |  |

| RAVS2                  | 37                                                      | Ground | The ground pin for receive clock and data recovery block active loop filter and oscillator. RAVS2 should be connected to analog GND.                                                                                                                        |  |

| RAVS3                  | 29                                                      | Ground | The ground pin for the RRCLK± PECL inputs. RAVS3 should be connected to analog GND.                                                                                                                                                                         |  |

| RAVS4                  | 35                                                      | Ground | The ground pin for the RSD± and ALOS± PECL inputs. RAVS4 should be connected to analog GND.                                                                                                                                                                 |  |

| RVSSO                  | 21                                                      | Ground | This pin is grounded for TXC± and RXDO±.                                                                                                                                                                                                                    |  |

| V <sub>SSI</sub>       | 19, 62,<br>106,48                                       | Ground | The core ground (V <sub>SSI</sub> ) pins should be connected to GND in common with V <sub>SSO</sub> .                                                                                                                                                       |  |

| V <sub>SSO</sub>       | 56, 72,<br>80, 113,<br>49                               | Ground | The pad ring ground ( $V_{SSO}$ ) pins should be connected to GND in common with $V_{SSI}$ .                                                                                                                                                                |  |

| V <sub>SS</sub>        | 1, 38,<br>39, 46,<br>47, 64,<br>65, 102,<br>103,<br>128 | Ground | These pins must be connected to GND for correct operation.                                                                                                                                                                                                  |  |

| ATP1,<br>ATP2,<br>ATP3 | 40, 3,<br>46                                            | I/O    | These Analog Test Points (ATPx) are for factory testing use only. These pins have to be tied to GND for correct chip operation.                                                                                                                             |  |

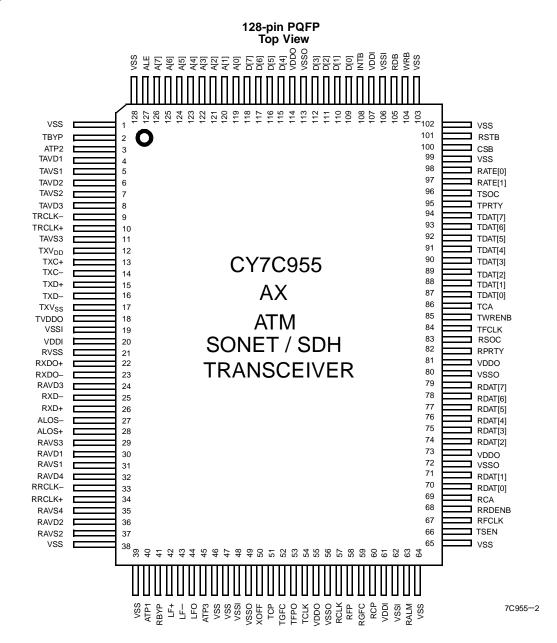

# **Pin Configuration**

## **Description**

### **Transmit Section**

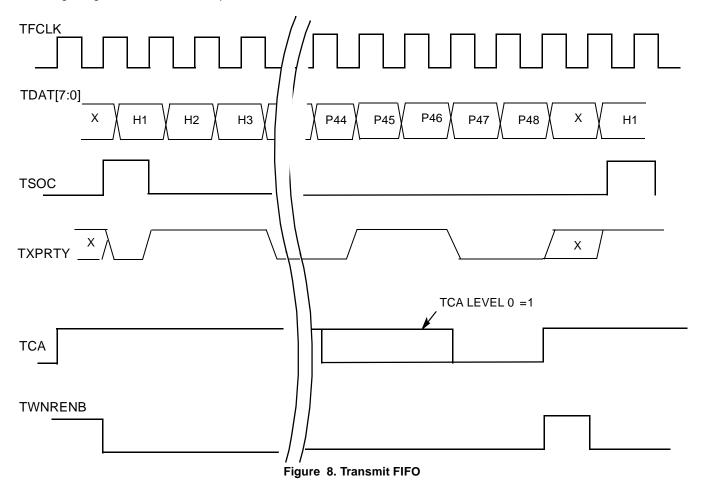

#### Transmit Utopia Interface (TUI)

The transmit interface provides a simple access from the external environment to the ATM Transceiver. The operation of this interface is compliant with the Utopia interface specification. The interface provides a 9-bit by 4-cell FIFO to decouple the system interface from the ATM physical layer timing. 9-bit words are clocked into the device through a clocked FIFO system interface. These 9 bits include an 8-bit data word along with a Start Of Cell (SOC) indication. The interface also provides full and almost full indications (TCA). Maximum clock rate for this interface is 33 MHz.

#### Transmit ATM Cell Processor (TACP)

The ATM cell processor provides HEC generation, idle/unassigned cell header modification, payload scrambling, and GFC insertion.

#### HEC Generator

The Header Error Check (HEC) code is contained in the last byte of the ATM cell header and is capable of single error correction and multiple error detection. When optionally generated, the Transmit ATM Cell Processor calculates a CRC–8 over the first four bytes of the ATM cell header using the polynomial  $x^8 + x^2 + x + 1$ . The coset  $x^6 + x^4 + x^2 + 1$  is added (modulo 2) to the residue of this function. The HEC is calculated in accordance with ANSI T1.624–1993 and CCITT Recommendation I.432. This HEC sequence is placed in the 5th byte of the ATM cell header.

## Idle/Unassigned Cell Header Modification

Idle (Unassigned) cells are sent by the ATM cell processor whenever a complete cell is not contained within the Transmit FIFO. This transforms the non-continuous cell input stream into a continuous stream of assigned and unassigned cells.

The ATM cell processor provides the ability to overwrite the Generic Flow Control (GFC), the Payload Type Indication (PTI), and the Cell Loss Priority (CLP) fields of Idle (Unassigned) cells with the values contained in the corresponding configuration registers. VPI and VCI are set to zero in Idle (Unassigned) cells.

#### Payload Scrambler

The 48 bytes of the ATM payload are scrambled using a parallel implementation of the polynomial  $x^{43}$  + 1 as described in CCITT Recommendation I.432. The scrambler can be optionally deselected.

#### GFC Insertion

The transmitted GFC field of an ATM cell can be derived from different sources. For assigned cells, the default is from pins TDAT[7:0]. For Idle (Unassigned) cells, the default is from GFC[3:0] (Reg–61H, bit 7–bit 4). However, if any bit of TGFCE[3:0] (Reg–67H, bit 7–bit4) is set, the corresponding transmitted GFC location will instead be taken from the serial TGFC (pin 52) input following the functional timing specifications described in the section on Transmit GFC Serial Link Interface.

#### Transmit SONET Path Overhead Processor (TPOP)

The SONET path overhead processor provides payload pointer alignment (H1, H2), path overhead insertion, and insertion of the Synchronous Payload Envelope (SPE). ATM cells (both assigned and unassigned) are inserted into the SPE for transmission in the SONET frame

#### SONET Overhead Insertion

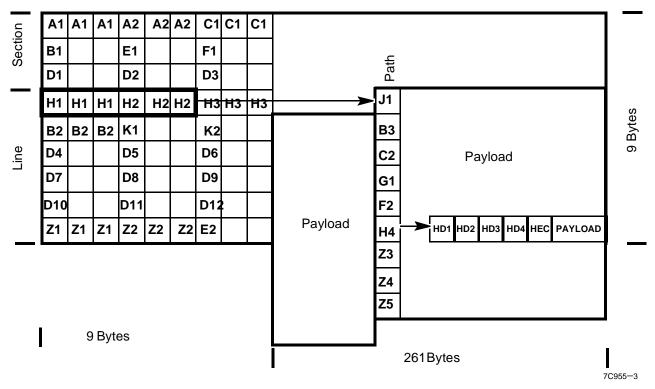

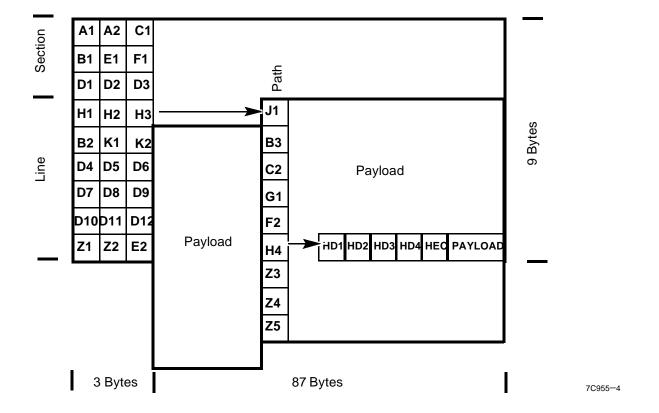

The SONET/SDH STS-3c/STM-1 frame structure is shown in Figure 1 and the SONET STS-1 frame structure is shown in Figure 2. The SONET frame occurs once every 125  $\mu$ s and is transmitted beginning with the A1 bytes, followed by the A2 bytes, C1 bytes, 261 bytes (87 bytes for STS-1) of the Synchronous Payload Envelope (SPE), B1 bytes, etc., until the entire frame is transmitted.

The TPOP generates the H1 and H2 bytes that indicate the beginning of the SPE and the H4 byte that indicates the ATM cell offset within the SPE. The default initial value for H1 and H2 pointer is 522, meaning that the first byte of the SPE (J1) corresponding to a frame actually starts after the C1 byte of the next frame.

In the default case described above, a 6h is present in the New Data Flag (NDF) portion of the first H1 (bits 0–4), a 2h is present in bits 5–7 and a 0Ah is present in the first H2 byte. The remaining H1 bytes for STS–3c/STM–1 are set to 93h and the remaining H2 bytes are set to FFh which is the concatenation indication for the J1 pointer. The Pointer Action byte, H3, is set to 00h. During Path AIS all of the H1 and H2 bits are set to 1.

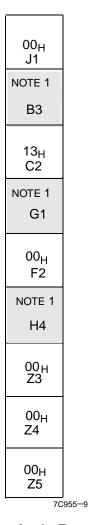

The STS path trace J1 is set to all zeros. The path BIP–8 (B3) byte provides path error monitoring. This function calculates the bit-interleaved parity-8 code using even parity over the previous SPE before scrambling and is inserted into the current B3 byte before scrambling. Bit-interleaved parity-8 forces the number of 1s in the xth bit of every byte in the previous SPE plus the xth bit of the B3 byte in the current SPE to be an even number.

The path signal level indicator, C2, defaults to 13h.

The path status, G1, has several functions. Bits 1 through 4 are used to indicate Far End Block Errors (FEBE) derived by counting the number of BIP–8 errors occurred in the last frame received. Valid codes are 0 through 8. If more than 8 errors have accumulated since the last, frame the maximum value is sent with the current frame, the FEBE counter is decremented by 8, and the remaining errors are sent with the next frame. FEBE may be inserted through register control for diagnostic purposes. Bits 1 through 4 can also be used to transmit Far End Receive Failures by setting these bits to 9 (1001). This error indicates to the far end that cell delineation has been lost. Bit 5 can be used to generate a yellow alarm condition. The default value for this bit is 0 (no alarm).

The multi-frame indicator, H4, is used to indicate the first ATM cell and may take on values of 00 to 34h.

The remaining bytes, F2, Z3, Z4, and Z5, are not used by the SONET path processing and are set to 00h upon transmission. When operating in STS-1 mode, SPE columns 30 and 59 can be configured as fixed stuff columns.

Figure 1. STS-3c/STM-1 Framing Format

Figure 2. STS-1 Framing Format

### Transmit SONET Line Overhead Processor (TLOP)

The Transmit SONET line overhead processor (TLOP) provides BIP-8/24 generation and line level alarms.

The BIP–8/24 code is calculated as if the STS–3c frame was composed of three STS–1s. The first B2 byte is calculated over the first STS–1 frame, the second B2 byte over the second STS–1 frame and the third B2 byte over the third STS–1 frame. Each B2 bit is calculated over the line and SPE portions of the previous frame before scrambling using even parity and inserted into the current frame before scrambling. For STS–1 RATE, a BIP–8 is calculated over the entire SPE and line overhead and placed in B2.

The Line Alarm Indication Signal (LAIS), is asserted by changing all bits of the SONET frame into 1 before scrambling. LAIS generation is controlled by a register setting (Reg–14H, bit 0).

The Line Far End Receive Failure (LFERF), also called Line RDI, is indicated by placing a 110 pattern in bits 6,7, and 8 of the first K2 byte. LFERF can be asserted under register (Reg–20H, bit 0) control.

The Line Far End Block Errors (LFEBE) are located in the third Z2 byte and indicate the number of B2 errors in the previous frame interval. Legal values for this byte are 00h through 18h.

All bytes of the line data communication channel (D4–D12) and all other unused bytes are encoded to 00h.

#### Transmit SONET Section Overhead Processor (TSOP)

The Transmit SONET Line Overhead Processor (TSOP) provides A1,A2 framing pattern generation, section BIP–8 (B1) insertion, section level alarm insertion, and frame scrambling.

The A1 and A2 bytes provide a framing pattern for frame alignment. All A1 bytes are coded to F6h and all A2 bytes are coded to 28h. These bytes are not scrambled upon transmission.

The STS-1 identification bytes, C1, are used for framing and de-interleaving purposes and are coded the order in their appearance in the STS-3c frame. The first C1 byte is coded to 01h, the second to 02h, and the third to 03h.

The section BIP–8 (B1) is the byte-interleaved parity-8 calculated over all bytes of the previous frame after scrambling and inserted into the current frame before scrambling.

The bytes of the section data communication channel, D1–D3 and the remaining unused bytes are set to 00h.

The frame is scrambled prior to transmission with the generating polynomial  $x^7 + x^6 + 1$ . The A1, A2, and C1 bytes are not scrambled. The scrambler runs continuously through the frame and resets at the beginning of the next transmission frame. The scrambler may be optionally disabled.

#### **Transmit Clock Generator (TCG)**

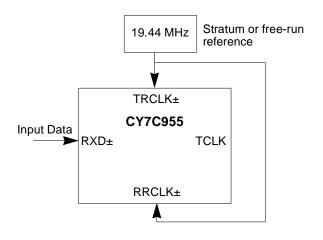

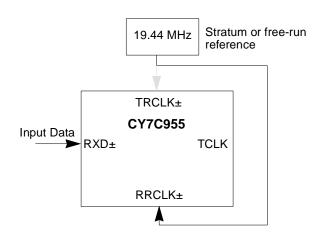

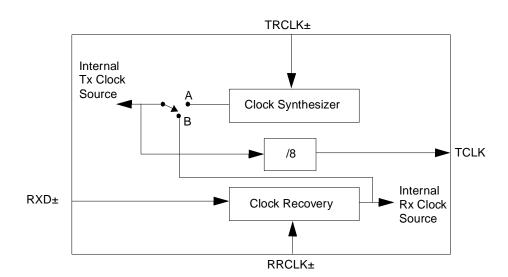

The TCG accepts a byte-rate transmit clock from TRCLK that operates at either 19.44 MHz for STS-3c/STM-1 RATE or at 6.48 MHz for STS-1 RATE. The Transmit PLL multiplies this byte-rate reference by eight to produce the bit-rate clock used by the parallel-to-serial converter. Optionally a bit-rate source can be taken from an external source (TBYP = 1) or from the Receive Clock Recovery block when in loop-time mode (LOOPT = 1). In loop-time mode the recovered clock is used to provide timing to the transmitter.

#### Parallel to Serial Converter (PSC)

The PSC converts the parallel data from the TSOP to serial data. The bit rate clock is derived from the Transmit Clock Generator. The serialized data and aligned output clock are presented to the Transmit Output Multiplexer.

#### Transmit Output Multiplexer (TOM)

The TOM selects between the serialized output data stream and associated clock provided by the PSC and the recovered data and clock from the Receive Clock Recovery block for transmission based on the state of the local loop back enable (LLE) register (Reg–05H, bit 2). When LLE = 1 the recovered data and recovered clock is selected for output on the transmit data lines (TXD±) and the transmit clock lines (TXC±). The output signal is 100K compatible differential Positive-referenced ECL (PECL) signal capable of driving any copper or fiber based media with impedances as LOW as  $50\Omega$ .

#### **Receive Section**

#### Receive Clock Recovery (RCR)

The RCR provides clock and data recovery from an incoming differential PECL data stream. Clock and data are recovered from the incoming differential PECL data stream without the need for external buffering and AC-coupling. The built-in line receiver inputs have a wide common-mode range (2.5-5V) and the ability to receive signals with as little as 200 mV differential voltage. They are compatible with all PECL signals. They are compatible with all PECL signals driven by optical modules or twisted-pair equalizers. The Receive PLL uses the RRCLK as a byte-rate reference. This input is multiplied by 8 and is used to improve PLL lock time and to provide a center frequency for operation in the absence of input data stream transitions. The receiver can recover clock and data in two different frequency ranges depending on the state of the RATE0 pin. To insure accurate data and clock recovery, the received data stream must be within 1000 ppm of RRCLK \* 8 (The PLL will declare Out Of Lock if the data rate is different from REFCLK x 8 by more than 2000 ppm. The PLL will remain Out Of Lock until the data rate pulls back to within 700 ppm of REFCLK x 8 frequency). The standards, however, specify that the RRCLK\*8 frequency accuracy be within 20-100 ppm. The wider frequency tolerance range of the CY7C955 is an advantage that allows for higher frequency tolerance in bench testing set-

A Loss of Signal (ROOLV = 1) is declared when no transitions have been detected on the incoming data stream for more than 512 bit-times. LOS is cleared when two valid framing patterns (A1, A2) have been found and the intervening data does not contain a period that violates the minimum transitions limit.

#### Serial to Parallel Conversion (SPC)

The SPC converts bit serial data to byte serial data from either the recovered received data or the transmit data from the PSC depending on the state of the DLE register (Reg–05H, bit 1). When DLE =1 transmit data is used for serial to parallel conversion. The SPC also provides SONET framing by scanning the incoming data for the SONET framing pattern A1, A2. For STS–1 RATE the framer looks for the pattern F628h and for STS–3 RATE the framer looks for the pattern F6F6F6282828h. Out of Frame (OOF) is declared when four consecutive frames contain a framing error. OOF clears when two frames contain valid framing characters. Loss of Frame

(LOF) is declared when the OOF condition fails to clear within 3 ms. LOF clears after 3 ms of frames with valid framing characters.

### Receive SONET Section Overhead Processor (RSOP)

The RSOP provides descrambling, SONET section alarm indication, and error monitoring.

The data is descrambled using the generating polynomial  $1 + x^6 + x^7$ . The A1, A2, and C1 bytes are not descrambled. The scrambling process may be disabled under register control.

The BIP–8 value calculated over the previous scrambled frame is compared with the B1 byte of the current frame section overhead after descrambling. If the two values do not match, the B1PAR output is taken HIGH. Up to 64,000 errors can be detected per second (8000 frames/second \* 8 bit-errors (max)/frame). Errors are recorded in a 16-bit saturating counter that can be read through the controller interface.

#### Receive SONET Line Overhead Processor (RLOP)

The RLOP provides SONET line alarm indications and error monitoring.

A Line Alarm Indication Signal (LAIS) is asserted when a 111 pattern is detected for five consecutive frames in bits 6,7, and 8 of the first K2 byte of the Automatic Protection Switching channel. LAIS is removed when anything other than a 111 pattern is received for five consecutive frames.

A Line Far End Receive Failure (LFERF) or Line RDI is indicated with a 110 pattern is detected for five consecutive frames in bits 6,7, and 8 of the first K2 byte. LFERF is removed when anything other than a 110 pattern is received for five consecutive frames.

The BIP–24 (BIP–8 for STS–1 RATE) value calculated over the previous line overhead and SPE is compared with the B2 bytes of current frame. Up to 192,000 errors can be detected per second (3 channels/frame \* 8 errors (max)/channel \* 8000 frames/second). Errors are recorded in a 20-bit saturating counter that can be read through the controller interface.

Far End Block Errors (FEBE) are detected by examining the value in the third Z2 byte. This value (0–18h) is added to the count in an 18-bit saturating counter that can be read through the controller interface.

#### Receive SONET Path Overhead Processor (RPOP)

The RPOP provides pointer interpretation, SPE extraction, SONET path alarm indications, and error monitoring.

The payload location is determined by examining the values in the H1 and H2 bytes of the line overhead which indicate the J1 byte of the SPE. The RPOP can process a J1 byte located anywhere in the SPE. Loss of Pointer (LOP) is set when a valid pointer value has not been found within eight consecutive frames. This register bit is cleared when a valid pointer is found for three consecutive frames. Path Alarm Indication Signal (PAIS) (Reg30H, bit 3) is set when the H1 and H2 bytes are set to all ones for 3 consecutive frames. This register bit is cleared when a valid pointer is found for three consecutive frames. PAIS does not cause LOP to be set. The SPE location

is provided to the Receive ATM Cell Processor for cell extraction

The BIP–8 value calculated over the previous SPE is compared with the B3 byte of the current path overhead. Up to 65,535 errors can be detected per second. Errors are recorded in a 16-bit saturating counter that can be read through the controller interface.

Path Far End Block Errors (PFEBE) are detected by examining the value in bits 1 through 4 of G1. This value (0–8h) is added to the count in a 16-bit saturating counter that can be read through the controller interface.

Path Far End Receive Failures (PFERF) are detected by examining the value in bits 1 through 4 of G1. If this value is 9h for two consecutive frames, PFERF is set. This register bit is cleared when anything other than 9h appears for two consecutive frames.

Path Remote Defect Indication (Path RDI) is detected by examining bit 5 of G1. If this value is 1h for 5 consecutive frames, PYEL is set. This register bit is cleared when a 0 appears in bit 5 for 5 consecutive frames.

## Receive ATM Cell Processor (RACP)

The RACP block provides cell delineation, HEC checking and correcting, cell filtering for idle/unassigned cells, cell payload descrambling, status indications, and error monitoring.

Cell delineation is performed by comparing the HEC sequence calculated over the first four bytes of the SPE to the fifth byte. If these values match, cell boundary has been determined. If not, the calculation advances one byte further into the payload (bytes 2–5) and the check is performed again. The HEC sequence is a CRC–8 calculated over the first 4 octets of the ATM cell header using the polynomial  $x^8 + x^2 + x + 1$ . The coset  $x^6 + x^4 + x^2 + 1$  is added (modulo 2) to the residue before comparison with the received sequence. This is the HUNT state of the cell delineation process. When a valid match has occurred the process enters the PRESYNC state. When 7 consecutive matches occur the process enters the SYNC state. If 6 consecutive incorrect HEC matches are detected the process moves back to the HUNT state. The average time for cell delineation is  $93\mu s$  for STS–1 and  $31\mu s$  for STS–3C.

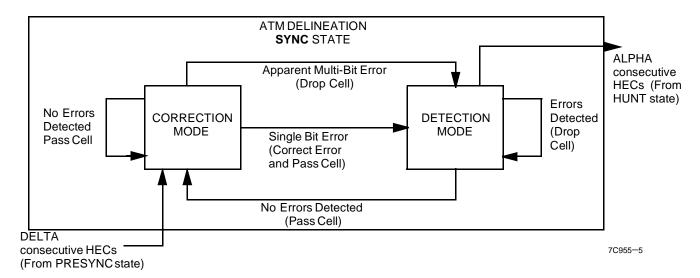

The HEC sequence is used not only to check for cell alignment, but also to insure that integrity of the ATM header. The HEC is used to correct single bit errors and to detect multiple bit errors. This feature can be disabled. The register file contains two saturating 8-bit counters for HEC errors; one for cells with single bit errors and another for multiple-bit errors. Cells with multiple bit errors are optionally discarded. *Figure 3* shows the state diagram for HEC.

The RACP optionally discards Idle/Unassigned cells. These cells contain a VPI/VCI address of 0h. Also, a Header Mask and Header Match register are provided to allow cells with a particular header characteristic in GFC, PTI and CLP to be filtered.

The payload of valid cells are descrambled using the polynomial  $x^{43}$  +1. The cell headers are not descrambled since they

were not scrambled upon transmission. The descrambling feature can be disabled.

Figure 3. HEC Verification State Diagram

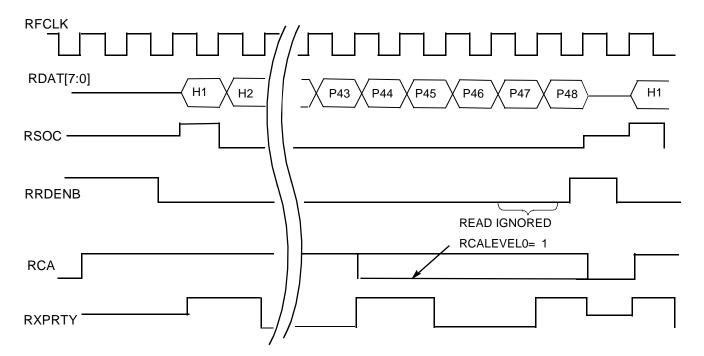

#### Receive Utopia Interface (RUI)

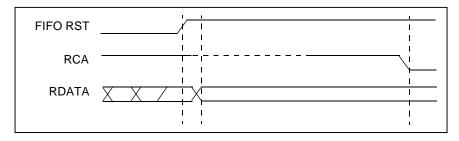

The RUI provides a simple access from the external environment to the ATM Transceiver. The operation of this interface is compliant with the Utopia interface specification that is being standardized by the ATM Forum. The interface provides a 10 bit by 4 cell FIFO to decouple the system interface from the ATM physical layer timing. Ten bit words are clocked out from the device through a clocked FIFO style interface. These 10 bits include an 8-bit data word along with an parity bit (RXPRTY) and a Start Of Cell (SOC) indication. The interface also provides a cell available (RCA) indication and a read enable (RRDENB) control. RCA allows the FIFO to indicate empty and almost empty conditions and RRDENB allows the downstream circuit to pause the reading process in case the downstream cannot accept anymore read. If the Receive FIFO overflows, FIFO reset will occur and up to 4 cells may be lost because of the operation.

## **Controller Interface (CI)**

The CI interface provides external access to the internal register file, device resetting and external input for the carrier detect signal. The ALOS input allows an external carrier detect from an optical module to cause an interrupt to the controller. The INTB and RALM pins can be configured to interrupt the external controller whenever any of several different error conditions occur. RALM signals the most important error conditions such as LOS, LOF, line AIS, path AIS, LCD, and LOP. INTB may indicate all possible errors depending on the state of the mask registers. INTB provides notification of the individual processing block that generated the error condition. The error register contained in each block will determine the exact cause of the interrupt.

Figure 4. SONET/SDH and ATM Interface

| F6 <sub>H</sub><br>A1  | F6 <sub>H</sub><br>A1 | F6 <sub>H</sub><br>A1 | 28 <sub>H</sub><br>A2  | 28 <sub>H</sub><br>A2 | 28 <sub>H</sub><br>A2 | 01 <sub>H</sub><br>C1  | 02 <sub>H</sub><br>C1 | 03 <sub>H</sub><br>C1 |

|------------------------|-----------------------|-----------------------|------------------------|-----------------------|-----------------------|------------------------|-----------------------|-----------------------|

| NOTE 1<br>B1           | 00 <sub>H</sub>       | 00 <sub>H</sub>       | 00 <sub>H</sub><br>E1  | 00 <sub>H</sub>       | 00 <sub>H</sub>       | 00 <sub>H</sub><br>F1  | 00 <sub>H</sub>       | 00 <sub>H</sub>       |

| 00 <sub>Н</sub><br>D1  | 00 <sub>H</sub>       | 00 <sub>H</sub>       | 00 <sub>H</sub><br>D2  | 00 <sub>H</sub>       | 00 <sub>H</sub>       | 00 <sub>H</sub><br>D3  | 00 <sub>H</sub>       | 00 <sub>H</sub>       |

| 62 <sub>H</sub><br>H1  | 93 <sub>H</sub><br>H1 | 93 <sub>H</sub><br>H1 | 0A <sub>H</sub><br>H2  | FF <sub>H</sub><br>H2 | FF <sub>H</sub><br>H2 | 00 <sub>Н</sub><br>Н3  | 00 <sub>Н</sub><br>Н3 | 00 <sub>Н</sub><br>Н3 |

| [NOTE 1]<br>B2         | [NOTE 1]<br>B2        | [NOTE 1]<br>B2        | 00 <sub>H</sub><br>K1  | 00 <sub>H</sub>       | 00 <sub>H</sub>       | 00 <sub>H</sub><br>K2  | 00 <sub>H</sub>       | 00 <sub>H</sub>       |

| 00 <sub>H</sub><br>D4  | 00 <sub>H</sub>       | 00 <sub>H</sub>       | 00 <sub>H</sub><br>D5  | 00 <sub>H</sub>       | 00 <sub>H</sub>       | 00 <sub>Н</sub><br>D6  | 00 <sub>H</sub>       | 00 <sub>H</sub>       |

| 00 <sub>H</sub><br>D7  | 00 <sub>H</sub>       | 00 <sub>H</sub>       | 00 <sub>Н</sub><br>D8  | 00 <sub>H</sub>       | 00 <sub>H</sub>       | 00 <sub>H</sub><br>D9  | 00 <sub>H</sub>       | 00 <sub>H</sub>       |

| 00 <sub>H</sub><br>D10 | 00 <sub>H</sub>       | 00 <sub>H</sub>       | 00 <sub>H</sub><br>D11 | 00 <sub>H</sub>       | 00 <sub>H</sub>       | 00 <sub>H</sub><br>D12 | 00 <sub>H</sub>       | 00 <sub>H</sub>       |

| 00 <sub>H</sub><br>Z1  | 00 <sub>H</sub><br>Z1 | 00 <sub>H</sub><br>Z1 | 00 <sub>H</sub><br>Z2  | 00 <sub>H</sub><br>Z2 | [NOTE 1]              | 00 <sub>H</sub><br>E2  | 00 <sub>H</sub>       | 00 <sub>H</sub>       |

7C955-7

### Note:

1. B1, B2, Z2, G1, H4, and B3 are variables.

Figure 5. Default Values for the Transmitted Section and Line STS-3C/STM-1 Overhead

| F6 <sub>H</sub>       | F6 <sub>H</sub><br>A2 | 00 <sub>Н</sub><br>С1 |

|-----------------------|-----------------------|-----------------------|

| NOTE 1                | 00 <sub>H</sub>       | 00 <sub>H</sub>       |

| B1                    | E1                    | F1                    |

| 00 <sub>H</sub>       | 00 <sub>H</sub>       | 00 <sub>Н</sub>       |

| D1                    | D2                    | D3                    |

| 62 <sub>H</sub>       | 0A <sub>H</sub>       | 00 <sub>Н</sub>       |

| H1                    | H2                    | Н3                    |

| NOTE 1                | 00 <sub>H</sub>       | 00 <sub>H</sub>       |

| B2                    | K1                    | K2                    |

| 00 <sub>H</sub>       | 00 <sub>H</sub>       | 00 <sub>Н</sub>       |

| D4                    | D5                    | D6                    |

| 00 <sub>H</sub>       | 00 <sub>H</sub>       | 00 <sub>H</sub>       |

| D7                    | D8                    | D9                    |

| 00 <sub>H</sub>       | 00 <sub>H</sub>       | 00 <sub>H</sub>       |

| D10                   | D11                   | D12                   |

| 00 <sub>H</sub><br>Z1 | NOTE 1                | 00 <sub>H</sub><br>E2 |

7C955-8

Figure 6. Default Values for the Transmitted Section and Line STS-1 Overhead

Figure 7. Default Values for the Transmitted Path Overhead

# **Loopback Operation**

# **SONET Overhead Description**

| Signal Values | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1, A2        | The frame alignment bytes mark the beginning of a SONET frame. They are transmitted every 125 $\mu$ s in both OC–1 and OC3c speeds. Transmit Side: In OC–1, A1(F6 <sub>H</sub> ) and A2 (28 <sub>H</sub> ) are inserted into the transmitted stream at the beginning of every frame. These bytes are not scrambled by the frame synchronous SONET scrambler. Receive Side: The receiver will search for and frame onto the incoming A1, A2 bytes.                                                                                                                              |

| C1            | This is the identification byte for the STS data stream. Transmit Side: In OC–1, C1 is transmitted as OH. In OC–3c, the sequence C1, C1, C1 of every frame is transmitted as 01 <sub>H</sub> , 02 <sub>H</sub> , 03 <sub>H</sub> . These bytes are not scrambled by the frame-synchronous SONET scrambler. Receive side: The receiver will ignore C1.                                                                                                                                                                                                                          |

| B1            | This is the section bit interleave parity byte. Transmit Side: B1 is calculated using the BIP–8 algorithm described in I.432. It is inserted into the SONET data stream before the frame synchronous SONET scrambler. Receive Side: Received B1 error events are accumulated in the SBE [15:0] (Reg–12H and Reg–13H).                                                                                                                                                                                                                                                          |

| H1, H2        | These are the pointer value byte. These bytes are used to locate the beginning of the Synchronous Payload Envelope (SPE) in the SONET/SDH frame. Transmit side: H1, H2 contains the normal new data flag (0110) together with 522 (decimal) as the fixed pointer value field. The concatenation indication byte is also inserted (H1* = 93, H2* = FF). Receive Side: H1 and H2 are used to locate the beginning of the SPE. If a valid pointer cannot be found, CY7C955 will indicate a Loss of Pointer State. Path AIS is detected by an all-ones pattern in H1 and H2 bytes. |

| H3            | This is the pointer action byte. Transmit Side: H3 will be all zeroes. Receive Side: Synchronous Payload Data will be stuffed in the H3 byte if a negative stuff event occurs. This byte is ignored otherwise.                                                                                                                                                                                                                                                                                                                                                                 |

| B2            | This is the line bit interleaved parity bytes, it is used to monitor line errors. Transmit Side: B2 is calculated over all bits of the line overhead and the SPE capacity of the previous frame before the frame is being scrambled. The B2 byte itself is then placed in the current frame before scramble.                                                                                                                                                                                                                                                                   |

| K2            | This is the identity line layer maintenance signal. Transmit Side: Bits 6, 7, and 8 of this byte are '110' before scrambling when Line Remote Defect Indication is true. The whole of K2 is an all-one pattern before scrambling if Line AIS is inserted. Receive Side: Bits 6, 7, and 8 of the K2 byte are being examined to determine the presence of AIS, and RDI signals. Access to APs registers will be available in future revisions.                                                                                                                                   |

| Z2            | This is the growth byte. It is used to provide far end block error function useful for remote performance monitoring. Transmit Side: The number of B2 errors detected in the last frame is inserted. Z2 is a number from 0–24 indicating 0–24 errors. Receive Side: A legal (0–24) Z2 number will be added to the line FEBE counter.                                                                                                                                                                                                                                           |

| В3            | This is the interleaved parity byte. Transmit Side: B3 is calculated over all bits of the SPE of the previous frame before scrambling and is placed in the current frame before scrambling. This provides path error monitoring capability for the link. Receive Side: The value in B3 is accumulated in a register.                                                                                                                                                                                                                                                           |

| C2            | This is the path signal label byte for indicating the contents of the SONET payload. Transmit Side: It's fixed value is 13H. This indicates the payload is ATM. Receive Side: The receive side expects C2 to be 13H. If the data is not 13H for 3 consecutive frames, an interrupt (if enabled) will be generated.                                                                                                                                                                                                                                                             |

| G1            | This is the path status byte. Transmit Side: Path remote defect Indication (Path RDI) together with the number of B3 errors in the last frame are inserted into G1 before scrambling for transmission. G1 is a number from 0–8, indicating 0–8 errors. Receive side: A legal G1 value (0–8) will be accumulated in the FEBE counter. Path remote defect indication is also detected through this byte.                                                                                                                                                                         |

| H4            | This is the cell offset byte. Transmit Side: This byte indicates the offset in bytes between the H4 byte and the first cell byte after H4. Receive Side: H4 byte is ignored.                                                                                                                                                                                                                                                                                                                                                                                                   |

# CY7C955 Register Map

| Address | Register                                                             |

|---------|----------------------------------------------------------------------|

| Reg-00H | Master Reset/Type/Identify Register                                  |

| Reg-01H | Master Configuration Register                                        |

| Reg-02H | Master Interrupt Register                                            |

| Reg-04H | Master Clock Monitor Register                                        |

| Reg-05H | Master Control Register                                              |

| Reg-06H | Transmit Clock Synthesis Control Register                            |

| Reg-07H | Receive Clock Synthesis Control Register                             |

| Reg-10H | Receive Section Overhead Processor Control Register                  |

| Reg-11H | Receive Section Overhead Processor Status Register                   |

| Reg-12H | LSB of the Receive Section Overhead Processor Status BIP-8 Counter   |

| Reg-13H | MSB of the Receive Section Overhead Processor Status BIP-8 Counter   |

| Reg-14H | Transmit Section Overhead Processor Control Register                 |

| Reg-15H | Transmit Section Overhead Processor Control Error Insertion Register |

| Reg-18H | Receive Line Overhead Processor Control and Status Register          |

| Reg-19H | Receive Line Overhead Processor Interrupt Enable and Status Register |

| Reg-1AH | Line BIP–8/24 Register                                               |

| Reg-1BH | Line BIP–8/24 Register                                               |

| Reg-1CH | Line BIP–8/24 Register                                               |

| Reg-1DH | Line Far-End Block Error Register                                    |

| Reg-1EH | Line Far-End Block Error Register                                    |

| Reg-1FH | Line Far-End Block Error Register                                    |

| Reg-20H | Transmit Line Overhead Processor Register                            |

| Reg-21H | Transmit Line Overhead Processor Error Insertion Register            |

| Reg-30H | Receive Path Overhead Processor Interrupt Register                   |

| Reg-31H | Receive Path Overhead Processor Register                             |

| Reg-33H | Receive Path Overhead Processor Interrupt Enable Register            |

| Reg-37H | Receive Path Signal Label Register                                   |

| Reg-38H | Path BIP–8 (B3) Register                                             |

| Reg-39H | Path BIP–8 (B3) Register                                             |

| Reg-3AH | Path Far-End Block Error Register                                    |

| Reg-3BH | Path Far-End Block Error Register                                    |

| Reg-3CH | Path Far-End Block Error Register                                    |

| Reg-40H | Transmit Path Overhead Processor Error Insertion Register            |

| Reg-41H | Transmit Path Overhead Processor Pointer Control Register            |

| Reg-45H | Transmit Path Overhead Processor Arbitrary Payload Pointer Register  |

| Reg-46H | Transmit Path Overhead Processor Arbitrary Payload Pointer Register  |

| Reg-48H | Transmit Path Overhead Processor Path Signal Label Register          |

| Reg-49H | Transmit Path Overhead Processor Arbitrary Path Status Register      |

| Reg-50H | Receive ATM Cell Processor Control and Status Register               |

| Reg-51H | Receive ATM Cell Processor Interrupt Register                        |

| Reg-52H | Receive ATM Cell Processor Match Header Pattern Register             |

| Reg-53H | Receive ATM Cell Processor Match Header Mask Register                |

| Reg-54H | Receive ATM Cell Processor Correctable HCS Error Count Register      |

# CY7C955 Register Map (continued)

| Address | Register                                                          |  |

|---------|-------------------------------------------------------------------|--|

| Reg-55H | Receive ATM Cell Processor Uncorrectable HCS Error Count Register |  |

| Reg-56H | Receive ATM Cell Processor Receive Cell Counter Register          |  |

| Reg-57H | Receive ATM Cell Processor Receive Cell Counter Register          |  |

| Reg-58H | Receive ATM Cell Processor Receive Cell Counter Register          |  |

| Reg-59H | Receive ATM Cell Processor Receive Configuration Register         |  |

| Reg-60H | Transmit ATM Cell Processor Control and Status Register           |  |

| Reg-61H | Transmit ATM Cell Processor Unassigned Cell Header Register       |  |

| Reg-62H | Transmit ATM Cell Processor Unassigned Cell Payload Register      |  |

| Reg-63H | Transmit ATM Cell Processor FIFO Control Register                 |  |

| Reg-64H | Transmit ATM Cell Processor Transmit Cell Counter Register        |  |

| Reg-65H | Transmit ATM Cell Processor Transmit Cell Counter Register        |  |

| Reg-66H | Transmit ATM Cell Processor Transmit Cell Counter Register        |  |

| Reg-67H | Transmit ATM Cell Processor Transmit Configuration Register       |  |

| Reg-80H | CY7C955 Test Control Register                                     |  |

| REG-00H      | Master Reset / Type / Identity Register |            |         |

|--------------|-----------------------------------------|------------|---------|

| BIT POSITION | NAME                                    | READ/WRITE | DEFAULT |

| 7            | RESET                                   | R/W        | 0       |

| 6            | TYPE[2]                                 | R          | 0       |