LM3485 Hysteretic PFET Buck Controller

# LM3485 Hysteretic PFET Buck Controller General Description • 4.5V

The LM3485 is a high efficiency PFET switching regulator controller that can be used to quickly and easily develop a small, low cost, switching buck regulator for a wide range of applications. The hysteretic control architecture provides for simple design without any control loop stability concerns using a wide variety of external components. The PFET architecture also allows for low component count as well as ultra-low dropout, 100% duty cycle operation. Another benefit is high efficiency operation at light loads without an increase in output ripple.

Current limit protection is provided by measuring the voltage across the PFET's  $R_{DS(ON)}$ , thus eliminating the need for a sense resistor. The cycle-by-cycle current limit can be adjusted with a single resistor, ensuring safe operation over a range of output currents.

### **Features**

- Easy to use control methodology

- No control loop compensation required

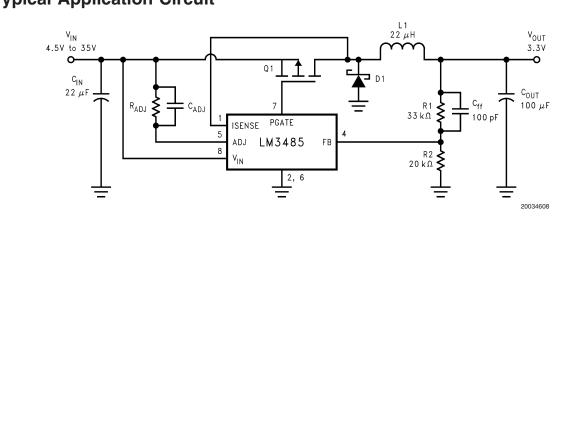

# **Typical Application Circuit**

- 4.5V to 35V wide input range

- 1.242V to V<sub>IN</sub> adjustable output range

- High Efficiency 93%

- ±1.3% (±2% over temp) internal reference

- 100% duty cycle

- Maximum operating frequency > 1MHz

- Current limit protection

- MSOP-8

### **Applications**

- Set-Top Box

- DSL/Cable Modem

- PC/IA

- Auto PC

- TFT Monitor

- Battery Powered Portable Applications

- Distributed Power Systems

- Always On Power

© 2004 National Semiconductor Corporation DS200346

# **Connection Diagram**

| Top View |        |                 |   |  |  |

|----------|--------|-----------------|---|--|--|

| 1        | ISENSE | V <sub>IN</sub> | 8 |  |  |

| 2        | GND    | PGATE           | 7 |  |  |

| 3        | NC     | PWR GND         | 6 |  |  |

| 4        | FB     | ADJ             | 5 |  |  |

| 20034609 |        |                 |   |  |  |

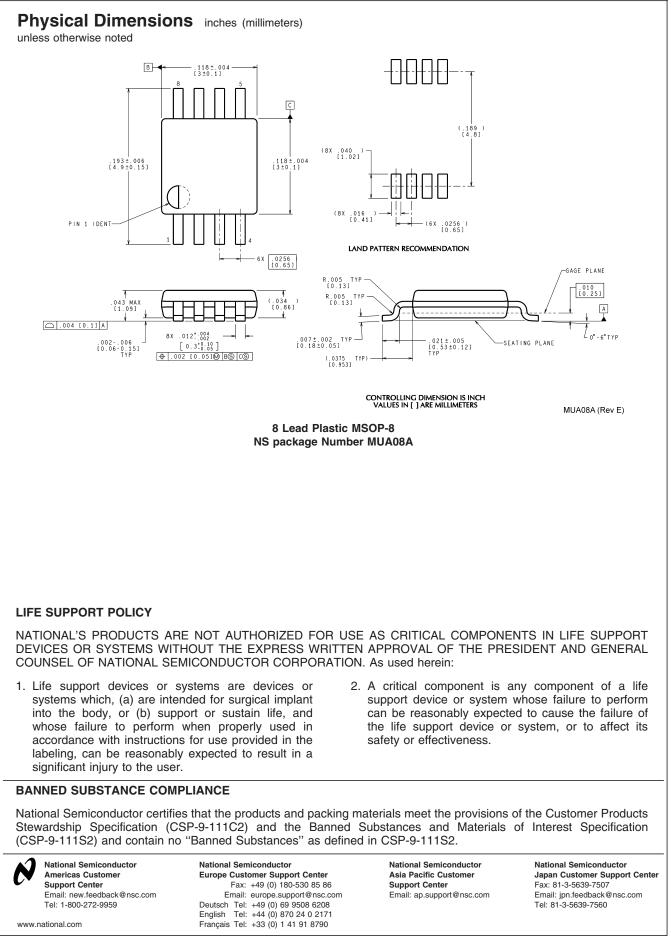

8 Lead Plastic MSOP-8 NS package Number MUA08A

# Package Marking and Ordering Information

| Order Number | Package Type | Package Marking | Supplied As:                |

|--------------|--------------|-----------------|-----------------------------|

| LM3485MM     | MSOP-8       | S29B            | 1000 units on Tape and Reel |

| LM3485MMX    | MSOP-8       | S29B            | 3500 units on Tape and Reel |

# **Pin Description**

| Pin Name | Pin Number | Description                                                                   |  |

|----------|------------|-------------------------------------------------------------------------------|--|

| ISENSE   | 1          | The current sense input pin. This pin should be connected to Drain            |  |

|          |            | node of the external PFET.                                                    |  |

| GND      | 2          | Signal ground.                                                                |  |

| NC       | 3          | No connection.                                                                |  |

| FB       | 4          | The feedback input. Connect the FB to a resistor voltage divider              |  |

|          |            | between the output and GND for an adjustable output voltage.                  |  |

| ADJ      | 5          | Current limit threshold adjustment. It connects to an internal 5.5µA          |  |

|          |            | current source. A resistor is connected between this pin and the              |  |

|          |            | input Power Supply. The voltage across this resistor is compared              |  |

|          |            | with the $V_{\text{DS}}$ of the external PFET to determine if an over-current |  |

|          |            | condition has occurred.                                                       |  |

| PWR GND  | 6          | Power ground.                                                                 |  |

| PGATE    | 7          | Gate Drive output for the external PFET. PGATE swings between                 |  |

|          |            | $V_{IN}$ and $V_{IN}$ -5V.                                                    |  |

| VIN      | 8          | Power supply input pin.                                                       |  |

www.national.com

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| VIN Voltage            | -0.3V to 36V             |

|------------------------|--------------------------|

| PGATE Voltage          | -0.3V to 36V             |

| FB Voltage             | -0.3V to 5V              |

| ISENSE Voltage         | -1.0V to 36V             |

| ADJ Voltage            | -0.3V to 36V             |

| Maximum Junction Temp. | 150°C                    |

| Power Dissipation      | 417mW @ T <sub>A</sub> = |

|                        | 25°C                     |

| ESD Susceptibilty         |                |

|---------------------------|----------------|

| Human Body Model (Note 3) | 2kV            |

| Lead Temperature          |                |

| Vapor Phase (60 sec.)     | 215°C          |

| Infared (15 sec.)         | 220°C          |

| Storage Temperature       | –65°C to 150°C |

# Operating Ratings (Note 1)

| Supply Voltage     | 4.5V to 35V     |

|--------------------|-----------------|

| Operating Junction |                 |

| Temperature        | –40°C to +125°C |

# **Electrical Characteristics**

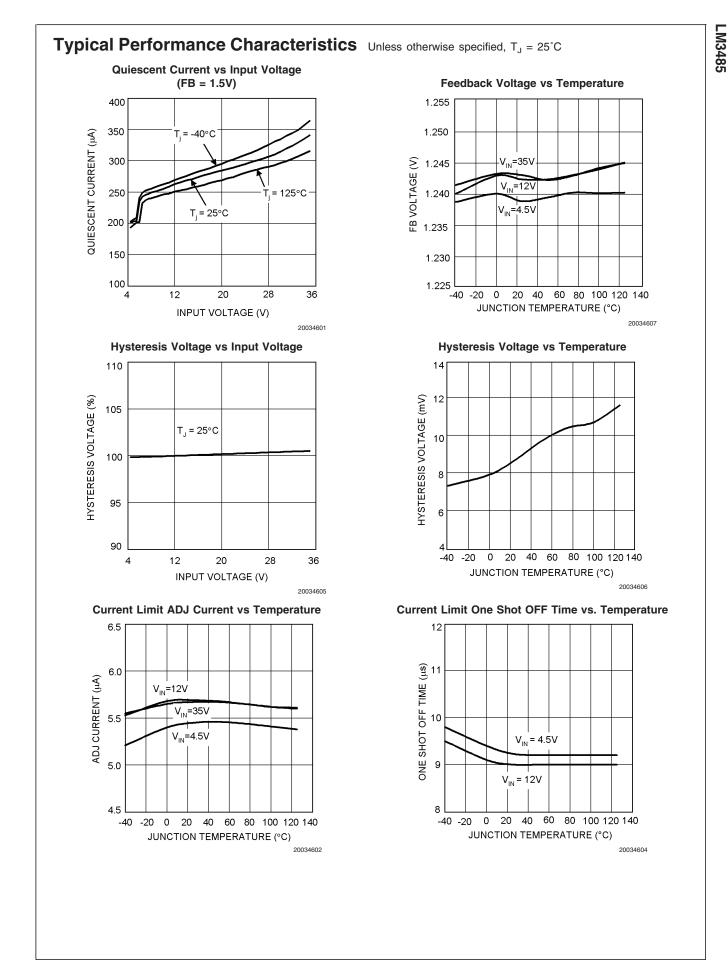

Specifications in Standard type face are for  $T_J = 25^{\circ}$ C, and in **bold type face** apply over the full **Operating Temperature Range** ( $T_J = -40^{\circ}$ C to +125°C). Unless otherwise specified,  $V_{IN} = 12V$ ,  $V_{ISNS} = V_{IN} - 1V$ , and  $V_{ADJ} = V_{IN} - 1.1V$ . Datasheet min/max specification limits are guaranteed by design, test, or statistical analysis.

| Symbol                   | Parameter                           | Conditions                                                                           | Min<br>(Note 4)       | Typ<br>(Note 5) | Max<br>(Note 4)       | Unit |

|--------------------------|-------------------------------------|--------------------------------------------------------------------------------------|-----------------------|-----------------|-----------------------|------|

| Ι <sub>Q</sub>           | Quiescent Current at<br>ground pin  | FB = 1.5V<br>(Not Switching)                                                         |                       | 250             | 400                   | μA   |

| $V_{FB}$                 | Feedback Voltage<br>(Note 6)        |                                                                                      | 1.226<br><b>1.217</b> | 1.242           | 1.258<br><b>1.267</b> | V    |

| V <sub>HYST</sub>        | Comparator<br>Hysteresis            |                                                                                      |                       | 10<br><b>14</b> | 15<br><b>20</b>       | mV   |

| V <sub>CL</sub> (Note 7) | Current limit<br>comparator trip    | $R_{ADJ} = 20k\Omega$                                                                |                       | 110             |                       | mV   |

|                          | voltage                             | $R_{ADJ} = 160 k\Omega$                                                              |                       | 880             |                       |      |

| V <sub>CL_OFFSET</sub>   | Current limit<br>comparator offset  | V <sub>FB</sub> = 1.5V                                                               | -20                   | 0               | +20                   | mV   |

| I <sub>CL_ADJ</sub>      | Current limit ADJ<br>current source | V <sub>FB</sub> = 1.5V                                                               | 3.0                   | 5.5             | 7.0                   | μA   |

| T <sub>CL</sub>          | Current limit one shot<br>off time  | $V_{ADJ} = 11.5V$<br>$V_{ISNS} = 11.0V$<br>$V_{FB} = 1.0V$                           | 6                     | 9               | 14                    | μs   |

| R <sub>PGATE</sub> Drive | Driver resistance                   | Source<br>I <sub>SOURCE</sub> = 100mA                                                |                       | 5.5             |                       | Ω    |

|                          |                                     | Sink<br>I <sub>Sink</sub> = 100mA                                                    |                       | 8.5             |                       |      |

| I <sub>PGATE</sub>       | Driver Output current               | Source<br>V <sub>IN</sub> = 7V,<br>P <sub>GATE</sub> = 3.5V                          |                       | 0.44            |                       | A    |

|                          |                                     | Sink<br>V <sub>IN</sub> = 7V,<br>P <sub>GATE</sub> = 3.5V                            |                       | 0.32            |                       |      |

| I <sub>FB</sub>          | FB pin Bias Current<br>(Note 8)     | V <sub>FB</sub> = 1.0V                                                               |                       | 300             | 750                   | nA   |

| T <sub>onmin_nor</sub>   | Minimum on time in normal operation | $V_{ISNS} = V_{ADJ}+0.1V$<br>$C_{load}$ on OUT =<br>1000pF<br>(Note 9)               |                       | 100             |                       | ns   |

| T <sub>onmin_cl</sub>    | Minimum on time in<br>current limit | $V_{ISNS} = V_{ADJ}+0.1V$<br>$V_{FB} = 1.0V C_{load}$ on<br>OUT = 1000pF<br>(Note 9) |                       | 175             |                       | ns   |

3

LM3485

### Electrical Characteristics (Continued)

Specifications in Standard type face are for  $T_J = 25^{\circ}$ C, and in **bold type face** apply over the full **Operating Temperature Range** ( $T_J = -40^{\circ}$ C to  $+125^{\circ}$ C). Unless otherwise specified,  $V_{IN} = 12$ V,  $V_{ISNS} = V_{IN} - 1$ V, and  $V_{ADJ} = V_{IN} - 1.1$ V. Datasheet min/max specification limits are guaranteed by design, test, or statistical analysis.

| Symbol                  | Parameter                           | Conditions               | Min<br>(Note 4) | <b>Typ</b><br>(Note 5) | Max<br>(Note 4) | Unit |

|-------------------------|-------------------------------------|--------------------------|-----------------|------------------------|-----------------|------|

| $%V_{FB}/\Delta V_{IN}$ | Feedback Voltage<br>Line Regulation | $4.5 \le V_{IN} \le 35V$ |                 | 0.010                  |                 | %/V  |

Note 1: Absolute maximum ratings are limits beyond which damage to the device may occur. Operating Ratings are conditions for which the device is intended to be functional, but device parameter specifications may not be guaranteed. For guaranteed specifications and test conditions, see the Electrical Characteristics.

**Note 2:** The maximum allowable power dissipation is a function of the maximum junction temperature,  $T_{J\_MAX}$ , the junction-to-ambient thermal resistance,  $\theta_{JA} = 240^{\circ}$ C/W, and the ambient temperature,  $T_{A}$ . The maximum allowable power dissipation at any ambient temperature is calculated using:

$P_{D\_MAX} = (T_{J\_MAX} - T_A)/\theta_{JA}. \ \text{Exceeding the maximum allowable power dissipation will cause excessive die temperature.}$

Note 3: The human body model is a 100 pF capacitor discharged through a  $1.5k\Omega$  resistor into each pin.

Note 4: All limits are guaranteed at room temperature (standard type face) and at temperature extremes (bold type face). All room temperature limits are 100% tested. All limits at temperature extremes are guaranteed via correlation using standard Statistical Quality Control (SQC) methods. All limits are used to calculate Average Outgoing Quality Level (AOQL).

Note 5: Typical numbers are at 25°C and represent the most likely norm.

Note 6: The  $V_{FB}$  is the trip voltage at the FB pin when PGATE switches from high to low.

Note 7:  $V_{CL} = I_{CL\_ADJ} * R_{ADJ}$

Note 8: Bias current flows out from the FB pin.

Note 9: A 1000pF capacitor is connected between VIN and PGATE.

www.national.com

LM3485

www.national.com

# **Functional Description**

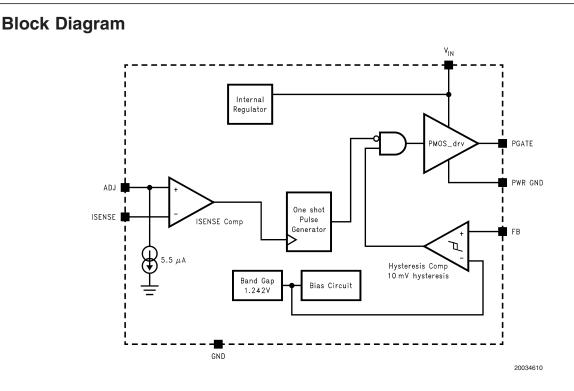

#### OVERVIEW

The LM3485 is buck (step-down) DC-DC controller that uses a hysteretic control scheme. The comparator is designed with approximately 10mV of hysteresis. In response to the voltage at the FB pin, the gate drive (PGATE pin) turns the external PFET on or off. When the inductor current is too high, the current limit protection circuit engages and turns the PFET off for approximately 9 $\mu$ s.

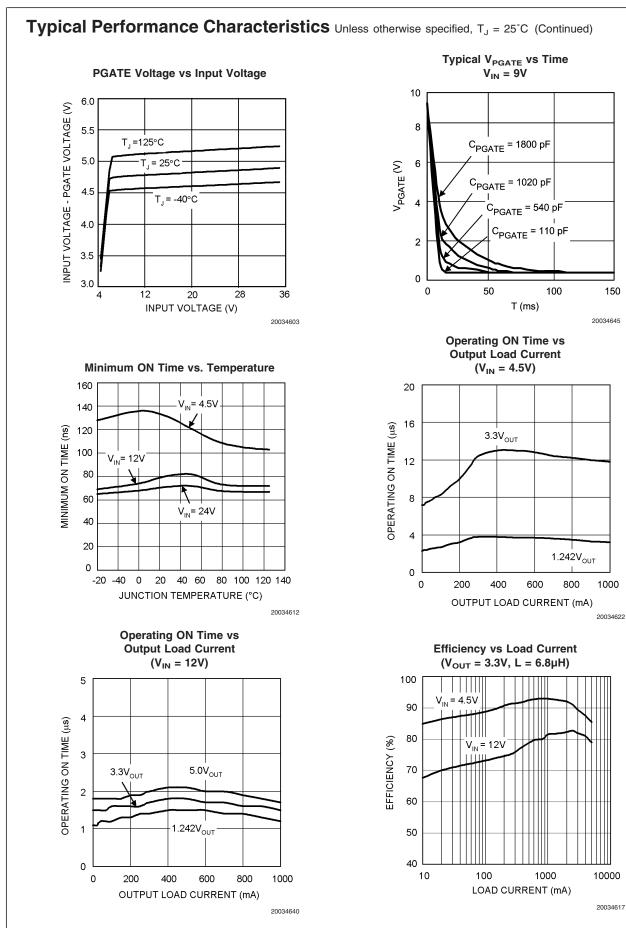

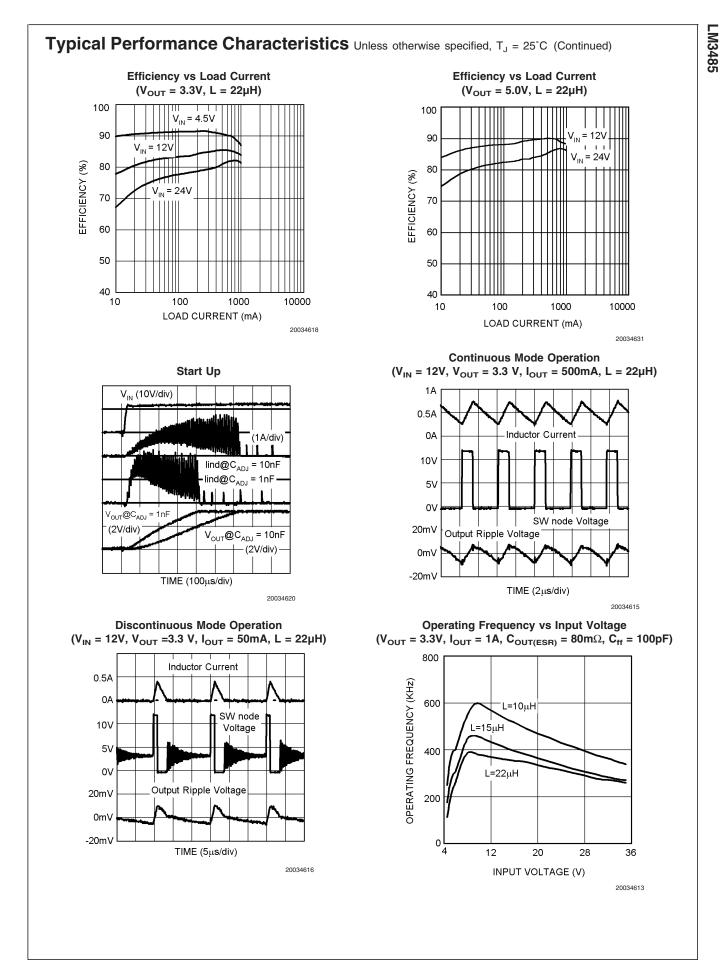

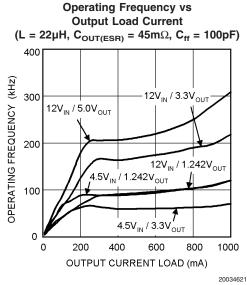

Hysteretic control does not require an internal oscillator. Switching frequency depends on the external components and operating conditions. Operating frequency reduces at light loads resulting in excellent efficiency compared to other architectures.

2 external resistors can easily program the output voltage. The output can be set in a wide range from 1.242V (typical) to  $V_{\rm IN}.$

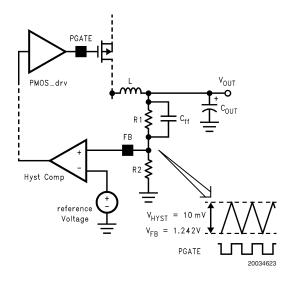

#### HYSTERETIC CONTROL CIRCUIT

The LM3485 uses a comparator based voltage control loop. The feedback is compared to a 1.242V reference and a 10mV hysteresis is designed into the comparator to ensure noise free operation.

When the FB input to the comparator falls below the reference voltage, the output of the comparator moves to a low state. This results in the driver output, PGATE, pulling the gate of the PFET low and turning on the PFET. With the PFET on, the input supply charges Cout and supplies current to the load via the series path through the PFET and the inductor. Current through the Inductor ramps up linearly and the output voltage increases. As the FB voltage reaches the upper threshold, which is the internal reference voltage plus 10mV, the output of the comparator changes from low to high, and the PGATE responds by turning the PFET off. As the PFET turns off, the inductor voltage reverses, the catch diode turns on, and the current through the inductor ramps down. Then, as the output voltage reaches the internal reference voltage again, the next cycle starts.

The LM3485 operates in discontinuous conduction mode at light load current or continuous conduction mode at heavy load current. In discontinuous conduction mode, current through the inductor starts at zero and ramps up to the peak, then ramps down to zero. Next cycle starts when the FB voltage reaches the internal voltage. Until then, the inductor current remains zero. Operating frequency is lower and switching losses reduce. In continuous conduction mode, current always flows through the inductor and never ramps down to zero.

The output voltage ( $V_{OUT}$ ) can be programmed by 2 external resistors. It can be calculated as follows:

#### V<sub>OUT</sub> = 1.242\* ( R1 + R2 ) / R2

**FIGURE 1. Hysteretic Window**

### Functional Description (Continued)

The minimum output voltage ripple (V\_{OUT\\_PP}) can be calculated in the same way.

$V_{OUT_{PP}} = V_{HYST} (R1 + R2) / R2$

For example, with V<sub>OUT</sub> set to 3.3V, V<sub>OUT\_PP</sub> is 26.6mV V<sub>OUT\_PP</sub> =  $0.01^*$  ( 33K + 20K ) / 20K = 0.0266V

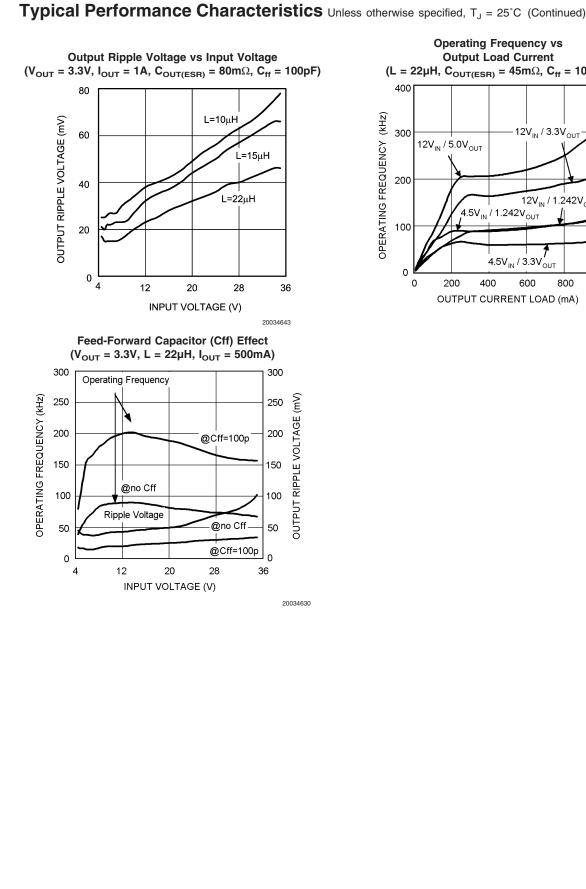

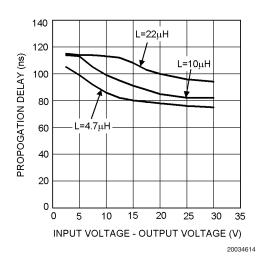

Operating frequency (F) is determined by knowing the input voltage, output voltage, inductor,  $V_{HYST}$ , ESR (Equivalent Series Resistance) of output capacitor, and the delay. It can be approximately calculated using the formula:

$$F = \frac{V_{OUT}}{V_{IN}} * \frac{(V_{IN} - V_{OUT}) * ESR}{(V_{HYST} * \alpha * L) + (V_{IN} * delay * ESR)}$$

where:

α: ( R1 + R2 ) / R2

delay: It includes the LM3485 propagation delay time and the PFET delay time. The propagation delay is 90ns typically. (See the Propagation Delay curve below.)

FIGURE 2. Propagation Delay

The operating frequency and output ripple voltage can also be significantly influenced by the speed up capacitor (Cff). Cff is connected in parallel with the high side feedback resistor, R1. The location of this capacitor is similar to where a feed forward capacitor would be located in a PWM control scheme. However it's effect on hysteretic operation is much different. The output ripple causes a current to be sourced or sunk through this capacitor. This current is essentially a square wave. Since the input to the feedback pin, FB, is a high impedance node, the current flows through R2. The end result is a reduction in output ripple and an increase in operating frequency. When adding Cff, calculate the formula above with  $\alpha$  = 1. The value of Cff depend on the desired operating frequency and the value of R2. A good starting point is 470pF ceramic at 100kHz decreasing linearly with increased operating frequency. Also note that as the output voltage is programmed below 2.5V, the effect of Cff will decrease significantly.

#### **CURRENT LIMIT OPERATION**

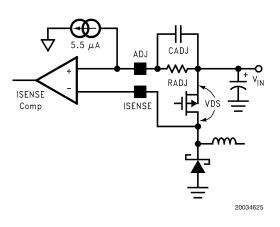

The LM3485 has a cycle-by-cycle current limit. Current limit is sensed across the  $V_{\rm DS}$  of the PFET or across an additional sense resistor. When current limit is activated, the LM3485 turns off the external PFET for a period of 9µs(typical). The current limit is adjusted by an external resistor,  $R_{\rm ADJ}.$

The current limit circuit is composed of the ISENSE comparator and the one-shot pulse generator. The positive input of the ISENSE comparator is the ADJ pin. An internal 5.5 $\mu$ A current sink creates a voltage across the external R<sub>ADJ</sub> resistor. This voltage is compared to the voltage across the PFET or sense resistor. The ADJ voltage can be calculated as follows:

$$V_{ADJ} = V_{IN} - (R_{ADJ} * 3.0 \mu A)$$

Where 3.0 $\mu$ A is the minimum I<sub>CL-ADJ</sub> value.

The negative input of the ISENSE comparator is the ISENSE pin that should be connected to the drain of the external PFET. The inductor current is determined by sensing the  $V_{\rm DS}$ . It can be calculated as follows.

$$V_{ISENSE} = V_{IN} - (R_{DSON} * I_{IND_{PEAK}}) = V_{IN} - V_{DS}$$

FIGURE 3. Current Sensing by V<sub>DS</sub>

The current limit is activated when the voltage at the ADJ pin exceeds the voltage at the  $I_{SENSE}$  pin. The ISENSE comparator triggers the 9µs one shot pulse generator forcing the driver to turn the PFET off. The driver turns the PFET back on after 9µs. If the current has not reduced below the set threshold, the cycle will repeat continuously.

A filter capacitor,  $C_{ADJ}$ , should be placed as shown in *Figure 3*.  $C_{ADJ}$  filters unwanted noise so that the ISENSE comparator will not be accidentally triggered. A value of 100pF to 1nF is recommended in most applications. Higher values can be used to create a soft-start function (See Start Up section).

The current limit comparator has approximately 100ns of blanking time. This ensures that the PFET is fully on when the current is sensed. However, under extreme conditions such as cold temperature, some PFETs may not fully turn on within the blanking time. In this case, the current limit threshold must be increased. If the current limit function is used, the on time must be greater than 100ns. Under low duty cycle operation, the maximum operating frequency will be limited by this minimum on time.

During current limit operation, the output voltage will drop significantly as will operating frequency. As the load current is reduced, the output will return to the programmed voltage. However, there is a current limit fold back phenomenon inherent in this current limit architecture. See *Figure 4*.

www.national.com

### Functional Description (Continued)

20034626

#### FIGURE 4. Current Limit Fold Back Phenomenon

At high input voltages (>28V) increased undershoot at the switch node can cause an increase in the current limit threshold. To avoid this problem, a low Vf Schottky catch diode must be used (See Catch Diode Selection). Additionally, a resistor can be placed between the ISENSE pin and the switch node. Any value up to approximately  $600\Omega$  is recommended.

#### START UP

The current limit circuit is active during start-up. During start-up the PFET will stay on until either the current limit or the feedback comparator is tripped

If the current limit comparator is tripped first then the fold back characteristic should be taken into account. Start-up into full load may require a higher current limit set point or the load must be applied after start-up.

One problem with selecting a higher current limit is inrush current during start-up. Increasing the capacitance ( $C_{ADJ}$ ) in parallel with  $R_{ADJ}$  results in soft-start.  $C_{ADJ}$  and  $R_{ADJ}$  create an RC time constant forcing current limit to activate at a lower current. The output voltage will ramp more slowly when using the soft-start functionality. There are example start-up plots for  $C_{ADJ}$  equal to 1nF and 10nF in the Typical Performance Characteristics. Lower values for  $C_{ADJ}$  will have little to no effect on soft-start.

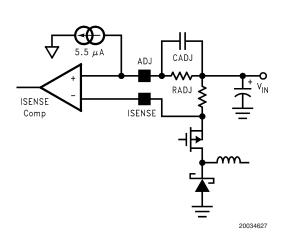

#### EXTERNAL SENSE RESISTOR

The V<sub>DS</sub> of a PFET will tend to vary significantly over temperature. This will result an equivalent variation in current limit. To improve current limit accuracy an external sense resistor can be connected from V<sub>IN</sub> to the source of the PFET, as shown in *Figure 5.*

#### FIGURE 5. Current Sensing by External Resistor

#### PGATE

When switching, the PGATE pin swings from VIN (off) to some voltage below VIN (on). How far the PGATE will swing depends on several factors including the capacitance, on time, and input voltage.

As shown in the Typical Performance Characteristics, PGATE voltage swing will increase with decreasing gate capacitance. Although PGATE voltage will typically be around VIN-5V, with every small gate capacitances, this value can increase to a typical maximum of VIN-8.3V.

Additionally, PGATE swing voltage will increase as on time increases. During long on times, such as when operating at 100% duty cycle, the PGATE voltage will eventually fall to its maximum voltage of VIN-8.3V (typical) regardless of the PFET gate capacitance.

The PGATE voltage will not fall below 0.4V (typical). Therefore, when the input voltage falls below approximately 9V, the PGATE swing voltage range will be reduced. At an input voltage of 7V, for instance, PGATE will swing from 7V to a minimum of 0.4V.

## **Design Information**

Hysteretic control is a simple control scheme. However the operating frequency and other performance characteristics highly depend on external conditions and components. If either the inductance, output capacitance, ESR,  $V_{\rm IN}$ , or Cff is changed, there will be a change in the operating frequency and output ripple. The best approach is to determine what operating frequency is desirable in the application and then begin with the selection of the inductor and  $C_{\rm OUT}$  ESR.

#### **INDUCTOR SELECTION (L1)**

The important parameters for the inductor are the inductance and the current rating. The LM3485 operates over a wide frequency range and can use a wide range of inductance values. A good rule of thumb is to use the equations used for National's **Simple Switchers**<sup>®</sup>. The equation for inductor ripple ( $\Delta i$ ) as a function of output current (I<sub>OUT</sub>) is:

for

$$I_{out} < 2.0$$

Amps

$\Delta i \le I_{out} * 0.386827 * I_{out}^{-0.366726}$

for  $I_{out} > 2.0$ Amps

$\Delta i \le I_{out} * 0.3$

The inductance can be calculated based upon the desired operating frequency where:

$$L = \frac{V_{IN} - V_{DS} - V_{OUT}}{\Delta i} * \frac{D}{F}$$

And

$$D = \frac{V_{OUT} + V_D}{V_{IN} - V_{DS} + V_D}$$

where D is the duty cycle,  $V_{\rm D}$  is the diode forward voltage, and  $V_{\rm DS}$  is the voltgae drop across the PFET.

The inductor should be rated to the following:

$$Ipk = (Iout + \Delta i/2)^* 1.1$$

$$RMS = \sqrt{I_{OUT}^2 + \frac{\Delta i^2}{3}}$$

The inductance value and the resulting ripple is one of the key parameters controlling operating frequency. The second is the ESR.

#### **OUTPUT CAPACITOR SELECTION (Cout)**

The ESR of the output capacitor times the inductor ripple current is equal to the output ripple of the regulator. However, the  $V_{HYST}$  sets the first order value of this ripple. As ESR is increased with a given inductance, then operating frequency increases as well. If ESR is reduced then the operating frequency reduces.

The use of ceramic capacitors has become a common desire of many power supply designers. However, ceramic capacitors have a very low ESR resulting in a 90° phase shift of the output voltage ripple. This results in low operating frequency and increased output ripple. To fix this problem a low value resistor should be added in series with the ceramic output capacitor. Although counter intuitive, this combination of a ceramic capacitor and external series resistance provide highly accurate control over the output voltage ripple. The other types capacitor, such as Sanyo POS CAP and OS-

www.national.com

CON, Panasonic SP CAP, Nichicon "NA" series, are also recommended and may be used without additional series resistance.

For all practical purposes, any type of output capacitor may be used with proper circuit verification.

#### INPUT CAPACITOR SELECTION (CIN)

A bypass capacitor is required between the input source and ground. It must be located near the source pin of the external PFET. The input capacitor prevents large voltage transients at the input and provides the instantaneous current when the PFET turns on.

The important parameters for the input capacitor are the voltage rating and the RMS current rating. Follow the manufacturer's recommended voltage derating. For high input voltage application, low ESR electrolytic capacitor, the Nichicon "UD" series or the Panasonic "FK" series, is available. The RMS current in the input capacitor can be calculated.

$$I_{\text{RMS}_{CIN}} = I_{\text{OUT}}^{*} \frac{(V_{\text{OUT}}^{*} (V_{\text{IN}} - V_{\text{OUT}}))^{1/2}}{V_{\text{IN}}}$$

The input capacitor power dissipation can be calculated as follows.

$P_{D(CIN)} = I_{RMS_{CIN}}^{2} * ESR_{CIN}$

The input capacitor must be able to handle the RMS current and the  $P_D$ . Several input capacitors may be connected in parallel to handle large RMS currents. In some cases it may be much cheaper to use multiple electrolytic capacitors than a single low ESR, high performance capacitor such as OS-CON or Tantalum. The capacitance value should be selected such that the ripple voltage created by the charge and discharge of the capacitance is less than 10% of the total ripple across the capacitor.

#### PROGRAMMING THE CURRENT LIMIT (RADJ)

The current limit is determined by connecting a resistor  $(R_{\text{AD},\text{J}})$  between input voltage and the ADJ pin.

$$R_{ADJ} = I_{IND\_PEAK} * R_{DSON} / I_{CL\_ADJ}$$

where:

R<sub>DSON</sub> : Drain-Source ON resistance of the external PFET

I<sub>CL ADJ</sub>: 3.0µA minimum

$I_{IND PEAK} = I_{LOAD} + I_{RIPPLE}/2$

Using the minimum value for  $I_{\rm CL\_ADJ}$  (3.0µA) ensures that the current limit threshold will be set higher than the peak inductor current.

The R<sub>ADJ</sub> value must be selected to ensure that the voltage at the ADJ pin does not fall below 3.5V. With this in mind, R<sub>ADJ\_MAX</sub> = (V<sub>IN</sub>-3.5)/7µA. If a larger R<sub>ADJ</sub> value is needed to set the desired current limit, either use a PFET with a lower R<sub>DSON</sub>, or use a current sense resistor as shown in *Figure 5*.

The current limit function can be disabled by connecting the ADJ pin to ground and ISENSE to VIN.

#### CATCH DIODE SELECTION (D1)

The important parameters for the catch diode are the peak current, the peak reverse voltage, and the average power dissipation. The average current through the diode can be calculated as following.

## Design Information (Continued)

#### $I_{D_AVE} = I_{OUT}^* (1 - D)$

The off state voltage across the catch diode is approximately equal to the input voltage. The peak reverse voltage rating must be greater than input voltage. In nearly all cases a Schottky diode is recommended. In low output voltage applications a low forward voltage provides improved efficiency. For high temperature applications, diode leakage current may become significant and require a higher reverse voltage rating to achieve acceptable performance.

#### P-CHANNEL MOSFET SELECTION (Q1)

The important parameters for the PFET are the maximum Drain-Source voltage ( $V_{DS}$ ), the on resistance ( $R_{DSON}$ ), Current rating, and the input capacitance.

The voltage across the PFET when it is turned off is equal to the sum of the input voltage and the diode forward voltage. The  $V_{\rm DS}$  must be selected to provide some margin beyond the input voltage.

PFET drain current, Id, must be rated higher than the peak inductor current,  $I_{\rm IND-PEAK}.$

Depending on operating conditions, the PGATE voltage may fall as low as V<sub>IN</sub> - 8.3V. Therefore, a PFET must be selected with a V<sub>GS</sub> greater than the maximum PGATE swing voltage. As input voltage desreases below 9V, PGATE swing voltage may also decrease. At 5.0V input the PGATE will swing from V<sub>IN</sub> to V<sub>IN</sub> - 4.6V. To ensure that the PFET turns on quickly and completely, a low threshold PFET should be used when the input voltage is less than 7V.

However, PFET switching losses will increase as the  $V_{\rm GS}$  threshold decreases. Therefore, whenever possible, a high threshold PFET should be selected. Total power loss in the FET can be approximated using the following equation:

PDswitch =  $R_{DSON}*I_{OUT}^{2*}D + F*I_{OUT}*V_{IN}*(t_{on} + t_{off})/2$ where:

$t_{on} = FET$  turn on time

$t_{off} = FET$  turn off time

A value of 10ns to 20ns is typical for ton and toff.

A PFET should be selected with a turn on rise time of less than 100ns. Slower rise times will degrade efficiency, can cause false current limiting, and in extreme cases may cause abnormal spiking at the PGATE pin.

The  $R_{\rm DSON}$  is used in determining the current limit resistor value,  $R_{\rm ADJ}$ . Note that the  $R_{\rm DSON}$  has a positive temperature

coefficient. At 100°C, the R<sub>DSON</sub> may be as much as 150% higher than the 25°C value. This increase in R<sub>DSON</sub> must be considered it when determining R<sub>ADJ</sub> in wide temperature range applications. If the current limit is set based upon 25°C ratings, then false current limiting can occur at high temperature.

Keeping the gate capacitance below 2000pF is recommended to keep switching losses and transition times low. This will also help keep the PFET drive current low, which will improve efficiency and lower the power dissipation within the controller.

As gate capacitance increases, operating frequency should be reduced and as gate capacitance decreases operating frequency can be increased.

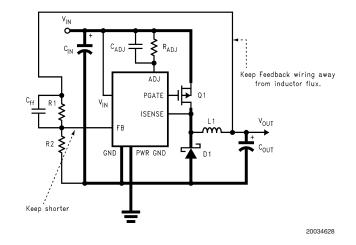

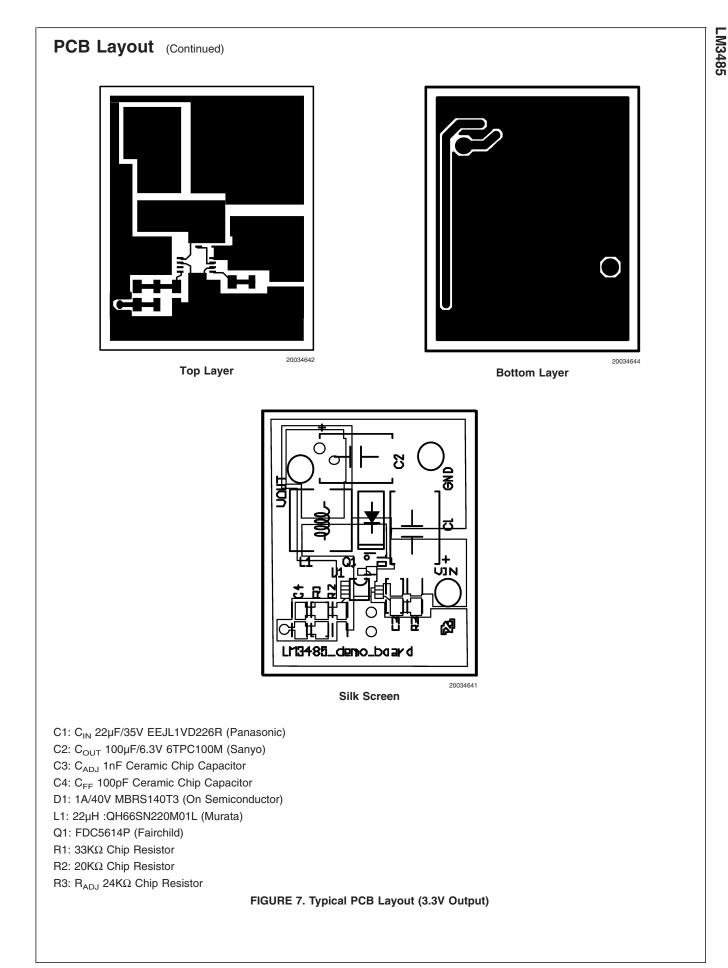

## **PCB** Layout

The PC board layout is very important in all switching regulator designs. Poor layout can cause switching noise into the feedback signal and general EMI problems. For minimal inductance, the wires indicated by heavy lines should be as wide and short as possible. Keep the ground pin of the input capacitor as close as possible to the anode of the diode. This path carries a large AC current. The switching node, the node with the diode cathode, inductor, and FET drain, should be kept short. This node is one of the main sources for radiated EMI since it is an AC voltage at the switching frequency. It is always good practice to use a ground plane in the design, particularly at high currents.

The two ground pins, PWR GND and GND, should be connected by as short a trace as possible; they can be connected underneath the device. These pins are resistively connected internally by approximately  $50\Omega$ . The ground pins should be tied to the ground plane, or to a large ground trace in close proximity to both the FB divider and C<sub>OUT</sub> grounds.

The gate pin of the external PFET should be located close to the PGATE pin. However, if a very small FET is used, a resistor may be required between PGATE and the gate of the FET to reduce high frequency ringing. Since this resistor will slow the PFET's rise time, the current limit blanking time should be taken into consideration (see Current Limit Operation).

The feedback voltage signal line can be sensitive to noise. Avoid inductive coupling to the inductor or the switching node, by keeping the FB trace away from these areas. PCB Layout (Continued)

LM3485

FIGURE 6. Typical PCB Layout Schematic (3.3V output)

www.national.com

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.