July 1995

# **COP472-3 Liquid Crystal Display Controller**

## **General Description**

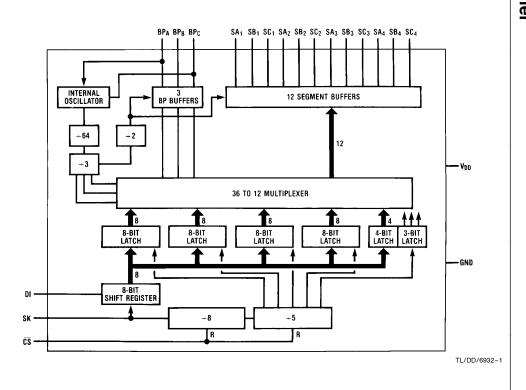

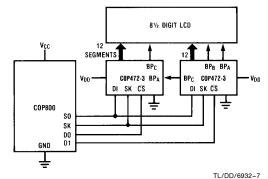

The COP472-3 Liquid Crystal Display (LCD) Controller is a peripheral member of the COPSTM family, fabricated using CMOS technology. The COP472-3 drives a multiplexed liquid crystal display directly. Data is loaded serially and is held in internal latches. The COP472-3 contains an on-chip oscillator and generates all the multi-level waveforms for backplanes and segment outputs on a triplex display. One COP472-3 can drive 36 segments multiplexed as 3 x 12 (4½ digit display). Two COP472-3 devices can be used together to drive 72 segments (3 x 24) which could be an 8½ digit display.

### **Features**

- Direct interface to TRIPLEX LCD

- Low power dissipation (100 µW typ.)

- Low cost

- Compatible with all COPS processors

- Needs no refresh from processor

- On-chip oscillator and latches

- Expandable to longer displays

- Operates from display voltage

- MICROWIRE™ compatible serial I/O

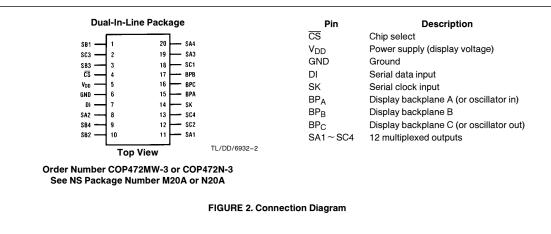

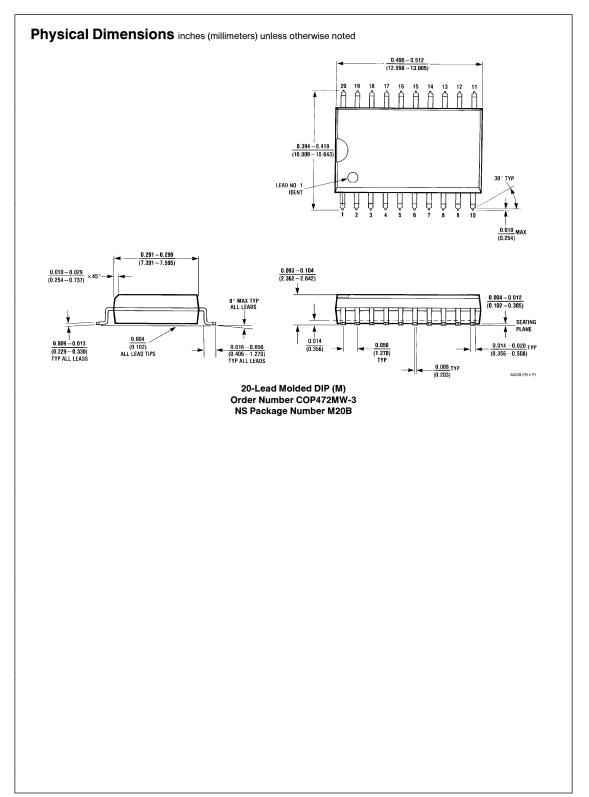

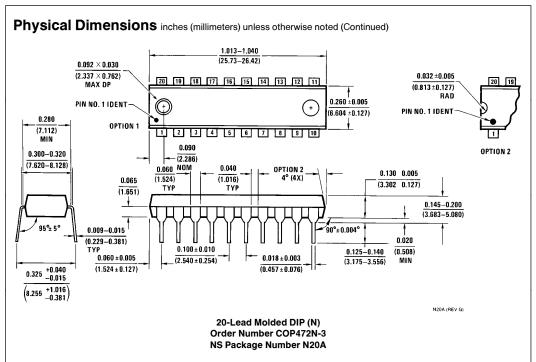

- 20-pin Dual-In-Line package and 20-pin SO

## **Block Diagram**

COPS™ and MICROWIRE™ are trademarks of National Semiconductor Corporation.

RRD-B30M56/Printed in U. S. A.

## **Absolute Maximum Ratings**

Voltage at CS, DI, SK pins -0.3V to +9.5VStorage Temperature  $-65^{\circ}\text{C}$  to  $+150^{\circ}\text{C}$  $\begin{array}{lll} \mbox{Voltage at all other Pins} & -0.3 \mbox{V to V}_{\mbox{DD}} + 0.3 \mbox{V} \\ \mbox{Operating Temperature Range} & 0^{\circ}\mbox{C to } 70^{\circ}\mbox{C} \\ \end{array}$ Lead Temp. (Soldering, 10 Seconds) 300°C

## **DC Electrical Characteristics**

GND = 0V, V<sub>DD</sub> = 3.0V to 5.5V, T<sub>A</sub> = 0°C to 70°C (depends on display characteristics)

| Parameter                                              | Conditions            | Min                               | Max                                  | Units |

|--------------------------------------------------------|-----------------------|-----------------------------------|--------------------------------------|-------|

| Power Supply Voltage, V <sub>DD</sub>                  |                       | 3.0                               | 5.5                                  | Volts |

| Power Supply Current, I <sub>DD</sub> (Note 1)         | V <sub>DD</sub> =5.5V |                                   | 250                                  | μΑ    |

|                                                        | V <sub>DD</sub> =3V   |                                   | 100                                  | μΑ    |

| Input Levels                                           |                       |                                   |                                      |       |

| DI, SK, CS                                             |                       |                                   |                                      |       |

| $V_{IL}$                                               |                       |                                   | 0.8                                  | Volts |

| V <sub>IH</sub>                                        |                       | 0.7 V <sub>DD</sub>               | 9.5                                  | Volts |

| BPA (as Osc. in)                                       |                       |                                   |                                      |       |

| $V_{IL}$                                               |                       |                                   | 0.6                                  | Volts |

| V <sub>IH</sub>                                        |                       | V <sub>DD</sub> -0.6              | V <sub>DD</sub>                      | Volts |

| Output Levels, BPC (as Osc. Out)                       |                       |                                   |                                      |       |

| $V_{OL}$                                               |                       |                                   | 0.4                                  | Volts |

| V <sub>OH</sub>                                        |                       | V <sub>DD</sub> −0.4              | V <sub>DD</sub>                      | Volts |

| Backplane Outputs (BPA, BPB, BPC)                      |                       |                                   |                                      |       |

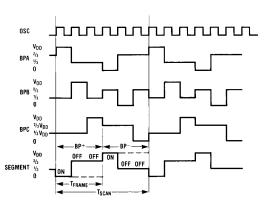

| V <sub>BPA, BPB, BPC</sub> ON                          | During                | $V_{DD}-\Delta V$                 | $V_{DD}$                             | Volts |

| V <sub>BPA, BPB, BPC</sub> OFF                         | BP+ Time              | $\frac{1}{3}$ $V_{DD} - \Delta V$ | $\frac{1}{3}$ $V_{DD} + \Delta V$    | Volts |

| V <sub>BPA, BPB, BPC</sub> ON                          | During                | 0                                 | ΔV                                   | Volts |

| V <sub>BPA</sub> , <sub>BPB</sub> , <sub>BPC</sub> OFF | BP- Time              | $^{2}/_{3}V_{DD}-\Delta V$        | $^{2}/_{3}$ $V_{DD} + \Delta V$      | Volts |

| Segment Outputs (SA <sub>1</sub> ∼ SA <sub>4</sub> )   |                       |                                   |                                      |       |

| V <sub>SEG</sub> ON                                    | During                | 0                                 | ΔV                                   | Volts |

| V <sub>SEG</sub> OFF                                   | BP+ Time              | $^{2}/_{3}V_{DD}-\Delta V$        | $^{2}/_{3}$ $V_{DD} + \Delta V$      | Volts |

| V <sub>SEG</sub> ON                                    | During                | $V_{DD}-\Delta V$                 | V <sub>DD</sub>                      | Volts |

| V <sub>SEG</sub> OFF                                   | BP Time               | ¹⁄₃ V <sub>DD</sub> −ΔV           | 1/ <sub>3</sub> V <sub>DD</sub> + ΔV | Volts |

| Internal Oscillator Frequency                          |                       | 15                                | 80                                   | kHz   |

| Frame Time (Int. Osc. ÷ 192)                           |                       | 2.4                               | 12.8                                 | ms    |

| Scan Frequency (1/T <sub>SCAN</sub> )                  |                       | 39                                | 208                                  | Hz    |

| SK Clock Frequency                                     |                       | 4                                 | 250                                  | kHz   |

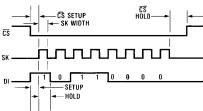

| SK Width                                               |                       | 1.7                               |                                      | μs    |

| DI                                                     |                       |                                   |                                      |       |

| Data Setup, t <sub>SETUP</sub>                         |                       | 1.0                               |                                      | μs    |

| Data Hold, t <sub>HOLD</sub>                           |                       | 100                               |                                      | ns    |

| CS                                                     |                       |                                   |                                      |       |

| <sup>t</sup> SETUP                                     |                       | 1.0                               |                                      | μs    |

| t <sub>HOLD</sub>                                      |                       | 1.0                               |                                      | μs    |

| Output Loading Capacitance                             |                       |                                   | 100                                  | pF    |

Note 1: Power supply current is measured in stand-alone mode with all outputs open and all inputs at VDD. Note 2:  $\Delta V\!=\!0.05V_{DD}.$

## **Absolute Maximum Ratings**

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

$\begin{array}{lll} \mbox{Voltage at CS, DI, SK Pins} & -0.3 \mbox{V to } +9.5 \mbox{V} \\ \mbox{Voltage at All Other Pins} & -0.3 \mbox{V to } \mbox{V}_{DD} + 0.3 \mbox{V} \\ \mbox{Operating Temperature Range} & -40 \mbox{°C to } +85 \mbox{°C} \\ \end{array}$

$\begin{array}{ll} \mbox{Storage Temperature} & -65^{\circ}\mbox{C to } +150^{\circ}\mbox{C} \\ \mbox{Lead Temperature} & \\ \mbox{(Soldering, 10 seconds)} & 300^{\circ}\mbox{C} \\ \end{array}$

## **DC Electrical Characteristics**

GND = 0V,  $V_{DD}$  = 3.0V to 5.5V,  $T_A$  =  $-40^{\circ}C$  to  $+85^{\circ}C$  (depends on display characteristics)

| Parameter                                            | Conditions            | Min                             | Max                                        | Units  |

|------------------------------------------------------|-----------------------|---------------------------------|--------------------------------------------|--------|

| Power Supply Voltage, V <sub>DD</sub>                |                       | 3.0                             | 5.5                                        | Volts  |

| Power Supply Current, I <sub>DD</sub> (Note 1)       | V <sub>DD</sub> =5.5V |                                 | 300                                        | μΑ     |

|                                                      | V <sub>DD</sub> =3V   |                                 | 120                                        | μΑ     |

| Input Levels                                         |                       |                                 |                                            |        |

| DI, SK, CS                                           |                       |                                 |                                            |        |

| V <sub>IL</sub>                                      |                       | 0.71/                           | 0.8                                        | Volts  |

| V <sub>IH</sub>                                      |                       | 0.7 V <sub>DD</sub>             | 9.5                                        | Volts  |

| BPA (as Osc. In)                                     |                       |                                 |                                            | .,,,,, |

| V <sub>IL</sub>                                      |                       | .,                              | 0.6                                        | Volts  |

| V <sub>IH</sub>                                      |                       | V <sub>DD</sub> -0.6            | V <sub>DD</sub>                            | Volts  |

| Output Levels, BPC (as Osc. Out)                     |                       |                                 |                                            |        |

| V <sub>OL</sub>                                      |                       |                                 | 0.4                                        | Volts  |

| V <sub>OH</sub>                                      |                       | V <sub>DD</sub> -0.4            | V <sub>DD</sub>                            | Volts  |

| Backplane Outputs (BPA, BPB, BPC)                    |                       |                                 |                                            |        |

| V <sub>BPA, BPB, BPC</sub> ON                        | During                | $V_{DD}-\Delta V$               | V <sub>DD</sub>                            | Volts  |

| V <sub>BPA, BPB, BPC</sub> OFF                       | BP+ Time              | $^{1}/_{3}$ $V_{DD} - \Delta V$ | 1/ <sub>3</sub> V <sub>DD</sub> + ΔV       | Volts  |

| V <sub>BPA, BPB, BPC</sub> ON                        | During                | 0                               | ΔV                                         | Volts  |

| V <sub>BPA, BPB, BPC</sub> OFF                       | BP- Time              | $^{2}/_{3}$ $V_{DD} - \Delta V$ | $^{2}/_{3}$ $V_{DD} + \Delta V$            | Volts  |

| Segment Outputs (SA <sub>1</sub> ∼ SA <sub>4</sub> ) |                       |                                 |                                            |        |

| V <sub>SEG</sub> ON                                  | During                | 0                               | ΔV                                         | Volts  |

| V <sub>SEG</sub> OFF                                 | BP+ Time              | $^{2}/_{3}$ $V_{DD} - \Delta V$ | $^{2}/_{3}$ $V_{DD} + \Delta V$            | Volts  |

| V <sub>SEG</sub> ON                                  | During                | $V_{DD}-\Delta V$               | V <sub>DD</sub>                            | Volts  |

| V <sub>SEG</sub> OFF                                 | BP- Time              | $^{1}/_{3}V_{DD}-\Delta V$      | $\frac{1}{3}$ V <sub>DD</sub> + $\Delta$ V | Volts  |

| Internal Oscillator Frequency                        |                       | 15                              | 80                                         | kHz    |

| Frame Time (Int. Osc. ÷ 192)                         |                       | 2.4                             | 12.8                                       | ms     |

| Scan Frequency (1/T <sub>SCAN</sub> )                |                       | 39                              | 208                                        | Hz     |

| SK Clock Frequency                                   |                       | 4                               | 250                                        | kHz    |

| SK Width                                             |                       | 1.7                             |                                            | μs     |

| DI                                                   |                       |                                 |                                            |        |

| Data Setup, t <sub>SETUP</sub>                       |                       | 1.0                             |                                            | μs     |

| Data Hold, t <sub>HOLD</sub>                         |                       | 100                             |                                            | ns     |

| <u>CS</u>                                            |                       |                                 |                                            |        |

| <sup>t</sup> SETUP                                   |                       | 1.0                             |                                            | μs     |

| <sup>t</sup> HOLD                                    |                       | 1.0                             |                                            | μs     |

| Output Loading Capacitance                           |                       |                                 | 100                                        | pF     |

3

Note 1: Power supply current is measured in stand-alone mode with all outputs open and all inputs at  $V_{DD}$ . Note 2:  $\Delta V = 0.05 \ V_{DD}$ .

FIGURE 3. Serial Load Timing Diagram

TL/DD/6932-3

TL/DD/6932-4

TL/DD/6932-5

FIGURE 4. Backplane and Segment Waveforms

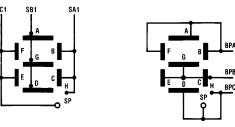

FIGURE 5. Typical Display Internal Connections Epson LD-370

4

## **Functional Description**

The COP472-3 drives 36 bits of display information organized as twelve segments and three backplanes. The COP472-3 requires 40 information bits: 36 data and 4 control. The function of each control bit is described below. Display information format is a function of the LCD interconnections. A typical segment/backplane configuration is illustrated in *Figure 5*, with this configuration the COP472-3 will drive 4 digits of 9 segments.

To adapt the COP472-3 to any LCD display configuration, the segment/backplane multiplex scheme is illustrated in Table I

Two or more COP472-3 chips can be cascaded to drive additional segments. There is no limit to the number of COP472-3's that can be used as long as the output loading capacitance does not exceed specification.

TABLE I. COP472-3 Segment/Backplane Multiplex Scheme

|            | Multiplex Scheme      |                            |          |  |  |

|------------|-----------------------|----------------------------|----------|--|--|

| Bit Number | Segment,<br>Backplane | Data to<br>Numeric Display |          |  |  |

| 1          | SA1, BPC              | SH                         |          |  |  |

| 2          | SB1, BPB              | SG                         |          |  |  |

| 3          | SC1, BPA              | SF                         |          |  |  |

| 4          | SC1, BPB              | SE                         | 5        |  |  |

| 5          | SB1, BPC              | SD                         | Digit 1  |  |  |

| 6          | SA1, BPB              | SC                         |          |  |  |

| 7          | SA1, BPA              | SB                         |          |  |  |

| 8          | SB1, BPA              | SA                         |          |  |  |

| 9          | SA2, BPC              | SH                         |          |  |  |

| 10         | SB2, BPB              | SG                         |          |  |  |

| 11         | SC2, BPA              | SF                         |          |  |  |

| 12         | SC2, BPB              | SE                         | Digit 2  |  |  |

| 13         | SB2, BPC              | SD                         | Digit L  |  |  |

| 14         | SA2, BPB              | SC                         |          |  |  |

| 15         | SA2, BPA              | SB                         |          |  |  |

| 16         | SB2, BPA              | SA                         |          |  |  |

| 17         | SA3, BPC              | SH                         |          |  |  |

| 18         | SB3, BPB              | SG                         |          |  |  |

| 19         | SC3, BPA              | SF                         |          |  |  |

| 20         | SC3, BPB              | SE                         | Digit 3  |  |  |

| 21         | SB3, BPC              | SD                         | 2.9.0    |  |  |

| 22         | SA3, BPB              | SC                         |          |  |  |

| 23         | SA3, BPA              | SB                         |          |  |  |

| 24         | SB3, BPA              | SA                         |          |  |  |

| 25         | SA4, BPC              | SH                         |          |  |  |

| 26         | SB4, BPB              | SG                         |          |  |  |

| 27         | SC4, BPA              | SF                         |          |  |  |

| 28         | SC4, BPB              | SE                         | Digit 4  |  |  |

| 29         | SB4, BPC              | SD                         | -        |  |  |

| 30<br>21   | SA4, BPB              | SC<br>SB                   |          |  |  |

| 31<br>32   | SA4, BPA<br>SB4, BPA  | SA                         |          |  |  |

|            |                       |                            | District |  |  |

| 33         | SC1, BPC              | SPA                        | Digit 1  |  |  |

| 34         | SC2, BPC              | SP2                        | Digit 2  |  |  |

| 35<br>36   | SC3, BPC              | SP3                        | Digit 3  |  |  |

| 36<br>37   | SC4, BPC not used     | SP4                        | Digit 4  |  |  |

| 37<br>38   | not used<br>Q6        |                            |          |  |  |

| 38<br>39   | Q6<br>Q7              |                            |          |  |  |

| 40         | SYNC                  |                            |          |  |  |

| 40         | STNO                  |                            |          |  |  |

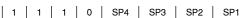

#### **SEGMENT DATA BITS**

Data is loaded in serially, in sets of eight bits. Each set of segment data is in the following format:

| SA | SB | SC | SD | SE | SF | SG | SH |

|----|----|----|----|----|----|----|----|

Data is shifted into an eight bit shift register. The first bit of the data is for segment H, digit 1. The eighth bit is segment A, digit 1. A set of eight bits is shifted in and then loaded into the digit one latches. The second set of 8 bits is loaded into digit two latches. The third set into digit three latches, and the fourth set is loaded into digit four latches.

#### **CONTROL BITS**

The fifth set of 8 data bits contains special segment data and control data in the following format:

|  | ١ | SYNC | Q7 | Q6 | Х | SP4 | SP3 | SP2 | SP1 |

|--|---|------|----|----|---|-----|-----|-----|-----|

|--|---|------|----|----|---|-----|-----|-----|-----|

The first four bits shifted in contain the special character segment data. The fifth bit is not used. The sixth and seventh bits program the COP472-3 as a stand alone LCD driver or as a master or slave for cascading COP472-3's. BPC of the master is connected to BPA of each slave. The following table summarizes the function of bits six and seven:

| Q7 | Q6 | Function    | <b>BPC Output</b> | <b>BPA Output</b> |

|----|----|-------------|-------------------|-------------------|

| 1  | 1  | Slave       | Backplane         | Oscillator        |

|    |    |             | Output            | Input             |

| 0  | 1  | Stand Alone | Backplane         | Backplane         |

|    |    |             | Output            | Output            |

| 1  | 0  | Not Used    | Internal          | Oscillator        |

|    |    |             | Osc. Output       | Input             |

| 0  | 0  | Master      | Internal          | Backplane         |

|    |    |             | Osc. Output       | Output            |

The eighth bit is used to synchronize two COP472-3's to drive an  $81/\!\!/_2\text{-}\text{digit}$  display.

#### LOADING SEQUENCE TO DRIVE A 41/2-DIGIT DISPLAY

Steps:

- 1. Turn  $\overline{\text{CE}}$  low.

- 2. Clock in 8 bits of data for digit 1.

- 3. Clock in 8 bits of data for digit 2.

- 4. Clock in 8 bits of data for digit 3.

- 5. Clock in 8 bits of data for digit 4.

- Clock in 8 bits of data for special segment and control function of BPC and BPA.

0 0 1 1 1 SP4 SP3 SP2 SP1

#### 7. Turn CS high.

Note:  $\overline{CS}$  may be turned high after any step. For example to load only 2 digits of data, do steps 1, 2, 3, and 7.

$\overline{\text{CS}}$  must make a high to low transition before loading data in order to reset internal counters.

# LOADING SEQUENCE TO DRIVE AN 8½-DIGIT DISPLAY

Two or more COP472-3's may be connected together to drive additional segments. An eight digit multiplexed display is shown in *Figure 7*. The following is the loading sequence to drive an eight digit display using two COP472-3's. The right chip is the master and the left the slave.

#### Steps:

- 1. Turn  $\overline{\text{CS}}$  low on both COP472-3's.

- 2. Shift in 32 bits of data for the slave's four digits.

- Shift in 4 bits of special segment data: a zero and three ones.

This synchronizes both the chips and BPA is oscillator input. Both chips are now stopped.

- 4. Turn CS high to both chips.

- 5. Turn CS low to master COP472-3.

- 6. Shift in 32 bits of data for the master's 4 digits.

- 7. Shift in four bits of special segment data, a one and three zeros.

This sets the master COP472-3 to BPA as a normal backplane output and BPC as oscillator output. Now both the chips start and run off the same oscillator.

8. Turn CS high.

The chips are now synchronized and driving 8 digits of display. To load new data simply load each chip separately in the normal manner, keeping the correct status bits to each COP472-3 (0110 or 0001).

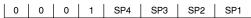

FIGURE 6. System Diagram - 41/2 Digit Display

FIGURE 7. System Diagram - 8½ Digit Display

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

Europe Fax: +49 (0) 180-530 85 86 Email: europe.support@nsc.com Deutsch Tel: +49 (0) 180-530 85 85 English Tel: +49 (0) 180-532 78 32 Français Tel: +49 (0) 180-532 93 85 Italiano Tel: +49 (0) 180-534 16 80

**National Semiconductor**

National Semiconductor Hong Kong Ltd. 13th Floor, Straight Block, Ocean Centre, 5 Canton Rd. Tsimshatsui, Kowloon Hong Kong Tel: (652) 2737-1600 Fax: (652) 2736-9960 National Semiconductor Japan Ltd. Tel: 81-043-299-2308 Fax: 81-043-299-2408

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.