# Timers, Counters, and Display Drivers

Timers

diginal light

gest over enter

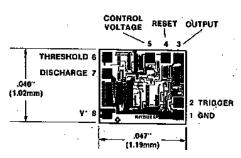

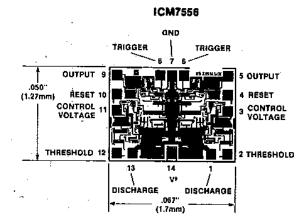

ICM7240/50/60 6-116 ICM7242 6-127 ICM7555 6-155 ICM7556 6-155

Counters

ICM7208 6-7 ICM7216 6-24 ICM7217/27 6-39 ICM7224/25 6-64 ICM7226 6-72 ICM7236 6-110 **Counter Timebase**

ICM7207/A 6-3

**Display Drivers**

ICM7211/12 6-14 ICM7218 6-55 ICM7231-34 6-84 ICM7235 6-104 ICM7243 6-133 ICM7281 6-143

Downloaded from Elcodis.com electronic components distributor

and the second of the second o

6

AND THE

9349

| Counters, | <b>Timers</b> | and | Display | Drivere  |

|-----------|---------------|-----|---------|----------|

|           |               |     | P J     | PILITEIS |

| Part Number                | Circuit Description                                                                                                                                         | Package                                         | Crystal Frequency | Dutant                                                                                                             |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------|

| ICM7207<br>ICM7207A        | Frequency counter timebase.                                                                                                                                 | 14-Pin DIP                                      | 6.5536 MHz        | 0.01, 0.1, or 1-second count window plus                                                                           |

| ICM7208                    | 7-digit unit counter. With addition of 7207 the                                                                                                             | 14-Pin DIP<br>28-Pin DIP                        | 5.2488 MHz        | Store, reset and MUX.                                                                                              |

|                            | circuit becomes a complete timer-frequency counter.                                                                                                         | -                                               |                   | LED display drive                                                                                                  |

| ICM7211<br>ICM7212         | Four-digit dispłay decoder drivers; ICM7211 is<br>LCD; ICM7212 is LED; Non-multiplexed for low<br>noise, BCD input, decoded display drive oetput.           | 40-Pin DIP (plastic)                            | <del>-</del>      | Four-digit, seven-segment direct display<br>drive; LED or ECO                                                      |

| ICM7216<br>ICM7226         | Eight-digit universal counter measures frequency,<br>period, frequency ratio, time interval, units;<br>on-board time base.                                  | 28-Pin DIP<br>40-Pin DIP<br>(Cerdip or plastic) | t or 10 MHz       | Eight-digit-common anode or common cathode direct LED drive: BCD output                                            |

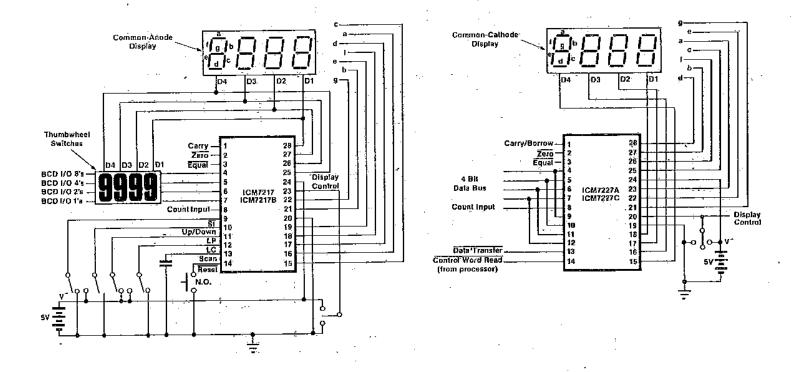

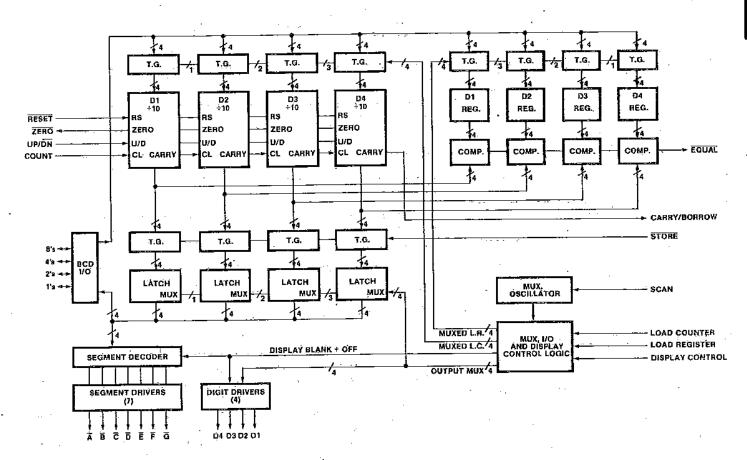

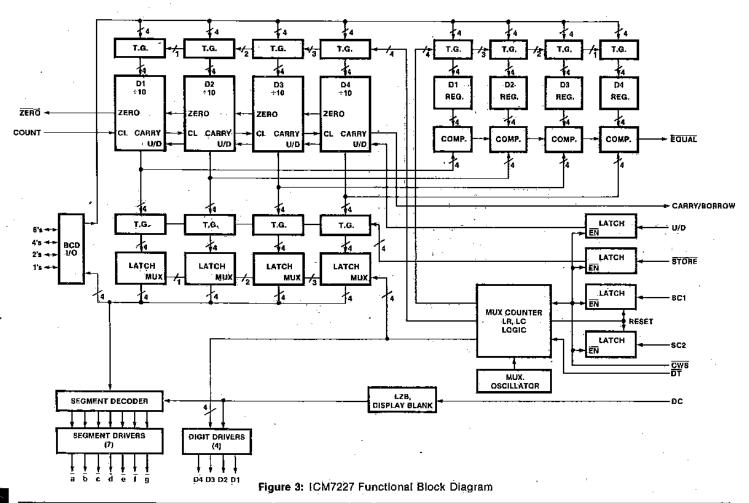

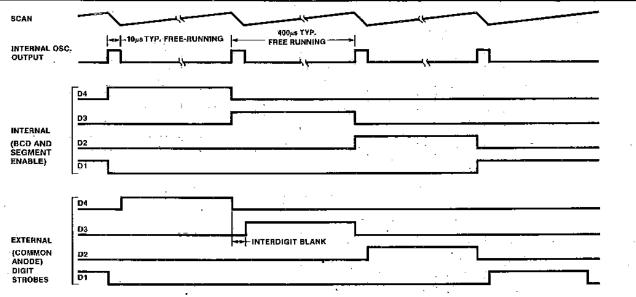

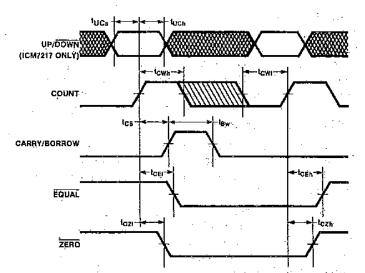

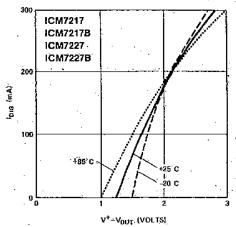

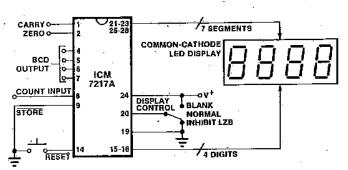

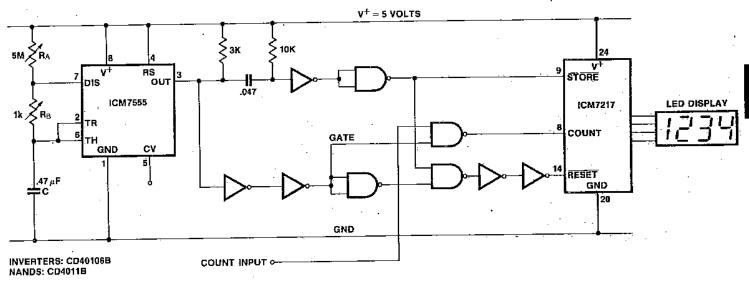

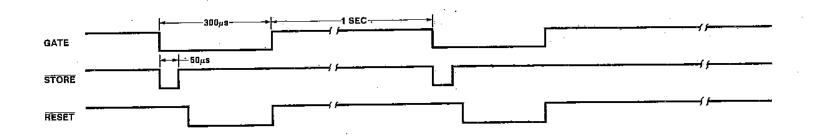

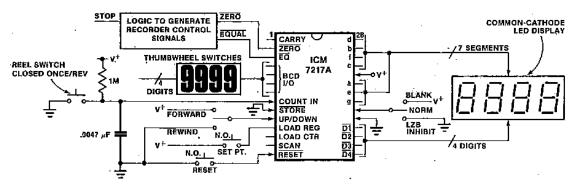

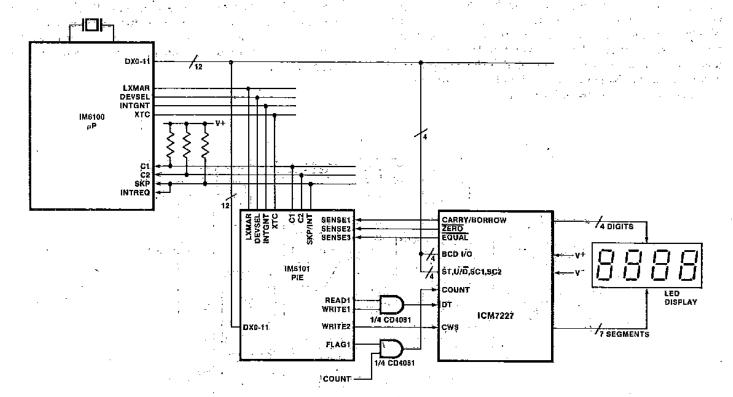

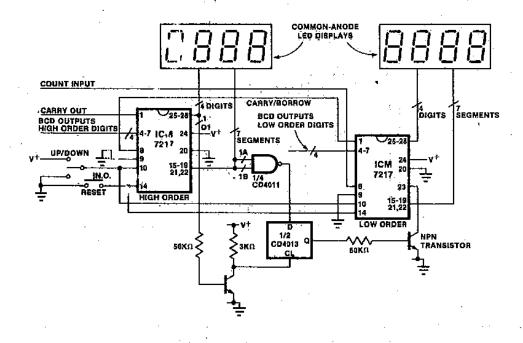

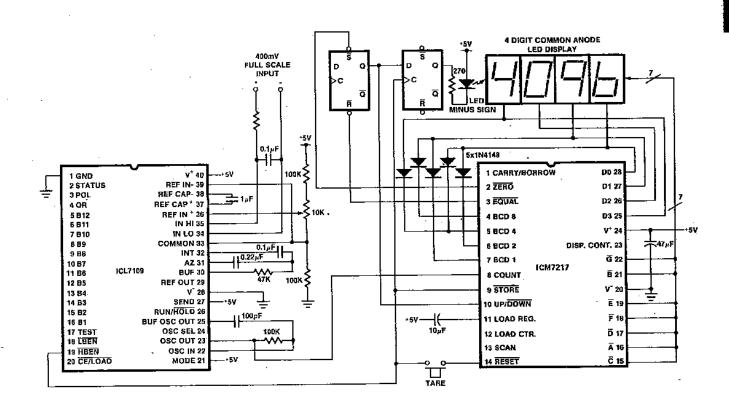

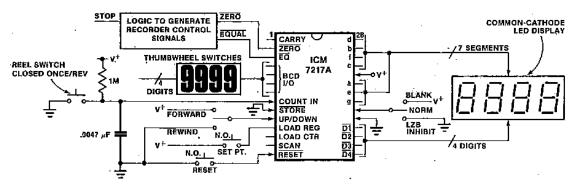

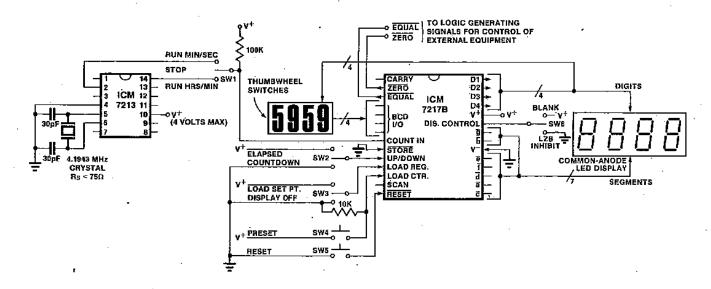

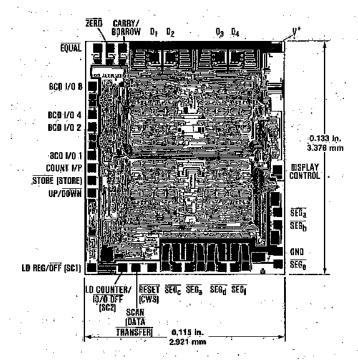

| ICM7217<br>ICM7227         | Four-digit CMOS up/down counter; presettable<br>start/count and compare register; for hard-<br>wired or microprocessor control applications;<br>cascadable. | 28-Pin Cerdip<br>or plastic                     | -<br>-            | Four-digit, seven-segment common anode<br>or common cathode direct LED display<br>drive; equal, zero, carry/borrow |

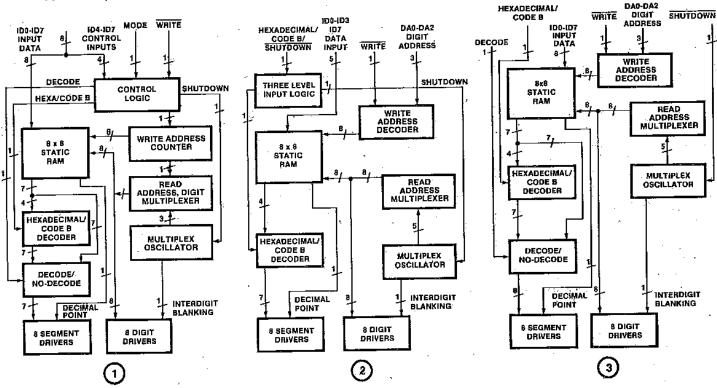

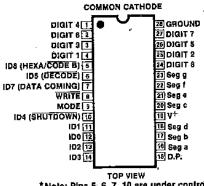

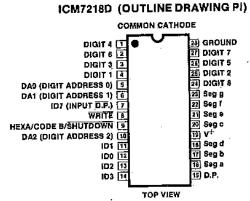

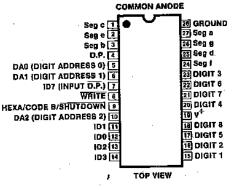

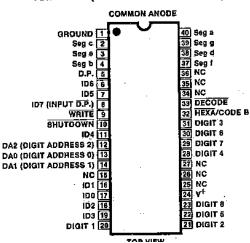

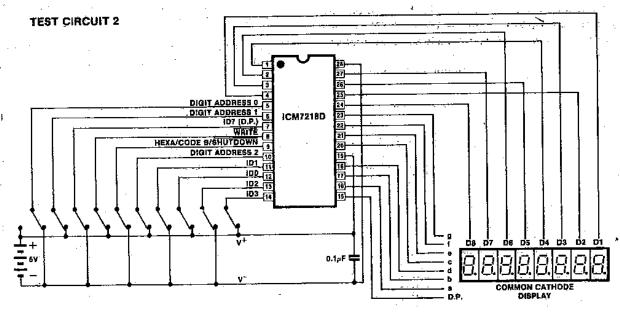

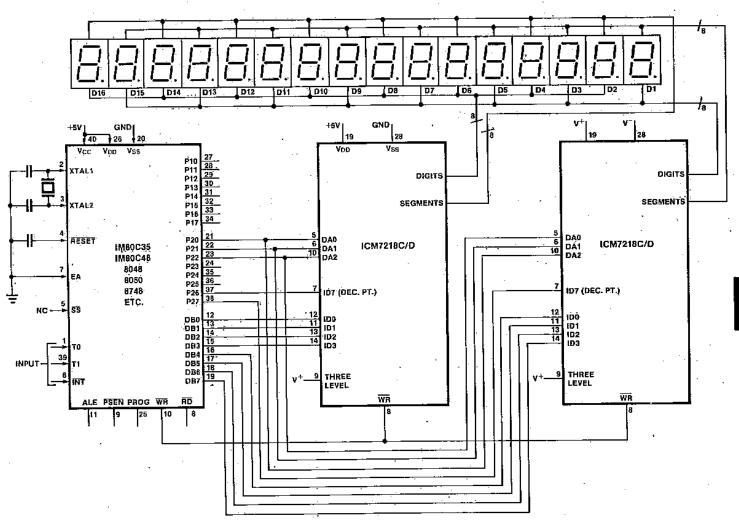

| ICM7218A/D<br>ICM7218E     | LED display driver system with 8x8 memory: numeric or dot (1 of 64) decoding; microprocessor compatible.                                                    | 28-Pin DIP<br>40-Pin DIP<br>(Cerdip or plastic) | _                 | Eight-digit, seven-segment plus decimal point; common cathode or common anode                                      |

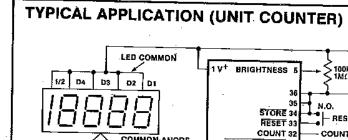

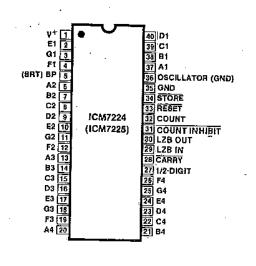

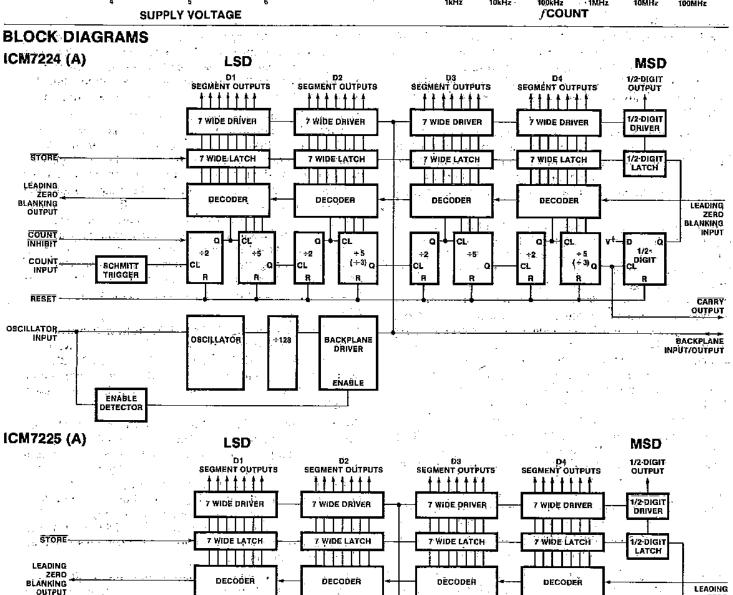

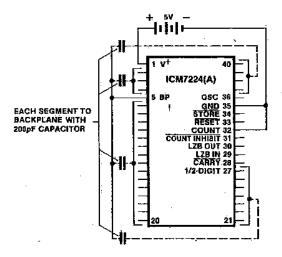

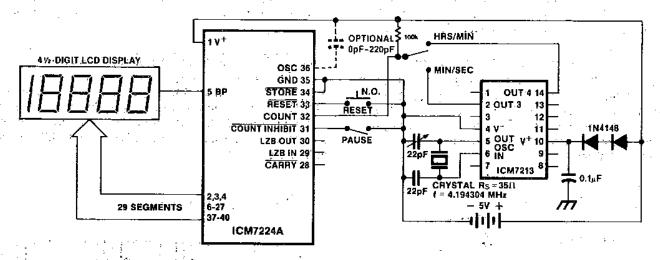

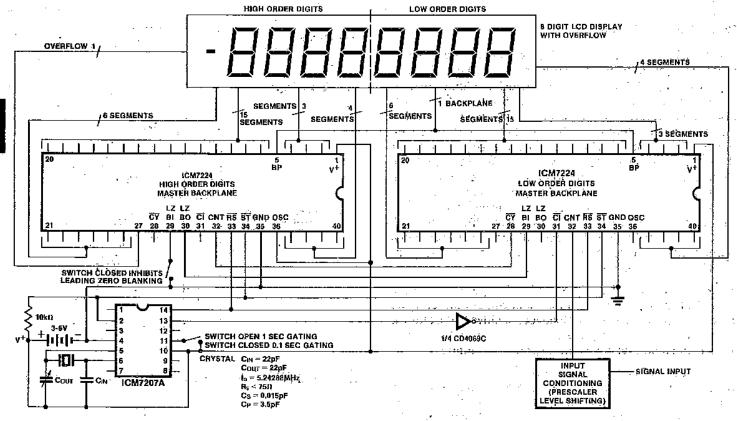

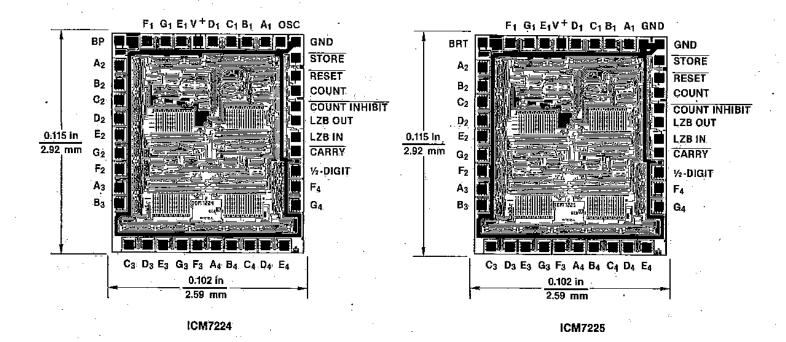

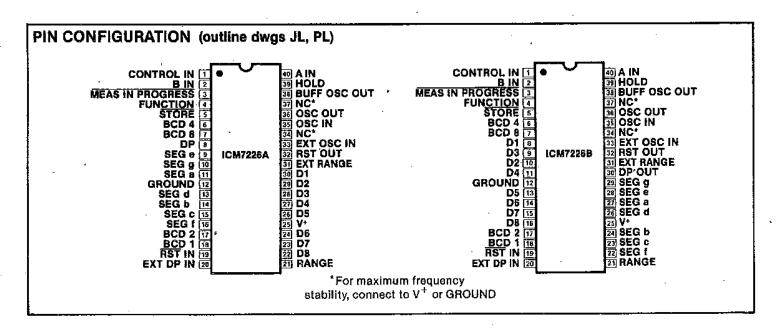

| ICM7224<br>ICM7225         | 4%-digit high speed counter/decoder/driver;<br>25 MHz typ; ICM7224 is LCD, ICM7225 is LED;<br>direct display drive, cascadable.                             | 40-Pin DIP<br>(plastic)                         | -                 | 4½-digit seven-segment direct display driver: LED or LCD                                                           |

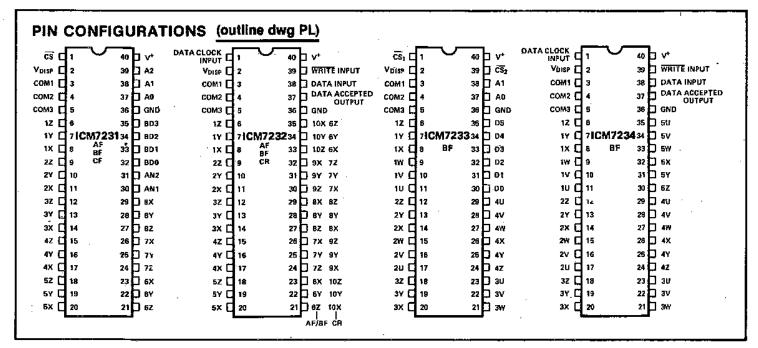

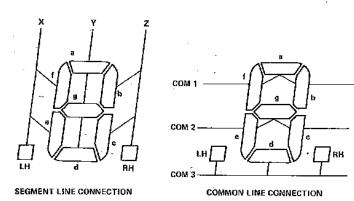

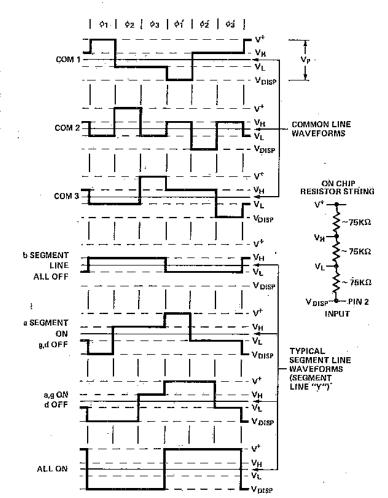

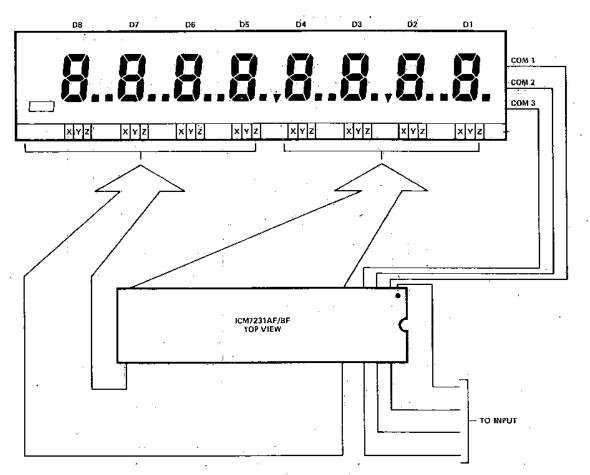

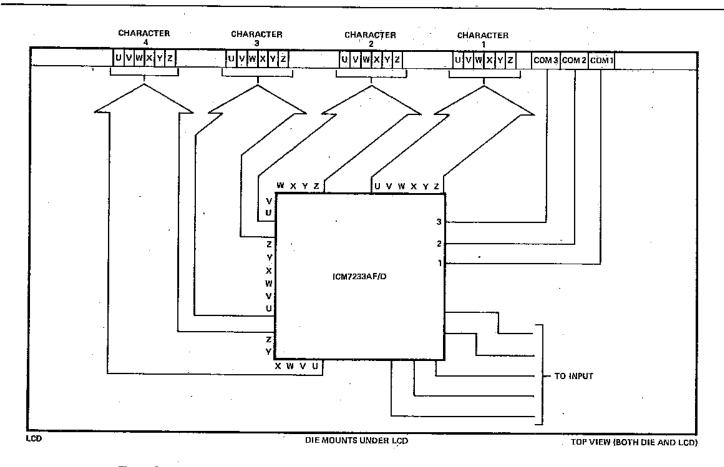

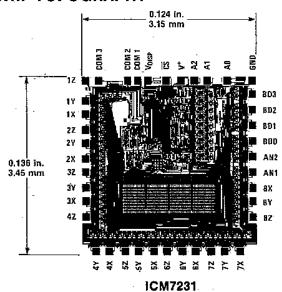

| ICM7231                    | 8-digit CMOS multiplexed LCD driver.<br>Parallel input                                                                                                      | 40-Pin DIP (plastic)                            | <del>-</del>      | Eight-digit, seven-segment-plus two flags                                                                          |

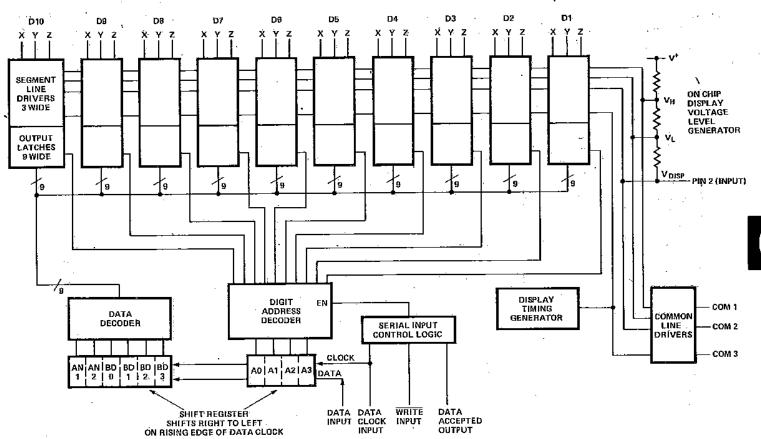

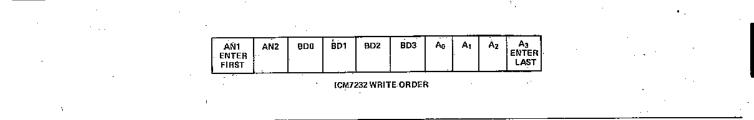

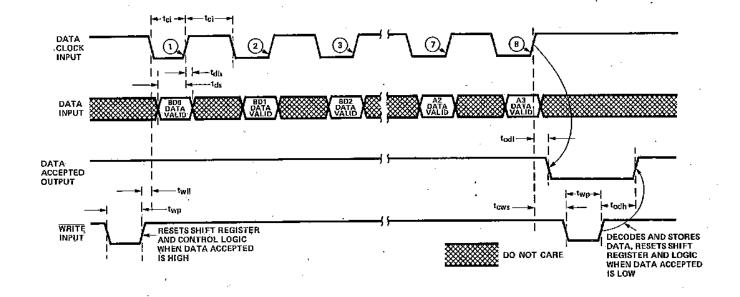

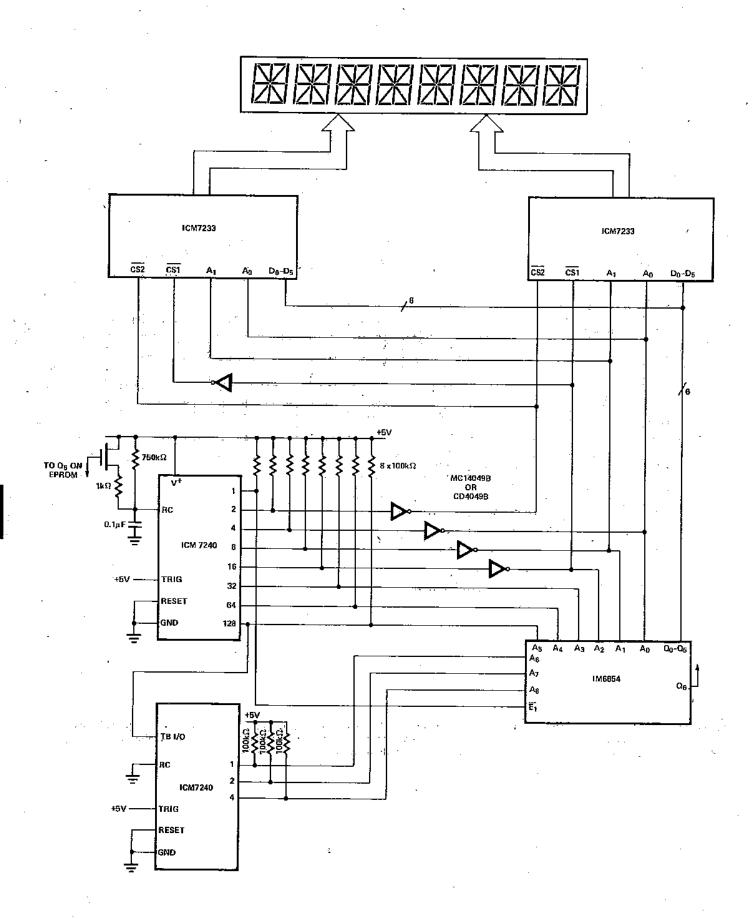

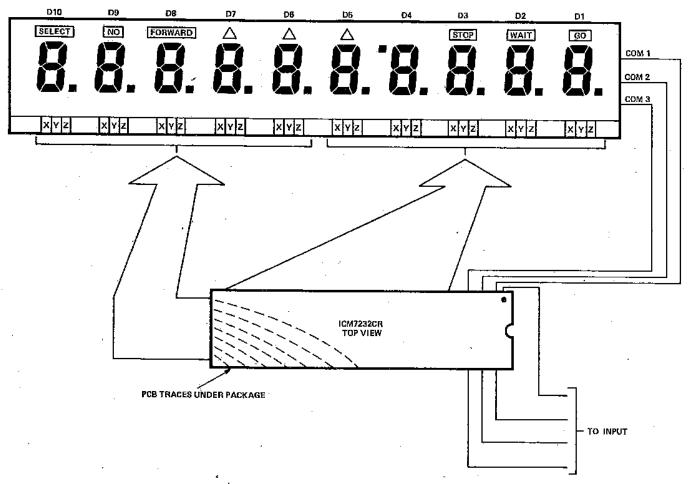

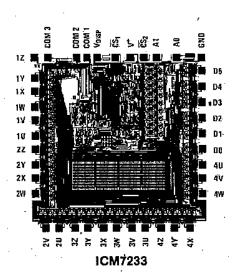

| ICM7232                    | 10%-digit CMOS mulliplexed LCD driver.<br>Serial input.                                                                                                     | 40-Pin DFP (plastic)                            | _                 | 10%-digit, seven-segment plus two flans                                                                            |

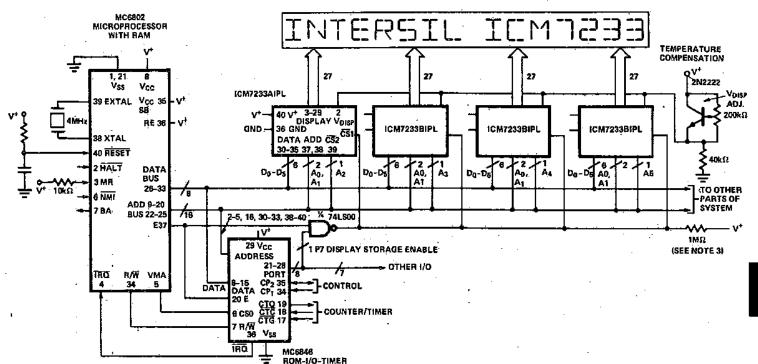

| ICM7233                    | 4-character CMOS multiplexed LCD driver,<br>Parallel alphanumeric (6-bit ASCit) input.                                                                      | 40-Pin DIP (plastic)                            | _                 | per digit Four-character, 16-segment plus colon                                                                    |

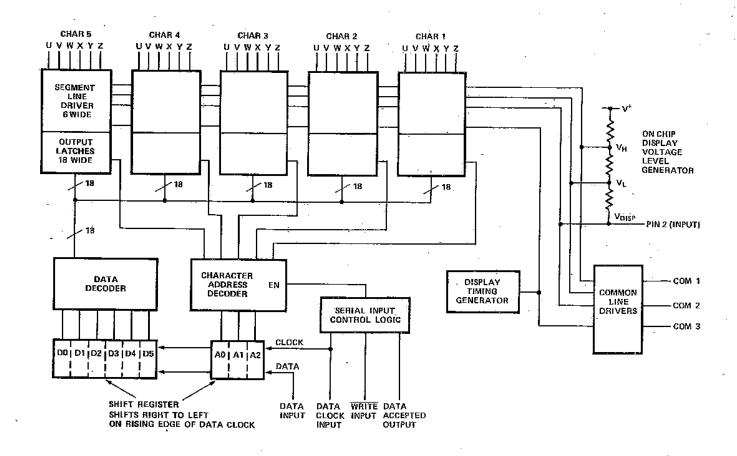

| ICM7234                    | 5-character CMOS multiplexed LCD driver,<br>Serial alphanumeric (6-bit ASCII) input.                                                                        | 40-Pin DIP (plastic)                            | _                 | Five-character, 16-segment plus colon                                                                              |

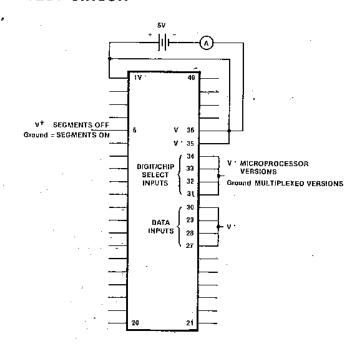

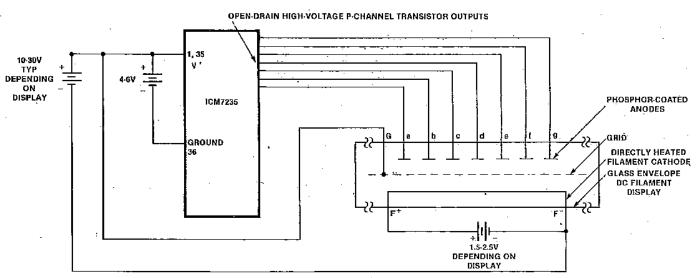

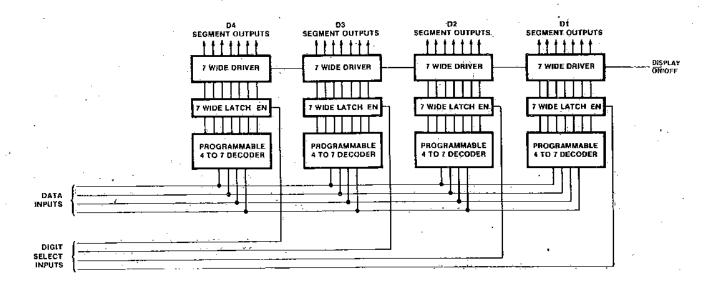

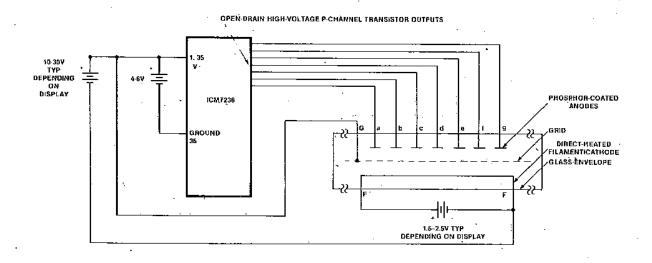

| ICM7235/A                  | 4-digit CMOS decoder/driver for direct drive<br>vacuum fluorescent displays. BCD input.                                                                     | 40-Pin DIP (plastic)                            | _                 | Four-digit, seven-segment, vacuum                                                                                  |

| ICM7235M/AM                | Same as above but microprocessor compatible.                                                                                                                |                                                 |                   | fluorescent display drive: either HEX or CODE B                                                                    |

| ICM7236                    | 4%-digit high speed CMOS counter/decoder/driver<br>for vacuum fluorescent displays: 25 MHz typ.<br>counting speed.                                          | 40-Pin DIP (plastic)                            | _                 | 4½-digit, seven-segment, vacuum<br>Iliiorescent display drive                                                      |

| CM7236A                    | Same as above but counting to 15959.                                                                                                                        | 40-Pin OIP (plastic)                            |                   | 4½-digit, seven-segment, vacuum                                                                                    |

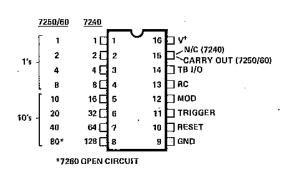

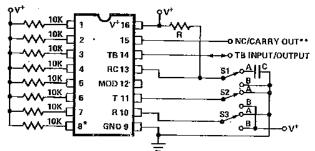

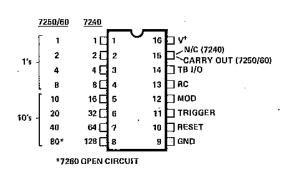

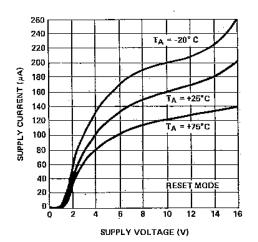

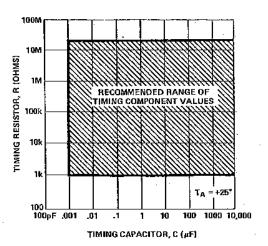

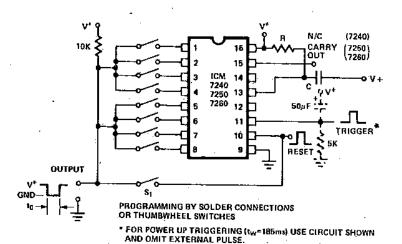

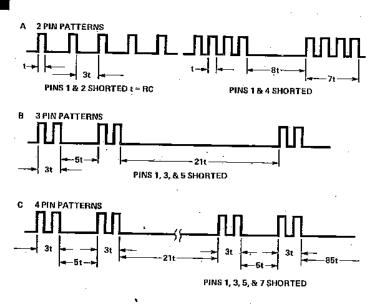

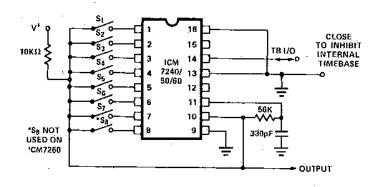

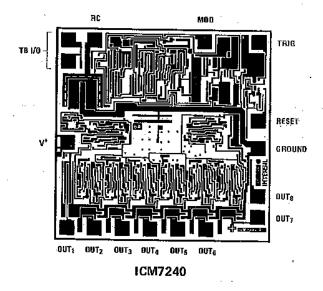

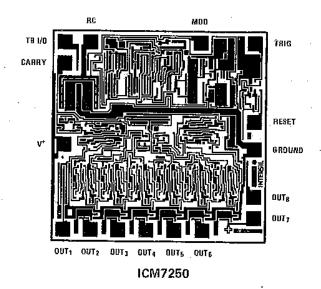

| CM7240<br>CM7250<br>CM7260 | Programmable CMOS counter/timers using external RC time base. Programmable from µs to years.                                                                | 16-Pin DIP                                      | External          | fluorescent display drive<br>Timed output                                                                          |

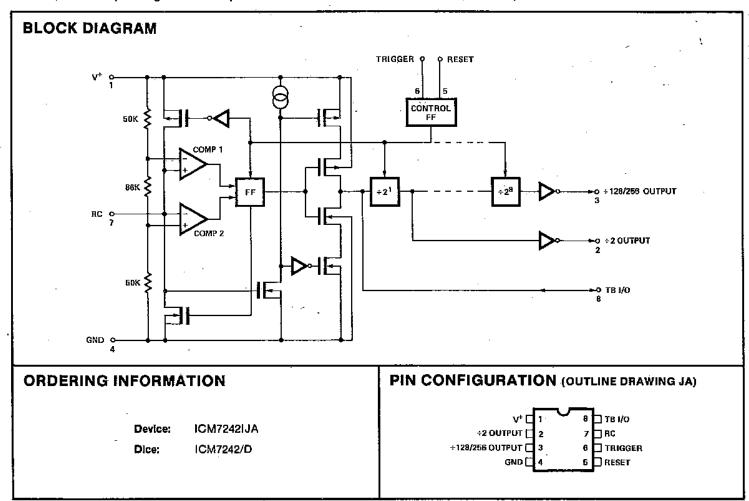

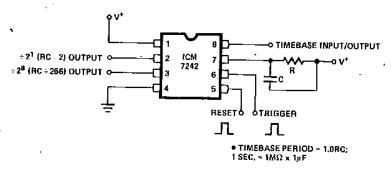

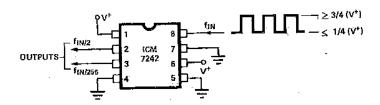

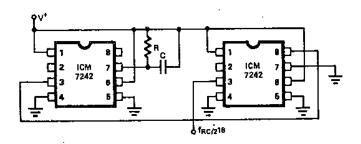

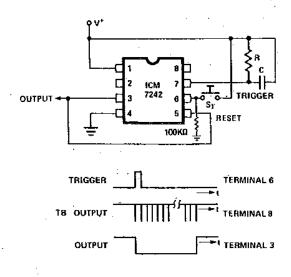

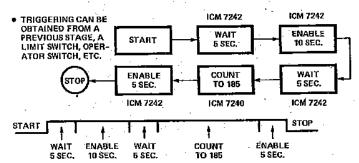

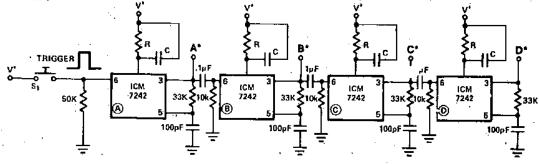

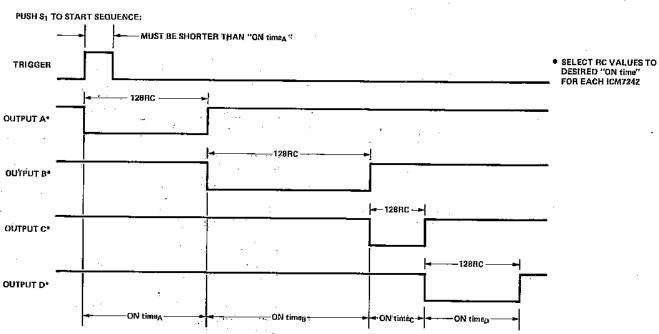

| CM7242                     | Fixed CMOS counter/timer. Uses external RC time base; sequence timing from $\mu$ s to minutes.                                                              | 8-Pin DIP                                       | External          | Timed output                                                                                                       |

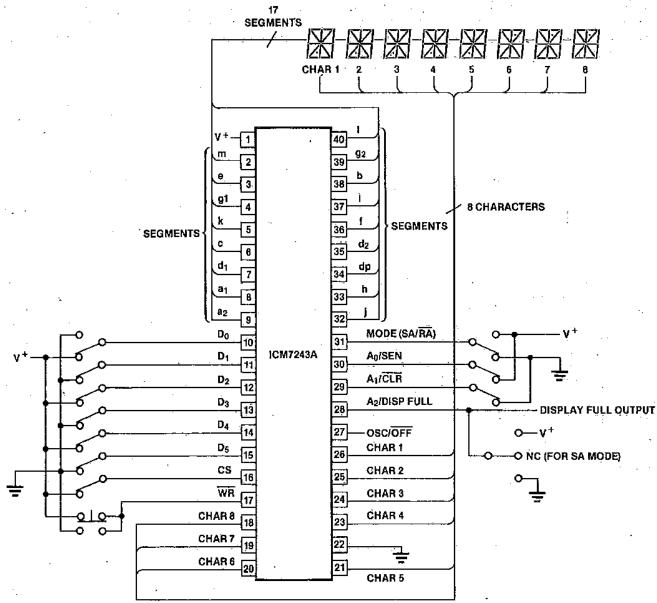

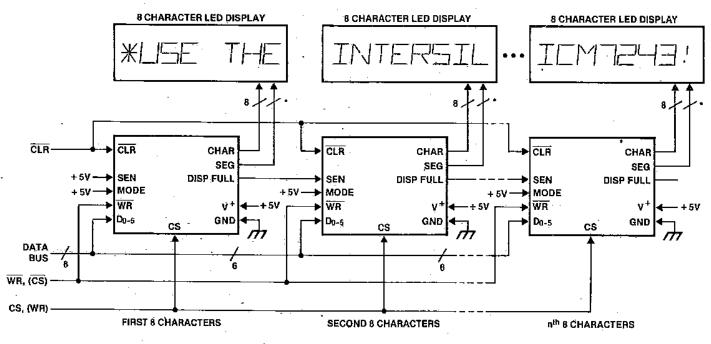

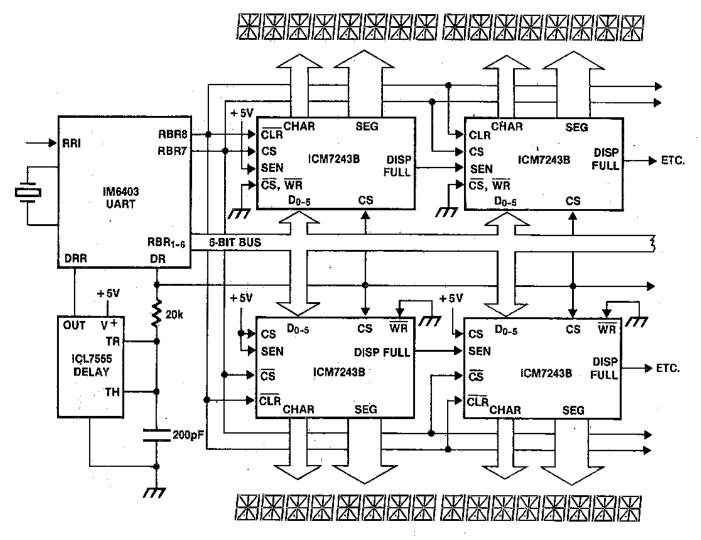

| CM7243                     | 8-character multiplexed LED display driver with alphanumeric (6-bit ASCII) input.                                                                           | 40-Pin Cerdip                                   |                   | Eight-character, 14/16-segment common                                                                              |

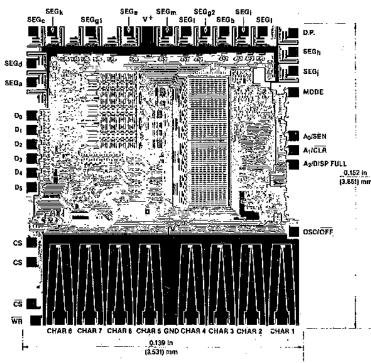

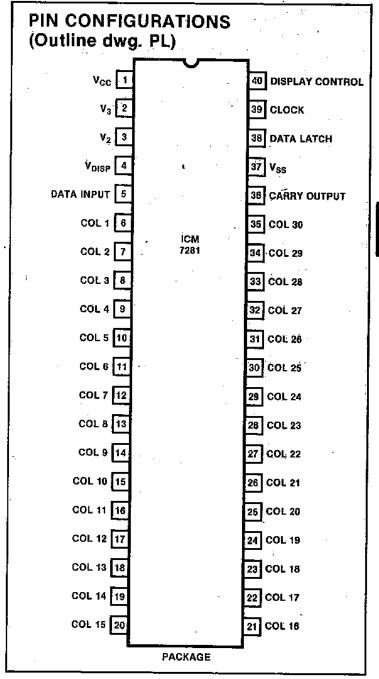

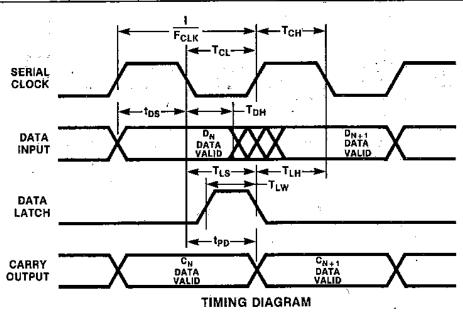

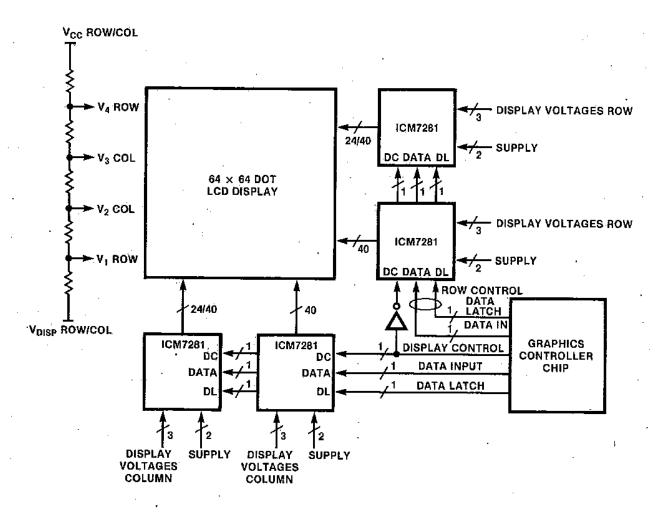

| CM7281                     | LCD Oot Matrix Column Driver                                                                                                                                | 40-Pia DID                                      | •                 | camode aspnanumeric LEO display drive                                                                              |

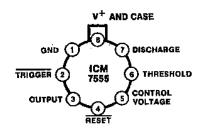

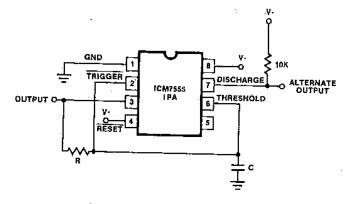

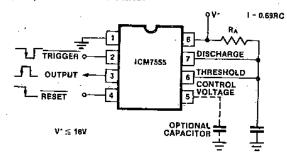

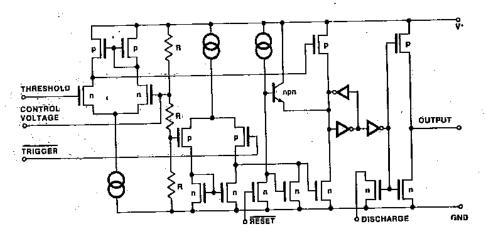

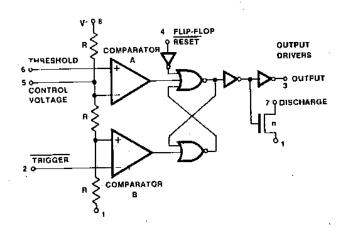

| CM7555<br>CM7556           | Single or dual CMOS version of industry-standard<br>555 timer; 80 µA.lyp. supply current; 500 kHz<br>guaranteed; 2-18V power supply.                        | 40-Pin DIP<br>8-Pin DIP<br>14-Pin DIP           |                   | Up to 256 x 256 dots                                                                                               |

# ICM7207/A **CMOS Oscillator Controller**

### **FEATURES**

- Stable HF oscillator

- Low power dissipation ≤ 5mW with 5 volt supply

- Counter chain has outputs at ÷ 2<sup>12</sup> and ÷ 2<sup>n</sup> or  $\div$  (2<sup>n</sup> x 10); n = 17 for 7207, and 20 for 7207A

- Low impedance output drivers ≤100 ohms

- Count windows of 10/100ms (7207 with 6.5536MHz crystal) or 0.1/1 sec. (7207A with 5.24288MHz crystal)

### **APPLICATIONS**

- System timebases

- Oscilloscope calibration generators

- Marker generator strobes

- Frequency counter controllers

### DESCRIPTION

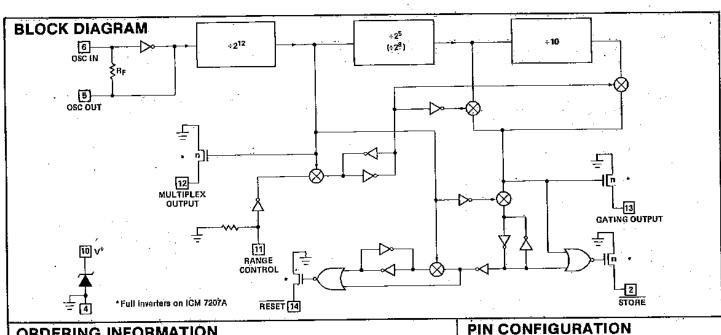

The ICM7207/A consist of a high stability oscillator and frequency divider providing 4 control outputs suitable for frequency counter timebases. Specifically, when used as a frequency counter timebase in conjunction with the ICM7208 frequency counter, the four outputs provide the gating signals for the count window, store function, reset function and multiplex frequency reference. Additionally, the duration of the count window may be changed by a factor of 10 to provide a 2 decade range counting system,

The normal operating voltage of the ICM7207/A is 5 volts at which the typical dissipation is less than 2mW using an oscillator frequency of 6.5536MHz (5.24288MHz).

In the 7207/A the GATING output, RESET, and the MULTIPLEX output provide both pull up and pull down, eliminating the need for 3 external resistors; although, buffering must be provided if interfacing with T2L is required.

### ORDERING INFORMATION

| PART     | PACKAGE                       | ORDER NUMBER                                |

|----------|-------------------------------|---------------------------------------------|

| ICM7207  | 14-Pin DIP<br>DICE<br>EV/Kit* | ICM7207IPD<br>ICM7207/D<br>ICM7207EV/KIt    |

| ICM7207A | 14-Pin DIP<br>DICE<br>EV/Kit* | ICM7207AIPD<br>ICM7207A/D<br>ICM7207AEV/KIt |

Temperature Range on packaged parts is ~ 20°C to +85°C

\*These EV/Kits contain just the IC and the corresponding crystal. The ICM7207A is also used in the 41/2 Digit Counter/Driver kits, the ICM7224 EV/Kit, ICM7225 EV/Kit, and ICM7236 EV/Kit, which include several ICs, a crystal, PC board, and some passive components.

#### RST GATING OUT stő 🗆 13 ] мих оит ICM 7207 RANGE CONTROL GROUND [ OSC OUT □ N/C OSC IN. . 9 N/C

(outline dwg PD)

### **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage                                                                   |

|----------------------------------------------------------------------------------|

| Output Currents                                                                  |

| Fower Dissipation @ 25°C Note 1                                                  |

| Operating Temperature Range20°C to +85°C Storage Temperature Range55°C to +125°C |

| NOTE 1: Derate by 2mW/°C above 25°C.                                             |

Absolute maximum ratings refer to values which if exceeded may permanently change or destroy the device. Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions above those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# TYPICAL OPERATING CHARACTERISTICS

TEST CONDITIONS: fosc = 6.5536MHz(7207), 5.24288MHz(7207A), V+ = 5V, T<sub>A</sub> = 25°C, test circuit unless otherwise specified.

| PARAMETER                                 | SYMBOL               | CONDITIONS                            | MIN.        | TYP. | MAX. | UNIT             |

|-------------------------------------------|----------------------|---------------------------------------|-------------|------|------|------------------|

| Operating Voltage Range                   | V+                   | -20°C to +85°C                        | 4           |      | 5.5  | V                |

| Supply Current                            | ļ+                   | All outputs open circuit              | <del></del> | 260  | 1000 |                  |

| Output on Resistances                     | r <sub>dB</sub> (on) | Output current = 5mA All outputs      |             | 50   | 120  | μA<br>Ω          |

| Output Leakage Currents                   | lolk                 | All outputs (STORE only)              | <del></del> |      | 50   | μΑ               |

| (Output Resistance<br>Terminals 12,13,14) | (Rout)               | Output current = 50μA, 7207A          |             |      | 33K  | Ω                |

| Input Pulldown Current                    | lp d                 | Terminal 11 connected to V+           |             | 50   | 200  | μΑ               |

| Input Noise Immunity                      | <del></del>          |                                       | 25          |      | 200  |                  |

| Oscillator Frequency Range                | fosc                 | Note 2                                | 2           |      | 10   | % supply voltage |

| Oscillator Stability                      | f <sub>STAB</sub>    | Cin = Cout = 22pF                     | <u>-</u> -  | 0.2  | 1.0  | MHz              |

| Oscillator Feedback<br>Resistance         | rosc                 | Quartz crystal open circuit<br>Note 3 | 3           | 0.2  | 1.0  | ppm/V<br>MΩ      |

NOTE 2: Dynamic dividers are used in the initial stages of the divider chain. These dividers have a lower frequency of operation determined by transistor sizes, threshold voltages and leakage currents.

NOTE 3: The feedback resistor has a non-linear value determined by the oscillator instantaneous input and output voltage voltages and the supply voltage.

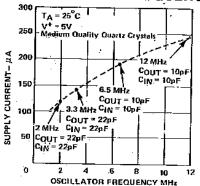

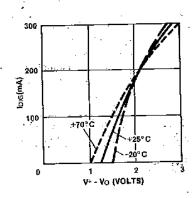

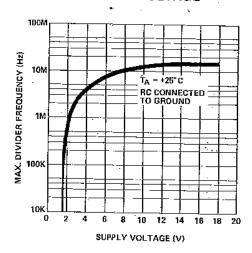

# SUPPLY CURRENT AS A FUNCTION OF OSCILLATOR FREQUENCY

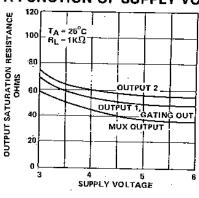

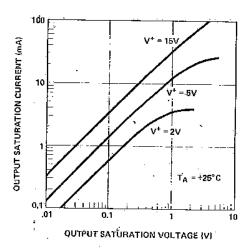

# OUTPUT SATURATION RESISTANCES AS A FUNCTION OF SUPPLY VOLTAGE

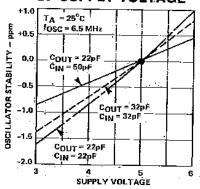

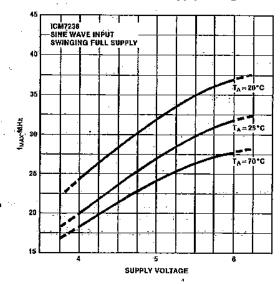

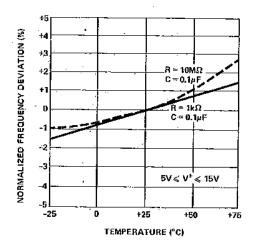

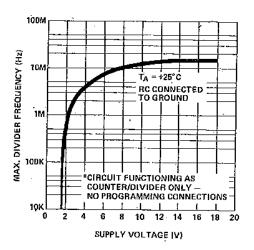

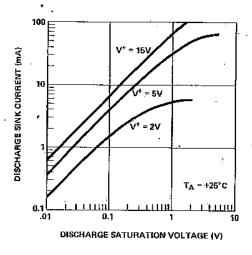

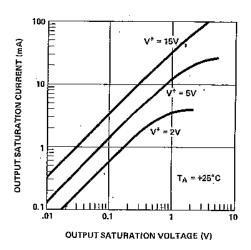

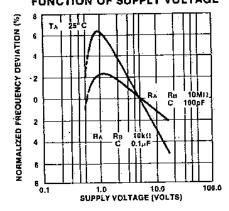

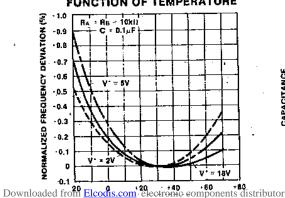

# OSCILLATOR STABILITY AS A FUNCTION OF SUPPLY VOLTAGE

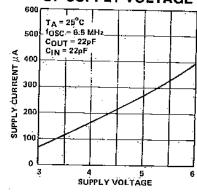

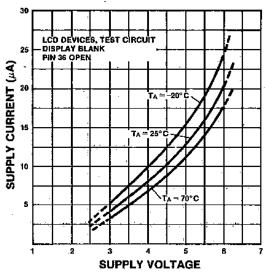

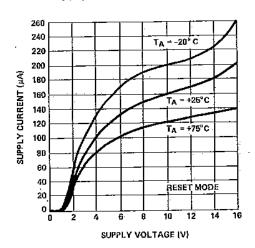

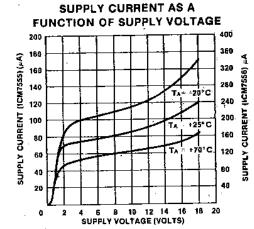

### SUPPLY CURRENT AS A FUNCTION OF SUPPLY VOLTAGE

# ICM7207/A

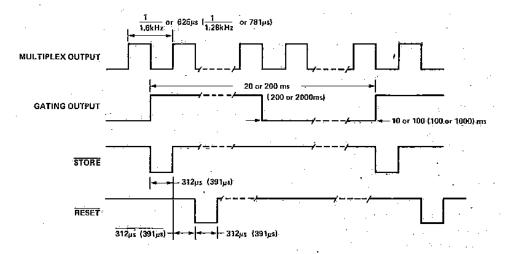

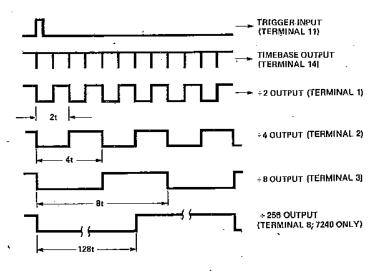

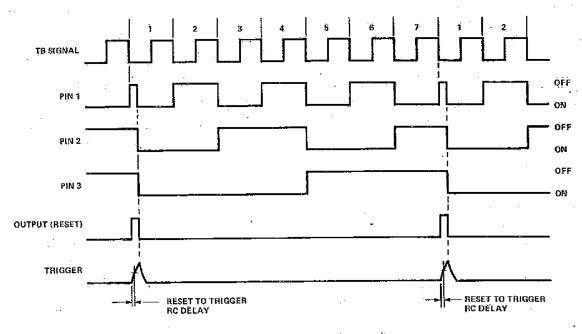

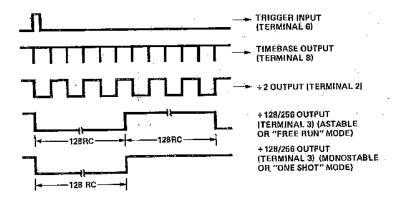

### **OUTPUT TIMING WAVEFORMS 7207 (7207A)**

### Crystal Frequency = 6.5536 (5.24288) MHz

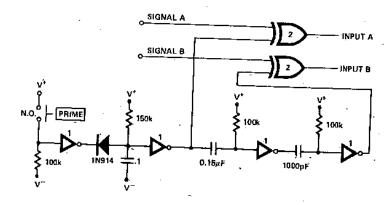

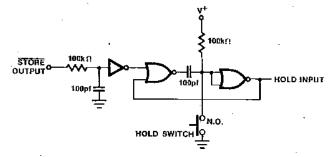

Referring to the test circuit, the crystal oscillator frequency is divided by 2<sup>12</sup> to provide both the multiplex frequency and generate the output pulse widths. The GATING OUTPUT

provides a 50% duty cycle signal whose period depends upon whether the RANGE CONTROL terminal is connected to  $V^{\pm}$  or GROUND (open circuit).

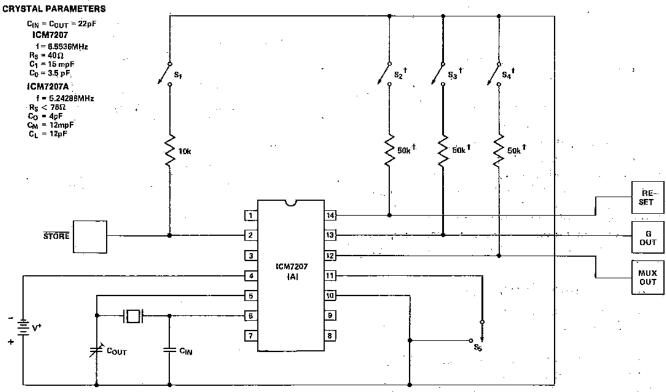

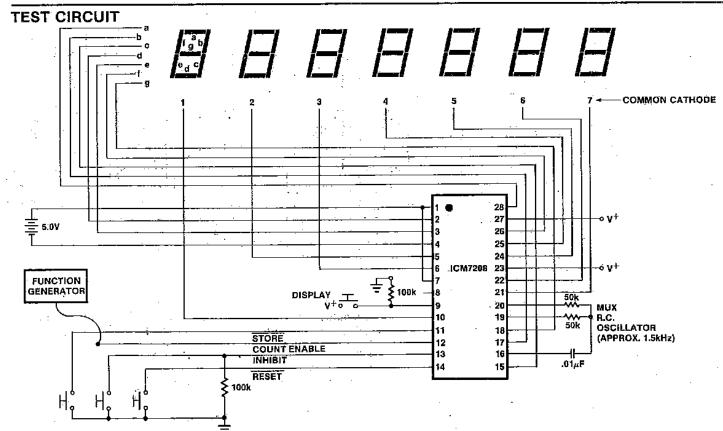

### **TEST CIRCUIT**

: SWITCHES  $s_1,s_2,s_3,s_4$  OPEN CIRCUIT FOR SUPPLY CURRENT MEASUREMENT. SWITCH  $|s_4\rangle$  OPEN CIRCUIT FOR SLOW GATING PERIOD.

† SWITCHES  $\mathbf{S}_2$ ,  $\mathbf{S}_3$ ,  $\mathbf{S}_4$  and 50k RESISTORS ARE NOT NEEDED WHEN USING THE ICM7207A.

# APPLICATION NOTES OSCILLATOR CONSIDERATIONS

The oscillator consists of a CMOS inverter with a non-linear resistor connected between the input and output terminals to provide biasing. Oscillator stabilities of approximately 0.1 ppm per 0.1 volt change are achievable at a supply voltage of 5 volts, using low cost crystals. The crystal specifications are shown in the TEST CIRCUIT.

It is recommended that the crystal load capacitance ( $G_L$ ) be no greater than 15pF for a crystal having a series resistance equal to or less than 75 $\Omega$ , otherwise the output amplitude of the oscillator may be too low to drive the divider reliably.

If a very high quality oscillator is desired, it is recommended that a quartz crystal be used having a tight tuning tolerance  $\pm 10\,$  ppm, a low series resistance (less than  $25\Omega$ ), a low motional capacitance of 5mpF and a load capacitance of 20pF. The fixed capacitor CIN should be 39pF and the oscillator tuning capacitor should range between approximately 8 and 60pF.

Use of a high quality crystal will result in typical oscillator stabilities of 0.05 ppm per 0.1 volt change of supply voltage.

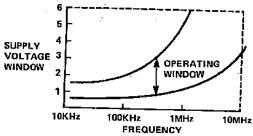

### FREQUENCY LIMITATIONS

The ICM7207/A uses dynamic frequency counters in the initial divider sections. Dynamic frequency counters are faster and consume less power than static dividers but suffer from the disadvantage that there is a minimum operating frequency at a given supply voltage.

For example, if instead of 6.5MHz, a 1MHz oscillator is required, it is recommended that the supply voltage be reduced to between 2 and 2.5 volts. This may be realized by using a series resistor in series with the 5V positive supply line plus a decoupling capacitor. The quartz crystal parameters, etc., will determine the value of this resistor. NOTE: Except for the output open drain n-channel transistors no other terminal is permitted to exceed the supply voltage limits.

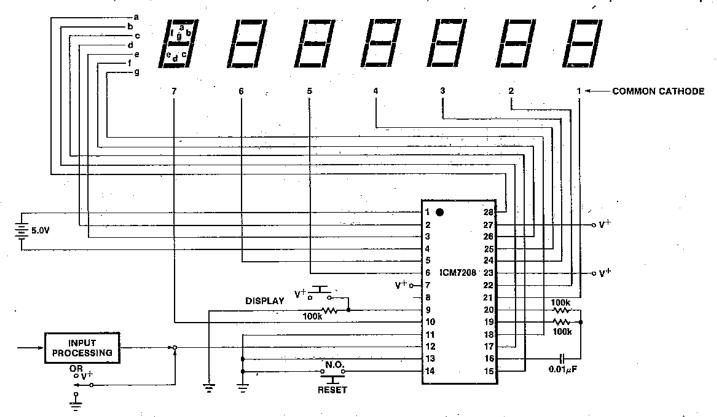

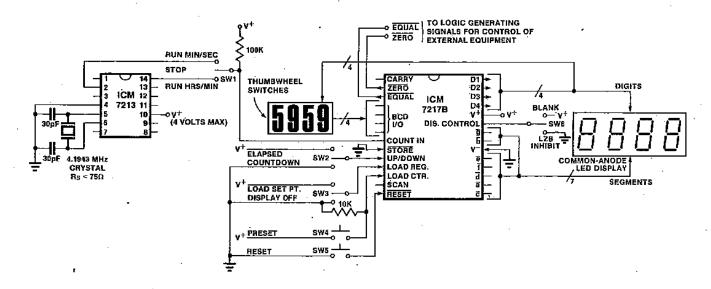

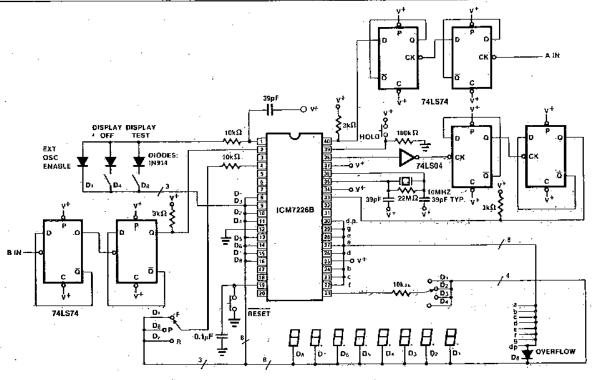

# PRACTICAL FREQUENCY COUNTER

A complete frequency counter using the ICM7207/A together with the ICM7208 Frequency Counter is described in the ICM7208 data sheet.

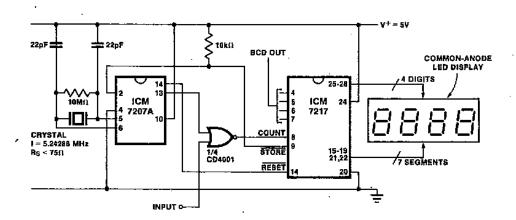

A complete frequency counter using the ICM7207/A together with the ICM7208 Frequency Counter is described in the ICM7208 data sheet, and app note A015. Other frequency counters using the ICM7207/A can be constructed using the ICM7224, ICM7225, and ICM7236, for LCD, LED and VF displays. The latter are available as EV/Kits also.

The ICM7207/A uses dynamic frequency counters in the initial divider sections. Dynamic frequency counters are faster and consume less power than static dividers but suffer from the disadvantage that there is a minimum operating frequency at a given supply voltage.

# **QUARTZ CRYSTAL MANUFACTURERS**

The following list of possible suppliers is intended to be of assistance in putting a design into production. It should not be interpreted as a comprehensive list of suppliers, nor does it constitute an endorsement by Intersii.

- a) CTS Knights, Sandwich, Illinois, (815) 786-8411

- b) Motorola Inc., Franklin Park, Illinois (312) 451-1000

- Sentry Manufacturing Co., Chickasaw, Oklahoma (405) 224-6780

- d) Tyco Filters Division, Phoenix, Arizona (602) 272-7945

- e) M-Tron Inds., Yankton, South Dakota (605) 665-9321

- f) Saronix, Palo Alto, California (415) 856-6900

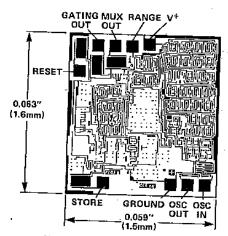

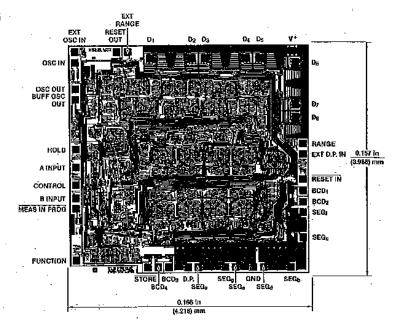

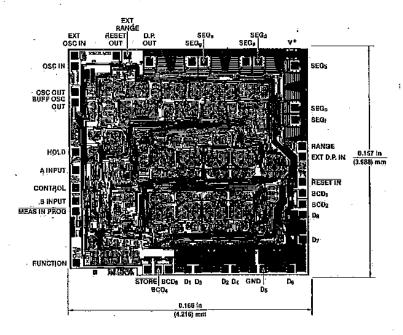

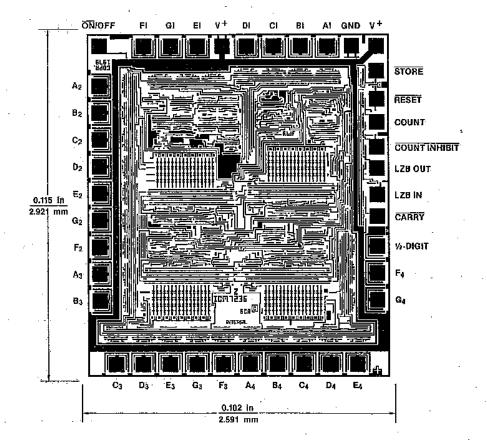

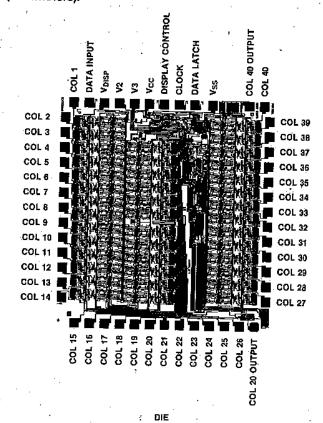

### CHIP TOPOGRAPHY

Chip may be die attached using conventional eutectic or epoxy procedures. Wire bonding may be either aluminum uitresonic or gold compression.

# **1CM7208 CMOS** 7 Decade Counter

#### **FEATURES**

- Low operating power dissipation < 10mW</li>

- Low quiescent power dissipation < 5mW</li>

- Counts and displays 7 decades

- Wide operating supply voltage range  $2V < V^{+} \le 6V$

- Drives directly 7 decade multiplexed common cathode LED display

- Internal store capability

- Internal inhibit to counter input

- · Test speedup point

- All terminals protected against static discharge

### DESCRIPTION

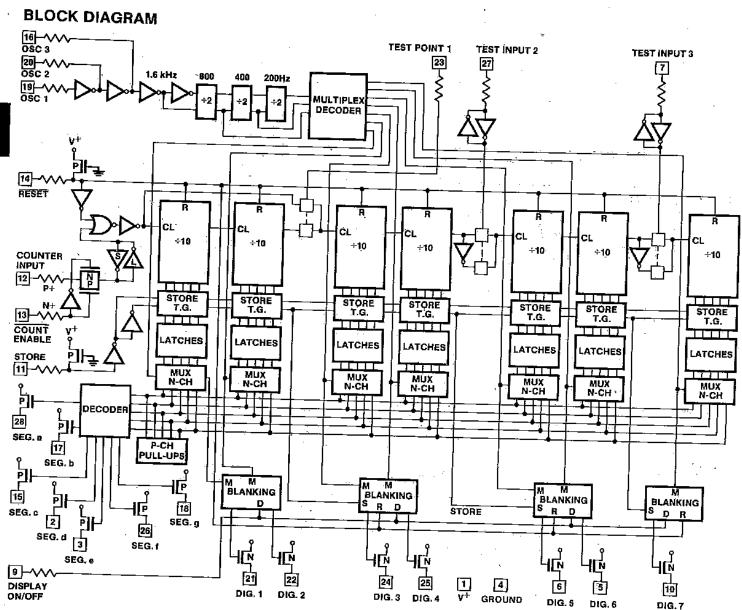

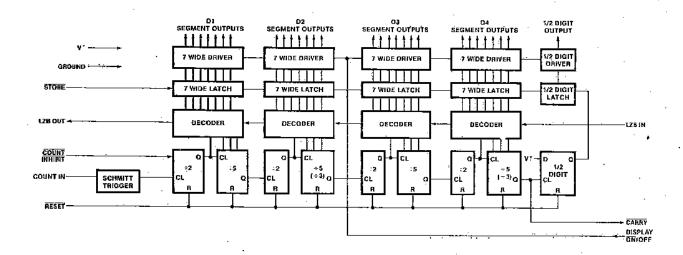

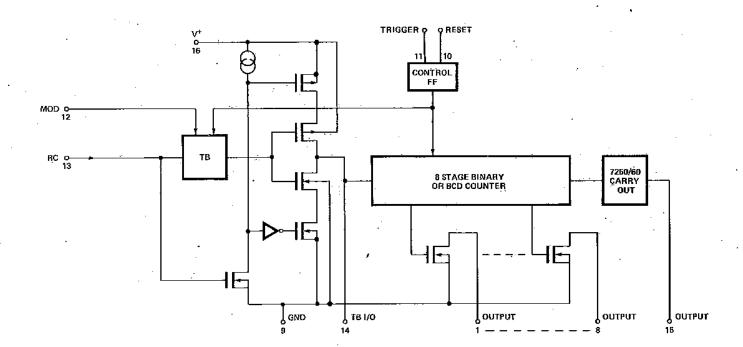

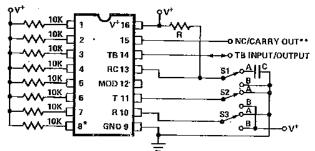

The ICM7208 is a fully integrated seven decade counterdecoder-driver and is manufactured using Intersil's low voltage metal gate C-MOS process.

Specifically the ICM7208 provides the following on chip functions: a 7 decade counter, multiplexer, 7 segment decoder, digit & segment driver, plus additional logic for display blanking, reset, input inhibit, and display on/off. For unit counter applications the only additional components are a 7 digit common cathode display, 3 resistors and a capacitor to generate the multiplex frequency reference, and the control switches.

The ICM7208 is intended to operate over a supply voltage of 2 to 6 volts as a medium speed counter, or over a more restricted voltage range for high frequency applications.

As a frequency counter it is recommended that the ICM7208 be used in conjunction with the ICM7207 Oscillator Controller, which provides a stable HF oscillator, and output signal gating.

### ORDERING INFORMATION

| ORDER<br>PART NUMBER                 | TEMPERATURE<br>RANGE | 28 LEAD<br>PACKAGE |  |  |  |  |  |

|--------------------------------------|----------------------|--------------------|--|--|--|--|--|

| ICM7208IPI                           | -20°C to +85°C       | PLASTIC            |  |  |  |  |  |

| ORDER DICE BY FOLLOWING PART NUMBER: |                      |                    |  |  |  |  |  |

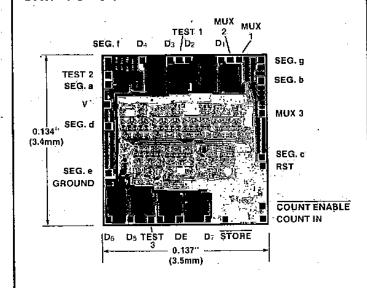

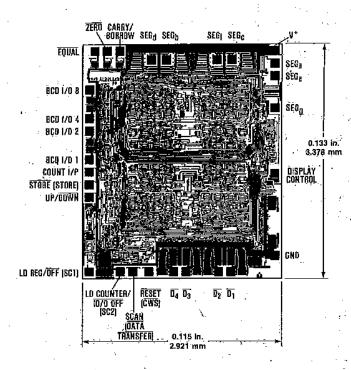

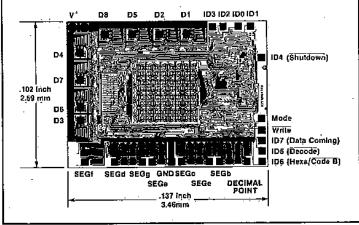

### CHIP TOPOGRAPHY

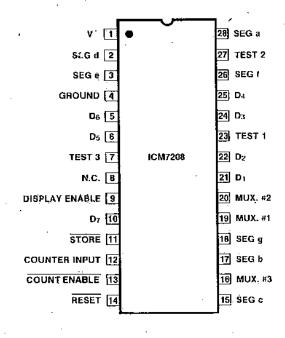

### PIN CONFIGURATION (OUTLINE DRAWING PI)

### ICM7208

| Power Dissipation (Note 1)                                                         |

|------------------------------------------------------------------------------------|

| Supply voltage (Note 2)                                                            |

| Output digit drive current (Note 3)                                                |

| Output segment drive current                                                       |

| Input voltage range (any input terminal) (Note 2) Not to exceed the supply voltage |

| Operating tomography reput terminal (Note 2) Not to exceed the supply voltage      |

| Operating temperature range20°C to +85°C                                           |

| ororage remperature range                                                          |

| Lead temperature (soldering, 10 seconds)                                           |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions above those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# TYPICAL OPERATION CHARACTERISTICS

TEST CONDITIONS: (V+ = 5V, T<sub>A</sub> = 25°C, TEST CIRCUIT, display off, unless otherwise specified)

| PARAMETER                                  | SYMBOL         | CONDITIONS                                                                                    | MIN      | TVD                                          | T diam    | 1              |

|--------------------------------------------|----------------|-----------------------------------------------------------------------------------------------|----------|----------------------------------------------|-----------|----------------|

| Quiescent Current                          | IQ             | All controls plus terminal 19 connected to V <sup>+</sup> No multiplex oscillator             | MIN      | <b>TYP</b> 30                                | 300       | UNITS          |

| Quiescent Current                          | lo             | All control inputs plus terminal 19 connected to V* except STORE which is connected to GROUND |          | 70                                           | 350       | μΑ             |

| Operating Supply Current                   | l <sup>+</sup> | All inputs connected to V <sup>+</sup> , RC multiplexer osc operating fin < 25KHz             |          | 210                                          | 500       | , ,,,,         |

| Operating Supply Current                   | J <sup>+</sup> | fin = 2MHz                                                                                    | <u> </u> | <u>.                                    </u> | 700       |                |

| Supply Voltage Range                       | V+             | f <sub>in</sub> ≤ 2MHz                                                                        | 3.5      |                                              |           | <u> </u>       |

| Digit Driver On Resistance                 | rDIG           |                                                                                               | 3.5      | <u> </u>                                     | 5.5       | . V            |

| Digit Driver Leakage<br>Current            | lpig           |                                                                                               |          | 4                                            | 12<br>500 | <u>Ω</u><br>μΑ |

| Segment Driver On Resistance               | rseg           | · · · · · · · · · · · · · · · · · · ·                                                         | <u> </u> | 40                                           |           | U              |

| Segment Driver<br>Leakage Çurrent          | !slk           | _                                                                                             | -        | · · · · · · · · · · · · · · · · · · ·        | 500       | μА             |

| Pullup Resistance of RESET or STORE Inputs | Rp             |                                                                                               | 100      | 400                                          |           |                |

| COUNTER INPUT Resistance                   | RIN            | Terminal 12 either at V <sup>+</sup> or GROUND                                                |          |                                              | 400       | kΩ             |

| COUNTER INPUT Hysteresis<br>Voltage        | VHIN           |                                                                                               |          | 25                                           | 100<br>50 | mV             |

NOTE 1: This value of power dissipation refers to that of the package and will not be obtained under normal operating conditions.

NOTE 2: The supply voltage must be applied before or at the same time as any input voltage. This poses no problems with a single power supply system. If a multiple power supply system is used, it is mandatory that the supply for the ICM7208 is switched on before the other supplies otherwise the device may be permanently damaged.

NOTE 3: The output digit drive current must be limited to 150mA or less under steady state conditions. (Short term transients up to 250mA will not damage the device.) Therefore, depending upon the LED display and the supply voltage to be used it may be necessary to include additional segment series resistors to limit the digit currents.

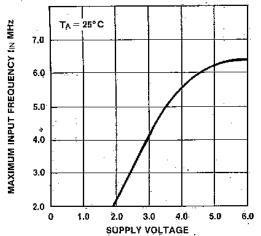

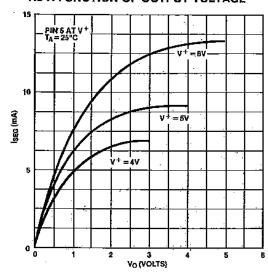

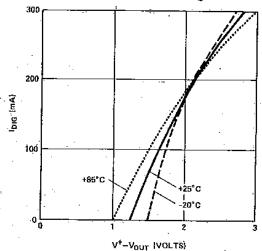

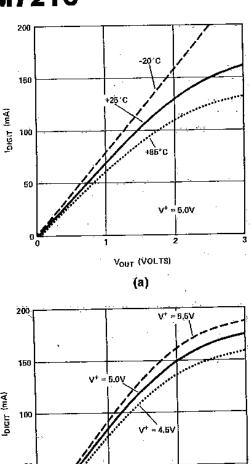

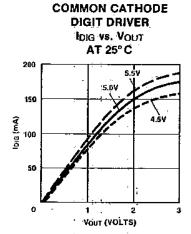

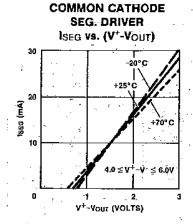

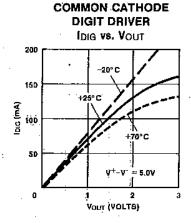

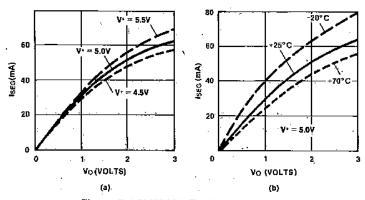

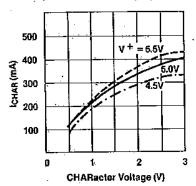

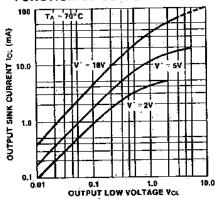

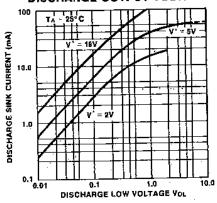

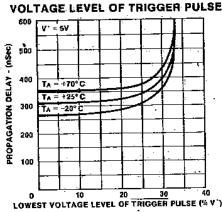

# TYPICAL PERFORMANCE CHARACTERISTICS MAXIMUM COUNTER INPUT FREQUENCY

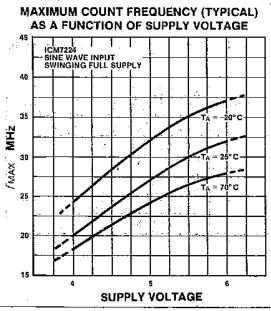

MAXIMUM COUNTER INPUT FREQUENCY AS A FUNCTION OF SUPPLY VOLTAGE

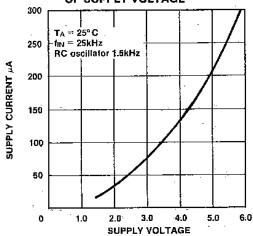

# SUPPLY CURRENT AS A FUNCTION OF SUPPLY VOLTAGE

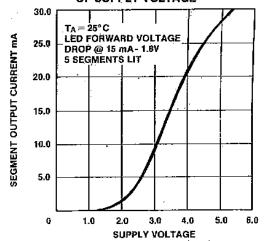

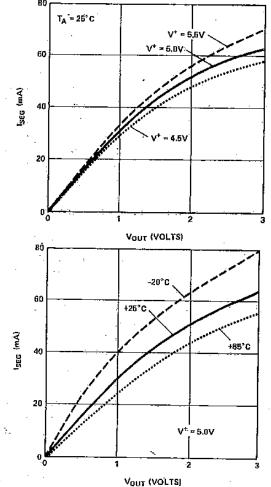

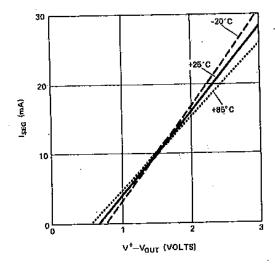

# SEGMENT OUTPUT CURRENT AS A FUNCTION OF SUPPLY VOLTAGE

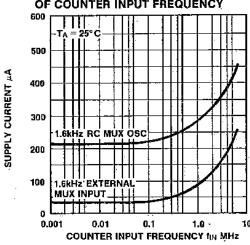

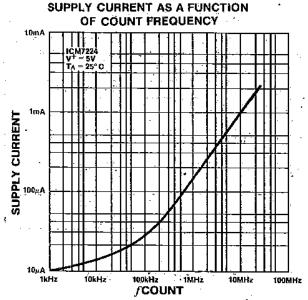

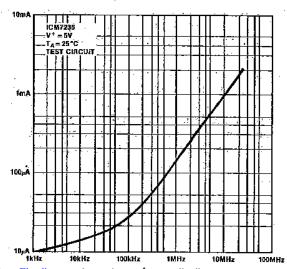

# SUPPLY CURRENT AS A FUNCTION OF COUNTER INPUT FREQUENCY

### **TEST PROCEDURES**

The ICM7208 is provided with three input terminals 7, 23, 27 which may be used to accelerate testing. The least two significant decade counters may be tested by applying an input to the 'COUNTER INPUT' terminal 12. 'TEST POINT' terminal 23 provides an input which bypasses the 2 least significant decade counters and permits an injection of a signal into the third decade counter. Similarly terminals 7 and 27 permit rapid counter advancing at two points further along the string of decade counters.

# CONTROL INPUT DEFINITIONS

|             |          |                | <u> </u>               |

|-------------|----------|----------------|------------------------|

| INPUT       | TERMINAL | <b>VOLTAGE</b> | FUNCTION               |

| 1 DISPLAY   | 9        | VŤ             | Display On             |

|             |          | Ground         | Display Off            |

| 2. STORE    | 11 7     | V+             | Counter                |

|             |          | •              | Information<br>Latched |

|             | ł        | Ground         | Counter                |

|             |          |                | Information            |

| <del></del> |          | ·              | Transferring           |

| 3. ENABLE   | 13       | V+             | input to Counter       |

|             |          |                | Blocked                |

|             |          | Ground         | Normal Operation       |

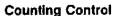

| 4 RESET     | 14 ' [   | V <sup>3</sup> | Normal Operation       |

| <u></u>     |          | Ground         | Counters Reset         |

# COUNTER INPUT DEFINITION

The internal counters of the ICM7208 index on the negative edge of the input signal at terminal #12.

### ICM7208

### **APPLICATION NOTES**

### 1. Format of Signal to be Counted

The noise immunity of the COUNTER INPUT Terminal is approximately 1/3 the supply voltage. Consequently, the input signal should be at least 50% of the supply in peak to peak amplitude and preferably equal to the supply. NOTE; The amplitude of the input signal should not exceed the supply; otherwise, damage may be done to the circuit.

The optimum input signal is a 50% duty cycle square wave equal in amplitude to the supply. However, as long as the rate of change of voltage is not less than approximately  $10^{-4}V/\mu sec$  at 50% of the power supply voltage, the input waveshape can be sinusoidal, triangular, etc.

When driving the input of the ICM7208 from TTL, a 1k-5k ohm pull-up resistor to the positive supply must be used to increase peak to peak input signal amplitude.

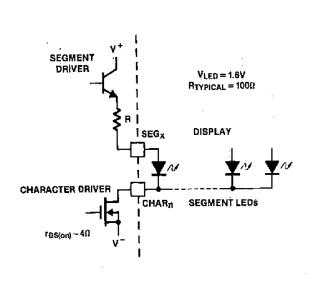

### 2. Display Considerations

Any common cathode multiplexable LED display may be used. However, if the peak digit current exceed 150 mA for any prolonged time, it is recommended that resistors be included in series with the segment outputs to limit digit current to 150mA.

The ICM7208 is specified with  $500\mu A$  of possible digit leakage current. With certain new LED displays that are extremely efficient at low currents, it may be necessary to include resistors between the cathode outputs and the positive supply to bleed off this leakage current.

### 3. Display Multiplex Rate

The ICM7208 has approximately  $0.5\mu s$  overlap between output drive signals. Therefore, if the multiplex rate is very fast, digit ghosting will occur. The ghosting determines the upper limit for the multiplex frequency. At very low multiplex rates flicker becomes visible.

It is recommended that the display multiplex rate be within the range of 50Hz to 200Hz, which corresponds to 400Hz to 1600Hz for the multiplex frequency input.

#### 4. Unit Counter

The unit counter updates the display for each negative transition of the input signal. The information on the display will count, after reset, from 00 to 9,999,999 and then reset to 0000000 and begin to count up again. To blank leading zeros, actuate reset at the beginning of a count. Leading zero blanking affects two digits at a time.

For battery operated systems the display may be switched off to conserve power.

An external generator may be used to provide the multiplex frequency input. This signal, applied to terminal 19 (terminals 16 and 20 open circuit), should be approximately equal to the supply voltage, and should be a square wave for minimum of power dissipation.

For stand alone systems, two inverters are provided so that a simple but stable RC oscillator may be built using only 2 resistors and a capacitor.

Figure 1 shows the schematic of an extremely simple unit counter that can be used for remote traffic counting, to name one application. The power cell stack should consist of 3 or 4 nickel cadmium rechargeable cells (nominal 3.6 or 4.8 volts). If 4 x 1.5 volt cells are used it is recommended that a diode be placed in series with the stack to guarantee that the supply voltage does not exceed 6 volts.

The input switch is shown to be a single pole double throw switch (SPDT). A single pole single throw switch (SPST) could also be used (with a pullup resistor), however, anti-bounce circuitry must be included in series with the counter input. In order to avoid contact bounce problems due to the SPDT switch the ICM7208 contains an input latch on chip.

Figure 1: Schematic Unit Counter

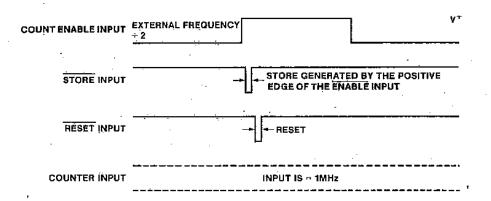

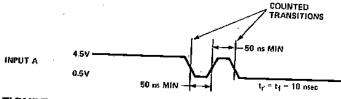

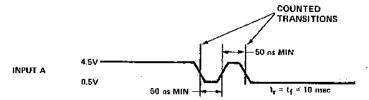

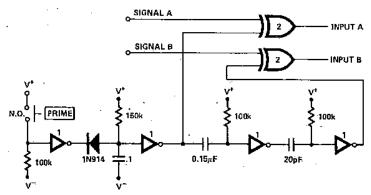

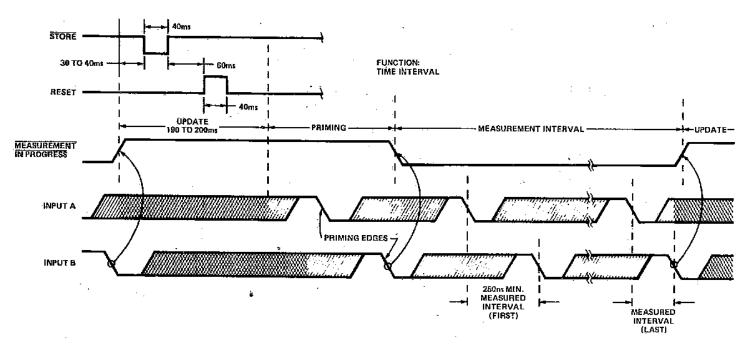

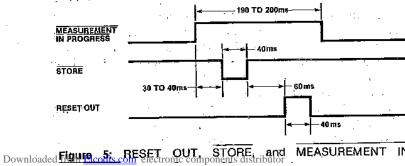

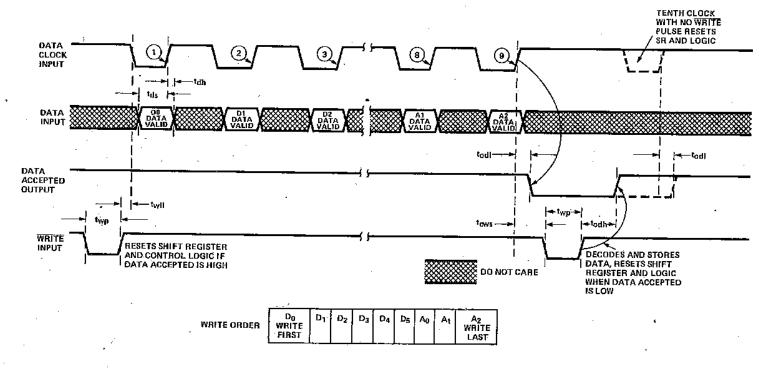

Figure 3: Frequency Counter Input Waveforms

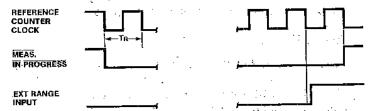

#### 6. Period Counter

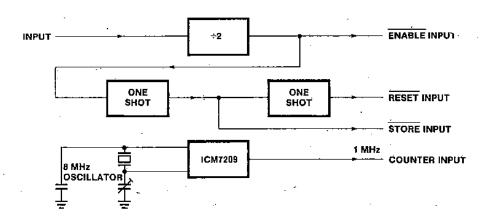

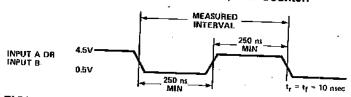

For this application, as opposed to the frequency counter, the gating and the input signal to be measured are reversed to the frequency counter. The input period is multiplied by two to produce a single polarity signal (50% duty cycle) equal to the input period, which is used to gate into the counter the frequency reference (1MHz in this case). Figure 5 shows a

block schematic of the input waveform generator. The 1MHz frequency reference is generated by the ICM7209 Clock Generator using an 8MHz oscillator frequency and internally dividing this frequency by 8. Alternatively, a 1MHz signal could be applied directly to COUNTER INPUT. Waveforms are shown in Figure 4.

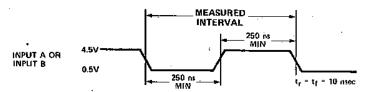

Figure 4: Period Counter Input Waveforms

Figure 5: Period Counter Input Generator

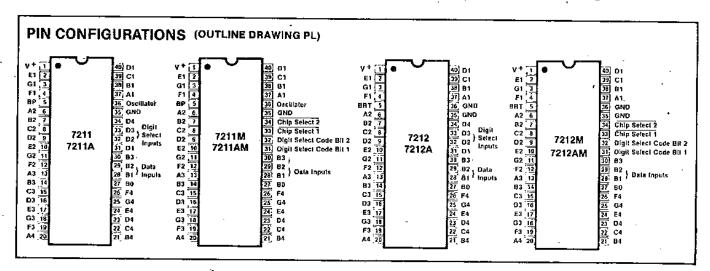

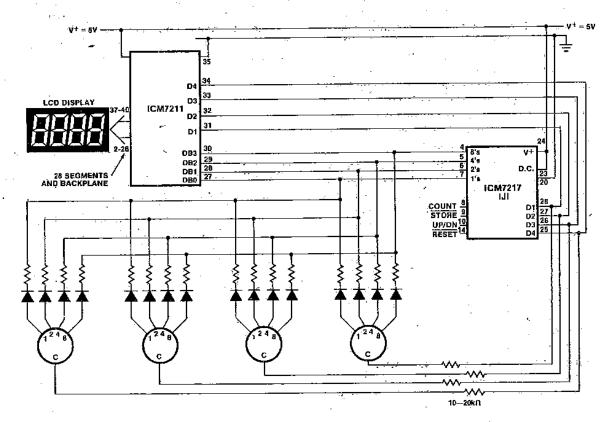

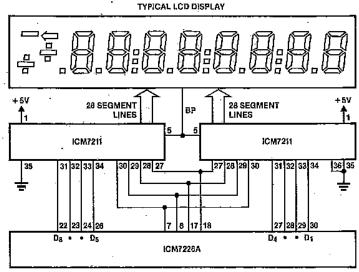

# ICM7211 (LCD) ICM7212 (LED)

# Four Digit CMOS Display Decoder/Drivers

### **ICM7211 (LCD) FEATURES**

- Four digit non-multiplexed 7 segment LCD display outputs with backplane driver

- Complete onboard RC oscillator to generate backplane frequency

- Backplane input/output allows simple synchronization of slave-device segment outputs to a master backplane signal

- ICM7211 devices provide separate Digit Select inputs to accept multiplexed BCD input (Pinout and functionally compatible with Siliconix DF411)

- ICM7211M devices provide data and digit select code input latches controlled by Chip Select inputs to provide a direct high speed processor interface

- ICM7211 decodes binary hexadecimal;

ICM7211A decodes binary to Code B (0-9, dash, E, H, L, P, blank)

### ICM7212 (LED) FEATURES

- 28 current-limited segment outputs provide 4-digit non-multiplexed direct LED drive at > 5mA per segment.

- Brightness input allows direct control of LED segment current with a single potentiometer. Can function digitally as a display enable.

- ICM7212M and ICM7212A devices provide same input configuration and output decoding options as the ICM7211.

### DESCRIPTION

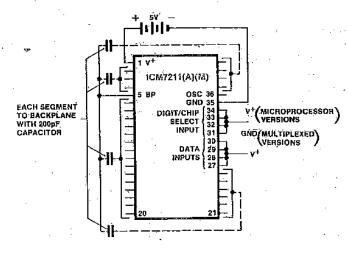

The ICM7211 (LCD) and ICM7212 (LED) devices constitute a family of non-multiplexed four-digit seven-segment CMOS display decoder-drivers.

The ICM7211 devices are configured to drive conventional LCD displays by providing a complete RC oscillator, divider chain, backplane driver, and 28 segment outputs. These outputs provide the zero d.c. component signals necessary for long display life.

The ICM7212 devices are configured to drive common-anode LED displays, providing 28 current-controlled low leakage open-drain n-channel outputs. These devices provide a BRighTness input, which may be used at normal logic levels as a display enable, or with a potentiometer as a continuous display brightness control.

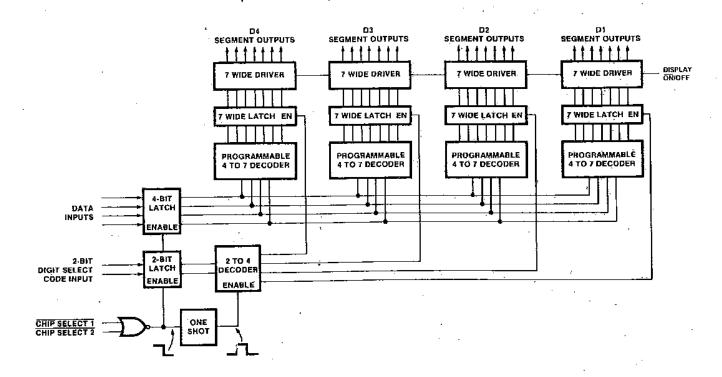

Both the LCD and LED devices are available with two input configurations. The basic devices provide four data-Bit inputs and four Digit Select inputs. This configuration is sultable for interfacing with multiplexed BCD or binary output devices, such as the ICM7217, ICM7226 and ICL71C03. The microprocessor interface (suffix M) devices provide data input latches and Digit Select code latches under control of high-speed Chip Select inputs. These devices simplify the task of implementing a cost-effective alphanumeric seven-segment display for microprocessor systems, without requiring extensive ROM or CPU time for decoding and display updating.

The standard devices will provide two different decoder configurations. The basic device will decode the four bit binary input into a seven-segment alphanumeric hexadecimal output. The "A" versions will provide the "Code B" output code, i.e., 0–9, dash, E, H, L, P, blank. Either device will correctly decode true BGD to seven-segment decimal outputs.

Devices in the ICM7211/7212 family are packaged in a standard 40 pin plastic dual-in-line package and all inputs are fully protected against static discharge.

# ICM7211/ICM7212

### ABSOLUTE MAXIMUM RATINGS

| Power Dissipation (Note 1)           | 0.5 W @ 70°C           |

|--------------------------------------|------------------------|

| Supply Voltage                       | 6.5V                   |

| Input Voltage (Any                   |                        |

| Terminall (Note 2)                   | V+ +0.3V, GROUND +0.3V |

| Operating Temperature Range          |                        |

| Storage Temperature Range            |                        |

| Lead Temperature (Soldering 10 sec.) |                        |

NOTE 1: This limit refers to that of the package and will not be realized during normal operation.

NOTE 2: Due to the SCR structure inherent in the CMOS process, connecting any terminal to voltages greater than V+ or less than GROUND may cause destructive device latchup. For this reason, it is recommended that no inputs from external sources not operating on the same power supply be applied to the device before its supply is established, and that in multiple supply systems, the supply to the ICM7211/ICM7212 be turned on first.

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions above those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **OPERATING CHARACTERISTICS**

TEST CONDITIONS: All parameters measured with V+ = 5V unless otherwise specified.

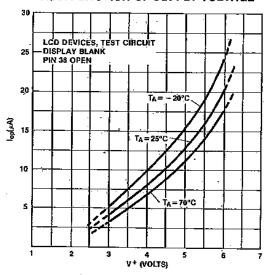

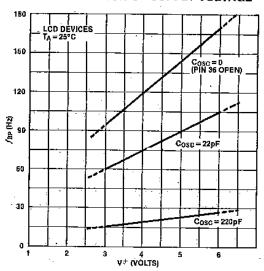

### ICM7211 CHARACTERISTICS (LCD)

| PARAMETER                      | SYMBOL          | CONDITIONS                  | MIN | TYP | MAX | UNIT |

|--------------------------------|-----------------|-----------------------------|-----|-----|-----|------|

| Operating Supply Voltage Range | Vsupp           | · · · · · ·                 | 3   | 5   | 6   | V    |

| Operating Current              | lop             | Test circuit, Display blank | 1   | 10  | 50  | μА   |

| Oscillator Input Current       | losci           | Ріп 36                      |     | ±2  | ±10 | "    |

| Segment Rise/Fall Time         | tris            | C <sub>L</sub> = 200pF      |     | 0.5 |     |      |

| Backplane Rise/Fall Time       | trib            | C <sub>L</sub> = 5000pF     |     | 1.5 |     | μS   |

| Oscillator Frequency           | fosc            | Pin 36 Floating             |     | 19  |     | kHz  |

| Backplane Frequency            | f <sub>bp</sub> | Pin 36 Floating             |     | 150 |     | Hz   |

### ICM7212 CHARACTERISTICS (COMMON ANODE LED)

| PARAMETER                      | SYMBOL | CONDITIONS                                | MIN | TYP   | MAX        | UNIT |

|--------------------------------|--------|-------------------------------------------|-----|-------|------------|------|

| Operating Supply Voltage Range | VSUPP  |                                           | 4   | 5     | 6          | ٧    |

| Operating Current              | lon    | Pin 5 (Brightness),                       |     | 10    | 50         | μΑ   |

| Display Off                    |        | Pins 27-34 - GROUND                       | 1   |       |            |      |

| Operating Current              | lop    | Pin 5 at V <sup>+</sup> , Display all 8'ş |     | 200   | -          | mΑ   |

| Segment Leakage Current        | Islk   | Segment Off                               |     | ±0.01 | <u>±</u> 1 | μА   |

| Segment On Current             | ISEG   | Segment On, V <sub>O</sub> = +3V          | 5   | 8     |            | mΑ   |

### **INPUT CHARACTERISTICS**

| PARAMETER                       | SYMBOL          | CONDITIONS                                                    | MIN | TYP  | MAX | UNIT |

|---------------------------------|-----------------|---------------------------------------------------------------|-----|------|-----|------|

| Logical "1" input voltage       | ViH             |                                                               | 3   |      |     |      |

| Logical "0" input voltage       | . VIL           | <u>.</u>                                                      |     |      | · 2 | V    |

| Input leakage current           | lilk            | Pins 27-34                                                    |     | 生:01 | ±1  | μΑ   |

| Input capacitance               | Cin             | Pins 27-34                                                    |     | 5    |     | рF   |

| BP/Brightness input leakage     | IBPLK           | Measured at Pin 5 with Pin 36 at GND                          |     | ±.01 | ±1  | μΑ   |

| BP/Brightness input capacitance | Свы             | All Devices                                                   |     | 200  |     | рF   |

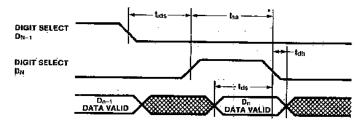

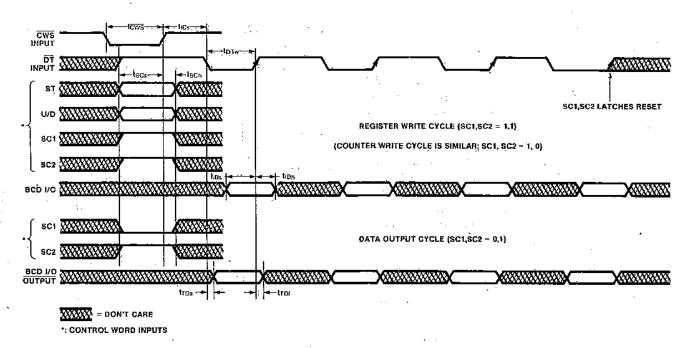

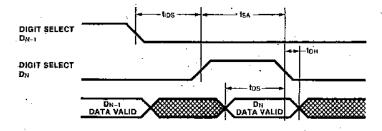

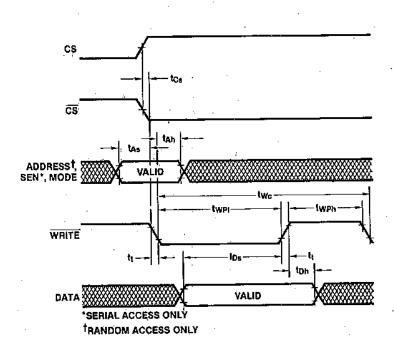

| AC CHARACTERISTICS - MULTIPL    | EXED INPUT      | CONFIGURATION                                                 |     |      |     |      |

| Digit Select Active Pulse Width | t <sub>sa</sub> | Refer to Timing Diagrams                                      | 1   |      |     | μS   |

| Data Setup Time                 | tos             |                                                               | 500 |      | -   |      |

| Data Hold Time                  | tah             |                                                               | 200 |      |     | ns   |

| Inter-Digit Select Time         | tids            |                                                               | 2   |      |     | μS   |

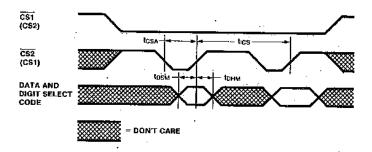

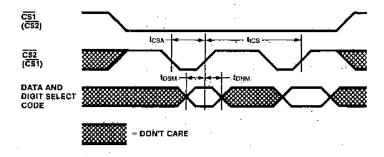

| AC CHARACTERISTICS - MICROPF    | OCESSOR I       | NTERFACE                                                      |     | •    |     |      |

| Chip Select Active Pulse Width  | tcsa            | other Chip Select either held active, or both driven together | 200 |      |     |      |

| Data Setup Time                 | tựs             |                                                               | 100 |      |     | ns   |

| Data Hold Time                  | tan             |                                                               | 10  | . 0  |     |      |

| Inter-Chip Select Time          | tics            |                                                               | 2   |      |     | μS   |

#

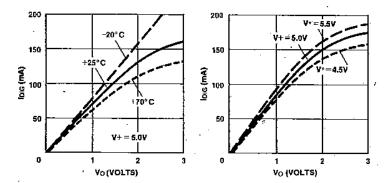

### TYPICAL CHARACTERISTICS

### ICM7211 OPERATING SUPPLY CURRENT AS A FUNCTION OF SUPPLY VOLTAGE

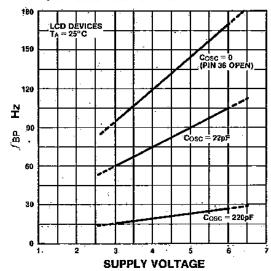

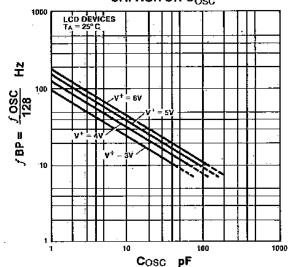

### ICM7211 BACKPLANE FREQUENCY AS A FUNCTION OF SUPPLY VOLTAGE

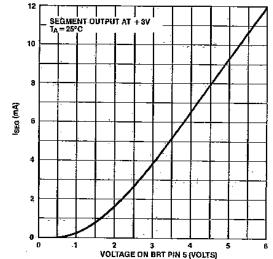

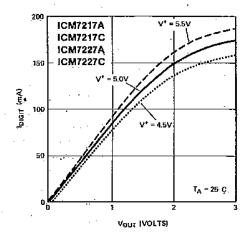

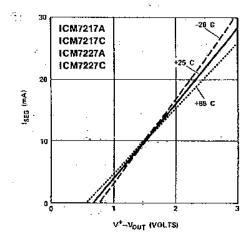

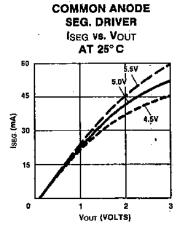

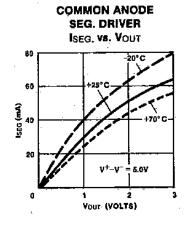

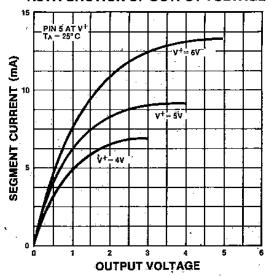

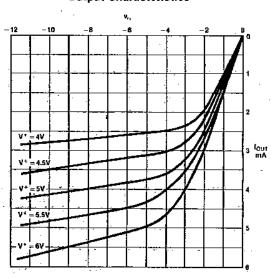

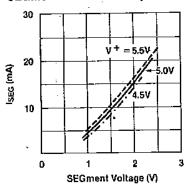

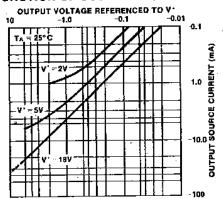

#### ICM7212 LED SEGMENT CURRENT AS A FUNCTION OF OUTPUT VOLTAGE

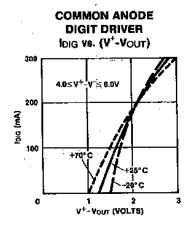

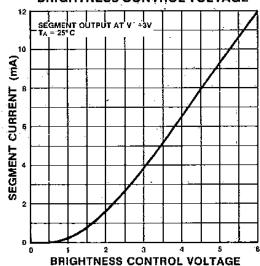

### ICM7212 LED SEGMENT CURRENT AS A FUNCTION OF BRIGHTNESS CONTROL VOLTAGE

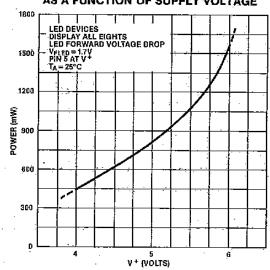

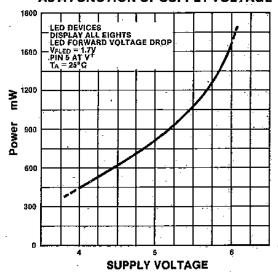

# ICM7212 OPERATING POWER (LED DISPLAY) AS A FUNCTION OF SUPPLY VOLTAGE

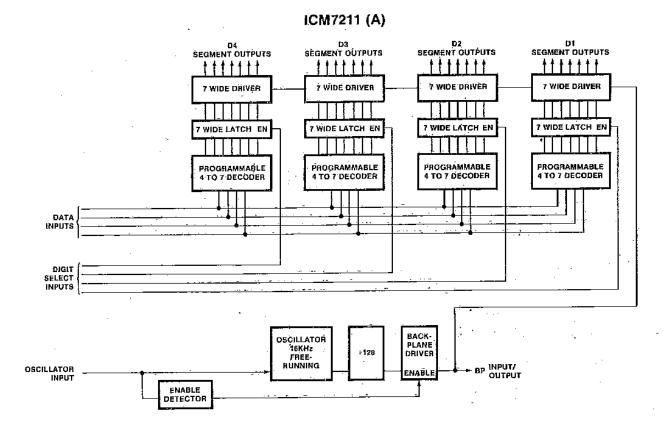

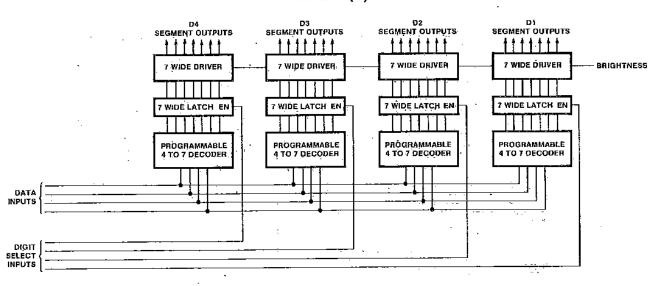

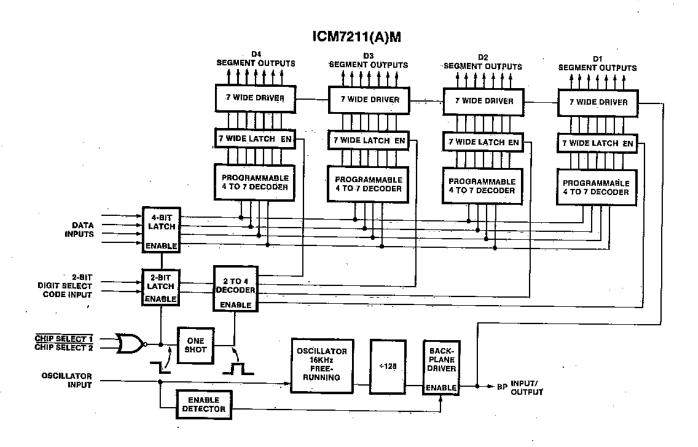

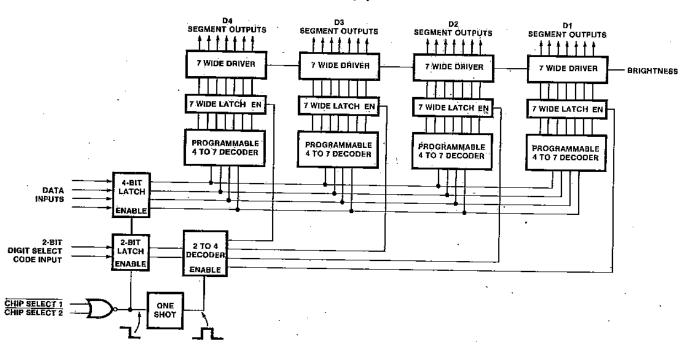

# **BLOCK DIAGRAMS**

### ICM7212 (A)

### ICM7211/ICM7212

### **INPUT DEFINITIONS**

In this table, V<sup>+</sup> and GROUND are considered to be normal operating input logic levels. Actual input low and high levels are specified under Operating Characteristics. For lowest power consumption, input signals should swing over the full supply.

| INPUT                     | TERMINAL | CONDITION                                                | FUNCTION                  |                                                                  |

|---------------------------|----------|----------------------------------------------------------|---------------------------|------------------------------------------------------------------|

| B0                        | 27       | V <sup>+</sup> = Logical One<br>GND = Logical Zero       | Ones (Least Significant)  |                                                                  |

| B1                        | 28       | V <sup>+</sup> = Logical One<br>GND = Logical Zero       | Twos                      | Data Input Bits                                                  |

| B2                        | 29       | V <sup>+</sup> = Logical One<br>GND = Logical Zero       | Fours                     | Data Input Dits                                                  |

| B3                        | 30       | V <sup>+</sup> = Logical One<br>GND = Logical Zero       | Eights (Most significant) | · · · · · · · · · · · · · · · · · · ·                            |

| OSC<br>(LCD Devices Only) | 36       | Floating or with ex-<br>ternal capacitor to V*<br>GROUND |                           | s, allowing segments to be synced to an<br>e BP terminal (Pin 5) |

### ICM7211/ICM7212

### **MULTIPLEXED-BINARY INPUT CONFIGURATION**

| INPUT | TERMINAL | CONDITION               | FUNCTION                            |

|-------|----------|-------------------------|-------------------------------------|

| D1    | 31       |                         | D1 (Least significant) Digit Select |

| D2    | 32       | V <sup>+</sup> = Active | D2 Digit Select                     |

| D3    | 33       | GND = Inactive          | D3 Digit Select                     |

| D4    | 34       |                         | D4 (Most significant) Digit Select  |

### ICM7211M/ICM7212M

### MICROPROCESSOR INTERFACE INPUT CONFIGURATION

| ſ | INPUT | DESCRIPTION                      | TERMINAL | CONDITION                 | FUNCTION                                                                                                                                                                   |

|---|-------|----------------------------------|----------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | DS1   | Digit Select<br>Code Bit 1 (LSB) | 31       | V⁴ = Lógical One          | DS1 & DS2 serve as a two bit Digit Select Code Input DS2, DS1 = 00 selects D4                                                                                              |

|   | DS2   | Digit Select<br>Code Bit 2 (MSB) | 32       | GND = Logical Zero        | DS2, DS1 = 01 selects D3 DS2, DS1 = 10 selects D2 DS2, DS1 = 11 selects D1                                                                                                 |

| Ì |       | Chip Select 1                    | 33       | V <sup>+</sup> = Inactive | When both CS1 and CS2 are taken low, the data at the Data                                                                                                                  |

|   | CS2   | Chip Select 2                    |          | GND = Active              | and Digit Select code inputs <u>are written</u> into the input latches. On the rising edge of either Chip Select, the data is decoded and written into the output latches. |

### **TEST CIRCUIT**

### ICM7211/ICM7212

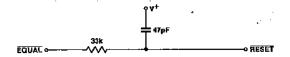

Figure 1: Multiplexed Input Timing Diagram

Figure 2: Microprocessor Interface Input Timing Diagram

### **DESCRIPTION OF OPERATION**

### **LCD DEVICES**

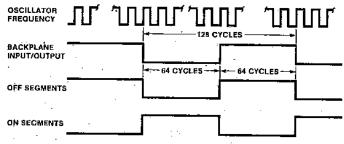

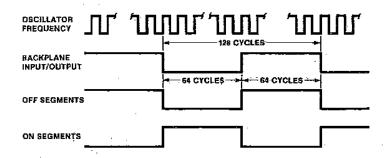

The LCD devices in the family (ICM7211, 7211A, 7211M, 7211AM) provide outputs suitable for driving conventional four-digit by seven-segment LCD displays, including 28 individual segment drivers, backplane driver, and a self-contained oscillator and divider chain to generate the backplane frequency.

The segment and backplane drivers each consist of a CMOS inverter, with the n- and p-channel devices ratioed to provide identical on resistances, and thus equal rise and fall times. This eliminates any dc component, which could arise from differing rise and fall times, and ensures maximum display life.

The backplane output devices can be disabled by connecting the OSCillator input (pin 36) to GrouND. This allows the 28 segment outputs to be synchronized directly to a signal input at the BP terminal (pin 5). In this manner, several slave devices may be cascaded to the backplane output of one master device, or the backplane may be derived from an external source. This allows the use of displays with characters in multiples of four and a single backplane. A slave device represents a load of approximately 200pF (comparable to one additional segment), thus the limitation of the number of devices that can be slaved to one master device backplane driver is the additional load represented by the larger backplane of displays of more than four digits; and the effect of that load on the backplane rise and fall times. A good rule of thumb to observe in order to minimize power consumption is to keep the rise and fall times less than about 5 microseconds. The backplane output driver should handle the backplane to a display of 16 onehalf-inch characters (rise and fall times not exceeding  $5\mu s$ . ie, 3 slave devices and the display backplane driven by a fourth master device). It is recommended that if more than four devices are to be slaved together, that the backplane signal be derived externally and all the ICM7211 devices be slaved to it. This external signal should be capable of driving very

Display Waveforms

large capacitive loads with short  $(1-2\mu s)$  rise and fall times. The maximum frequency for a backplane signal should be about 160Hz although this may be too fast for optimum display response at lower display temperatures, depending on the display used.

The onboard oscillator is designed to free run at approximately 19KHz at microampere power levels. The oscillator frequency is divided by 128 to provide the backplane frequency, which will be approximately 150Hz with the oscillator free-running; the oscillator frequency may be reduced by connecting an external capacitor between the OSCillator terminal and  $V^{+}$ .

The oscillator may also be overdriven if desired, although care must be taken to ensure that the backplane driver is not disabled during the negative portion of the overdriving signal (which could cause a d.c. component to the display). This can be done by driving the OSCillator input between the positive supply and a level out of the range where the backplane disable is sensed (about one fifth of the supply voltage above GrouND). Another technique for overdriving the oscillator (with a signal swinging the full supply) is to skew the duty cycle of the overdriving signal such that the negative portion has a duration shorter than about one microsecond. The backplane disable sensing circuit will not respond to signals of this duration.

#### **LED DEVICES**

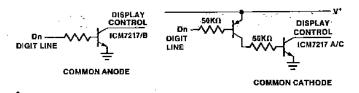

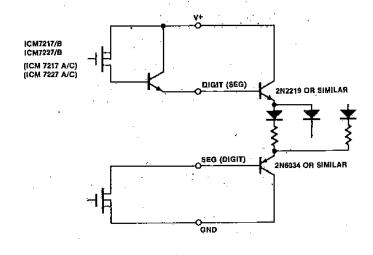

The LED devices in the family (ICM7212, 7212A, 7212M, 7212AM) provide outputs suitable for directly driving four-digit by seven-segment common-anode LED displays, including 28 individual segment drivers, each consisting of a low-leakage, current-controlled, open-drain n-channel transistor.

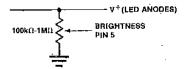

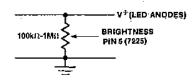

The drain current of these transistors can be controlled by varying the voltage at the BRighTness input (pin 5). The voltage at this pin is transferred to the gates of the output devices for "on" segments, and thus directly modulates the transistor's "on" resistance. A brightness control can be easily implemented with a single potentiometer controlling the voltage at pin 5, connected as in Fig (3). The potentiometer should be a high value (100K $\Omega$  to 1M $\Omega$ ) to minimize I2R power consumption, which can be significant when the display is off.

The BRighTness input may also be operated digitally as a display enable; when high, the display is fully on, and low fully off. The display brightness may also be controlled by varying the duty cycle of a signal swinging between the two voltages at the BRighTness input.

Note that the LED devices have two connections for GrouND; both of these pins should be connected. The

### ICM7211/ICM7212

double connection is necessary to minimize effects of bond wire resistance with the large total display currents possible.

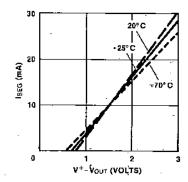

When operating LED devices at higher temperatures and/or higher supply voltages, the device power dissipation may need to be reduced to prevent excessive chip temperatures. The maximum power dissipation is 1 watt at 25°C, derated linearly above 35°C to 500mW at 70°C (-15mW/°C above 35°C). Power dissipation for the device is given by:

$$P = (V+-V_{FLED}) (I_{SEG}) (n_{SEG})$$

where V<sub>FLED</sub> is the LED forward voltage drop, Iseg is segment current, and nseg is the number of "on" segments. It is recommended that if the device is to be operated at elevated temperatures the segment current be limited by use of the BRighTness input to keep power dissipation within the limits described above.

Figure 3: Brightness control

#### INPUT CONFIGURATIONS AND OUTPUT CODES

The standard devices in the ICM7211/12 family accept a four-bit true binary (ie, positive level = logical one) input at pins 27 thru 30, least significant bit at pin 27 ascending to the most significant bit at pin 30. The ICM7211, ICM7211M, ICM7212, and ICM7212M devices decode this binary input into a seven-segment alphanumeric hexadecimal output, while the ICM7211A, ICM7211AM, ICM7212A, and ICM7212AM decode the binary input into the same seven-segment output as in the ICM7218 "Code B", ie 0-9, dash, E. H, L, P, blank. These codes are shown explicitly in Table 1. Either decoder option will correctly decode true BCD to a seven-segment decimal output.

These devices are actually mask-programmable to provide any 16 combinations of the seven segment outputs decoded from the four input bits. For larger quantity orders, (10K pcs. minimum) custom decoder options can be arranged. Contact the factory for details.

The ICM7211, ICM7211A, ICM7212, and ICM7212A devices are designed to accept multiplexed binary or BCD input. These devices provide four separate digit lines (least significant digit at pin 31 ascending to most significant digit at pin 34), each of which when taken to a positive level decodes and stores in the output latches of its respective digit the character corresponding to the data at the input port, pins 27 through 30. More than one digit select may be activated simultaneously (which will write the same character into all selected digits), although the timing requirements shown in Fig (1) and under Operating Characteristics for data setup, hold, and inter-digit select times must be met to ensure correct output.

The ICM7211M, ICM7211AM, ICM7212M, and ICM7212AM devices are intended to accept data from a data bus under processor control.

In these devices, the four data input bits and the two-bit digit select code (DS1 pin 31, DS2 pin 32) are written into input buffer latches when both chip select inputs (CS1 pin 33, CS2 pin 34) are taken low. On the rising edge of either chip select input, the content of the data input latches is decoded and stored in the output latches of the digit selected by the contents of the digit select code latches.

A select code of 00 writes into D4, DS2 = 0, DS1 = 1 writes into D3, DS2 = 1, DS1 = 0 writes into D2, and 11 writes into D1. The timing relationships for inputting data are shown in Fig (2), and the chip select pulse widths and data setup and hold times are specified under Operating Characteristics.

Table 1: Output Codes

|      | BINA | ARY |     | HEXADECIMAL'            | CODE B<br>ICM7211A(M) |

|------|------|-----|-----|-------------------------|-----------------------|

| В3   | B2   | 81  | BO  | ICM7212(M)              | ICM7212A(M)           |

| 0    | 0    | 0   | 0   | 0                       | 0                     |

| 0    | 0    | 0   | - 1 | ;                       | ;                     |

| 0    | 0    | 1   | 0   | 5                       | 2                     |

| 0    | 0    | 1   | 1   | 3                       |                       |

| 0    | 1    | 0   | . 0 | 4                       | 4                     |

| 0    | 1    | o   | 1   | S                       | 5                     |

| 0    | 1    | 1   | 0   | יט ייזי פר ער נפיידי פס | 3 W W C - ® O         |

| . 0. | i    | 1   | 1   | -                       | j                     |

| 1    | 0    | 0   | 0   | 8                       | 8                     |

| 1    | 0    | 0   | 1   | 9                       | 9                     |

| 1    | 0    | 1   | 0   | R                       | ~ ,                   |

| 1    | 0    | 1   | 1   | . የ                     | ε<br>H                |

| 1    | 1    | 0   | 0   | [ [                     |                       |

| 11   | 1    | 0   | 1   | ð                       | Ł<br>P                |

| 1 -  | 1    | 1   | 0   | កាកាឧ                   | P                     |

| 1    | 1    | 1   | 1   | F                       | (BLANK)               |

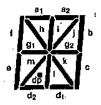

### SEGMENT ASSIGNMENT

### **APPLICATIONS**

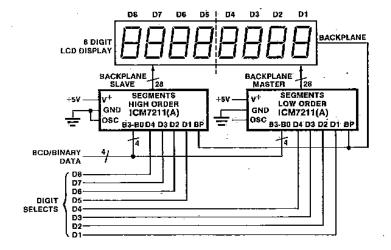

1. Ganged ICM7211's Driving 8-Digit LCD Display.

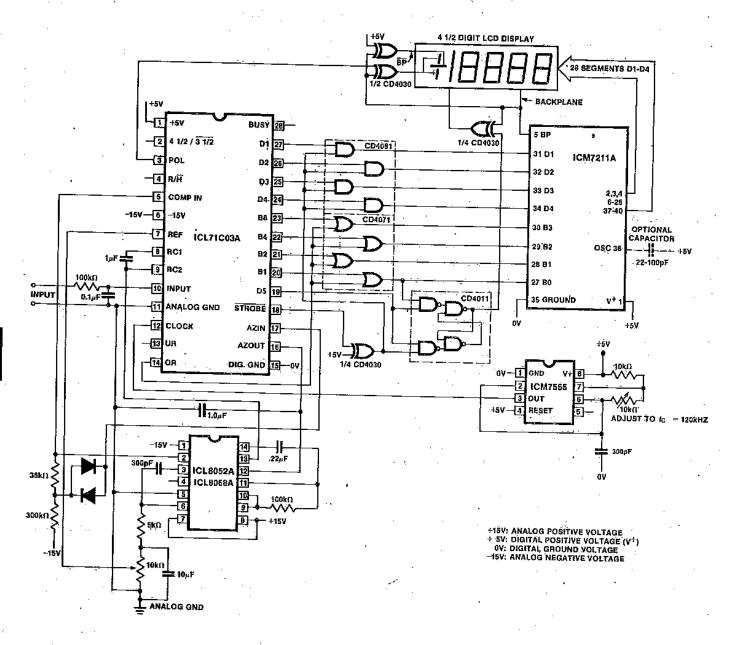

NOTE: See also ICL8052/ICL8068/ICL71C03 and ICL7135 Data Sheets for similar circuits with fewer features.

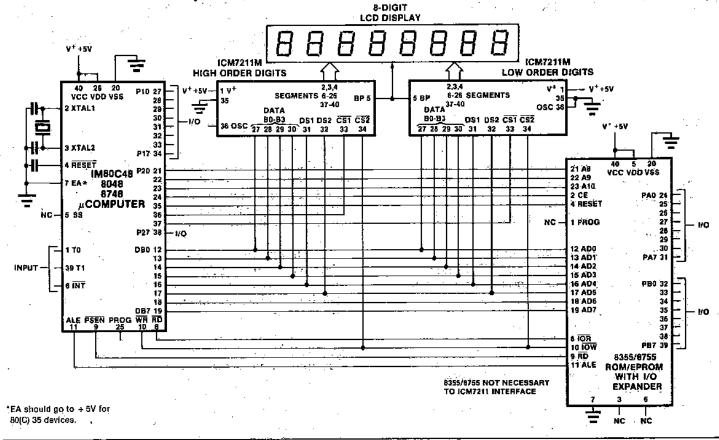

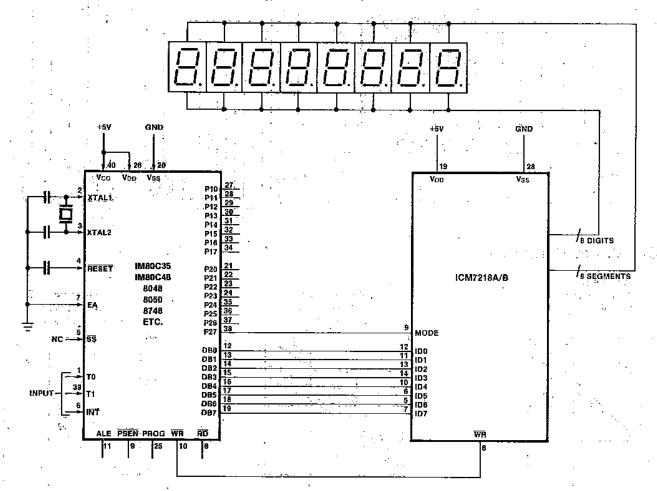

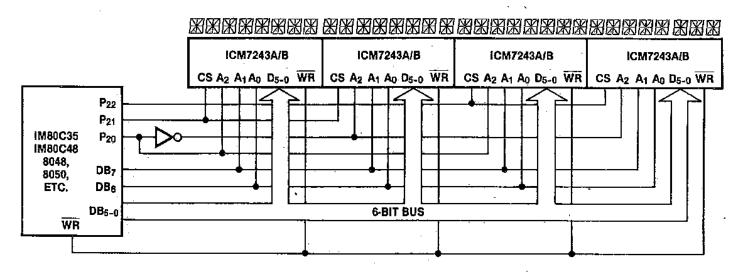

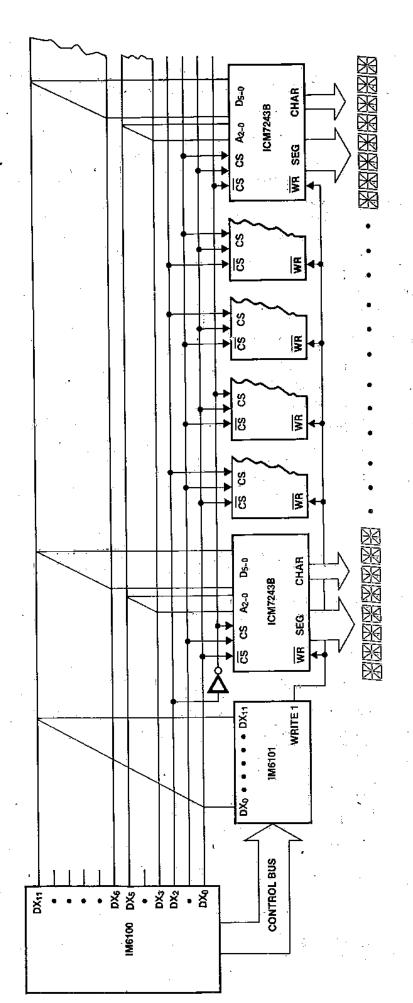

### 3. 8048/8748/IM80C48 Microprocessor Interface.

### **ORDERING INFORMATION**

| ORDER PART NUMBER |                               | OUTPUT CODE           | INPUT CONFIGURATIONS     |  |  |

|-------------------|-------------------------------|-----------------------|--------------------------|--|--|

| LCD               | ICM7211 IPL<br>ICM7211A IPL   | HEXADECIMAL<br>CODE B | MULTIPLEXED 4-BIT        |  |  |

| DISPLAY           | ICM7211M IPL<br>ICM7211AM IPL | HEXADECIMAL<br>CODE B | MICROPROCESSOR INTERFACE |  |  |

| LED               | ICM7212 IPL<br>ICM7212A IPL   | HEXADECIMAL CODE B    | MULTIPLÈXED 4-BIT        |  |  |

| DISPLAY           | ICM7212M IPL<br>ICM7212AM IPL | HEXADECIMAL CODE B    | MICROPROCESSOR INTERFACE |  |  |

Evaluation Kits are also available. Order ICM7211 EV/Kit or ICM7212 EV/Kit.

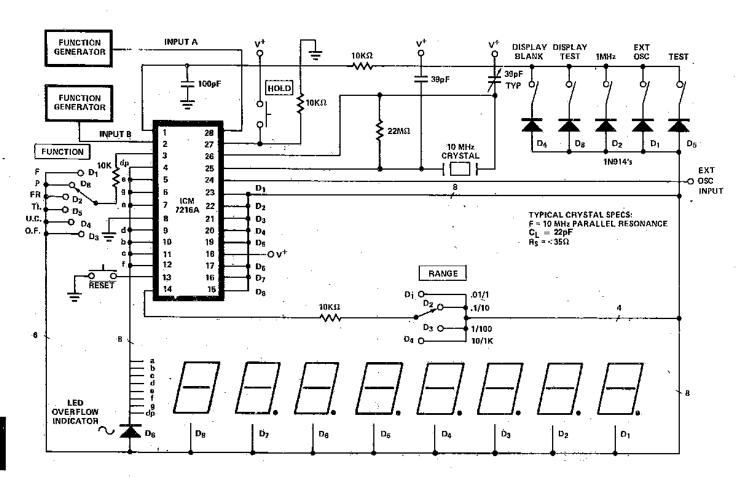

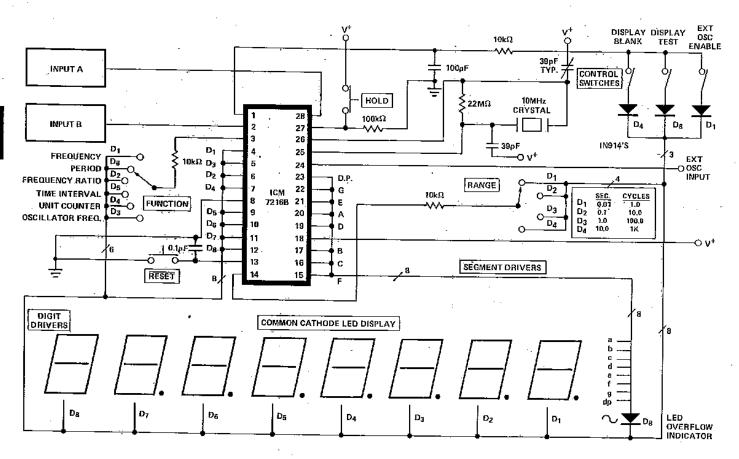

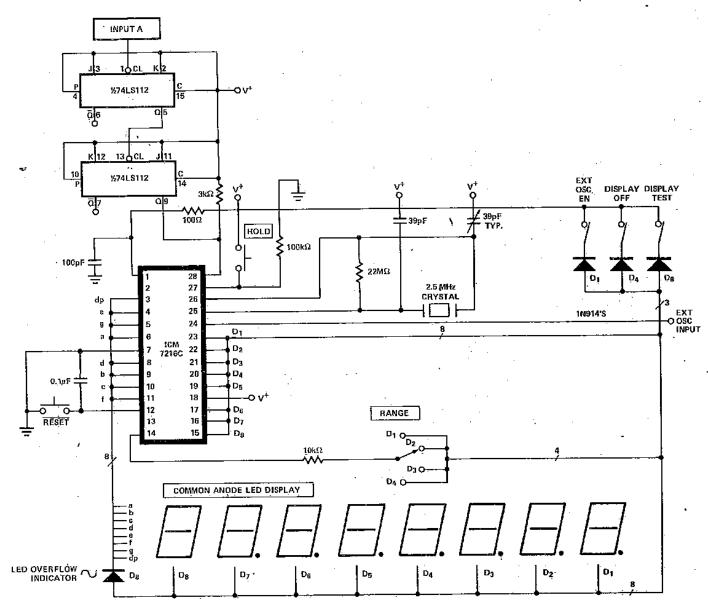

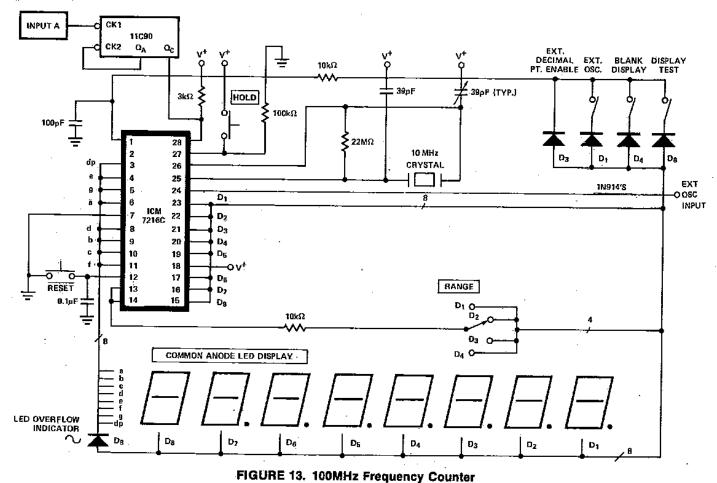

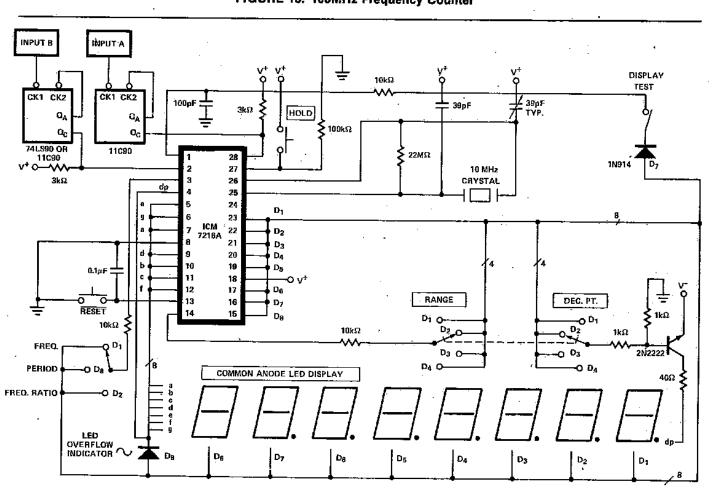

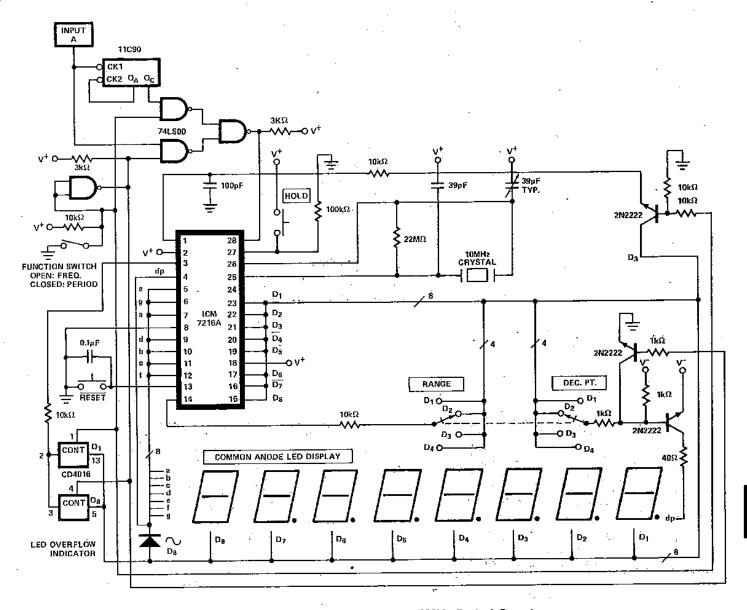

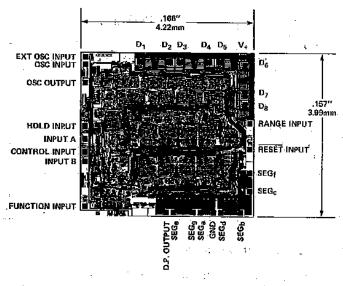

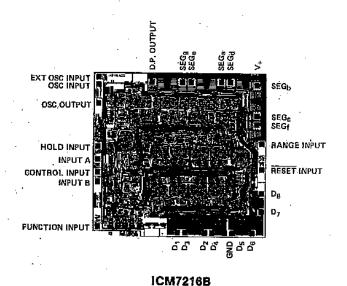

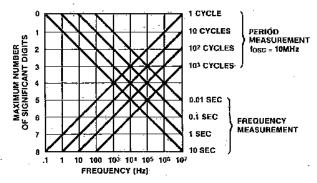

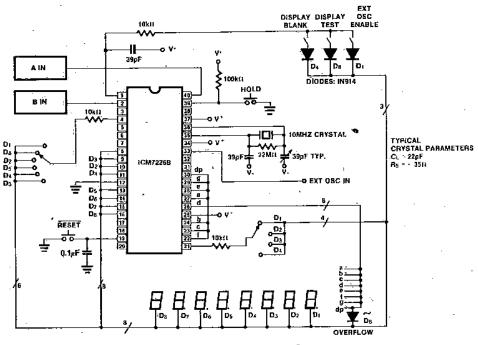

# ICM7216A/B/C/D 10 MHz Universal/ Frequency Counters

### **FEATURES**

### **ALL VERSIONS:**

- Functions as a frequency counter.

Measures frequencies from DC to 10 MHz

- Four internal gate times:

0.01 sec, 0.1 sec, 1 sec, 10 sec in frequency counter mode

- Output directly drives digits and segments of large multiplexed LED displays.

Common anode and common cathode versions

- Single nominal 5V supply required

- Stable high frequency oscillator, uses either 1 MHz or 10 MHz crystal

- Internally generated decimal points, interdigit blanking, leading zero blanking and overflow indication

- Display Off mode turns off display and puts chip into low power mode

- Hold and Reset inputs for additional flexibility

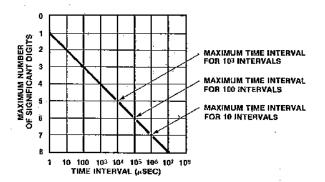

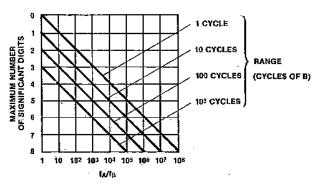

### ICM7216A AND B

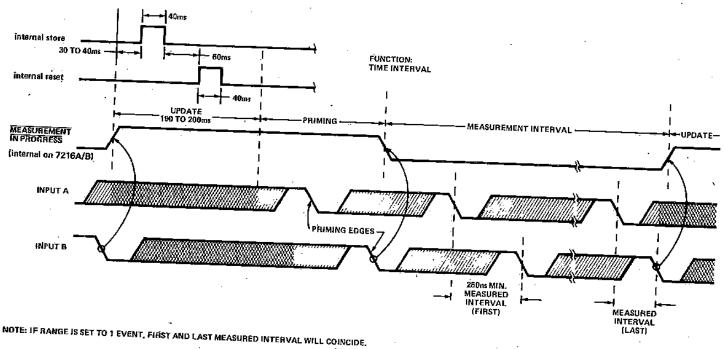

- Functions also as a period counter, unit counter, frequency ratio counter or time interval counter

- 1 cycle, 10 cycles, 100 cycles, 1000 cycles in period, frequency ratio and time interval modes

- Measures period from 0.5µs to 10s

#### ICM7216C AND D

Decimal point and leading zero blanking may be externally selected

### **GENERAL DESCRIPTION**

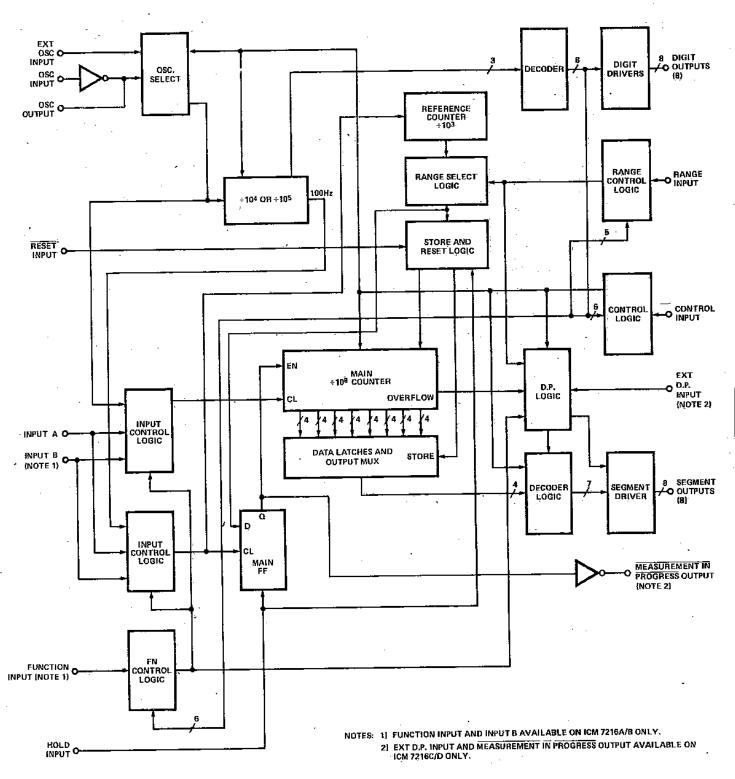

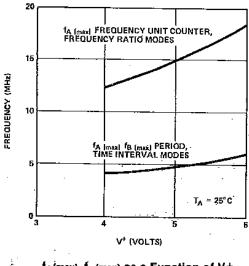

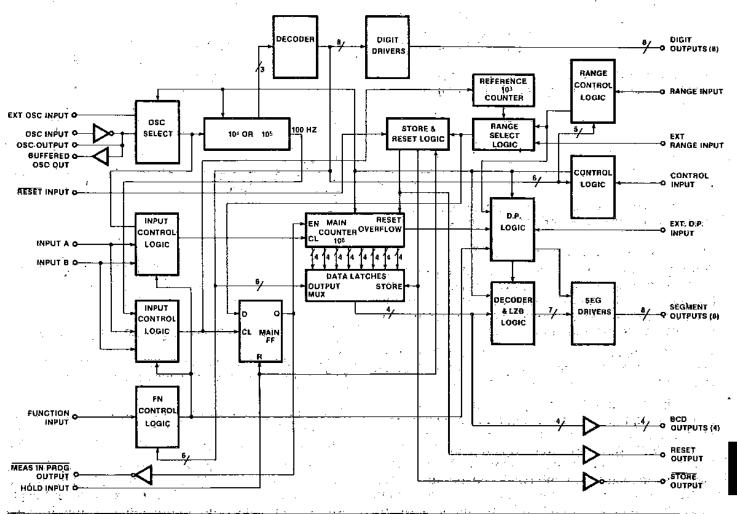

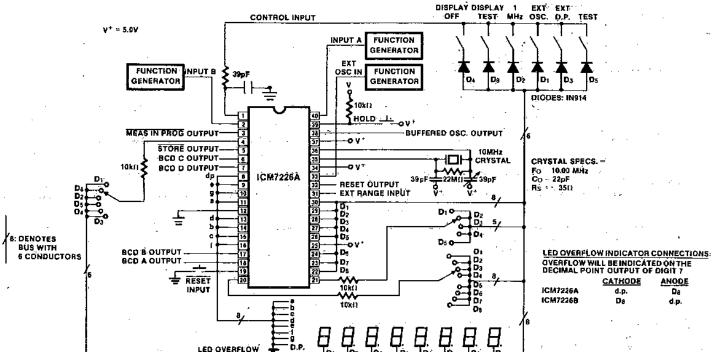

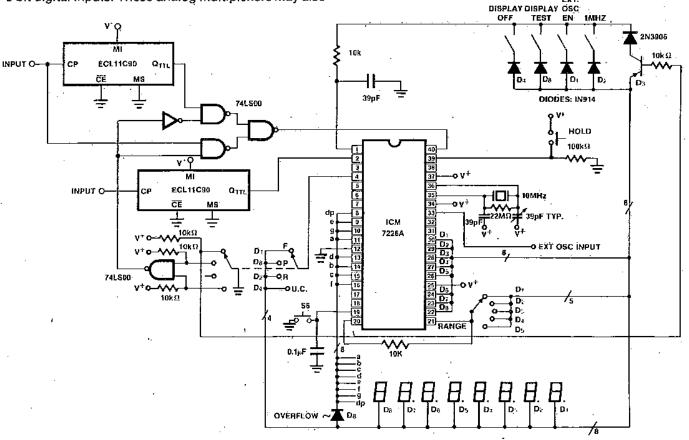

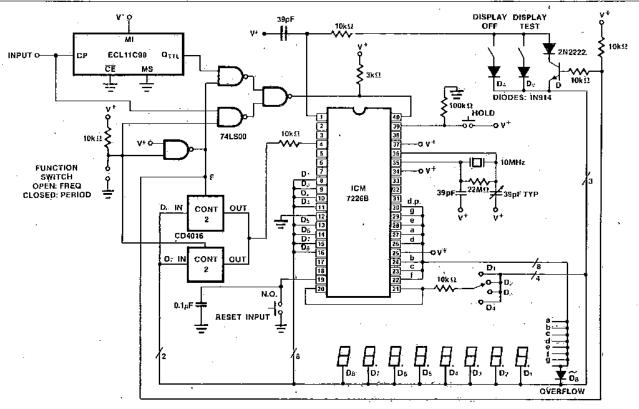

The ICM7216A and B are fully integrated Universal Counters with LED display drivers. They combine a high frequency oscillator, a decade timebase counter, an 8-decade data counter and latches, a 7-segment decoder, digit multiplexers and 8 segment and 8 digit drivers which directly drive large multiplexed LED displays. The counter inputs have a maximum frequency of 10 MHz in frequency and unit counter modes and 2 MHz in the other modes. Both inputs are digital inputs. In many applications, amplification and level shifting will be required to obtain proper digital signals for these inputs.

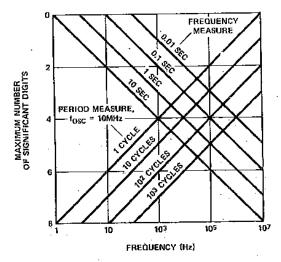

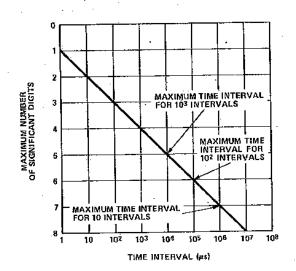

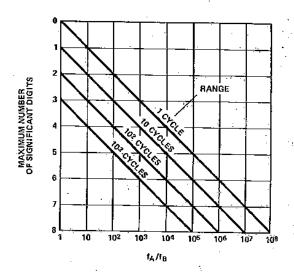

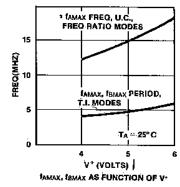

The ICM7216A and B can function as a frequency counter, period counter, frequency ratio (fa/fB) counter, time interval counter or as a totalizing counter. The counter uses either a 10 MHz or 1 MHz quartz crystal timebase. For period and time interval, the 10MHz timebase gives a 0.1 µsec resolution. In period average and time interval average, the resolution can be in the nanosecond range. In the frequency mode, the user can select accumulation times of 0.01 sec, 0.1 sec, 1 sec and 10 sec. With a 10 sec accumulation time, the frequency can be displayed to a resolution of 0.1 Hz in the least significant digit. There is 0.2 seconds between measurements in all ranges.

The ICM7216C and D function as frequency counters only, as described above.

All versions of the ICM7216 incorporate leading zero blanking. Frequency is displayed in kHz. In the iCM7216A and B, time is displayed in µsec. The display is multiplexed at 500Hz with a 12.2% duty cycle for each digit. The ICM7216A and C are designed for common anode display with typical peak segment currents of 25mA. The ICM7216B and D are designed for common cathode displays with typical peak segment currents of 12mA. In the display off mode, both digit and segment drivers are turned off, enabling the display to be used for other functions.

### ORDERING INFORMATION

Universal Counter; Common Anode LED Universal Counter; Common Cathode LED Frequency Counter; Common Anode LED Frequency Counter; Common Cathode LED

Evaluation Kit:

Use ICM7226 EV/Kit

ICM 7216 A IJI

ICM 7216 B IPI

ICM 7216 C IJI

ICM 7216 D IPI

Type Package JI - 28 pin CERDIP

PI - 28 pin PLASTIC DIP

Temperature Range -20°C to +85°C

### ICM7216

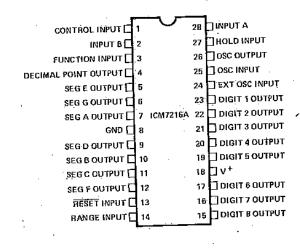

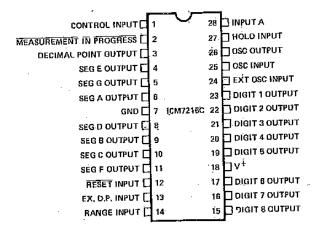

# PIN CONFIGURATIONS (outline dwgs JI, PI)

#### 28 DINPUT A CONTROL INPUT HOLD INPUT INPUT B [ 2 OSC OUTPUT FUNCTION INPUT 3 JOSC INPUT 25 DIGIT 1 CUTPUT 4 24 EXT OSC INPUT DIGIT 3 OUTPUT 23 DECIMAL POINT OUTPUT DIGIT 2 OUTPUT 6 DIGIT 4 OUTPUT 7 ICM7216B 22 SEG G OUTPUT 21 SEG E OUTPUT 20 SEG A OUTPUT рівіт в очтечт 📑 9 19 SEG D OUTPUT DIGIT 6 OUTPUT 10 18 🗖 V+ DIGIT 7 OUTPUT [ 11 17 SEG B OUTPUT DIGIT 8 OUTPUT 🗖 12 16 SEG C OUTPUT RESET INPUT 13 15 SEG F OUTPUT RANGE INPUT

| CONTROL INPUT           | <del>,                                    </del> | 28 | □INPUT A             |

|-------------------------|--------------------------------------------------|----|----------------------|

| MEASUREMENT IN PROGRESS | 2                                                | 27 | ] Ного імват         |

| DIGIT 1 OUTPUT          | 3                                                | 26 | OSC OUTPUT           |

| DIGIT 3 QUTPUT          | 4                                                | 25 | OSC INPUT            |

| DIGIT 2 OUTPUT          | 5                                                | 24 | EXT. OSC INPUT       |

| DIGIT 4 OUTPUT          | 6                                                | 23 | DECIMAL POINT OUTPUT |

| GND [                   | 7 (CM7216D                                       | 22 | I SEG G OUTPUT       |

| DIGIT 5 OUTPUT          | 8.                                               | 21 | SEG E OUTPUT         |

| ∫ DIGIT 6 OUTPUT 🗀      | 9                                                | 20 | SEG A OUTPUT         |

| DIGIT 7 OUTPUT          | 10                                               | 19 | ☐ SEG D OUTPUT       |

| DIGIT 8 OUTPUT          | u                                                | 18 | Dv⁺                  |

| RESET INPUT             | 12                                               | 17 | SEG B OUTPUT         |

| EX. D.P. INPUT          | 13                                               | 16 | SEG C OUTPUT         |

| RANGE INPUT             | 14                                               | 15 | SEG F OUTPUT         |

|                         |                                                  |    | ı                    |

### **EVALUATION KIT**

The ICM7226 Universal Counter System has all of the features of the ICM7216 plus a number of additional features. The ICM7226 Evaluation Kit consists of the ICM7226AIJL (Common Anode LED Display), a 10MHz quartz crystal, eight 7 segment 0.3" LED's, P.C. board, resistors, capacitors, diodes, switches, socket; everything needed to quickly assemble a functioning ICM7226 Universal Counter System.

# **ABSOLUTE MAXIMUM RATINGS**

| Maximum Supply Voltage                                                   |

|--------------------------------------------------------------------------|

| Voltage On Any Input or Output Terminal(1) V + + 0.3V to -0.3V           |

| Maximum Power Dissipation at 70°C                                        |

| Lead Temperature (Soldering, 10 sec) 300°C Maximum Operating Temperature |

| Range                                                                    |

|                                                                          |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions above those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

<sup>1.</sup> The ICM7216 may be triggered into a destructive latchup mode if either input signals are applied before the power supply is applied or if input or outputs are forced to voltages exceeding V+ to GND by more than 0.3 volts.

# **ELECTRICAL CHARACTERISTICS**

**TEST CONDITIONS:**  $V^+ = 5.0V$ , Test Circuit,  $T_A = 25^{\circ}$ C, unless otherwise specified.

| PARAMETER                                       | SYMBOL               | CONDITION                                 | MIN.                 | TYP.                                             | MAX.                 | UNITS                                            |

|-------------------------------------------------|----------------------|-------------------------------------------|----------------------|--------------------------------------------------|----------------------|--------------------------------------------------|

| ICM7216A/B                                      |                      |                                           |                      | - <del> </del> -                                 | mAA.                 | UNITS                                            |

| Operating Supply Current                        | j+                   | Display Off, Unused Inputs to GND         |                      | 2                                                | _                    | .                                                |

| Supply Voltage Range                            | 4                    | -20° C < TA < +85° C, INPUT A,            | +                    | +                                                | 5                    | mA                                               |

| <u> </u>                                        |                      | INPUT B Frequency at f <sub>max</sub>     | 4.75                 |                                                  | 6.0                  | l v                                              |

| Maximum Frequency<br>INPUT A, Pin 28            | fA(max)              | -20°C < TA < +85°C                        | 1                    | <del>                                     </del> | -                    | +                                                |

| MFOT A, PIN 28                                  | ļ ·                  | 4.75 < V <sup>+</sup> ≤ 6.0V, Figure 1,   | 1                    |                                                  |                      |                                                  |

|                                                 |                      | Function = Frequency, Ratio, Unit         | 1                    |                                                  |                      |                                                  |

|                                                 | <u> </u>             | Function = Period, Time Interval          | 10<br>2.5            | ]                                                |                      | MHz                                              |

| Maximum Frequency                               | f <sub>B(max)</sub>  | -20°C < TA < +85°C                        |                      | <del>                                     </del> | <del></del>          | MHz                                              |

| INPUT B, Pin 2                                  |                      | 4.75 < V <sup>+</sup> ≤ 6.0V,             | 2.5                  | 1                                                | 1                    | MHz                                              |

| Minimum Caracati                                | <u> </u>             | Figure 2                                  |                      |                                                  |                      | '*''',2                                          |

| Minimum Separation<br>INPUT A to INPUT B        |                      | -20° C < TA < +85° C                      | ]                    | 1                                                | <u> </u>             |                                                  |

| Time Interval Function                          | ļ                    | 4.75 < V <sup>+</sup> ≤ 6.0V,<br>Figure 3 | 250                  |                                                  | 1.                   | ns                                               |

| Maximum Osc. Freq. and Ext.                     | ;-                   | -20°C < TA < +85°C                        |                      | <del> </del>                                     | <u> </u>             | <u> </u>                                         |

| Osc. Frequency                                  | fosc                 | 4.75 < V <sup>+</sup> ≤ 6.0V              | 10                   |                                                  |                      | 1                                                |

| Minimum Ext. Osc. Freq.                         | fosc                 |                                           | 10                   | <del> </del>                                     |                      | MHz                                              |

| Oscillator Transconductance                     | g <sub>m</sub>       | $V^{+} = 4.75V, T_{A} = +85^{\circ}C$     |                      | <del> </del>                                     | 100                  | kHz                                              |

| Multiplex Frequency                             | fmux                 |                                           | 2000                 | <del> </del>                                     | <u> </u>             | μmhos                                            |

| Time Between Measurements                       | ımux                 | f <sub>osc</sub> = 10MHz                  |                      | 500                                              | <u> </u>             | Hz                                               |

| Input Voltages:                                 | <u> </u>             | fosc = 10MHz                              |                      | 200                                              | <u>l</u>             | ms                                               |

| Pins 2,13,25,27,28                              |                      | 20°C c.T. 1 250 C                         |                      |                                                  | ] .                  |                                                  |

| Input Low Voltage                               | VINL                 | -20°C < T <sub>A</sub> < +85°C            |                      |                                                  |                      | ·                                                |

| Input High Voltage                              | VINH                 |                                           | 3.5                  | ]                                                | 1.0                  | ] v                                              |

| Input Resistance to V <sup>+</sup>              | R <sub>IN</sub>      | $V_{IN} = V^{+} - 1.0V$                   |                      |                                                  | <del> </del>         | -                                                |

| Pins 13,24                                      |                      | VIN = V' = 1.0V                           | 100                  | 400                                              |                      | kΩ                                               |

| Input Leakage<br>Pin 27,28,2                    |                      | ·                                         | · · ·                | †                                                | <u> </u>             | <del>                                     </del> |

|                                                 | lilk .               |                                           |                      |                                                  | 20                   | μА                                               |

| Minimum Input Rate of Change                    | dV <sub>IN</sub> /dt | Supplies Well D                           |                      |                                                  | <u> </u>             |                                                  |

| ICM7216A                                        | d'A INVOC            | Supplies Well Bypassed                    | <u> </u>             | 15                                               |                      | mV/μs                                            |

| Digit Driver:                                   |                      |                                           | •                    |                                                  |                      |                                                  |

| Pins 15,16,17,19,20,21,22,23                    |                      | · 1                                       |                      |                                                  | <u>'</u>             |                                                  |

| High Output Current                             | Юн                   | V <sub>OUT</sub> = V <sup>+</sup> - 2.0V  | ,,,                  |                                                  |                      |                                                  |

| Low Output Current                              | lor                  | V <sub>OUT</sub> = + 1.0V                 | -140                 | -180<br>+0.3                                     |                      | mA                                               |

| SEGment Driver:                                 |                      |                                           | <del></del>          | . 0.3                                            | <del></del>          | mA                                               |

| Pins 4,5,6,7,9,10,11,12                         |                      | 1                                         |                      |                                                  |                      |                                                  |

| Low Output Current High Output Current          | lou                  | Vour = + 1.5V                             | 20                   | 35                                               |                      | mA                                               |

| Multiplex Inputs:                               | loн                  | $V_{OUT} = V^{+} - 2.5V$                  | · · · · · ·          | -100                                             |                      | μΑ                                               |

| Pins 1,3,14                                     | j                    | ł                                         |                      |                                                  | -                    |                                                  |

| Input Low Voltage                               | VINL                 |                                           |                      |                                                  |                      |                                                  |

| Input High Voltage                              | VINH                 | 1                                         | 2.0                  |                                                  | Q.8                  | V<br>V                                           |

| Input Resistance to GROUND                      | RIN                  | V <sub>IN</sub> = +1.0V                   | 50                   | 100                                              |                      | kΩ                                               |

| CM7216B                                         |                      |                                           |                      | — · <del> </del>                                 | <u> </u>             |                                                  |

| Digit Driver:                                   |                      |                                           | 1                    |                                                  | ļ                    |                                                  |