# 128K x 24 Three Megabit 3.3V CMOS Static RAM

Description

for ultra dense systems.

times for ease of use.

### Features

- High density 3 megabit 3.3V static RAM

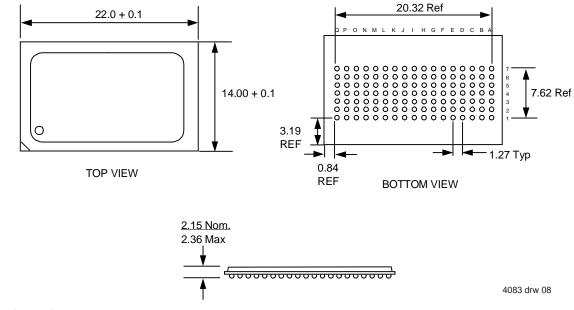

- Low profile 119 lead, 14mm x 22mm BGA (Ball Grid Array)

- Fast RAM access times: 10,12,15ns

- Single 3.3V power supply

- Multiple Vcc & GND pins for maximum noise immunity

- Inputs/outputs directly LVTTL compatible

- Commercial (0° C to +70° C) Industrial (-40° C to +85° C) temperature options

- Commercial: 10/12/15 ns

- Industrial: 12/15 ns

## **Pin Names**

| I/O0 - 23 | Data Inputs/Outputs |

|-----------|---------------------|

| A0 - 16   | Addresses           |

| CS        | Chip Select         |

| WE        | Write Enable        |

| ŌĒ        | Output Enable       |

| Vcc       | Power               |

| GND       | Ground              |

| NC        | No Connect          |

4083 tbl 01

## **Pin Configuration**

|   |    |                        |       |       |       |       |       | _     |     |       |       |       |       |       |       |     |     |

|---|----|------------------------|-------|-------|-------|-------|-------|-------|-----|-------|-------|-------|-------|-------|-------|-----|-----|

|   | A  | В                      | С     | D     | Е     | F     | G     | Н     | J   | К     | L     | М     | Ν     | Р     | R     | Т   | U   |

| 1 | NC | NC                     | I/O12 | I/O13 | I/O14 | I/O15 | I/O16 | I/O17 | NC  | I/O18 | I/O19 | I/O20 | I/O21 | I/O22 | I/O23 | NC  | NC  |

| 2 | A0 | A5                     | NC    | VCC   | GND   | VCC   | GND   | VCC   | GND | VCC   | GND   | VCC   | GND   | VCC   | NC    | A9  | A13 |

| 3 | A1 | A6                     | NC    | GND   | VCC   | GND   | VCC   | GND   | VCC | GND   | VCC   | GND   | VCC   | GND   | NC    | A10 | A14 |

| 4 | A2 | $\overline{\text{CS}}$ | NC    | GND   | GND   | GND   | GND   | GND   | GND | GND   | GND   | GND   | GND   | GND   | NC    | WE  | ŌĒ  |

| 5 | A3 | A7                     | NC    | GND   | VCC   | GND   | VCC   | GND   | VCC | GND   | VCC   | GND   | VCC   | GND   | NC    | A11 | A15 |

| 6 | A4 | A8                     | NC    | VCC   | GND   | VCC   | GND   | VCC   | GND | VCC   | GND   | VCC   | GND   | VCC   | NC    | A12 | A16 |

| 7 | NC | NC                     | I/O0  | I/O1  | I/O2  | I/O3  | I/O4  | I/O5  | NC  | I/O6  | I/07  | I/08  | I/O9  | I/O10 | I/O11 | NC  | NC  |

|   |    |                        |       |       |       |       |       |       |     |       |       |       |       |       |       |     |     |

### **Top View**

4083 drw 02

### **JANUARY 2003**

©2003 Integrated Device Technology, Inc.

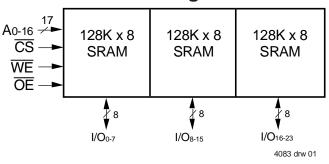

### **Functional Block Diagram**

static RAMS encapsulated in a Ball Grid Array (BGA).

The IDT7MMV4101 is a three megabit static RAM constructed on an

The IDT7MMV4101 is packaged in a plastic BGA. The BGA configu-

All inputs and outputs of the IDT7MMV4101 are LVTTL compatible and

multilayer laminate substrate using three 3.3V, 128K x 8 (IDT71V124)

ration allows 119 leads to be placed on a package 14mm by 22mm. At a

maximum of 3.5mm high, this low-profile surface mount package is ideal

operate from a single 3.3V supply. Full asynchronous circuitry requires

no clocks or refresh for operation and provides equal access and cycle

#### IDT7MMV4101 128K x 24 Three Megabit 3.3V CMOS Static RAM

## **Capacitance** (TA = +25°C, f = 1.0MHz)

| Symbol | Parameter <sup>(1)</sup> | Conditions | Max. | Unit        |

|--------|--------------------------|------------|------|-------------|

| Cin    | Input Capacitance        | Vin = 3dV  | 20   | pF          |

| Cvo    | I/O Capacitance          | Vout = 3dV | 10   | pF          |

|        |                          |            |      | 4083 tbl 02 |

NOTE:

1. This parameter is guaranteed by design but not tested.

### **Truth Table**

| Mode             | <u>CS</u> | ŌE | WE | I/O     | Power   |  |

|------------------|-----------|----|----|---------|---------|--|

| Standby          | Н         | Х  | Х  | High-Z  | Standby |  |

| Read             | L         | L  | Н  | DATAOUT | Active  |  |

| Write            | L         | Х  | L  | DATAℕ   | Active  |  |

| Outputs Disabled | L         | Н  | Н  | High-Z  | Active  |  |

4083 tbl 04

## **Recommended DC Operating Conditions**

| Symbol             | Parameter          | Min.                | Тур. | Max.                     | Unit |

|--------------------|--------------------|---------------------|------|--------------------------|------|

| Vcc <sup>(1)</sup> | Supply Voltage     | 3.15                | 3.3  | 3.6                      | V    |

| Vcc <sup>(2)</sup> | Supply Voltage     | 3.0                 | 3.3  | 3.6                      | V    |

| GND                | Ground             | 0                   | 0    | 0                        | V    |

| ViH                | Input High Voltage | 2.0                 |      | Vcc + 0.3 <sup>(4)</sup> | V    |

| Vil                | Input Low Voltage  | -0.3 <sup>(3)</sup> |      | 0.8                      | V    |

NOTES:

1. For 7MMV4101S10BG only.

2. For all speed grades except 7MMV4101S10BG.

3. VIL (min) = -1.5V for pulse width less than 5ns, once per cycle.

4. VIH (max) = Vcc + 1.5V for pulse width less than 5ns, once per cycle.

## Absolute Maximum Ratings<sup>(1)</sup>

| Symbol | Rating                                  | Commercial      | Industrial      | Unit |

|--------|-----------------------------------------|-----------------|-----------------|------|

| Vcc    | Supply Voltage<br>Relative to GND       | -0.5 to +4.6    | -0.5 to +4.6    | V    |

| Vterm  | Terminal Voltage with<br>Respect to GND | -0.5 to Vcc+0.5 | -0.5 to Vcc+0.5 | V    |

| Та     | Operating<br>Temperature                | 0 to +70        | -40 to +85      | °C   |

| Tbias  | Temperature<br>Under Bias               | -10 to +85      | -10 to +85      | °C   |

| Tstg   | Storage Temperature                     | -55 to +125     | -55 to +125     | °C   |

| Ιουτ   | DC Output Current                       | 50              | 50              | mA   |

NOTES:

4083 tbl 03

1. Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

## **DC Electrical Characteristics** (Vcc = 3.3V ±10%)

| Symbol | Parameter              | Test Condition                                             | Min. | Max. | Unit |

|--------|------------------------|------------------------------------------------------------|------|------|------|

| llul   | Input Leakage Current  | Vcc = Max., VIN = GND to Vcc                               |      | 15   | μΑ   |

| lllol  | Output Leakage Current | Vcc = Max., $\overline{CS} \ge V_{H}$ , Vout = GND to Vcc, |      | 5    | μΑ   |

| Vol    | Output Low Voltage     | Iol = 8mA, Vcc = Min.                                      |      | 0.4  | V    |

| Vон    | Output High Voltage    | $I_{OH} = -4mA$ , $V_{CC} = Min$ .                         | 2.4  |      | V    |

4083 tbl 06

|        |                                      |                                                                                                                          | -10 <sup>(1)</sup> | -12  | -15  |      |

|--------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--------------------|------|------|------|

| Symbol | Parameter                            | Test Condition                                                                                                           | Max.               | Max. | Max. | Unit |

| lcc    | Dynamic Operating<br>Current         | $V_{CC} = Max., \overline{CS} \le V_{IL},$<br>f = fMax, Outputs Open                                                     | 295                | 275  | 255  | mA   |

| lsb    | Standby Power<br>Supply Current      | $V_{CC} = Max., \overline{CS} \ge V_{H}, f = f_{MAX}, Outputs Open$                                                      | 95                 | 85   | 85   | mA   |

| ISB1   | Full Standby Power<br>Supply Current | $\label{eq:constraint} \begin{split} \overline{CS} &\geq Vcc - 0.2V, \ f=0 \\ V_N &> Vcc - 0.2V \ or < 0.2V \end{split}$ | 10                 | 10   | 10   | mA   |

2

NOTES:

1. Commercial temperature only, Vcc = -5% to +10%.

4083 tbl 07

# **Commercial and Industrial Temperature Ranges**

#### IDT7MMV4101 128K x 24 Three Megabit 3.3V CMOS Static RAM

**AC Test Conditions**

| Input Pulse Levels            | GND to 3.0V         |

|-------------------------------|---------------------|

| Input Rise/Fall Times         | 3ns                 |

| Input Timing Reference Levels | 1.5V                |

| Output Reference Levels       | 1.5V                |

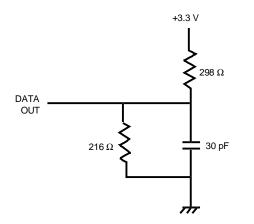

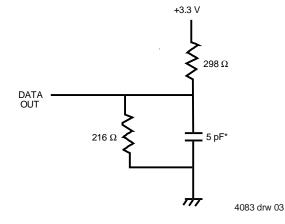

| Output Load                   | See Figures 1 and 2 |

4083 tbl 08

Figure 1. Output Load

Figure 2. Output Load (for toLz, toHz, tCHz, tCLz, tWHZ, toW) \* Includes scope and jig.

4083 tbl 09

# **AC Electrical Characteristics**<sup>(2)</sup>

(Vcc = 3.3V ±10%)

|                     |                                    | -1   | 0 <sup>(3)</sup> | -    | 12       | -15  |      |      |

|---------------------|------------------------------------|------|------------------|------|----------|------|------|------|

| Symbol              | Parameter                          | Min. | Max.             | Min. | Max.     | Min. | Max. | Unit |

| Read Cycle          |                                    |      |                  |      |          |      |      |      |

| trc                 | Read Cycle Time                    | 10   |                  | 12   |          | 15   |      | ns   |

| taa                 | Address Access Time                |      | 10               |      | 12       |      | 15   | ns   |

| tacs                | Chip Select Access Time            |      | 10               |      | 12       |      | 15   | ns   |

| tcLz <sup>(1)</sup> | Chip Select to Output in Low-Z     | 3    |                  | 3    |          | 3    |      | ns   |

| toe                 | Output Enable to Output Valid      |      | 4                |      | 6        |      | 7    | ns   |

| toLz <sup>(1)</sup> | Output Enable to Output in Low-Z   | 0    |                  | 0    |          | 0    |      | ns   |

| tcHz <sup>(1)</sup> | Chip Deselect to Output in High-Z  |      | 5                |      | 6        |      | 7    | ns   |

| tohz <sup>(1)</sup> | Output Disable to Output in High-Z |      | 5                |      | 6        |      | 7    | ns   |

| tон                 | Output Hold from Address Change    | 3    |                  | 3    |          | 3    |      | ns   |

| tpu <sup>(1)</sup>  | Chip Select to Power-Up Time       | 0    |                  | 0    |          | 0    |      | ns   |

| tpd <sup>(1)</sup>  | Chip Deselect to Power-Down Time   |      | 10               |      | 12       |      | 15   | ns   |

| Nrite Cycle         |                                    |      | <u>8</u>         | 8    | <u>.</u> |      |      |      |

| twc                 | Write Cycle Time                   | 10   |                  | 12   |          | 15   |      | ns   |

| tcw                 | Chip Select to End-of-Write        | 8    |                  | 10   |          | 12   | _    | ns   |

| taw                 | Address Valid to End-of-Write      | 8    |                  | 10   |          | 12   |      | ns   |

| tas                 | Address Set-up Time                | 0    |                  | 0    |          | 0    |      | ns   |

| twp                 | Write Pulse Width                  | 8    |                  | 10   |          | 12   |      | ns   |

| twr                 | Write Recovery Time                | 0    |                  | 0    |          | 0    |      | ns   |

| twHz <sup>(1)</sup> | Write Enable to Output in High-Z   |      | 5                |      | 5        |      | 5    | ns   |

| tow                 | Data to Write Time Overlap         | 6    |                  | 6    |          | 7    |      | ns   |

| tон                 | Data Hold from Write Time          | 0    |                  | 0    |          | 0    | _    | ns   |

| tow <sup>(1)</sup>  | Output Active from End-of-Write    | 3    |                  | 3    |          | 3    |      | ns   |

NOTES:

1. This parameter is guaranteed by design but not tested.

2. These specifications are for the individual 71V124 Static RAMs.

3. Commercial temperature only, Vcc = -5% to +10%.

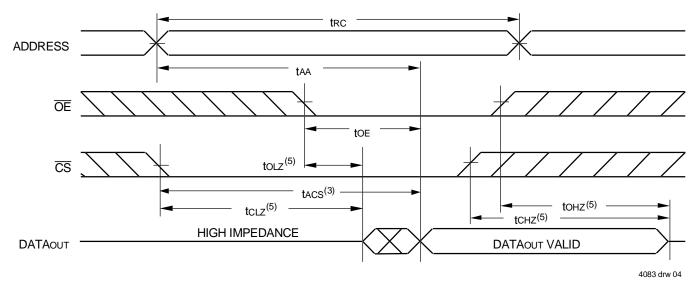

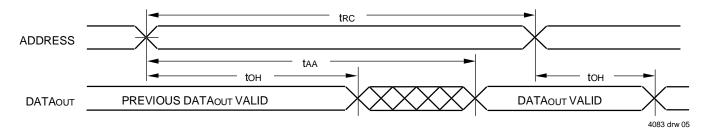

# Timing Waveform of Read Cycle No. 1<sup>(1)</sup>

## Timing Waveform of Read Cycle No. 2<sup>(1,2,4)</sup>

#### NOTES:

- 1.  $\overline{\text{WE}}$  is HIGH for Read Cycle.

- 2. Device is continuously selected,  $\overline{CS}$  is LOW.

- 3. Address must be valid prior to or coincident with the later of  $\overline{CS}$  transition LOW; otherwise taa is the limiting parameter.

- 4.  $\overline{OE}$  is LOW.

- 5. Transition is measured ±200mV from steady state.

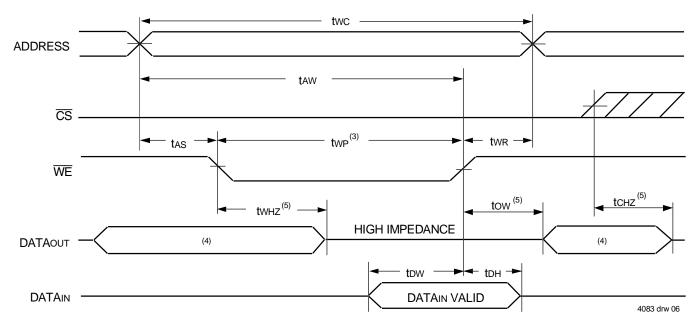

# Timing Waveform of Write Cycle No. 1 ( $\overline{WE}$ Controlled Timing)<sup>(1,4,5)</sup>

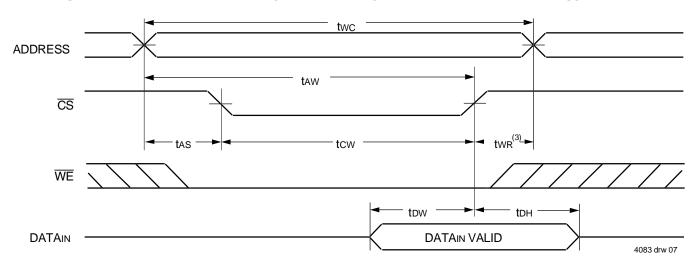

Timing Waveform of Write Cycle No. 2 (CS Controlled Timing)<sup>(1, 4)</sup>

#### NOTES:

- 1. A write occurs during the overlap of a LOW  $\overline{\text{CS}}$  and a LOW  $\overline{\text{WE}}$ .

- 2.  $\overline{OE}$  is continuously HIGH. During a  $\overline{WE}$  controlled write cycle with  $\overline{OE}$  LOW, twp must be greater than or equal to twHz + tow to allow the I/O drivers to turn off and data to be placed on the bus for the required tow. If  $\overline{OE}$  is HIGH during a  $\overline{WE}$  controlled write cycle, this requirement does not apply and the minimum write pulse is the specified twp.

- 3. During this period, I/O pins are in the output state, and input signals must not be applied.

- 4. If the CS LOW transition occurs simultaneously with or after the WE LOW transition, the outputs remain in a high impedance state. CS must be active during the tcw write period.

- 5. Transition is measured ±200mV from steady state.

#### IDT7MMV4101 128K x 24 Three Megabit 3.3V CMOS Static RAM

## **Package Dimensions**

1. All dimensions are in mm.

NOTES:

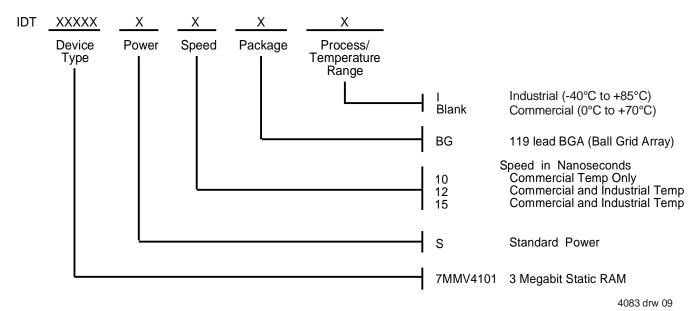

## **Ordering Information**

## **Datasheet History**

| 09/18/00 |       | Add datasheet history                                  |

|----------|-------|--------------------------------------------------------|

|          | Pg. 2 | Reduce ICC, ISB, and ISB1 to reflect K step die shrink |

| 01/07/03 |       | Changed datasheet from Prelininary to final release    |

*CORPORATE HEADQUARTERS* 2975 Stender Way Santa Clara, CA 95054 for SALES: 800-345-7015 or 408-727-6116 fax:408-492-8674 www.idt.com for Tech Support: sramhelp@idt.com 800 544-7726, x4033

The IDT logo is a registered trademark of Integrated Device Technology, Inc.

Copyright © Each Manufacturing Company.

All Datasheets cannot be modified without permission.

This datasheet has been download from :

www.AllDataSheet.com

100% Free DataSheet Search Site.

Free Download.

No Register.

Fast Search System.

www.AllDataSheet.com