# **DATA BOOK**

W83C553F

**SYSTEM I/O**

**CONTROLLER**

WITH PCI

**ARBITER**

#### **Copyright Notice**

Copyright 1995, 1996, 1997 WINBOND SYSTEMS LABORATORY.

All rights reserved.

Issued: September 27, 1995

Publication no: 2565; Ver. A.6

Issued: October 1, 1996

Publication no: 2565; Ver. A.6.2

Issued: March 1, 1997

Publication no: 2565; Ver. A.7.0b

Issued: September 1, 1997

Publication no: 2565; Ver.A.7.0c

Issued: February 22, 1998

Publication no. 2565; Ver.A.7.0d

#### Disclaimer

This document contains information on a product under development at WINBOND SYSTEMS

LABORATORY. The information is intended to help you to evaluate this product. WINBOND SYSTEMS

LABORATORY reserves the right to change or discontinue work on this proposed product without notice.

WINBOND SYSTEMS

LABORATORY makes no warranty

for the use of its products and bears

no responsibility for any errors which

appear in this document.

Specifications are subject to change

without notice.

#### Trademarks

The company and product names mentioned in this document may be the trademarks or registered trademarks of their manufacturers.

W I N B O N D SYSTEMS LABORATORY

2727 North First Street, San Jose, CA 95134 USA W83C553F Table of Contents

### **PREFACE**

This document describes the function and use of the Winbond Systems Laboratory W83C553F System I/O (SIO) Controller with PCI arbiter. It provides all of the information necessary for design engineers to incorporate the device into notebook and desktop computer systems.

#### **Organization of the Manual**

The information in this document is organized into the following seven chapters:

Chapter 1 This consists of an overview discussion of the product and

General information its features. Included are the stylistic conventions used in

this manual.

Chapter 2 Provides pin-out diagrams and pin descriptions.

Pin Descriptions

Chapter 3 Discusses the design of the device and the implementation

System Architecture of the device's features.

Chapter 4 Describes the software control of the chip set's various

Register Information functions.

Chapter 5 Provides the operating specifications for the device.

Electrical Specifications

Chapter 6 Provides timing diagrams and tables of timing values.

**Timing Diagrams**

Chapter 7 Shows the critical dimensions of the device.

Mechanical Description

Chapter 8 Shows the temperature calculation of the device.

Thermal Information

Appendix A I/O Driver Characteristics

W83C553F Table of Contents

## **TABLE OF CONTENTS**

| Prefa | ce    |                                                                 | 1  |  |  |  |  |  |  |  |

|-------|-------|-----------------------------------------------------------------|----|--|--|--|--|--|--|--|

|       | 1.0   | General Information                                             | 5  |  |  |  |  |  |  |  |

|       | 1.1   | Features                                                        |    |  |  |  |  |  |  |  |

|       | 1.2   | General Description                                             |    |  |  |  |  |  |  |  |

|       | 1.3   | Stylistic Conventions Used in this Manual                       | 9  |  |  |  |  |  |  |  |

| 2.0   | Pin D | escriptions                                                     |    |  |  |  |  |  |  |  |

|       | 2.1   | Pin Assignments                                                 |    |  |  |  |  |  |  |  |

|       | 2.2   | Pin Description                                                 |    |  |  |  |  |  |  |  |

| 3.0   |       | em Architecture                                                 |    |  |  |  |  |  |  |  |

| 0.0   | 3.1   | Overview                                                        |    |  |  |  |  |  |  |  |

|       | 3.2   | Active State                                                    |    |  |  |  |  |  |  |  |

|       | 3.3   | Bus Structures                                                  |    |  |  |  |  |  |  |  |

|       | 3.4   | PCI-to-ISA Bridge                                               |    |  |  |  |  |  |  |  |

|       | 3.5   | PCI Bus Cycles                                                  |    |  |  |  |  |  |  |  |

|       | 3.6   | PCI I/O Read Cycle                                              |    |  |  |  |  |  |  |  |

|       | 3.7   | PCI I/O Write Cycle                                             |    |  |  |  |  |  |  |  |

|       |       | PCI Configuration Read Cycle                                    |    |  |  |  |  |  |  |  |

|       | 3.8   |                                                                 |    |  |  |  |  |  |  |  |

|       | 3.9   | PCI Configuration Write Cycle                                   |    |  |  |  |  |  |  |  |

|       | 3.10  | PCI Memory Read                                                 |    |  |  |  |  |  |  |  |

|       | 3.11  | PCI Memory Write                                                |    |  |  |  |  |  |  |  |

|       | 3.12  | PCI Memory Read Line                                            |    |  |  |  |  |  |  |  |

|       | 3.13  | PCI Memory Write and Invalidate                                 |    |  |  |  |  |  |  |  |

|       | 3.14  | Transaction Termination                                         |    |  |  |  |  |  |  |  |

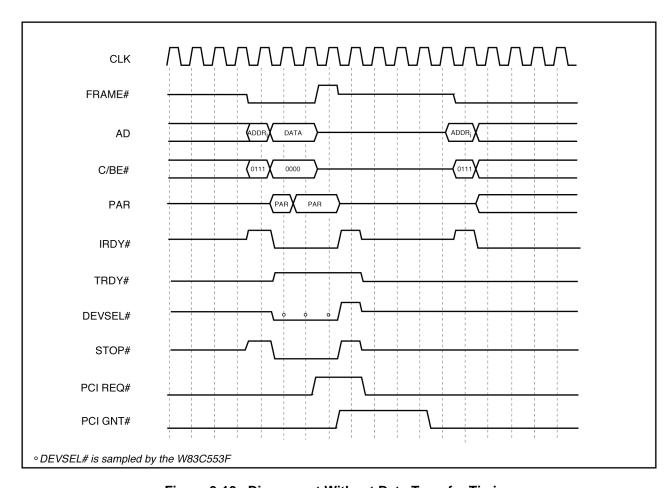

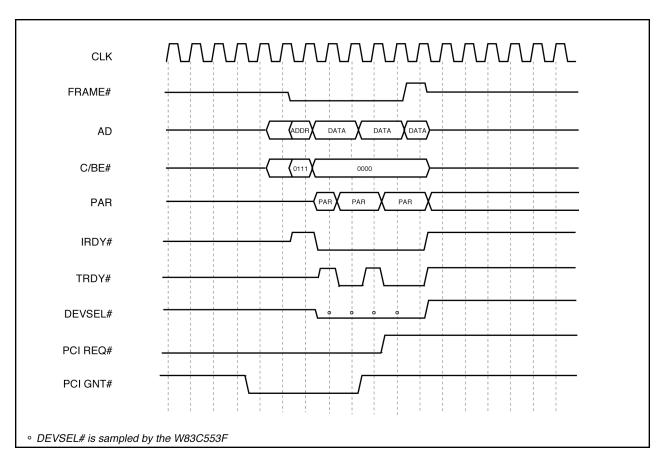

|       |       | 3.14.1 PCI Disconnect With Data Transfer Timing                 |    |  |  |  |  |  |  |  |

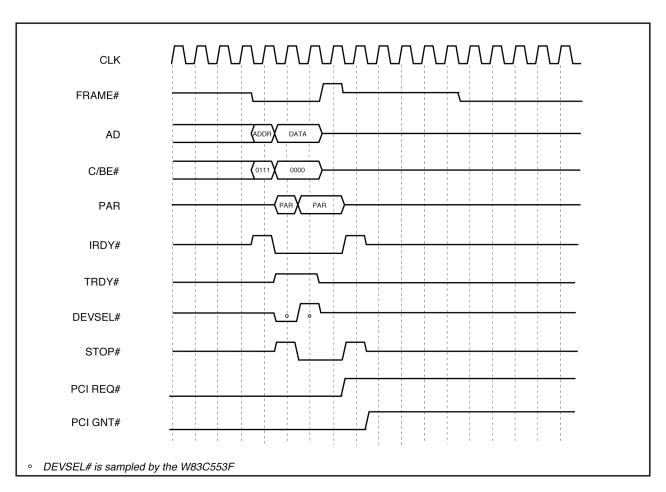

|       |       | 3.14.2 PCI Disconnect Without Data Transfer Timing              |    |  |  |  |  |  |  |  |

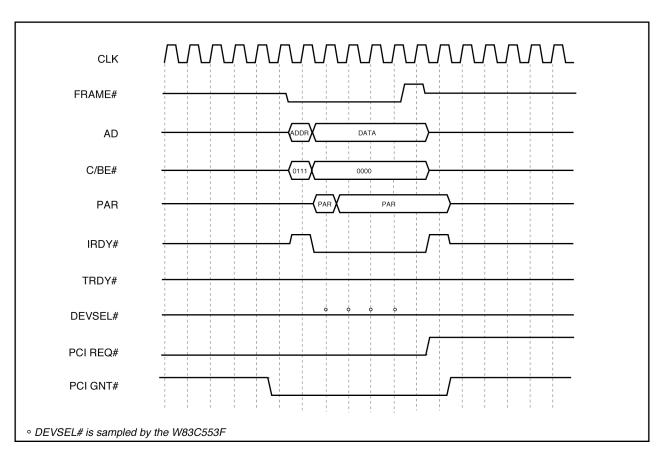

|       |       | 3.14.3 PCI Target Abort Timing                                  |    |  |  |  |  |  |  |  |

|       |       | 3.14.4 PCI Preemption Timing                                    |    |  |  |  |  |  |  |  |

|       |       | 3.14.5 PCI Master Abort Timing                                  |    |  |  |  |  |  |  |  |

|       | 3.15  | IDE Interface Operation                                         |    |  |  |  |  |  |  |  |

|       | 3.16  | PIO Transfers                                                   |    |  |  |  |  |  |  |  |

|       | 3.17  | 32-Bit Data Transfers                                           |    |  |  |  |  |  |  |  |

|       | 3.18  | Bus Master Transfers                                            |    |  |  |  |  |  |  |  |

|       | 3.19  | 82C59A Interrupt Controller                                     | 49 |  |  |  |  |  |  |  |

|       | 3.20  | 82C37A DMA Controller                                           |    |  |  |  |  |  |  |  |

|       | 3.21  | 82C54 Counter/Timer                                             | 50 |  |  |  |  |  |  |  |

|       | 3.22  | PCI Arbiter                                                     | 50 |  |  |  |  |  |  |  |

|       | 3.23  | Break Events                                                    |    |  |  |  |  |  |  |  |

|       | 3.24  | CPU Modes (X86 or PowerPC)                                      | 51 |  |  |  |  |  |  |  |

| 4.0   | Regis | ster Information                                                | 52 |  |  |  |  |  |  |  |

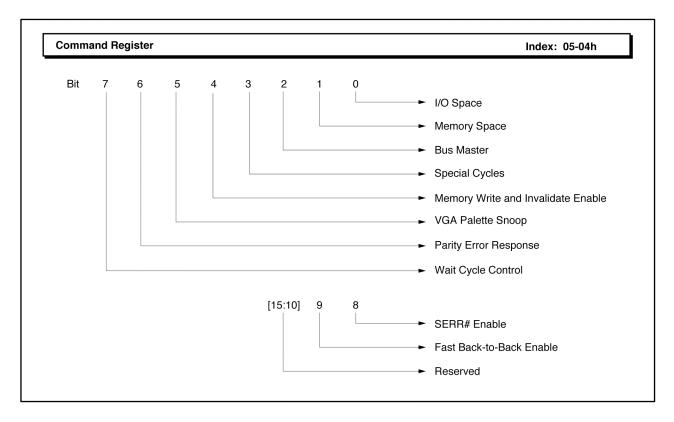

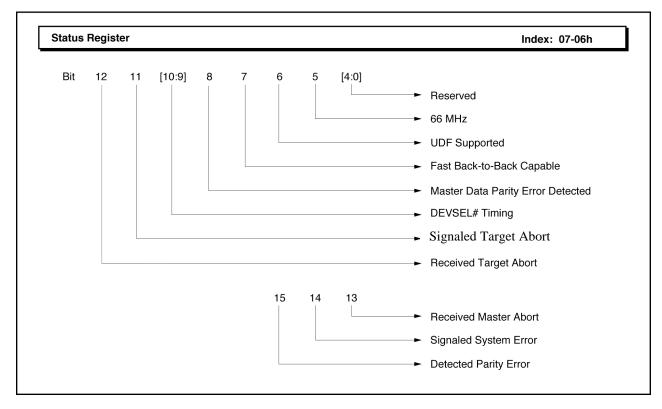

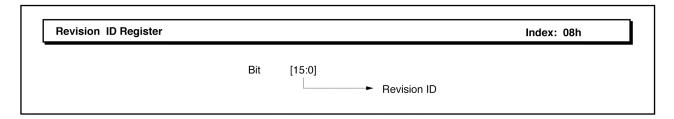

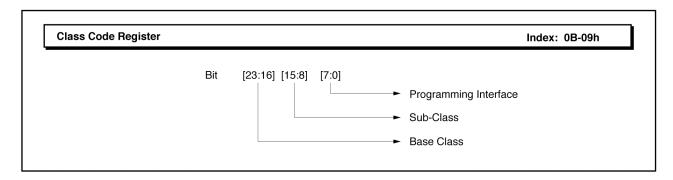

|       | 4.1   | PCI Configuration Space - ISA Bridge Registers (Function 0)     | 54 |  |  |  |  |  |  |  |

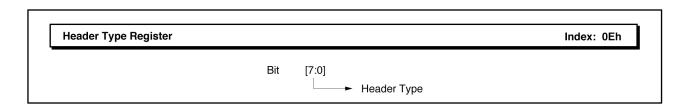

|       |       | 4.1.1 Function 0 Header Registers                               |    |  |  |  |  |  |  |  |

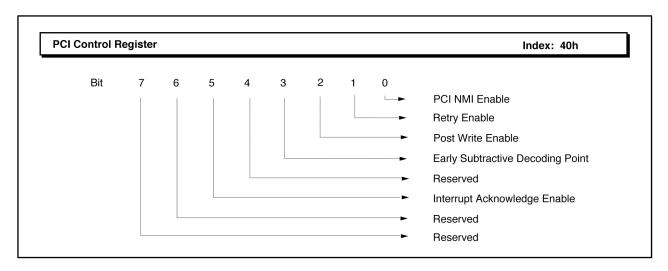

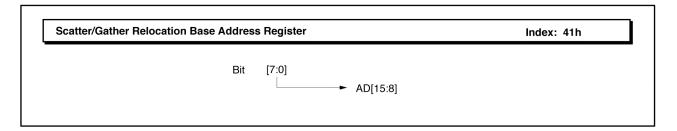

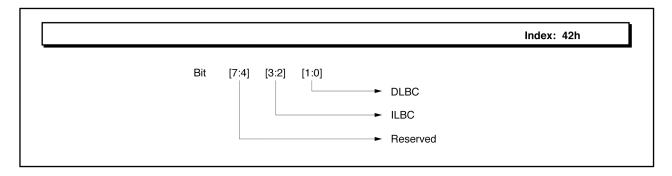

|       |       | 4.1.2 Function 0 Control Registers                              | 58 |  |  |  |  |  |  |  |

|       | 4.2   | ISA Bridge (Function 0) I/O Registers                           | 78 |  |  |  |  |  |  |  |

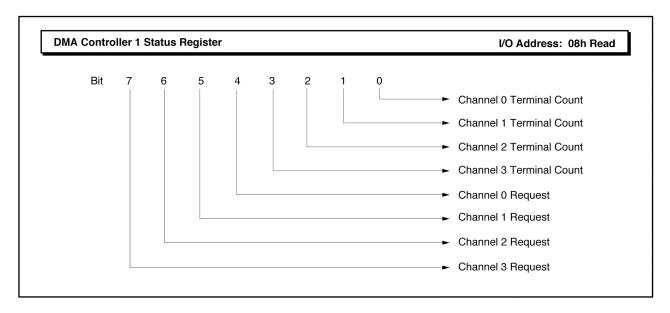

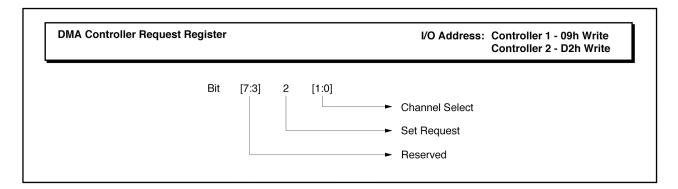

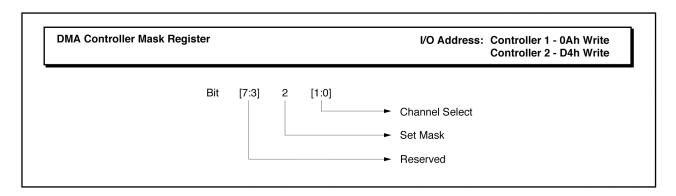

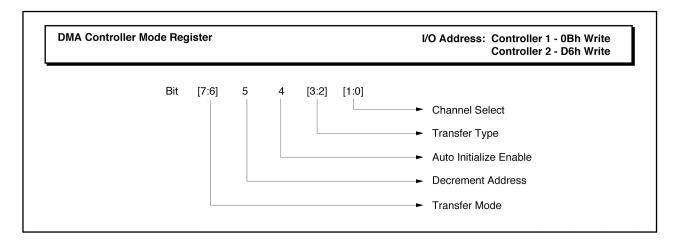

|       |       | 4.2.1 DMA Controller I/O Registers                              |    |  |  |  |  |  |  |  |

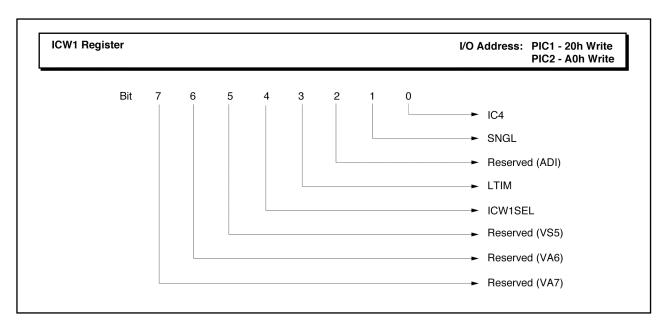

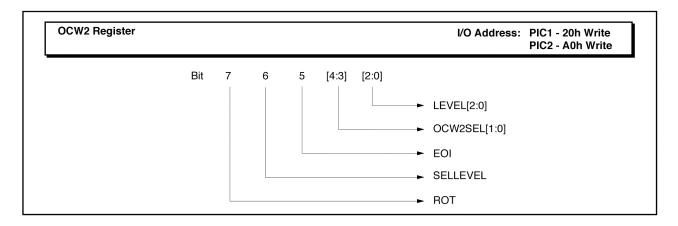

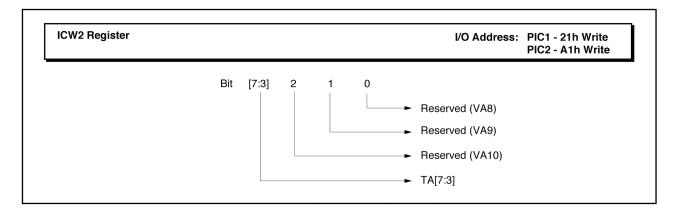

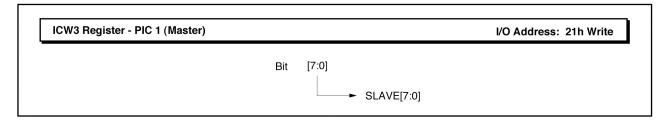

|       |       | 4.2.2 Programmable Interrupt Controller (PIC) Registers         |    |  |  |  |  |  |  |  |

|       |       | 4.2.3 Counter/Timer I/O Registers                               |    |  |  |  |  |  |  |  |

|       |       | 4.2.4 Miscellaneous I/O Control Registers                       |    |  |  |  |  |  |  |  |

|       | 4.3   | PCI Configuration Space - Bus Master IDE Registers (Function 1) |    |  |  |  |  |  |  |  |

|       |       | 4.3.1 Function 1 Header Registers                               |    |  |  |  |  |  |  |  |

W83C553F Table of Contents

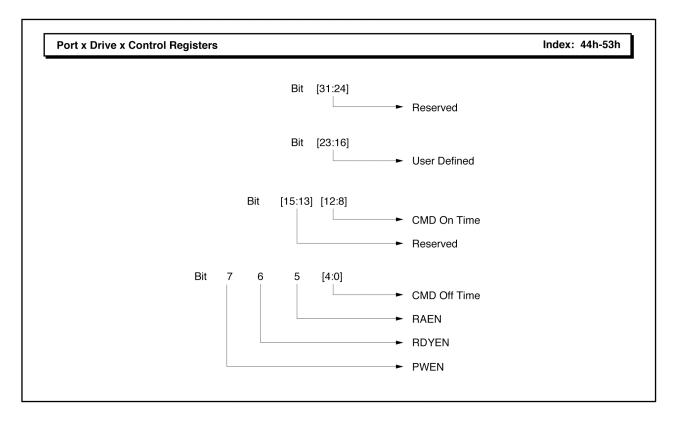

|        | 4.3.2                                        | Function 1 Control Registers                                                                                                 | 123                                           |

|--------|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

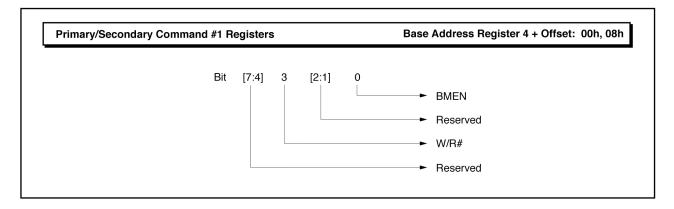

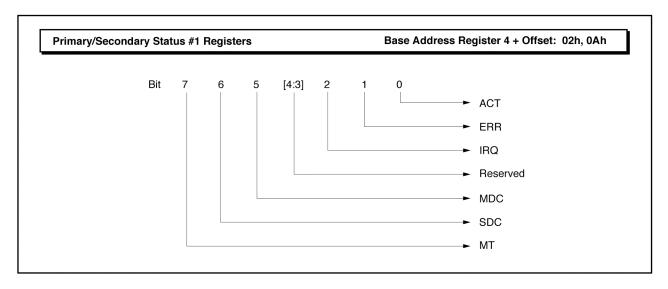

| 4.4    | Bus Ma                                       | aster IDE (Function 1) I/O Registers                                                                                         | 129                                           |

|        | 4.4.1                                        | Primary/Secondary Command Registers                                                                                          | 130                                           |

|        | 4.4.2                                        | Primary/Secondary Status Registers                                                                                           | 131                                           |

|        | 4.4.3                                        | Primary/Secondary PRD Table                                                                                                  | 132                                           |

|        |                                              |                                                                                                                              | 100                                           |

| Electi | ricai Spec                                   | cifications                                                                                                                  | 133                                           |

| Timin  | g Diagrai                                    | ms                                                                                                                           |                                               |

|        | PCI Tin                                      | ning Diagrams                                                                                                                | 136                                           |

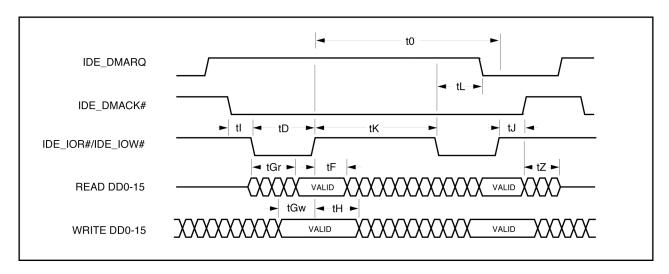

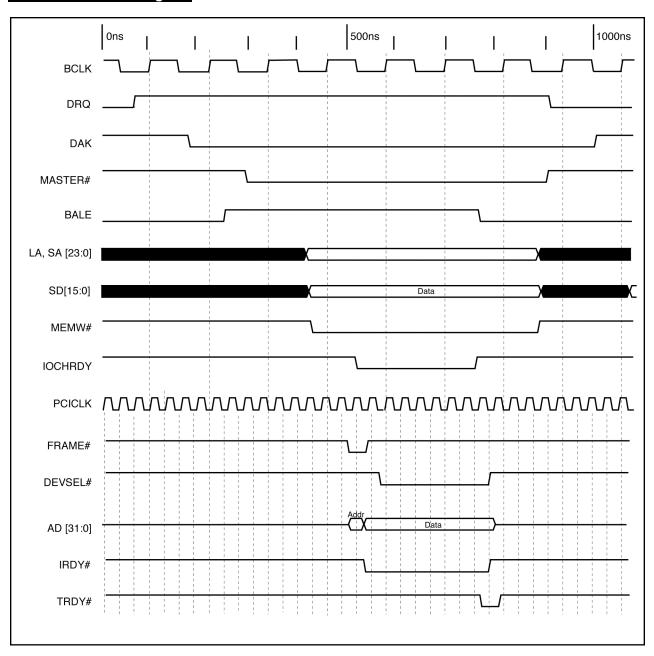

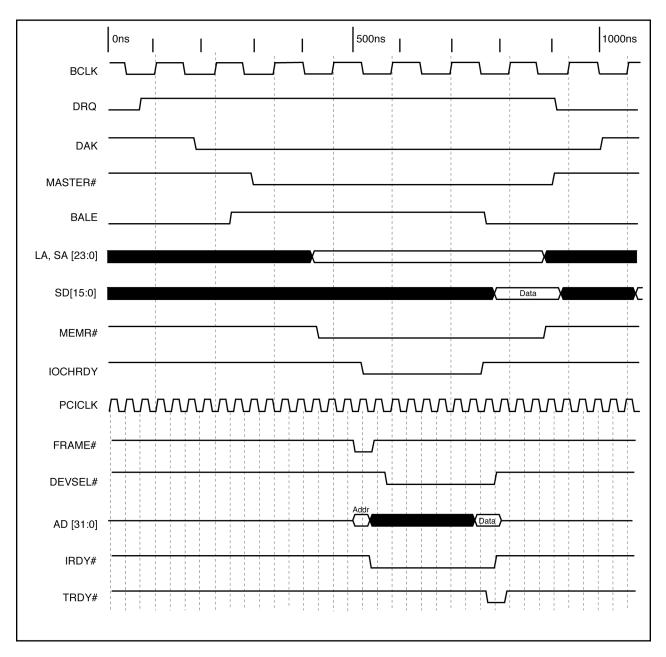

| ~      | IDE/AT                                       | A Data Transfers                                                                                                             | 142                                           |

| 6.3    | ISA Bu                                       | s Timing                                                                                                                     | 150                                           |

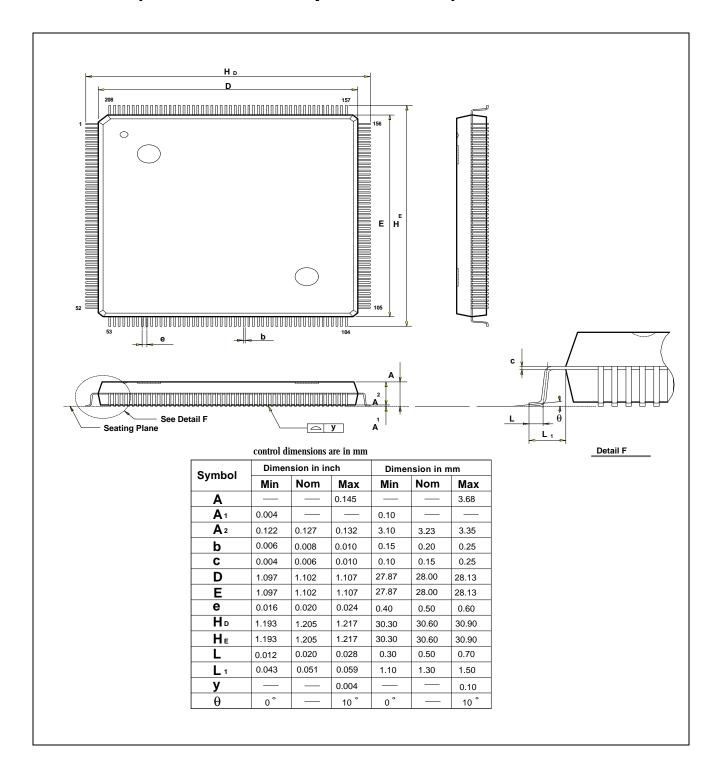

| Mech   | anical De                                    | escription                                                                                                                   | 153                                           |

| Thern  | nal Inforn                                   | nation                                                                                                                       | 154                                           |

|        |                                              |                                                                                                                              |                                               |

|        | Electr<br>Timin<br>6.1<br>6.2<br>6.3<br>Mech | 4.4 Bus Ma 4.4.1 4.4.2 4.4.3  Electrical Spec Timing Diagra 6.1 PCI Tir 6.2 IDE/AT 6.3 ISA Bu Mechanical De Thermal Informal | 4.4 Bus Master IDE (Function 1) I/O Registers |

## 1.0 GENERAL INFORMATION

#### 1.1 Features

#### **High Integration PCI-ISA solution**

- Optimized for lowest system cost

- Complies with PCI Revision 2.0 specification

- Universal PCI device supporting x86 and PowerPC (non-x86) modes of operation

#### Nand tree on most signal pins to facilitate board level testing in PCB manufacturing environment

#### **Integrated PCI Bus Master IDE controller**

- Dual channel Bus Master IDE for up to 4 peripherals, including hard drives, ATAPI (IDE) CD-ROMs, tapes, etc.

- Multi-threading capability allows two simultaneous I/O processes

- Independent IDE Timing registers allow fast/slow devices on the same cable

- Two independent DMA channels for Bus Master scatter/gather DMA transfers across the PCI bus

- Large 64 byte DMA FIFO for zero wait state PCI burst transfers

- Support for multiword DMA Mode 1 (13.3 MB/s), Mode 2 (16.6 MB/s) IDE drives

- PIO IDE support for Modes 0-4 disks

- Edge rate controlled outputs directly drive IDE headers

- Four byte pre-fetch and posted write buffers

- DMA channels can be re-configured for P-n-P motherboard devices

- Software and register set compatible with Intel Bus Master PCI-IDE specification (SFF 8038i)

- Supported by existing device drivers for MS-DOS, Windows, NT 3.1, NT 3.5x, NT4.0, OS/2 2.1, OS/2 Warp, NetWare 3.12 and 4.x\*\*

- Recompiled PowerPC device drivers also available

#### **PCI** Arbiter

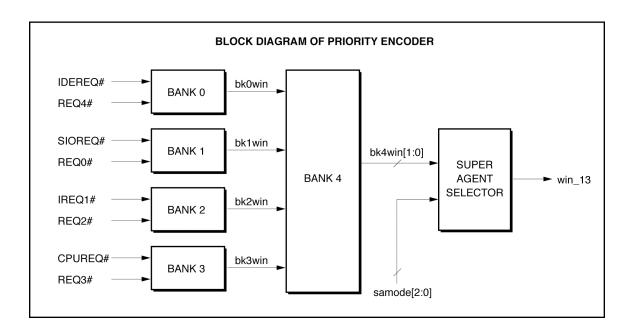

- Supports CPU, IDE, ISA and five additional bus masters

- Programmable access windows allow fine tuning of PCI access for each bus master

- Can be disabled on power-up via strapped pin

\*\* OS/2, Novell driver by DTC

#### Power Management Break Event support for Green PC applications

#### Built-in Integrated Peripheral Controller (IPC) with standard PC-AT peripherals

- Two 82C37A DMA controllers (types A, B, and F)

- 32-bit addressing allows use of alternate CPUs, such as PowerPC

- supports multiple 8-bit and 16-bit scatter/gather DMA channels

- Two 82C59A interrupt controllers

- all IRQ inputs may be programmed for edge or level sensitivity

- One 82C54 counter/timer

- Routes external PCI interrupts to a software-selectable interrupt channel

#### **PCI Bus Interface**

- PCI Revision 2.1 compliant

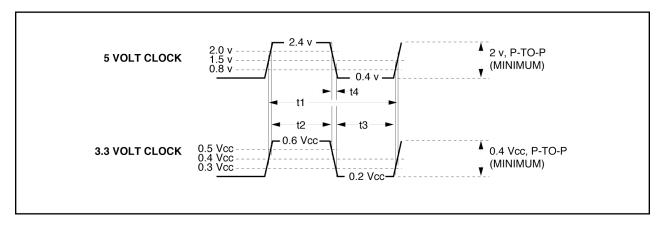

- PCI clock frequencies up to 33 MHz at 5V

- Supports delayed completion for ISA cycles

- Active address decoding for internal I/O devices

- Subtractive decoding for ISA bridge, KBC and RTC

- Supports disconnection (with retry) for slow internal accesses to improve latency

- Short PCI bus ownership when mastering to minimize overall system latency

- Fast DMA transfers from I/O devices to PCI agents as a master

- Separate request and grant signals for ISA DMA and IDE controllers

#### ISA Bus Bridge

- •

- Full implementation of a standard ISA bus

- Separate ISA and IDE data buses reduce noise and increase system performance

- Synchronous PCI-to-ISA interface with direct drive for 5 ISA slots

#### **XD-Bus interface**

- Support for BIOS ROM or PowerPC systems boot ROM

- Support for flash EPROM

- Provides keyboard controller connections

- Provides real-time clock connections

- Provides data buffer control

#### Miscellaneous

- Port B support

- Port 92 support

Uses 0.6um, ultra-low power CMOS technology for Rev. E and below; 0.5um for Rev. G.

Packaged in a 208-pin PQFP package

#### 1.2 General Description

The W83C553F Enhanced System I/O (SIO) Controller with PCI Arbiter is a highly integrated device intended for use in any Peripheral Component Interconnect (PCI) system, supporting x86 or PowerPC (non-x86) type microprocessors. It supports all PCI 2.1 compliant CPU bridge implementations and directly interfaces with PCI and ISA industry standard buses, including two direct drive IDE channels supporting up to four peripherals.

The W83C553F is a universal PCI device which can be used with many CPU-to-PCI bridge solution. The W83C553F includes 32-bit ISA DMA addressing (rather than 24-bit) to simplify its use in systems using re-compiled versions of 32-bit operating systems (such as Windows NT running on PowerPC, Alpha, or other RISC CPU).

The peripheral controller integrated into the W83C553F includes two enhanced seven channel 82C37A 32-bit DMA controllers that support fast DMA transfers with a four byte line buffer to isolate the PCI bus from the ISA bus, enhancing performance. Both DMA controllers support scatter/gather data transfer capability.

The W83C553F Enhanced SIO controller provides the bridge between the PCI bus and the ISA expansion bus. It also integrates a PCI bus master IDE controller, an eight master PCI arbiter (which may be disabled if desired) and many of the common I/O functions found in today's ISA based PC systems. The W83C553F incorporates the logic for a complete PCI interface (master and slave) and ISA interface (master and slave). Also included is PCI and ISA arbitration, 14 level interrupt controller, a 16-bit BIOS timer, three programmable counter/timers, non-maskable-interrupt (NMI) control logic and register support for power management break events.

The built-in Enhanced PCI IDE Controller is a highly integrated dual port controller, providing a high performance data path between IDE devices and the PCI bus. Four IDE chip select signals provide accessing of up to four devices. Each device has its own programmable registers for selecting 16-bit and 32-bit data pipelined transfer rates, read-ahead and posted writes. A large 64 Byte DMA FIFO buffers data to and from the IDE disks enabling the integrated scatter/gather DMA controller to efficiently perform zero wait state burst transfers across the PCI bus when enough data is available in the FIFO. Bus master IDE significantly improves the overall system performance of a multi-master PCI configuration by greatly reducing the bus and CPU utilization required for the disk and CD-ROM interface. Burst data transfers at 33 MHz can be sustained at 132 MB/s on the PCI bus.

The integrated bus-mastering PCI-IDE core is the original Sonata W83789F core with some modification of interrupt routing. This controller is fully compliant to Intel's Bus-Mastering Controller and SFF8038i specifications. BIOS support has been incorporated in all the leading BIOS companies' software. Driver software, previously tested and qualified for the W83789F, is available from Winbond Systems Laboratory for all major operating systems, including recompiled PowerPC versions.

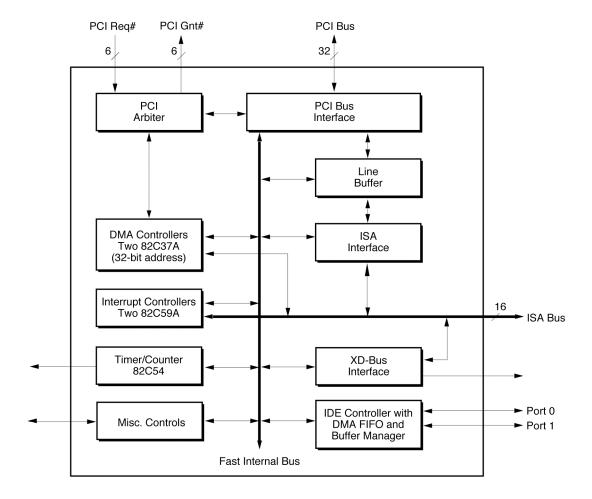

Figure 1-1. W83C553F Enhanced System I/O Controller Block Diagram

#### 1.3 Stylistic Conventions Used in this Manual

The following stylistic conventions have been used throughout this manual:

• Signal names: Signals that are active at a low voltage level are indicated by a pound sign (#) after the signal name. Signal names not followed by the # are active at the high voltage level.

- Least significant bits in words and words within memory spaces begin with zero (0). When a range is given, the most significant bit is shown to the left and the least significant bit is shown to the right. For example, AD[31:0].

- Hexadecimal numbers are given with the number in upper case followed by a lower case 'h'. For example, "8AFFh".

## 2.0 PIN DESCRIPTIONS

This chapter shows the pin diagrams, pins listed by pin number, device logic symbols, and describes each pin signal for the W83C553F.

#### 2.1 Pin Assignments

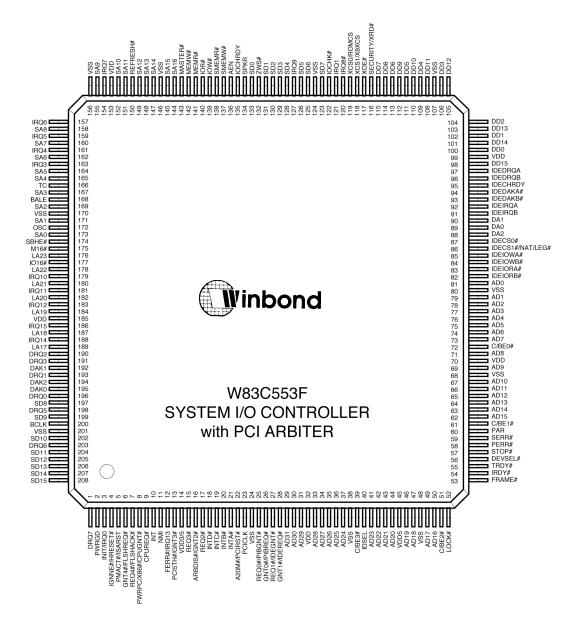

Figure 2-1. Pin Assignments for the W83C553F

| <b>Table 2-1.</b> | W83C553F | <b>Pins Listed</b> | bv | Pin | Number |

|-------------------|----------|--------------------|----|-----|--------|

|                   |          |                    |    |     |        |

| 1  | DRQ7               | 53  | FRAME#       | 105 | DD12              | 157 | IRQ6  |

|----|--------------------|-----|--------------|-----|-------------------|-----|-------|

| 2  | PWRGD              | 54  | IRDY#        | 106 | DD3               | 158 | SA8   |

| 3  | INIT               | 55  | TRDY#        | 107 | VSS               | 159 | IRQ5  |

| 4  | IGNNE#/HRESET#     | 56  | DEVSEL#      | 108 | DD11              | 160 | SA7   |

| 5  | PMACT#/ISARST      | 57  | STOP#        | 109 | DD4               | 161 | IRQ4  |

| 6  | GNT4#/FLSHREQ#     | 58  | PERR#        | 110 | DD10              | 162 | SA6   |

| 7  | REQ4#/FLSHACK#     | 59  | SERR#        | 111 | DD5               | 163 | IRQ3  |

| 8  | PWRPC/X86#/CPUGNT# | 60  | PAR          | 112 | DD9               | 164 | SA5   |

| 9  | CPUREQ#            | 61  | C/BE1#       | 113 | DD6               | 165 | SA4   |

| 10 | INT                | 62  | AD15         | 114 | DD8               | 166 | TC    |

| 11 | NMI                | 63  | AD14         | 115 | DD7               | 167 | SA3   |

| 12 | FERR#/IRQ13        | 64  | AD13         | 116 | SECURITY/XRD#     | 168 | BALE  |

| 13 | PCI5TH#/GNT3#      | 65  | AD12         | 117 | XOE#              | 169 | SA2   |

| 14 | VDD                | 66  | AD11         | 118 | XCS1/X8XCS        | 170 | VSS   |

| 15 | REQ3#              | 67  | AD10         | 119 | XCS0/ROMCS        | 171 | SA1   |

| 16 | ARBDIS#/GNT2#      | 68  | VSS          | 120 | IRQ8#             | 172 | OSC   |

| 17 | REQ2#              | 69  | AD9          | 121 | IRQ1              | 173 | SA0   |

| 18 | INTD#              | 70  | VDD          | 122 | IOCHK#            | 174 | SBHE# |

| 19 | INTC#              | 71  | AD8          | 123 | SD7               | 175 | M16#  |

| 20 | INTB#              | 72  | C/BE0#       | 124 | VSS               | 176 | LA23  |

| 21 | INTA#              | 73  | AD7          | 125 | SD6               | 177 | IO16# |

| 22 | A20M#/PCIRST#      | 74  | AD6          | 126 | SD5               | 178 | LA22  |

| 23 | PCICLK             | 75  | AD5          | 127 | IRQ9              | 179 | IRQ10 |

| 24 | VSS                | 76  | AD4          | 128 | SD4               | 180 | LA21  |

| 25 | REQ0#/PIBGNT#      | 77  | AD3          | 129 | SD3               | 181 | IRQ11 |

| 26 | GNT0#/PIBREQ#      | 78  | AD2          | 130 | SD2               | 182 | LA20  |

| 27 | REQ1#/IDEGNT#      | 79  | AD1          | 131 | SD1               | 183 | IRQ12 |

| 28 | GNT1#/IDEREQ#      | 80  | VSS          | 132 | ZWS#              | 184 | LA19  |

| 29 | AD31               | 81  | AD0          | 133 | SD0               | 185 | VDD   |

| 30 | AD30               | 82  | IDEIORB#     | 134 | SPKR              | 186 | IRQ15 |

| 31 | AD29               | 83  | IDEIORA#     | 135 | IOCHRDY           | 187 | LA18  |

| 32 | VDD                | 84  | IDEIOWB#     | 136 | AEN               | 188 | IRQ14 |

| 33 | AD28               | 85  | IDEIOWA#     | 137 | SMEMW#            | 189 | LA17  |

| 34 | AD27               | 86  | IDECS1#/NAT/ | 138 | SMEMR#            | 190 | DRQ2  |

| 35 | AD26               |     | LEG#         | 139 | IOW#              | 191 | DRQ3  |

| 36 | AD25               | 87  | IDECS0#      | 140 | IOR#              | 192 | DAK1  |

| 37 | AD24               | 88  | DA2          | 141 | MEMR#             | 193 | DRQ1  |

| 38 | VSS                | 89  | DA0          | 142 | MEMW#             | 194 | DAK2  |

|    | C/BE3#             | 90  | DA1          | 143 | MASTER#           | 195 | DAK0  |

| 40 | IDSEL              | 91  | IDEIRQB      | 144 | SA16              | 196 | DRQ0  |

| 41 | AD23               | 92  | IDEIRQA      | 145 | SA15              | 197 | SD8   |

| 42 | AD22               | 93  | IDEDAKB#     | 146 | VSS               | 198 | DRQ5  |

| 43 | AD21               | 94  | IDEDAKA#     | 147 | SA14              | 199 | SD9   |

| 44 | AD20               | 95  | IDECHRDY     | 148 | SA13              | 200 | BCLK  |

|    | VDD                | 96  | IDEDRQB      | 149 | SA12              | 201 | VSS   |

| 46 | AD19               | 97  | IDEDRQA      | 150 | REFRESH#          | 202 | SD10  |

| 47 | AD18               | 98  | DD15         | 151 | SA11              | 203 | DRQ6  |

| 48 | VSS                | 99  | VDD          | 152 | SA10              | 204 | SD11  |

| 49 | AD17               | 100 | DD0          | 153 | VDD               | 205 | SD12  |

| 50 | AD16               | 101 | DD14         | 154 | IRQ7              | 206 | SD13  |

| 51 | C/BE2#             | 102 | DD1          | 155 | SA9               | 207 | SD13  |

|    | LOCK#              | 103 | DD13         | 156 | VSS               | 208 | SD15  |

|    |                    | 104 | DD2          | -20 | - e <del> e</del> | _30 |       |

|    |                    | 10. |              |     |                   |     |       |

Note: Pins direction and assignment may not reflect exact pins, refers to exact pin description.

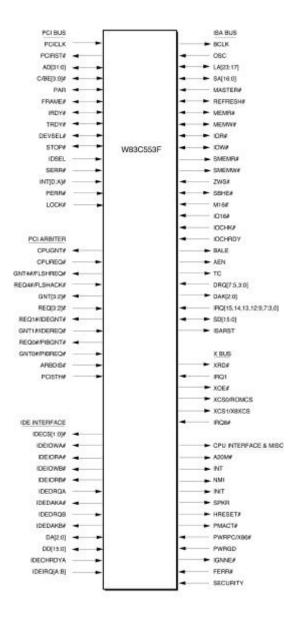

Figure 2-2. W83C553F Logic Symbol Diagram

#### 2.2 Pin Descriptions

This section describes the location and function of each pin on the W83C553F. Note the following conventions used in the tables:

• Where more than one pin is listed for a signal, the first pin number corresponds to the most significant bit of the bus. For example, the Bus Command and Byte Enables bits 3 to 0 (C/BE[3:0]#) use pins 1, 12, 22, and 31.

- Active low is indicated by the pound (#) sign. For example, PCIRST# is active low.

- Six strap pins are marked bold.

Table 2-2. PCI Bus Signals

| Pin Name           | Pin#                                                                   | Input/<br>Output | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------------|------------------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCICLK             | 23                                                                     | Input            | Clock. Provides timing for all transactions on the PCI bus. Also divides down to generate BCLK.                                                                                                                                                                                                                                                                                                                                                                                                        |

| A20M# /<br>PCIRST# | 22                                                                     | Output           | Address Bit 20 Mask or PCI Reset. This multi-function pin functions as Address Bit 20 Mask when the W83C553F is in x86 mode, as determined by pin 8 strapping after power-up. It functions as PCI Reset when the W83C553F is in PowerPC mode. It is driven for one millisecond duration after one of the following conditions:  - PWRGD active edge  - Hot Reset is set (port 92, bit 0)  - Reset Drive is set (Clock Divisor Register bit 3) PCI Reset is equivalent to ISA Reset logically inverted. |

| AD[31:0]           | 29-31,33-37,41-<br>44, 46,47, 49,<br>50, 62-67,<br>69,71,73 -<br>79,81 | Input/<br>Output | Address or Data. These bits are multiplexed on the same PCI pins. A valid 32-bit address is available during the address phase with FRAME# asserted. All subsequent cycles are the data phases.                                                                                                                                                                                                                                                                                                        |

| C/BE[3:0]#         | 39, 51, 61,<br>72                                                      | Input/<br>Output | Bus Command and Byte Enables. These bits are multiplexed on the same PCI pins. During the address phase of a transaction, C/BE[3:0]# define the bus command. During the data phase, C/BE[3:0]# are used for byte enables.                                                                                                                                                                                                                                                                              |

| PAR                | 60                                                                     | Input/<br>Output | Parity. Even parity across AD[31:0] and C/BE[3:0]#. PAR is valid one clock after the address phase. For data phases, PAR is valid one clock after either IRDY# is asserted on the write transaction, or TRDY# is asserted on a read transaction. PAR remains valid until one clock after the completion of the current phase. PAR is driven only for read data phases, and checked during write data phases.                                                                                           |

Table 2-2 (Continued). PCI Bus Signals

| Pin Name | Pin # | Input/<br>Output | Description                                                                                                                                                                                                                                                                              |

|----------|-------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FRAME#   | 53    | Input/<br>Output | Cycle Frame. Indicates the start and duration of an access. It is asserted to indicate the start of a bus transaction; during which data transfers continue. When FRAME# is de-asserted, the transaction is in the final data phase.                                                     |

| PERR#    | 58    | Input/<br>Output | PCI Parity Error.                                                                                                                                                                                                                                                                        |

| IRDY#    | 54    | Input/<br>Output | Initiator Ready. Indicates the initiating agent's ability to complete the current transaction's data phase. It is used jointly with TRDY#. During a write, it indicates that valid data is present on AD[31:0]. During a read cycle, it indicates the master is prepared to accept data. |

| TRDY#    | 55    | Input/<br>Output | Target Ready. Indicates the target's ability to complete the current data phase of the transaction. It is used with IRDY#. During a read cycle, it indicates that valid data is present on AD[31:0]. During a write cycle, it indicates the target is prepared to accept data.           |

| DEVSEL#  | 56    | Input/<br>Output | Device Select. This signal is asserted by the W83C553F when it is acting as a target in a transaction. It is an input when the W83C553F is acting as the initiator of a transaction.                                                                                                     |

| STOP#    | 57    | Input/<br>Output | Stop. This is asserted to terminate the current transaction. It causes a disconnect condition, limiting slave I/O cycles to one data transfer since I/O burst transfers are not supported. During master cycles, it indicates the target wants to terminate the cycle.                   |

| IDSEL    | 40    | Input            | Initialization Device Select. Chip select signal, used during PCI configuration read and write cycles.                                                                                                                                                                                   |

| SERR#    | 59    | Input/OD         | System Error. The W83C553F monitors the SERR# pin to generate an NMI if enabled.                                                                                                                                                                                                         |

Table 2-2 (Continued). PCI Bus Signals

| Pin Name  | Pin # | Input/<br>Output | Description                                                                                                                             |

|-----------|-------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| INT[A:B]# | 21-20 | Input            | PCI Interrupts. These PCI interrupts can be routed to the programmable interrupt controller inside the W83C553F under software control. |

| INT[C:D]# | 19-18 | Input/<br>OD     | PCI Interrupts. These PCI interrupts can be routed to the programmable interrupt controller inside the W83C553F under software control. |

| LOCK#     | 52    | Input            | PCI Lock. LOCK# is used to indicate an atomic operation that may require multiple transactions to complete.                             |

**Table 2-3. PCI Arbiter Signals**

| Pin Name           | Pin# | Input/<br>Output | Description                                                                                                                                                                                                                                                                           |

|--------------------|------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GNT0# /<br>PIBREQ# | 26   | Output           | This is a multifunction pin. The W83C553F PCI-ISA bridge (Function 0) asserts this signal to request the use of the PCI bus when the on-chip PCI arbiter is disabled. This pin functions as GNT0# when the on-chip PCI arbiter is enabled, allowing PCI access to an external master. |

| REQ0# /<br>PIBGNT# | 25   | Input            | This is a multifunction pin. An external arbiter asserts this signal to grant the next PCI access to the PCI-ISA bridge (Function 0) when the on-chip PCI arbiter is disabled. This pin functions as REQ0# when the on-chip PCI arbiter is enabled.                                   |

| GNT1# /<br>IDEREQ# | 28   | Output           | This is a multifunction pin. The W83C553F IDE master (Function 1) asserts this signal to request the use of the PCI bus when the on-chip PCI arbiter is disabled. This pin functions as GNT1# when the on-chip PCI arbiter is enabled, allowing PCI access to an external master.     |

| REQ1# /<br>IDEGNT# | 27   | Input            | This is a multifunction pin. An external arbiter asserts this signal to grant the next PCI access to the IDE master when the on-chip PCI arbiter is disabled. This pin functions as REQ1# when the on-chip PCI arbiter is enabled.                                                    |

| ARBDIS# /<br>GNT2# | 16   | Input/<br>Output | When the on-chip PCI arbiter is enabled, it uses this pin to grant the next PCI access. If a 2.2k Ohm resistor straps this pin to ground, the PCI arbiter is disabled after power-up. This <u>overrides</u> the strapping of PCI5TH# on pin 13.                                       |

| REQ2#              | 17   | Input            | When the on-chip PCI arbiter is enabled, external PCI masters use this pin to request access to the PCI bus.                                                                                                                                                                          |

Table 2-3 (continued). PCI Arbiter Signals

| Pin Name                | Pin# | Input/<br>Output | Description                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------------------|------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCI5TH# /<br>GNT3#      | 13   | Input/<br>Output | When the on-chip PCI arbiter is enabled, GNT3# behaves as a normal PCI grant output.                                                                                                                                                                                                                                                                                                                       |

|                         |      |                  | If a 2.2K ohm resistor straps this pin to ground, pin 6 and 7 function as GNT4# and REQ4# after power-up. If this pin is weakly strapped to VCC, pin 6 and 7 function as FLSHREQ# and FLSHACK# after power-up. The PCI5TH# function is overridden by the ARBDIS# function (i.e., if the on-chip PCI arbiter is disabled, pin 6 and 7 function as FLSHREQ# and FLSHACK# no matter how PCI5TH# is strapped.) |

| REQ3#                   | 15   | Input            | When the on-chip PCI arbiter is enabled, REQ3# behaves as a normal PCI request input.                                                                                                                                                                                                                                                                                                                      |

| GNT4# /<br>FLSHREQ#     | 6    | Output           | This is a multifunction pin which is alternately used to request flushing all buffers or granting PCI access to an external master.                                                                                                                                                                                                                                                                        |

| REQ4# /<br>FLSHACK#     | 7    | Input            | This is a multifunction pin which is alternately used as flush acknowledge or as a PCI access request input.                                                                                                                                                                                                                                                                                               |

| PWRPC/X86#<br>/ CPUGNT# | 8    | Input/<br>Output | This multifunction pin is sampled by the W83C553F, following the PWRGD active edge. If a 2.2K ohm resistor is weakly pulling this pin to VCC at this time, the W83C553F is in PowerPC mode. If a weak pull down resistor is connected to ground, the chip is in x86 mode.  When the PCI arbiter within the W83C553F is enabled (pin 16 Arbdis#/GNT2# is weakly pulled high), this pin functions as the     |

|                         |      |                  | CPU Grant output which allows the system CPU-to-PCI bridge to have access to PCI.                                                                                                                                                                                                                                                                                                                          |

| CPUREQ#                 | 9    | Input            | This input allows the system CPU to request access to the PCI bus in systems with the PCI arbiter within the W83C553F enabled.                                                                                                                                                                                                                                                                             |

**Table 2-4. IDE Interface Bus Signals**

| Pin Name             | Pin # | Input/<br>Output | Description                                                                                                                                                                                                                                                                                                                                           |

|----------------------|-------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IDECS0#              | 87    | Output           | Drive Chip Select 0. This signal is decoded from the AD bus to select both primary and secondary IDE Port Command Block Registers.                                                                                                                                                                                                                    |

| IDECS1#/<br>NAT/LEG# | 86    | Input/<br>Output | Drive Chip Select 1. This signal is decoded from the AD bus to select both primary and secondary IDE Port Auxiliary Registers.  Native or Legacy Mode Select. During reset, this pin is sampled as an input to set the Native or Legacy mode of the bus master IDE controller (Function 1). A high selects Native mode and a low selects Legacy mode. |

| IDEIOWA#             | 85    | Output           | Drive I/O Write A. This signal is used jointly with IDECS0# and IDECS1#. The rising edge of IDEIOWA# latches data into the primary port IDE device.                                                                                                                                                                                                   |

| IDEIORA#             | 83    | Output           | Drive I/O Read A. This signal is used jointly with IDECS0# and IDECS1#. The falling edge of IDEIORA# enables data from the primary port IDE device. The data is latched internally on the rising edge of IDEIORA#.                                                                                                                                    |

| IDEIOWB#             | 84    | Output           | Drive I/O Write B. This signal is used jointly with IDECS0# and IDECS1#. The rising edge of IDEIOWB# latches data into the secondary port IDE device.                                                                                                                                                                                                 |

| IDEIORB#             | 82    | Output           | Drive I/O Read B. This signal is used jointly with IDECS0# and IDECS1#. The falling edge of the IDEIORB# enables data from the secondary port IDE device. The data is latched internally on the rising edge of IDEIORB#.                                                                                                                              |

Table 2-4 (continued). IDE Interface Bus Signals

| Pin Name | Pin#                                                                                       | Input/<br>Output | Description                                                                                                                                                                        |

|----------|--------------------------------------------------------------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IDEDRQA  | 97                                                                                         | Input            | DMA Request A. This signal is the primary port DMA handshake from the IDE device. When asserted, it indicates a data transfer is requested.                                        |

| IDEDAKA# | 94                                                                                         | Output           | DMA Acknowledge A. This is the primary port DMA handshake to the IDE device. When asserted, it indicates a data transfer can be executed.                                          |

| IDEDRQB  | 96                                                                                         | Input            | DMA Request B. This is the secondary port DMA handshake from the IDE device. When asserted, it indicates a data transfer is requested.                                             |

| IDEDAKB# | 93                                                                                         | Output           | DMA Acknowledge B. This is the secondary port DMA handshake to the IDE device. When asserted, it indicates a data transfer can be executed.                                        |

| DA[2:0]  | 88,90,89                                                                                   | Output           | IDE Drive Address.                                                                                                                                                                 |

| DD[15:0] | 98,101,103,<br>105,108,<br>110,112,<br>114,115,<br>113,111,<br>109,106,<br>104,102,<br>100 | Input/<br>Output | IDE Drive Data. 16-bit bi-directional bus.                                                                                                                                         |

| IDECHRDY | 95                                                                                         | Input            | IDE I/O Channel Ready. When IDECHRDY is negated, the current cycle will be extended. This input is connected to the primary port, and can also be connected to the secondary port. |

| IDEIRQB  | 91                                                                                         | Input            | IDE IRQ B. Secondary port interrupt request.                                                                                                                                       |

| IDEIRQA  | 92                                                                                         | Input            | IDE IRQ A. Primary port interrupt request.                                                                                                                                         |

Table 2-5. ISA Bus Signals

| Pin Name  | Pin#                                                                                        | Input/<br>Output | Description                                                                                                                                                    |

|-----------|---------------------------------------------------------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BCLK      | 200                                                                                         | Output           | ISA Bus Clock.                                                                                                                                                 |

| OSC       | 172                                                                                         | Input            | Oscillator. 14 MHz input for generating the internal timer clock.                                                                                              |

| LA[23:17] | 176,178,<br>180,182,<br>184,187,<br>189                                                     | Input/<br>Output | Latchable Address. The current bus owner drives LA[23:17] to provide 16M of memory space.                                                                      |

| SA[16:0]  | 144,145,<br>147-149,<br>151,152,<br>155,158,<br>160,162,<br>164,165,<br>167,169,<br>171,173 | Input/<br>Output | System Address. SA[16:0] provides the 17 least significant address bits for memory accesses and SA[15:0] provides the entire 16 address bits for I/O accesses. |

| MASTER#   | 143                                                                                         | Input            | ISA Master. Master control signal from the ISA bus.                                                                                                            |

| REFRESH#  | 150                                                                                         | Input/<br>Output | ISA DRAM Refresh Control. This pin is an open drain output and allows other masters to initiate refresh requests.                                              |

| MEMR#     | 141                                                                                         | Input/<br>Output | Memory Read. Acts as an output during PCI master and DMA cycles and as an input during ISA master cycles.                                                      |

| MEMW#     | 142                                                                                         | Input/<br>Output | Memory Write. Acts as an output during PCI master and DMA cycles and as an input during ISA master cycles.                                                     |

Table 2-5 (Continued). ISA Bus Signals

| Pin Name | Pin # | Input/<br>Output | Description                                                                                                                |

|----------|-------|------------------|----------------------------------------------------------------------------------------------------------------------------|

| IOR#     | 140   | Input/<br>Output | I/O Read. Act as an output during PCI master and DMA cycles and as an input during ISA master cycles.                      |

| IOW#     | 139   | Input/<br>Output | I/O Write. Act as an output during PCI master and DMA cycles and as input during ISA master cycles.                        |

| SMEMR#   | 138   | Output           | Memory Read To Address Below 1M. An external pull-up resistor is required.                                                 |

| SMEMW#   | 137   | Output           | Memory Write To Address Below 1M. An external pull-up resistor is required.                                                |

| ZWS#     | 132   | Input            | Zero Wait State. This signal is used by ISA slaves to terminate a transfer cycle before the default ready counter expires. |

| SBHE#    | 174   | Input/<br>Output | System Byte High Enable. SBHE# is asserted to indicate that data is being transferred on SD[15:8].                         |

| M16#     | 175   | Input/<br>Output | Memory Cycle 16-Bit Select. This signal is used by memory slaves to indicate 16-bit transfer capability.                   |

| IO16#    | 177   | Input            | I/O Cycle 16-Bit Select. This signal is used by I/O slaves to indicate 16-bit transfer capability.                         |

| IOCHK#   | 122   | Input            | I/O Channel Check. This assertion of this signal indicates an error has occurred.                                          |

Table 2-5 (Continued). ISA Bus Signals

| Pin Name               | Pin #                                                           | Input/<br>Output | Description                                                                                                                                                                          |

|------------------------|-----------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IOCHRDY                | 135                                                             | Input/<br>Output | I/O Channel Ready. This signal is used by ISA slaves to extend the transfer cycle beyond the default ready timer expiration.                                                         |

| BALE                   | 168                                                             | Output           | Bus Address Latch Enable. This signal indicates that a valid address is on the bus.                                                                                                  |

| AEN                    | 136                                                             | Output           | Address Enable. AEN is asserted during DMA cycles to prevent I/O devices from misinterpreting the cycle as a valid I/O cycle.                                                        |

| TC                     | 166                                                             | Output           | Termination Count. This signal is asserted to indicate that a DMA channel's word count has reached terminal count.                                                                   |

| DRQ[7:5, 3:0]          | 1,203,198,<br>191,190,<br>193,196                               | Input            | DMA Request. DMA service request from the DMA controllers.                                                                                                                           |

| DAK[2:0]               | 194,192,<br>195                                                 | Output           | Encoded DMA Acknowledge. The channel number of the arbitration winner is encoded in binary. An external decoder is required to generate DACK[7:5, 3:0]#. The inactive value is 100b. |

| IRQ[15, 14, 12:9, 7:3] | 186,188,<br>183,181,<br>179,127,<br>154,157,<br>159,161,<br>163 | Input            | Interrupt Request.                                                                                                                                                                   |

Table 2-5 (Continued). ISA Bus Signals

| Pin Name           | Pin #                                                           | Input/<br>Output  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------------|-----------------------------------------------------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

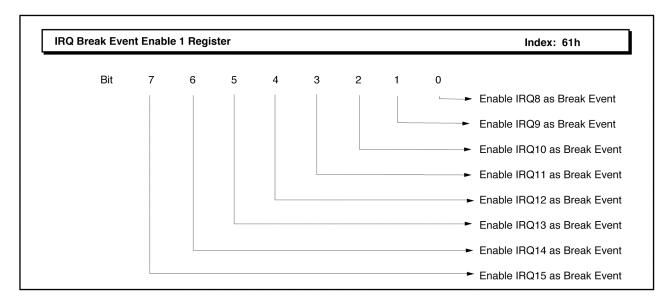

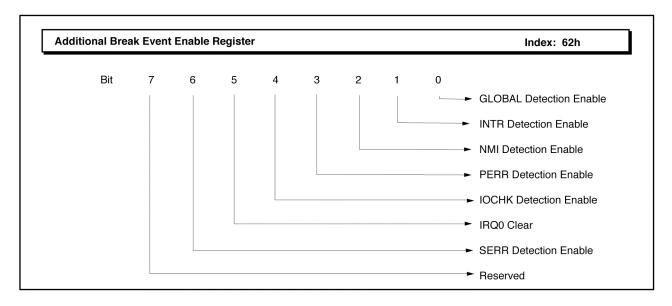

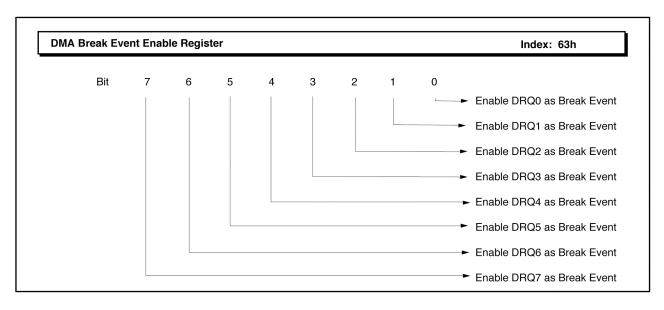

| PMACT# /<br>ISARST | 5                                                               | Output            | This multi-function pin functions as ISA Reset when the W83C553F is in PowerPC mode, as determined by pin 8 strapping after power-up. It is driven for one millisecond duration after one of the following conditions:  - PWRGD active edge - Hot Reset bit set (port 92, bit 0) - Reset Drive bit set (Clock Divisor Register bit 3)  ISA Reset is the inverted logical equivalent of PCI Reset.  When the W83C553F is in x86 mode, this pin functions as Power Management Active. It is the output signal to the CPU bridge which indicates the system activity status by becoming active when a break event has occurred. Break events are programmed into PCI Configuration Registers index 60h - 63h. |

| SD[15:0]           | 208-204,<br>202,199,<br>197,123,<br>125,126,<br>128-131,<br>133 | Input /<br>Output | Bidirectional Data Bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

Table 2-6. X Bus Signals

| Pin Name           | Pin# | Input/<br>Output | Description                                                                                                                                                                                                                                                                                                                                                                      |  |

|--------------------|------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SECURITY /<br>XRD# | 116  | Output/<br>Input | X Bus Read. When active "0", data flows from XD to SD. When the W83C553F is in PowerPC mode, this pin is sampled after reset and its value is reflected in bit 2 of the Port 92 register (see page 107).                                                                                                                                                                         |  |

| IRQ1               | 121  | Input            | Keyboard Controller Interrupt.                                                                                                                                                                                                                                                                                                                                                   |  |

| IRQ8#              | 120  | Input            | Real Time Clock Interrupt.                                                                                                                                                                                                                                                                                                                                                       |  |

| XOE#               | 117  | Output/<br>Input | X Bus Buffer Enable. This signal enables an external X-bus buffer whenever an X-bus device is decoded. This pin is a strap pin, needs a 2.2k Ohm resistor pull up, otherwise will be in test mode.                                                                                                                                                                               |  |

| XCS0/<br>ROMCS     | 119  | Output           | This is a multi-function pin. When the W83C553F is in PowerPC mode, this pin functions as the chip select for an external ROM, using default ISA memory cycle timing. When the W83C553F is in x86 mode, this pin functions as the lower bit of the X-bus Address.                                                                                                                |  |

| XCS1/X8XCS         | 118  | Output           | This is a multi-function pin. When the W83C553F is in PowerPC mode, this pin functions as the chip select for ports in the 800h-8FFh I/O address range. When the W83C553F is in x86 mode, this pin functions as the upper bit of the X-bus Address. In x86 mode, an external decoder is required to decode the chip selects for X-bus devices:    XCS[1:0]   Device   Device   O |  |

Table 2-7. CPU Interface and Miscellaneous Signals

| Pin Name            | Pin# | Input/<br>Output | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|---------------------|------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| INT                 | 10   | Output           | Interrupt. Interrupt signal from the W83C553F interrupt controller to the CPU.                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| NMI                 | 11   | Output           | Non-Maskable Interrupt.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| INIT                | 3    | Output           | It functions as Initialize CPU/Software Reset (INIT) when the W83C553F is in x86 mode, as determined by pin 8 strapping after reset. INIT is asserted for four PCI clocks following one of these events:  - Hot Reset bit set (port 92, bit 0)  - CPU Shutdown Cycle  - keyboard Reset Emulation bit is set (bit 1, Index 4E)                                                                                                                                                  |  |

| SPKR                | 134  | Output           | Speaker Data. This output drives an externally buffered speaker.                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| PWRGD               | 2    | Input            | Power good signal from the power supply. This signal is used to generate other reset signals to reset the system.                                                                                                                                                                                                                                                                                                                                                              |  |

| FERR#/IRQ13         | 12   | Input            | This multi-function pin's default function is Interrupt Request 13 (IRQ13). The Numerical Co-processor Error (FERR#) function may be enabled by a bit in the Function 0 PCI Configuration Space AT System Control Register (Index 4Eh, bit 4).                                                                                                                                                                                                                                 |  |

| IGNNE# /<br>HRESET# | 4    | Output           | This multi-function pin functions as Ignore Numeric Error (IGNNE#) when the W83C553F is in x86 mode as determined by pin 8 strapping after reset. It functions as HRESET# when the W83C553F is in PowerPC mode. For connection to the PowerPC, HRESET# is asserted for a duration of one millisecond after one of the following events:  - PWRGD active edge - Hot Reset bit set (port 92, bit 0) - CPU Shutdown Cycle - Keyboard Reset Emulation bit is set (bit 1, Index 4E) |  |

**Table 2-8. Power and Ground Signals**

| Pin Name | Pin #                                                  | Input/<br>Output | Description                                                                                                         |

|----------|--------------------------------------------------------|------------------|---------------------------------------------------------------------------------------------------------------------|

| VSS      | 24,38,48,<br>68,80,<br>107,124,<br>146,156,<br>170,201 | -                | These 11 pins are connected to the power supply ground. All VSS pins must be connected for proper device operation. |

| VDD      | 14,32,45,<br>70,99,153,185                             | -                | These 7 pins are connected to the power supply +5V. All VDD pins must be connected for proper device operation.     |

## 3.0 SYSTEM ARCHITECTURE

#### 3.1 Overview

The W83C553F is a multi-function PCI device. "Function 0" is the PCI-to-ISA bridge logic; "Function 1" is the bus master IDE controller. Each function has its own separate PCI configuration space and I/O register space.

The W83C553F's bus hierarchy is designed to provide concurrency of operations performed on all buses simultaneously and is structured as follows:

- PCI Bus is primary I/O bus

- ISA Bus is secondary I/O bus

The W83C553F accepts cycles from the PCI bus and translates them onto the ISA bus. It also requests the PCI master bridge to generate PCI cycles on behalf of IDE DMA or an ISA master. The ISA bus interface thus contains a standard ISA Bus Controller and data buffering logic. ISA control includes ISA command generation, I/O recovery control, wait-state insertion, and data buffer routing. Five ISA slots can be supported without external buffering circuitry.

The W83C553F initiates and performs standard ISA bus refreshing. The integrated controller generates the command and refresh address to the ISA bus. Since an ISA refresh is transparent to the PCI bus and the DMA cycle, an arbiter resolves any conflicts among PCI, refresh, and DMA cycles.

IDE data transfers are executed with two specific protocols. The standard protocol is to execute PIO cycles on the PCI bus and the dual IDE interfaces. An enhanced protocol is supported, allowing the W83C553F to transfer data across the PCI bus as a bus master directly to/from memory, and across the dual IDE interfaces with single or multiword DMA cycles. This protocol minimizes CPU overhead while maximizing the PCI bus bandwidth.

All IDE PIO protocol data transfers (8-bit, 16-bit and 32-bit) are automatically detected and supported. Read ahead can be enabled for each individual device for 16-bit and 32-bit I/O read operations. This allows the controller to execute additional IDE read cycles while the host is completing the previous memory write. Posted writes can be enabled for each individual device for 16-bit and 32-bit I/O write operations which allow the IDE controller to complete the present write cycle while the host executes the next system memory read operation maximizing the disk sub-system performance while reducing system overhead.

Bus Master data/command transfers are supported as defined in the proposed PCI "Programming Interface for Bus Master IDE Controller" specification Rev. 1.0 (SFF8038i). This allows the system microprocessor to be freed from the task of manually transferring data between the IDE controller and the system memory as is required by the standard PIO protocol. In a multitasking environment, the system CPU can perform other tasks with the maximum PCI bus bandwidth available while data transfers are executed by the W83C553F.

The IDE interface is fully ANSI CAM compliant to the ATA Revision 3.0 and the ATA-2 specifications. Each storage device on the two ports is individually programmable to select the desired command on and off times to support ATA defined PIO MODES 0 through 2 and Multiword DMA MODE 0. Also supported are SFF PIO MODES 3, 4 and 5 (proposed) and Multiword DMA MODES 1 and 2.

The devices supported are ATA compliant hard disks, tape drives, and CD ROMs. The W83C553F is compliant with the emerging ATAPI Specification.

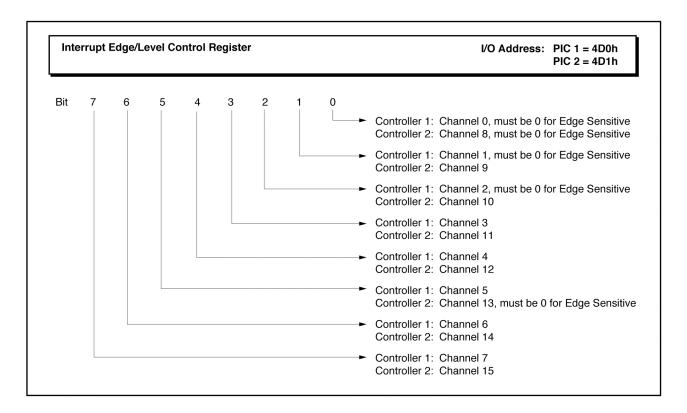

Two interrupt controllers can handle a total of 15 interrupt channels. IRQ0 is internally connected to OUT0, of the 82C54 counter/timer. Usually an interrupt is generated by the rising edge of IRQ. IRQ8 and IRQ13, however, are fixed to trigger on the falling edge for direct connection to the real time clock interrupt or Pentium CPU floating point error signal. RX 4D0h and RX4D1h can be programmed to change the IRQs from edge sensitive to level sensitive interrupts. All external IRQ lines are not internally pulled-up. I/O port and channel definition matches the IBM PC/AT requirement.

Types A, B, F DMA are supported by the W83C553F. Two integrated 82C37A DMA controllers each generate memory addresses and control signals to transfer information between a peripheral device and memory, without CPU intervention. Four DMA channels permit 8-bit peripheral device data transfers. Three channels permit 16-bit peripheral device data transfers. During a DMA or master cycle, the CPU is held and the W83C553F takes control. Both DMA controllers support scatter/gather transfer capability on all channels and 32-bit addressing.

The W83C553F has two basic operational states: reset and active. The reset state brings all internal logic to a known state, and configures some chip features. The active state is the normal operating state that allows software to perform chip configuration, access to the PCI and ISA register sets, and accessing of up to four IDE devices.

#### 3.2 Active State

When active, the W83C553F will monitor all PCI bus cycles and respond to configuration and I/O cycles. The W83C553F will always respond to configuration cycles when properly addressed but will always respond to I/O cycles, as indicated in the internal configuration registers.

Configuration cycles are executed anytime the W83C553F IDSEL pin is asserted, a valid command is detected, and AD[1:0] are "0" during the address phase. Configuration cycles are executed to program the W83C553F internal configuration register sets. I/O cycles will only be executed when enabled as indicated in the configuration registers. I/O cycles are used to transfer command/status and data to/from the IDE devices, as well as to program the bus master register set.

Four basic data paths are provided. One provides the timing and control functions for 8-bit I/O cycles that communicate control/status information with the IDE devices. A second data path provides the timing and control functions for 16-bit and 32-bit I/O cycles that are used to transfer data to/from the IDE drives with the PIO protocol. The third is used to access the internal Configuration and Bus Master IDE Register set. The fourth data path is used for the bus master data transfer protocol. A block of logic is used to interface to the PCI bus as well as separate 8-bit from 16/32-bit cycles and provide bus master support. A separate block of logic is used to control the IDE interface and timing as well as control the packing and unpacking of the data between the IDE buffer logic and the PCI buffer logic.

#### 3.3 Bus Structures

Table 3-1. Address and Data Paths for Basic Cycles

| Cycle                 | Address Bus Path                                            | Data Bus Path                            |

|-----------------------|-------------------------------------------------------------|------------------------------------------|

| ISA-to-PCI data read  | PCI address/data->W83C553F ->Latched & ISA addressing       | ISA data->W83C553F->PCI address/data     |

| PCI-to-ISA data write | PCI address/data->W83C553F ->Latched & ISA addressing       | PCI address/data->W83C553F<br>->ISA data |

| DMA read              | W83C553F->PCI address/data, W83C553F->Latched & ISA address | PCI address/data->W83C553F ->ISA data    |

| DMA write             | W83C553F->PCI address/data, W83C553F->Latched & ISA address | ISA data->W83C553F->PCI address/data     |

| ISA refresh           | W83C553F->ISA address                                       |                                          |

#### 3.4 PCI-to-ISA Bridge

The W83C553F PCI System I/O provides the PCI bus interface functions. It contains both PCI master and slave bus bridging. When PIBGNT# is asserted, the master bridge translates an ISA master or DMA cycle to the PCI bus, based on the ISA Address Decoder status. When PIBGNT# is de-asserted, the slave bridge accepts these cycles, initiated from the PCI bus, and targeted to the W83C553F's internal registers or ISA bus. The PCI Address Decoder supports the slave bridge in processing the PCI master initiated cycles. The cycles are then forwarded to the ISA bus interface for translation onto the ISA bus.

As a PCI slave, the W83C553F responds to both I/O and memory transactions. It always target-terminates after the first data phase of a bursting cycle. It also converts a single interrupt acknowledge cycle into two cycles for the two internal 82C59s.

The W83C553F functions as the subtractive decoder in a PCI/ISA system by accepting all accesses not positively decoded by some other device. This function only applies to the low 64 K I/O or low 16 M memory accesses.

The W83C553F positively decodes I/O addresses for internal registers by asserting DEVSEL# on the medium timing. In the x86 mode, the keyboard controller and RTC are subtractively decoded.

As long as PIBGNT# is asserted, the PCI master bridge, on behalf of DMA devices or ISA Masters, drives the PCI address/data, C/BE[3:0]# and PAR signals. When MEMR# or MEMW# is asserted, the W83C553F sends FRAME# and IRDY# to the PCI bus if the targeted memory is not on the ISA side. Addresses and commands are valid during the address phase, while PAR is asserted one clock later. The W83C553F always activates FRAME# for 2 PCLKs because it does not conduct bursting cycles for PCI-to-ISA reads or writes.

The ISA Address Decoder determines the destination of the ISA master or DMA devices. It provides the following options, as defined in Registers 48h to 4Bh:

- Memory space 0 512KB

- Memory space 512 KB 640 KB

- Video Buffer memory space 640 KB 768 KB

- Expansion ROM memory space 768 KB 896 KB, in eight 16 KB sections

- Lower BIOS memory space 896 KB 960 KB

- Memory space within 1 MB x MB 16 MB. Not accessible to the PCI bus.

- Memory space less than 16 MB automatically forwards to the PCI.

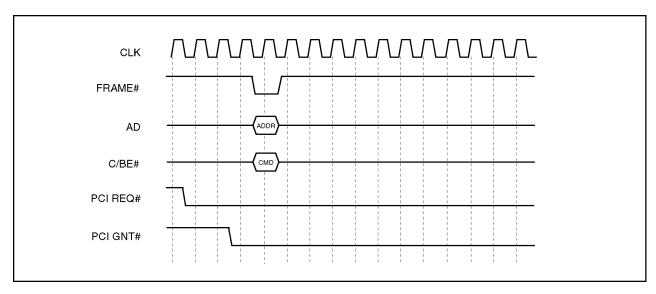

#### 3.5 PCI Bus Cycles

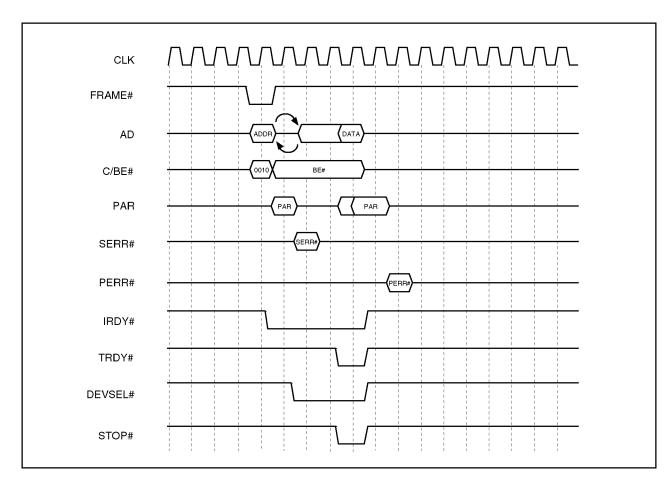

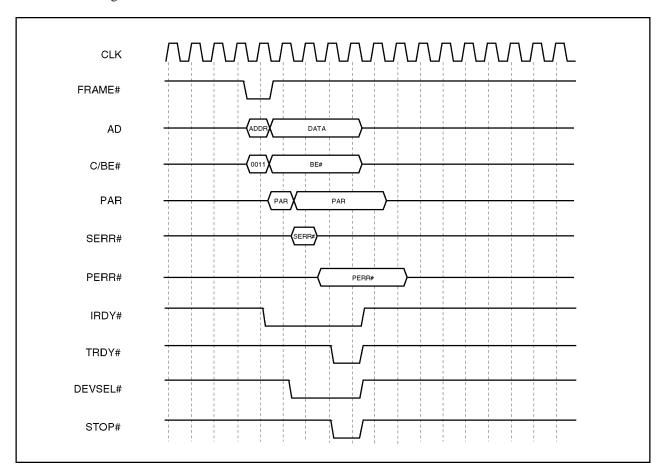

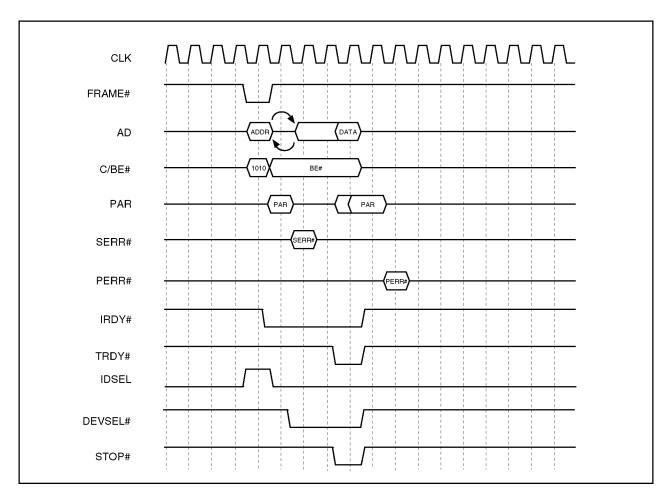

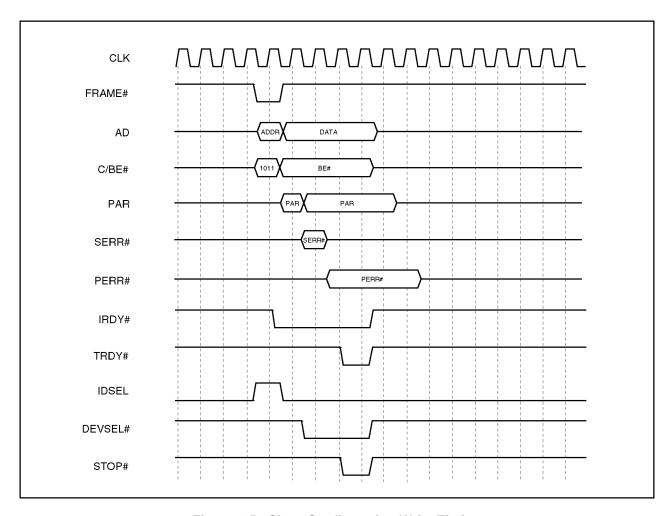

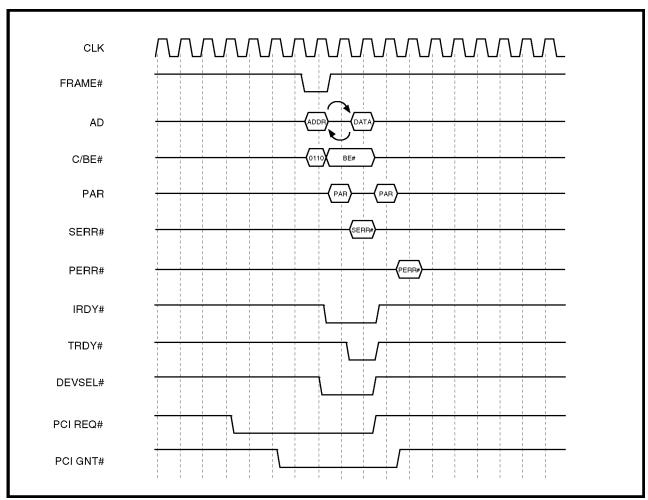

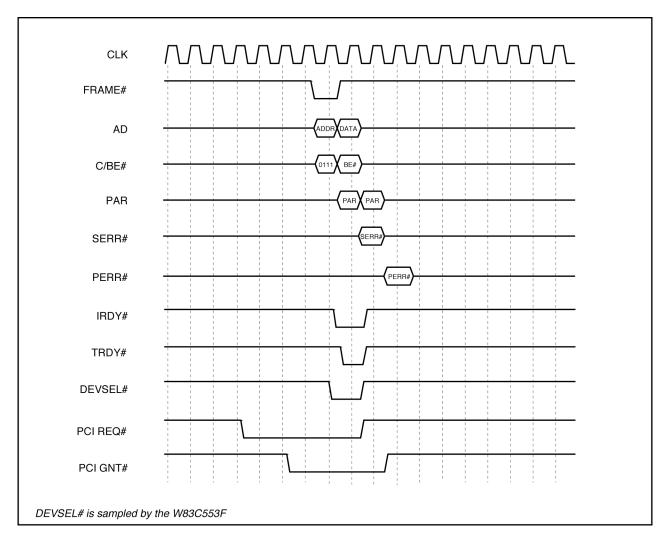

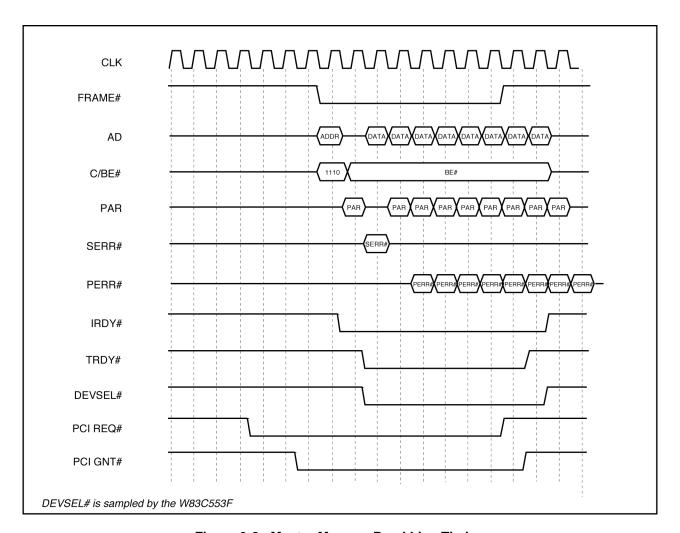

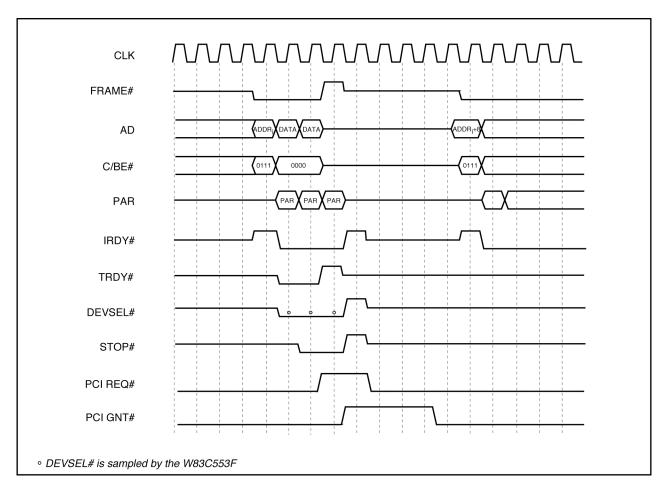

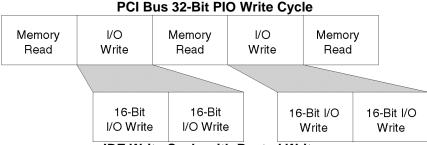

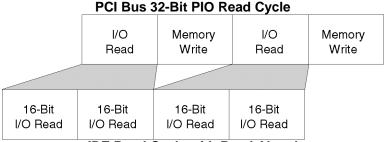

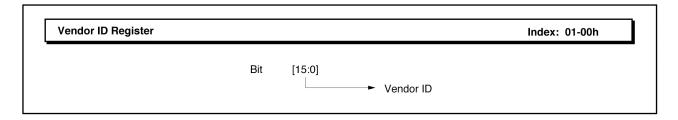

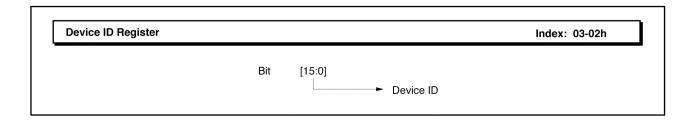

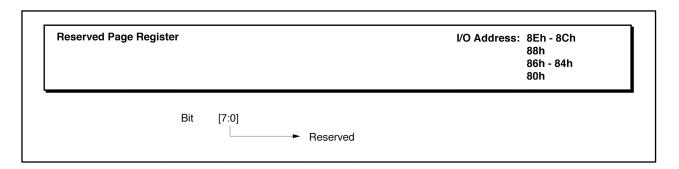

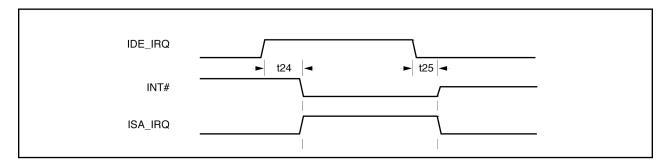

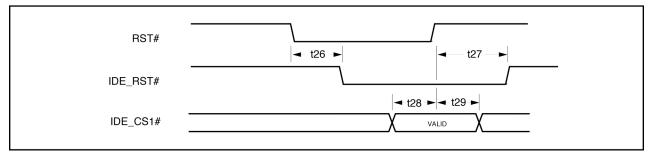

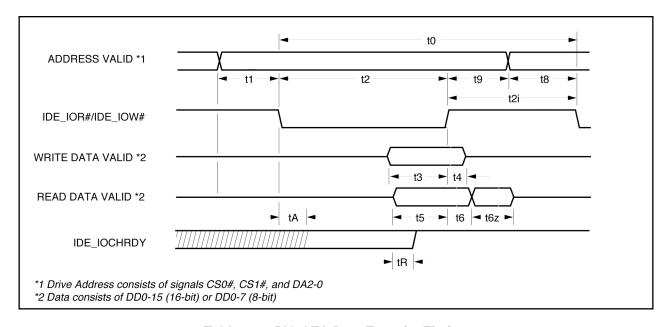

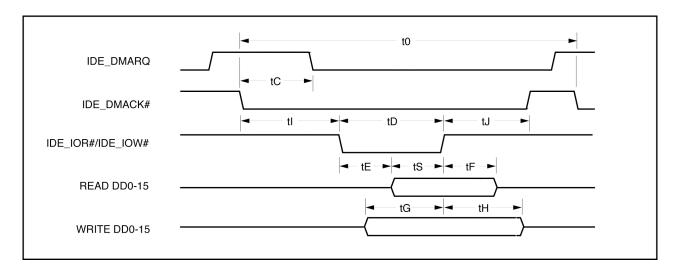

The PCI bus cycle can be split into two phases, the address phase and the data phase. The address phase of a PCI cycle is defined as the first rising clock edge when FRAME# is asserted. On this clock edge, C/BE[3:0]# contains the bus command that defines the PCI bus cycle, AD [31:0] contains a valid address, and IDSEL will be stable and valid if it is a configuration cycle. All subsequent clocks comprise the data phase until the cycle is complete. If this cycle is claimed, DEVSEL# will be asserted.