## INTEGRATED CIRCUITS

Product specification File under Integrated Circuits, IC22

#### **Product specification**

## Multimedia bridge, high performance Scaler and PCI circuit (SPCI)

#### CONTENTS

| 1    | FEATURES                              |

|------|---------------------------------------|

| 1.1  | Video processing                      |

| 1.2  | Audio processing                      |

| 1.3  | Scaling                               |

| 1.4  | Interfacing                           |

| 1.5  | General                               |

| 2    | GENERAL DESCRIPTION                   |

| 3    | QUICK REFERENCE DATA                  |

| 4    | ORDERING INFORMATION                  |

| 5    | BLOCK DIAGRAM                         |

| 6    | PINNING                               |

| 7    | FUNCTIONAL DESCRIPTION                |

| 7.1  | General                               |

| 7.2  | PCI interface                         |

| 7.3  | Main control                          |

| 7.4  | Register Programming Sequencer (RPS)  |

| 7.5  | Status and interrupts                 |

| 7.6  | General Purpose Inputs/Outputs (GPIO) |

| 7.7  | Event counter                         |

| 7.8  | Video processing                      |

| 7.9  | High Performance Scaler (HPS)         |

| 7.10 | Binary Ratio Scaler (BRS)             |

| 7.11 | Video data formats on the PCI-bus     |

| 7.12 | Scaler register                       |

| 7.13 | Scaler event description              |

| 7.14 | Clipping                              |

| 7.15 | Data Expansion Bus Interface (DEBI)   |

| 7.16 | Audio interface                       |

| 7.17 | I <sup>2</sup> C-bus interface        |

| 7.18 | SAA7146A register tables              |

| 7.18 | SAA7146A register tables |

|------|--------------------------|

|------|--------------------------|

| 8                            | BOUNDARY SCAN TEST                                                              |

|------------------------------|---------------------------------------------------------------------------------|

| 8.1<br>8.2                   | Initialization of boundary scan circuit<br>Device identification codes          |

| 9                            | ELECTRICAL OPERATING CONDITIONS                                                 |

| 10                           | CHARACTERISTICS                                                                 |

| 11                           | APPLICATION EXAMPLE                                                             |

| 12                           | PACKAGE OUTLINES                                                                |

| 13                           | SOLDERING                                                                       |

| 13.1<br>13.2<br>13.3<br>13.4 | Introduction<br>Reflow soldering<br>Wave soldering<br>Repairing soldered joints |

| 14                           | DEFINITIONS                                                                     |

| 15                           | LIFE SUPPORT APPLICATIONS                                                       |

| 16                           | PURCHASE OF PHILIPS I <sup>2</sup> C COMPONENTS                                 |

|                              |                                                                                 |

#### 1 FEATURES

#### 1.1 Video processing

- Full size, full speed video delivery to and from the frame buffer or virtual system memory enables various processing possibilities for any external PCI device

- Full bandwidth PCI-bus master write and read (up to 132 Mbytes/s)

- Virtual memory support (4 Mbytes per DMA channel)

- Processing of maximum 4095 active samples per line and maximum 4095 lines per frame

- Vanity picture (mirror) for video phone and video conferencing applications

- Video flip (upside down picture)

- Colour space conversion with gamma correction for different kinds of displays

- · Chroma Key generation and utilization

- · Pixel dithering for low resolution video output formats

- · Brightness, contrast and saturation control

- Video and Vertical Blanking Interval (VBI) synchronized programming of internal registers with Register Programming Sequencer (RPS), ability to control two asynchronous data streams simultaneously

- Memory Management Unit (MMU) supports virtual demand paging memory management (Windows, Unix, etc.)

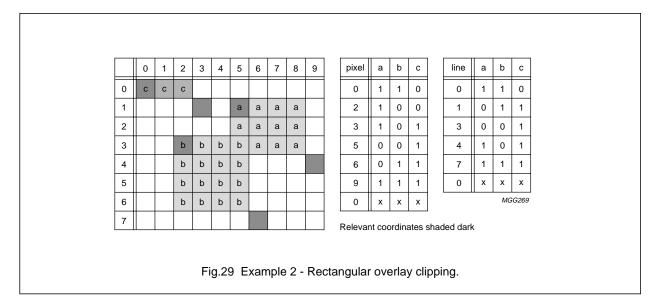

- Rectangular clipping of frame buffer areas minimizes PCI-bus load

- Random shape mask clipping protects selectable areas of frame buffer

- 3 × 128 Dword video FIFO with overflow detection and 'graceful' recovery.

#### 1.2 Audio processing

- Time Slot List (TSL) processing for flexible control of audio frames up to 256 bits on 2 asynchronous bidirectional digital audio interfaces simultaneously (4 DMA channels)

- · Video synchronous audio capture, e.g. for sound cards

- Various synchronization modes to support I<sup>2</sup>S and other different audio and DSP data formats

- Audio input level monitoring enables peak control via software

- Programmable bit clock generation for master and slave applications.

1998 Apr 09

#### 1.3 Scaling

- Scaling of video pictures down to randomly sized windows (vertical down to 1 : 1024; horizontal down to 1 : 256)

- High Performance Scaler (HPS) offers two-dimensional, phase correct data processing for improved signal quality of scaled video data, especially for compression applications

- Horizontal and vertical FIR filters with up to 65 taps

- Horizontal upscaling (zoom) supports e.g. CCIR to square pixel conversion

- Additional Binary Ratio Scaler (BRS) supports CIF and QCIF formats, especially for video phone and video conferencing.

#### 1.4 Interfacing

- Dual D1 (8-bit, CCIR 656) video I/O interface

- DMSD2 compatible (16-bit YUV) video input interface

- Supports various packed (pixel dithering) and planar video output formats

- Data Expansion Bus Interface (DEBI) for interfacing with e.g. MPEG or JPEG decoders with Intel (ISA like) and Motorola (68000 like) protocol style, capability for immediate and block mode (DMA) transfers with up to 23 Mbytes/s peak data rate

- 5 digital audio I/O ports

- 4 independent user configurable General Purpose I/O Ports (GPI/O) for interrupt and status processing

- PCI interface (release 2.1)

- I<sup>2</sup>C-bus interface (bus master).

### SAA7146A

#### 1.5 General

- Subsystem (board) vendor ID support for board identification via software driver

- Internal arbitration control

- Diagnostic support and event analysis

- Programmable Vertical Blanking Interval (VBI) data region for e.g. to support INTERCAST, teletext, closed caption and similar applications

- 3.3 V supply enables reduced power consumption, 5 V tolerant I/Os for 5 V PCI signalling environment.

#### 2 GENERAL DESCRIPTION

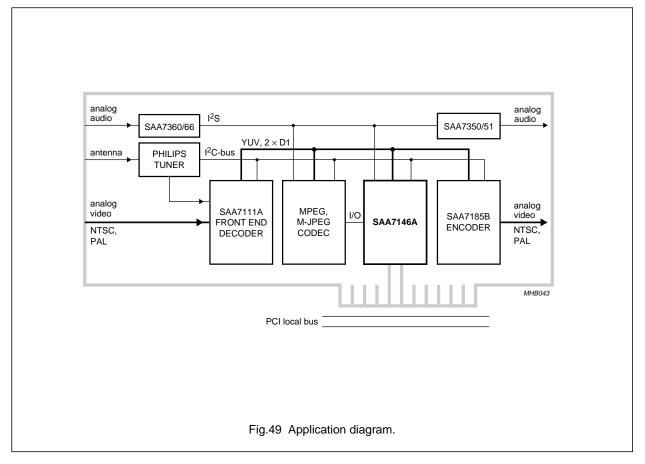

The SAA7146A, Multimedia PCI-bridge, is a highly integrated circuit for DeskTop Video (DTV) applications. The device provides a number of interface ports that enable a wide variety of video and audio ICs to be connected to the PCI-bus thus supporting a number of video applications in a PC. One example of the application capabilities is shown in Fig.49.

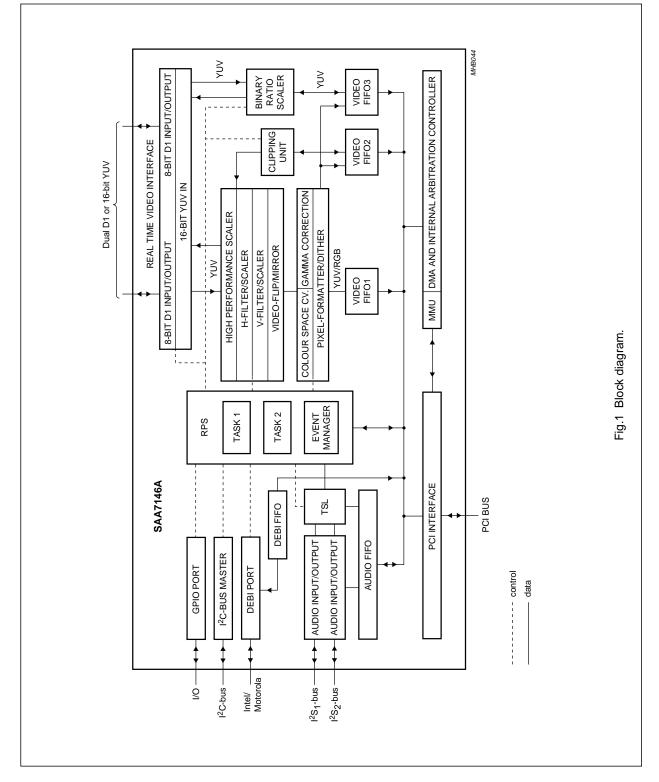

Figure 1 shows the various interface ports and the main internal function blocks.

#### 3 QUICK REFERENCE DATA

| SYMBOL                          | PARAMETER                              | MIN.                              | TYP.    | MAX.     | UNIT |

|---------------------------------|----------------------------------------|-----------------------------------|---------|----------|------|

| V <sub>DDD</sub>                | digital supply voltage                 | 3.0                               | 3.3     | 3.6      | V    |

| I <sub>DDD(tot)</sub>           | total digital supply current           | otal digital supply current – 400 |         |          |      |

| V <sub>i</sub> ; V <sub>o</sub> | data input/output levels               |                                   | TTL cor | npatible |      |

| f <sub>LLC</sub>                | LLC input clock frequency              | -                                 | -       | 32       | MHz  |

| f <sub>PCI</sub>                | PCI input clock frequency              | -                                 | -       | 33       | MHz  |

| f <sub>I2S</sub>                | I <sup>2</sup> S input clock frequency | -                                 | _       | 12.5     | MHz  |

| T <sub>amb</sub>                | operating ambient temperature          | 0                                 | -       | 70       | °C   |

#### **4 ORDERING INFORMATION**

| TYPE NUMBER | PACKAGE |                                                                                                                      |          |  |  |

|-------------|---------|----------------------------------------------------------------------------------------------------------------------|----------|--|--|

| ITPE NOMBER | NAME    | DESCRIPTION                                                                                                          | VERSION  |  |  |

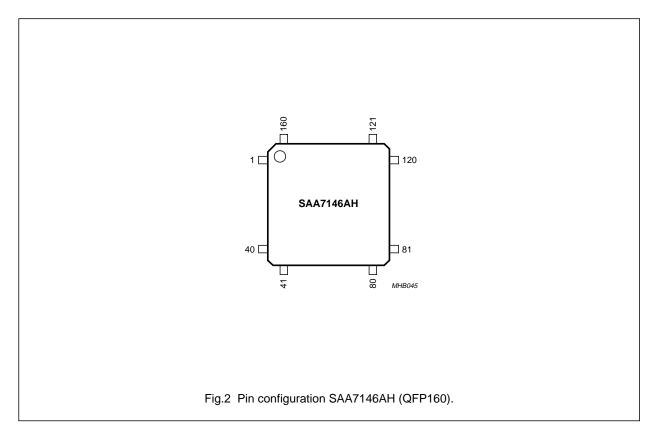

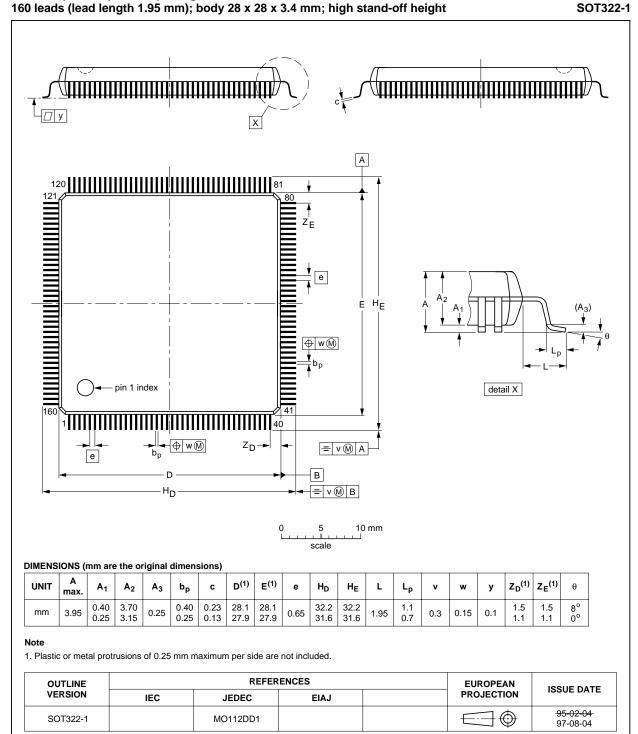

| SAA7146AH   | QFP160  | plastic quad flat package; 160 leads (lead length 1.95 mm); body $28 \times 28 \times 3.4$ mm; high stand-off height | SOT322-1 |  |  |

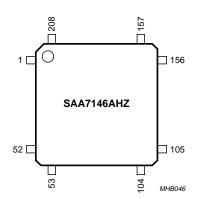

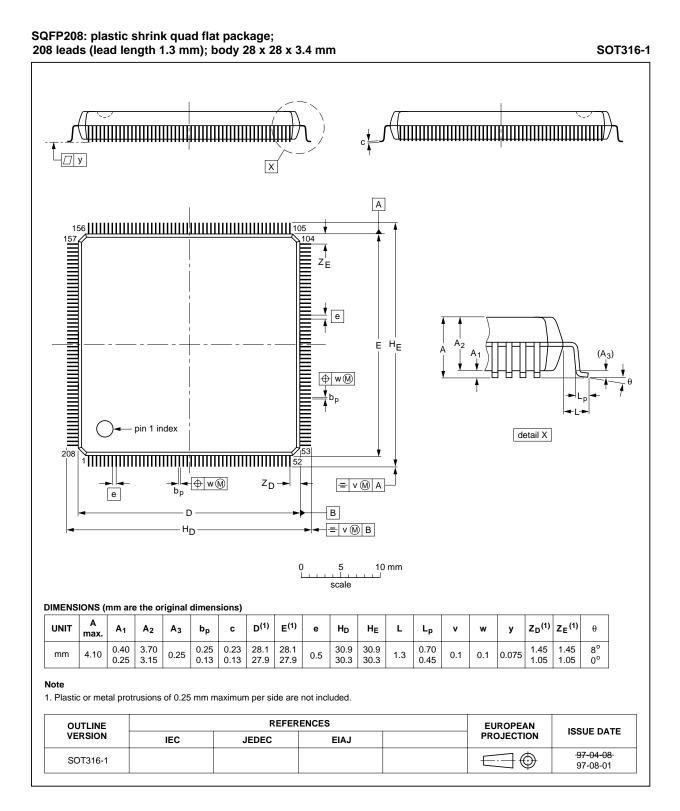

| SAA7146AHZ  | SQFP208 | plastic shrink quad flat package; 208 leads (lead length 1.3 mm); body $28 \times 28 \times 3.4$ mm                  | SOT316-1 |  |  |

#### 5 BLOCK DIAGRAM

I

### SAA7146A

### 6 PINNING

#### Pin description for QFP160

| SYMBOL            | PIN | STATUS | DESCRIPTION                                                                               |

|-------------------|-----|--------|-------------------------------------------------------------------------------------------|

| D1_A0             | 1   | I/O    | bidirectional digital CCIR 656 D1 port A bit 0                                            |

| D1_A1             | 2   | I/O    | bidirectional digital CCIR 656 D1 port A bit 1                                            |

| D1_A2             | 3   | I/O    | bidirectional digital CCIR 656 D1 port A bit 2                                            |

| D1_A3             | 4   | I/O    | bidirectional digital CCIR 656 D1 port A bit 3                                            |

| V <sub>DDD1</sub> | 5   | Р      | digital supply voltage 1 (3.3 V)                                                          |

| V <sub>SSD1</sub> | 6   | Р      | digital ground 1                                                                          |

| D1_A4             | 7   | I/O    | bidirectional digital CCIR 656 D1 port A bit 4                                            |

| D1_A5             | 8   | I/O    | bidirectional digital CCIR 656 D1 port A bit 5                                            |

| D1_A6             | 9   | I/O    | bidirectional digital CCIR 656 D1 port A bit 6                                            |

| D1_A7             | 10  | I/O    | bidirectional digital CCIR 656 D1 port A bit 7                                            |

| VS_A              | 11  | I/O    | bidirectional vertical sync signal port A                                                 |

| HS_A              | 12  | I/O    | bidirectional horizontal sync signal port A                                               |

| LLC_A             | 13  | I/O    | bidirectional line-locked system clock port A                                             |

| PXQ_A             | 14  | I/O    | bidirectional pixel qualifier signal to mark valid pixels port A; note 1                  |

| V <sub>DDD2</sub> | 15  | Р      | digital supply voltage 2 (3.3 V)                                                          |

| V <sub>SSD2</sub> | 16  | Р      | digital ground 2                                                                          |

| TRST              | 17  | I      | test reset input (JTAG pin must be set LOW for normal operation)                          |

| TMS               | 18  | I      | test mode select input (JTAG pin must be floating or set to HIGH during normal operation) |

| TCLK              | 19  | I      | test clock input (JTAG pin should be set LOW during normal operation)                     |

| TDO               | 20  | 0      | test data output (JTAG pin not active during normal operation)                            |

| TDI               | 21  | I      | test data input (JTAG pin must be floating or set to HIGH during normal operation)        |

| V <sub>DDD3</sub> | 22  | Р      | digital supply voltage 3 (3.3 V)                                                          |

| V <sub>SSD3</sub> | 23  | Р      | digital ground 3                                                                          |

| INTA#             | 24  | 0      | PCI interrupt line output (active LOW)                                                    |

| RST               | 25  | I      | PCI global reset input (active LOW)                                                       |

| CLK               | 26  | I      | PCI clock input                                                                           |

| GNT#              | 27  | I      | bus grant input signal, PCI arbitration signal (active LOW)                               |

| REQ#              | 28  | 0      | bus request output signal, PCI arbitration signal (active LOW)                            |

| V <sub>DDD4</sub> | 29  | Р      | digital supply voltage 4 (3.3 V)                                                          |

| V <sub>SSD4</sub> | 30  | Р      | digital ground 4                                                                          |

| AD PCI31          | 31  | I/O    | bidirectional PCI multiplexed address/data bit 31                                         |

| AD PCI30          | 32  | I/O    | bidirectional PCI multiplexed address/data bit 30                                         |

| AD PCI29          | 33  | I/O    | bidirectional PCI multiplexed address/data bit 29                                         |

| AD PCI28          | 34  | I/O    | bidirectional PCI multiplexed address/data bit 28                                         |

| V <sub>DDD5</sub> | 35  | Р      | digital supply voltage 5 (3.3 V)                                                          |

| V <sub>SSD5</sub> | 36  | Р      | digital ground 5                                                                          |

| AD PCI27          | 37  | I/O    | bidirectional PCI multiplexed address/data bit 27                                         |

# Multimedia bridge, high performance Scaler and PCI circuit (SPCI)

| SYMBOL             | PIN | STATUS | DESCRIPTION                                                              |

|--------------------|-----|--------|--------------------------------------------------------------------------|

| AD PCI26           | 38  | I/O    | bidirectional PCI multiplexed address/data bit 26                        |

| AD PCI25           | 39  | I/O    | bidirectional PCI multiplexed address/data bit 25                        |

| AD PCI24           | 40  | I/O    | bidirectional PCI multiplexed address/data bit 24                        |

| C/BE# [3]          | 41  | I/O    | bidirectional PCI multiplexed bus command and byte enable 3 (active LOW) |

| IDSEL              | 42  | I      | PCI initialization device select signal input                            |

| AD PCI23           | 43  | I/O    | bidirectional PCI multiplexed address/data bit 23                        |

| AD PCI22           | 44  | I/O    | bidirectional PCI multiplexed address/data bit 22                        |

| AD PCI21           | 45  | I/O    | bidirectional PCI multiplexed address/data bit 21                        |

| AD PCI20           | 46  | I/O    | bidirectional PCI multiplexed address/data bit 20                        |

| V <sub>DDD6</sub>  | 47  | Р      | digital supply voltage 6 (3.3 V)                                         |

| V <sub>SSD6</sub>  | 48  | Р      | digital ground 6                                                         |

| AD PCI19           | 49  | I/O    | bidirectional PCI multiplexed address/data bit 19                        |

| AD PCI18           | 50  | I/O    | bidirectional PCI multiplexed address/data bit 18                        |

| AD PCI17           | 51  | I/O    | bidirectional PCI multiplexed address/data bit 17                        |

| AD PCI16           | 52  | I/O    | bidirectional PCI multiplexed address/data bit 16                        |

| V <sub>DDD7</sub>  | 53  | Р      | digital supply voltage 7 (3.3 V)                                         |

| V <sub>SSD7</sub>  | 54  | Р      | digital ground 7                                                         |

| C/BE# [2]          | 55  | I/O    | bidirectional PCI multiplexed bus command and byte enable 2 (active LOW) |

| FRAME#             | 56  | I/O    | bidirectional PCI cycle frame signal (active LOW)                        |

| IRDY#              | 57  | I/O    | bidirectional PCI initiator ready signal (active LOW)                    |

| TRDY#              | 58  | I/O    | bidirectional PCI target ready signal (active LOW)                       |

| DEVSEL#            | 59  | I/O    | bidirectional PCI device select signal (active LOW)                      |

| STOP#              | 60  | I/O    | bidirectional PCI stop signal (active LOW)                               |

| PERR#              | 61  | 0      | PCI parity error signal output (active LOW)                              |

| PAR                | 62  | I/O    | bidirectional PCI parity signal                                          |

| C/BE# [1]          | 63  | I/O    | bidirectional PCI-bus command and byte enable 1 (active LOW)             |

| V <sub>DDD8</sub>  | 64  | Р      | digital supply voltage 8 (3.3 V)                                         |

| V <sub>SSD8</sub>  | 65  | Р      | digital ground 8                                                         |

| AD PCI15           | 66  | I/O    | bidirectional PCI multiplexed address/data bit 15                        |

| AD PCI14           | 67  | I/O    | bidirectional PCI multiplexed address/data bit 14                        |

| AD PCI13           | 68  | I/O    | bidirectional PCI multiplexed address/data bit 13                        |

| AD PCI12           | 69  | I/O    | bidirectional PCI multiplexed address/data bit 12                        |

| V <sub>DDD9</sub>  | 70  | Р      | digital supply voltage 9 (3.3 V)                                         |

| V <sub>SSD9</sub>  | 71  | Р      | digital ground 9                                                         |

| AD PCI11           | 72  | I/O    | bidirectional PCI multiplexed address/data bit 11                        |

| AD PCI10           | 73  | I/O    | bidirectional PCI multiplexed address/data bit 10                        |

| AD PCI9            | 74  | I/O    | bidirectional PCI multiplexed address/data bit 9                         |

| AD PCI8            | 75  | I/O    | bidirectional PCI multiplexed address/data bit 8                         |

| V <sub>DDD10</sub> | 76  | Р      | digital supply voltage 10 (3.3 V)                                        |

| V <sub>SSD10</sub> | 77  | Р      | digital ground 10                                                        |

| C/BE# [0]          | 78  | I/O    | bidirectional PCI multiplexed bus command and byte enable 0 (active LOW) |

## Multimedia bridge, high performance Scaler and PCI circuit (SPCI)

| SYMBOL             | PIN | STATUS | DESCRIPTION                                                                       |

|--------------------|-----|--------|-----------------------------------------------------------------------------------|

| AD PCI7            | 79  | I/O    | bidirectional PCI multiplexed address/data bit 7                                  |

| AD PCI6            | 80  | I/O    | bidirectional PCI multiplexed address/data bit 6                                  |

| V <sub>SSD11</sub> | 81  | Р      | digital ground 11                                                                 |

| AD PCI5            | 82  | I/O    | bidirectional PCI multiplexed address/data bit 5                                  |

| AD PCI4            | 83  | I/O    | bidirectional PCI multiplexed address/data bit 4                                  |

| AD PCI3            | 84  | I/O    | bidirectional PCI multiplexed address/data bit 3                                  |

| AD PCI2            | 85  | I/O    | bidirectional PCI multiplexed address/data bit 2                                  |

| V <sub>DDD11</sub> | 86  | Р      | digital supply voltage 11 (3.3 V)                                                 |

| V <sub>SSD12</sub> | 87  | Р      | digital ground 12                                                                 |

| AD PCI1            | 88  | I/O    | bidirectional PCI multiplexed address/data bit 1                                  |

| AD PCI0            | 89  | I/O    | bidirectional PCI multiplexed address/data bit 0                                  |

| V <sub>DDD12</sub> | 90  | Р      | digital supply voltage 12 (3.3 V)                                                 |

| V <sub>SSD13</sub> | 91  | Р      | digital ground 13                                                                 |

| AD15               | 92  | I/O    | bidirectional DEBI multiplexed address data line bit 15                           |

| AD14               | 93  | I/O    | bidirectional DEBI multiplexed address data line bit 14                           |

| AD13               | 94  | I/O    | bidirectional DEBI multiplexed address data line bit 13                           |

| AD12               | 95  | I/O    | bidirectional DEBI multiplexed address data line bit 12                           |

| V <sub>DDD13</sub> | 96  | Р      | digital supply voltage 13 (3.3 V)                                                 |

| V <sub>SSD14</sub> | 97  | Р      | digital ground 14                                                                 |

| AD11               | 98  | I/O    | bidirectional DEBI multiplexed address data line bit 11                           |

| AD10               | 99  | I/O    | bidirectional DEBI multiplexed address data line bit 10                           |

| AD9                | 100 | I/O    | bidirectional DEBI multiplexed address data line bit 9                            |

| AD8                | 101 | I/O    | bidirectional DEBI multiplexed address data line bit 8                            |

| V <sub>DDD14</sub> | 102 | Р      | digital supply voltage 14 (3.3 V)                                                 |

| V <sub>SSD15</sub> | 103 | Р      | digital ground 15                                                                 |

| RWN_SBHE           | 104 | 0      | DEBI data transfer control signal output (read write not/system byte high enable) |

| AS_ALE             | 105 | 0      | DEBI address strobe and address latch enable output                               |

| LDS_RDN            | 106 | 0      | lower data strobe/read not output                                                 |

| UDS_WRN            | 107 | 0      | upper data strobe/write not output                                                |

| DTACK_RDY          | 108 | I      | DEBI data transfer acknowledge or ready input                                     |

| V <sub>DDD15</sub> | 109 | Р      | digital supply voltage 15 (3.3 V)                                                 |

| V <sub>SSD16</sub> | 110 | Р      | digital ground 16                                                                 |

| AD0                | 111 | I/O    | bidirectional DEBI multiplexed address data line bit 0                            |

| AD1                | 112 | I/O    | bidirectional DEBI multiplexed address data line bit 1                            |

| AD2                | 113 | I/O    | bidirectional DEBI multiplexed address data line bit 2                            |

| AD3                | 114 | I/O    | bidirectional DEBI multiplexed address data line bit 3                            |

| V <sub>DDD16</sub> | 115 | Р      | digital supply voltage 16 (3.3 V)                                                 |

| V <sub>SSD17</sub> | 116 | Р      | digital ground 17                                                                 |

| AD4                | 117 | I/O    | bidirectional DEBI multiplexed address data line bit 4                            |

| AD5                | 118 | I/O    | bidirectional DEBI multiplexed address data line bit 5                            |

SYMBOL

AD6

AD7

WS0

SD0

WS1 SD1

WS2

SD2 V<sub>DDD17</sub>

BCLK1

SAA7146A

## Multimedia bridge, high performance Scaler and PCI circuit (SPCI)

| PIN | STATUS | DESCRIPTION                                                               |

|-----|--------|---------------------------------------------------------------------------|

| 119 | I/O    | bidirectional DEBI multiplexed address data line bit 6                    |

| 120 | I/O    | bidirectional DEBI multiplexed address data line bit 7                    |

| 121 | I/O    | bidirectional word select signal for audio interface A1                   |

| 122 | I/O    | bidirectional serial data for audio interface A1                          |

| 123 | I/O    | bidirectional bit clock for audio interface A1                            |

| 124 | 0      | word select output signal for audio interface A1/A2                       |

| 125 | I/O    | bidirectional serial data for audio interface A1/A2                       |

| 126 | 0      | word select output signal for audio interface A1/A2                       |

| 127 | I/O    | bidirectional serial data for audio interface A1/A2                       |

| 128 | Р      | digital supply voltage 17 (3.3 V)                                         |

| 129 | Р      | digital ground 18                                                         |

| 130 | 0      | word select output signal for audio interface A1/A2                       |

| 131 | I/O    | bidirectional serial data for audio interface A1/A2                       |

| 132 | I/O    | bidirectional bit clock for audio interface A2                            |

| 133 | I/O    | bidirectional word select signal for audio interface A2                   |

| 134 | I/O    | bidirectional serial data for audio interface A2                          |

| 135 | I      | audio reference clock input signal                                        |

| 136 | I/O    | bidirectional I <sup>2</sup> C-bus clock line                             |

| 137 | I/O    | bidirectional I <sup>2</sup> C-bus data line                              |

| 138 | Р      | digital supply voltage 18 (3.3 V)                                         |

| 139 | I      | I <sup>2</sup> C-bus voltage sense input; see note 3 of "Characteristics" |

| 140 | Р      | digital ground 19                                                         |

| 141 | I/O    | general purpose I/O signal 3                                              |

| 142 | I/O    | general purpose I/O signal 2                                              |

| 143 | I/O    | general purpose I/O signal 1                                              |

| V <sub>SSD18</sub> | 129 | Р   | digital ground 18                                                         |

|--------------------|-----|-----|---------------------------------------------------------------------------|

| WS3                | 130 | 0   | word select output signal for audio interface A1/A2                       |

| SD3                | 131 | I/O | bidirectional serial data for audio interface A1/A2                       |

| BCLK2              | 132 | I/O | bidirectional bit clock for audio interface A2                            |

| WS4                | 133 | I/O | bidirectional word select signal for audio interface A2                   |

| SD4                | 134 | I/O | bidirectional serial data for audio interface A2                          |

| ACLK               | 135 | I   | audio reference clock input signal                                        |

| SCL                | 136 | I/O | bidirectional I <sup>2</sup> C-bus clock line                             |

| SDA                | 137 | I/O | bidirectional I <sup>2</sup> C-bus data line                              |

| V <sub>DDD18</sub> | 138 | Р   | digital supply voltage 18 (3.3 V)                                         |

| V <sub>DDI2C</sub> | 139 | I   | I <sup>2</sup> C-bus voltage sense input; see note 3 of "Characteristics" |

| V <sub>SSD19</sub> | 140 | Р   | digital ground 19                                                         |

| GPIO3              | 141 | I/O | general purpose I/O signal 3                                              |

| GPIO2              | 142 | I/O | general purpose I/O signal 2                                              |

| GPIO1              | 143 | I/O | general purpose I/O signal 1                                              |

| GPIO0              | 144 | I/O | general purpose I/O signal 0                                              |

| D1_B0              | 145 | I/O | bidirectional digital CCIR 656 D1 port B bit 0                            |

| D1_B1              | 146 | I/O | bidirectional digital CCIR 656 D1 port B bit 1                            |

| D1_B2              | 147 | I/O | bidirectional digital CCIR 656 D1 port B bit 2                            |

| D1_B3              | 148 | I/O | bidirectional digital CCIR 656 D1 port B bit 3                            |

| V <sub>DDD19</sub> | 149 | Р   | digital supply voltage 19 (3.3 V)                                         |

| V <sub>SSD20</sub> | 150 | Р   | digital ground 20                                                         |

| D1_B4              | 151 | I/O | bidirectional digital CCIR 656 D1 port B bit 4                            |

| D1_B5              | 152 | I/O | bidirectional digital CCIR 656 D1 port B bit 5                            |

| D1_B6              | 153 | I/O | bidirectional digital CCIR 656 D1 port B bit 6                            |

| D1_B7              | 154 | I/O | bidirectional digital CCIR 656 D1 port B bit 7                            |

| V <sub>DDD20</sub> | 155 | Р   | digital supply voltage 20 (3.3 V)                                         |

| V <sub>SSD21</sub> | 156 | Р   | digital ground 21                                                         |

| LLC_B              | 157 | I/O | bidirectional line-locked system clock port B                             |

| VS_B               | 158 | I/O | bidirectional vertical sync signal port B                                 |

### SAA7146A

| SYMBOL | PIN | STATUS | DESCRIPTION                                                              |

|--------|-----|--------|--------------------------------------------------------------------------|

| HS_B   | 159 | I/O    | bidirectional horizontal sync signal port B                              |

| PXQ_B  | 160 | I/O    | bidirectional pixel qualifier signal to mark valid pixels port B; note 2 |

#### Notes

1. For continuous CCIR 656 format at the D1\_A port this pin must be set HIGH.

2. For continuous CCIR 656 format at the D1\_B port this pin must be set HIGH.

# Multimedia bridge, high performance Scaler and PCI circuit (SPCI)

### Pin description for SQFP208

| SYMBOL            | PIN | STATUS | DESCRIPTION                                                                               |  |

|-------------------|-----|--------|-------------------------------------------------------------------------------------------|--|

| V <sub>SSD0</sub> | 1   | Р      | digital ground 0                                                                          |  |

| D1_A0             | 2   | I/O    | bidirectional digital CCIR 656 D1 port A bit 0                                            |  |

| D1_A1             | 3   | I/O    | bidirectional digital CCIR 656 D1 port A bit 1                                            |  |

| D1_A2             | 4   | I/O    | bidirectional digital CCIR 656 D1 port A bit 2                                            |  |

| D1_A3             | 5   | I/O    | bidirectional digital CCIR 656 D1 port A bit 3                                            |  |

| V <sub>DDD1</sub> | 6   | Р      | digital supply voltage 1 (3.3 V)                                                          |  |

| n.c.              | 7   | -      | reserved pin; not connected internally                                                    |  |

| V <sub>SSD1</sub> | 8   | Р      | digital ground 1                                                                          |  |

| D1_A4             | 9   | I/O    | bidirectional digital CCIR 656 D1 port A bit 4                                            |  |

| D1_A5             | 10  | I/O    | bidirectional digital CCIR 656 D1 port A bit 5                                            |  |

| D1_A6             | 11  | I/O    | bidirectional digital CCIR 656 D1 port A bit 6                                            |  |

| D1_A7             | 12  | I/O    | bidirectional digital CCIR 656 D1 port A bit 7                                            |  |

| V <sub>DDD2</sub> | 13  | Р      | digital supply voltage 2 (3.3 V)                                                          |  |

| n.c.              | 14  | -      | reserved pin; not connected internally                                                    |  |

| V <sub>SSD2</sub> | 15  | Р      | digital ground 2                                                                          |  |

| VS_A              | 16  | I/O    | bidirectional vertical sync signal port A                                                 |  |

| HS_A              | 17  | I/O    | bidirectional horizontal sync signal port A                                               |  |

| LLC_A             | 18  | I/O    | bidirectional line-locked system clock port A                                             |  |

| PXQ_A             | 19  | I/O    | bidirectional pixel qualifier signal to mark valid pixels port A; note 1                  |  |

| n.c.              | 20  | -      | reserved pin; do not connect                                                              |  |

| V <sub>DDD3</sub> | 21  | Р      | digital supply voltage 3 (3.3 V)                                                          |  |

| n.c.              | 22  | -      | reserved pin; not connected internally                                                    |  |

| V <sub>SSD3</sub> | 23  | Р      | digital ground 3                                                                          |  |

| TRST              | 24  | I      | test reset input (JTAG pin must be set LOW for normal operation)                          |  |

| TMS               | 25  | I      | test mode select input (JTAG pin must be floating or set to HIGH during normal operation) |  |

| TCLK              | 26  | I      | test clock input (JTAG pin should be set LOW during normal operation)                     |  |

| TDO               | 27  | 0      | test data output (JTAG pin not active during normal operation)                            |  |

| TDI               | 28  | I      | test data input (JTAG pin must be floating or set to HIGH during normal operation)        |  |

| V <sub>DDD4</sub> | 29  | Р      | digital supply voltage 4 (3.3 V)                                                          |  |

| n.c.              | 30  | -      | reserved pin; not connected internally                                                    |  |

| V <sub>SSD4</sub> | 31  | Р      | digital ground 4                                                                          |  |

| INTA#             | 32  | 0      | PCI interrupt line output (active LOW)                                                    |  |

| RST#              | 33  | I      | PCI global reset input (active LOW)                                                       |  |

| CLK               | 34  | I      | PCI clock input                                                                           |  |

| GNT#              | 35  | I      | bus grant input signal input, PCI arbitration signal (active LOW)                         |  |

| REQ#              | 36  | 0      | bus request output signal output, PCI arbitration signal (active LOW)                     |  |

| V <sub>DDD5</sub> | 37  | Р      | digital supply voltage 5 (3.3 V)                                                          |  |

| n.c.              | 38  | -      | reserved pin; not connected internally                                                    |  |

## SAA7146A

| SYMBOL             | PIN | STATUS | DESCRIPTION                                                              |  |  |

|--------------------|-----|--------|--------------------------------------------------------------------------|--|--|

| V <sub>SSD5</sub>  | 39  | Р      | digital ground 5                                                         |  |  |

| AD PCI31           | 40  | I/O    | bidirectional PCI multiplexed address/data bit 31                        |  |  |

| AD PCI30           | 41  | I/O    | bidirectional PCI multiplexed address/data bit 30                        |  |  |

| AD PCI29           | 42  | I/O    | bidirectional PCI multiplexed address/data bit 29                        |  |  |

| AD PCI28           | 43  | I/O    | bidirectional PCI multiplexed address/data bit 28                        |  |  |

| V <sub>DDD6</sub>  | 44  | Р      | digital supply voltage 6 (3.3 V)                                         |  |  |

| n.c.               | 45  | _      | reserved pin; not connected internally                                   |  |  |

| V <sub>SSD6</sub>  | 46  | Р      | digital ground 6                                                         |  |  |

| AD PCI27           | 47  | I/O    | bidirectional PCI multiplexed address/data bit 27                        |  |  |

| AD PCI26           | 48  | I/O    | bidirectional PCI multiplexed address/data bit 26                        |  |  |

| AD PCI25           | 49  | I/O    | bidirectional PCI multiplexed address/data bit 25                        |  |  |

| AD PCI24           | 50  | I/O    | bidirectional PCI multiplexed address/data bit 24                        |  |  |

| V <sub>DDD7</sub>  | 51  | Р      | digital supply voltage 7 (3.3 V)                                         |  |  |

| n.c.               | 52  | _      | reserved pin; do not connect                                             |  |  |

| n.c.               | 53  | _      | reserved pin; not connected internally                                   |  |  |

| V <sub>SSD7</sub>  | 54  | Р      | digital ground 7                                                         |  |  |

| C/BE# [3]          | 55  | I/O    | bidirectional PCI multiplexed bus command and byte enable 3 (active LOW) |  |  |

| IDSEL              | 56  | I      | PCI initialization device select input signal                            |  |  |

| AD PCI23           | 57  | I/O    | bidirectional PCI multiplexed address/data bit 23                        |  |  |

| AD PCI22           | 58  | I/O    | bidirectional PCI multiplexed address/data bit 22                        |  |  |

| AD PCI21           | 59  | I/O    | bidirectional PCI multiplexed address/data bit 21                        |  |  |

| AD PCI20           | 60  | I/O    | bidirectional PCI multiplexed address/data bit 20                        |  |  |

| n.c.               | 61  | _      | reserved pin; do not connect                                             |  |  |

| n.c.               | 62  | _      | reserved pin; not connected internally                                   |  |  |

| V <sub>SSD8</sub>  | 63  | Р      | digital ground 8                                                         |  |  |

| AD PCI19           | 64  | I/O    | bidirectional PCI multiplexed address/data bit 19                        |  |  |

| AD PCI18           | 65  | I/O    | bidirectional PCI multiplexed address/data bit 18                        |  |  |

| AD PCI17           | 66  | I/O    | bidirectional PCI multiplexed address/data bit 17                        |  |  |

| AD PCI16           | 67  | I/O    | bidirectional PCI multiplexed address/data bit 16                        |  |  |

| V <sub>DDD8</sub>  | 68  | Р      | digital supply voltage 8 (3.3 V)                                         |  |  |

| n.c.               | 69  | _      | reserved pin; do not connect                                             |  |  |

| V <sub>SSD9</sub>  | 70  | Р      | digital ground 9                                                         |  |  |

| C/BE# [2]          | 71  | I/O    | bidirectional PCI multiplexed bus command and byte enable 2 (active LOW) |  |  |

| FRAME#             | 72  | I/O    | bidirectional PCI cycle frame signal (active LOW)                        |  |  |

| IRDY#              | 73  | I/O    | bidirectional PCI initiator ready signal (active LOW)                    |  |  |

| TRDY#              | 74  | I/O    | bidirectional PCI target ready signal (active LOW)                       |  |  |

| V <sub>DDD9</sub>  | 75  | Р      | digital supply voltage 9 (3.3 V)                                         |  |  |

| n.c.               | 76  | _      | reserved pin; do not connect                                             |  |  |

| V <sub>SSD10</sub> | 77  | Р      | digital ground 10                                                        |  |  |

| DEVSEL#            | 78  | I/O    | bidirectional PCI device select signal (active LOW)                      |  |  |

# Multimedia bridge, high performance Scaler and PCI circuit (SPCI)

| SYMBOL             | PIN | STATUS | DESCRIPTION                                                            |  |  |

|--------------------|-----|--------|------------------------------------------------------------------------|--|--|

| STOP#              | 79  | I/O    | bidirectional PCI stop signal (active LOW)                             |  |  |

| PERR#              | 80  | 0      | PCI parity error output signal (active LOW)                            |  |  |

| n.c.               | 81  | -      | reserved pin; do not connect                                           |  |  |

| PAR                | 82  | I/O    | bidirectional PCI parity signal                                        |  |  |

| C/BE# [1]          | 83  | I/O    | bidirectional PCI-bus command and byte enable 1 (active LOW)           |  |  |

| V <sub>DDD10</sub> | 84  | Р      | digital supply voltage 10 (3.3 V)                                      |  |  |

| n.c.               | 85  | -      | reserved pin; not connected internally                                 |  |  |

| V <sub>SSD11</sub> | 86  | Р      | digital ground 11                                                      |  |  |

| AD PCI15           | 87  | I/O    | bidirectional PCI multiplexed address/data bit 15                      |  |  |

| AD PCI14           | 88  | I/O    | bidirectional PCI multiplexed address/data bit 14                      |  |  |

| AD PCI13           | 89  | I/O    | bidirectional PCI multiplexed address/data bit 13                      |  |  |

| AD PCI12           | 90  | I/O    | bidirectional PCI multiplexed address/data bit 12                      |  |  |

| V <sub>DDD11</sub> | 91  | Р      | digital supply voltage 11 (3.3 V)                                      |  |  |

| n.c.               | 92  | -      | reserved pin; not connected internally                                 |  |  |

| V <sub>SSD12</sub> | 93  | Р      | digital ground 12                                                      |  |  |

| AD PCI11           | 94  | I/O    | bidirectional PCI multiplexed address/data bit 11                      |  |  |

| AD PCI10           | 95  | I/O    | bidirectional PCI multiplexed address/data bit 10                      |  |  |

| AD PCI9            | 96  | I/O    | bidirectional PCI multiplexed address/data bit 9                       |  |  |

| AD PCI8            | 97  | I/O    | bidirectional PCI multiplexed address/data bit 8                       |  |  |

| n.c.               | 98  | _      | reserved pin; do not connect                                           |  |  |

| n.c.               | 99  | _      | reserved pin; not connected internally                                 |  |  |

| V <sub>SSD13</sub> | 100 | Р      | digital ground 13                                                      |  |  |

| C/BE# [0]          | 101 | I/O    | bidirectional PCI multiplexed bus command and byte enable (active LOW) |  |  |

| AD PCI7            | 102 | I/O    | bidirectional PCI multiplexed address/data bit 7                       |  |  |

| AD PCI6            | 103 | I/O    | bidirectional PCI multiplexed address/data bit 6                       |  |  |

| V <sub>DDD12</sub> | 104 | Р      | digital supply voltage 12 (3.3 V)                                      |  |  |

| n.c.               | 105 | -      | reserved pin; do not connect                                           |  |  |

| n.c.               | 106 | -      | reserved pin; not connected internally                                 |  |  |

| V <sub>SSD14</sub> | 107 | Р      | digital ground 14                                                      |  |  |

| AD PCI5            | 108 | I/O    | bidirectional PCI multiplexed address/data bit 5                       |  |  |

| AD PCI4            | 109 | I/O    | bidirectional PCI multiplexed address/data bit 4                       |  |  |

| AD PCI3            | 110 | I/O    | bidirectional PCI multiplexed address/data bit 3                       |  |  |

| AD PCI2            | 111 | I/O    | bidirectional PCI multiplexed address/data bit 2                       |  |  |

| V <sub>DDD13</sub> | 112 | Р      | digital supply voltage 13 (3.3 V)                                      |  |  |

| n.c.               | 113 | _      | reserved pin; not connected internally                                 |  |  |

| V <sub>SSD15</sub> | 114 | Р      | digital ground 15                                                      |  |  |

| AD PCI1            | 115 | I/O    | bidirectional PCI multiplexed address/data bit 1                       |  |  |

| AD PCI0            | 116 | I/O    | bidirectional PCI multiplexed address/data bit 0                       |  |  |

| V <sub>DDD14</sub> | 117 | Р      | digital supply voltage 14 (3.3 V)                                      |  |  |

| n.c.               | 118 | -      | reserved pin; not connected internally                                 |  |  |

| V <sub>SSD16</sub> | 119 | Р      | digital ground 16                                                      |  |  |

## Multimedia bridge, high performance Scaler and PCI circuit (SPCI)

| SYMBOL             | PIN | STATUS | DESCRIPTION                                                                       |  |  |  |

|--------------------|-----|--------|-----------------------------------------------------------------------------------|--|--|--|

| AD15               | 120 | I/O    | bidirectional DEBI multiplexed address data line bit 15                           |  |  |  |

| AD14               | 121 | I/O    | bidirectional DEBI multiplexed address data line bit 14                           |  |  |  |

| AD13               | 122 | I/O    | bidirectional DEBI multiplexed address data line bit 13                           |  |  |  |

| AD12               | 123 | I/O    | bidirectional DEBI multiplexed address data line bit 12                           |  |  |  |

| V <sub>DDD15</sub> | 124 | Р      | digital supply voltage 15 (3.3 V)                                                 |  |  |  |

| n.c.               | 125 | -      | reserved pin; not connected internally                                            |  |  |  |

| V <sub>SSD17</sub> | 126 | Р      | digital ground 17                                                                 |  |  |  |

| AD11               | 127 | I/O    | bidirectional DEBI multiplexed address data line bit 11                           |  |  |  |

| AD10               | 128 | I/O    | bidirectional DEBI multiplexed address data line bit 10                           |  |  |  |

| AD9                | 129 | I/O    | bidirectional DEBI multiplexed address data line bit 9                            |  |  |  |

| AD8                | 130 | I/O    | bidirectional DEBI multiplexed address data line bit 8                            |  |  |  |

| V <sub>DDD16</sub> | 131 | Р      | digital supply voltage 16 (3.3 V)                                                 |  |  |  |

| n.c.               | 132 | -      | reserved pin; not connected internally                                            |  |  |  |

| V <sub>SSD18</sub> | 133 | Р      | digital ground 18                                                                 |  |  |  |

| RWN_SBHE           | 134 | 0      | DEBI data transfer control output signal (read write not/system byte high enable) |  |  |  |

| AS_ALE             | 135 | 0      | DEBI address strobe and address latch enable output                               |  |  |  |

| LDS_RDN            | 136 | 0      | lower data strobe/read not output                                                 |  |  |  |

| UDS_WRN            | 137 | 0      | upper data strobe/write not output                                                |  |  |  |

| DTACK_RDY          | 138 | I      | DEBI data transfer acknowledge or ready input                                     |  |  |  |

| V <sub>DDD17</sub> | 139 | Р      | digital supply voltage 17 (3.3 V)                                                 |  |  |  |

| n.c.               | 140 | -      | reserved pin; not connected internally                                            |  |  |  |

| V <sub>SSD19</sub> | 141 | Р      | digital ground 19                                                                 |  |  |  |

| AD0                | 142 | I/O    | bidirectional DEBI multiplexed address data line bit 0                            |  |  |  |

| AD1                | 143 | I/O    | bidirectional DEBI multiplexed address data line bit 1                            |  |  |  |

| AD2                | 144 | I/O    | bidirectional DEBI multiplexed address data line bit 2                            |  |  |  |

| AD3                | 145 | I/O    | bidirectional DEBI multiplexed address data line bit 3                            |  |  |  |

| V <sub>DDD18</sub> | 146 | Р      | digital supply voltage 18 (3.3 V)                                                 |  |  |  |

| n.c.               | 147 | -      | reserved pin; not connected internally                                            |  |  |  |

| V <sub>SSD20</sub> | 148 | Р      | digital ground 20                                                                 |  |  |  |

| AD4                | 149 | I/O    | bidirectional DEBI multiplexed address data line bit 4                            |  |  |  |

| AD5                | 150 | I/O    | bidirectional DEBI multiplexed address data line bit 5                            |  |  |  |

| AD6                | 151 | I/O    | bidirectional DEBI multiplexed address data line bit 6                            |  |  |  |

| AD7                | 152 | I/O    | bidirectional DEBI multiplexed address data line bit 7                            |  |  |  |

| n.c.               | 153 | _      | reserved pin; do not connect                                                      |  |  |  |

| n.c.               | 154 | _      | reserved pin; do not connect                                                      |  |  |  |

| V <sub>DDD19</sub> | 155 | Р      | digital supply voltage 19 (3.3 V)                                                 |  |  |  |

| n.c.               | 156 | -      | reserved pin; not connected internally                                            |  |  |  |

| n.c.               | 157 | -      | reserved pin; do not connect                                                      |  |  |  |

| V <sub>SSD21</sub> | 158 | Р      | digital ground 21                                                                 |  |  |  |

| WS0                | 159 | I/O    | bidirectional word select signal for audio interface A1                           |  |  |  |

| SD0                | 160 | I/O    | bidirectional serial data for audio interface A1                                  |  |  |  |

## SAA7146A

| SYMBOL             | PIN | STATUS | DESCRIPTION                                                               |  |  |

|--------------------|-----|--------|---------------------------------------------------------------------------|--|--|

| BCLK1              | 161 | I/O    | bidirectional bit clock for audio interface A1                            |  |  |

| WS1                | 162 | 0      | word select output signal for audio interface A1/A2                       |  |  |

| SD1                | 163 | I/O    | bidirectional serial data for audio interface A1/A2                       |  |  |

| WS2                | 164 | 0      | word select output signal for audio interface A1/A2                       |  |  |

| SD2                | 165 | I/O    | bidirectional serial data for audio interface A1/A2                       |  |  |

| V <sub>DDD20</sub> | 166 | Р      | digital supply voltage 20 (3.3 V)                                         |  |  |

| n.c.               | 167 | -      | reserved pin; not connected internally                                    |  |  |

| V <sub>SSD22</sub> | 168 | Р      | digital ground 22                                                         |  |  |

| WS3                | 169 | 0      | word select output signal for audio interface A1/A2                       |  |  |

| SD3                | 170 | I/O    | bidirectional serial data for audio interface A1/A2                       |  |  |

| BCLK2              | 171 | I/O    | bidirectional bit clock for audio interface A2                            |  |  |

| WS4                | 172 | I/O    | bidirectional word select signal for audio interface A2                   |  |  |

| SD4                | 173 | I/O    | bidirectional serial data for audio interface A2                          |  |  |

| ACLK               | 174 | I      | audio reference clock input signal                                        |  |  |

| SCL                | 175 | I/O    | bidirectional I <sup>2</sup> C-bus clock line                             |  |  |

| SDA                | 176 | I/O    | bidirectional I <sup>2</sup> C-bus data line                              |  |  |

| V <sub>DDD21</sub> | 177 | Р      | digital supply voltage 21 (3.3 V)                                         |  |  |

| V <sub>DDI2C</sub> | 178 | 1      | I <sup>2</sup> C-bus voltage sense input; see note 3 of "Characteristics" |  |  |

| V <sub>SSD23</sub> | 179 | Р      | digital ground 23                                                         |  |  |

| GPIO3              | 180 | I/O    | general purpose I/O signal 3                                              |  |  |

| GPIO2              | 181 | I/O    | general purpose I/O signal 2                                              |  |  |

| GPIO1              | 182 | I/O    | general purpose I/O signal 1                                              |  |  |

| GPIO0              | 183 | I/O    | general purpose I/O signal 0                                              |  |  |

| V <sub>DDD22</sub> | 184 | Р      | digital supply voltage 22 (3.3 V)                                         |  |  |

| n.c.               | 185 | -      | reserved pin; not connected internally                                    |  |  |

| V <sub>SSD24</sub> | 186 | Р      | digital ground 24                                                         |  |  |

| D1_B0              | 187 | I/O    | bidirectional digital CCIR 656 D1 port B bit 0                            |  |  |

| D1_B1              | 188 | I/O    | bidirectional digital CCIR 656 D1 port B bit 1                            |  |  |

| D1_B2              | 189 | I/O    | bidirectional digital CCIR 656 D1 port B bit 2                            |  |  |

| D1_B3              | 190 | I/O    | bidirectional digital CCIR 656 D1 port B bit 3                            |  |  |

| V <sub>DDD23</sub> | 191 | Р      | digital supply voltage 23 (3.3 V)                                         |  |  |

| n.c.               | 192 | -      | reserved pin; not connected internally                                    |  |  |

| V <sub>SSD25</sub> | 193 | Р      | digital ground 25                                                         |  |  |

| D1_B4              | 194 | I/O    | bidirectional digital CCIR 656 D1 port B bit 4                            |  |  |

| D1_B5              | 195 | I/O    | bidirectional digital CCIR 656 D1 port B bit 5                            |  |  |

| D1_B6              | 196 | I/O    | bidirectional digital CCIR 656 D1 port B bit 6                            |  |  |

| D1_B7              | 197 | I/O    | bidirectional digital CCIR 656 D1 port B bit 7                            |  |  |

| V <sub>DDD24</sub> | 198 | Р      | digital supply voltage 24 (3.3 V)                                         |  |  |

| n.c.               | 199 | -      | reserved pin; not connected internally                                    |  |  |

| V <sub>SSD26</sub> | 200 | Р      | digital ground 26                                                         |  |  |

| LLC_B              | 201 | I/O    | bidirectional line-locked system clock port B                             |  |  |

### SAA7146A

Product specification

| SYMBOL             | PIN | STATUS | DESCRIPTION                                                              |  |

|--------------------|-----|--------|--------------------------------------------------------------------------|--|

| VS_B               | 202 | I/O    | bidirectional vertical sync signal port B                                |  |

| HS_B               | 203 | I/O    | bidirectional horizontal sync signal port B                              |  |

| PXQ_B              | 204 | I/O    | bidirectional pixel qualifier signal to mark valid pixels port B; note 2 |  |

| n.c.               | 205 | -      | reserved pin; do not connect                                             |  |

| V <sub>DDD25</sub> | 206 | Р      | digital supply voltage 25 (3.3 V)                                        |  |

| n.c.               | 207 | -      | reserved pin; not connected internally                                   |  |

| n.c.               | 208 | -      | reserved pin; do not connect                                             |  |

#### Notes

- 1. For continuous CCIR 656 format at the D1\_A port this pin must be set HIGH.

- 2. For continuous CCIR 656 format at the D1\_B port this pin must be set HIGH.

Fig.3 Pin configuration SAA7146AHZ (SQFP208).

### Multimedia bridge, high performance Scaler and PCI circuit (SPCI)

#### 7 FUNCTIONAL DESCRIPTION

This chapter provides information about the features realized with this device. First, a general, thus short, description of the functionality is given. The following sections deal with the single features in a detailed manner.

#### 7.1 General

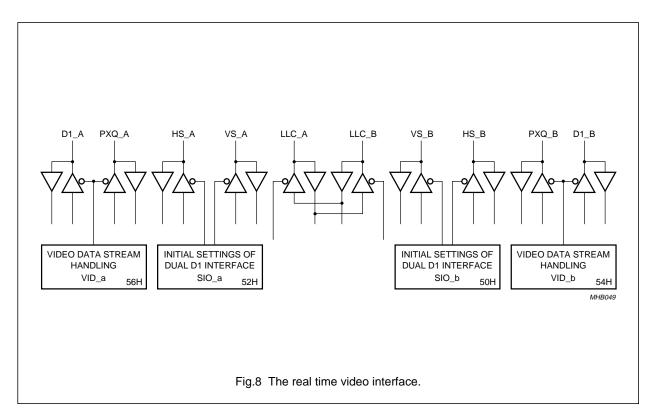

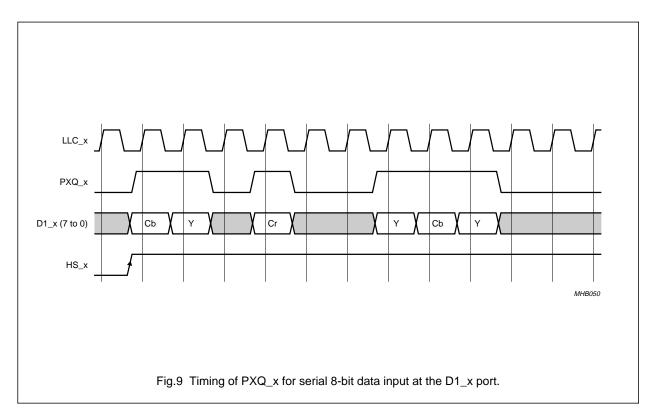

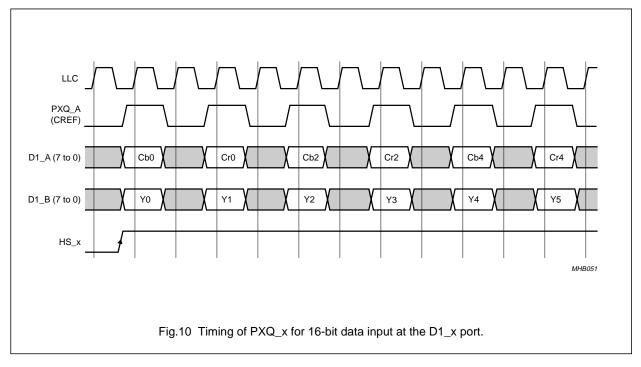

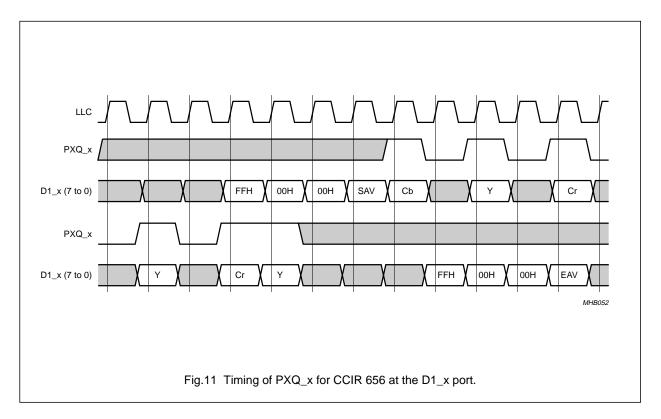

The Dual D1 (DD1) interface can be connected to digital video decoder ICs such as the SAA7110 and SAA7111A, digital video encoder such as the SAA7185B, video compression CODECs or to a D1 compatible connector, e.g. for interconnection to an external digital camera. The interface supports bidirectional full duplex two channel full D1 (CCIR 656), optionally with separate sync lines H/V, pixel qualifier signal and double pixel clock I/O, up to 32 MHz. It also supports a 16-bit parallel 'YUV bus' for interfacing to the SAA7110.

One of the two internal video processors of the SAA7146A is the two-dimensional High Performance Scaler (HPS). Phase accurate re-sampling by interpolation supports independent horizontal up and downscaling. In the horizontal direction the scaling process is performed in two functional blocks: integer decimation by window averaging (up to 65 tap), and phase linear interpolation (10 tap filter for luminance, 6 tap filter for chrominance). The vertical processing for downscaling either uses averaging over a window (up to 65 tap) or linear interpolation (2 tap). The scaling function can be used for random sized display windowing, for horizontal upscaling (zoom) or for conversion between various sample schemes such as CCIR or SQP. Incorporated with the HPS function is brightness, contrast and saturation control. Colour key generation is also established. The output of the HPS can be formatted in various RGB and YUV formats. Additionally, this output can be dithered for low bit rate formats. Packed formats as well as planar formats (YUV) are supported.

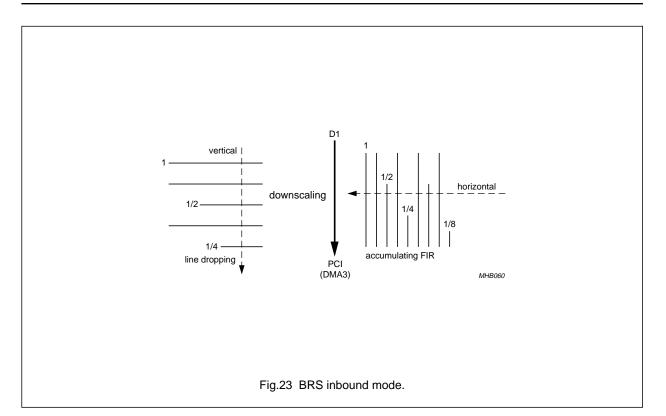

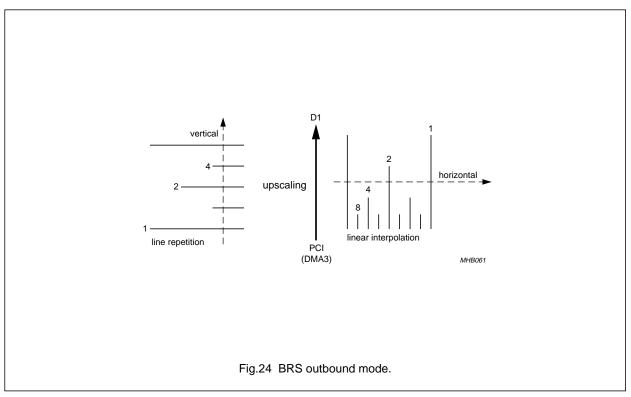

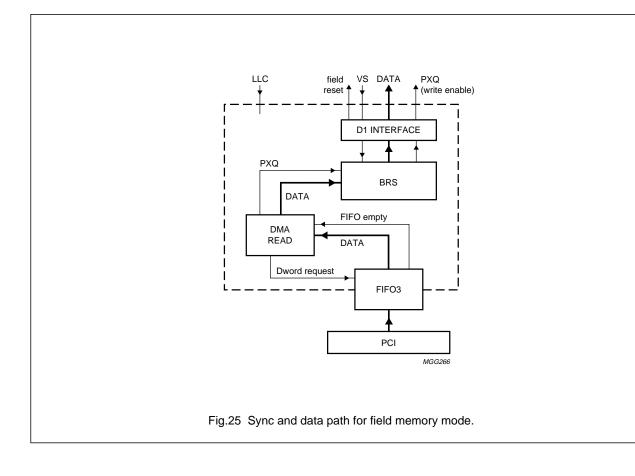

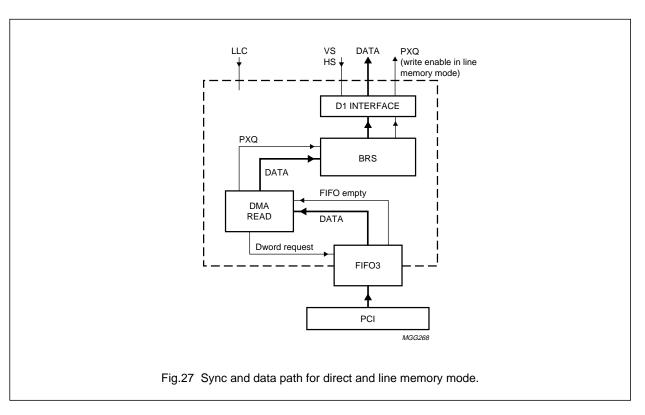

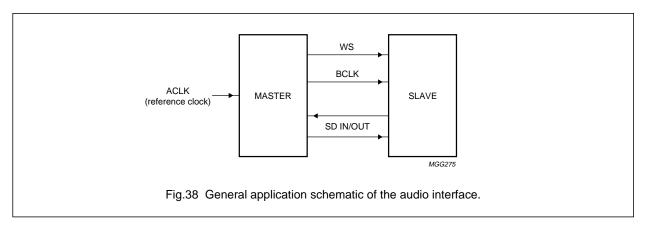

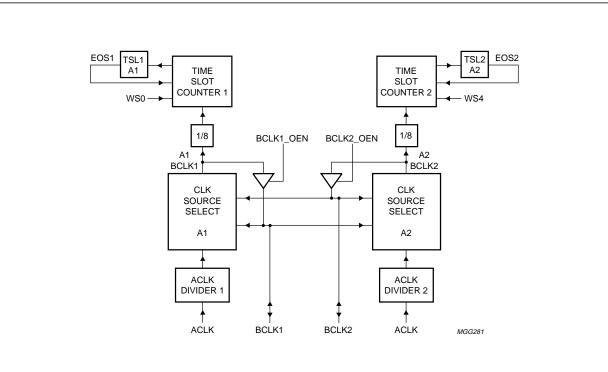

A second video channel (YUV 4 : 2 : 2 format) bypasses the HPS and connects the real time video interface with the PCI interface. This video bypass channel, using the second video processor Binary Ratio Scaler (BRS), is bidirectional and has means to convert from full size video (50 or 60 Hz) to Common Interchange Format (CIF), Quarter Common Interchange Format (QCIF) or Quarter Quarter Common Interchange Format (QQCIF) and vice versa (binary ratio 1, 2, 4, 8,  $\frac{1}{2}$ ,  $\frac{1}{4}$  and  $\frac{1}{8}$  only). Multiple programmable VBI data and test signal regions can be bypassed without processing during each field. The bidirectional digital audio serial interface is based on the l<sup>2</sup>S-bus standard, but supports flexible programming for various data and timing formats.

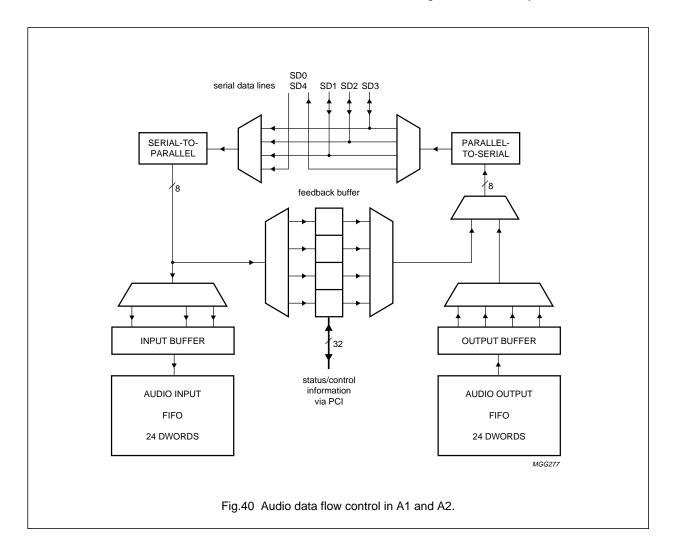

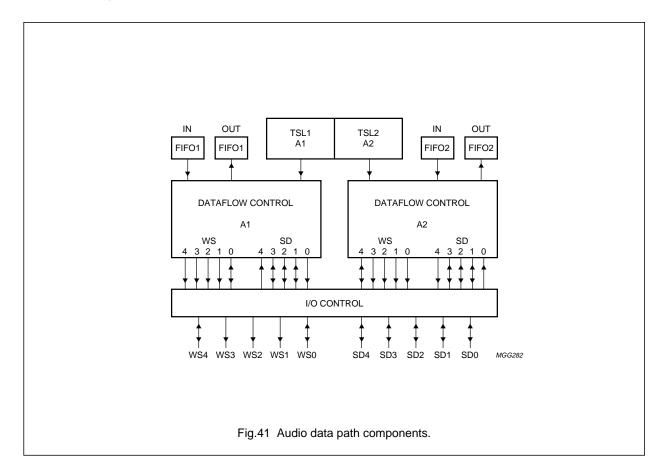

Two independent interface circuits control audio data streaming of up to  $2 \times 128$ -bit frame width (bidirectional or simultaneous input/output). Five or more I<sup>2</sup>S devices such as the SAA7360 and SAA7366 (ADC) and SAA7350 and SAA7351 (DAC) can be connected gluelessly.

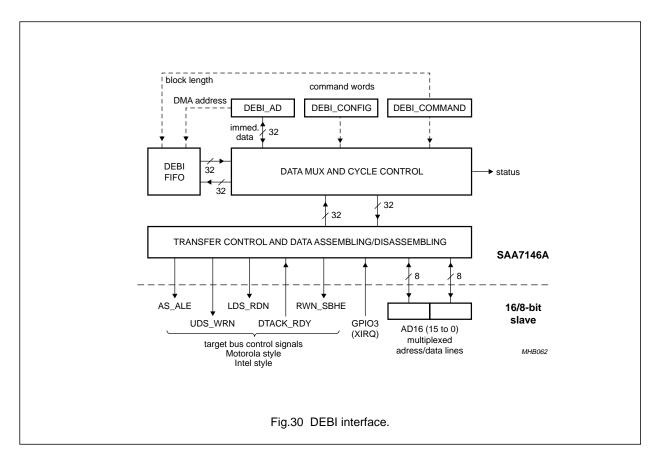

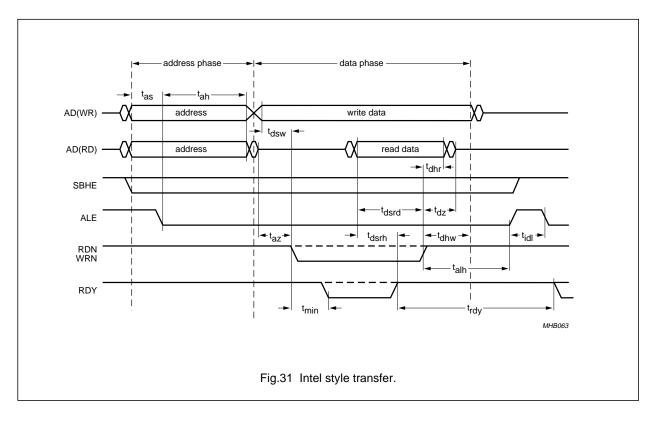

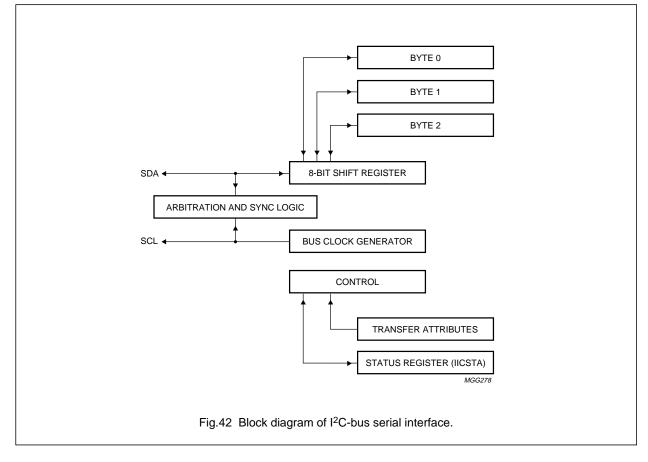

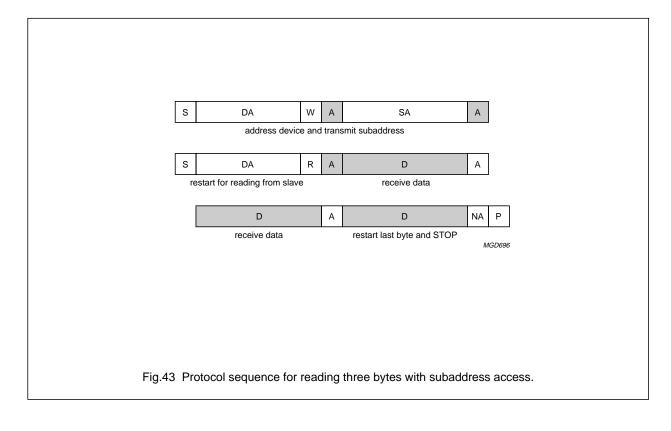

The peripheral data port [Data Expansion Bus Interface (DEBI)] enables 8 or 16-bit parallel access for system set-up and programming of peripheral multimedia devices (behind SAA7146A), but is also highly capable to interface compressed MPEG/JPEG data of peripheral ICs with the PCI system. DEBI supports both Intel compatible (ISA-bus like) and Motorola (68000 style) compatible handshaking protocols with up to 23 Mbytes/s peak data rate. Besides the parallel port, there is also an I<sup>2</sup>C-bus port to control peripheral ICs such as single-chip decoders SAA7110 and SAA7111A or as encoders such as SAA7185B and SAA7187 or as audio ICs.

The PCI interface has master read and master write capability. The video signal flows to and from the PCI and is controlled by three video DMA channels with a total FIFO capacity of 384 Dwords. The video DMA channel definition supports the typical video data structure (hierarchy) of pixels, lines, fields and frames. The audio signal flow is controlled by four audio DMA channels, each with 24 Dwords FIFO capacity. The DEBI port is connected to the PCI by single instruction direct access (immediate mode) and via a data DMA channel for streaming data (block mode) with 32 Dwords FIFO capacity. To improve PCI-bus efficiency, an arbiter schedules the access to PCI-bus for all local DMA channels.

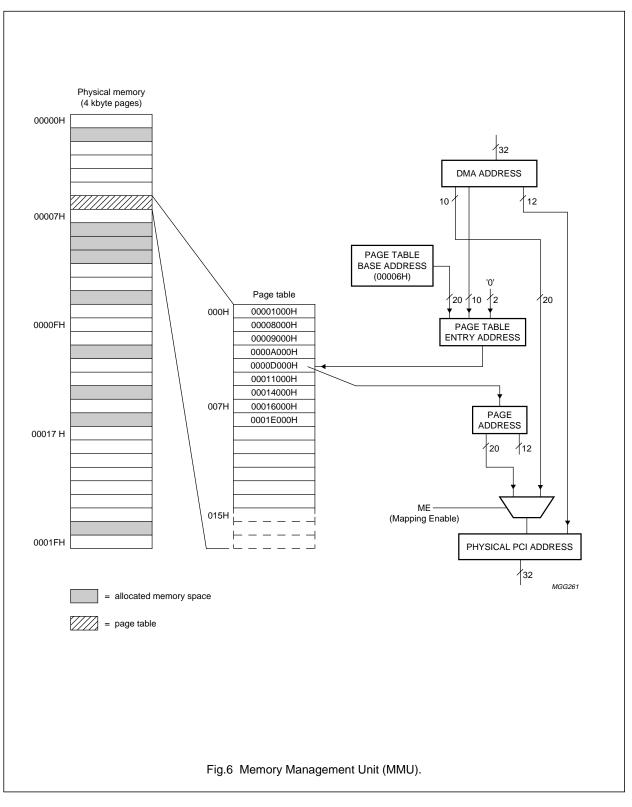

The PCI interface of the SAA7146A supports virtual memory addressing for operating systems running virtual demand paging. The integrated Memory Management Unit (MMU) translates linear addressing to physical addresses using a page table inside the system memory provided by the software driver. The MMU supports up to 4 Mbytes of virtual address space per DMA channel.

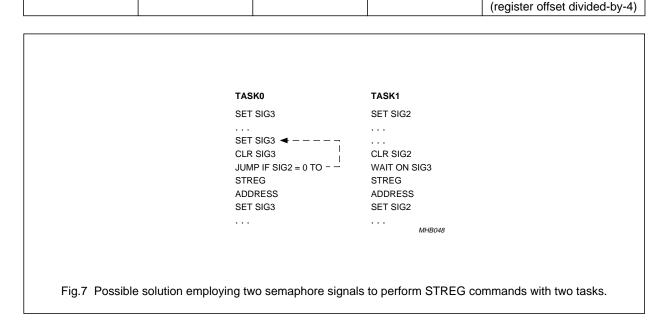

The SAA7146A can change its programming sets using a Register Programming Sequencer (RPS) that works by itself on a user defined program controlled by internally supported real time events. The SAA7146A has two RPS machines to optimize flow control of e.g. an MPEG compressed data stream and real time video scaling control. The RPS programming is defined by an instruction list in the system main memory that consists of multiple RPS commands.

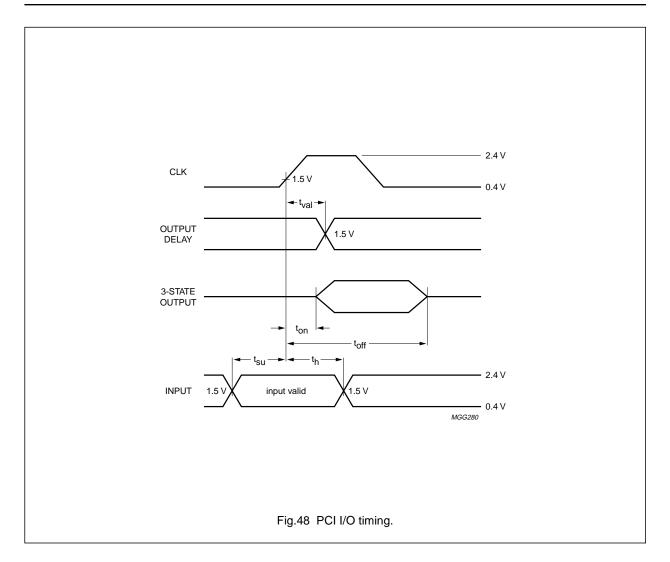

#### 7.2 PCI interface

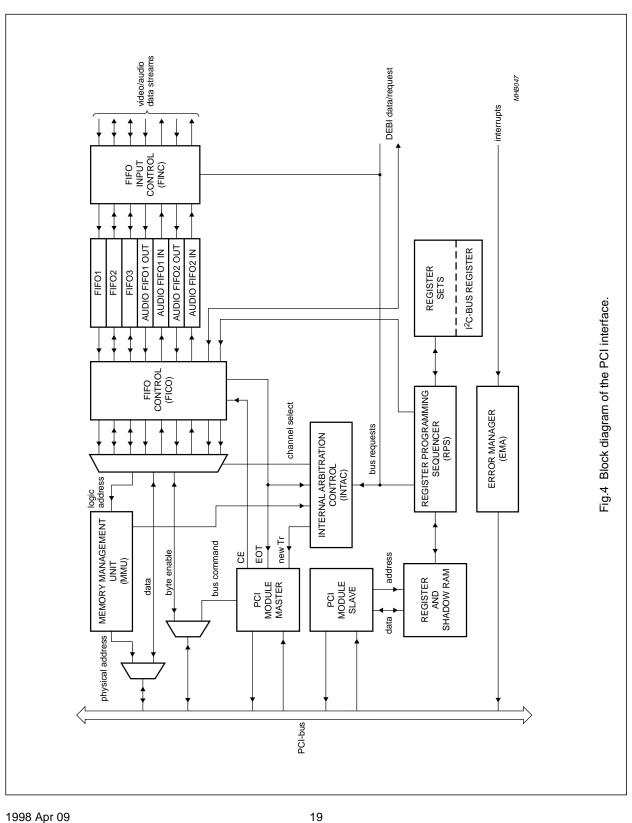

This section describes the interface of the SAA7146A to the PCI-bus. This includes the PCI modules, the DMA controls of the video, audio and data channels, the Memory Management Unit (MMU) and the Internal Arbitration Control (INTAC). The handling of the FIFOs and the corresponding errors are also described and a list of all DMA control registers is given.

#### 7.2.1 PCI MODULES AND CONFIGURATION SPACE

The SAA7146A provides a PCI-bus interface having both slave and master capability. The master and the slave module fulfil the PCI local bus specification revision 2.1. They decode the C/BE# lines to provide a byte-wise access and support 32-bit transfers up to a maximum clock rate of 33 MHz. To increase bus performance, they are able to handle fast back-to-back transfers.

During normal operation the SAA7146A checks for parity errors and reports them via the PERR# pin. If an address parity error is detected the SAA7146A will not respond. Using the SAA7146A as a slave, access is obtained only to the programmable registers and to its configuration space. Video, audio and other data of the SAA7146A reads/writes autonomously via the master interface (see Fig.4). The use of the PCI master module, i.e. which DMA channel gets access to the PCI-bus, is controlled by the INTAC (see Section 7.2.5).

The registers described in Table 1 are closely related to the PCI specification. It should be noted that Header type, Cache Line Size, BIST, Card bus CIS Pointer and Expansion ROM Base Address Registers are not implemented. All registers, which are not implemented are treated as read only with a value of zero. Some values are loaded after PCI reset via I<sup>2</sup>C-bus from EEPROM with device address 1010000 (binary). This loading will take approximately 1 ms at 33 MHz PCI clock. If any device tries to read or write data from or to the SAA7146A during the loading phase after reset, the SAA7146A will disconnect with retry.

Product specification

SAA7146A

I

## Multimedia bridge, high performance Scaler and PCI circuit (SPCI)

| ADDRESS<br>(HEX) | NAME                | BIT       | ТҮРЕ       | DESCRIPTION                                                                                                                                           |

|------------------|---------------------|-----------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00               | Device ID           | 31 to 16  | RO 7146H   | SAA7146A                                                                                                                                              |

|                  | Vendor ID           | 15 to 0   | RO 1131H   | Philips                                                                                                                                               |

| 04               | Status Register     | 31        | -          | detected parity error                                                                                                                                 |

|                  |                     | 29        | -          | received master abort                                                                                                                                 |

|                  |                     | 28        | -          | received target abort                                                                                                                                 |

|                  |                     | 26 and 25 | RO 01      | DEVSEL# timing medium                                                                                                                                 |

|                  |                     | 24        | -          | data parity error detected                                                                                                                            |

|                  |                     | 23        | RO 1       | fast back-to-back capable                                                                                                                             |

| Ī                | Command             | 9         | RW         | fast back-to-back enable                                                                                                                              |

|                  | Register            | 6         | RW         | parity error response                                                                                                                                 |

|                  |                     | 2         | RW         | bus master enable                                                                                                                                     |

|                  |                     | 1         | RW         | memory space                                                                                                                                          |

| 08               | Class Code          | 31 to 8   | RO 048000H | other multimedia device                                                                                                                               |

|                  | Revision ID         | 7 to 0    | RO 01H     | reading these 8 bits returns 01H                                                                                                                      |

| 0C               | Latency             | 15 to 8   | RW         | this register specifies, in units of PCI-bus clocks, the value of the latency timer for this PCI-bus master                                           |

| 10               | Base Address        | 31 to 9   | RW         | this value must be added to the register offset to claim                                                                                              |

|                  | Register            | 8 to 0    | RO         | access to the programming registers; the lower 8 bits are forced to zero                                                                              |

| 2C               | Subsystem ID        | 31 to 16  | RO         | this value will be loaded after a PCI reset from external hardware using the I <sup>2</sup> C-bus; the default value is 0000H                         |

|                  | Subsystem vendor ID | 15 to 0   | RO         | this value will be loaded after a PCI reset from external hardware using the I <sup>2</sup> C-bus; the default value is 0000H                         |

| 3C               | Max_Lat             | 31 to 24  | RO         | this value will be loaded after a PCI reset from external hardware using the I <sup>2</sup> C-bus; the default value is 26H                           |

|                  | Min_Gnt             | 23 to 16  | RO         | this value will be loaded after a PCI reset from external hardware using the I <sup>2</sup> C-bus; the default value is 0FH                           |

|                  | Interrupt Pin       | 15 to 8   | RO 01H     | The interrupt pin register tells which interrupt pin the device uses. This device uses interrupt pin INTA#. When these bits are read they return 01H. |

|                  | Interrupt Line      | 7 to 0    | RW         | the interrupt line register tells which input of the system<br>interrupt controller the device's interrupt pin is<br>connected to                     |

| Table 1 | Configuration | space | registers |

|---------|---------------|-------|-----------|

|         |               |       |           |

#### 7.2.2 VIDEO DMA CONTROL

The SAA7146A's DMA control is able to support up to three independent video targets or sources respectively. For this purpose it provides three video DMA channels. Each channel consists of a FIFO, a FIFO Input Control (FINC) placed on the video side of the FIFO, and a FIFO Control (FICO) placed on the PCI side of the FIFO. Channel 1 only supports the unidirectional data stream into the PCI memory. It is not able to read data from system memory. However, this access is possible using Channels 2 or 3. Table 2 surveys the possibilities and purposes of each video DMA channel.

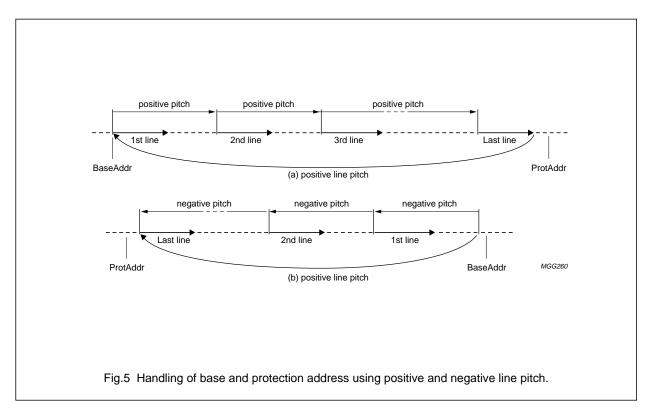

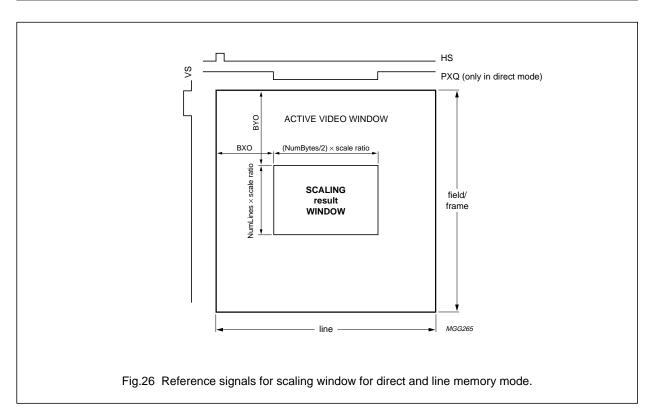

Each FIFO, i.e. each DMA channel, has its own programming set including base address (doubled for odd and even fields), pitch, protection address, page table base address, several handling mode control bits and a transfer enable bit (TR\_E). In addition, each channel has a threshold and a burst length definition for internal arbitration (see Table 6, Section 7.2.5). To handle the reading modes FIFO 2 and FIFO 3 offer some additional registers: Number of Bytes per line (NumBytes), Number of Lines per field (NumLines) and the vertical scaling ratio (only FIFO 3, see Table 69). The programming sets could be reloaded after the previous job is done [Video Transfer Done (VTD)] to support several DMA targets per FIFO. The programming set currently used is loaded by the Register Programming Sequencer (RPS). If the RPS is not used, the registers could be rewritten each time, using the SAA7146A as a slave. But then the programmer must take care of the synchronization of these write accesses.

All registers needed for DMA control are described in Table 3, except the transfer enable bits, which are described in Table 10. The registers are accessed through PCI base address with appropriate offset (see Table 1).

| FIFO   | SIZE       | DIRECTION    | PURPOSE                                                                                                                                                                       |

|--------|------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FIFO 1 | 128 Dwords | write to PCI | FIFO 1 buffers data from the HPS output and writes into PCI memory.<br>In planar mode FIFO 1 gets the Y data.                                                                 |

| FIFO 2 | 128 Dwords | RW           | <b>Planar mode</b> : FIFO 2 buffers U data provided by the HPS; the associated DMA control 2 sends it into the PCI memory.                                                    |

|        |            |              | <b>Clip mode</b> : DMA control 2 reads clipping information (clip bit mask or rectangular overlay data) from the PCI system memory and buffers it in FIFO 2.                  |

| FIFO 3 | 128 Dwords | RW           | <b>Planar mode</b> : FIFO 3 buffers V data provided by the HPS and writes it into the PCI memory.                                                                             |

|        |            |              | <b>Chroma keying mode</b> : FIFO 3 buffers chroma keying information and writes it into PCI memory.                                                                           |

|        |            |              | <b>BRS mode</b> : FIFO 3 buffers data provided by the BRS. DMA control 3 sends it into the PCI memory.                                                                        |

|        |            |              | <b>Read mode</b> : DMA control 3 reads video data from the PCI system memory (the same data up to four times to offer a simple upscaling algorithm) and buffers it in FIFO 3. |

Table 2

Size, direction and purpose of the video FIFOs and the associated DMA controls

| OFFSET<br>(HEX) | NAME      | BIT      | TYPE | DESCRIPTION                                                                                                                                                                        |  |  |

|-----------------|-----------|----------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 00              | BaseOdd1  | 31 to 0  | RW   | <b>PCI base address for odd fields</b> of the upper (or lower if pitch is negative) left pixel of the transferred field                                                            |  |  |