# Addressable relay driver

# NE/SA5090

### DESCRIPTION

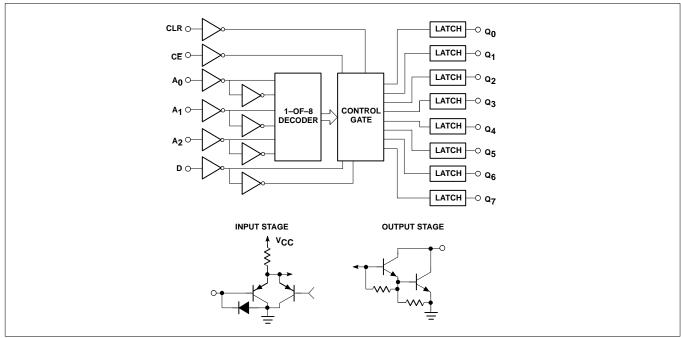

The NE/SA5090 addressable relay driver is a high-current latched driver, similar in function to the 9934 address decoder. The device has 8 open-collector Darlington power outputs, each capable of 150mA load current. The outputs are turned on or off by respectively loading a logic "1" or logic "0" into the device data input. The required output is defined by a 3-bit address. The device must be enabled by a  $\overline{CE}$  input line which also serves the function of further address decoding. A common clear input,  $\overline{CLR}$ , turns all outputs off when a logic "0" is applied. The device is packaged in a 16-pin plastic or Cerdip package.

## FEATURES

- 8 high-current outputs

- Low-loading bus-compatible inputs

- Power-on clear ensures safe operation

- Will operate in addressable or demultiplex mode

- Allows random (addressed) data entry

- Easily expandable

- Pin-compatible with 9334 (Siliconix or Fairchild)

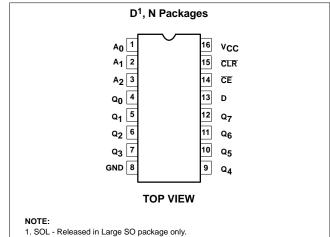

### **PIN CONFIGURATION**

# **APPLICATIONS**

- Relay driver

- Indicator lamp driver

- Triac trigger

- LED display digit driver

- Stepper motor driver

## **BLOCK DIAGRAM**

# NE/SA5090

# **PIN DESIGNATION**

| PIN NO.   | SYMBOL                         | NAME AND FUNCTION                                                                                                                                                                             |

|-----------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1-3       | A <sub>0</sub> -A <sub>2</sub> | A 3-bit binary address on these pins defines which of the 8 output latches is to receive the data.                                                                                            |

| 4-7, 9-12 | Q <sub>0</sub> -Q <sub>7</sub> | The 8 device outputs.                                                                                                                                                                         |

| 13        | D                              | The data input. When the chip is enabled, this data bit is transferred to the defined output such that:<br>"1" turns output switch "ON"<br>"0" turns output switch "OFF"                      |

| 14        | CE                             | The chip enable. When this input is low, the output latches will accept data. When CE goes high, all outputs will retain their existing state, regardless of address of data input condition. |

| 15        | CLR                            | The clear input. When CLR goes low all output switches are turned "OFF". The high data input will override the clear function on the addressed latch.                                         |

### **ORDERING INFORMATION**

| DESCRIPTION                                      | TEMPERATURE RANGE | ORDER CODE | DWG # |

|--------------------------------------------------|-------------------|------------|-------|

| 16-Pin Plastic Small Outline Large (SOL) Package | 0 to +70°C        | NE5090D    | 0171B |

| 16-Pin Plastic Dual In-Line Package (DIP)        | 0 to +70°C        | NE5090N    | 0406C |

| 16-Pin Plastic Dual In-Line Package (DIP)        | -40 to +85°C      | SA5090N    | 0406C |

| 16-Pin Plastic Small Outline Large (SOL) Package | –40 to +85°C      | SA5090D    | 0171B |

# **TRUTH TABLE**

| INPUTS |   |   |   |   | OUTPUTS |                 |                |                   |     |   |   | MODE |     |                   |

|--------|---|---|---|---|---------|-----------------|----------------|-------------------|-----|---|---|------|-----|-------------------|

| CL     | C | D | Α | Α | Α       | Q               | Q              | Q                 | Q   | Q | Q | Q    | Q   |                   |

| R      | Ε |   | 0 | 1 | 2       | 0               | 1              | 2                 | 3   | 4 | 5 | 6    | 7   |                   |

| L      | Н | Х | Х | Х | Х       | Н               | Н              | Н                 | Н   | Н | Н | Н    | Н   | Clear             |

| L      | L | L | L | L | L       | н               | Н              | Н                 | Н   | Н | Н | Н    | Н   |                   |

| L      | L | Н | L | L | L       | L               | Н              | Н                 | Н   | Н | Н | Н    | Н   |                   |

| L      | L | L | н | L | L       | н               | Н              | Н                 | н   | н | н | н    | Н   | Demultiplex       |

| L      | L | н | н | L | L       | н               | L              | Н                 | н   | н | н | н    | Н   |                   |

| L      | L | L | н | н | Н       | н               | н              | н                 | н   | н | н | н    | Н   |                   |

| L      | L | Н | Н | Н | Н       | н               | Н              | Н                 | н   | Н | Н | Н    | L   |                   |

| н      | Н | Х | Х | Х | Х       | Q <sub>N-</sub> | 1 —            |                   |     |   |   |      |     | Memory            |

| н      | L | L | L | L | L       | н               | Q <sub>N</sub> | I-1 —             |     |   |   |      | ->  |                   |

| н      | L | Н | L | L | L       | L               | QN             | l-1 <sup>──</sup> |     |   |   |      |     |                   |

| н      | L | L | н | L | L       | Q <sub>N-</sub> |                |                   | N-1 |   |   |      |     | Addressable Latch |

| н      | L | н | н | L | L       | Q <sub>N-</sub> | 1 L            | Q                 | N-1 |   |   |      |     |                   |

| н      | L | L | н | н | Н       | Q <sub>N-</sub> | 1 —            |                   |     |   |   |      | ► H |                   |

| н      | L | н | н | н | Н       | Q <sub>N-</sub> |                |                   |     |   |   |      | ► L |                   |

#### NOTES:

X=Don't care condition

$\begin{array}{l} Q_{N-1} = \mbox{Previous output state} \\ L = \mbox{Low voltage level/"ON" output state} \\ H = \mbox{High voltage level/"OFF" output state} \end{array}$

Product specification

# **ABSOLUTE MAXIMUM RATINGS**

T<sub>A</sub>=25°C, unless otherwise specified.

| SYMBOL            | PARAMETER                                     | RATING      | UNIT |

|-------------------|-----------------------------------------------|-------------|------|

| V <sub>CC</sub>   | Supply voltage                                | -0.5 to +7  | V    |

| V <sub>IN</sub>   | Input voltage                                 | -0.5 to +15 | V    |

| V <sub>OUT</sub>  | Output voltage                                | 0 to +30    | V    |

| I <sub>GND</sub>  | Ground current                                | 500         | mA   |

| I <sub>OUT</sub>  | Output current<br>Each output                 | 200         | mA   |

| P <sub>D</sub>    | Maximum power dissipation,                    |             |      |

|                   | T <sub>A</sub> =25°C (still-air) <sup>1</sup> |             |      |

|                   | N package                                     | 1712        | mW   |

|                   | D package                                     | 1315        | mW   |

| T <sub>A</sub>    | Ambient temperature range                     | 0 to +70    | °C   |

| TJ                | Junction temperature                          | 150         | °C   |

| T <sub>STG</sub>  | Storage temperature range                     | -65 to +150 | °C   |

| T <sub>SOLD</sub> | Lead soldering temperature (10sec. max)       | 300         | °C   |

NOTES:

1. Derate above 25°C at the following rates: F package at 11.1mW/°C N package at 13.7mW/°C D package at 10.5mW/°C

# DC ELECTRICAL CHARACTERISTICS

$V_{CC}$  = 4.75V to 5.25V, 0°C  ${\leq}T_{A}{\leq}$  +70°C, unless otherwise specified.1

| SYMBOL           | PADAMETED         | TEST CONDITIONS                              | LIMITS |      |      |      |

|------------------|-------------------|----------------------------------------------|--------|------|------|------|

|                  | PARAMETER         | TEST CONDITIONS                              | Min    | Тур  | Max  | UNIT |

|                  | Input voltage     |                                              |        |      |      |      |

| V <sub>IH</sub>  | High              |                                              | 2.0    |      |      | V    |

| V <sub>IL</sub>  | Low               |                                              |        |      | 0.8  |      |

|                  | Output voltage    |                                              |        |      |      |      |

| V <sub>OL</sub>  | Low               | I <sub>OL</sub> =150mA, T <sub>A</sub> =25°C |        | 1.05 | 1.30 | V    |

|                  |                   | Over temperature                             |        |      | 1.50 |      |

|                  | Input current     |                                              |        |      |      |      |

| I <sub>IH</sub>  | High              | V <sub>IN</sub> =V <sub>CC</sub>             |        | <1.0 | 10   | μA   |

| IIL              | Low               | V <sub>IN</sub> =0V                          |        | -3.0 | -250 |      |

| I <sub>OH</sub>  | Leakage current   | V <sub>OUT</sub> =28V,                       |        | 5    | 250  | μA   |

|                  | Supply current    |                                              |        |      |      |      |

| I <sub>CCL</sub> | All outputs low   | V <sub>CC</sub> =5.25V                       |        | 35   | 60   | mA   |

| ICCH             | All outputs high  |                                              |        | 22   | 50   |      |

| P <sub>D</sub>   | Power dissipation | No output load                               |        |      | 315  | mW   |

NOTES:

1. All typical values are at V<sub>CC</sub>=5V and T<sub>A</sub>=25°C

#### Product specification

# NE/SA5090

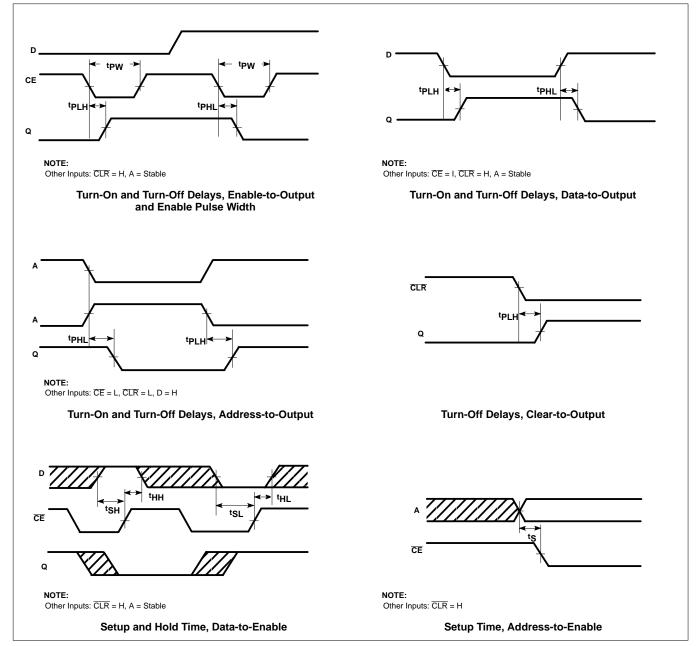

# SWITCHING CHARACTERISTICS

V<sub>CC</sub>=5V, T<sub>A</sub>=25°C, V<sub>OUT</sub>=5V, I<sub>OUT</sub>=100MA, V<sub>IL</sub>=0.8V, V<sub>IH</sub>=2.0V.

| SYMBOL             | PARAMETER                            | ТО          | FROM      | MIN | TYP | MAX  | UNIT |

|--------------------|--------------------------------------|-------------|-----------|-----|-----|------|------|

|                    | Propagation delay time               |             |           |     |     |      |      |

| t <sub>PLH</sub>   | Low-to-high <sup>1</sup>             | Output      | CE        |     | 900 | 1800 | ns   |

| t <sub>PHL</sub>   | High-to-low <sup>1</sup>             |             |           |     | 130 | 260  |      |

| t <sub>PLH</sub>   | Low-to-high <sup>2</sup>             |             |           |     | 920 | 1850 |      |

|                    |                                      | Output      | Data      |     |     |      | ns   |

| t <sub>PHL</sub>   | High-to-low <sup>2</sup>             |             |           |     | 130 | 260  |      |

| t <sub>PLH</sub>   | Low-to-high <sup>3</sup>             |             |           |     | 900 | 1800 |      |

|                    |                                      | Output      | Address   |     |     |      | ns   |

| t <sub>PHL</sub>   | High-to-low <sup>3</sup>             |             |           |     | 130 | 260  |      |

| t <sub>PLH</sub>   | Low-to-high <sup>4</sup>             |             |           |     | 920 | 1850 |      |

|                    |                                      | Output      | CLR       |     |     |      | ns   |

| t <sub>PHL</sub>   | High-to-low <sup>4</sup>             |             |           |     |     |      |      |

| Switching          | setup requirements                   |             | -         |     |     |      |      |

|                    | Setup time high                      | Chip enable | High data | 40  |     |      | 20   |

| t <sub>S(H)</sub>  | Setup time low                       | Chip enable | Low data  | 50  |     |      | ns   |

| t <sub>S(A)</sub>  | Address setup time                   | Chip enable | Address   | 40  |     |      | ns   |

|                    | Hold time high                       | Chip enable | High data | 10  |     |      | ns   |

| t <sub>H(H)</sub>  | Hold time low                        | Chip enable | Low data  | 10  |     |      | 115  |

| t <sub>PW(E)</sub> | Chip enable pulse width <sup>1</sup> |             |           | 40  |     |      | ns   |

NOTES:

1. See Turn-On and Turn-Off Delays, Enable-to-Output and Enable Pulse Width timing diagram.

2. See Turn-On and Turn-Off Delays, Data-to-Output timing diagram.

3. See Turn-On and Turn-Off Delays, Address-to-Output timing diagram.

4. See Turn-Off Delay, Clear-to-Output timing diagram.

5. See Setup and Hold Time, Data-to-Enable timing diagram.

6. See Setup Time, Address-to-Enable timing diagram.

## FUNCTIONAL DESCRIPTION

This peripheral driver has latched outputs which hold the input date until cleared. The NE5090 has active-Low, open-collector outputs, all of which are cleared when power is first applied. This device is identical to the NE590, except the outputs can withstand 28V.

## Addressable Latch Function

Any given output can be turned on or off by presenting the address of the output to be set or cleared to the three address pins, by holding the "D" input High to turn on the selected output, or by holding it Low to turn off, holding the  $\overline{CLR}$  input High, and bringing the  $\overline{CE}$  input Low. Once an output is turned on or off, it will remain so until addressed again, or until all outputs are cleared by bringing the  $\overline{CLR}$  input Low while holding the  $\overline{CE}$  input High.

## **Demultiplexer Operation**

By holding the  $\overline{\text{CLR}}$  and  $\overline{\text{CE}}$  inputs Low and the "D" input High, the addressed output will remain on and all other outputs will be off.

## **High Current Outputs**

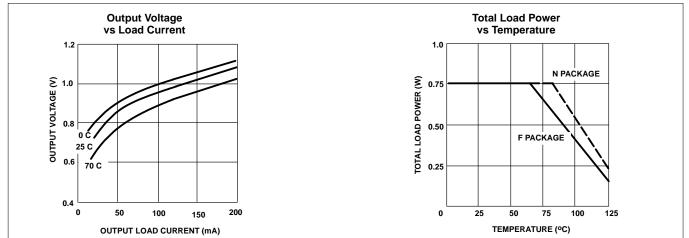

The obvious advantage of this device over other drivers such as the 9334 and N74LS259 is the fact that the outputs of the NE5090 are each capable of 200mA and 28V. It must be noted, however, that the total power dissipation would be over 2.5W if all 8 outputs were on together and carrying 200mA each. Since the total power dissipation is limited by the package to 1W, and since power dissipation due to supply current is 0.25W, the total load power dissipation by the device is limited to 0.75W at room temperature, and decreases as ambient temperature rises.

The maximum die junction temperature must be limited to  $165^{\circ}$ C, and the temperature rise above ambient and the junction temperature are defined as:

$$T_R = \theta_{JA} \times P_D$$

$$T_J = T_A + t_R$$

where

For example, if we are using the NE5090 in a plastic package in an application where the ambient temperature is never expected to rise above 50°C, and the output current at the 8 outputs, when on, are 100, 40, 50, 200, 15, 30, 80, and 10mA, we find from the graph of output voltage vs load current that the output voltages are expected to be about 0.92, 0.75, 0.78, 1.04, 0.5, 0.7, 0.9, and 0.4V, respectively. Total device power due to these loads is found to be 473.5mW. Adding the 200mW due to the power supply brings total device power dissipation to 723.5mW. The thermal resistances are 83°C,per W for plastic packages and 100°C per W for Cerdips. Using the equations above we find:

Plastic  $T_R$ =83×0.7235=60°C Plastic  $T_J$ =50+60=100°C Cerdip  $T_R$ =100×0.7235=72.4°C Cerdip  $T_J$ =50+72.4=122.4°C

Thus we find that  $T_J$  for either package is below the 165°C maximum and either package could be used in this application. The graphs of total load power vs ambient temperature would also give us this same information, although interpreting the graphs would not yield the same accuracy.

# NE/SA5090

# TIMING DIAGRAMS

# Addressable relay driver

# NE/SA5090

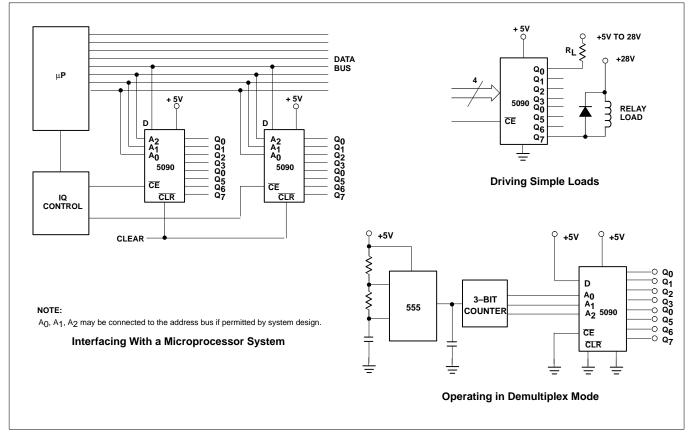

# **TYPICAL APPLICATIONS**

# **TYPICAL PERFORMANCE CHARACTERISTICS**