# MIXIM

# Low-Cost, 2-Channel, ±14-Bit Serial ADCs

## General Description

The MAX110/MAX111 analog-to-digital converters (ADCs) use an internal auto-calibration technique to achieve 14-bit resolution plus overrange, with no external components. Operating supply current is only 550μA (MAX110) and reduces to 4μA in power-down mode, making these ADCs ideal for high-resolution battery-powered or remote-sensing applications. A fast serial interface simplifies signal routing and opto-isolation, saves microcontroller pins, and offers compatibility with SPI™, QSPI™, and MICROWIRE™. The MAX110 operates with ±5V supplies, and converts differential analog signals in the -3V to +3V range. The MAX111 operates with a single +5V supply and converts differential analog signals in the ±1.5V range, or singleended signals in the 0V to +1.5V range.

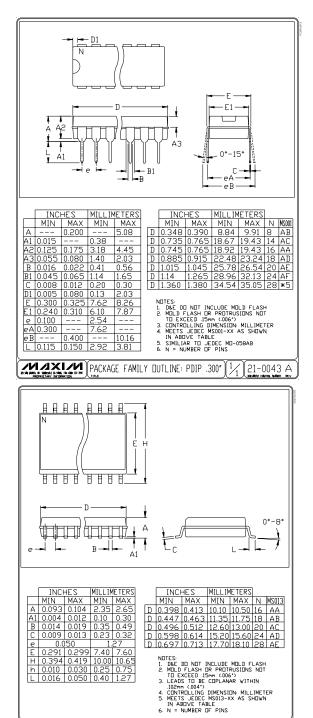

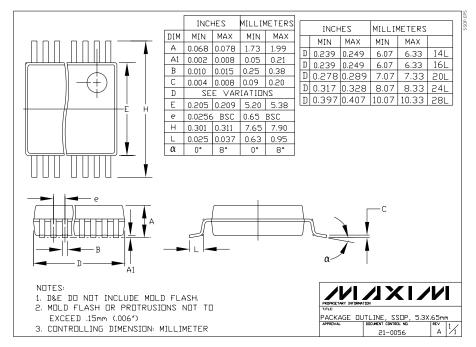

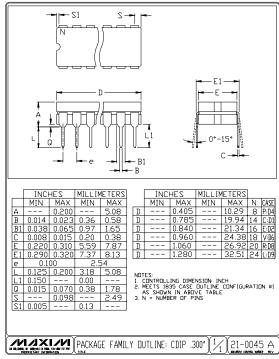

Internal calibration allows for both offset and gain-error correction under microprocessor (µP) control. Both devices are available in space-saving 16-pin DIP and SO packages, as well as an even smaller 20-pin SSOP package.

## Applications

**Process Control**

Weigh Scales

Panel Meters

**Data-Acquisition Systems**

Temperature Measurement

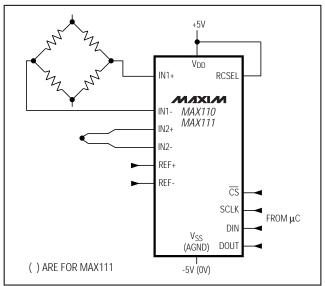

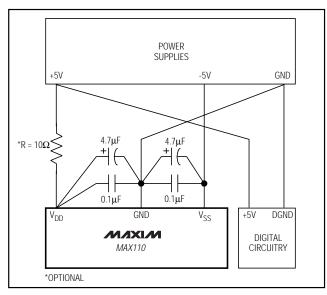

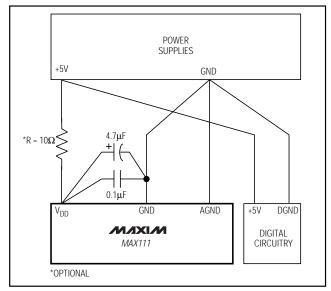

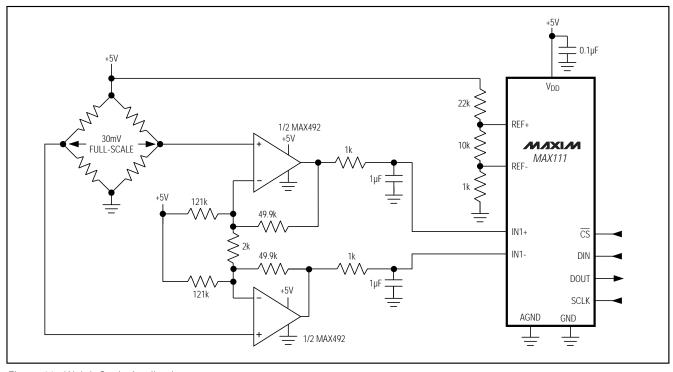

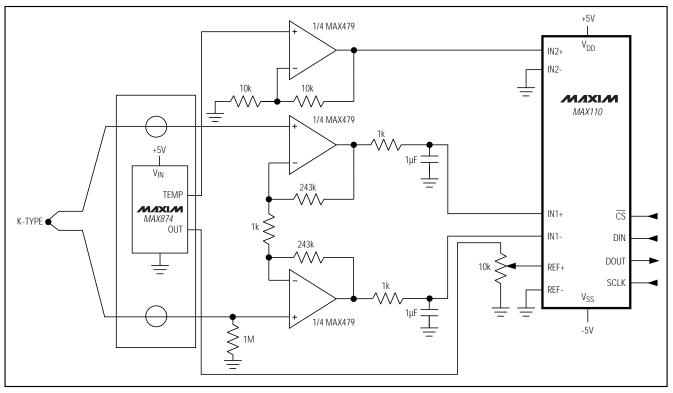

## Typical Operating Circuit

#### **Features**

- Single +5V Supply (MAX111)

- **Two Differential Input Channels**

- 14-Bit Resolution Plus Sign and Overrange

- 0.03% Linearity (MAX110) 0.05% Linearity (MAX111)

- Low Power Consumption: 550µA (MAX110) 640µA (MAX111) 4µA Shutdown Current

- Up to 50 Conversions/sec

- 50Hz/60Hz Rejection

- **Auto-Calibration Mode**

- **No External Components Required**

- 16-Pin DIP/SO, 20-Pin SSOP

## Ordering Information

| PART       | TEMP. RANGE                      | PIN-PACKAGE    | INL(%)     |

|------------|----------------------------------|----------------|------------|

| MAX110ACPE | $0^{\circ}$ C to $+70^{\circ}$ C | 16 Plastic DIP | $\pm 0.03$ |

| MAX110BCPE | 0°C to +70°C                     | 16 Plastic DIP | ±0.05      |

| MAX110ACWE | 0°C to +70°C                     | 16 Wide SO     | ±0.03      |

| MAX110BCWE | 0°C to +70°C                     | 16 Wide SO     | ±0.05      |

| MAX110ACAP | 0°C to +70°C                     | 20 SSOP        | ±0.03      |

| MAX110BCAP | 0°C to +70°C                     | 20 SSOP        | ±0.05      |

| MAX110BC/D | 0°C to +70°C                     | Dice*          | ±0.05      |

|            |                                  |                |            |

Ordering Information continued at end of data sheet.

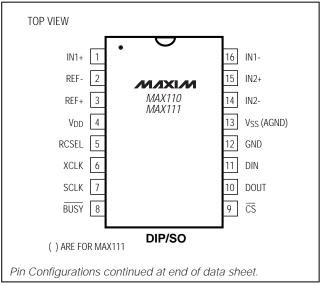

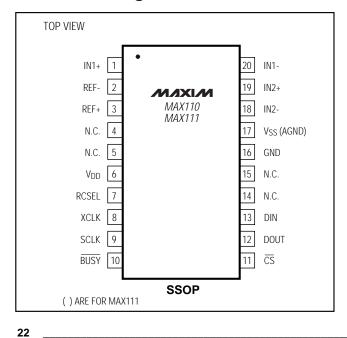

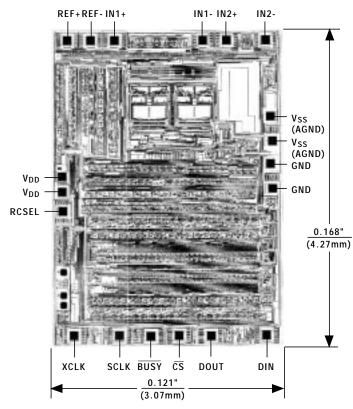

## Pin Configurations

SPI and QSPI are trademarks of Motorola, Inc. MICROWIRE is a trademark of National Semiconductor Corp.

NIXIN

Maxim Integrated Products 1

For free samples & the latest literature: http://www.maxim-ic.com, or phone 1-800-998-8800. For small orders, phone 1-800-835-8769.

<sup>\*</sup> Contact factory for dice specifications.

#### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>DD</sub> to GND                | +6V                                    |

|---------------------------------------|----------------------------------------|

| Vss to GND (MAX110)                   | +0.3V to -6V                           |

| AGND to DGND                          | 0.3V to +0.3V                          |

| V <sub>IN1+</sub> , V <sub>IN1-</sub> | $(V_{DD} + 0.3V)$ to $(V_{SS} - 0.3V)$ |

| VIN2+, VIN2                           | $(V_{DD} + 0.3V)$ to $(V_{SS} - 0.3V)$ |

| V <sub>REF+</sub> , V <sub>REF-</sub> | $(V_{DD} + 0.3V)$ to $(V_{SS} - 0.3V)$ |

| Digital Inputs and Outputs            | $(V_{DD} + 0.3V)$ to -0.3V             |

| Continuous Power Dissipation          |                                        |

| 16-Pin Plastic DIP (derate 10.53m)    | W/°C above +70°C)842mW                 |

| 16-Pin Wide SO (derate 9.52mW/°C above +70°C)762mW |

|----------------------------------------------------|

| 20-Pin SSOP (derate 8.00mW/°C above +70°C)640mW    |

| 16-Pin CERDIP (derate 10.00mW/°C above +70°C)800mW |

| Operating Temperature Ranges                       |

| MAX11C0°C to +70°C                                 |

| MAX11 F40°C to +85°C                               |

| MAX11C                               | 0°C to +70°C   |

|--------------------------------------|----------------|

| MAX11E                               | 40°C to +85°C  |

| MAX11_BMJE                           | 55°C to +125°C |

| Storage Temperature Range            | 65°C to +160°C |

| Lead Temperature (soldering, 10sec). | +300°C         |

|                                      |                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **ELECTRICAL CHARACTERISTICS—MAX110**

$(V_{DD} = 5V \pm 5\%, V_{SS} = -5V \pm 5\%, f_{XCLK} = 1MHz, \div 2 \text{ mode (DV2} = 1), 81,920 \text{ CLK cycles/conv}, V_{REF+} = 1.5V, V_{REF-} = -1.5V, T_{A} = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_{A} = +25^{\circ}\text{C.}$ )

| PARAMETER                             | SYMBOL                                 |                                           | CONDITIONS                                                           | MIN TY                 | P MAX                     | UNITS  |  |

|---------------------------------------|----------------------------------------|-------------------------------------------|----------------------------------------------------------------------|------------------------|---------------------------|--------|--|

| ACCURACY (Note 1)                     | 1                                      | 1                                         |                                                                      |                        |                           | I      |  |

| Resolution                            | RES                                    | (Note 2)                                  |                                                                      | 14 + POL<br>+ OFL      |                           | Bits   |  |

| Differential Nonlinearity             | DNL                                    | (Notes 3, 4)                              |                                                                      |                        | ±2                        | LSB    |  |

| No-Missing-Codes<br>Resolution        |                                        | (Note 3)                                  |                                                                      | 13 + POL<br>+ OFL      |                           | Bits   |  |

|                                       |                                        | MAX110AC/E                                | -VREF ≤ VIN ≤ VREF                                                   | ±0.0                   | 03 ±0.06                  |        |  |

|                                       |                                        | IVIAX I TOAC/L                            | -0.83 x V <sub>REF</sub> ≤ V <sub>IN</sub> ≤ 0.83 x V <sub>REF</sub> | ±0.0                   | 15 ±0.03                  |        |  |

| Relative Accuracy                     | INL                                    | MAX110BC/E                                | -VREF ≤ VIN ≤ VREF                                                   | ±0.0                   | )4                        | %FSR   |  |

| (Notes 3, 5–7)                        | IINL                                   | WAXTTOBC/L                                | -0.83 x V <sub>REF</sub> ≤ V <sub>IN</sub> ≤ 0.83 x V <sub>REF</sub> | ±0.0                   | 18                        | 701 31 |  |

|                                       |                                        | MAX110BM                                  | -V <sub>REF</sub> ≤ V <sub>IN</sub> ≤ V <sub>REF</sub>               |                        | ±0.1                      |        |  |

|                                       |                                        | IVIAXTIODIVI                              | -0.83 x V <sub>REF</sub> ≤ V <sub>IN</sub> ≤ 0.83 x V <sub>REF</sub> |                        | ±0.05                     |        |  |

| Offset Error                          |                                        | $V_{IN+} = V_{IN-} = 0V$                  |                                                                      |                        | ±4                        | mV     |  |

| Offset Error                          |                                        | After offset null                         |                                                                      | 0.003                  |                           | μV/°C  |  |

| Temperature Drift                     |                                        | Uncalibrated                              |                                                                      | 0.0                    | 2                         | μν/ Ο  |  |

| Common-Mode Rejection Ratio           | CMRR                                   | $-2.5V \le (V_{IN+} = V_{I}$              | $N_{-}$ ) $\leq 2.5V$                                                | 6                      |                           | ppm/V  |  |

| Full-Scale Error                      |                                        | After gain calibration (Note 5)           |                                                                      |                        | ±0.1                      | - %    |  |

| ruii-scale Elloi                      |                                        | Uncalibrated                              |                                                                      | -8                     | 0                         | 70     |  |

| Full-Scale Error<br>Temperature Drift |                                        |                                           |                                                                      | 8                      |                           | ppm/°C |  |

| Dowar Cumply Dalaction                |                                        | Vss = -5V, Vpp =                          | 4.75V to 5.25V                                                       | 15                     |                           | nnm    |  |

| Power-Supply Rejection                |                                        | V <sub>DD</sub> = 5V, V <sub>SS</sub> = - | 30                                                                   | ppm                    |                           |        |  |

| ANALOG INPUTS                         | <u>'</u>                               |                                           |                                                                      | •                      |                           | •      |  |

| Differential Input Voltage<br>Range   | VIN                                    | (Note 6)                                  |                                                                      | -VREF                  | +VREF                     | V      |  |

| Absolute Input Voltage<br>Range       | V <sub>IN+</sub> ,<br>V <sub>IN-</sub> |                                           |                                                                      | V <sub>SS</sub> + 2.25 | V <sub>DD</sub> -<br>2.25 | V      |  |

| Input Bias Current                    | I <sub>IN+</sub> , I <sub>IN-</sub>    |                                           |                                                                      |                        | 500                       | nA     |  |

| Input Capacitance                     |                                        | (Note 3)                                  |                                                                      |                        | 10                        | pF     |  |

## **ELECTRICAL CHARACTERISTICS—MAX110 (continued)**

$(V_{DD} = 5V \pm 5\%, V_{SS} = -5V \pm 5\%, f_{XCLK} = 1MHz, \div 2 \text{ mode (DV2} = 1), 81,920 \text{ CLK cycles/conv}, V_{REF+} = 1.5V, V_{REF-} = -1.5V, T_{A} = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_{A} = +25^{\circ}\text{C.}$ )

| PARAMETER                                     | SYMBOL                                   |                                        | MIN                                                                                 | TYP                    | MAX             | UNITS                  |      |

|-----------------------------------------------|------------------------------------------|----------------------------------------|-------------------------------------------------------------------------------------|------------------------|-----------------|------------------------|------|

| REFERENCE INPUTS                              |                                          |                                        |                                                                                     |                        |                 |                        | '    |

| Differential Reference<br>Input Voltage Range | VREF                                     |                                        | 0                                                                                   |                        | 3.0             | V                      |      |

| Absolute Reference Input<br>Voltage Range     | V <sub>REF+</sub> ,<br>V <sub>REF-</sub> |                                        |                                                                                     | V <sub>SS</sub> + 2.25 |                 | V <sub>DD</sub> - 2.25 | V    |

| Reference Input Current                       | I <sub>REF+</sub> ,<br>I <sub>REF-</sub> | $V_{REF+} = 2.5V, V_{RE}$              | OV                                                                                  |                        |                 | 500                    | nA   |

| Reference Input<br>Capacitance                |                                          | (Note 3)                               |                                                                                     |                        |                 | 10                     | pF   |

| CONVERSION TIME                               |                                          |                                        |                                                                                     |                        |                 |                        | '    |

| Synchronous Conversion<br>Time (Note 7)       | tCONV                                    | 10,240 clock-cycl<br>102,400 clock-cyc |                                                                                     |                        | 20.48<br>204.80 |                        | ms   |

| Oversampling Clock<br>Frequency               | fosc                                     | (Note 8)                               |                                                                                     | 0.25                   |                 | 1.25                   | MHz  |

| DIGITAL INPUTS (CS, SCI                       | LK, DIN, and                             | XCLK when RCSE                         | L = 0V)                                                                             |                        |                 |                        |      |

| Input High Voltage                            | VIH                                      |                                        |                                                                                     | 2.4                    |                 |                        | V    |

| Input Low Voltage                             | VIL                                      |                                        |                                                                                     |                        |                 | 0.8                    | V    |

| Input Capacitance                             |                                          | (Note 3)                               |                                                                                     |                        |                 | 10                     | pF   |

| Input Leakage Current                         | ILKG                                     | Digital inputs at 0'                   |                                                                                     |                        | ±1              | μA                     |      |

| DIGITAL OUTPUTS (DOU                          | T, BUSY, an                              | d XCLK when RCSI                       | EL = V <sub>DD</sub> )                                                              | I                      |                 |                        |      |

|                                               |                                          | DOUT, BUSY, ISINK = 1.6mA              |                                                                                     |                        |                 | 0.4                    | 1    |

| Output Low Voltage                            | VOL                                      | XCLK, ISINK = 200                      | )μA                                                                                 |                        |                 | 0.4                    | - V  |

| Output High Voltage                           | Voh                                      | DOUT, BUSY, V <sub>DI</sub>            | D = 4.75V, I <sub>SOURCE</sub> = 1.0mA                                              | V <sub>DD</sub> - 0.   |                 |                        | V    |

|                                               |                                          |                                        | 5V, I <sub>SOURCE</sub> = 200μA                                                     | V <sub>DD</sub> - 0.   | 5               |                        |      |

| Leakage Current                               | I <sub>LKG</sub>                         | $V_{OUT} = 5V \text{ or } 0V$          |                                                                                     |                        |                 | ±10                    | μΑ   |

| Output Capacitance                            |                                          | (Note 3)                               |                                                                                     |                        |                 | 10                     | pF   |

| POWER REQUIREMENTS                            | (all digital i                           | nputs at 0V or 5V)                     |                                                                                     |                        |                 |                        |      |

| Positive Supply Voltage                       | V <sub>DD</sub>                          | Performance guar                       | ranteed by supply rejection test                                                    | 4.75                   |                 | 5.25                   | V    |

| Negative Supply Voltage                       | Vss                                      | Performance guar                       | ranteed by supply rejection test                                                    | -4.75                  |                 | -5.25                  | V    |

|                                               |                                          | V <sub>DD</sub> = 5.25V,               | f <sub>XCLK</sub> = 500kHz,<br>continuous-conversion mode                           |                        | 550             | 950                    |      |

| Positive Supply Current                       | IDD                                      | V <sub>SS</sub> = -5.25V               | XCLK unloaded,<br>continuous-conversion mode, RC<br>oscillator operational (Note 9) |                        | 780             |                        | μΑ   |

| Negative Supply Current                       | Iss                                      | $V_{DD} = 5.25V,$<br>$V_{SS} = -5.25V$ | f <sub>XCLK</sub> = 500kHz,<br>continuous-conversion mode                           |                        | 320             | 650                    | μА   |

| Power-Down Current                            | I <sub>DD</sub>                          | Vpp = 5.25V, Vcc                       | = -5.25V, V <sub>XCLK</sub> = 0V, PD = 1                                            |                        | 4               | 10                     | μΑ   |

| I OWEI-DOWII CUITEIIL                         | Iss                                      | VDD - 5.25V, VSS                       | 0.20V, VXCLK - UV, PD = 1                                                           |                        | 0.05            | 2                      | _ μA |

#### **ELECTRICAL CHARACTERISTICS—MAX111**

$(V_{DD} = 5V \pm 5\%, f_{XCLK} = 1MHz, \pm 2 \text{ mode (DV2} = 1), 81,920 \text{ CLK cycles/conv}, V_{REF+} = 1.5V, V_{REF-} = 0V, T_A = T_{MIN} \text{ to } T_{MAX, unless otherwise noted.}$  Typical values are at  $T_A = +25^{\circ}C$ .)

| PARAMETER                             | SYMBOL                              |                                       | MIN                                                                    | TYP               | MAX   | UNITS                 |           |  |  |

|---------------------------------------|-------------------------------------|---------------------------------------|------------------------------------------------------------------------|-------------------|-------|-----------------------|-----------|--|--|

| ACCURACY (Note 1)                     |                                     |                                       |                                                                        |                   |       |                       |           |  |  |

| Resolution                            | RES                                 | (Note 2)                              | (Note 2)                                                               |                   | L     |                       | Bits      |  |  |

| Differential Nonlinearity             | DNL                                 | (Notes 3, 4)                          |                                                                        |                   |       | ±2                    | LSB       |  |  |

| No-Missing-Codes<br>Resolution        |                                     | (Note 3)                              |                                                                        | 13 + PO<br>+ OFL  | L     |                       | Bits      |  |  |

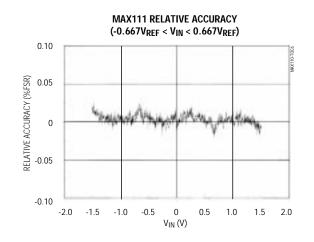

|                                       |                                     | MAX111AC/E                            | -V <sub>REF</sub> ≤ V <sub>IN</sub> ≤ V <sub>REF</sub>                 |                   | ±0.05 | ±0.10                 |           |  |  |

|                                       |                                     | IVIAXTITAC/E                          | -0.667 x V <sub>REF</sub> ≤ V <sub>IN</sub> ≤ 0.667 x V <sub>REF</sub> |                   | ±0.03 | ±0.05                 |           |  |  |

| Relative Accuracy, Differential Input | INL                                 | MAX111BC/E                            | -V <sub>REF</sub> ≤ V <sub>IN</sub> ≤ V <sub>REF</sub>                 |                   |       | ±0.18                 | %FSR      |  |  |

| (Notes 3, 5–7)                        | IIVL                                | WAXTITIDO/L                           | -0.667 x VREF ≤ VIN ≤ 0.667 x VREF                                     |                   |       | ±0.10                 | 701 310   |  |  |

|                                       |                                     | MAX111BM                              | -VREF ≤ VIN ≤ VREF                                                     |                   |       | ±0.25                 |           |  |  |

|                                       |                                     | IVIAATTIDIVI                          | -0.667 x V <sub>REF</sub> ≤ V <sub>IN</sub> ≤ 0.667 x V <sub>REF</sub> |                   |       | ±0.20                 |           |  |  |

|                                       |                                     | MAV111AC/E                            | 0V ≤ V <sub>IN</sub> ≤ V <sub>REF</sub>                                |                   | ±0.1  |                       |           |  |  |

|                                       |                                     | MAX111AC/E                            | V <sub>IN</sub> ≤ 0.667 x V <sub>REF</sub>                             |                   | ±0.06 |                       | 1         |  |  |

| Relative Accuracy,                    | INL                                 | MAX111BC/E                            | 0V ≤ V <sub>IN</sub> ≤ V <sub>REF</sub>                                |                   | ±0.18 |                       | -<br>%FSR |  |  |

| Single-Ended Input (IN- = GND)        | IINL                                |                                       | V <sub>IN</sub> ≤ 0.667 x V <sub>REF</sub>                             |                   | ±0.10 |                       | 4 %FSK    |  |  |

| (IIV GIVE)                            |                                     | MAX111BM                              | 0V ≤ V <sub>IN</sub> ≤ V <sub>REF</sub>                                |                   | ±0.25 |                       | 1         |  |  |

|                                       |                                     | IVIAXTITBIVI                          | V <sub>IN</sub> ≤ 0.667 x V <sub>REF</sub>                             |                   | ±0.15 |                       | 1         |  |  |

| Offset Error                          |                                     | $V_{IN+} = V_{IN-} = 0V$              |                                                                        |                   |       | ±4                    | mV        |  |  |

| Common-Mode Rejection<br>Ratio        | CMRR                                | $10\text{mV} \le (V_{\text{IN}+} = V$ | <sub>IN-</sub> ) ≤ 2.0V                                                |                   | 6     |                       | ppm/V     |  |  |

| Full Cools Fran                       |                                     | After gain calibration (Note 5)       |                                                                        |                   |       | ±0.2                  | %         |  |  |

| Full-Scale Error                      |                                     | Uncalibrated                          |                                                                        | -8                |       | 0                     | 7%        |  |  |

| Full-Scale Error<br>Temperature Drift |                                     |                                       |                                                                        |                   | 8     |                       | ppm/°C    |  |  |

| Power-Supply Rejection                |                                     | $V_{DD} = 4.75V \text{ to 5}.$        | 25V                                                                    |                   | 15    |                       | ppm       |  |  |

| ANALOG INPUTS                         | 1                                   | <u>I</u>                              |                                                                        | I                 |       |                       | 1         |  |  |

| Differential Input Voltage<br>Range   | VIN                                 | (Note 6)                              |                                                                        | -V <sub>REF</sub> |       | +V <sub>REF</sub>     | V         |  |  |

| Absolute Input Voltage<br>Range       | VIN+,<br>VIN-                       |                                       |                                                                        | 0                 |       | V <sub>DD</sub> - 3.2 | V         |  |  |

| Input Bias Current                    | I <sub>IN+</sub> , I <sub>IN-</sub> |                                       |                                                                        |                   |       | 500                   | nA        |  |  |

| Input Capacitance                     |                                     | (Note 3)                              |                                                                        |                   |       | 10                    | pF        |  |  |

## **ELECTRICAL CHARACTERISTICS—MAX111 (continued)**

$(V_{DD} = 5V \pm 5\%, f_{XCLK} = 1 MHz, \pm 2 \text{ mode } (DV2 = 1), 81,920 \text{ CLK cycles/conv}, V_{REF+} = 1.5V, V_{REF-} = 0V, T_A = T_{MIN} \text{ to } T_{MAX}, unless \text{ otherwise noted.}$  Typical values are at  $T_A = +25^{\circ}\text{C}$ .)

| PARAMETER                                     | SYMBOL                                   |                                                                  | CONDITIONS                                                                          | MIN                   | TYP    | MAX                   | UNITS |

|-----------------------------------------------|------------------------------------------|------------------------------------------------------------------|-------------------------------------------------------------------------------------|-----------------------|--------|-----------------------|-------|

| REFERENCE INPUTS                              |                                          |                                                                  |                                                                                     |                       |        |                       | •     |

| Differential Reference<br>Input Voltage Range | V <sub>REF</sub>                         |                                                                  |                                                                                     |                       |        |                       | V     |

| Absolute Reference Input<br>Voltage Range     | V <sub>REF+</sub> ,<br>V <sub>REF-</sub> |                                                                  |                                                                                     | 0                     |        | V <sub>DD</sub> - 3.2 | V     |

| Reference Input Current                       | I <sub>REF+</sub> ,<br>I <sub>REF-</sub> | $V_{REF+} = 1.5V, V_{RE}$                                        | EF- = 0V                                                                            |                       |        | 500                   | nA    |

| Reference Input<br>Capacitance                |                                          | (Note 3)                                                         |                                                                                     |                       |        | 10                    | рF    |

| CONVERSION TIME                               |                                          |                                                                  |                                                                                     |                       |        |                       |       |

| Synchronous Conversion                        | tCONV                                    | 10,240 clock-cycle                                               | es/conversion                                                                       |                       | 20.48  |                       | ms    |

| Time (Note 7)                                 | ICONV                                    | 102,400 clock-cyc                                                | cles/conversion                                                                     |                       | 204.80 | )                     | – ms  |

| Oversampling Clock<br>Frequency               | fosc                                     | (Note 8)                                                         |                                                                                     | 0.25                  |        | 1.25                  | MHz   |

| DIGITAL INPUTS (CS, SCL                       | K, DIN, and                              | XCLK when RCSE                                                   | L = 0V)                                                                             | •                     |        |                       |       |

| Input High Voltage                            | VIH                                      |                                                                  |                                                                                     | 2.4                   |        |                       | V     |

| Input Low Voltage                             | VIL                                      |                                                                  |                                                                                     |                       |        | 0.8                   | V     |

| Input Capacitance                             |                                          | (Note 3)                                                         |                                                                                     |                       |        | 10                    | pF    |

| Input Leakage Current                         | I <sub>LKG</sub>                         | Digital inputs at 0\                                             |                                                                                     |                       |        | ±1                    | μΑ    |

| DIGITAL OUTPUTS (DOU                          | Γ, <del>BUSY</del> , an                  | d XCLK when RCSE                                                 | $EL = V_{DD}$ )                                                                     |                       |        |                       |       |

| Output Low Voltage                            | VoL                                      | DOUT, BUSY, I <sub>SINK</sub> = 1.6mA                            |                                                                                     |                       |        | 0.4                   | V     |

|                                               | -01                                      | XCLK, I <sub>SINK</sub> = 200                                    |                                                                                     |                       | 0.4    | •                     |       |

| Output High Voltage                           | VoH                                      | DOUT, BUSY, V <sub>DD</sub> = 4.75V, I <sub>SOURCE</sub> = 1.0mA |                                                                                     | V <sub>DD</sub> - 0.5 |        |                       | V     |

|                                               |                                          | $XCLK$ , $V_{DD} = 4.75$                                         | V <sub>DD</sub> - 0.5                                                               | 5                     |        |                       |       |

| Leakage Current                               | I <sub>LK</sub> G                        | V <sub>OUT</sub> = 5V or 0V                                      |                                                                                     |                       |        | ±1                    | μΑ    |

| Output Capacitance                            |                                          | (Note 3)                                                         |                                                                                     |                       |        | 10                    | pF    |

| POWER REQUIREMENTS                            | (all digital i                           |                                                                  |                                                                                     |                       |        |                       |       |

| Positive Supply Voltage                       | V <sub>DD</sub>                          | Performance guar                                                 | anteed by supply rejection test                                                     | 4.75                  |        | 5.25                  | V     |

| Supply Current                                | les                                      | V <sub>DD</sub> = 5.25V                                          | f <sub>XCLK</sub> = 500kHz,<br>continuous-conversion mode                           |                       | 640    | 1200                  | ^     |

| Supply Current                                | I <sub>DD</sub>                          | ν <sub>DD</sub> = 3.25V                                          | XCLK unloaded,<br>continuous-conversion mode, RC<br>oscillator operational (Note 9) | 960                   |        |                       | μΑ    |

| Power-Down Current                            | I <sub>DD</sub>                          | $V_{DD} = 5.25V, V_{XC}$                                         | LK = 0V, $PD = 1$                                                                   |                       | 4      | 10                    | μΑ    |

- **Note 1:** These specifications apply after auto-null and gain calibration. Performance at power-supply tolerance limits is guaranteed by power-supply rejection tests. Tests are performed at V<sub>DD</sub> = 5V and V<sub>SS</sub> = -5V (MAX110).

- **Note 2:** 32,768 LSBs cover an input voltage range of  $\pm V_{REF}$  (15 bits). An additional bit (OFL) is set for  $V_{IN} > V_{REF}$ .

- Note 3: Guaranteed by design. Not subject to production testing.

- **Note 4:** DNL is less than  $\pm 2$  counts (LSBs) out of  $2^{15}$  counts ( $\pm 14$  bits). The major source of DNL is noise, and this can be further improved by averaging.

- Note 5: See 3-Step Calibration section in text.

- Note 6: V<sub>REF</sub> = (V<sub>REF+</sub> V<sub>REF-</sub>), V<sub>IN</sub> = (V<sub>IN1+</sub> V<sub>IN1-</sub>) or (V<sub>IN2+</sub> V<sub>IN2-</sub>). The voltage is interpreted as negative when the voltage at the negative input terminal exceeds the voltage at the positive input terminal.

- Note 7: Conversion time is set by control bits CONV1–CONV4.

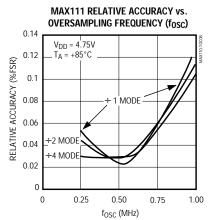

- **Note 8:** Tested at clock frequency of 1MHz with the divide-by-2 mode (i.e. oversampling clock of 500kHz). See *Typical Operating Characteristics* section for the effect of other clock frequencies. Also read the *Clock Frequency* section.

- Note 9: This current depends strongly on CXCLK (see Applications Information section).

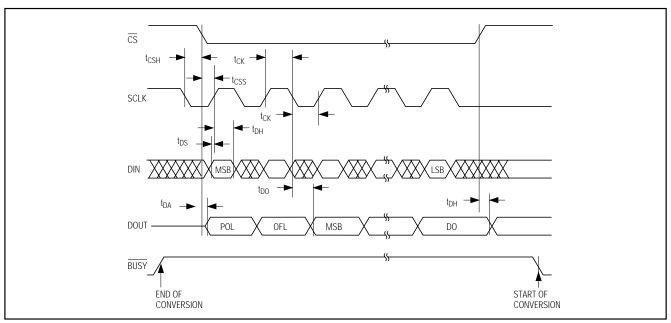

#### **TIMING CHARACTERISTICS** (see Figure 6)

$(V_{DD} = 5V, V_{SS} = -5V \text{ (MAX110)}, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted. Typical values are at } T_A = +25^{\circ}\text{C.})$

| PARAMETER                               | SYMBOL          | C                        | MIN                    | TYP | MAX | UNITS |     |  |

|-----------------------------------------|-----------------|--------------------------|------------------------|-----|-----|-------|-----|--|

| <u> </u>                                |                 | $T_A = +25^{\circ}C$     |                        | 60  |     |       |     |  |

| CS to SCLK Setup Time (Note 10)         | tcss            | MAX11C/E                 |                        | 80  |     |       | ns  |  |

| (14010-10)                              |                 | MAX11_ BM                |                        | 100 |     |       |     |  |

| CS to SCLK Hold Time (Note 10)          | tcsh            |                          |                        | 0   |     |       | ns  |  |

| DIN L COLV.C. L. T'                     |                 | $T_A = +25^{\circ}C$     |                        | 60  |     |       |     |  |

| DIN to SCLK Setup Time (Note 10)        | t <sub>DS</sub> | MAX11C/E                 |                        | 80  |     |       | ns  |  |

| (14010-10)                              |                 | MAX11_ BM                |                        | 100 |     |       |     |  |

| DIN to SCLK Hold Time<br>(Note 10)      | tDH             |                          |                        | 0   |     |       | ns  |  |

|                                         | tCK             | $T_A = +25^{\circ}C$     |                        | 100 |     |       |     |  |

| SCLK, XCLK Pulse Width (Note 10)        |                 | MAX11C/E                 |                        |     |     |       | ns  |  |

| (Note 10)                               |                 | MAX11_ BM                |                        | 160 |     |       |     |  |

| D-t- A Tim-                             |                 | C <sub>LOAD</sub> = 50pF | T <sub>A</sub> = +25°C | 0   | 35  | 80    |     |  |

| Data Access Time<br>(Note 10)           | t <sub>DA</sub> |                          | MAX11C/E               | 0   |     | 100   | ns  |  |

| (************************************** |                 |                          | MAX11_ BM              | 0   |     | 120   |     |  |

| SCLK to DOUT Valid                      |                 |                          | $T_A = +25^{\circ}C$   | 0   | 60  | 100   |     |  |

| Delay (Note 10)                         | t <sub>DO</sub> | $C_{LOAD} = 50pF$        | MAX11C/E               | 0   |     | 120   | ns  |  |

|                                         |                 |                          | MAX11_ BM              | 0   |     | 140   |     |  |

| Bus Relinquish Time                     | tDH             | $T_A = +25^{\circ}C$     |                        |     | 35  | 80    | ns  |  |

| (Note 10)                               | וטו             | MAX11C/E/M               |                        |     |     | 120   | 113 |  |

| ·                                       |                 | $T_A = +25^{\circ}C$     | <u> </u>               |     | 2.0 |       |     |  |

| RC Oscillator Frequency                 |                 | MAX11C/E                 |                        |     |     | 2.8   | MHz |  |

|                                         |                 | MAX11_ BM                |                        | 1.1 |     | 3.0   |     |  |

**Note 10:** Timing specifications are guaranteed by design. All input control signals are specified with  $t_f = t_f = 5$ ns (10% to 90% of +5V) and timed from a +1.6V voltage level.

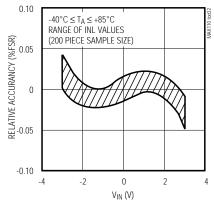

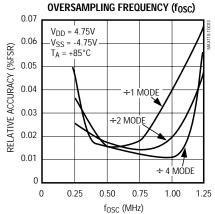

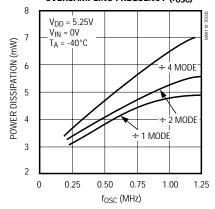

## Typical Operating Characteristics

(MAX110,  $V_{DD}$  = 5V,  $V_{SS}$  = -5V,  $V_{REF+}$  = 1.5V,  $V_{REF-}$  = -1.5V, differential input ( $V_{IN+}$  = - $V_{IN-}$ ),  $f_{XCLK}$  = 1MHz,  $\div$  2 mode (DV2 = 1), 81,920 clocks/conv,  $T_{A}$  = +25°C, unless otherwise noted.)

# MAX110 RELATIVE ACCURACY (-0.83 V<sub>REF</sub>)

## MAX110 RELATIVE ACCURACY (-Vpff < Vin < Vpff)

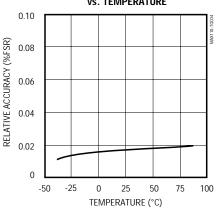

## MAX110 RELATIVE ACCURACY vs.

## MAX110 RELATIVE ACCURACY vs. TEMPERATURE

# MAX110 POWER DISSIPATION vs. OVERSAMPLING FREQUENCY (fosc)

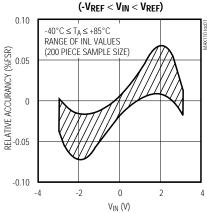

## \_Typical Operating Characteristics (continued)

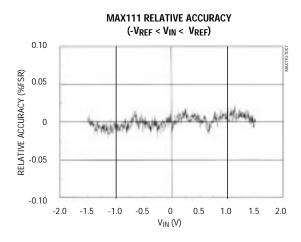

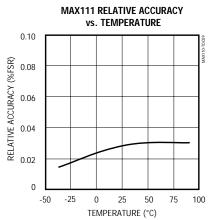

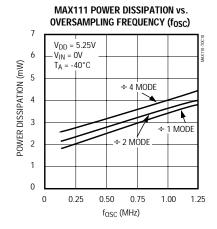

(MAX111,  $V_{DD}$  = 5V,  $V_{REF+}$  = 1.5V,  $V_{REF-}$  = 0V, differential input ( $\overline{V}_{IN+}$  = - $V_{IN-}$ ),  $f_{XCLK}$  = 1MHz,  $\div$  2 mode (DV2 = 1), 81,920 clocks/conv,  $T_A$  = +25°C, unless otherwise noted.)

## Pin Description

| PIN    |              | NAME            | FUNCTION                                                                                                                                                                                                                                                                                      |  |  |  |  |

|--------|--------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| DIP/SO |              |                 | FUNCTION                                                                                                                                                                                                                                                                                      |  |  |  |  |

| 1      | 1            | IN1+            | Channel 1 Positive Analog Input                                                                                                                                                                                                                                                               |  |  |  |  |

| 2      | 2            | REF-            | Negative Reference Input                                                                                                                                                                                                                                                                      |  |  |  |  |

| 3      | 3            | REF+            | Positive Reference Input                                                                                                                                                                                                                                                                      |  |  |  |  |

| 4      | 6            | V <sub>DD</sub> | Positive Power-Supply Input—connect to +5V                                                                                                                                                                                                                                                    |  |  |  |  |

| 5      | 7            | RCSEL           | RC Select Input. Connect to GND to select external clock mode. Connect to $V_{DD}$ to select RC OSC mode. XCLK must be connected to $V_{DD}$ or GND through a resistor (1M $\Omega$ or less) when RC OSC mode is selected.                                                                    |  |  |  |  |

| 6      | 8            | XCLK            | Clock Input / RC Oscillator Output. TTL/CMOS-compatible oversampling clock input when RCSEL = GND. Connects to the internal RC oscillator when RCSEL = $V_{DD}$ . XCLK must be connected to $V_{DD}$ or GND through a resistor (1M $\Omega$ or less) when RC OSC mode is selected.            |  |  |  |  |

| 7      | 9            | SCLK            | Serial Clock Input. TTL/CMOS-compatible clock input for serial-interface data I/O.                                                                                                                                                                                                            |  |  |  |  |

| 8      | 10           | BUSY            | Busy Output. Goes low at conversion start, and returns high at end of conversion.                                                                                                                                                                                                             |  |  |  |  |

| 9      | 11           | CS              | Chip-Select Input. Pull this input low to perform a control-word-write/data-read operation. A conversion begins when $\overline{\text{CS}}$ returns high, provided $\overline{\text{NO-OP}}$ is a 1. See the section Using the MAX110/MAX111 with SPI, QSPI, and MICROWIRE Serial Interfaces. |  |  |  |  |

| 10     | 12           | DOUT            | Serial Data Output. High-impedance when CS is high.                                                                                                                                                                                                                                           |  |  |  |  |

| 11     | 13           | DIN             | Serial Data Input. See Control Register section.                                                                                                                                                                                                                                              |  |  |  |  |

| 12     | 16           | GND             | Digital Ground                                                                                                                                                                                                                                                                                |  |  |  |  |

| 13     | 17           | V <sub>SS</sub> | MAX110 Negative Power-Supply Input—connect to -5V                                                                                                                                                                                                                                             |  |  |  |  |

| 13     | 17           | AGND            | MAX111 Analog Ground                                                                                                                                                                                                                                                                          |  |  |  |  |

| 14     | 18           | IN2-            | Channel 2 Negative Analog Input                                                                                                                                                                                                                                                               |  |  |  |  |

| 15     | 19           | IN2+            | Channel 2 Positive Analog Input                                                                                                                                                                                                                                                               |  |  |  |  |

| 16     | 20           | IN1-            | Channel 1 Negative Analog Input                                                                                                                                                                                                                                                               |  |  |  |  |

| _      | 4, 5, 14, 15 | N.C.            | No Connect—there is no internal connection to this pin                                                                                                                                                                                                                                        |  |  |  |  |

## Detailed Description

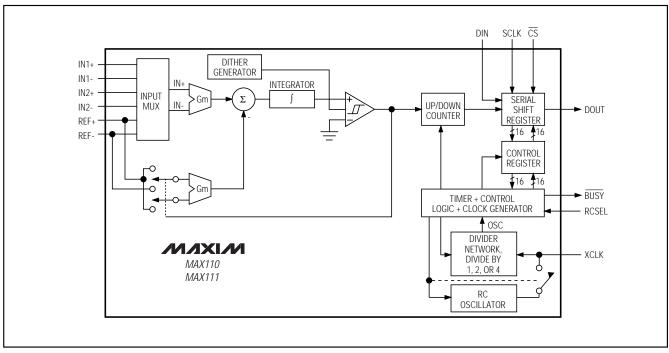

The MAX110/MAX111 ADC converts low-frequency analog signals to a 16-bit serial digital output (14 data bits, a sign bit, and an overrange bit) using a first-order sigma-delta loop (Figure 1). The differential input voltage is internally connected to a precision voltage-to-current converter. The resulting current is integrated and applied to a comparator. The comparator output then drives an up/down counter and a 1-bit DAC. When the DAC output is fed back to the integrator input, the sigma-delta loop is completed.

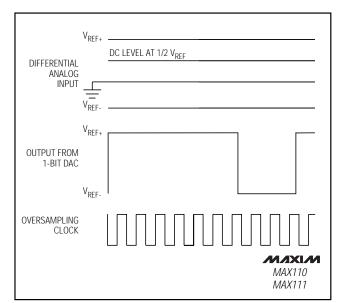

During a conversion, the comparator output is a  $V_{REF}$  to  $V_{REF}$  square wave; its duty cycle is proportional to the magnitude of the differential input voltage applied

to the ADC. The up/down counter clocks data in from the comparator at the oversampling clock rate and averages the pulse-width-modulated (PWM) square wave to produce the conversion result. A 16-bit static shift register stores the result at the end of the conversion. Figure 2 shows the ADC waveforms for a differential analog input equal to 1/2 (VREF+ - VREF-). The resulting comparator and 1-bit DAC outputs are high for seven cycles and low for three cycles of the oversampling clock.

Since the analog input signal is integrated over many clock cycles, much of the signal and quantization noise is attenuated. The more clock cycles allowed during each conversion, the greater the noise attenuation (see *Programming Conversion Time*).

Figure 1. Functional Diagram

#### **Oversampling Clock**

XCLK internally connects to a clock-frequency divider network, whose output is the ADC oversampling clock, fosc. This allows the selected clock source (internal RC oscillator or external clock applied to XCLK) to be divided by one, two, or four (see *Clock Divider-Ratio Control Bits*).

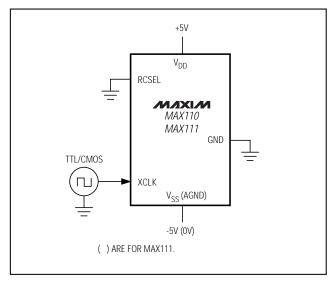

Figure 3 shows the two methods for providing the oversampling clock to the MAX110/MAX111. In externalclock mode (Figure 3a), the internal RC oscillator is disabled and XCLK accepts a TTL/CMOS-level clock to provide the oversampling clock to the ADC.

Select external-clock mode (Figure 3a) by connecting RCSEL to GND and a TTL/CMOS-compatible clock to XCLK (see *Selecting the Oversampling Clock Frequency*).

In RC-oscillator mode (Figure 3b), the internal RC oscillator is active and its output is connected to XCLK (Figure 1). Select RC-oscillator mode by connecting RCSEL to VDD. This enables the internal oscillator and connects it to XCLK for use by the ADC and external system components. Minimize the capacitive loading on XCLK when using the internal RC oscillator.

Figure 2. ADC Waveforms During a Conversion

10 \_\_\_\_\_\_\_ // // XI/VI

Figure 3a. Connection for External-Clock Mode

# $V_{DD}$ RCSEL MAX110 MAX111 GND XCLK $V_{SS}$ (AGND) -5V (0V) ( ) ARE FOR MAX111.

Figure 3b. Connection for Internal RC-Oscillator Mode—XCLK connects to the internal RC oscillator. Note, the pull-up resistor is not necessary if the internal oscillator is never shut down.

#### **ADC Operation**

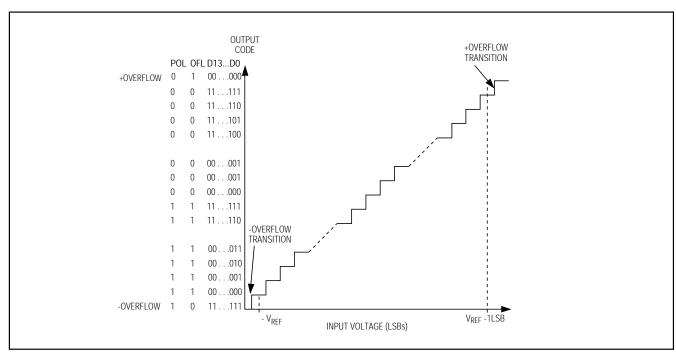

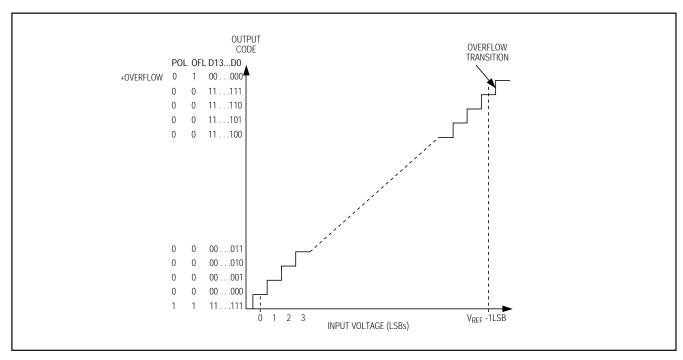

The output data from the MAX110/MAX111 is arranged in twos-complement format (Figures 4, 5). The sign bit (POL) is shifted out first, followed by the overrange bit (OR), and the 14 data bits (MSB first) (see Figure 6). The MAX110 operates from  $\pm 5V$  power supplies and converts low-frequency analog signals in the  $\pm 3V$  range when using the maximum reference voltage of  $V_{REF} = 3V$  ( $V_{REF} = V_{REF+} - V_{REF-}$ ). Within the  $\pm 3V$  input range, greater accuracy is obtained within  $\pm 2.5V$  (see *Electrical Characteristics* for details). Note that a negative input voltage is defined as  $V_{IN-} > V_{IN+}$ . For the MAX110, the absolute voltage at any analog input pin must remain within the ( $V_{SS} + 2.25V$ ) to ( $V_{DD} - 2.25V$ ) range.

The MAX111 operates from a single +5V supply and converts low-frequency differential analog signals in the  $\pm 1.5$ V range when using the maximum reference voltage of V<sub>REF</sub> = 1.5V. As indicated in the *Electrical Characteristics*, greater accuracy is achieved within the  $\pm 1.2$ V range. The absolute voltage at any analog input pin for the MAX111 must remain within 0V to V<sub>DD</sub> - 3.2V. When V<sub>IN-</sub> > V<sub>IN+</sub> the input is interpreted as negative.

The overrange bit (OFL) is provided to sense when the input voltage level has exceeded the reference voltage level. The converter does not "saturate" until the input voltage is typically 20% larger. The linearity is not guaranteed in this range. Note that the overrange bit works

properly if the reference voltage remains within the recommended voltage range (see *Reference Inputs*). If the reference voltage exceeds the recommended input range, the overrange bit may not operate properly.

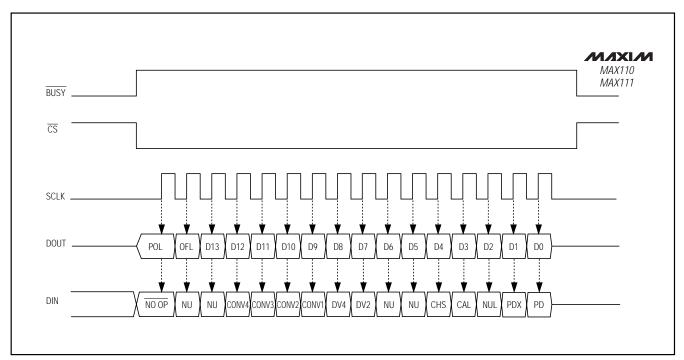

#### Digital Interface—Starting a Conversion

Data is transferred into and out of the serial I/O shift register by pulling  $\overline{\text{CS}}$  low and applying a serial clock at SCLK. This fully static shift register allows SCLK to range from DC to 2MHz. Output data from the ADC is clocked out on SCLK's falling edge and should be read on SCLK's rising edge. Input data to the ADC at DIN is clocked in on SCLK's rising edge. A new conversion begins when  $\overline{\text{CS}}$  returns high, provided the MSB in the input control word  $\overline{\text{(NO-OP)}}$  is a 1 (see *Using the MAX110/MAX111 with MICROWIRE, SPI, and QSPI Serial Interfaces*). Figure 6 shows the detailed serial-interface timing diagram.

CS must remain high during the conversion (while BUSY remains low). Bringing CS low during the conversion causes the ADC to stop converting, and may result in erroneous output data.

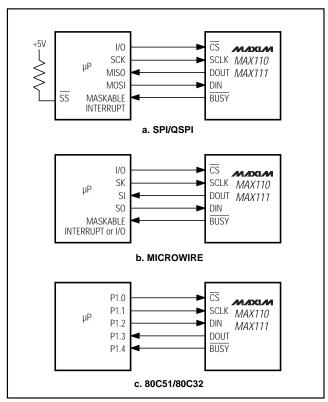

# Using the MAX110/MAX111 with SPI, QSPI, and MICROWIRE Serial Interfaces

Figure 7 shows the most common serial-interface connections. The MAX110/MAX111 are compatible with SPI, QSPI (CPHA = 0, CPOL = 0), and MICROWIRE serial-interface standards.

Figure 4. Differential Transfer Function

Figure 5. Unipolar Transfer Function

Figure 6. Detailed Serial-Interface Timing

Figure 7. Common Serial-Interface Connections

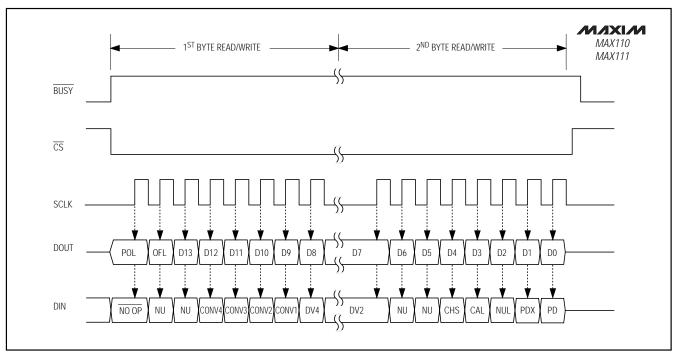

The ADC serial interface operates with just SCLK, DIN, and DOUT (allow sufficient time for the conversion to complete between read/write operations). Achieve continuous operation by connecting  $\overline{\text{BUSY}}$  to an uncommitted  $\mu\text{P}$  I/O or interrupt, to signal the processor when the conversion results are ready. Figures 8a and 8b show the timing for SPI/MICROWIRE and QSPI operation.

The fully static 16-bit I/O register allows infinite time between the two 8-bit read/write operations necessary to obtain the full 16 bits of data with SPI and MICROWIRE.  $\overline{\text{CS}}$  must remain low during the entire two-byte transfer (Figure 8a). QSPI allows a full 16-bit data transfer (Figure 8b).

Interfacing to the 80C32 Microcontroller Family Figure 7c shows the general 80C32 connection to the MAX110/MAX111 using Port 1. For a more detailed discussion, see the MAX110 evaluation kit manual.

#### I/O Shift Register

Serial data transfer is accomplished with a 16-bit fully static shift register. The 16-bit control word shifted into this register during a data-transfer operation controls the ADC's various functions. The MSB (NO-OP) enables/disables transfer of the control word within the ADC. A logic 1 causes the remaining 15 bits in the control word to be transferred from the I/O register into the control register when  $\overline{CS}$  goes high, updating the ADC's configuration and starting a new conversion. If

Figure 8a. SPI/MICROWIRE-Interface Timing

Figure 8b. QSPI Serial-Interface Timing

14 \_\_\_\_\_\_\_*N*/X///

Table 1. Input Control-Word Bit Map

| 15    | 14 | 13 | 12    | 11    | 10    | 9     | 8   | 7   | 6  | 5  | 4   | 3   | 2   | 1   | 0  |

|-------|----|----|-------|-------|-------|-------|-----|-----|----|----|-----|-----|-----|-----|----|

| NO-OP | NU | NU | CONV4 | CONV3 | CONV2 | CONV1 | DV4 | DV2 | NU | NU | CHS | CAL | NUL | PDX | PD |

First bit clocked in.

| BIT          | NAME        | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                      |

|--------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15           | NO-OP       | If this bit is a logic high, the remaining 15 LSBs are transferred to the control register and a new conversion begins when $\overline{\text{CS}}$ returns high. If this bit is set low, the control word is not passed to the control register, the ADC configuration remains unchanged, and no new conversion begins when $\overline{\text{CS}}$ returns high. |

| 5, 6, 13, 14 | NU          | Used for test purposes only. Set these bits low.                                                                                                                                                                                                                                                                                                                 |

| 9–12         | CONV1-CONV4 | Conversion Time Control Bits. See Table 4.                                                                                                                                                                                                                                                                                                                       |

| 7, 8         | DV2, DV4    | XCLK to Oversampling Cock Ratio Control Bits. See Table 5.                                                                                                                                                                                                                                                                                                       |

| 4            | CHS         | Input Channel Select. A logic high selects channel 2 (IN2+ and IN2-), while a logic low selects channel 1 (IN1+ and IN1-). See Tables 2 and 3.                                                                                                                                                                                                                   |

| 3            | CAL         | Gain-Calibration Bit. A logic high selects gain-calibration mode. See Table 3.                                                                                                                                                                                                                                                                                   |

| 2            | NUL         | Internal Offset-Null Bit. A logic high selects offset-null mode. See Table 3.                                                                                                                                                                                                                                                                                    |

| 1            | PDX         | Oscillator Power-Down. Set this bit high to power down the RC oscillator.                                                                                                                                                                                                                                                                                        |

| 0            | PD          | Analog Power-Down. Set this bit high to power down the analog section.                                                                                                                                                                                                                                                                                           |

NO-OP is a zero, the control word is not transferred to the control register, the ADC's configuration remains unchanged, and no new conversion is initiated. This allows specific ADCs in a "daisy chain" arrangement to be reconfigured while leaving the remaining ADCs unchanged. Table 1 lists the various ADC control word functions.

Output data is shifted out of DOUT at the same time the input control word for the next conversion is shifted in (Figure 8).

On power-up, all internal registers reset to zero. Therefore, when writing the first control word to the ADC, the data simultaneously shifted out will be zeros. The first conversion begins when  $\overline{\text{CS}}$  goes high  $\overline{\text{(NO-OP)}}$  = 1). The results are placed in the 16-bit I/O register for access on the next data-transfer operation.

#### Power-Down Mode

Bits 0 and 1 control the ADC's power-down mode. If bit 0 (PD) is a logic high, power is removed from all analog circuitry except the RC oscillator. A logic high at bit 1 (PDX) removes power from the RC oscillator. If both bits PD and PDX are a logic high, or if PD is high and RCSEL is low, the supply currents reduce to  $4\mu A$ . If an external XCLK clock continues to run in power-down mode, the supply current will depend on the clock rate.

When PDX is set high, the internal RC oscillator stops shortly after  $\overline{\text{CS}}$  returns high. If the next control word written to the device has  $\overline{NO-OP} = 1$  instructing the ADC to convert, BUSY will go low, but because the RC oscillator is stopped, BUSY will remain low and will not allow a new conversion to begin. To avoid this situation, write a "dummy" control word with  $\overline{NO-OP} = 0$  and any combination of bits 14-0 in the control word following the control word with PDX = 0. With  $\overline{NO-OP}$  = 0, bits 14-0 are ignored and the internal state machine resets. Next, perform a normal 3-step calibration (see Table 3). Note that XCLK must be connected to VDD or GND through a resistor (suggested value is  $1M\Omega$ ) when the RC oscillator mode is selected (RCSEL = VDD). This resistor is not necessary if the external oscillator mode is used, or if the internal oscillator is not shut down.

#### **Selecting the Analog Inputs**

Bit 4 (CHS) controls which of the two differential inputs connect to the internal ADC inputs (see the *Functional Diagram*). A logic high selects IN2+ and IN2- while a logic low selects IN1+ and IN1-. Table 2 shows the allowable input multiplexer configurations.

**Table 2. Allowable Input Multiplexer Configurations**

| CAL | NUL | CHS | NO-OP | ADC IN+      | ADC IN-      | DESCRIPTION                                                                                                                                                                                           |

|-----|-----|-----|-------|--------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | 0   | 0   | 1     | IN1+         | IN1-         | Channel 1 connected to ADC inputs. Conversion begins when $\overline{\text{CS}}$ returns high.                                                                                                        |

| 0   | 0   | 1   | 1     | IN2+         | IN2-         | Channel 2 connected to ADC inputs. Conversion begins when $\overline{\text{CS}}$ returns high.                                                                                                        |

| 0   | 1   | 0   | 1     | IN1-         | IN1-         | IN1- connected to the ADC inputs; offset-null mode selected. Autonull conversion begins when $\overline{\text{CS}}$ returns high, and the results are stored in the null register.                    |

| 0   | 1   | 1   | 1     | IN2-         | IN2-         | IN2- connected to the ADC inputs; offset-null mode selected. Autonull conversion begins when $\overline{\text{CS}}$ returns high, and the results are stored in the null register.                    |

| 1   | 1   | Х   | 1     | REF-         | REF-         | REF- connected to the ADC inputs; offset-null mode selected. Autonull conversion begins when $\overline{\text{CS}}$ returns high, and the results are stored in the null register.                    |

| 1   | 0   | Х   | 1     | REF+         | REF-         | REF+ and REF- connected to the ADC inputs; gain-calibration mode selected. Autocal conversion begins when $\overline{\text{CS}}$ returns high, and the results are stored in the 16-bit I/O register. |

| X   | Х   | Х   | 0     | No<br>Change | No<br>Change | Input control word is not transferred to the control register. ADC configuration remains unchanged and no new conversion starts when $\overline{\text{CS}}$ returns high.                             |

X = Don't Care

Table 3. Procedure to Calibrate the ADC

|      |                                                                                                                                                                                                                                             | CONTROL WORD |             |                 |              |             |              |     |     |     |    |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------------|-----------------|--------------|-------------|--------------|-----|-----|-----|----|

| STEP | DESCRIPTION                                                                                                                                                                                                                                 | NO-OP        | Not<br>Used | CONV1-<br>CONV4 | DV2 &<br>DV4 | Not<br>Used | снѕ          | CAL | NUL | PDX | PD |

| 1    | Sets the new conversion speed (if required) and performs an offset correction conversion with the internal ADC inputs shorted to REF. The result is stored in the null register. (This step also selects the speed/resolution for the ADC.) | 1            | 00          | New<br>Data     | XX           | 00          | Х            | 1   | 1   | 0   | 0  |

| 2    | Performs a gain-calibration conversion with<br>the null register contents as the starting value.<br>The result is stored in the calibration register.                                                                                       | 1            | 00          | No<br>Change    | xx           | 00          | X            | 1   | 0   | 0   | 0  |

| 3    | Performs an offset-null conversion with the internal ADC inputs shorted to the selected input channel's negative input (IN1- or IN2-). The next operation performs the first signal conversion with the new setup.                          | 1            | 00          | No<br>Change    | XX           | 00          | 0<br>or<br>1 | 0   | 1   | 0   | 0  |

X = Don't Care

#### 3-Step Calibration

The data sheet electrical specifications apply to the device after optional calibration of gain error and offset. Uncalibrated, the gain error is typically 2%.

Table 3 describes the three steps required to calibrate the ADC completely.

Once the ADC is calibrated to the selected channel, set CAL = 0 and NUL = 0 and leave CHS unchanged in the next control word to perform a signal conversion on the selected analog input channel.

Calibrate the ADC after the following operations:

- when power is first applied

- if the reference common-mode voltage changes

- if the common-mode voltage of the selected input channel varies significantly. The CMRR of the analog inputs is 0.25LSB/V.

- after changing channels (if the common-mode voltages of the two channels are different)

- after changing conversion speed/resolution.

- after significant changes in temperature. The offset drift with temperature is typically 0.003μV/°C.

Automatic gain calibration is not allowed in the 102,400 cycles per conversion mode (see Programming Conversion Time). In this mode, calibration can be achieved by connecting the reference voltage to one input channel and performing a normal conversion. Subsequent conversion results can be corrected by software. Do not issue a NO-OP command directly following the gain calibration, as the calibration data will be lost.

#### **Programming Conversion Time**

The MAX110/MAX111 are specified for 12 bits of accuracy and up to  $\pm 14$  bits of resolution. The ADC's resolution depends on the number of clock cycles allowed during each conversion. Control-register bits 9–12 (CONV1–CONV4) determine the conversion time by controlling the nominal number of oversampling clock cycles required for each conversion (OSCC/CONV). Table 4 lists the available conversion times and resulting resolutions.

To program a new conversion time, perform a 3-step calibration with the appropriate CONV1–CONV4 data used in Table 3. The ADC is now calibrated at the new conversion speed/resolution.

**Table 4. Available Conversion Times**

| CONV4 | CONV3 | CONV2 | CONV1 | CLOCK CYCLES<br>PER<br>CONVERSION | NOMINAL CONVERSION TIME<br>RCSEL = GND, DV2 = DV4 = 0, XCLK = 500kHz<br>(ms) | CONVERSION<br>RESOLUTION<br>(Bits) |

|-------|-------|-------|-------|-----------------------------------|------------------------------------------------------------------------------|------------------------------------|

| 1     | 0     | 0     | 1     | 10,240                            | 20.48                                                                        | 12 + POL                           |

| 0     | 0     | 1     | 1     | 20,480                            | 40.96                                                                        | 13 + POL                           |

| 0     | 1     | 1     | 0     | 81,920                            | 163.84                                                                       | 14 + POL                           |

| 0     | 0     | 0     | 0     | 102,400*                          | 204.80                                                                       | 14 + POL                           |

<sup>\*</sup> Gain-calibration mode is not available with 102,400 clock cycles/conversion selected.

#### Table 5. Clock Divider-Ratio Control

| DV2 | DV4 | DESCRIPTION                                                                                           |

|-----|-----|-------------------------------------------------------------------------------------------------------|

| 0   | 0   | XCLK or internal RC oscillator connects directly to the ADC; fosc = fxclk.                            |

| 0   | 1   | XCLK or internal RC oscillator is divided by 4 and connects to the ADC; fosc = fxclk ÷ 4.             |

| 1   | 0   | XCLK or internal RC oscillator is divided by 2 and connects to the ADC; $f_{OSC} = f_{XCLK} \div 2$ . |

| 1   | 1   | Not allowed                                                                                           |

Clock duty cycles of 50% ±10% are recommended.

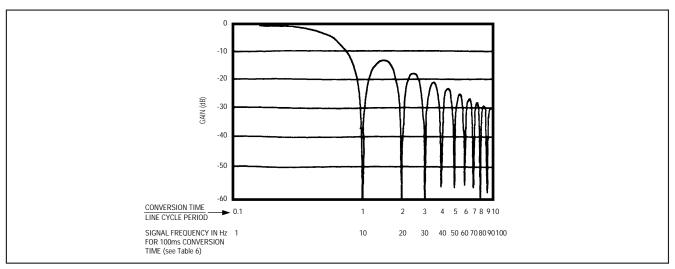

Figure 9. MAX110/MAX111 Noise Rejection Follows SIN(X) / X Function

#### Selecting the Oversampling Clock Frequency

Choose the oversampling frequency, fosc, carefully to achieve the best relative-accuracy performance from the MAX110/MAX111 (see *Typical Operating Characteristics*).

#### Clock Divider-Ratio Control Bits

Bits 7 and 8 (DV2 and DV4) program the clock-frequency divider network. The divider network sets the frequency ratio between fxclk (the frequency of the external TTL/CMOS clock or internal RC oscillator) and fosc (the oversampling frequency used by the ADC). An oversampling clock frequency between 450kHz and 700kHz is optimum for the converter. Best performance over the extended temperature range is obtained by choosing 1MHz or 1.024MHz with the divide-by-2 option (DV2 = 1) (see the section Effect of Dither on INL). To determine the converter's accuracy at other clock frequencies, see the Typical Operating Characteristics and Table 5.

#### Effect of Dither on Relative Accuracy

First-order sigma-delta converters require dither for randomizing any systematic tone being generated in the modulator. The frequency of the dither source plays an important role in linearizing the modulator. The ratio of the dither generator's frequency to that of the modulator's oversampling clock can be changed by setting the DV2/DV4 bits. The XCLK clock is directly used by the dither generator while the DV2/DV4 bits reduce the oversampling clock by a ratio of 2 or 4. Over the commercial temperature range, any ratio (i.e., 1, 2, or 4) between the dither frequency and the oversampling

clock frequency can be used for best performance. Over the extended and military temperature ranges, the ratio of 2 or 4 gives the best performance. See the *Typical Operating Characteristics* to observe the effect of the clock divider on the converter's linearity.

#### 50Hz/60Hz Line Frequency Rejection

High rejection of 50Hz or 60Hz is obtained by using an oversampling clock frequency and a clock-cycles/conversion setting so the conversion time equals an integral number of line cycles, as in the following equation:

$$fosc = fline x m / n$$

where fosc is the oversampling clock frequency, fLINE = 50Hz or 60Hz, m is the number of clock cycles per conversion (see Table 4), and n is the number of line cycles averaged every conversion.

This noise rejection is inherent in integrating and sigma-delta ADCs, and follows a SIN(X) / X function (Figure 9). Notches in this function represent extremely high rejection, and correspond to frequencies with an integral number of cycles in the MAX110/MAX111's selected conversion time.