MORE THAN 16,057 SECTORS (271,299,072 BITS) CMOS 3.3V-ONLY SERIAL READ FLASH MEMORY

#### **DESCRIPTION**

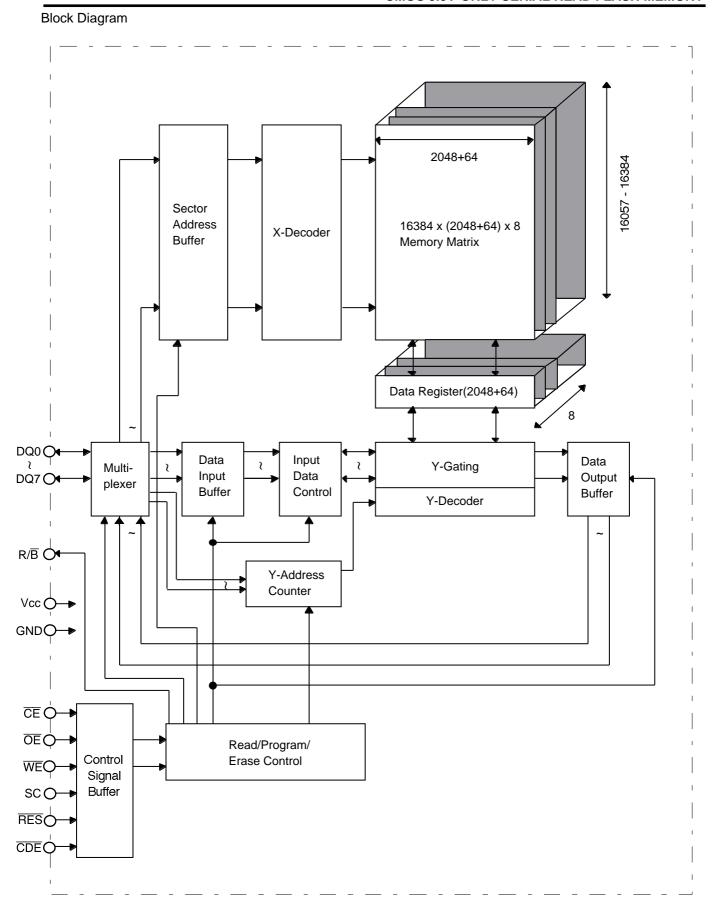

The MITSUBISHI M5M29F25611 is a CMOS Flash Memory with AND type multi-level memory cells.

It has fully automatic programming and erase capabilities with a single 3.3V power supply.

The functions are controlled by simple external commands. To fit the I/O card applications, the unit of programming and erase is as small as (2048+64) bytes.

Available sectors of M5M29F25611 are more than 16,057(98% of all sector address) and less than 16,384 sectors.

## **FEATURES**

- On-board single power supply(Vcc): Vcc=3.0V to 3.6V

- Organization

AND Flash Memory:

(2048+64)bytes x (More than 16,057 sectors)

Data register: (2048+64)bytes

Multi-level memory cell:

2bit / per memory cell.

Automatic programming :

Sector program time: 2.5 ms typ.

System bus free

Address, data latch function

Internal automatic program verify function

Status data polling function

Automatic erase :

Single sector erase time: 1.0 ms typ.

System bus free

Internal automatic erase verify function

Status data polling function

Erase mode :

Single sector erase ((2048+64)byte unit)

Fast access time :

Serial read First access time: 50µs max.

Serial access time: 50ns max.

Low power dissipation :

Icc2 = 30mA typ. / 50mA max. (Read)

ISB2 =  $30\mu A$  typ.  $/50\mu A$  max. (Standby)

Icc3 = 20mA typ. / 40mA max. (Program)

ICC4 = 20mA typ. / 40mA max. (Erase)

ISB3 =  $1\mu A$  typ. /  $10\mu A$  max. (Deep standby)

Package : 48pin-TSOP(I) (12.0 x 20.0mm2)

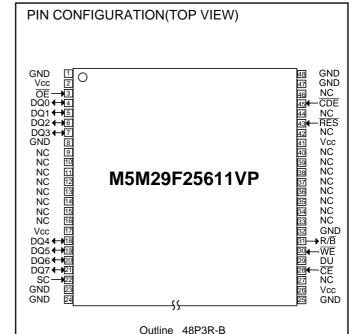

## Pin Description

| Pin name  | Function            |

|-----------|---------------------|

| DQ0-7     | Input / Output      |

| CE        | Chip enable         |

| ŌĒ        | Output enable       |

| WE        | Write enable        |

| CDE       | Command data enable |

| Vcc note1 | Power supply        |

| GND note1 | Ground              |

| R/B       | Ready / Busy        |

| RES       | Reset               |

| SC        | Serial clock        |

| NC        | No connect          |

| DU note2  | Don't Use           |

|           |                     |

Note1:All Vcc and GND pins should be connected to a common power supply and a ground, respectively. Note2:Pin should not be connected to anything.

MORE THAN 16,057 SECTORS (271,299,072 BITS) CMOS 3.3V-ONLY SERIAL READ FLASH MEMORY

2

MORE THAN 16,057 SECTORS (271,299,072 BITS) CMOS 3.3V-ONLY SERIAL READ FLASH MEMORY

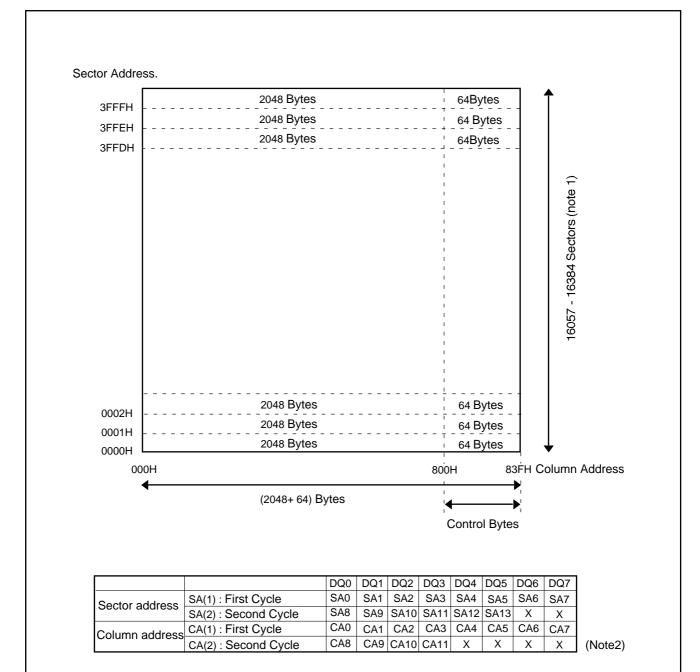

## Memory Map & Address

Note 1: Some failed sectors may exist in the device.

The failed sectors can be recognized by reading the sector valid data written in a part of the column address 820H - 825H. The sector valid data must be read and kept outside of the sector before the sector erase.

When the sector is programmed, the sector valid data should be written back to the sector.

2: An X means "Don't care". The pin level can be set to either VIL or VIH, as shown on page 12.

MORE THAN 16,057 SECTORS (271,299,072 BITS) CMOS 3.3V-ONLY SERIAL READ FLASH MEMORY

#### Mode Selection

|                      | Pin     |     |     |     |     |      |     | (note3) |                         |

|----------------------|---------|-----|-----|-----|-----|------|-----|---------|-------------------------|

| Mode                 |         | CE  | ŌĒ  | WE  | SC  | RES  | CDE | R/B     | DQ0 - DQ7               |

| Deep Standby         | (note4) | Х   | Х   | Х   | Х   | VILR | Х   | Voн     | Hi - Z                  |

| Standby              |         | ViH | X   | X   | X   | Vihr | X   | Vон     | Hi - Z                  |

| Output disable       |         | VIL | Vін | ViH | X   | VIHR | X   | Voн     | Hi - Z                  |

| Status register read | (note1) | VIL | VIL | ViH | Х   | VIHR | Х   | Vон     | Status register outputs |

| Command Write        | (note2) | VIL | ViH | VIL | VIL | Vihr | VIL | Voн     | Din                     |

- Notes: 1. Default mode after the power on is the status register read mode(refer to status transition P.11). From DQ0 to DQ7 pins output the status when  $\overline{CE}=V_{\parallel L}$  and  $\overline{OE}=V_{\parallel L}$ .

- 2. Refer to the command definition(P.5). Data can be read, programmed and erased after commands are written in this mode.

- 3. The  $R/\overline{B}$  bus should be pulled up to Vcc to maintain the VoH level while the  $R/\overline{B}$  pin outputs a high impedance.

- 4. An X means "Don't care". The pin level can be set to either VIL or VIH as shown on page 12.

## Pin Description

#### CE

$\overline{\text{CE}}$  is used to select the device. The status returns to the Standby at the rising edge of  $\overline{\text{CE}}$  in the reading operation. However, the status does not return to the Standby at the rising edge of  $\overline{\text{CE}}$  in the busy state in programming and erase operation.

#### **OE**

Memory data, status register data and identifier code (ID code) can be read, when OE is VIL.

## WE

Commands and address are latched at the rising edge of  $\overline{\text{WE}}$ .

#### SC

Programming and reading data is latched at the rising edge of SC.

#### RES

$\overline{\text{RES}}$  pin must be kept at the VILR (GND±0.2V) level when Vcc is turned on and off. In this way, data in the memory is protected against unintentional erase and programming.  $\overline{\text{RES}}$  must be kept at the VIHR (Vcc±0.2V) level during any operations such as programming, erase and read

### CDE

Commands and data are latched when  $\overline{\text{CDE}}$  is V<sub>I</sub>L and Address is latched when  $\overline{\text{CDE}}$  is V<sub>I</sub>H.

### R/B

The R/ $\overline{B}$  indicates the program/erase status of the flash memory. The R/ $\overline{B}$  signal is initially at a high impedance state. It turns to a Vol level after the (40H) command in programming operation or the(B0H) command in erase operation. No commands can be written during the R/ $\overline{B}$  pin outputs a Vol. After the erase or programming operation finishes, the R/ $\overline{B}$  signal turns back to the high impedance state.

The  $R/\overline{B}$  indicates the first access status of the flash memory in serial read (1) and (2). It turns to a Vol level after the sector address (SA(2)) in serial read (1) and serial read (2) operation. No commands can be written during the  $R/\overline{B}$  pin outputs a Vol. Also, no serial clock can be input during the  $R/\overline{B}$  pin outputs a Vol. After the first access operation finishes, the  $R/\overline{B}$  signal turns back to the high impedance state.

### DQ0-DQ7

The DQ pins are used to input data, address and command, and are used to output memory data, status register data and identifier code (ID code).

# MORE THAN 16,057 SECTORS (271,299,072 BITS) CMOS 3.3V-ONLY SERIAL READ FLASH MEMORY

# Command Definition (note 1,2)

|                       |               |                         |             | Firs          | it   |           | Second cycle   |                 |  |

|-----------------------|---------------|-------------------------|-------------|---------------|------|-----------|----------------|-----------------|--|

|                       | Comm          | nand                    | Bus         | Operation     | Data | Operation | Data           |                 |  |

|                       |               |                         | cycles      | mode (note 3) | in   | mode      | in             | out             |  |

| Serial read(1)        | Without CA    | Vithout CA              |             | Write         | 00H  | Write     | SA(1) (note 4) | -               |  |

|                       | With CA       |                         | 3+2h(note6) | Write         | 00H  | Write     | SA(1) (note 4) | -               |  |

| Serial read(2)        |               |                         | 3           | Write         | F0H  | Write     | SA(1) (note 4) | -               |  |

| Read identifier c     | odes          |                         | 1           | Write         | 90H  | Read      | - ID (n        | ote8,9)         |  |

| Data Recovery F       | Read          |                         | 1           | Write         | 01H  | Read      | - Recove       | - Recovery Data |  |

| Auto Erase            | Single sector |                         | 4           | Write         | 20H  | Write     | SA(1) (note 4) | -               |  |

| Auto Program          | Program (1)   | Without CA (note 7)     | 4           | Write         | 10H  | Write     | SA(1) (note 4) | -               |  |

|                       |               | With CA (note 7)        | 4+2h(note6) | Write         | 10H  | Write     | SA(1) (note 4) | -               |  |

|                       | Program (2)   | (note 10)               | 4           | Write         | 1FH  | Write     | SA(1) (note 4) | -               |  |

|                       | Program (3) ( | control bytes) (note 7) | 4           | Write         | 0FH  | Write     | SA(1) (note 4) | -               |  |

|                       | Program (4)   | Without CA (note 7)     | 4           | Write         | 11H  | Write     | SA(1) (note 4) | -               |  |

|                       |               | With CA (note 7)        | 4+2h(note6) | Write         | 11H  | Write     | SA(1) (note 4) | -               |  |

| Reset                 |               | 1                       | Write       | FFH           | -    | -         | -              |                 |  |

| Clear status register |               | 1                       | Write       | 50H           | -    | -         | -              |                 |  |

| Data Recovery V       | Vrite         |                         | 4           | Write         | 12H  | Write     | SA(1) (note 4) | -               |  |

|                |                                               |                         |             | Third o   | cycle         | Four      | th cycle        |

|----------------|-----------------------------------------------|-------------------------|-------------|-----------|---------------|-----------|-----------------|

|                | Comi                                          | mand                    | Bus         | Operation | Data          | Operation | Data            |

|                | With CA erial read(2) uto Erase Single sector |                         |             | mode      | in            | mode      | in              |

| Serial read(1) | Without CA                                    |                         | 3           | Write     | SA(2) (note4) | -         | -               |

|                | With CA                                       |                         | 3+2h(note6) | Write     | SA(2) (note4) | Write     | CA(1) (note5)   |

| Serial read(2) |                                               |                         | 3           | Write     | SA(2) (note4) | -         | -               |

| Auto Erase     | Single sector                                 |                         | 4           | Write     | SA(2) (note4) | Write     | B0H (note11)    |

| Auto Program   | Program (1)                                   | Without CA (note 7)     | 4           | Write     | SA(2) (note4) | Write     | 40H (note11,12) |

|                |                                               | With CA (note 7)        | 4+2h(note6) | Write     | SA(2) (note4) | Write     | CA(1) (note5)   |

|                |                                               | (note 10)               | 4           | Write     | SA(2) (note4) | Write     | 40H (note11,12) |

|                | Program (3) (d                                | control bytes) (note 7) | 4           | Write     | SA(2) (note4) | Write     | 40H (note11,12) |

|                | Program (4)                                   | Without CA (note 7)     | 4           | Write     | SA(2) (note4) | Write     | CA(1) (note5)   |

|                |                                               | With CA (note 7)        | 4+2h(note6) | Write     | SA(2) (note4) | Write     | 40H (note11,12) |

| Data Recovery  | Write                                         |                         | 4           | Write     | SA(2) (note4) | Write     | 40H (note11,12) |

|                |             |                  |             | Fifth cycle |               | Six   | th cycle        |

|----------------|-------------|------------------|-------------|-------------|---------------|-------|-----------------|

| Command        |             | Bus              | Operation   | Data        | Operation     | Data  |                 |

|                |             |                  | cycles      | mode        | in            | mode  | in              |

| Serial read(1) | With CA     |                  | 3+2h(note6) | Write       | CA(2) (note5) | -     | -               |

| Auto Program   | Program (1) | With CA (note 7) | 4+2h(note6) | Write       | CA(2) (note5) | Write | 40H (note11,12) |

|                | Program (4) | With CA (note 7) | 4+2h(note6) | Write       | CA(2) (note5) | Write | 40H (note11,12) |

Notes: 1. Commands, sector address and column address are latched at rising edge of  $\overline{\text{WE}}$  pulses. Program data is latched at rising edge of SC pulses.

- 2. The chip is in the read status register mode when RES is set to VIHR first time after the power up.

- 3. Refer to the command read and write mode in mode selection table (P.4).

- 4. SA(1)=Sector address (SA0 SA7), SA(2)=Sector address (SA8 SA13).

- 5. CA(1)=Column address (CA0 CA7), CA(2)=Column address (CA8 CA11).(0 CA11 CA0 83FH)

- 6. The variable h is the input number of times of set of CA(1) and CA(2).(1 h 2048+64) Set of CA(1) and CA(2) can be input not only one time but free times.

- 7. By using program(1) and (3), data can additionally be programmed for each sector before erase.

- 8. ID=Identifier code; Manufacturer code (1CH), Device code (6CH).

- 9. The manufacturer identifier code is output when  $\overline{\text{CDE}}$  is low and the device identifier code is output when  $\overline{\text{CDE}}$  is high.

- 10. Before program (2) operations, data in the programmed sector must be erased.

- 11. No commands can be written during auto program and erase (when the  $R/\overline{B}$  pin outputs a Vol.).

- 12. The fourth cycle or sixth cycle of the auto program comes after the program data input is complete.

MORE THAN 16,057 SECTORS (271,299,072 BITS) CMOS 3.3V-ONLY SERIAL READ FLASH MEMORY

### Mode Description

#### Read

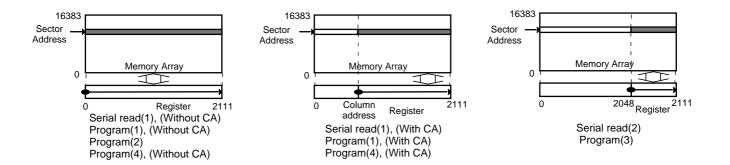

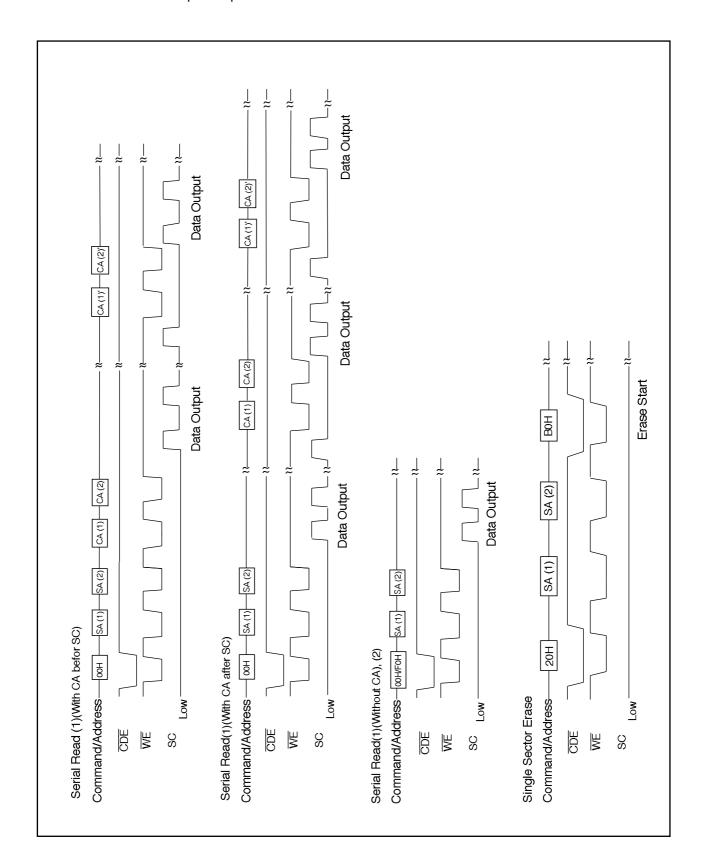

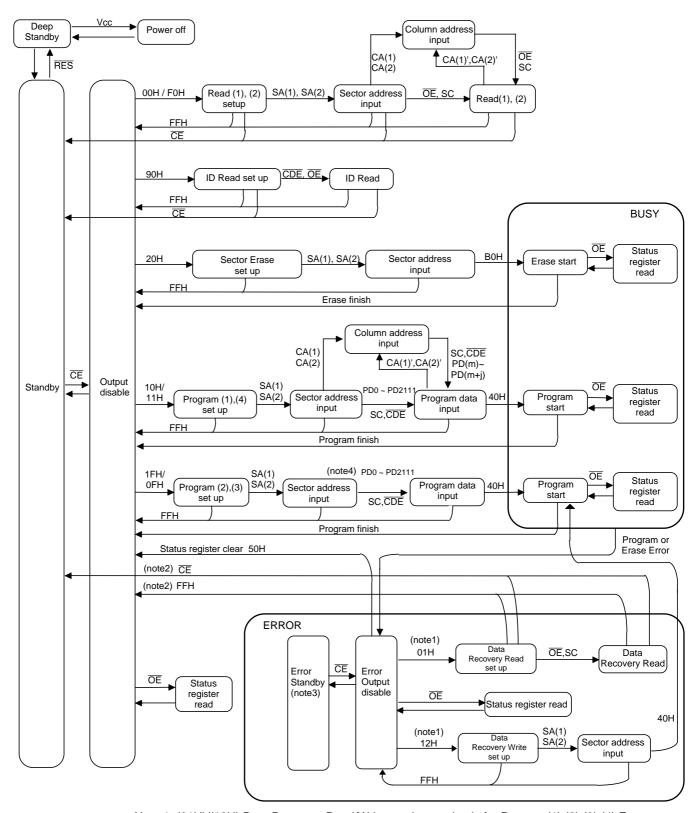

#### Serial read(1)

Memory data D0-D2111 in the sector of address SA is sequentially read. Output data is not valid after the number of the serial clock SC pulse exceeds 2112. When the column address CA is input after SA, memory data D(m) -D(m+j) in the sector of address SA is sequentially read. Then output data is not valid after the number of the SC pulse exceeds (2112-m).

The mode turns back to the Standby mode at any time when  $\overline{CE}$  is ViH.

### Serial read(2)

Memory data D2048-D2111 in the sector of address SA is sequentially read. Output data is not valid after the number of the SC pulse exceeds 64. The mode turns back to the Standby mode at any time when  $\overline{CE}$  is ViH.

#### **Automatic Erase**

#### Single sector Erase

Memory data D0-D2111 in the sector of address SA is erased automatically by internal control circuits. After the sector erase starts, the erasure completion can be checked through the  $R/\overline{B}$  signal and status data polling. All the bits in the sector are "1" after the erase. The sector valid data stored in a part of memory data D2048-D2111 must be read and kept outside of the sector before the sector erase.

#### Automatic program

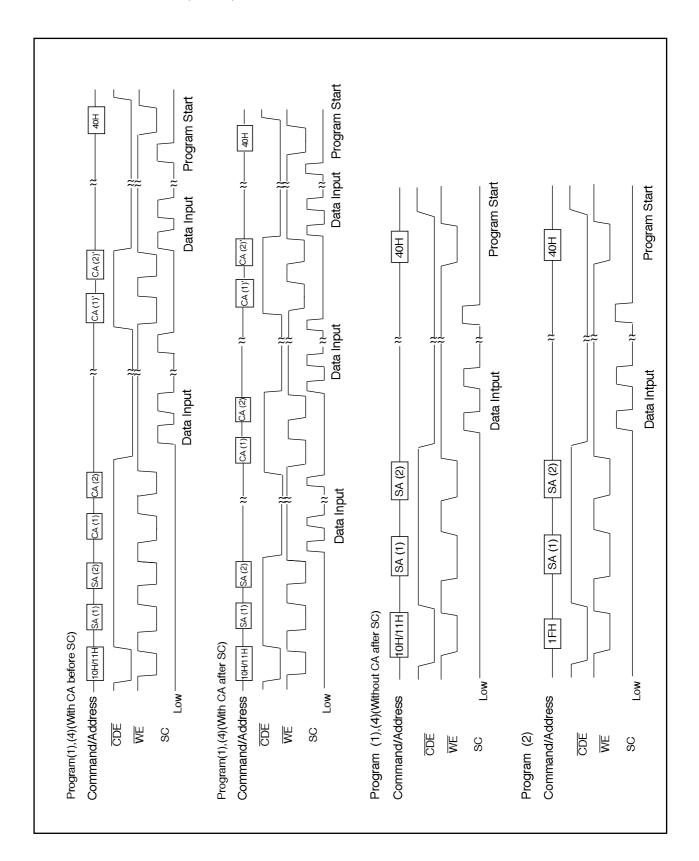

### Program(1)

Program data PD0-PD2111 is programmed into the sector of address SA automatically by internal control circuits. When CA is input after SA, program data PD(m) -PD(m+j) is programmed form CA into the sector of address SA automatically by internal control circuits. By using program(1), data can additionally be programmed for each sector before the following erase. When the column is programmed, the data of the column must be [FF].

After the programming starts, the program completion can be checked through the  $R/\overline{B}$  signal and status data polling. Programmed bits in the sector turn from "1" to "0" when they are programmed. The sector valid data should be included in the program data PD2048-PD2111. In this mode, E/W number of times must be counted whenever program(1) execute.

## Program(2)

Program data PD0-PD2111 is programmed into the sector of address SA automatically by internal control circuits. After the programming starts, the program completion can be checked through the R/B signal and status data polling. Programmed bits in the sector turn from "1" to "0" when they are programmed. The sector must be erased before programming. The sector valid data should be included in the program data PD2048-PD2111. In this mode, Write number of times must be counted whenever program(2) execute.

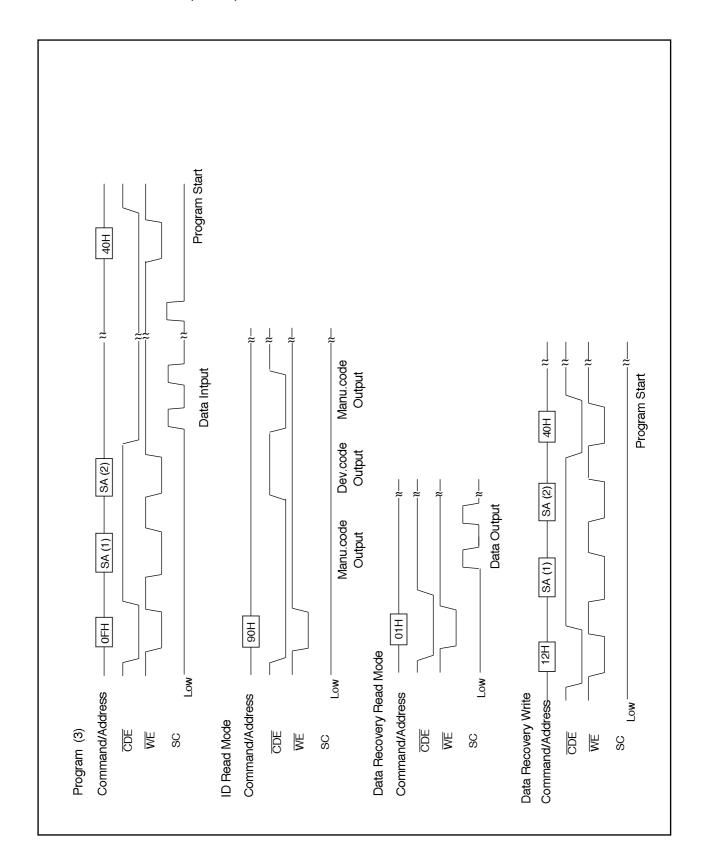

### Program(3)

Program data PD2048-PD2111 is programmed into the sector of address SA automatically by internal control circuits. By using program(3), data can additionally be programmed for each sector before the following erase. When the column is programmed, the data of the column must be [FF].

After the programming starts, the program completion can be checked through the R/B signal and status data polling. Programmed bits in the sector turn from "1" to "0" when they programmed. In this mode, E/W number of times must be counted whenever program(3) execute.

#### Program(4)

Program data PD0-PD2111 is programmed into the sector of address SA automatically by internal control circuits. When CA is input after SA, program data PD(m) -PD(m+j) is programmed from CA into the sector of address SA automatically by internal control circuits. By using program(4), data can be rewritten for each sector before the following erase. So the column data before programming operation are either "1" to "0".

After the programming starts, the program completion can be checked through the R/B single and status data polling. The sector valid data should be included in the program data PD2048-PD2111. In this mode, E/W number of times must be counted whenever program(4) execute.

MORE THAN 16,057 SECTORS (271,299,072 BITS) CMOS 3.3V-ONLY SERIAL READ FLASH MEMORY

### Status Register Read

The status returns to the register read mode from Standby mode ,when  $\overline{CE}$  and  $\overline{OE}$  is  $\forall \mathbb{L}$ . In the status register read mode, DQ pins output the same operation status as in the status data polling defined in the function description, table 1 (page 34).

#### Identifier Read

The manufacturer and device identifier code can be read in the identifier read mode. The manufacturer and device identifier code is selected with  $\overline{\text{CDE}}$  VIL and VIH, respectively.

#### Data Recovery Read

When programming was error, the program data can be read. When additional programming (Program(1),(3),(4))was error, the data compounded of the program data and the original data in the sector of address SA can be read. Output data is not valid after the number of SA pulse exceeds 2112. The mode turns back to the Standby mode at any time when  $\overline{CE}$  is ViH. (See timing waveform in page 31)

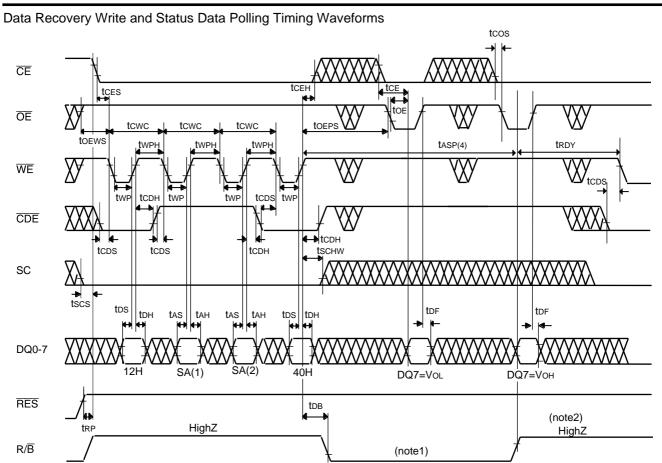

## Data Recovery Write

When programming into a sector of address SA was an error, the program data can be re-written automatically by selecting the other sector SA'. In this Case, top address [SA13] of sector of address SA' must be the same as SA. Since the data recovery write mode utilizes program(4), rewritten sector of address SA' needs no sector erase before rewritten. After the data recovery write mode starts, the program completion can be checked through R/B signal and the status data polling.

MORE THAN 16,057 SECTORS (271,299,072 BITS) CMOS 3.3V-ONLY SERIAL READ FLASH MEMORY

Command / Address / Data Input Sequence

MORE THAN 16,057 SECTORS (271,299,072 BITS) CMOS 3.3V-ONLY SERIAL READ FLASH MEMORY

Command / Address / Data Input Sequence

MORE THAN 16,057 SECTORS (271,299,072 BITS) CMOS 3.3V-ONLY SERIAL READ FLASH MEMORY

Command / Address / Data Input Sequence

MORE THAN 16,057 SECTORS (271,299,072 BITS) CMOS 3.3V-ONLY SERIAL READ FLASH MEMORY

### Status Transition

Note 1: (01H)/(12H) Data Recovery Read/Write can be used only for Program(1),(2),(3),(4) Errors.

- 2: When Reset is done by CE or FFH, Error Status Flag is cleared.

- 3: When Error Standby, Icc3 level is current.

- 4: When Program(3) mode, input data is PD2048 ~ PD2111.

# MORE THAN 16,057 SECTORS (271,299,072 BITS) CMOS 3.3V-ONLY SERIAL READ FLASH MEMORY

## Absolute Maximum Ratings

| Symbol    | Parameter                      | Test conditions     | Ratings       | Unit |

|-----------|--------------------------------|---------------------|---------------|------|

| VIN, VOUT | All input and output voltages  | With respect to GND | -0.6 to +7 1) | V    |

| Vcc       | Vcc voltage                    | With respect to GND | -0.6 to +7    | V    |

| Topr      | Operating temperature range    |                     | 0 to +70      | °C   |

| Tstg      | Storage temperature range 2)   |                     | -65 to +125   | °C   |

| Tbias     | Storage temperature under bias |                     | -10 to +80    | °C   |

Notes: 1. VIN, VOUT = -2.0V for pulse width 20ns

2. Device storage temperature range before programming.

## Capacitance ( $Ta = 25^{\circ}C$ , f = 1MHz)

| Symbol | Parameter          | Test conditions                      |     | Limits |     | Unit |

|--------|--------------------|--------------------------------------|-----|--------|-----|------|

| Symbol |                    | Test conditions                      | Min | Тур    | Max |      |

| Cin    | Input capacitance  | Ta = 25°C, f = 1MHz, Vin = Vout = 0V | -   | -      | 6   | pF   |

| Cout   | Output capacitance | 14 - 25 5,1 - 11112, 111 - 1001 - 01 | -   | -      | 12  | pF   |

## **Read Operation**

DC Characteristics ( Vcc = 3.0V to 3.6V ,  $Ta = 0 \text{ to } +70^{\circ}C$ )

| 0      | D                           | Tantana Bilana                                                    |           | Limits |              | 1.121 |

|--------|-----------------------------|-------------------------------------------------------------------|-----------|--------|--------------|-------|

| Symbol | Parameter                   | Test conditions                                                   | Min       | Тур    | Max          | Unit  |

| ILI    | Input leakage current       | GND Vin Vcc                                                       | -         | -      | 2            | μA    |

| ILO    | Output leakage current      | GND Vout Vcc                                                      | -         | -      | 2            | μA    |

| ISB1   |                             | CE = VIH                                                          | -         | 0.3    | 1            | mA    |

| ISB2   | Standby Vcc current         | $\overline{CE} = Vcc \pm 0.2V$<br>$\overline{RES} = Vcc \pm 0.2V$ | -         | 30     | 50           | μA    |

| ISB3   | Deep Standby Vcc current    | $\overline{RES} = GND \pm 0.2V$                                   | -         | 1      | 10           | μA    |

| ICC1   | Operating Vcc current       | IOUT = 0mA, f = 0.2MHz                                            | -         | 20     | 25           | mA    |

| ICC2   | Operating vcc current       | IOUT = 0mA, f = 20MHz                                             | -         | 30     | 50           | mA    |

| VIL    | Input low voltage           |                                                                   | -0.3 1)   | -      | 0.8          | V     |

| ViH    | Input high voltage          |                                                                   | 2.0       | -      | Vcc + 0.3 2) | V     |

| VILR   | Input low voltage(RES pin)  |                                                                   | -0.2      | -      | 0.2          | V     |

| VIHR   | Input high voltage(RES pin) |                                                                   | Vcc - 0.2 | -      | Vcc + 0.2    | ٧     |

| VoL    | Output low voltage          | IoL = 2mA                                                         | -         | -      | 0.4          | V     |

| Voн    | Output high voltage         | Iон = -2mA                                                        | 2.4       | -      | -            | V     |

Notes: 1.  $V_{IL}$ min = -1.0 $V_{IL}$  for pulse width 50ns.  $V_{IL}$ min = -2.0 $V_{IL}$  for pulse width 20ns.

2. Vihmax = Vcc + 1.5V for pulse width 20ns. If Vih is over the specified maximum value, the read operations are not guaranteed.

MORE THAN 16,057 SECTORS (271,299,072 BITS) CMOS 3.3V-ONLY SERIAL READ FLASH MEMORY

AC Characteristics (for power on and off, serial read) (Vcc =3.0 to 3.6V, Ta = 0 to +70°C)

**Test Conditions**

• Input pulse levels : 0.4V/2.4V

• Input pulse levels for RES: 0.2V/Vcc-0.2V

Input rise and fall times: 5ns

Output load: 1 TTL gate + 100pF (Including scope and jig.)

• Reference levels for measuring timing: 0.8V, 1.8V

| Courada a l | Davamatan                          | Took oon dikingo        |     | Limits |     | l lait |

|-------------|------------------------------------|-------------------------|-----|--------|-----|--------|

| Symbol      | Parameter                          | Test conditions         | Min | Тур    | Max | Unit   |

| tcwc        | Write cycle time                   |                         | 120 | -      | -   | ns     |

| tscc        | Serial clock cycle time            |                         | 50  | -      | -   | ns     |

| tces        | CE setup time                      |                         | 0   | -      | -   | ns     |

| tceh        | CE hold time                       |                         | 0   | -      | -   | ns     |

| twp         | Write pulse time                   | CE = VIL, OE = VIH      | 60  | -      | -   | ns     |

| twph        | Write pulse high time              |                         | 40  | -      | -   | ns     |

| tas         | Address setup time                 |                         | 50  | -      | -   | ns     |

| tah         | Address hold time                  |                         | 10  | -      | -   | ns     |

| tDS         | Data setup time                    |                         | 50  | -      | -   | ns     |

| tDH         | Data hold time                     |                         | 10  | -      | -   | ns     |

| tsac        | SC to output delay                 | CE = OE = VIL, WE = VIH | -   | -      | 50  | ns     |

| toes        | OE setup time for SC               |                         | 0   | -      | -   | ns     |

| toel        | OE low to output low-z             |                         | 0   | -      | 40  | ns     |

| toer        | OE setup time before read          |                         | 250 | -      | -   | ns     |

| toews       | OE setup time before command write |                         | 0   | -      | -   | ns     |

| tsh         | SC to output hold                  | CE = OE = VIL, WE = VIH | 15  | _      | -   | ns     |

| tDF 1)      | OE hight to output float           | CE = VIL, WE = VIH      | -   | -      | 40  | ns     |

| twsp 2)     | WE to SC delay time                | ,                       | 50  | _      | -   | μs     |

| trp         | RES to CE setup time               |                         | 1   | -      | -   | ms     |

| tsон        | SC to OE hold time                 |                         | 50  | -      | -   | ns     |

| tsp         | SC pulse width                     |                         | 20  | -      | -   | ns     |

| tspl        | SC pulse low time                  |                         | 20  | -      | -   | ns     |

| tscs        | SC setup time for CE               |                         | 0   | -      | -   | ns     |

| tcds        | CDE setup time for WE              |                         | 0   | -      | -   | ns     |

| tcdh        | CDE hold time for WE               |                         | 20  | _      | -   | ns     |

| tvrs        | Vcc setup time for RES             | CE = VIH                | 1   | _      | -   | us     |

| tvrh        | RES to Vcc hold time               | CE = VIH                | 1   | _      | _   | μs     |

| tcesr       | CE setup time for RES              | 0E = VIII               | 1   | -      | -   | μs     |

| tDFP        | R/B undefined for Vcc off          |                         | 0   | -      | -   | ns     |

| tbsy        | RES high to device ready           |                         | _   | -      | 1   | ms     |

| tcph        | CE pulse high time                 |                         | 200 | -      | -   | ns     |

| tcwrs       | CE.WE setup time for RES           |                         | 0   | -      | -   | ns     |

| tcwrh       | RES to CE, WE hold time            |                         | 0   | -      | -   | ns     |

| tsw         | SC setup for WE                    |                         | 50  | -      | -   | ns     |

| tсон        | CE hold time for OE                |                         | 0   | -      | -   | ns     |

| tscd        | SA(2)to CA(2)delay time            |                         | -   | -      | 30  | μs     |

| trs         | R/B setup time for SC              |                         | 200 | -      | -   | ns     |

| tDBR        | Time to device Busy on Read mode   |                         | -   | _      | 1   | μs     |

| trbsy       | Busy time on Read mode             |                         | _   | 45     | -   | us     |

Notes: 1. tDF is a time after which the DQ pins become open.

2. tWSD(min) is specified as a reference point only for SC, if tWSD is greater than the specified tWSD(min) limit, then access time is controlled exclusively by tSAC.

MORE THAN 16,057 SECTORS (271,299,072 BITS) CMOS 3.3V-ONLY SERIAL READ FLASH MEMORY

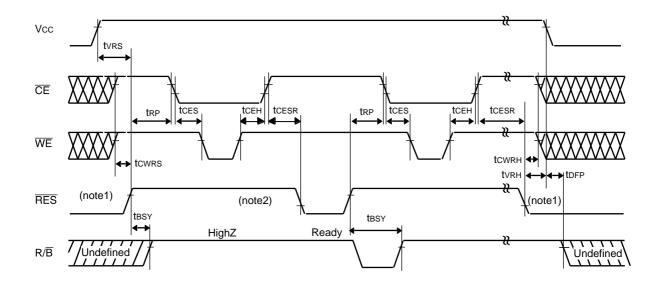

## Power on and off Sequence

note1: RES must be kept at the VILR level as shown in page 12 at the rising and falling edges of Vcc to guarantee data stored in the chip.

note2 :  $\overline{\text{RES}}$  must be kept at the VIHR level specified in page 12 while DQ7 outputs the VoL level in the status data polling and  $R/\overline{B}$  outputs the VoL level.

MORE THAN 16,057 SECTORS (271,299,072 BITS) CMOS 3.3V-ONLY SERIAL READ FLASH MEMORY

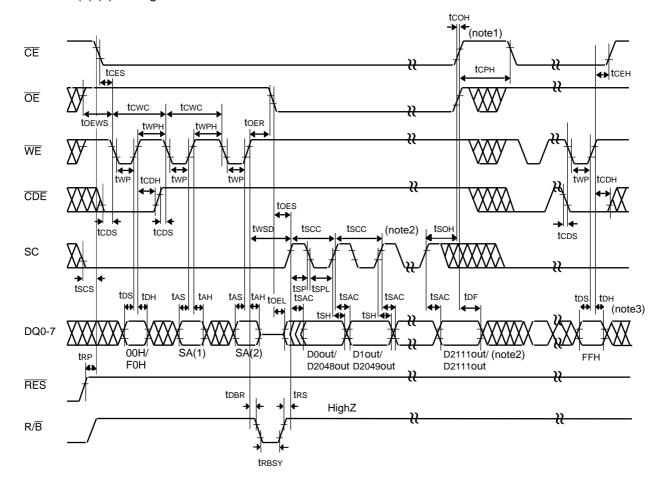

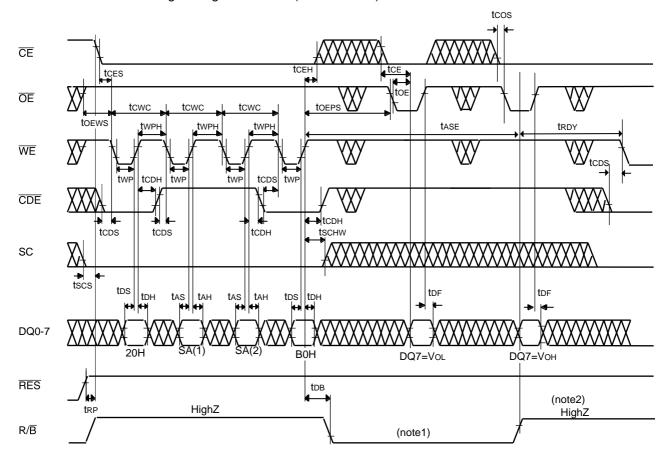

## Serial Read (1)/(2) Timing Waveforms

Note 1. The status returns to the Standby at the rising edge of  $\overline{CE}$ .

- 2. Output data is not valid after the number of the SC pulse exceed 2112 and 64 in the serial read mode (1) and (2), respectively.

- 3. The status can return to the Ready after the command FFH is input.

MORE THAN 16,057 SECTORS (271,299,072 BITS) CMOS 3.3V-ONLY SERIAL READ FLASH MEMORY

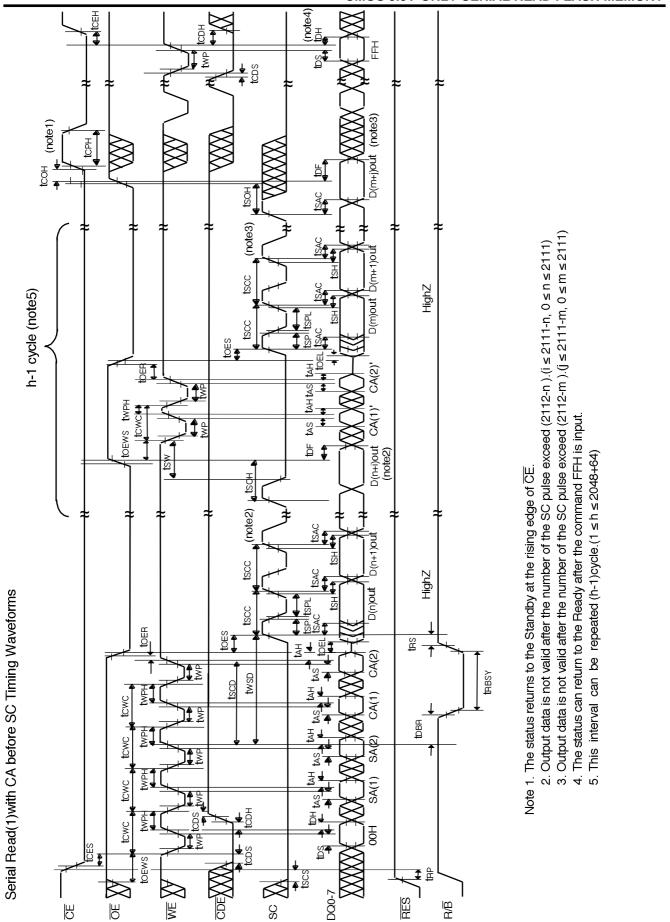

# MORE THAN 16,057 SECTORS (271,299,072 BITS) CMOS 3.3V-ONLY SERIAL READ FLASH MEMORY

Note 1. The status returns to the Standby at the rising edge of  $\overline{\text{CE}}$ .

- 2. Output data is not valid after the number of the SC pulse exceed 2112.( $0 \le k \le 2111$ )

- 3. Output data is not valid after the number of the SC pulse exceed (2112-m ). (j  $\leq$  2111-m, 0  $\leq$  m  $\leq$  2111)

- 4. The status can return to the Ready after the command FFH is input.

- 5. This interval can be repeated h cycle. (1 s h s 2048+64)

MORE THAN 16,057 SECTORS (271,299,072 BITS) CMOS 3.3V-ONLY SERIAL READ FLASH MEMORY

## **Erase and Programming Operations**

DC Characteristics ( $Vcc = 3.0V \text{ to } 3.6V \text{ , } Ta = 0 \text{ to } +70^{\circ}C$ )

| Cumbal | Parameter                | Test conditions                                                |         | Limits |              | Unit |

|--------|--------------------------|----------------------------------------------------------------|---------|--------|--------------|------|

| Symbol | Parameter                | rest conditions                                                | Min     | Тур    | Max          | Unit |

| ILI    | Input leakage current    | GND VIN VCC                                                    | -       | -      | 2            | μA   |

| ILO    | Output leakage current   | GND Vout Vcc                                                   | -       | -      | 2            | μA   |

| ISB1   |                          | CE = VIH                                                       | -       | 0.3    | 1            | mA   |

| ISB2   | Standby Vcc current      | $\overline{CE} = Vcc \pm 0.2V$ $\overline{RES} = Vcc \pm 0.2V$ | -       | 30     | 50           | μA   |

| ISB3   | Deep Standby Vcc current | RES = GND ± 0.2V                                               | -       | 1      | 10           | μA   |

| Іссз   | Operating Vcc current    | In programming                                                 | -       | 20     | 40           | mA   |

| ICC4   | Sperating vec carrent    | In erase                                                       | -       | 20     | 40           | mA   |

| VIL    | Input low voltage        |                                                                | -0.3 1) | -      | 0.8          | V    |

| ViH    | Input high voltage       |                                                                | 2.0     | -      | Vcc + 0.3 2) | V    |

| Vol    | Output low voltage       | IoL = 2mA                                                      | -       | -      | 0.4          | V    |

| Voн    | Output high voltage      | Ioн = -2mA                                                     | 2.4     | -      | -            | V    |

Notes: 1. Vilmin = -0.6V for pulse width 20ns.

<sup>2.</sup> If VIH is over the specified maximum value, the Erase and Programming operations are not guaranteed.

MORE THAN 16,057 SECTORS (271,299,072 BITS) CMOS 3.3V-ONLY SERIAL READ FLASH MEMORY

AC Characteristics (for Erase,program,ID read,status register read , data recovery read and data recovery write.) (Vcc = 3.0V to 3.6V, Ta = 0 to +70°C)

## **Test Conditions**

• Input pulse levels: 0.4V/2.4V

• Input pulse levels for RES: 0.2V/Vcc - 0.2V

Input rise and fall times: 5ns

Output load: 1 TTL gate + 100pF (Including scope and jig.)

• Reference levels for measuring timing: 0.8V, 1.8V

| Symbol   | Parameter                                 | Test condition |     | Limits |     | Unit |

|----------|-------------------------------------------|----------------|-----|--------|-----|------|

| Syllibol | Falametel                                 | Test condition | Min | Тур    | Max |      |

| tcwc     | Write cycle time                          |                | 120 | -      | -   | ns   |

| tscc     | Serial clock cycle time                   |                | 50  | -      | -   | ns   |

| tces     | CE setup time                             |                | 0   | -      | -   | ns   |

| tCEH     | CE hold time                              |                | 0   | -      | -   | ns   |

| twp      | Write pulse width                         |                | 60  | -      | -   | ns   |

| twph     | Write pulse high time                     |                | 40  | -      | -   | ns   |

| tas      | Address setup time                        |                | 50  | -      | -   | ns   |

| tah      | Address hold time                         |                | 10  | -      | -   | ns   |

| tDS      | Data setup time                           |                | 50  | -      | -   | ns   |

| tDH      | Data hold time                            |                | 10  | -      | -   | ns   |

| toews    | OE setup time before command write        |                | 0   | -      | -   | ns   |

| toeps    | OE setup time before status polling       |                | 40  | -      | -   | ns   |

| toer     | OE setup time before read                 |                | 250 | -      | -   | ns   |

| tdb      | Time to device busy                       |                | -   | -      | 150 | ns   |

| tdbr     | Time to device busy on Read Mode          |                | -   | -      | 1   | μs   |

| tase     | Auto erase time                           |                | -   | 1.0    | 10  | ms   |

| tASP(1)  | Auto program time (1)                     |                | -   | 3.0    | 40  | ms   |

| tASP(2)  | Auto program time (2)                     |                | -   | 2.5    | 40  | ms   |

| tASP(3)  | Auto program time (3)                     |                | -   | 3.0    | 40  | ms   |

| tASP(4)  | Auto program time (4)                     |                | -   | 3.5    | 40  | ms   |

| tasrw    | Data Recovery Write time                  |                | -   | 3.5    | 40  | ms   |

| twsp     | WE to SC delay time                       |                | 50  | -      | -   | μs   |

| trbsy    | Busy Time on Read Mode                    |                | -   | 45     | -   | μs   |

| twsdr    | WE to SC delay time on Recovery Read Mode |                | 2   | -      | -   | μs   |

| tCPH     | CE pulse high time                        |                | 200 | -      | -   | ns   |

| tsp      | SC pulse width                            |                | 20  | -      | -   | us   |

| tspl     | SC pulse low time                         |                | 20  | -      | -   | ns   |

| tsds     | Data setup time for SC                    |                | 0   | -      | -   | ns   |

| tsdh     | Data hold time for SC                     | CDE = VIL      | 30  | -      | -   | ns   |

| tsw      | SC setup for WE                           |                | 50  | -      | -   | ns   |

| tscs     | SC setup for CE                           |                | 0   | -      | -   | ns   |

| tschw    | SC hold time for WE                       |                | 20  | -      | -   | ns   |

| tCE      | CE to output delay                        |                | -   | -      | 120 | ns   |

| toE      | OE to output delay                        |                | -   | -      | 60  | ns   |

| tDF 1)   | OE high to output float                   |                | -   | -      | 40  | ns   |

| trp      | RES to CE setup time                      |                | 1   | -      | -   | ms   |

Notes: 1. tDF is a time after which the DQ pins become open.

## **MITSUBISHI LSIs**

# M5M29F25611VP

MORE THAN 16,057 SECTORS (271,299,072 BITS) CMOS 3.3V-ONLY SERIAL READ FLASH MEMORY

AC Characteristics (for Erase,program,ID read,status register read , data recovery read and data recovery write.) (Vcc = 3.0V to 3.6V, Ta = 0 to +70°C)

### **Test Conditions**

• Input pulse levels : 0.4V/2.4V

• Input pulse levels for RES: 0.2V/Vcc - 0.2V

Input rise and fall times: 5ns

Output load: 1 TTL gate + 100pF (Including scope and jig.)

• Reference levels for measuring timing: 0.8V, 1.8V

| Courants and | narameter                                 | Took oon diking |     | Limits |     | Unit |

|--------------|-------------------------------------------|-----------------|-----|--------|-----|------|

| Symbol       | parameter                                 | Test condition  | Min | Тур    | Max | Unit |

| tcds         | CDE setup time for WE                     |                 | 0   | -      | -   | ns   |

| tcdh         | CDE hold time for WE                      |                 | 20  | -      | -   | ns   |

| tcdss        | CDE setup time for SC                     |                 | 1.5 | -      | -   | μs   |

| tcdsh        | CDE hold time for SC                      |                 | 30  | -      | -   | ns   |

| trdy         | Next cycle ready time                     |                 | 0   | -      | -   | ns   |

| tcdoh        | CDE to OE hold time                       |                 | 50  | -      | -   | ns   |

| tCDAC        | CDE to output delay                       |                 | -   | -      | 50  | ns   |

| tCDF         | CDE to output invalid                     |                 | 0   | -      | 100 | ns   |

| tcos         | CE setup time for OE                      |                 | 0   | -      | -   | ns   |

| tсон         | CE hold time for OE                       |                 | 0   | -      | -   | ns   |

| tcdos        | CDE to OE setup time                      |                 | 20  | -      | -   | ns   |

| toes         | OE setup time for SC                      |                 | 0   | -      | -   | ns   |

| toel         | OE low to output low-z                    |                 | 0   | -      | 40  | ns   |

| tsac         | SC to output delay                        |                 | -   | -      | 50  | ns   |

| tsH          | SC to output hold                         |                 | 15  | -      | -   | ns   |

| trs          | R/B setup for SC                          |                 | 200 | -      | -   | ns   |

| tcwн         | CE hold time for WE                       |                 | 1   | -      | -   | μs   |

| tcwhr        | CE hold time for WE on Recovery Read Mode |                 | 2   | -      | -   | μs   |

| twwн         | WE hold time for WE                       |                 | 1   | -      | -   | μs   |

MORE THAN 16,057 SECTORS (271,299,072 BITS) CMOS 3.3V-ONLY SERIAL READ FLASH MEMORY

Erase and Status Data Polling Timing Waveforms (Sector Erase)

Note: 1. Any commands, including reset command FFH, cannot be input while R/B outputs a Vol.

2. The status returns to the Standby or the Output disable after  $R/\overline{B}$  returns to HighZ.

MORE THAN 16,057 SECTORS (271,299,072 BITS) CMOS 3.3V-ONLY SERIAL READ FLASH MEMORY

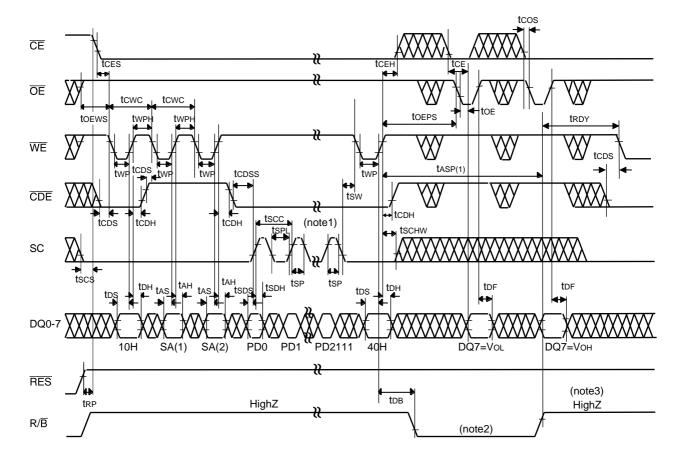

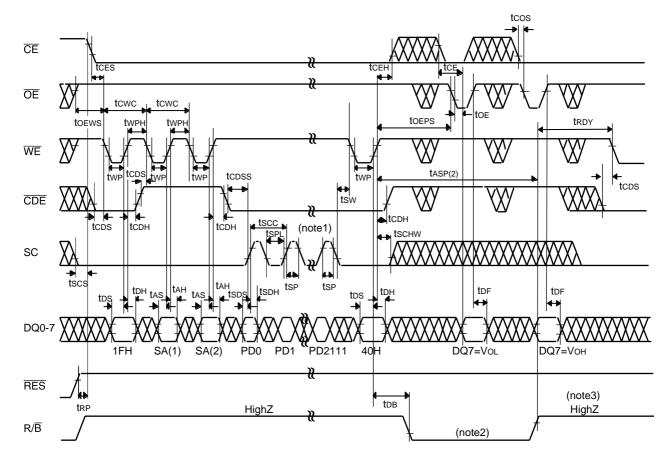

## Program(1) and Status Data Polling Timing Waveforms

Notes: 1. The programming operation is not guaranteed when the number of the SC pulse exceeds 2112.

- 2. Any commands, including reset command FFH, cannot be input while  $R/\overline{B}$  is Vol.

- 3. The status returns to the Standby or the Output disable after  $R/\overline{B}$  returns to HighZ.

- 4. By using program(1), data can be programmed additionally for each sector before erase.

MORE THAN 16,057 SECTORS (271,299,072 BITS) CMOS 3.3V-ONLY SERIAL READ FLASH MEMORY

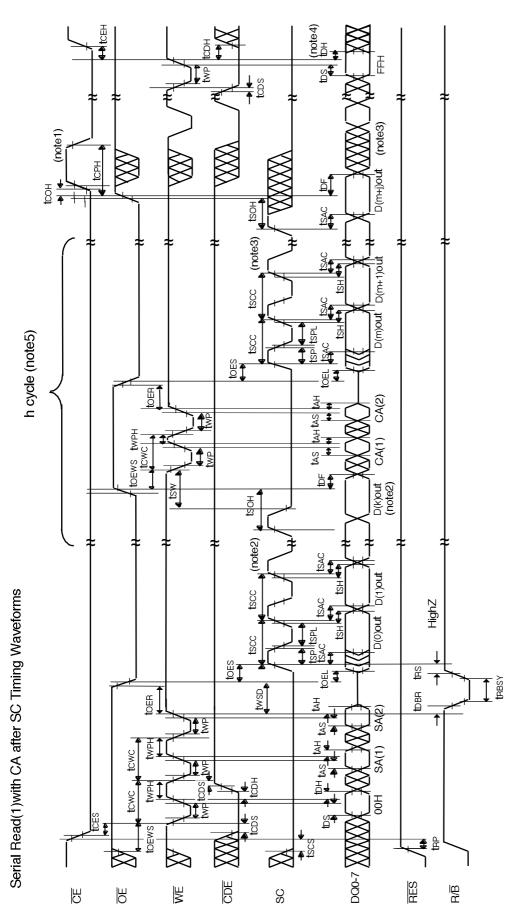

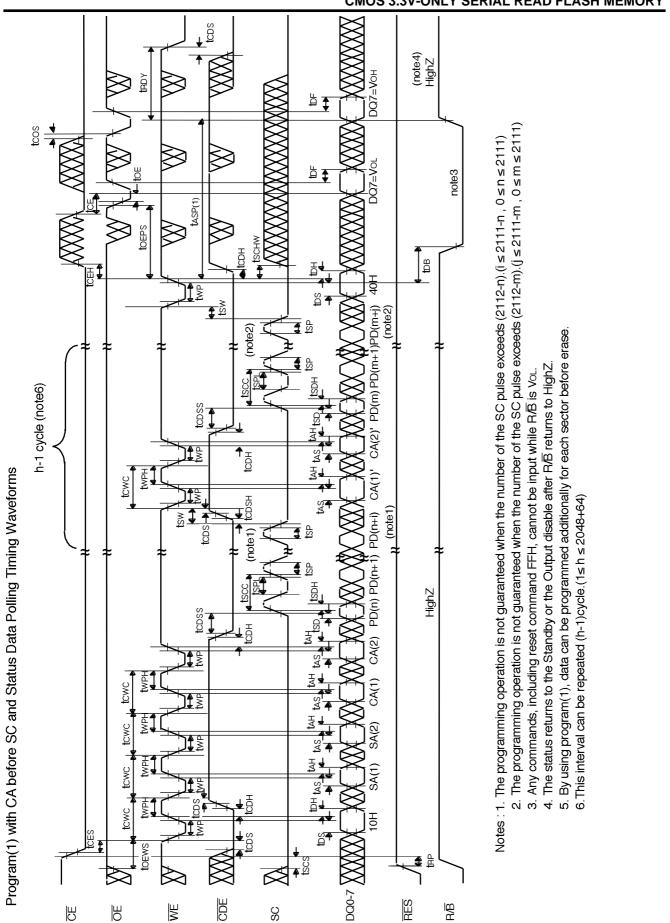

# MORE THAN 16,057 SECTORS (271,299,072 BITS) CMOS 3.3V-ONLY SERIAL READ FLASH MEMORY

Notes : 1. The programming operation is not guaranteed when the number of the SC pulse exceeds 2112.(0 ≤ k ≤ 2111)

- 2. The programming operation is not guaranteed when the number of the SC pulse exceeds (2112-m). (j ≤ 2111-m, 0 ≤ m ≤ 2111)

- 4. The status returns to the Standby or the Output disable after  $R\overline{B}$  returns to HighZ. 3. Any commands, including reset command FFH, cannot be input while R/B is Vol.

- 5. By using program(1), data can be programmed additionally each sector before erase.

6.This interval can be repeated h cycle. (1 ≤ h ≤ 2048+64)

MORE THAN 16,057 SECTORS (271,299,072 BITS) CMOS 3.3V-ONLY SERIAL READ FLASH MEMORY

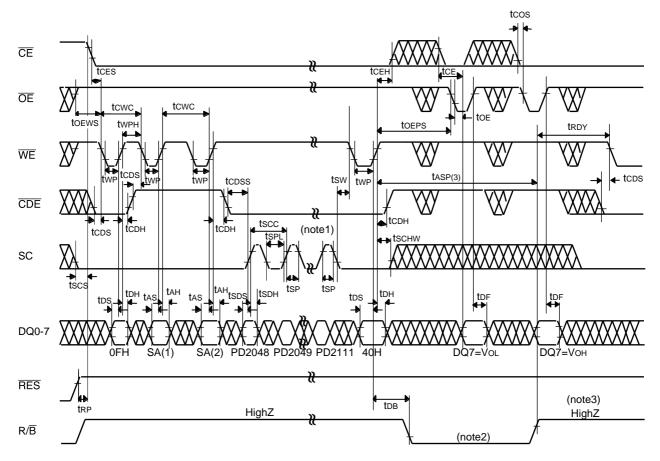

## Program(2) and Status Data Polling Timing Waveforms

Notes: 1. The programming operation is not guaranteed when the number of the SC pulse exceeds 2112.

- 2. Any commands, including reset command FFH, cannot be input while  $\mbox{R}/\overline{\mbox{B}}$  is  $\mbox{Vol.}$

- 3. The status returns to the Standby or the Output disable after  $R/\overline{B}$  returns to HighZ.

- 4. By using program(2), the programmed data of each sector must be erased before programming next data.

MORE THAN 16,057 SECTORS (271,299,072 BITS) CMOS 3.3V-ONLY SERIAL READ FLASH MEMORY

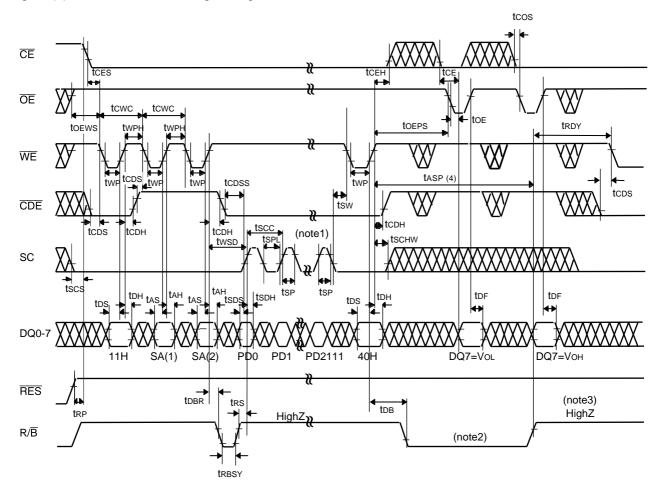

## Program(3) and Status Data Polling Timing Waveforms

Notes: 1. The programming operation is not guaranteed when the number of the SC pulse exceeds 64.

- 2. Any commands, including reset command FFH, cannot be input while  $R/\overline{B}$  is Vol.

- 3. The status returns to the Standby or the Output disable after  $R/\overline{B}$  returns to HighZ.

- 4. By using program(3), data can be programmed additionally for each sector before erase.

MORE THAN 16,057 SECTORS (271,299,072 BITS) CMOS 3.3V-ONLY SERIAL READ FLASH MEMORY

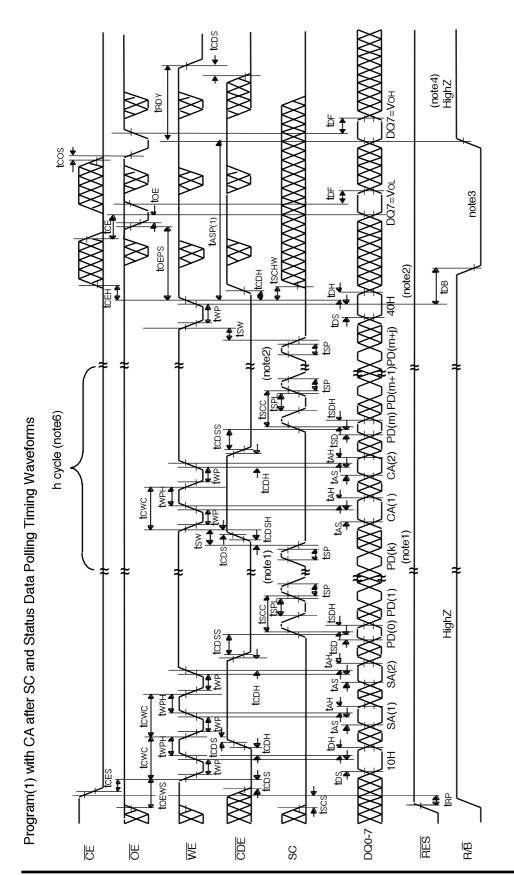

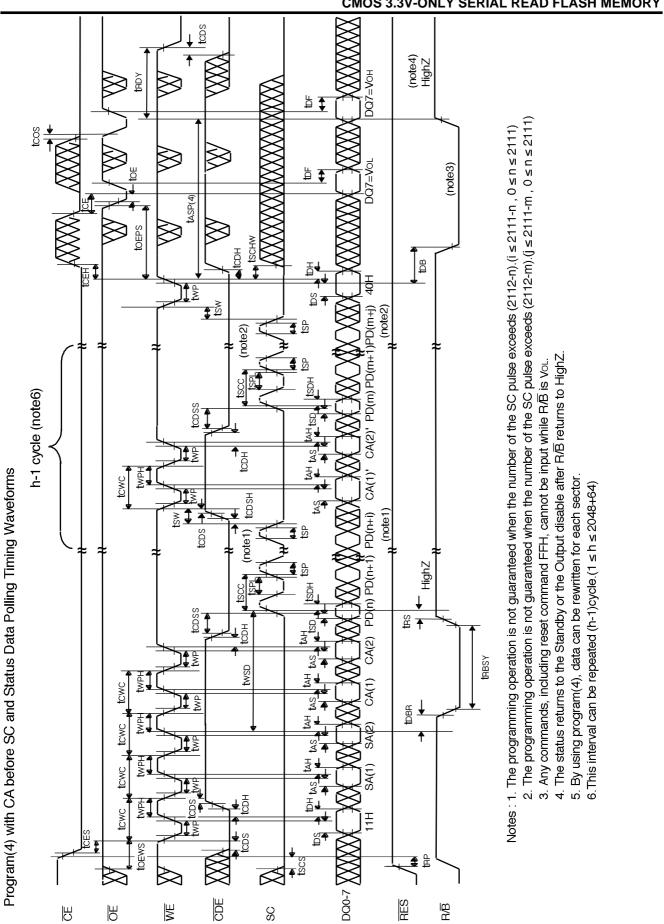

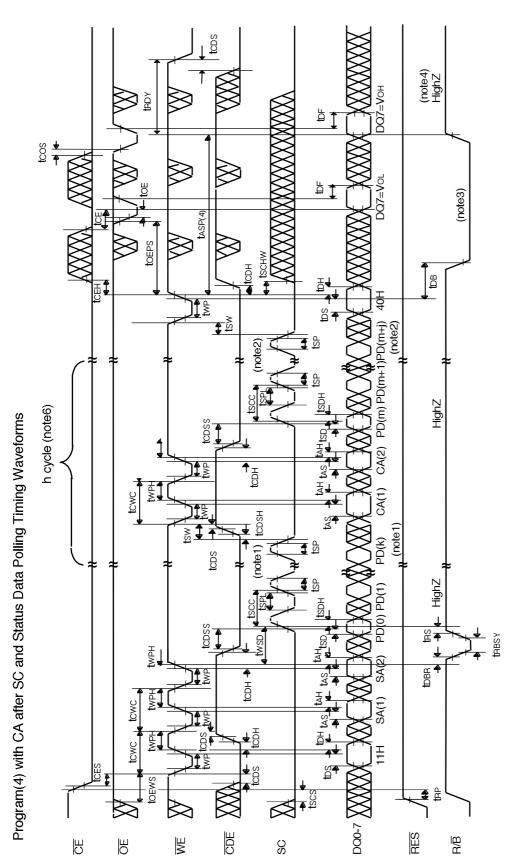

## Program(4) and Status Data Polling Timing Waveforms

Notes: 1. The programming operation is not guaranteed when the number of the SC pulse exceeds 2112.

- 2. Any commands, including reset command FFH, cannot be input while  $R/\overline{B}$  is Vol.

- 3. The status returns to the Standby or the Output disable after  $R/\overline{B}$  returns to HighZ.

- 4. By using program(4), data can be rewritten for each sector.

MORE THAN 16,057 SECTORS (271,299,072 BITS) CMOS 3.3V-ONLY SERIAL READ FLASH MEMORY

# MORE THAN 16,057 SECTORS (271,299,072 BITS) CMOS 3.3V-ONLY SERIAL READ FLASH MEMORY

Notes: 1. The programming operation is not guaranteed when the number of the SC pulse exceeds 2112. (0 sk s 2111)

- 2. The programming operation is not guaranteed when the number of the SC pulse exceeds (2112-m). (j ≤ 2111-m, 0 ≤ m ≤ 2111) 3. Any commands, including reset command FFH, cannot be input while R/B is Vol

- 4. The status returns to the Standby or the Output disable after R/B returns to HighZ.

- The state of the control of the contro

- 6. This interval can be repeated h cycle.(1 ≤ h ≤ 2048+64)

MORE THAN 16,057 SECTORS (271,299,072 BITS) CMOS 3.3V-ONLY SERIAL READ FLASH MEMORY

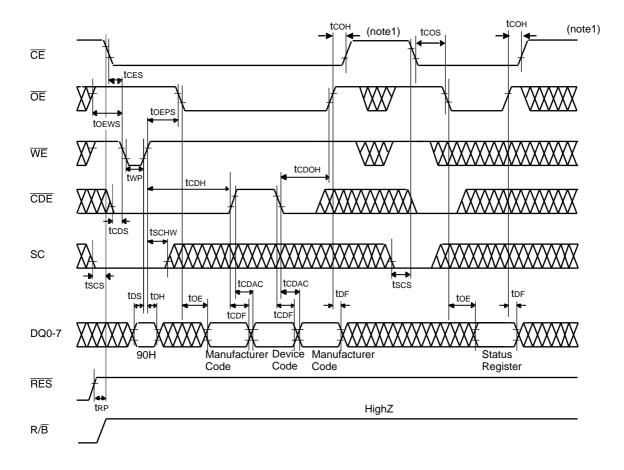

ID and Status Register Read Timing Waveforms

Note : 1. The status returns to the Standby at the rising edge of  $\overline{\text{CE}}$ .

MORE THAN 16,057 SECTORS (271,299,072 BITS) CMOS 3.3V-ONLY SERIAL READ FLASH MEMORY

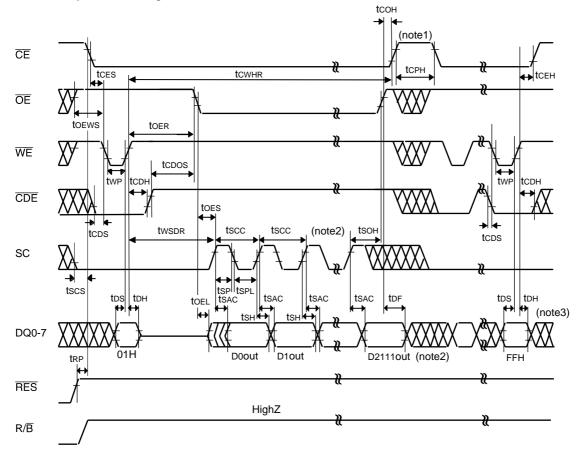

## Data Recovery Read Timing Waveforms

Note 1. The status returns to the Standby at the rising edge of  $\overline{\text{CE}}$ .

- 2. Output data is not valid after the number of the SC pulse exceeds 2112 and 64 in the Data Recovery Read mode.

- 3. The status can return to the Ready after the command FFH is input.

MORE THAN 16,057 SECTORS (271,299,072 BITS) CMOS 3.3V-ONLY SERIAL READ FLASH MEMORY

Note : 1. Any commands, including reset command FFH, cannot be input while  $R/\overline{B}$  outputs a Vol.

2. The status returns to the Standby or the Output disable after  $R/\overline{B}$  returns to HighZ.

MORE THAN 16,057 SECTORS (271,299,072 BITS) CMOS 3.3V-ONLY SERIAL READ FLASH MEMORY

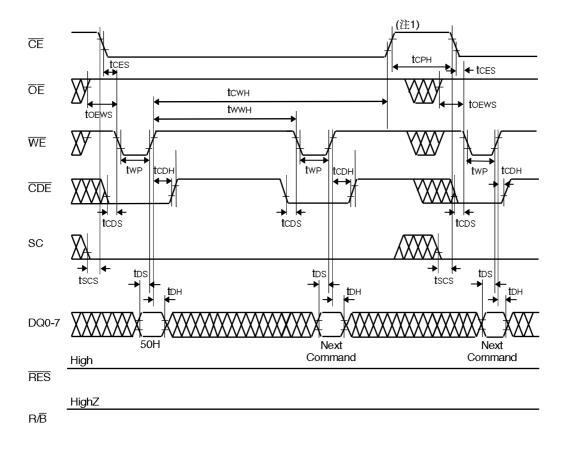

## Clear Status Register Timing Waveforms

Note 1. The status returns to the Standby at the rising edge of  $\overline{\text{CE}}$ .

MORE THAN 16,057 SECTORS (271,299,072 BITS) CMOS 3.3V-ONLY SERIAL READ FLASH MEMORY

## **Function Description**

### Status Register

The M5M29F25611 outputs the operation status data as follows: DQ7 pin outputs a Vol to indicate that the memory is in either erase or program operation. The level of DQ7 pin turns to a VoH when the operation finishes. DQ5 and DQ4 pins output Vols to indicate that the erase and program operations are successfully completed or not, respectively. If these pins output VoHs, it indicates that these operations have timed out. When these pins are monitored, DQ7 pin must turn to a VoH. To execute other erase and program operation, the status data must be cleared after a time out occurs. From DQ0 to DQ3 and DQ6 pins are reserved for future use. The pins output Vols and should be masked out during the status data read mode.

The function of the status register is summarized in the following table.

#### Table 1.

|     | Flag Definition | Definition                                                                  |  |  |

|-----|-----------------|-----------------------------------------------------------------------------|--|--|

| DQ7 | Ready/Busy      | "Voh" = Ready "Voh" = Busy                                                  |  |  |

| DQ6 | Reserved        | Outputs a VoL and should be masked out during the status data polling mode. |  |  |

| DQ5 | Erase Check     | "Voн" = Fail "Voь" = Pass                                                   |  |  |

| DQ4 | Program Check   | "Voн" = Fail "Voь" = Pass                                                   |  |  |

| DQ3 | Reserved        |                                                                             |  |  |

| DQ2 | Reserved        | Outputs a VoL and should be masked out during the status data polling mode. |  |  |

| DQ1 | Reserved        |                                                                             |  |  |

| DQ0 | Reserved        |                                                                             |  |  |

MORE THAN 16,057 SECTORS (271,299,072 BITS) CMOS 3.3V-ONLY SERIAL READ FLASH MEMORY

# **Notes**

## **Unusable Sector**

Initially, the M5M29F25611 contains unusable sectors. Due to the nature of the device architecture, the device can also be screened and tested for partial invalid sectors for selected systems that can utilize the devices.

1. Tested for partial invalid sectors. The usable sectors were programmed the following data.

| Column address | 820H | 821H | 822H | 823H | 824H | 825H |

|----------------|------|------|------|------|------|------|

| Data           | 1CH  | 71H  | C7H  | 1CH  | 71H  | C7H  |

2. No erase and program for the partial invalid sectors by the system.

| Item                       | Min          |

|----------------------------|--------------|

| Usable sectors (initially) | 16,057 (98%) |

## Enable High System Reliability

The device may fail during a program or erase operation due to program or erase cycle. The following architecture will enable high system reliability if a failure occurs.

- 1. Error in read: Error correction that more than 3 bit error correction per each sector read is required for data reliability.

- 2. Error in program or erase operation: The device may fail during a program or erase operation due to program or erase cycle. The status register indicates that the program and erase operations are successfully completed or not. After every program and erase operations, read status register to confirm the program and erase operations are successfully completed.

When the error happens in sector, try to reprogram the data into another sector. Then, prevent further system access to sector that error happens. Typically, recommended number of a spare sectors are 1.8% within initial usable 16,057 sectors by each device. If the number of failed sectors exceed the number of the spare sectors, usable data area in the device decreases. In the case of reprogramming to the spare sector, do not use the data from the failed sector. The reprogram data must be the data reloaded from outer buffer, or use the Data recovery read mode or the Data recovery write mode (see the "Mode Description"). To avoid consecutive sector failurechoose addresses of spare sectors as far as possible from the failed sectors.

3. The write/erase endurance is  $1 \times 10^5$  cycles.

MORE THAN 16,057 SECTORS (271,299,072 BITS) CMOS 3.3V-ONLY SERIAL READ FLASH MEMORY

## Keep safety first in your circuit designs!

•Mitsubishi Electric Corporation puts the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to personal injury, fire or property damage. Remember to give due consideration to safety when making your circuit designs, with appropriate measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of non-flammable material or (iii) prevention against any malfunction or mishap.

### Notes regarding these materials

- These materials are intended as a reference to assist our customers in the selection of the Mitsubishi semiconductor product best suited to the customer's application; they do not convey any license under any intellectual property rights, or any other rights, belonging to Mitsubishi Electric Corporation or a third party.

- Mitsubishi Electric Corporation assumes no responsibility for any damage, or infringement of any third-party's rights, originating in the use of any product data, diagrams, charts, programs, algorithms, or circuit application examples contained in these materials.

- All information contained in these materials, including product data, diagrams, charts, programs and algorithms represents information on products at the time of publication of these materials, and are subject to change by Mitsubishi Electric Corporation without notice due to product improvements or other reasons. It is therefore recommended that customers contact Mitsubishi Electric Corporation or an authorized Mitsubishi Semiconductor product distributor for the latest product information before purchasing a product listed herein.

The information described here may contain technical inaccuracies or typographical errors. Mitsubishi Electric Corporation assumes no responsibility for any damage, liability, or other loss rising from these inaccuracies or errors.

Please also pay attention to information published by Mitsubishi Electric Corporation by various means, including the Mitsubishi Semiconductor home page (http://www.mitsubishichips.com).

- When using any or all of the information contained in these materials, including product data, diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a total system before making a final decision on the applicability of the information and products. Mitsubishi Electric Corporation assumes no responsibility for any damage, liability or other loss resulting from the information contained herein.

- Mitsubishi Electric Corporation semiconductors are not designed or manufactured for use in a device or system that is used under circumstances in which human life is potentially at stake. Please contact Mitsubishi Electric Corporation or an authorized Mitsubishi Semiconductor product distributor when considering the use of a product contained herein for any specific purposes, such as apparatus or systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater use.

- ●The prior written approval of Mitsubishi Electric Corporation is necessary to reprint or reproduce in whole or in part these materials.

- ●If these products or technologies are subject to the Japanese export control restrictions, they must be exported under a license from the Japanese government and cannot be imported into a country other than the approved destination.

Any diversion or reexport contrary to the export control laws and regulations of Japan and/or the country of destination is prohibited.

● Please contact Mitsubishi Electric Corporation or an authorized Mitsubishi Semiconductor product distributor for further details on these materials or the products contained therein.