# *82C82*

March 1997

# Features

- Full Eight-Bit Parallel Latching Buffer

- Bipolar 8282 Compatible

- Three-State Noninverting Outputs

- Propagation Delay ..... 35ns Max.

- Gated Inputs:

- Reduce Operating Power

- Eliminate the Need for Pull-Up Resistors

- Single 5V Power Supply

- Low Power Operation ..... ICCSB = 10μA

- Operating Temperature Ranges

- C82C82 .....0°C to +70°C

# **CMOS Octal Latching Bus Driver**

# Description

The Intersil 82C82 is a high performance CMOS Octal Latching Buffer manufactured using a self-aligned silicon gate CMOS process (Scaled SAJI IV). The 82C82 provides an eight-bit parallel latch/buffer in a 20 pin package. The active high strobe (STB) input allows transparent transfer of data and latches data on the negative transition of this signal. The active low output enable ( $\overline{OE}$ ) permits simple interface to state-of-the-art microprocessor systems.

# **Ordering Information**

| PART NUMBER | TEMP. RANGE                              | PACKAGE      | PKG. NO. |

|-------------|------------------------------------------|--------------|----------|

| CP82C82     | 0 <sup>o</sup> C to +70 <sup>o</sup> C   | 20 Ld PDIP   | E20.3    |

| IP82C82     | -40 <sup>o</sup> C to +85 <sup>o</sup> C |              |          |

| CS82C82     | 0 <sup>o</sup> C to +70 <sup>o</sup> C   | 20 Ld PLCC   | N20.35   |

| IS82C82     | -40°C to +85°C                           |              |          |

| CD82C82     | 0 <sup>o</sup> C to +70 <sup>o</sup> C   | 20 Ld CERDIP | F20.3    |

| ID82C82     | -40 <sup>o</sup> C to +85 <sup>o</sup> C |              |          |

| MD82C82/B   | -55°C to +125°C                          |              |          |

| 8406701RA   | 1                                        | SMD #        |          |

| MR82C82/B   | -55°C to +125°C                          | 20 Pad CLCC  | J20.A    |

| 84067012A   |                                          | SMD #        |          |

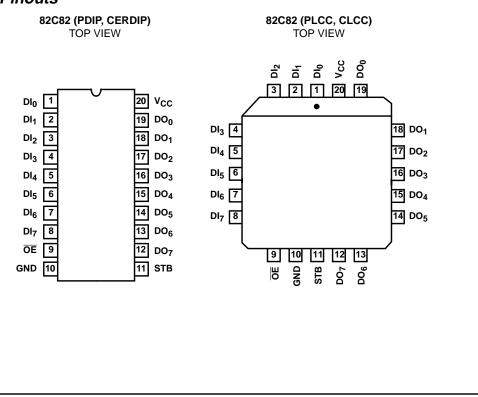

# **Pinouts**

#

| STB                                                                                                                                       | OE              | DI        | DO   |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------|------|--|--|--|

| Х                                                                                                                                         | Н               | Х         | Hi-Z |  |  |  |

| Н                                                                                                                                         | L               | L         | L    |  |  |  |

| Н                                                                                                                                         | L               | Н         | Н    |  |  |  |

| $\downarrow$                                                                                                                              | L               | Х         | †    |  |  |  |

| H = Logic One<br>L = Logic Zero<br>X = Don't Care<br>† = Latched to Value of Last<br>Data<br>Hi-Z = High Impedance<br>↓ = Neg. Transition |                 |           |      |  |  |  |

| PIN NAMES                                                                                                                                 |                 |           |      |  |  |  |

| PIN                                                                                                                                       | PIN DESCRIPTION |           |      |  |  |  |

|                                                                                                                                           |                 | ata Innut | Dine |  |  |  |

| PIN                              | DESCRIPTION                 |

|----------------------------------|-----------------------------|

| DI <sub>0</sub> -DI <sub>7</sub> | Data Input Pins             |

| DO0-DO7                          | Data Output Pins            |

| STB                              | Active High Strobe          |

| ŌĒ                               | Active Low Output<br>Enable |

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures. http://www.intersil.com or 407-727-9207 | Copyright © Intersil Corporation 1999 4-274

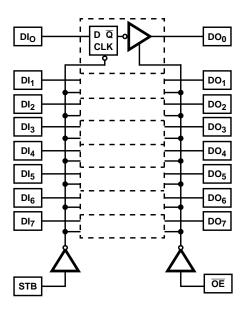

### Functional Diagram

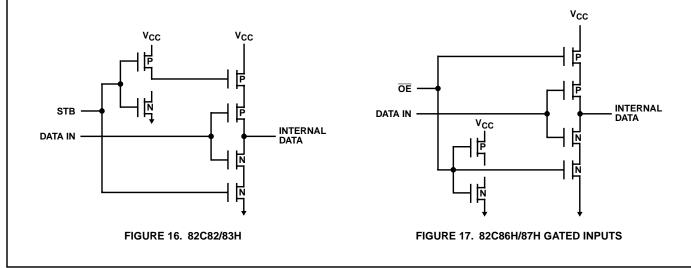

# Gated Inputs

During normal system operation of a latch, signals on the bus at the device inputs will become high impedance or make transitions unrelated to the operation of the latch. These unrelated input transitions switch the input circuitry and typically cause an increase in power dissipation in CMOS devices by creating a low resistance path between V<sub>CC</sub> and GND when the signal is at or near the input switching threshold. Additionally, if the driving signal becomes high impedance ("float" condition), it could create an indeterminate logic state at the input and cause a disruption in device operation.

The Intersil 82C8X Series of bus drivers eliminates these conditions by turning off data inputs when data is latched (STB = logic zero for the 82C82/83H) and when the device is disabled ( $\overline{OE}$  = logic one for 82C86H/87H). These gated inputs disconnect the input circuitry from the V<sub>CC</sub> and ground power supply pins by turning off the upper P-channel and lower N-channel (see Figures 1, 2). No new current flow from V<sub>CC</sub> to GND occurs during input transitions and invalid logic states from floating inputs are not transmitted. The next stage is held to a valid logic level internal to the device.

DC input voltage levels can also cause an increase in ICC if these input levels approach the minimum  $V_{IH}$  or maximum  $V_{IL}$  conditions. This is due to the operation of the input circuitry in its linear operating region (partially conducting state). The 82C8X series gated inputs mean that this condition will occur only during the time the device is in the trans parent mode (STB = logic one). ICC remains below the maximum ICC standby specification of I0mA during the time inputs are disabled, thereby, greatly reducing the average power dissipation of the 82C8X series devices

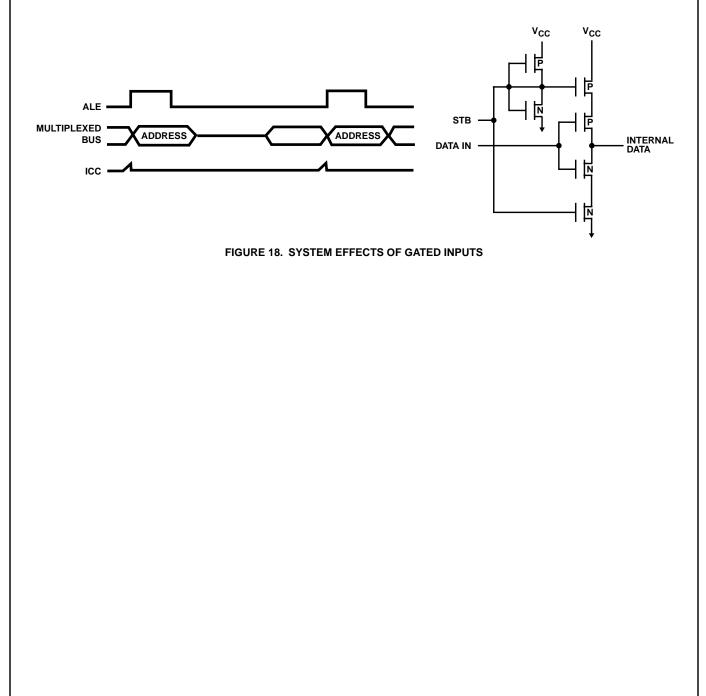

#### Typical 82C82 System Example

In a typical 80C86/88 system, the 82C82 is used to latch multiplexed addresses and the STB input is driven by ALE (Address Latch Enable) (see Figure 3). The high pulse width of ALE is approximately 100ns with a bus cycle time of 800ns (80C86/88 at 5MHz). The 82C82 inputs are active only 12.5% of the bus cycle time. Average power dissipation related to input transitioning is reduced by this factor also.

# Application Information

#### **Decoupling Capacitors**

The transient current required to charge and discharge the 300pF load capacitance specified in the 82C82 data sheet is determined by:

$$I = C_1 (dv/dt)$$

(EQ. 1)

Assuming that all outputs change state at the same time and that dv/dt is constant;

$$I = C_{L}$$

(EQ. 2)

$$\frac{(V_{CC} \times 80\%)}{tR/tF}$$

(EQ. 3)

where tR = 20ns, V<sub>CC</sub> = 5.0V, C<sub>L</sub> = 300pF on each of eight outputs.

$I = (8 \times 300 \times 10^{-12}) \times (5.0 \text{V} \times 0.8) / (20 \times 10^{-9}) = 480 \text{mA} \quad (EQ. 4)$

This current spike may cause a large negative voltage spike on V<sub>CC</sub>, which could cause improper operation of the device. To filter out this noise, it is recommended that a  $0.1\mu F$  ceramic disc decoupling capacitor be placed between V<sub>CC</sub> and GND at each device, with placement being as near to the device as possible.

#### **Absolute Maximum Ratings**

| Supply Voltage                  | <b>+</b> 8.0V                   |

|---------------------------------|---------------------------------|

| Input, Output or I/O VoltageGNE | 0-0.5V to V <sub>CC</sub> +0.5V |

| ESD Classification              | Class 1                         |

#### **Operating Conditions**

| Operating Voltage Range +4.5V to +5.5V |

|----------------------------------------|

| Operating Temperature Range            |

| C82C82                                 |

| I82C8240°C to +85°C                    |

| M82C8255°C to +125°C                   |

#### **Thermal Information**

| Thermal Resistance (Typical)   CERDIP.   CLCC.   PDIP   PLCC.   Storage Temperature Range.   Maximum Junction Temperature | - | <sup>θ</sup> JC<br>18 <sup>o</sup> C/W<br>22 <sup>o</sup> C/W<br>N/A<br>N/A<br><sup>o</sup> C to +150 <sup>o</sup> C |

|---------------------------------------------------------------------------------------------------------------------------|---|----------------------------------------------------------------------------------------------------------------------|

| Ceramic Package<br>Plastic Package<br>Minimum Lead Temperature (Soldering 10<br>(PLCC Lead Tips Only)                     |   | +150 <sup>0</sup> C                                                                                                  |

#### **Die Characteristics**

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### DC Electrical Specifications $V_{CC} = 5.0V \pm 10\%$ ;

$\begin{array}{l} T_A = 0^0 C \ to \ +70^0 C \ (C82C82); \\ T_A = -40^0 C \ to \ +85^0 C \ (I82C82); \\ T_A = -55^0 C \ to \ +125^0 C \ (M82C82) \end{array}$

| SYMBOL          | PARAMETER                         | MIN                   | МАХ  | UNITS  | TEST CONDITIONS                                                                     |

|-----------------|-----------------------------------|-----------------------|------|--------|-------------------------------------------------------------------------------------|

| V <sub>IH</sub> | Logical One Input Voltage         | 2.0                   | -    | V      | C82C82, I82C82 (Note 1)                                                             |

|                 |                                   | 2.2                   | -    | V      | M82C82 (Note 1)                                                                     |

| V <sub>IL</sub> | Logical Zero Input Voltage        | -                     | 0.8  | V      |                                                                                     |

| V <sub>OH</sub> | Logical One Output Voltage        | 2.9                   | -    | V      | $I_{OH} = -8mA, \overline{OE} = GND$                                                |

|                 |                                   | V <sub>CC</sub> -0.4V | -    | V      | $I_{OH} = -100\mu A, \overline{OE} = GND$                                           |

| V <sub>OL</sub> | Logical Zero Output Voltage       | -                     | 0.4  | V      | $I_{OL} = 8mA, \overline{OE} = GND$                                                 |

| II              | Input Leakage Current             | -1.0                  | 1.0  | μA     | $V_{IN} = GND \text{ or } V_{CC}, DIP Pins 1-9, 11$                                 |

| IO              | Output Leakage Current            | -10.0                 | 10.0 | μΑ     | $V_{O} = GND \text{ or } V_{CC}, \overline{OE} \ge V_{CC} - 0.5V$<br>DIP Pins 12-19 |

| ICCSB           | Standby Power Supply Cur-<br>rent | -                     | 10   | μΑ     | $V_{IN} = V_{CC}$ or GND, $V_{CC} = 5.5V$ , Outputs Open                            |

| ICCOP           | Operating Power Supply<br>Current | -                     | 1    | mA/MHz | $T_A = +25^{\circ}C$ , $V_{CC} = 5V$ , Typical (See Note 2)                         |

NOTES:

1.  $V_{IH}$  is measured by applying a pulse of magnitude =  $V_{IH}$  min to one data input at a time and checking the corresponding device output for a valid logical "1" during valid input high time. Control pins (STB, OE) are tested separately with all device data input pins at V<sub>CC</sub> -0.4.

2. Typical ICCOP = 1mA/MHz of STB cycle time. (Example: 5MHz μP, ALE = 1.25MHz, ICCOP = 1.25mA).

#### **Capacitance** $T_A = +25^{\circ}C$

| SYMBOL           | PARAMETER          | TYPICAL | UNITS | TEST CONDITIONS                                               |

|------------------|--------------------|---------|-------|---------------------------------------------------------------|

| C <sub>IN</sub>  | Input Capacitance  | 13      | pF    | Freq = 1MHz, all measurements are<br>referenced to device GND |

| C <sub>OUT</sub> | Output Capacitance | 20      | pF    |                                                               |

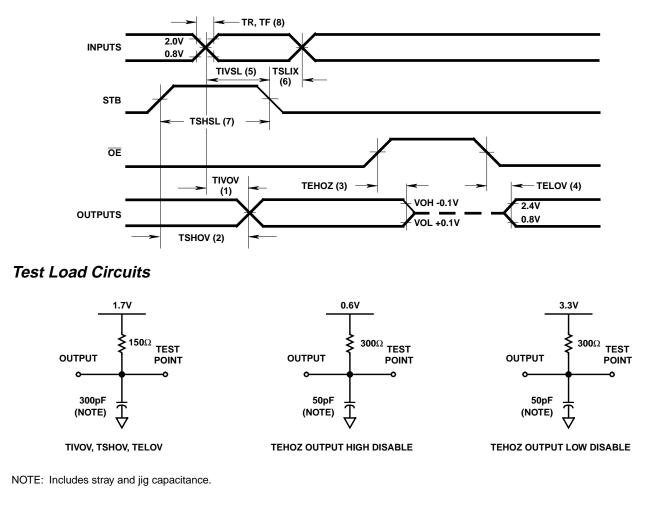

| $ \begin{array}{llllllllllllllllllllllllllllllllllll$ |                                   |     |     |       |                 |  |

|-------------------------------------------------------|-----------------------------------|-----|-----|-------|-----------------|--|

| SYMBOL                                                | PARAMETER                         | MIN | MAX | UNITS | TEST CONDITIONS |  |

| (1) TIVOV                                             | Propagation Delay Input to Output | -   | 35  | ns    | Notes 2, 3      |  |

| (2) TSHOV                                             | Propagation Delay STB to Output   | -   | 55  | ns    | Notes 2, 3      |  |

| (3) TEHOZ                                             | Output Disable Time               | -   | 35  | ns    | Notes 2, 3      |  |

| (4) TELOV                                             | Output Enable Time                | -   | 50  | ns    | Notes 2, 3      |  |

| (5) TIVSL                                             | Input to STB Setup Time           | 0   | -   | ns    | Notes 2, 3      |  |

| (6) TSLIX                                             | Input to STB Hold Time            | 25  | -   | ns    | Notes 2, 3      |  |

| (7) TSHSL                                             | STB High Time                     | 25  | -   | ns    | Notes 2, 3      |  |

| (8) TR, TF                                            | Input Rise/Fall Times             | -   | 20  | ns    | Notes 2, 3      |  |

NOTES:

1. Output load capacitance is rated at 300pF for ceramic and plastic packages.

2. All AC parameters tested as per test circuits and definitions below. Input rise and fall times are driven at 1ns/V.

3. Input test signals must switch between V\_{IL} - 0.4V and V\_{IH} +0.4V.

# Timing Waveforms

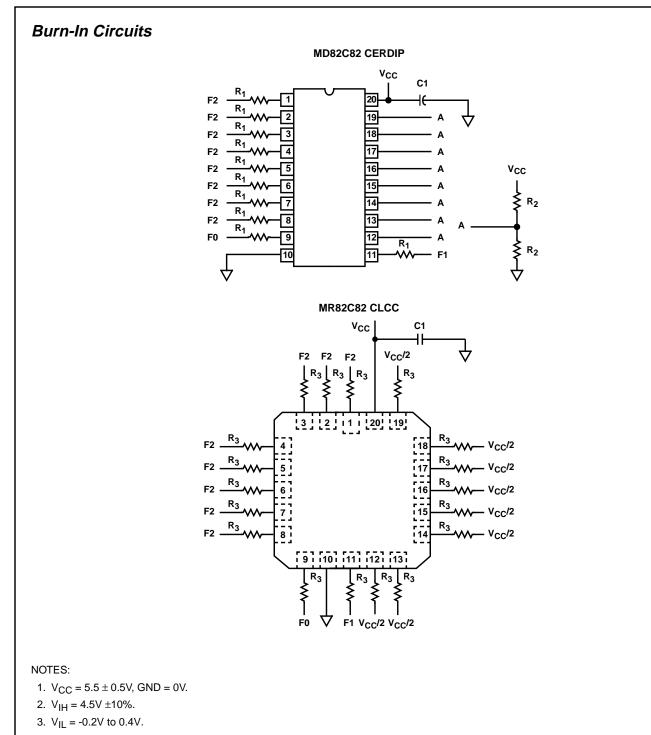

- 4.  $R_1 = 47k\Omega \pm 5\%$ .

- 5.  $R_2 = 2.0 k\Omega \pm 5\%$ .

- 6.  $R_3 = 4.2k\Omega \pm 5\%$ .

- 7.  $R_4 = 470 k\Omega \pm 5\%$ .

- 8.  $C_1 = 0.01 \mu F$  minimum.

- 9.  $F_0 = 100 \text{kHz} \pm 10\%$ .

- 10.  $F_1 = F_0/_2$ ,  $F_2 = F_1/_2$ .

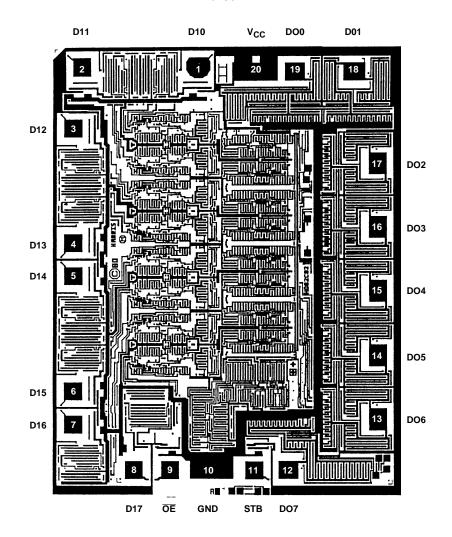

# **Die Characteristics**

#### **DIE DIMENSIONS:**

118.1 x 92.1 x 19 ±1mils

# METALLIZATION:

Type: Si - Al Thickness: 11kÅ ±1kÅ

# Metallization Mask Layout

GLASSIVATION: Type: SiO<sub>2</sub>

Thickness: 8kÅ ±1kÅ

WORST CASE CURRENT DENSITY: 2.00 x 10<sup>5</sup> A/cm<sup>2</sup>

82C82

#### All Intersil semiconductor products are manufactured, assembled and tested under ISO9000 quality systems certification.

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see web site http://www.intersil.com