# **PWM Power Control with Interference Suppression**

# Description

The U6083B is a PWM IC in bipolar technology for the control of an N-channel power MOSFET used as a high

# Features

- Pulse-width modulation up to 2 kHz clock frequency

- Protection against short circuit, load dump over-voltage and reverse V<sub>S</sub>

- Duty cycle 18 to 100% continuously

- Internally reduced pulse slope of lamp's voltage

side switch. The IC is ideal for use in the brightness control (dimming) of lamps e.g., in dashboard applications.

- Interference and damage protection according to VDE 0839 and ISO/TR 7637/1.

- Charge pump noise suppressed

- Ground wire breakage protection

# **Ordering Information**

| Extended Type Number | Package | Remarks |

|----------------------|---------|---------|

| U6083B               | DIP8    |         |

### **Block Diagram**

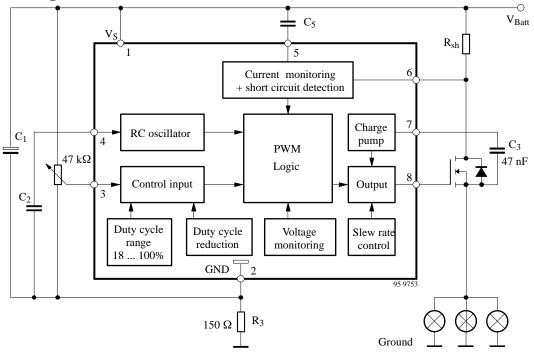

Figure 1. Block diagram with external circuit

**TELEFUNKEN Semiconductors** Rev. A1, 14-Feb-97

# **Pin Description**

# **Functional Description**

#### Pin 1, Supply Voltage, V<sub>s</sub> or V<sub>Batt</sub>

#### **Overvoltage Detection**

#### Stage 1:

If overvoltages  $V_{Batt} > 20 V$  (typ.) occur, the external transistor is switched off and switched on again at  $V_{Batt} < 18.5 V$  (hysteresis).

#### Stage 2:

If  $V_{Batt} > 28.5 V$  (typ), the voltage limitation of the IC is reduced from  $V_S = 26$  V to 20 V. The gate of the external transistor remains at the potential of the IC ground, thus producing voltage sharing between FET and lamps in the event of overvoltage pulses occuring (e.g., load dump). The short-circuit protection is not in operation. At VBatt approx. < 23 V, the overvoltage detection stage 2 is switched off. Thus during overvoltage detection stage 2 the lamp voltage V<sub>lamp</sub> is calculated to :

$V_{Lamp} = V_{Batt} - V_S - V_{GS}$

$V_S$  = Supply voltage of the IC at overvoltage detection stage 2

$V_{GS} = Gate - source voltage of the FET$

#### **Undervoltage Detection**

In the event of voltages of approximately  $V_{Batt} < 5.0$  V, the external FET is switched off and the latch for shortcircuit detection is reset.

A hysteresis ensures that the FET is switched on again at approximately  $V_{Batt} \ge 5.4$  V.

#### Pin 2, GND

#### **Ground-Wire Breakage**

To protect the FET in the case of ground-wire breakage, a 1 M $\Omega$  resistor between gate and source it is recommended to provide proper switch-off conditions.

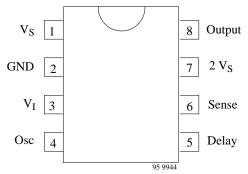

| Pin | Symbol           | Function                       |

|-----|------------------|--------------------------------|

| 1   | VS               | Supply voltage V <sub>S</sub>  |

| 2   | GND              | IC ground                      |

| 3   | VI               | Control input (duty cycle)     |

| 4   | Osc              | Oscillator                     |

| 5   | Delay            | Short circuit protection delay |

| 6   | Sense            | Current sensing                |

| 7   | 2 V <sub>S</sub> | Voltage doubler                |

| 8   | Output           | Output                         |

#### **Pin 3, Control Input**

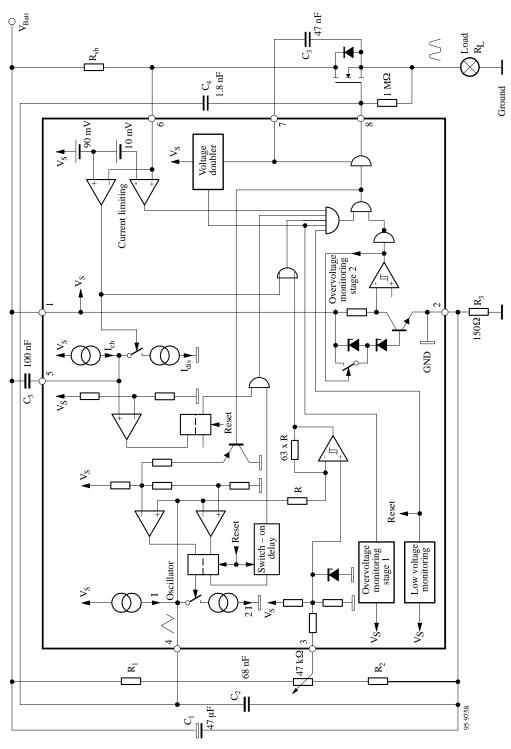

The pulse width is controlled by means of an external potentiometer (47 k $\Omega$ ). The characteristic (angle of rotation/duty cycle) is linear. The duty cycle can be varied from 18 to 100%. It is possible to further restrict the duty cycle with the resistors  $R_1$  and  $R_2$  (see figure 3).

In order to reduce the power dissipation of the FET and to increase the lifetime of the lamps, the IC automatically reduces the maximum duty cycle at Pin 8 if the supply voltage exceeds  $V_2 = 13$  V. Pin 3 is protected against short-circuit to  $V_{Batt}$  and ground ( $V_{Batt} \leq 16.5$  V).

#### Pin 4, Oscillator

The oscillator determines the frequency of the output voltage. This is defined by an external capacitor,  $C_2$ . It is charged with a constant current, I, until the upper switching threshold is reached. A second current source is then activated which taps a double current,  $2 \times I$ , from the charging current. The capacitor,  $C_2$ , is thus discharged at the current, I, until the lower switching threshold is reached. The second source is then switched off again and the procedure starts once more.

#### **Example for Oscillator Frequency Calculation:**

Switching thresholds  $V_{T100}$  = High switching threshold (100% duty cycle)  $V_{T100} = V_S \times \alpha_1 = (V_{Batt} - I_S \times R_3) \times \alpha_1$  $V_{T<100}$  = High switching threshold (< 100% duty cycle)  $V_{T<100} = V_S \times \alpha_2 = (V_{Batt} - I_S \times R_3) \times \alpha_2$ V<sub>TL</sub> = Low switching threshold  $V_{TL} = V_S \times \alpha_3 = (V_{Batt} - I_S \times R_3) \times \alpha_3$ whereas  $\alpha_1$ ,  $\alpha_2$  and  $\alpha_3$  are fixed constant.

#### **Calculation Example**

The above mentioned threshold voltages are calculated for the following values given in the data sheet.

$V_{Batt} = 12 \text{ V}, I_S = 4 \text{ mA}, R_3 = 150 \Omega$ ,  $\alpha_1 = 0.7, \, \alpha_2 = 0.67 \text{ and } \alpha_3 = 0.28.$

$V_{T100} = (12 V - 4 mA \times 150 \Omega) \times 0.7 \approx 8 V$

$V_{T<100} = 11.4 \ V \ \times \ 0.67 = 7.6 \ V$

$V_{TL} = 11.4 \ V \ \times \ 0.28 = 3.2 \ V$

#### **Oscillator Frequency**

3 cases have to be distinguished

1)  $f_1$  for duty cycle = 100%, no slope reduction with capacitor C<sub>4</sub> (see figure 3)

$$f_1 = \frac{I_{osc}}{2 \times (V_{T100} - V_{TL}) \times C_2} , \text{ whereas } C_2 = 68 \text{ nF}$$

$$I_{osc} = 45 \text{ } \mu\text{A}$$

$f_1 = \ldots = 75 \ Hz$

2)  $f_2$  for duty cycle < 100%, no slope reduction with capacitor C<sub>4</sub>

For a duty cycle of less than 100%, the oscillator frequency, f, is as follows:

$$f_2 = \frac{I_{osc}}{2 \times (V_{T<100} - V_{TL}) \times C_2} \text{ , whereas } C_2 = 68 \text{ nF}$$

$$I_{osc} = 45 \text{ } \mu\text{A}$$

$$f_2 = ... = 69Hz$$

3)  $f_3$  with duty cycle < 100% with slope reduction capacitor C<sub>4</sub> (see page 3 "Output Slope Control")

$$f_{3} = \frac{I_{osc}}{2 \times (V_{T<100} - V_{TL}) \times C_{2} + 2V_{Batt} \times C_{4}}$$

whereas  $C_{4} = 68 \text{ nF}$

whereas  $C_2 = 68 \text{ nF}$

$$C_4 = 1.8 \ \text{nF}$$

$$I_{osc} = 45 \ \mu\text{A}$$

$$f_3 = ... = 70 \ \text{Hz}$$

By selecting different values of  $C_2$  and  $C_4$ , it is possible to have a range of oscillator frequency, f, from 10 to 2000 Hz as shown in the data sheet.

#### **Output Slope Control**

The slope of the lamp voltage is internally limited to reduce radio interference, by limitation of the voltage gain of the PWM comparator.

Thus the voltage rise on the lamp is proportional to the oscillator voltage increase at the switchover time according to the equation.

$\begin{array}{l} dV_8/dt = \alpha_4 \ \times \ dV_4/dt = \\ 2 \ \times \ \alpha_4 \ \times \ f \ \times \ (\alpha_2 - \alpha_3) \ \times \ (V_{Batt} - I_S \ \times \ R_3) \\ \text{when} \\ f = 75 \text{ Hz}, \ V_{TX} = V_{T < 100} \text{ and } \alpha_4 = 63 \\ \text{we obtain} \end{array}$

**TELEFUNKEN Semiconductors** Rev. A1, 14-Feb-97 Via an external capacitor,  $C_4$ , the slope can be further reduced as follows:

$$dV_8/dt = I_{OSC}/(C_4 + C_2/\alpha_4)$$

when

$I_{OSC}$  = 45  $\mu A,\,C_4$  = 1.8 nF,  $C_2$  = 68 nF and  $\alpha_4$  = 63

then  $dV_8/dt = 45 \ \mu A/(1.8 \ nF + 68 \ nF/63) = 15.6 \ V/ms$

To damp oscillation tendencies, a resistance of 100  $\Omega$  in series with capacitance  $C_4$  is recommended.

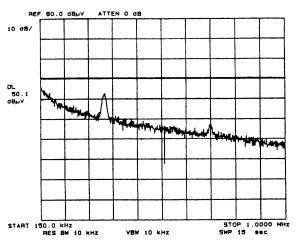

#### **Interference Suppression**

"On board" radio reception according to VDE 0879 part 3/4.81

Test conditions refering to figure 2.

Application circuit according to figure 1 or 3.

Load: nine 4-W lamps in parallel.

Figure 2. Voltage spectrum of on-board radio reception

#### Pins 5 and 6, Short-Circuit Protection and Current Sensing,

#### 1. Short-Circuit Detection and Time Delay, t<sub>d</sub>

The lamp current is monitored by means of an external shunt resistor. If the lamp current exceeds the threshold for the short-circuit detection circuit ( $V_{T2} \approx 90 \text{ mV}$ ), the duty cycle is switched over to 100% and the capacitor  $C_5$  is charged by a current source of  $I_{ch} - I_{dis}$ . The external FET is switched off after the cut-off threshold ( $V_{T5}$ ) is reached. Renewed switching on of the FET is possible only after a power-on reset. The current source,  $I_{dis}$ , ensures that the capacitor  $C_5$  is not charged by parasitic currents.

TEMIC Semiconductors

Time delay, t<sub>d</sub>, is as follows:

$t_d = C_5 \times V_{T5}/(I_{ch} - I_{dis})$ With  $C_5 = 100$  nF and  $V_{T5} = 10.4$  V,  $I_{ch} = 13$   $\mu$ A,  $I_{dis} = 3 \mu$ A, we have  $t_d = 100$  nF × 10.4 V/ (13  $\mu$ A - 3  $\mu$ A)

$t_{d} = 104 \text{ ms}$

#### 2. Current Limitation:

The lamp current is limited by a control amplifier to protect the external power transistor. The voltage drop across an external shunt resistor acts as the measured variable. Current limitation takes place for a voltage drop of  $V_{T1} \approx 100 \text{ mV}$ . Owing to the difference  $V_{T1}$ - $V_{T2} \approx 10 \text{ mV}$ , it is ensured that current limitation

occurs only when the short-circuit detection circuit has responded.

After a power-on reset, the output is inactive for half an oscillator cycle. During this time, the supply voltage capacitor can be charged so that current limitation is guaranteed in the event of a short-circuit when the IC is switched on for the first time.

#### Pins 7 and 8, Charge Pump and Output,

Output, Pin 8, is suitable for controlling a power MOSFET. During the active integration phase, the supply current of the operational amplifier is mainly supplied by the capacitor  $C_3$  (bootstrapping). In addition, a trickle charge is generated by an integrated oscillator ( $f_7 \approx 400 \text{ kHz}$ ) and a voltage doubler circuit. This permits a gate voltage supply at a duty cycle of 100%.

## **Absolute Maximum Ratings**

| Parameters                | Symbol           | Value       | Unit |

|---------------------------|------------------|-------------|------|

| Junction temperature      | Tj               | 150         | °C   |

| Ambient temperature range | T <sub>amb</sub> | -40 to +110 | °C   |

| Storage temperature range | T <sub>stg</sub> | -55 to +125 | °C   |

### **Thermal Resistance**

| Parameters       | Symbol            | Value | Unit |

|------------------|-------------------|-------|------|

| Junction ambient | R <sub>thJA</sub> | 120   | K/W  |

# **Electrical Characteristics**

$T_{amb} = -40$  to  $+110^{\circ}$ C,  $V_{Batt} = 9$  to 16.5 V, (basic function is guaranteed between 6.0 V to 9.0 V) reference point ground, unless otherwise specified (see figure 1). All other values refer to Pin GND (Pin 2).

| Parameters           | Test Conditions / Pins         | Symbol            | Min. | Тур. | Max. | Unit |

|----------------------|--------------------------------|-------------------|------|------|------|------|

| Current consumption  | Pin 1                          | IS                |      |      | 7.9  | mA   |

| Supply voltage       | Overvoltage detection, stage 1 | V <sub>Batt</sub> |      |      | 25   | V    |

| Stabilized voltage   | $I_S = 10 \text{ mA}$ Pin 1    | Vs                | 24.5 |      | 27.0 | V    |

| Battery undervoltage | - on                           | V <sub>Batt</sub> | 4.4  | 5.0  | 5.6  | V    |

| detection            | - off                          |                   | 4.8  | 5.4  | 6.0  |      |

| Parameters                  | Test Conditions / Pins                                            | Symbol            | Min.              | Тур.              | Max.              | Unit |

|-----------------------------|-------------------------------------------------------------------|-------------------|-------------------|-------------------|-------------------|------|

| Battery overvoltage detect  | tion                                                              |                   |                   |                   |                   |      |

| Stage 1:                    | – on                                                              |                   |                   |                   |                   |      |

|                             | – off                                                             | V <sub>Batt</sub> | 18.3              | 20.0              | 21.7              | V    |

|                             | _                                                                 |                   | 16.7              | 18.5              | 20.3              |      |

| Stage 2:                    |                                                                   | V                 | 25.5              | 29.5              | 22.5              | v    |

| Detection stage 2           | – on<br>– off                                                     | V <sub>Batt</sub> | 25.5<br>19.5      | 28.5<br>23.0      | 32.5<br>26.5      | v    |

| Stabilized voltage          | $I_S = 30 \text{ mA}$ Pin 1                                       | Vs                | 19.5              | 20.0              | 20.5              | v    |

| Short-circuit protection    | Pin 6                                                             | *\$               | 10.5              | 20.0              | 21.5              |      |

| Short-circuit current       | $V_{T1} = V_S - V_6$                                              | V <sub>T1</sub>   | 85                | 100               | 120               | mV   |

| limitation                  | 11 5 0                                                            |                   |                   |                   |                   |      |

| Short-circuit detection     | $V_{T2} = V_S - V_6$                                              | V <sub>T2</sub>   | 75                | 90                | 105               | mV   |

|                             | 12 5 0                                                            | $V_{T1} - V_{T2}$ | 3                 | 10                | 30                |      |

| Delay timer short circuit o | <b>letection,</b> $V_{Batt} = 12 \text{ V} \text{ Pin 5}$         |                   |                   | •                 |                   | •    |

| Switched off threshold      | $V_{T5} = V_S - V_5$                                              | V <sub>T5</sub>   | 10.2              | 10.4              | 10.6              | V    |

| Charge current              |                                                                   | I <sub>ch</sub>   |                   | 13                |                   | μΑ   |

| Discharge current           |                                                                   | I <sub>dis</sub>  |                   | 3                 |                   | μA   |

| Capacitance current         | $I_5 = I_{ch} - I_{dis}$                                          | I <sub>5</sub>    | 5                 | 10                | 15                | mA   |

| Voltage doubler             | Pin 7                                                             |                   |                   |                   |                   |      |

| Voltage                     | Duty cycle 100%                                                   | V <sub>7</sub>    | 2 V <sub>S</sub>  |                   |                   |      |

| Oscillator frequency        |                                                                   | f <sub>7</sub>    | 280               | 400               | 520               | kHz  |

| Internal voltage limitation | $I_7 = 5 \text{ mA}$                                              | V <sub>7</sub>    | 26                | 27.5              | 30.0              | V    |

|                             | (whichever is lower)                                              |                   | V <sub>S+14</sub> | V <sub>S+15</sub> | V <sub>S+16</sub> |      |

| Edge steepness              | $\frac{dv_8/dt = \alpha_4 dV_4/dt}{dV_8/dt_{max}}$                | α <sub>4</sub>    | 53                | 63                | 72<br>130         | V/ms |

| Gate output                 | Pin 8                                                             |                   |                   |                   |                   |      |

| Voltage                     | Low level                                                         | V <sub>8</sub>    | 0.35              | 0.70              | 0.95              | V    |

|                             | $V_{Batt} = 16.5 V$<br>$T_{amb} = 110^{\circ}C, R_3 = 150 \Omega$ |                   |                   |                   | 1.5 *)            |      |

|                             | High level,<br>duty cycle 100%                                    | V <sub>8</sub>    |                   | V <sub>7</sub>    |                   |      |

| Current                     | $V_8 = Low level$                                                 | I <sub>8</sub>    | 1.0               |                   |                   | mA   |

|                             | $V_8 = High \ level, \ I_7 >   \ I_8  $                           |                   | -1.0              |                   |                   |      |

| Duty cycle                  | Min: $C_2 = 68 \text{ nF}$                                        | t <sub>p</sub> /T | 15                | 18                | 21                |      |

|                             | Max: $V_{Batt} \le 12.4 V$                                        |                   | 100               |                   |                   | %    |

|                             | $V_{Batt} = 16.5 \text{ V}, C_2 = 68 \text{ nF}$                  |                   | 65                | 73                | 81                |      |

| Oscillator                  |                                                                   | ii                |                   | i                 |                   | i    |

| Frequency                   | Pin4                                                              | f                 | 10                |                   | 2000              | Hz   |

| Threshold cycle             | $V_8 = \text{High}, \ \alpha_1 = \frac{V_{T100}}{V_S}$            | $\alpha_1$        | 0.68              | 0.7               | 0.72              |      |

| Upper                       |                                                                   |                   |                   |                   |                   |      |

|                             | $V_8 = Low, \ \alpha_2 = \frac{V_{T < 100}}{V_S}$                 | α <sub>2</sub>    | 0.65              | 0.67              | 0.69              |      |

| Lower                       | $\alpha_3 = \frac{V_{TL}}{V_S}$                                   | α3                | 0.26              | 0.28              | 0.3               |      |

| Oscillator current          | $V_{Batt} = 12 V$                                                 | ±Iosc             | 34                | 45                | 54                | μΑ   |

| Frequency                   | $C_4$ open, $C_2 = 68 \text{ nF}$<br>duty cycle = 50%             | f                 | 56                | 75                | 90                | Hz   |

\*) Reference point is battery ground.

**TELEFUNKEN Semiconductors** Rev. A1, 14-Feb-97

# U6083B

TEMIC Semiconductors

# Application

Figure 3.

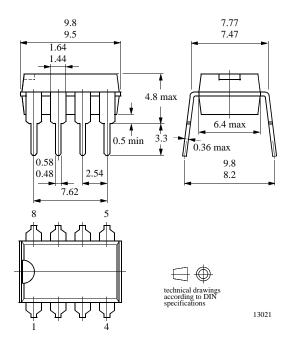

# **Package Information**

Package DIP8

Dimensions in mm

**TELEFUNKEN Semiconductors** Rev. A1, 14-Feb-97

# **Ozone Depleting Substances Policy Statement**

#### It is the policy of TEMIC TELEFUNKEN microelectronic GmbH to

- 1. Meet all present and future national and international statutory requirements.

- 2. Regularly and continuously improve the performance of our products, processes, distribution and operating systems with respect to their impact on the health and safety of our employees and the public, as well as their impact on the environment.

It is particular concern to control or eliminate releases of those substances into the atmosphere which are known as ozone depleting substances (ODSs).

The Montreal Protocol (1987) and its London Amendments (1990) intend to severely restrict the use of ODSs and forbid their use within the next ten years. Various national and international initiatives are pressing for an earlier ban on these substances.

**TEMIC TELEFUNKEN microelectronic GmbH** semiconductor division has been able to use its policy of continuous improvements to eliminate the use of ODSs listed in the following documents.

- 1. Annex A, B and list of transitional substances of the Montreal Protocol and the London Amendments respectively

- 2. Class I and II ozone depleting substances in the Clean Air Act Amendments of 1990 by the Environmental Protection Agency (EPA) in the USA

- 3. Council Decision 88/540/EEC and 91/690/EEC Annex A, B and C (transitional substances) respectively.

**TEMIC** can certify that our semiconductors are not manufactured with ozone depleting substances and do not contain such substances.

We reserve the right to make changes to improve technical design and may do so without further notice. Parameters can vary in different applications. All operating parameters must be validated for each customer application by the customer. Should the buyer use TEMIC products for any unintended or unauthorized application, the buyer shall indemnify TEMIC against all claims, costs, damages, and expenses, arising out of, directly or indirectly, any claim of personal damage, injury or death associated with such unintended or unauthorized use.

TEMIC TELEFUNKEN microelectronic GmbH, P.O.B. 3535, D-74025 Heilbronn, Germany Telephone: 49 (0)7131 67 2831, Fax number: 49 (0)7131 67 2423