PMC PMC-Sierra, Inc.

PM5344 SPTX

ISSUE 6

SONET/SDH PATH TERMINATING TRANSCEIVER

## PM5344

# SPTX

# SONET/SDH PATH TERMINATING TRANSCEIVER TELECOM

# DATA SHEET

**ISSUE 6: JULY 1998**

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS' INTERNAL USE

ISSUE 6

### **PUBLIC REVISION HISTORY**

| Issue No | Date of issue | Details of Change                                        |

|----------|---------------|----------------------------------------------------------|

| 6        | July 1998     | Data Sheet Reformatted — No Change in Technical Content. |

|          |               | Generated R5 data sheet from PMC-920813, P8              |

ISSUE 6

SONET/SDH PATH TERMINATING TRANSCEIVER

## **CONTENTS**

| 1 | FEATUR  | RES      | 1                           |

|---|---------|----------|-----------------------------|

|   | 1.1     | THE RE   | CEIVER SECTION:1            |

|   | 1.2     | THE TR   | ANSMITTER SECTION:          |

| 2 | APPLIC  | ATIONS.  | 5                           |

| 3 | REFER   | ENCES    | 6                           |

| 4 | APPLIC  | ATION E  | XAMPLES7                    |

| 5 | BLOCK   | DIAGRA   | М9                          |

| 6 | DESCR   | IPTION   |                             |

| 7 | PIN DIA | GRAM     |                             |

| 8 | PIN DES | SCRIPTIC | DN13                        |

| 9 | FUNCTI  | ONAL DI  | ESCRIPTION25                |

|   | 9.1     | RECEIV   | E PATH OVERHEAD PROCESSOR25 |

|   |         | 9.1.1    | POINTER INTERPRETER         |

|   |         | 9.1.2    | MULTIFRAME FRAMER29         |

|   |         | 9.1.3    | SPE TIMING                  |

|   |         | 9.1.4    | ERROR MONITOR               |

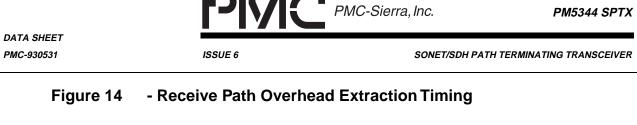

|   |         | 9.1.5    | PATH OVERHEAD EXTRACT       |

|   |         | 9.1.6    | TANDEM CONNECTION ORIGINATE |

|   |         | 9.1.7    | RECEIVE ALARM PORT          |

|   | 9.2     | RECEIV   | 'E PATH TRACE BUFFER        |

|   | 9.3     | RECEIV   | E TELECOMBUS ALIGNER        |

|   |         | 9.3.1    | ELASTIC STORE               |

|   |         | 9.3.2    | POINTER GENERATOR           |

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS' INTERNAL USE i

| DATA SHEET<br>PMC-930531 |      |                              | ISSUE 6                      | SONET/SDH PATH TERMINATING TRANSCEIVER |

|--------------------------|------|------------------------------|------------------------------|----------------------------------------|

|                          |      | 9.3.3                        | TANDEM CONNECTION ALARM      |                                        |

|                          | 9.4  | TRANS                        | SMIT PATH OVERHEAD PROCESSOR |                                        |

|                          |      | 9.4.1                        | BIP-8 CALCULATE              |                                        |

|                          |      | 9.4.2                        | FEBE CALCULATE               |                                        |

|                          |      | 9.4.3                        | TRANSMIT ALARM PORT          |                                        |

|                          |      | 9.4.4                        | PATH OVERHEAD INSERT         |                                        |

|                          |      | 9.4.5                        | SPE MULTIPLEXER              |                                        |

|                          |      | 9.4.6                        | GENERATED BUS CONTROLLER.    |                                        |

|                          | 9.5  | TRANS                        | SMIT TELECOMBUS ALIGNER      |                                        |

|                          |      | 9.5.1                        | ELASTIC STORE                |                                        |

|                          |      | 9.5.2                        | POINTER GENERATOR            |                                        |

|                          |      | 9.5.3                        | TANDEM CONNECTION ALARM      |                                        |

|                          | 9.6  | TRANS                        | SMIT PATH TRACE BUFFER       | 41                                     |

|                          | 9.7  | TELEC                        | OMBUS INTERFACE              | 41                                     |

|                          | 9.8  | MICRC                        | PROCESSOR INTERFACE          | 41                                     |

|                          | 9.9  | REGIS                        | TER MEMORY MAP               | 41                                     |

| 10                       | NORM | AL MODE REGISTER DESCRIPTION |                              |                                        |

| 11                       | TEST | FEATURES DESCRIPTION128      |                              |                                        |

|                          | 11.1 | TEST                         | MODE REGISTER MEMORY MAP     |                                        |

|                          | 11.2 | I/O TES                      | ST MODE                      |                                        |

| 12                       | OPER | ATION                        |                              |                                        |

|                          | 12.1 | CONFI                        | GURATION OPTIONS             |                                        |

|                          |      | 12.1.1                       | STS-1 (SINGLE AU3) MODE      |                                        |

|                          |      | 12.1.2                       |                              |                                        |

| DATA SHEET |               | PMC PMC-Sierra,                 | Inc. PM5344 SPTX                       |

|------------|---------------|---------------------------------|----------------------------------------|

| PMC-930531 |               | ISSUE 6                         | SONET/SDH PATH TERMINATING TRANSCEIVER |

|            | 12.1.3        | STS-3C (AU4) MODE               | 141                                    |

|            | 12.1.4        | ORIGINATING TCTE MODE           | 141                                    |

|            | 12.1.5        | TRANSMIT TCTE TERMINATING MODE  | 141                                    |

|            | 12.1.6        | PATH AND TCTE TERMINATING MODE  | 141                                    |

|            | 12.1.7        | RECEIVE TCTE BYPASS MODE        | 142                                    |

|            | 12.1.8        | TRANSMIT TCTE BYPASS MODE       | 142                                    |

| 13         | FUNCTIONAL T  | IMING                           | 143                                    |

|            | 13.1 RECEIV   | /E SECTION                      | 143                                    |

|            | 13.1.1        | RECEIVE STREAM TIMING           | 143                                    |

|            | 13.1.2        | EXTERNAL PATH TERMINATION RECE  | IVE BUS TIMING144                      |

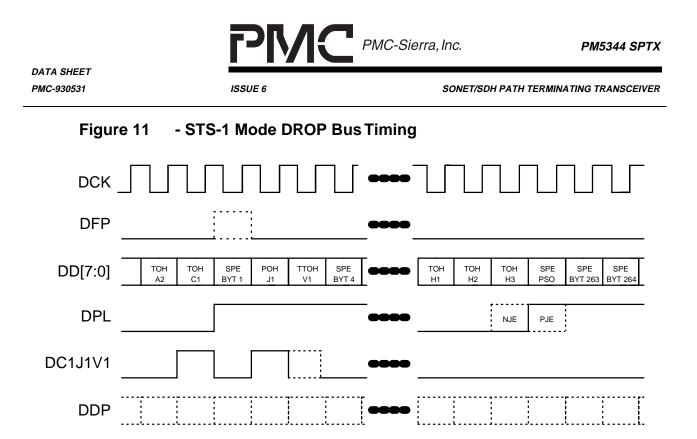

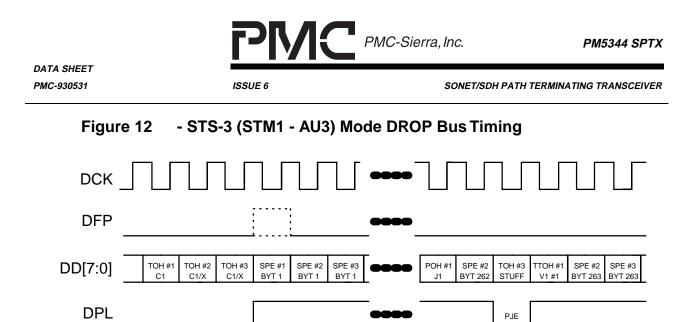

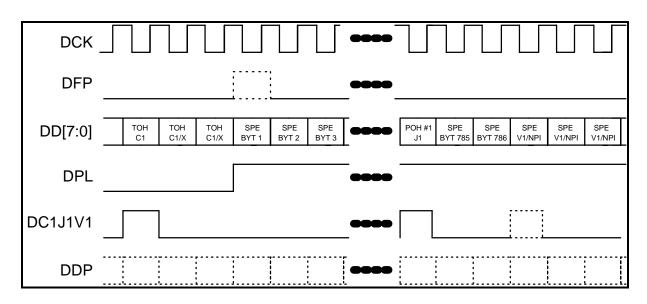

|            | 13.1.3        | DROP BUS TIMING                 | 147                                    |

|            | 13.1.4        | RECEIVE LOW-SPEED INTERFACE TIM | /ING150                                |

|            | 13.1.5        | RECEIVE ALARM STATUS TIMING     | 153                                    |

|            | 13.2 TRANS    | MIT SECTION                     | 155                                    |

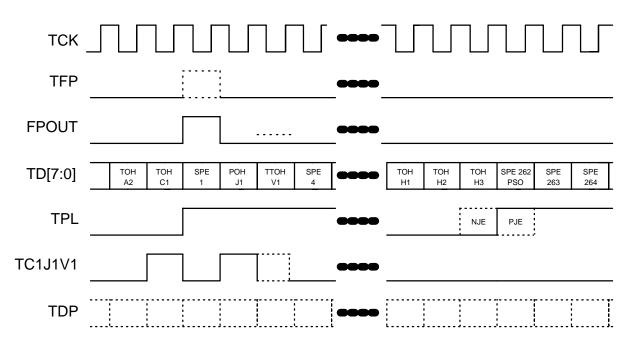

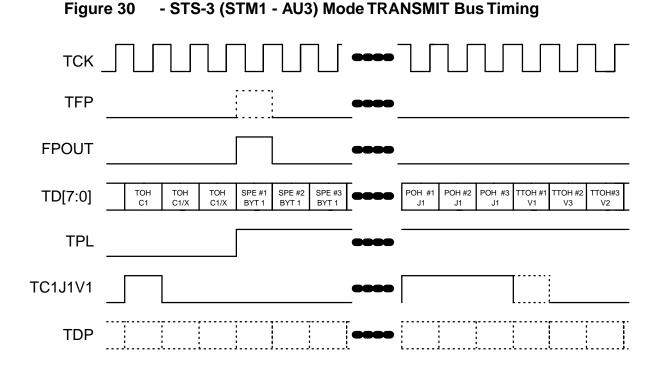

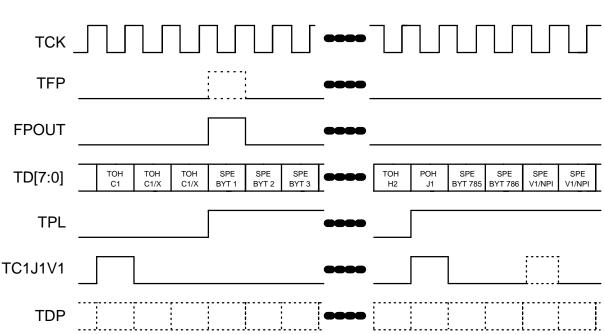

|            | 13.2.1        | GENERATED BUS TIMING            |                                        |

|            | 13.2.2        | ADD BUS TIMING                  | 158                                    |

|            | 13.2.3        | TRANSMIT LOW-SPEED INTERFACE T  | IMING161                               |

|            | 13.2.4        | TRANSMIT BUS TIMING             | 163                                    |

|            | 13.2.5        | ELASTIC STORE BYPASS TIMING     | 166                                    |

| 14         | ABSOLUTE MAX  | XIMUM RATINGS                   |                                        |

| 15         | D.C. CHARACTE | RISTICS                         | 171                                    |

| 16         | MICROPROCES   | SOR INTERFACE TIMING CHARACTERI | STICS174                               |

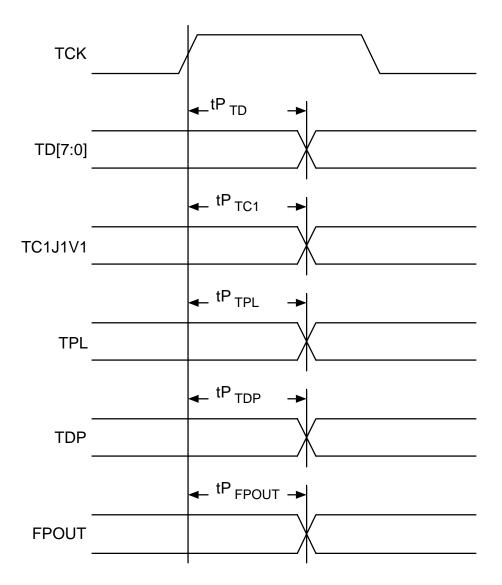

| 17         | SPTX TIMING C | HARACTERISTICS                  |                                        |

| 18         | ORDERING ANI  | D THERMAL INFORMATION           |                                        |

ISSUE 6

SONET/SDH PATH TERMINATING TRANSCEIVER

19

SONET/SDH PATH TERMINATING TRANSCEIVER

## LIST OF REGISTERS

| REGISTER 00H: SPTX MASTER CONFIGURATION                                 | 46  |

|-------------------------------------------------------------------------|-----|

| REGISTER 01H: SPTX MASTER ALARM CONFIGURATION                           | .49 |

| REGISTER 02H: SPTX MASTER PARITY CONFIGURATION                          | .51 |

| REGISTER 03H: SPTX MASTER RESET AND IDENTITY                            | .53 |

| REGISTER 04H: SPTX MASTER INTERRUPT STATUS #1                           | 54  |

| REGISTER 05H: SPTX MASTER INTERRUPT STATUS #2                           | 55  |

| REGISTER 06H: SPTX MASTER TRANSMIT CONTROL                              | 56  |

| REGISTER 07H: SPTX MASTER LOOPBACK, ADD BUS CONTROL                     | .57 |

| REGISTER 08H: SPTX MASTER SIGNAL ACTIVITY MONITOR, ACCUMULATION TRIGGER | 58  |

| REGISTER 10H, 50H, 90H: RPOP STATUS AND CONTROL                         | 60  |

| REGISTER 11H, 51H, 91H: RPOP ALARM INTERRUPT STATUS                     | .62 |

| REGISTER 12H, 52H, 92H: RPOP POINTER INTERRUPT STATUS                   | .63 |

| REGISTER 13H, 53H, 93H: RPOP ALARM INTERRUPT                            | 65  |

| REGISTER 14H, 54H, 94H: POINTER INTERRUPT ENABLE                        | 67  |

| REGISTER 15H, 55H, 95H: RPOP POINTER LSB                                | 69  |

| REGISTER 16H, 56H, 96H: RPOP POINTER MSB                                | 70  |

| REGISTER 17H, 57H, 97H: RPOP PATH SIGNAL LABEL                          | 71  |

| REGISTER 18H, 58H, 98H: RPOP PATH BIP-8 LSB                             | 72  |

| REGISTER 19H, 59H, 99H: PATH BIP-8 MSB                                  | .73 |

| REGISTER 1AH, 5AH, 9AH: RPOP FEBE LSB                                   | 74  |

| REGISTER 1BH, 5BH, 9BH: RPOP FEBE MSB                                   | 75  |

| REGISTER 1CH, 5CH, 9CH: RPOP TRIBUTARY MULTIFRAME STATUS AND CONTROL    | 76  |

| REGISTER 1DH, 5DH, 9DH: RPOP TANDEM CONNECTION AND RING CONTROL         | 78  |

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS' INTERNAL USE v

ISSUE 6

SONET/SDH PATH TERMINATING TRANSCEIVER

|               | 10002.0               |                                           | 02/12/1 |

|---------------|-----------------------|-------------------------------------------|---------|

| REGISTER 1EH, | 5EH, 9EH: RPOP TANDE  | EM CONNECTION IEC COUNT LSB               | 80      |

| REGISTER 1FH, | 5FH, 9FH: RPOP TANDE  | M CONNECTION IEC COUNT MSB                | 81      |

| REGISTER 24H, | 64H, A4H: PMON RECEI  | VE POSITIVE POINTER JUSTIFICATION COUNT   | 82      |

| REGISTER 25H, | 65H, A5H: PMON RECEI  | VE NEGATIVE POINTER JUSTIFICATION COUNT   | 83      |

| REGISTER 26H, | 66H, A6H: PMON TRANS  | SMIT POSITIVE POINTER JUSTIFICATION COUNT | 84      |

| REGISTER 27H, | 67H, A7H: PMON TRANS  | SMIT NEGATIVE POINTER JUSTIFICATION COUNT | 85      |

| REGISTER 28H, | 68H, A8H: RTAL CONTRO | OL                                        | 86      |

| REGISTER 29H, | 69H, A9H: RTAL INTERR | UPT STATUS AND DIAGNOSTIC                 | 88      |

| REGISTER 2AH, | 6AH, AAH: RTAL ALARM  | I AND DIAGNOSTIC CONTROL                  | 91      |

| REGISTER 30H, | 70H, B0H: TPOP CONTR  | OL                                        | 93      |

| REGISTER 31H, | 71H, B1H: TPOP GENER  | ATED BUS CONTROL                          | 95      |

| REGISTER 32H, | 72H, B2H: TPOP SOURC  | CE CONTROL                                | 97      |

| REGISTER 33H, | 73H, B3H: TPOP CURRE  | ENT POINTER LSB                           | 98      |

| REGISTER 34H, | 74H, B4H: TPOP CURRE  | ENT POINTER MSB                           | 99      |

| REGISTER 35H, | 75H, B5H: TPOP PAYLOA | AD POINTER LSB                            | .100    |

| REGISTER 36H, | 76H, B6H: TPOP PAYLOA | AD POINTER MSB                            | .101    |

| REGISTER 37H, | 77H, B7H: TPOP PATH T | RACE                                      | .102    |

| REGISTER 38H, | 78H, B8H: TPOP PATH S | IGNAL LABEL                               | .103    |

| REGISTER 39H, | 79H, B9H: TPOP PATH S | TATUS                                     | .104    |

| REGISTER 3AH, | 7AH, BAH: TPOP PATH U | JSER CHANNEL                              | .106    |

| REGISTER 3BH, | 7BH, BBH: TPOP PATH C | GROWTH #1                                 | .107    |

| REGISTER 3CH, | 7CH, BCH: TPOP PATH   | GROWTH #2                                 | .108    |

| REGISTER 3DH, | 7DH, BDH: TPOP TANDE  | EM CONNECTION MAINTENANCE                 | .109    |

| REGISTER 3EH: | TPOP CONCATENATION    | I LSB                                     | .110    |

DATA SHEET PMC-930531

| PMC-9305 | ISSUE 6                                                 | SONET/SDH PATH TERMINATING TRANSCEIVER |

|----------|---------------------------------------------------------|----------------------------------------|

|          | REGISTER 3FH: TPOP CONCATENATION MSB                    |                                        |

|          | REGISTER 40H, 80H, C0H: TTAL CONTROL                    |                                        |

|          | REGISTER 41H, 81H, C1H: TTAL INTERRUPT STATUS AND DIAG  | NOSTIC114                              |

|          | REGISTER 42H, 82H, C2H: TTAL ALARM AND DIAGNOSTIC CON   | ITROL117                               |

|          | REGISTER 48H, 88H, C8H: SPTB CONTROL                    |                                        |

|          | REGISTER 49H, 89H, C9H: SPTB PATH TRACE IDENTIFIER STAT | <sup>-</sup> US121                     |

|          | REGISTER 4AH, 8AH, CAH: SPTB INDIRECT ADDRESS REGIST    | ER123                                  |

|          | REGISTER 4BH, 8BH, CBH: SPTB INDIRECT DATA REGISTER     |                                        |

|          | REGISTER 4CH, 8CH, CCH: SPTB EXPECTED PATH SIGNAL LAI   | 3EL125                                 |

|          | REGISTER 4DH, 8DH, CDH: SPTB PATH SIGNAL LABEL STATUS   | 126                                    |

|          | REGISTER 100H: MASTER TEST                              |                                        |

|          | TEST REGISTER 101H: (WRITE IN I/O TEST MODE)            |                                        |

|          | TEST REGISTER 102H: (WRITE IN I/O TEST MODE)            |                                        |

|          | TEST REGISTER 103H: (WRITE IN I/O TEST MODE)            |                                        |

|          | TEST REGISTER 104H: (WRITE IN I/O TEST MODE)            |                                        |

|          | TEST REGISTER 101H: (READ IN I/O TEST MODE)             |                                        |

|          | TEST REGISTER 102H: (READ IN I/O TEST MODE)             |                                        |

|          | TEST REGISTER 103H: (READ IN I/O TEST MODE)             |                                        |

|          | TEST REGISTER 104H: (READ IN I/O TEST MODE)             |                                        |

|          | TEST REGISTER 105H: (READ IN I/O TEST MODE)             |                                        |

DATA SHEET

ISSUE 6

#### **LIST OF FIGURES**

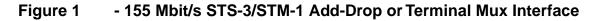

| FIGURE 1  | - 155 MBIT/S STS-3/STM-1 ADD-DROP OR TERMINAL MUX INTERFACE7        |

|-----------|---------------------------------------------------------------------|

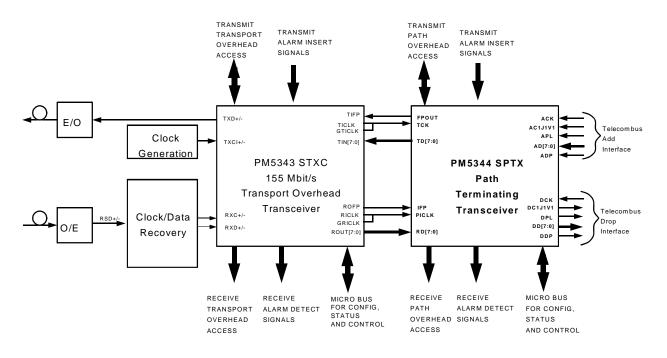

| FIGURE 2  | - 622 MBIT/S STS-12/STM-4 ADD-DROP MULTIPLEXER AGGREGATE INTERFACE8 |

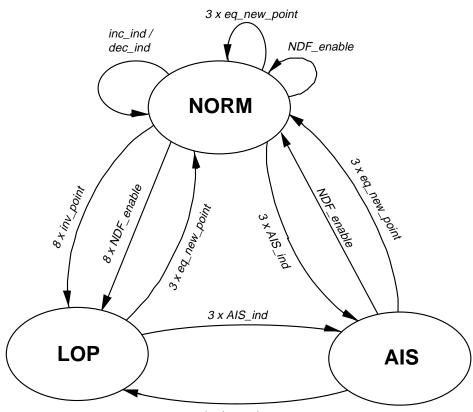

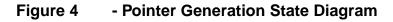

| FIGURE 3  | - POINTER INTERPRETATION STATE DIAGRAM                              |

| FIGURE 4  | - POINTER GENERATION STATE DIAGRAM                                  |

| FIGURE 5  | - STS-1 (SINGLE AU3) RECEIVE STREAM TIMING143                       |

| FIGURE 6  | - STS-3 (STM1 - AU3) RECEIVE STREAM TIMING144                       |

| FIGURE 7  | - STS-3C (STM1 - AU4) RECEIVE STREAM TIMING144                      |

| FIGURE 8  | - STS-1 MODE RECEIVE BUS TIMING145                                  |

| FIGURE 9  | - STS-3 (STM1 - AU3) MODE RECEIVE BUS TIMING146                     |

| FIGURE 10 | - STS-3C (STM1 - AU4) MODE RECEIVE BUS TIMING                       |

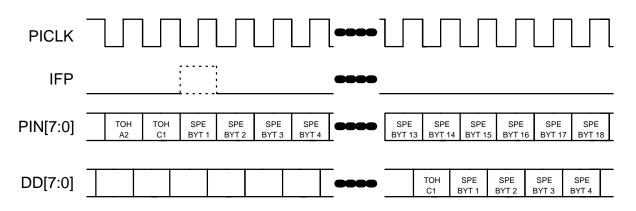

| FIGURE 11 | - STS-1 MODE DROP BUS TIMING                                        |

| FIGURE 12 | - STS-3 (STM1 - AU3) MODE DROP BUS TIMING149                        |

| FIGURE 13 | - STS-3C (STM1 - AU4) MODE DROP BUS TIMING150                       |

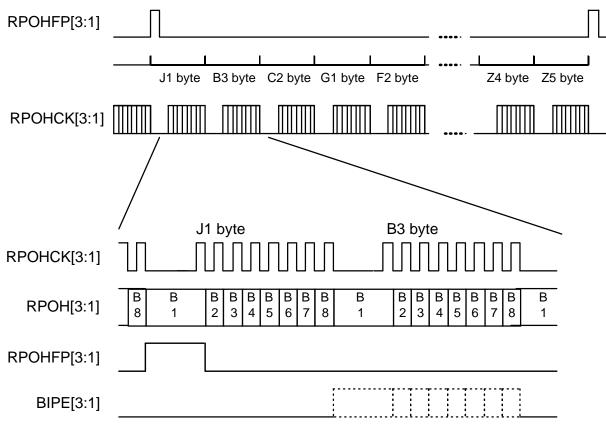

| FIGURE 14 | - RECEIVE PATH OVERHEAD EXTRACTION TIMING                           |

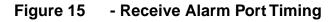

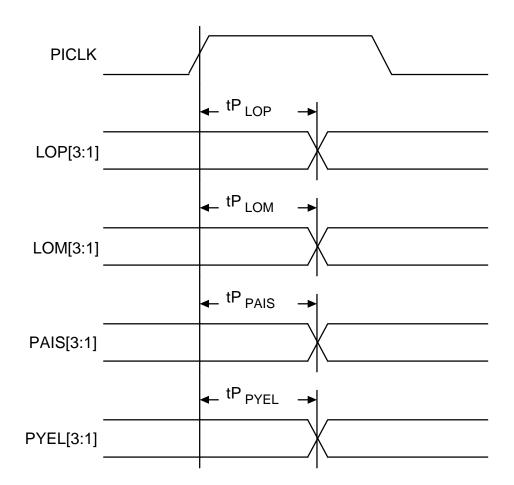

| FIGURE 15 | - RECEIVE ALARM PORT TIMING152                                      |

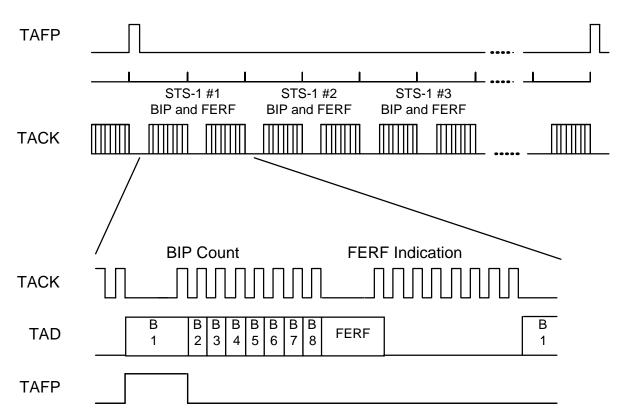

| FIGURE 16 | - RECEIVE TANDEM CONNECT MAINTENANCE INSERTION TIMING               |

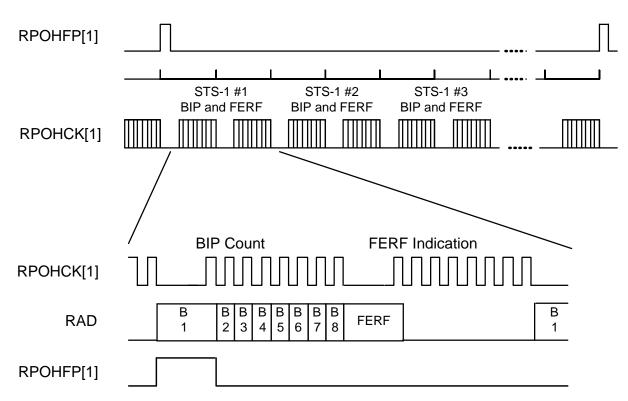

| FIGURE 17 | - LOSS OF POINTER (LOP) DECLARATION/REMOVAL TIMING                  |

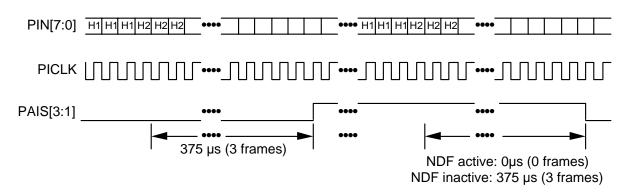

| FIGURE 18 | - PATH AIS (PAIS) DECLARATION/REMOVAL TIMING                        |

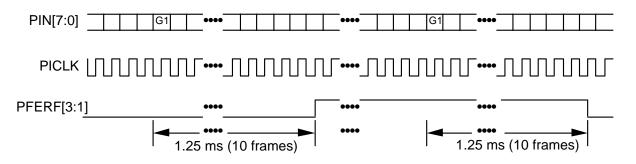

| FIGURE 19 | - PATH FERF ALARM (PFERF) DECLARATION/REMOVAL TIMING154             |

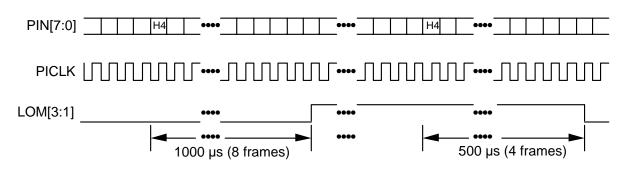

| FIGURE 20 | - LOSS OF MULTIFRAME (LOM) DECLARATION/REMOVAL TIMING155            |

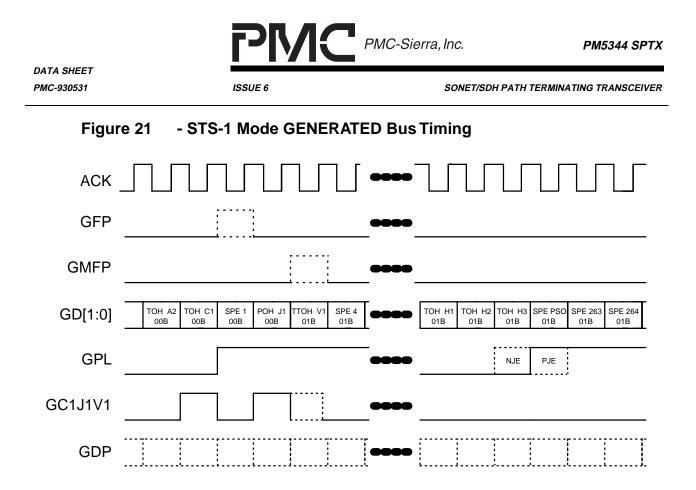

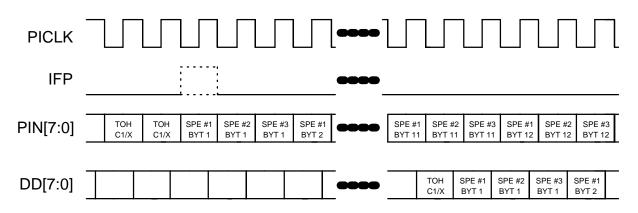

| FIGURE 21 | - STS-1 MODE GENERATED BUS TIMING156                                |

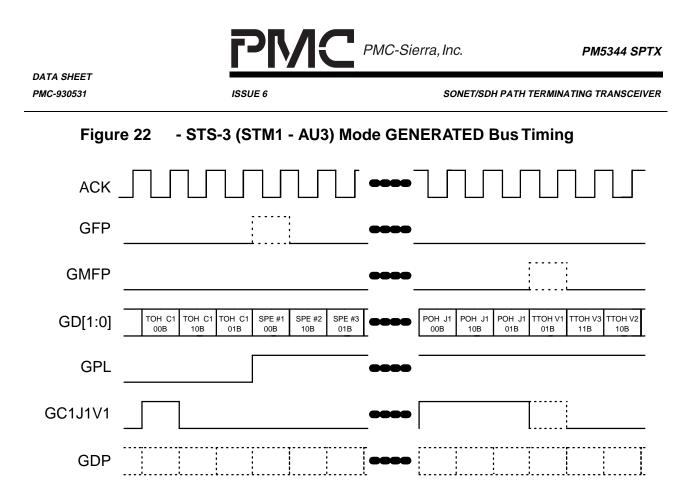

| FIGURE 22 | - STS-3 (STM1 - AU3) MODE GENERATED BUS TIMING157                   |

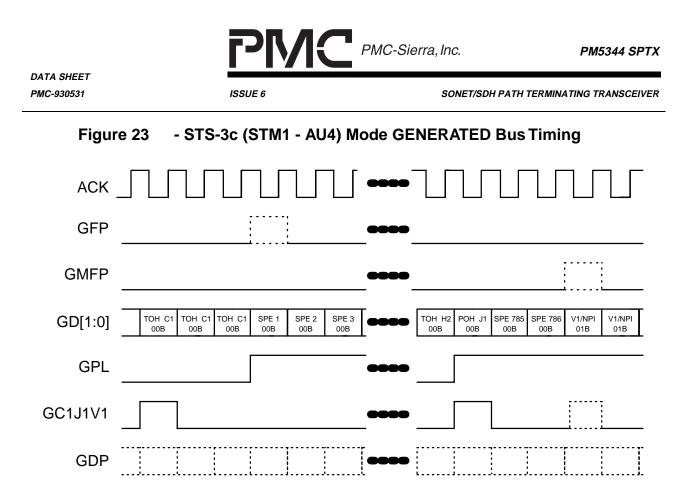

| FIGURE 23 | - STS-3C (STM1 - AU4) MODE GENERATED BUS TIMING158                  |

# PMC-Sierra, Inc.

| DATA SHEET<br>PMC-930531 | ISSUE 6 SONET/SDH PATH TERMINATING TRANSCEIVE                 |

|--------------------------|---------------------------------------------------------------|

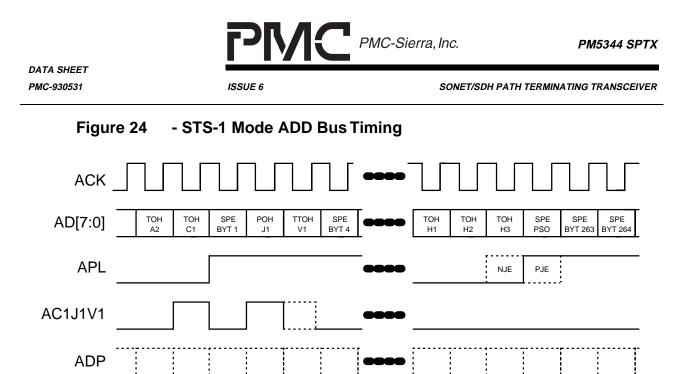

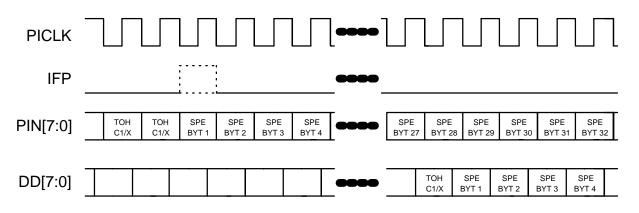

| FIGURE 24                | - STS-1 MODE ADD BUS TIMING                                   |

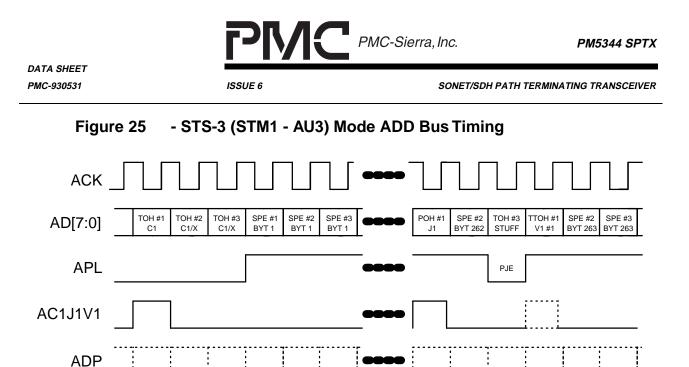

| FIGURE 25                | - STS-3 (STM1 - AU3) MODE ADD BUS TIMING160                   |

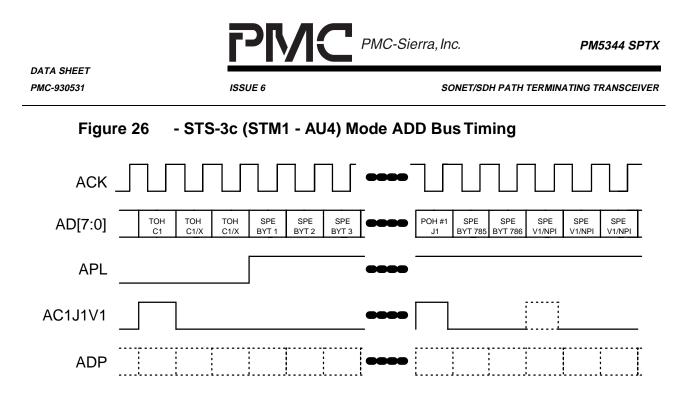

| FIGURE 26                | - STS-3C (STM1 - AU4) MODE ADD BUS TIMING161                  |

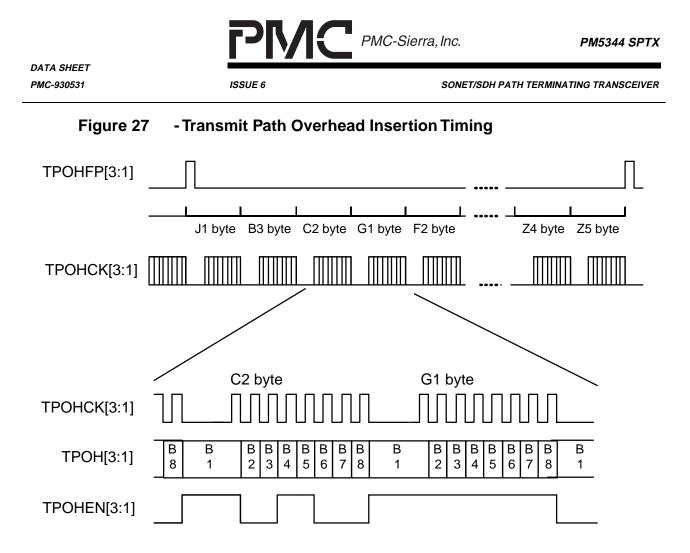

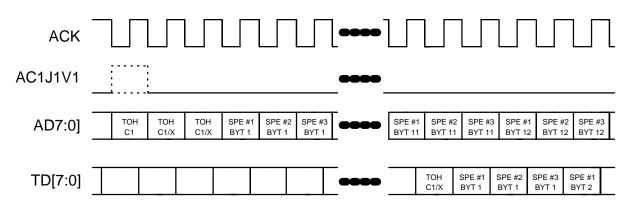

| FIGURE 27                | - TRANSMIT PATH OVERHEAD INSERTION TIMING                     |

| FIGURE 28                | - TRANSMIT ALARM PORT TIMING163                               |

| FIGURE 29                | - STS-1 MODE TRANSMIT BUS TIMING164                           |

| FIGURE 30                | - STS-3 (STM1 - AU3) MODE TRANSMIT BUS TIMING165              |

| FIGURE 31                | - STS-3C (STM1 - AU4) MODE TRANSMIT BUS TIMING166             |

| FIGURE 32                | - STS-1 (SINGLE AU3) RECEIVE ELASTIC STORE BYPASS TIMING166   |

| FIGURE 33                | - STS-3 (STM1 - AU3) RECEIVE ELASTIC STORE BYPASS TIMING      |

| FIGURE 34                | - STS-3C (STM1 - AU4) RECEIVE ELASTIC STORE BYPASS TIMING     |

| FIGURE 35                | - STS-1 (SINGLE AU3) TRANSMIT ELASTIC STORE BYPASS TIMING168  |

| FIGURE 36                | - STS-3 (STM1 - AU3) TRANSMIT ELASTIC STORE BYPASS TIMING168  |

| FIGURE 37                | - STS-3C (STM1 - AU4) TRANSMIT ELASTIC STORE BYPASS TIMING169 |

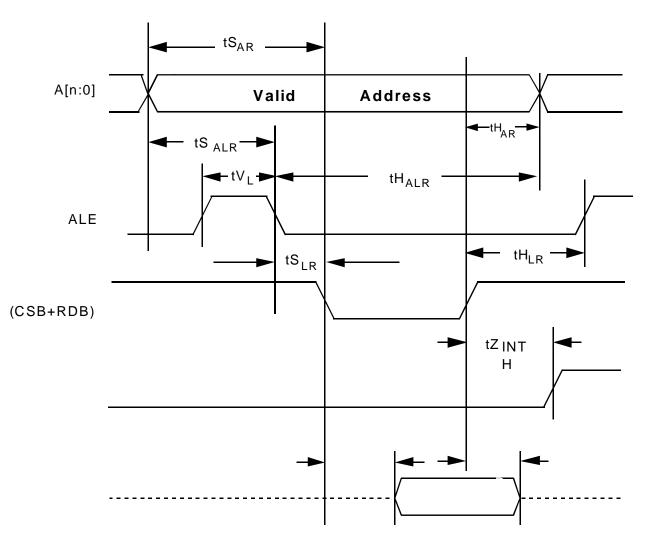

| FIGURE 38                | - MICROPROCESSOR INTERFACE READ TIMING (INTEL MODE)           |

| FIGURE 39                | - MICROPROCESSOR INTERFACE READ TIMING (MOTOROLA MODE)176     |

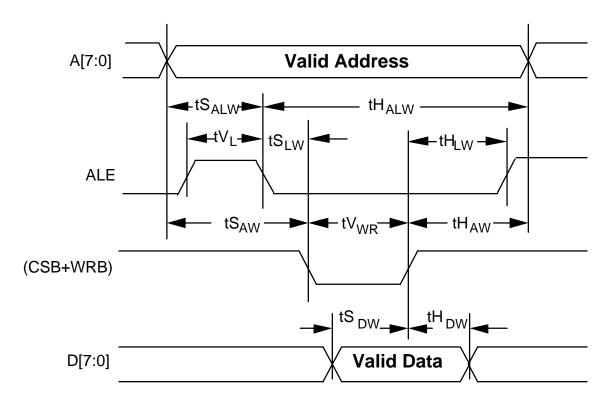

| FIGURE 40                | - MICROPROCESSOR INTERFACE WRITE TIMING (INTEL MODE)178       |

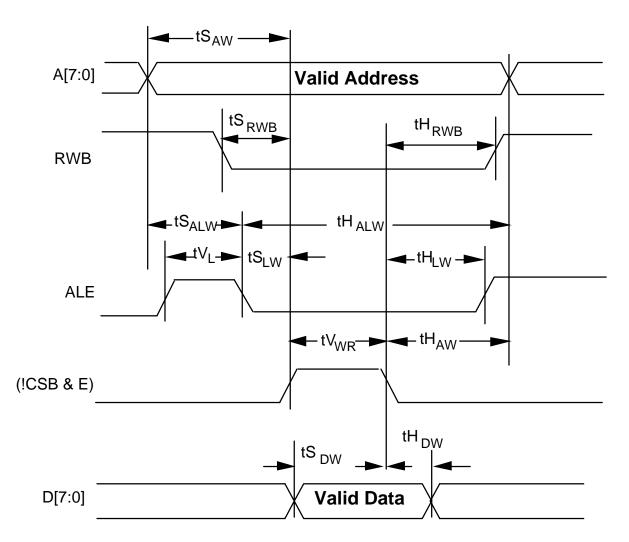

| FIGURE 41                | - MICROPROCESSOR INTERFACE WRITE TIMING (MOTOROLA MODE)179    |

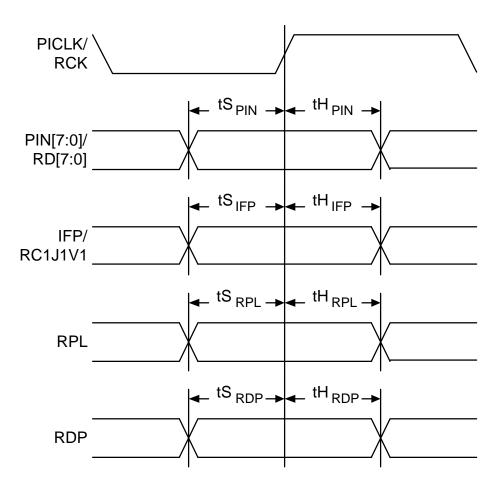

| FIGURE 42                | - RECEIVE LINE INPUT TIMING                                   |

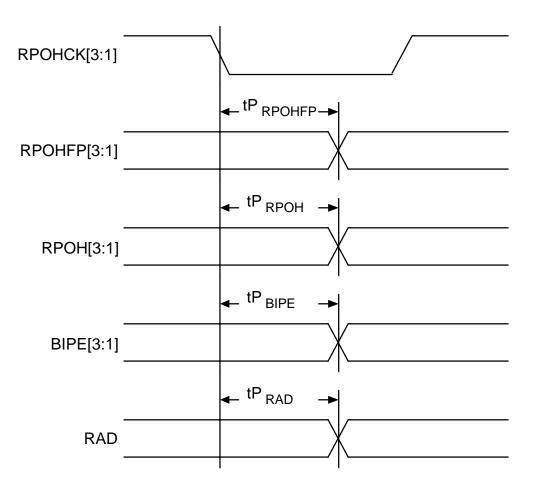

| FIGURE 43                | - RECEIVE ALARM OUTPUT TIMING                                 |

| FIGURE 44                | - RECEIVE OVERHEAD AND ALARM PORT OUTPUT TIMING               |

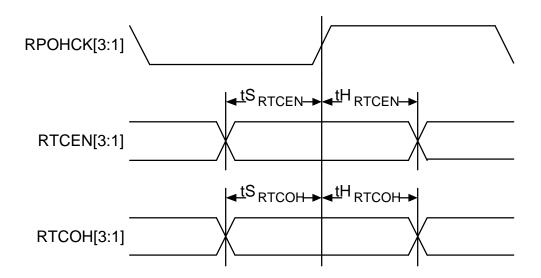

| FIGURE 45                | - RECEIVE TANDEM CONNECTION INPUT TIMING                      |

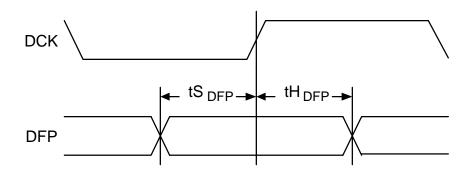

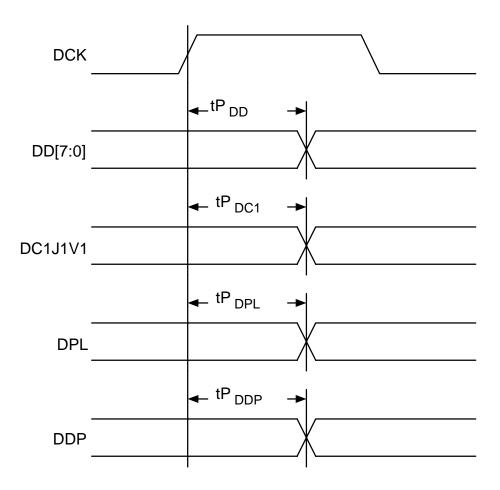

| FIGURE 46                | - DROP BUS INPUT TIMING                                       |

| FIGURE 47                | - DROP BUS OUTPUT TIMING                                      |

|                          | PMC                          | PMC-Sierra, Inc.                | PM5344 SPTX         |

|--------------------------|------------------------------|---------------------------------|---------------------|

| DATA SHEET<br>PMC-930531 | ISSUE 6                      | SONET/SDH PATH TERMI            | INATING TRANSCEIVER |

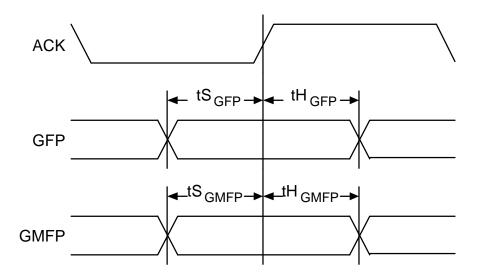

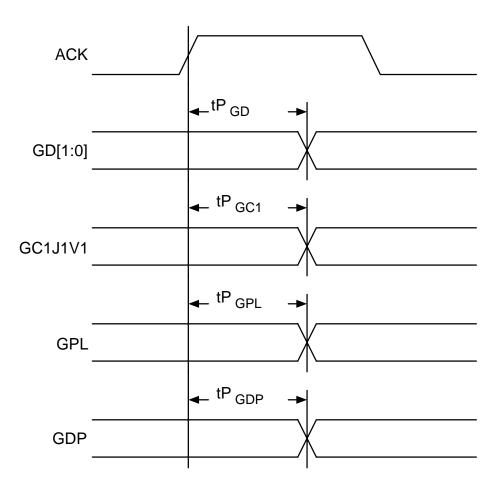

| FIGURE 48                | - GENERATED BUS INPUT TIMING | G                               | 187                 |

| FIGURE 49                | - GENERATED BUS OUTPUT TIM   | NG                              | 188                 |

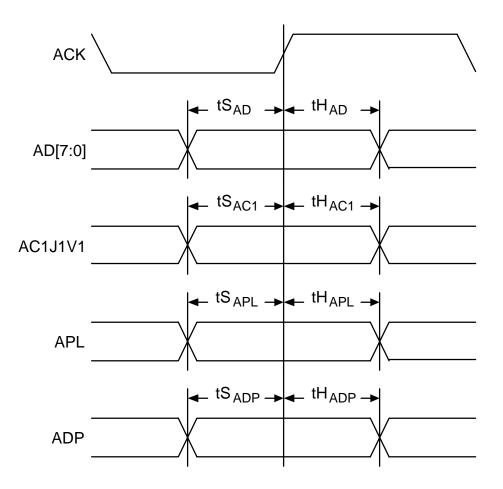

| FIGURE 50                | - ADD BUS INPUT TIMING       |                                 | 189                 |

| FIGURE 51                | - TRANSMIT OVERHEAD INPUT T  | IMING                           | 190                 |

| FIGURE 52                | - TRANSMIT OVERHEAD OUTPUT   | T TIMING                        | 190                 |

| FIGURE 53                | - TRANSMIT ALARM PORT INPUT  | TIMING                          | 191                 |

| FIGURE 54                | - TRANSMIT STREAM INPUT TIMI | NG                              | 192                 |

| FIGURE 55                | - TRANSMIT STREAM OUTPUT TI  | MING                            | 193                 |

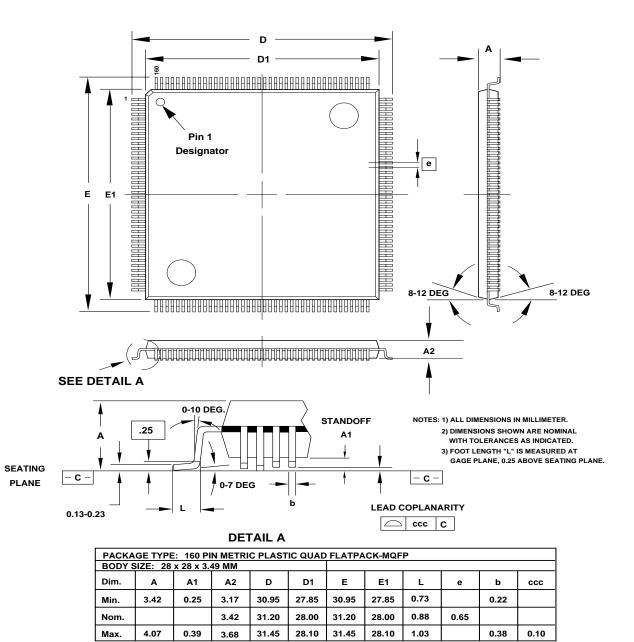

| FIGURE 56                | - 160 PIN COPPER LEADFRAME I | PLASTIC QUAD FLAT PACK (R SUFFI | X):196              |

ISSUE 6

SONET/SDH PATH TERMINATING TRANSCEIVER

## LIST OF TABLES

| TABLE 1 - PIN DESCRIPTION   13             |                                                             |     |  |  |

|--------------------------------------------|-------------------------------------------------------------|-----|--|--|

| TABLE 2 - PATH SIGNAL LABEL MATCH/MISMATCH |                                                             |     |  |  |

| TABLE 3- REG                               | GISTER MEMORY MAP                                           | 41  |  |  |

| TABLE 4- REC                               | CEIVE ELASTIC STORE DEPTH CONTROL                           | 89  |  |  |

| TABLE 5- TRA                               | ANSMIT ELASTIC STORE DEPTH CONTROL                          | 115 |  |  |

| TABLE 6-TES                                | ST MODE REGISTER MEMORY MAP                                 | 128 |  |  |

| TABLE 7 - D.C.                             | . CHARACTERISTICS                                           | 171 |  |  |

| TABLE 8- MIC                               | ROPROCESSOR INTERFACE READ ACCESS (FIGURE 38, FIGURE 39)    | 174 |  |  |

| TABLE 9- MIC                               | ROPROCESSOR INTERFACE WRITE ACCESS (FIGURE 40, FIGURE 41)   | 177 |  |  |

| TABLE 10                                   | - RECEIVE LINE INPUT TIMING (FIGURE 42)                     |     |  |  |

| TABLE 11                                   | - RECEIVE ALARM OUTPUT TIMING (FIGURE 43)                   |     |  |  |

| TABLE 12                                   | - RECEIVE OVERHEAD AND ALARM PORT OUTPUT TIMING (FIGURE 44) | 183 |  |  |

| TABLE 13                                   | - RECEIVE TANDEM CONNECTION INPUT TIMING (FIGURE 45)        | 184 |  |  |

| TABLE 14                                   | - DROP BUS INPUT TIMING (FIGURE 46)                         | 185 |  |  |

| TABLE 15                                   | - DROP BUS OUTPUT TIMING (FIGURE 47)                        | 186 |  |  |

| TABLE 16                                   | - GENERATED BUS INPUT TIMING (FIGURE 48)                    |     |  |  |

| TABLE 17                                   | - GENERATED BUS OUTPUT TIMING (FIGURE 49)                   |     |  |  |

| TABLE 18                                   | - ADD BUS INPUT TIMING (FIGURE 50)                          |     |  |  |

| TABLE 19                                   | - TRANSMIT OVERHEAD INPUT TIMING (FIGURE 51)                | 189 |  |  |

| TABLE 20                                   | - TRANSMIT OVERHEAD OUTPUT TIMING (FIGURE 52)               | 190 |  |  |

| TABLE 21                                   | - TRANSMIT ALARM PORT INPUT TIMING (FIGURE 53)              | 191 |  |  |

| TABLE 22                                   | - TRANSMIT STREAM INPUT TIMING (FIGURE 54)                  | 191 |  |  |

| TABLE 23                                   | - TRANSMIT STREAM OUTPUT TIMING (FIGURE 55)                 |     |  |  |

**ISSUE 6**

SONET/SDH PATH TERMINATING TRANSCEIVER

#### 1 FEATURES

- Monolithic SONET/SDH Path Terminating Transceiver that terminates the path overhead of one or three STS-1 (AU3) paths or a single STS-3c (AU4) path.

- Maps one or three STS-1 (AU3) payloads or a single STS-3c (AU4) payload to system timing reference, accommodating plesiochronous timing offsets between the references through pointer processing.

- Operates at 19.44 MHz or 6.48 MHz, processing a duplex 19.44 Mbyte/s or 6.48 Mbyte/s data stream.

- Supports line loopback from line side receive stream to transmit stream and diagnostic loopback from ADD bus interface to DROP bus interface.

- Operates in conjunction with the PM5343 STXC, or with the PM5312 STTX and PM5318 SIPO to form a complete physical interface up to photonics.

- Provides a generic 8-bit microprocessor bus interface for configuration, control, and status monitoring.

- Low power, +5 Volt, CMOS technology, TTL compatible inputs and outputs.

- 160 pin plastic quad flat pack (PQFP) package.

#### **<u>1.1 The receiver section:</u>**

- Operates in STS-3 (AU3) or STS-3c (AU4) mode.

- Accepts a byte serial line side multiplex of three STS-1 (AU3) streams or a single STS-3c (AU4) stream, interprets the STS (AU) pointer bytes (H1, H2, and H3), and extracts the synchronous payload envelope(s) and inserts the synchronous payload envelope(s) into a bus referenced to system timing, using pointer processing.

- Extracts and processes the three STS-1 (AU3) path overhead streams or the single STS-3c (AU4) path overhead stream.

- Detects loss of pointer (LOP).

- Detects loss of tributary multiframe (LOM).

- Detects path alarm indication signal (AIS).

- Detects path FERF alarm.

- Extracts and serializes the entire path overhead from the three STS-1 (AU3) or single STS-3c (AU4) stream. Identifies the positions of the path overhead bytes in the serialized streams.

- Extracts the path signal label (C2) byte into an internal register and detects for path signal label unstable and for signal label mismatch with the expected signal label that is downloaded by the microprocessor.

- Extracts the 64 byte or 16 byte path trace (J1) message into an internal register bank.

- Detects for unstable path trace message and mismatch with the expected path trace message that is downloaded by the microprocessor.

- Detects received path BIP-8 and counts received path BIP-8 errors for performance monitoring purposes. Path BIP-8 errors are also available on an output pin. BIP-8 errors are selectable to be treated on a bit basis or block basis.

- Counts received path far end block errors (FEBEs) for performance monitoring purposes.

- Extracts the three STS-1 (AU3) payloads or single STS-3c (AU4) payload and presents it on a byte serial bus.

- Supports Telecombus interfaces by indicating the location of the STS identification byte (C1), the path trace byte(s) (J1), the first tributary overhead byte(s) (V1), and all synchronous payload envelope bytes in the byte serial stream. Also generates bus parity.

- Accomodates phase and frequency differences between the receive stream and the DROP bus via pointer adjustments in the DROP bus.

- Supports tandem connection origination applications by sourcing a new tandem path maintenance byte (Z5) reporting the received BIP-8 errors and the data link message and correcting subsequent path BIP-8 bytes (B3) to reflect the change in Z5.

- Supports tandem connection termination applications by accumulating the incoming error count (IEC) and extracting the tandem connection data link carried in the tandem path maintenance byte (Z5).

• Maintains existing pointer value during incoming signal failures in tandem path terminating mode.

PMC-Sierra, Inc.

- Maintains the existing tributary multiframe sequence on the H4 byte until a new phase alignment has been verified.

- Provides a "Telecombus" line side receive interface when path termination is done by an upstream device.

- Provides a serial alarm port communication of FEBE and path FERF alarms to the transmit stream in the returning direction.

#### **1.2 The transmitter section:**

- Operates in STS-1 (AU3) or STS-3c (AU4) mode.

- Accepts a byte serial multiplex of three STS-1 (AU3) streams or an STS-3c (AU4) stream, extracts the synchronous payload envelope(s) and inserts the synchronous payload envelope(s) with a generated pointer into the transmit system, using pointer processing.

- Supports system side "Telecombus" interfaces by accepting indications of the location of the STS identification byte (C1), the path trace byte(s) (J1), the first tributary overhead byte(s) (V1), and all synchronous payload envelope bytes in the byte serial stream.

- Provides line side "Telecombus" interface on the transmit stream indicating the location of the STS identification byte (C1), the path trace byte(s) (J1), the first tributary overhead byte(s) (V1), and all synchronous payload envelope bytes.

- Accomodates phase and frequency differences between the ADD bus and the transmit stream via pointer adjustments in the transmit stream.

- Optionally inserts STS path alarm indication signal (AIS).

- Optionally inserts STS path FERF alarm.

- Inserts the path overhead bytes in the three STS-1 (AU3) or single STS-3c (AU4) stream. The path overhead bytes may be sourced from internal registers or from bit serial path overhead input streams. Path overhead insertion may also be disabled.

- Optionally calculates and inserts path BIP-8 error detection codes.

| PMC     | PMC-Sierra, Inc. |

|---------|------------------|

| ISSUE 6 | SONE             |

- Optionally inserts the path FEBE count into the path status byte (G1) based on BIP-8 errors detected in the receive path.

- Inserts the path signal label (C2) byte from an internal register.

- Inserts the 64 byte or 16 byte path trace (J1) message from an internal register bank.

- Errors may be inserted in the path BIP8 byte (B3) for diagnostic purposes.

- Optionally inserts all-ones payload data for unequipped operations.

- Optionally generates cyclical tributary multiframe pattern.

- Supports in-band error reporting of BIP-8 and path alarms in the path status byte (G1).

ISSUE 6

SONET/SDH PATH TERMINATING TRANSCEIVER

#### 2 APPLICATIONS

- SONET/SDH Add Drop Multiplexers

- SONET/SDH Terminal Multiplexers

- SONET/SDH Cross Connects

- SONET/SDH Tandem Path Termination Equipment

- SONET/SDH Test Equipment

SONET/SDH PATH TERMINATING TRANSCEIVER

#### 3 REFERENCES

- 1. American National Standard for Telecommunications Digital Hierarchy -Optical Interface Rates and Formats Specification, ANSI T1.105-1988.

- 2. American National Standard for Telecommunications Layer 1 In-Service Digital Transmission Performance Monitoring, T1X1.3/93-005R1, April 1993.

- 3. Bell Communications Research SONET Transport Systems: Common Generic Criteria, TR-TSY-000253, Issue 2, December 1991.

- 4. CCITT Study Group XVIII Report R 105, Geneva, 9 19 June 1992.

- 5. CCITT Recommendation G781M, 13 October, 1992.

- 6. ETSI DE/TM1015, "Generic Functional Requirement for SDH Transmission Equipment", Version 0.4, February 1993.

- 7. CCITT Study Group XVII Contribution D2166 "Tandem Connection / Tandem Connection Bundle Maintenance Working Solution", June 1992.

PM5344 SPTX

SONET/SDH PATH TERMINATING TRANSCEIVER

#### 4 APPLICATION EXAMPLES

**ISSUE 6**

The following two examples show the SPTX used in typical SONET/SDH network equipment applications. In the first example, the SPTX is paired with the PM5343 STXC 155 Mbit/s Section and Line overhead terminating transceiver to provide a complete 155 Mbit/s SONET STS-3 or STS-3c/SDH STM-1 interface. In the second example, four SPTX chips are used in conjunction with the PM5312 STTX 622 Mbit/s Section and Line overhead terminating transceiver to provide a complete 622 Mbit/s SONET STS-12/SDH STM-4 interface. In both cases external clock recovery and synthesis is available from a number of commercial sources (additional information is available from PMC).

# Figure 2 - 622 Mbit/s STS-12/STM-4 Add-Drop Multiplexer Aggregate Interface

PMC-Sierra, Inc.

PM5344 SPTX

DATA SHEET PMC-930531

ISSUE 6

SONET/SDH PATH TERMINATING TRANSCEIVER

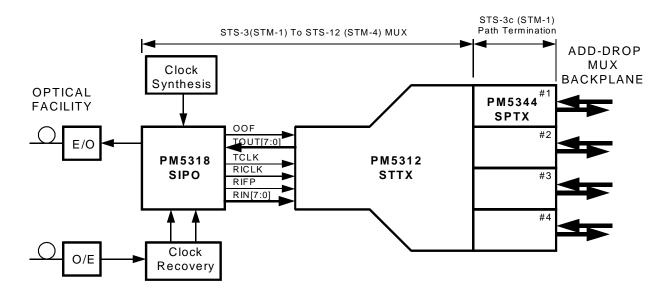

#### 5 BLOCK DIAGRAM

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS' INTERNAL USE 9

PM5344 SPTX

**ISSUE 6**

DATA SHEET PMC-930531

SONET/SDH PATH TERMINATING TRANSCEIVER

#### 6 DESCRIPTION

The PM5344 SPTX SONET/SDH Path Terminating Transceiver is a monolithic integrated circuit that implements payload alignment and path termination for three STS-1 (AU3) paths or a single STS-3c (AU4) path, mapping these payloads onto a Telecombus-like system backplane.

The SPTX operates in conjunction with the PM5343 STXC SONET/SDH Transport Terminating Transceiver to form a complete system for terminating section, line, and path overhead of a SONET STS-3 (SDH STM-1) or SONET STS-1 electrical interface. Four SPTX devices operate in conjunction with the PM5712 SLIM SONET/SDH Line Interface Module to form a complete system for terminating section, line, and path overhead of a SONET STS-12 (SDH STM-4) electrical interface.

The SPTX provides receive path termination for a SONET STS-1, STS-3 or STS-3c stream, or equivalently, an AU3 or an SDH STM-1 stream carrying three AU3s or one AU4. The SPTX interprets the received payload pointers (H1, H2) and extracts the synchronous payload envelope (virtual container). The extracted SPE (VC) is placed on a Telecombus DROP bus. Frequency offsets (e.g., due to plesiochronous network boundaries, or the loss of a primary reference timing source) and phase differences (due to normal network operation) between the received data stream and the DROP bus are accommodated by pointer adjustments in the DROP bus. In addition to its basic processing of the received SONET/SDH overhead, the SPTX provides convenient access to all overhead bytes, which are extracted and serialized on lower rate interfaces, allowing additional external processing of overhead, if desired.

The SPTX provides transmit path origination for a SONET STS-1, STS-3 or STS-3c stream, or equivalently, an AU3 or an SDH STM-1 stream carrying three AU3s or one AU4. The SPTX generates the transmit payload pointers (H1, H2) and inserts the synchronous payload envelope (virtual container) from a Telecombus ADD bus into the transmit stream. Frequency offsets (e.g., due to plesiochronous network boundaries, or the loss of a primary reference timing source) and phase differences (due to normal network operation) between the transmit data stream and the ADD bus are accommodated by pointer adjustments in the transmit stream. In addition to its basic processing of the transmit SONET/SDH overhead, the SPTX provides convenient access to all overhead bytes, which are inserted serially on lower rate interfaces, allowing additional external sourcing of overhead, if desired. The SPTX also supports the insertion of a large variety of errors into the transmit stream, such as bit interleaved parity errors, and inverted NDF flags, which are useful for system

ISSUE 6

SONET/SDH PATH TERMINATING TRANSCEIVER

diagnostics and tester applications. The SPTX supports in-band error reporting where the path status byte (G1) inserted in the DROP bus reflects the number of BIP-8 errors detected and the path FERF status. The SPTX can be programmed to pass the path status byte on the ADD bus through unmodified. This feature allows the transmit path processor to be located remotely to the receive processor without having to incur the cost of routing an alarm port.

The SPTX supports tandem connection termination applications where the tandem connection maintenance byte (Z5) carries the incoming BIP-8 error count, a tandem data link, and a path AIS code. The incoming error count is accumulated and the receive data link is serialized for external processing. A new data link can be inserted from a low speed serial input. An incoming signal failure alarm (ISF) is used to convey path AIS in place of all-ones in the pointer (H1, H2).

The SPTX maintains a large number of statistics for performance monitoring purposes. BIP-8 errors, and tandem path incoming error counts are accumulated. In addition, the SPTX is selectable to accumulate positive and negative pointer justifications that it receives or justifications that it generates on the DROP bus. It also accumulates positive and negative pointer justifications in the transmit stream. Excessive justifications may be indicative of clock synchronization failures.

In STS-3c, STS-3 (AU4, three AU3s) applications, no auxiliary high speed clocks are required as the SPTX operates from a set of plesiochronous 19.44 MHz clocks. In STS-1 (single AU3) applications, the SPTX operates from a set of plesiochronous 6.48 MHz clocks. The SPTX is configured, controlled and monitored via a generic 8-bit microprocessor bus interface.

The SPTX is implemented in low power, +5 Volt, CMOS technology. It has TTL compatible inputs and outputs and is packaged in a 160 pin PQFP package.

ISSUE 6

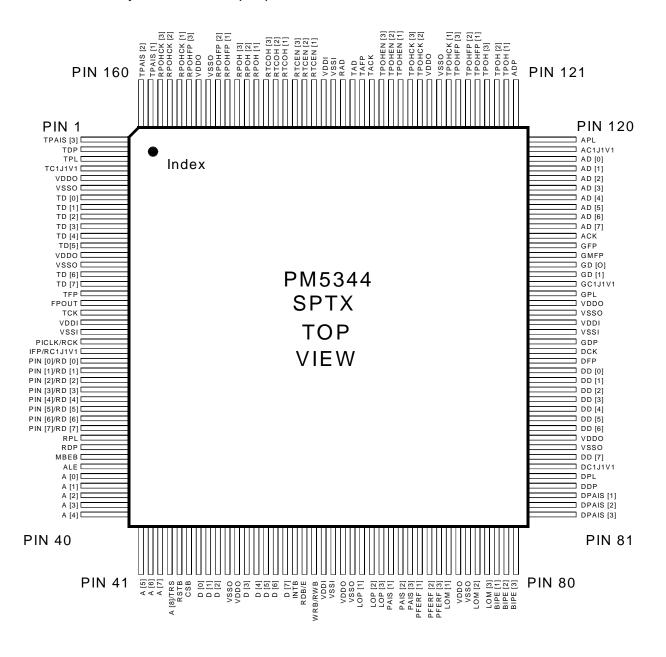

#### 7 PIN DIAGRAM

The SPTX is packaged in an 160 pin PQFP package having a body size of 28 mm by 28 mm and a pin pitch of 0.65 mm.

ISSUE 6

PMC PMC-Sierra, Inc.

SONET/SDH PATH TERMINATING TRANSCEIVER

#### 8 PIN DESCRIPTION

| Pin Name | Туре  | Pin           | Function                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------|-------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

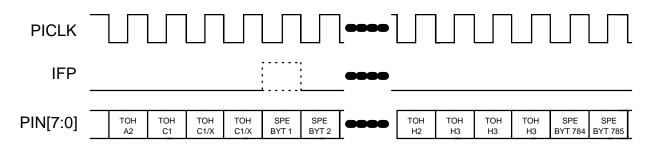

| PICLK /  | Input | <b>No.</b> 22 | The parallel input clock (PICLK) provides timing for sampling the receive<br>SONET/SDH stream, PIN[7:0] when external path termination is disabled. PICLK<br>is nominally a 19.44 MHz or 6.48 MHz, 50% duty cycle clock. Inputs PIN[7:0] and<br>IFP are sampled on the rising edge of PICLK. Inputs RPL and RDP are ignored.<br>Outputs LOP[3:1], PAIS[3:1], and PFERF[3:1] are updated on the rising edge of<br>PICLK.                   |

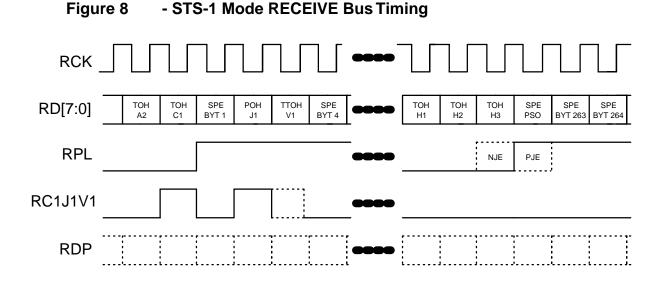

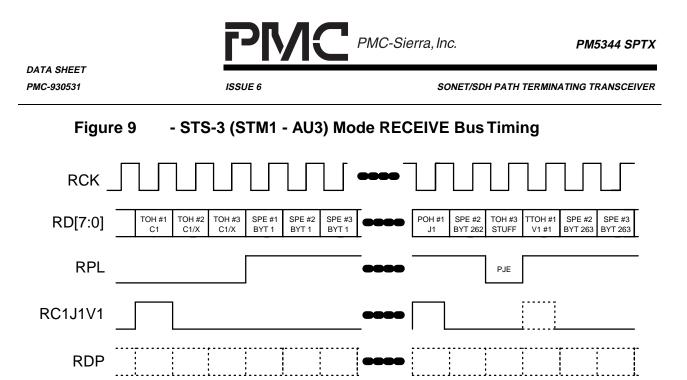

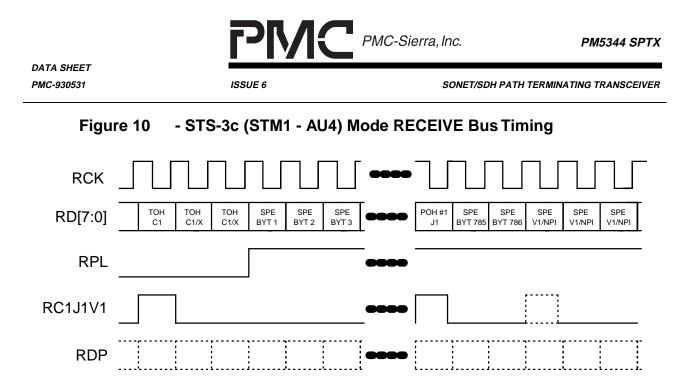

| RCK      |       |               | The RECEIVE bus clock (RCK) provides timing for the RECEIVE bus interface when external path termination is enabled. RCK is nominally a 19.44 MHz or 6.48 MHz, 50% duty cycle clock. Outputs LOP[3:1], LOM[3:1], PAIS[3:1], PFERF[3:1], BIPE[3:1], RAD, RPOH[3:1], RPOHFP[3:1], are RPOHCLK[3:1] are inactive. Inputs RTCEN[3:1] and RTCOH[3:1] are ignored. Inputs RD[7:0], RC1J1V1, RPL, and RDP are sampled on the rising edge of RCK. |

| PIN[7]   | Input | 31            | The parallel receive data bus (PIN[7:0]) carries the SONET/SDH frame in byte                                                                                                                                                                                                                                                                                                                                                              |

| PIN[6]   |       | 30            | serial format when external path termination is disabled. PIN[7] is the most                                                                                                                                                                                                                                                                                                                                                              |

| PIN[5]   |       | 29            | significant bit (corresponding to bit 1 of each serial word, the first bit transmitted).<br>PIN[0] is the least significant bit (corresponding to bit 8 of each serial word, the last                                                                                                                                                                                                                                                     |

| PIN[4]   |       | 28            | bit transmitted). PIN[7:0] is sampled on the rising edge of PICLK.                                                                                                                                                                                                                                                                                                                                                                        |

| PIN[3]   |       | 27            |                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| PIN[2]   |       | 26            |                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| PIN[1]   |       | 25            |                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| PIN[0] / |       | 24            |                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| RD[7]    |       |               | The RECEIVE bus data (RD[7:0]) carries the SONET/SDH frame in byte serial                                                                                                                                                                                                                                                                                                                                                                 |

| RD[6]    |       |               | format when external path termination is enabled. RD[7] is the most significant bit                                                                                                                                                                                                                                                                                                                                                       |

| RD[5]    |       |               | (corresponding to bit 1 of each serial word, the first bit transmitted). RD[0] is the least significant bit (corresponding to bit 8 of each serial word, the last bit                                                                                                                                                                                                                                                                     |

| RD[4]    |       |               | transmitted). RD[7:0] is sampled on the rising edge of RCK.                                                                                                                                                                                                                                                                                                                                                                               |

| RD[3]    |       |               |                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| RD[2]    |       |               |                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| RD[1]    |       |               |                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| RD[0]    |       |               |                                                                                                                                                                                                                                                                                                                                                                                                                                           |

## Table 1 - Pin Description

ISSUE 6

| Pin Name                            | Туре   | Pin<br>No.        | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------------------------------|--------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IFP /                               | Input  | 23                | The active high framing position signal (IFP) indicates when the first byte of the synchronous payload envelope (SPE byte 1 of STS-1 #1) is available on the PIN[7:0] bus when external path termination is disabled. Note that IFP has a fixed relationship to the SONET/SDH frame; the start of the SPE is determined by the STS (AU) pointer and may change relative to IFP. IFP is sampled on the rising edge of PICLK.                                                                                                                                                                                                                                                                         |

| RC1J1V1                             |        |                   | The receive composite timing signal (RC1J1V1) indicates the frame, payload and tributary multiframe boundaries on the RECEIVE bus when external path termination is enabled. RC1J1V1 pulses high with the RECEIVE bus payload active signal (RPL) set low to mark the first STS-1 identification byte or equivalently the STM identification byte. RC1J1V1 pulses high with RPL set high to mark the path trace byte (J1). Optionally, the RC1J1V1 signal pulses high with RPL set high on the V1 byte to indicate tributary multiframe boundaries. RC1J1V1 is sampled on the rising edge of RCK.                                                                                                   |

| RPL                                 | Input  | 32                | The RECEIVE bus payload active signal (RPL) indicates when RD[7:0] is carrying a payload byte. It is set high during path overhead and payload bytes and low during transport overhead bytes. RPL is set high during the H3 byte to indicate a negative pointer justification event and set low during the byte following H3 to indicate a positive pointer justification event. RPL is ignored when external path termination is disabled. RPL is sampled on the rising edge of RCK.                                                                                                                                                                                                               |

| RDP                                 | Input  | 33                | The RECEIVE bus data parity signal (RDP) indicates the parity of the RECEIVE bus signals. The RECEIVE data bus (RD[7:0]) is always included in parity calculations. Internal register bits controls the inclusion of the RPL and RC1J1V1 signals in parity calculations and the sense (odd/even) of the parity. RDP is ignored when external path termination is disabled. RDP is sampled on the rising edge of RCK.                                                                                                                                                                                                                                                                                |

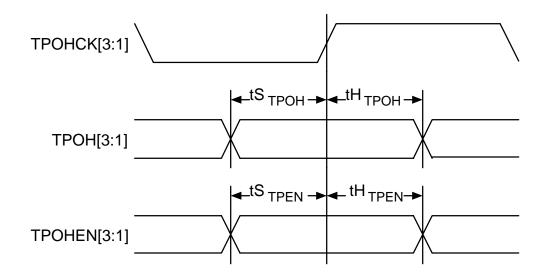

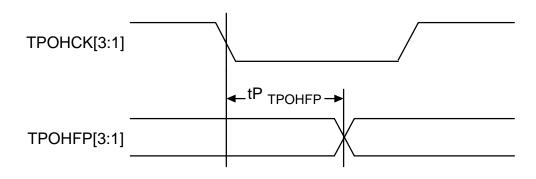

| RPOHCK[3]<br>RPOHCK[2]<br>RPOHCK[1] | Output | 158<br>157<br>156 | The receive path overhead clocks (RPOHCK[3:1]) provide timing to process the BIPE[3:1] signals, to insert tandem path incoming error count and data link, and to sample the extracted path overhead for the corresponding STS-1 (AU3) stream.<br>RPOHCK[3:1] are nominally 576 kHz clocks. In STS-3c (AU4) mode or STS-1 mode, only RPOHCK[1] is active. RTCEN[3:1], and RTCOH[3:1] are sampled on the rising edge of the corresponding RPOHCK signal. BIPE[3:1], RPOH[3:1] and RPOHFP[3:1] are updated on the falling edge of the corresponding RPOHCK signal.<br>RPOHCK[1] provides timing for the serial receive alarm indication port (RAD), which is updated on the falling edge of RPOHCK[1]. |

ISSUE 6

| Pin Name                            | Туре   | Pin<br>No.        | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------------------------|--------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RPOH[3]<br>RPOH[2]<br>RPOH[1]       | Output | 150<br>149<br>148 | The receive path overhead data signals (RPOH[3:1]) contain the path overhead bytes (J1, B3, C2, G1, F2, H4, Z3, Z4, and Z5) extracted from the path overhead of the corresponding STS-1 (AU3) stream. In STS-3c (AU4) mode or STS-1 mode, only RPOH[1] is active. Each RPOH signal is updated on the falling edge of the corresponding RPOHCK signal.                                                                                                                                                                                                                                                      |

|                                     |        |                   | RPOH[3:1] are inactive when external path termination is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| RPOHFP[3]<br>RPOHFP[2]<br>RPOHFP[1] | Output | 155<br>152<br>151 | The receive path overhead frame position signals (RPOHFP[3:1]) may be used to locate the individual path overhead bits in the path overhead data stream for the corresponding STS-1 (AU3) stream. Each RPOHFP[3:1] signal is logic 1 when bit 1 (the most significant bit) of the path trace byte (J1) is present in the corresponding RPOH stream. In STS-3c (AU4) mode or STS-1 mode, only RPOHFP[1] is active. Each RPOHFP signal is updated on the falling edge of the corresponding RPOHCK signal.                                                                                                    |

|                                     |        |                   | RPOHFP[1] may be used to located the BIP error count and path FERF indication<br>bits on the receive alarm port data signal (RAD). RPOHFP[1] is logic 1 when the<br>first of eight BIP error positions from the first STS-1 (AU3) or the STS-3c (AU4)<br>stream is present on the receive alarm data signal (RAD).                                                                                                                                                                                                                                                                                         |

|                                     |        |                   | RPOHFP[3:1] are inactive when external path termination is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| RTCEN[3]<br>RTCEN[2]<br>RTCEN[1]    | Input  | 144<br>143<br>142 | The receive tandem connection overhead insert enable signals (RTCEN[3:1]) control the insertion of incoming error count and data link in the tandem connection maintenance byte (Z5), on a bit-by-bit basis. When RTCEN is set high, the data on the corresponding RTCOH stream is inserted into the associated bit in the Z5 byte. RTCEN has significance only during the the J1 byte positions in the RPOHCK clock sequence and is ignored at all other times. In STS-3c (AU4) mode or STS-1 mode, only RTCEN[1] is significant. RTCEN is sampled on the rising edge of the corresponding RPOHCK signal. |

|                                     |        |                   | RTCEN[3:1] are ignored when external path termination is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| RTCOH[3]<br>RTCOH[2]<br>RTCOH[1]    | Input  | 147<br>146<br>145 | The receive tandem connection overhead data signals (RTCOH[3:1]) contain the incoming error count and data link message to be inserted into the tandem connection maintenance byte (Z5). When RTCEN is set high, the values sampled on RTCOH is inserted into the Z5 byte. When RTCEN is set low, the IEC field of Z5 reports the incoming path BIP error count and the data link field is set to all ones. In STS-3c (AU4) mode or STS-1 mode, only RTCEN[1] is significant. RTCOH is sampled on the rising edge of the corresponding RPOHCK signal.                                                      |

ISSUE 6

| Pin Name                         | Туре   | Pin<br>No.     | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------------------------------|--------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BIPE[3]<br>BIPE[2]<br>BIPE[1]    | Output | 80<br>79<br>78 | The bit interleaved parity error signals (BIPE[3:1]) signal is set high for one<br>RPOHCK period for each path BIP-8 error detected (up to eight per frame) or once<br>if any of the BIP-8 bits are in error depending on whether BIP-8 errors are treated<br>on a bit or block basis. Path BIP-8 errors are detected by comparing the extracted<br>path BIP-8 byte (B3) with the computed BIP-8 for the previous frame. In STS-3c<br>(AU4) mode or STS-1 mode, only BIP[1] is active. BIPE[3:1] is updated on the<br>falling edge of RPOHCK.<br>BIPE[3:1] are inactive when external path termination is enabled.                                                                                                                                                                                                                                                                 |

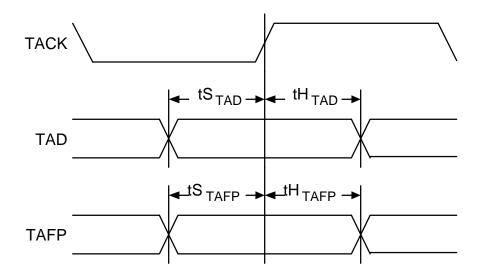

| RAD                              | Output | 139            | The receive alarm port data signal (RAD) contains the path BIP error count and the path FERF status of the three receive STS-1 (AU3) streams or the single STS-3c (AU4) stream. RAD is updated on the falling edge of RPOHCK[1].<br>RAD is inactive when external path termination is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| LOP[3]<br>LOP[2]<br>LOP[1]       | Output | 66<br>65<br>64 | The loss of pointer signals (LOP[3:1]) indicate the loss of pointer state in the associated SONET/SDH stream. LOP is set high when invalid STS pointers are received in eight consecutive frames, or if eight consecutive enabled NDFs are detected in the corresponding STS-1 (AU3) stream. The loss of pointer state is exited (LOP set low) when the same valid STS pointer, with disabled NDF, is detected for three consecutive frames. In STS-3c (AU4) mode, only LOP[1] is active and loss of pointer state (LOP[1]) depends only on the first of three H1, H2 bytes; the value of the concatenation indicators do not affect LOP[1] signal. In STS-1 mode, only LOP[1] is active. LOP[3:1] are updated on the rising edge of PICLK.                                                                                                                                        |

| PAIS[3]<br>PAIS[2]<br>PAIS[1]    | Output | 69<br>68<br>67 | LOP[3:1] are inactive when external path termination is enabled.<br>The path alarm indication signals (PAIS[3:1]) indicate the STS path AIS state<br>associated with the SONET/SDH stream. PAIS is set high when an all ones<br>pattern is observed in the STS-1 pointer bytes (H1, and H2) for three consecutive<br>frames in the corresponding STS-1 (AU3) stream. Path AIS is removed when the<br>same valid pointer with normal NDF is detected for three consecutive frames or a<br>single valid pointer with NDF set is received. In STS-3c (AU4) mode, only PAIS[1]<br>is active and depends only on the first of three H1, H2 bytes; the value of the<br>concatenation indicators do not affect PAIS[1]. In STS-1 mode, only PAIS[1] is<br>active. PAIS[3:1] are updated on the rising edge of PICLK.<br>PAIS[3:1] are inactive when external path termination is enabled. |

| PFERF[3]<br>PFERF[2]<br>PFERF[1] | Output | 72<br>71<br>70 | The path far end receive failure signals (PFERF[3:1]) indicate the STS path FERF state associated with the SONET/SDH stream. PFERF is set high when the path FERF alarm bit (bit 5) of the STS path status (G1) byte is set high for five consecutive frames. STS path FERF is removed when bit 5 of the G1 byte is set low for five consecutive frames. In STS-3c (AU4) mode and STS-1 mode, only PFERF[1] is active. PFERF[3:1] are updated on the rising edge of PICLK. PFERF[3:1] are inactive when external path termination is enabled.                                                                                                                                                                                                                                                                                                                                      |

ISSUE 6

| Pin Name                                                             | Туре   | Pin<br>No.                                   | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------------------------------------------------------------|--------|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LOM[3]<br>LOM[2]<br>LOM[1]                                           | Output | 77<br>76<br>73                               | The loss of multiframe signals (LOM[3:1]) indicate the tributary multiframe synchronization status associated with the SONET/SDH stream. LOM is set low when a correct sequence has been detected for four consecutive frames. LOM is set high if a correct four frame sequence is not detected in eight frames. In STS-3c (AU4) mode and STS-1 mode, only LOM[1] is active. LOM[3:1] are updated on the rising edge of PICLK.                                                                                                                                    |

|                                                                      |        |                                              | LOM[3:1] are inactive when external path termination is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| DCK                                                                  | Input  | 98                                           | The DROP bus clock (DCK) provides timing for the DROP bus interface. DCK is nominally a 19.44 MHz or 6.48 MHz, 50% duty cycle clock. Frequency offsets between PICLK/RCK and DCK are accommodated by pointer justification events on the DROP bus. DFP is sampled on the rising edge of DCK. Outputs DPL, DC1J1V1, DDP and DD[7:0] are updated on the rising edge of DCK.                                                                                                                                                                                         |

| DFP                                                                  | Input  | 97                                           | The active high DROP bus reference frame position signal (DFP) indicates when<br>the first byte of the synchronous payload envelope (SPE byte 1 of STS-1 #1) is<br>available on the DD[7:0] bus. Note that DFP has a fixed relationship to the<br>SONET/SDH frame; the start of the SPE is determined by the STS (AU) pointer<br>and may change relative to DFP. DFP is sampled on the rising edge of DCK.                                                                                                                                                        |

| DPAIS[3:1]                                                           | Input  | 81<br>82<br>83                               | The active high DROP bus path alarm indication signals (DPAIS[3:1]) controls the insertion of path AIS in the DROP bus DD[7:0]. A high level on DPAIS forces the insertion of the all ones pattern into the complete SPE, and the payload pointer bytes (H1, H2, and H3). DROP bus path AIS insertion can also be inserted via register access or in response to ISF code in terminating tandem connection termination equipment applications. In STS-3c (AU4) mode or STS-1 mode, only DPAIS[1] is significant. DPAIS[3:1] is sampled on the rising edge of DCK. |

| DD[7]<br>DD[6]<br>DD[5]<br>DD[4]<br>DD[3]<br>DD[2]<br>DD[1]<br>DD[0] | Output | 87<br>90<br>91<br>92<br>93<br>94<br>95<br>96 | The DROP bus data (DD[7:0]) contains the SONET/SDH receive payload data.<br>The transport overhead bytes, with the exception of the H1, H2 pointer bytes, are<br>set to zeros. The fixed stuff columns in a tributary mapped SPE (VC) may also be<br>optionally set to zero or NPI. DD[7] is the most significant bit (corresponding to bit<br>1 of each serial word, the first bit transmitted). DD[0] is the least significant bit<br>(corresponding to bit 8 of each serial word, the last bit transmitted). DD[7:0] is<br>updated on the rising edge of DCK.  |

| DPL                                                                  | Output | 85                                           | The active high DROP bus payload active signal (DPL) indicates when the DD[7:0] is carrying a payload byte. It is set high during path overhead and payload bytes and low during transport overhead bytes. DPL is set high during the H3 byte to indicate a negative pointer justification event and set low during the byte following H3 to indicate a positive pointer justification event. DPL is updated on the rising edge of DCK.                                                                                                                           |

ISSUE 6

| Pin Name | Туре   | Pin<br>No. | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------|--------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DC1J1V1  | Output | 86         | The DROP bus composite timing signal (DC1J1V1) indicates the frame, payload<br>and tributary multiframe boundaries on the DROP data bus DD[7:0]. DC1J1V1<br>pulses high with the DROP bus payload active signal (DPL) set low to mark the first<br>STS-1 Identification byte or equivalently the STM identification byte (C1).<br>DC1J1V1 pulses high with DPL set high to mark the path trace byte (J1).<br>Optionally, the DC1J1V1 signal pulses high on the V1 byte to indicate tributary<br>multiframe boundaries. DC1J1V1 is updated on the rising edge of DCK. |

| DDP      | Output | 84         | The DROP bus data parity signal (DDP) indicates the parity of the DROP bus signals. The DROP data bus (DD[7:0]) is always included in parity calculations. The internal register bits control the inclusion of the DPL and DC1J1V1 signals in parity calculation and the sense (odd/even) of the parity. DDP is updated on the rising edge of DCK.                                                                                                                                                                                                                   |

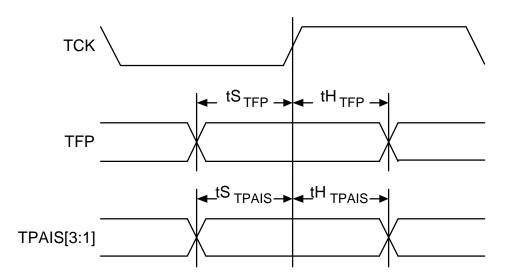

| ACK      | Input  | 110        | The ADD bus clock (ACK) provides timing for the ADD bus and the GENERATED bus interfaces. ACK is nominally a 19.44 MHz or 6.48 MHz, 50% duty cycle clock. Inputs AD[7:0], APL, AC1J1V1, GFP and GMFP are sampled on the rising edge of ACK. Outputs GPL, GC1J1V1, and GD[1:0] are updated on the rising edge of ACK.                                                                                                                                                                                                                                                 |

| AD[7]    | Input  | 111        | The ADD bus data (AD[7:0]) contains the SONET/SDH transmit payload data. The                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| AD[6]    |        | 112        | transport overhead bytes, including the H1, H2 pointer bytes, are ignored. The                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| AD[5]    |        | 113        | phase relation of the SPE (VC) to the transport frame is determined by the ADD bus composite timing signal (AC1J1V1). AD[7] is the most significant bit                                                                                                                                                                                                                                                                                                                                                                                                              |

| AD[4]    |        | 114        | (corresponding to bit 1 of each serial word, the first bit transmitted). AD[0] is the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |