# 1K Bit Serial Electrically Erasable PROM

#### **FEATURES**

- Operating temperature range

- KM93C46: Commercial

- KM93C46I: Industrial

- Single 5 Volt supply

- High performance advanced CMOS technology - Reliable floating gate technology

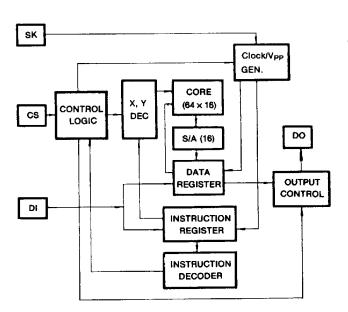

- 64 × 16 serial read/write memory

- TTL compatible

- · Low power dissipation

- Standby current: 250μA (TTL)

- Active current: 3 mA (TTL)

- Self-timed programming cycle

- Device status signal during programming

- 100,000 Cycle Endurance

- Available in plastic DIP and SOP

#### **GENERAL DESCRIPTION**

67E D

The KM93C46 is a CMOS 5V-Only 1,024 bit nonvolatile, sequential EEPROM. It is fabricated with the well defined floating gate CMOS technology using Fowler-Nordheim tunneling for erasing and pro-

The KM93C46 is organized as 64 registers of 16 bits each, which can be read/written serially by a microprocessor. It operates in a self-timed mode with the DO pin indicating the READY/BUSY status of the device.

The KM93C46 is designed for applications up to 100,000 erase/write cycles per word and over 10 years of data retention.

# **FUNCTIONAL BLOCK DIAGRAM**

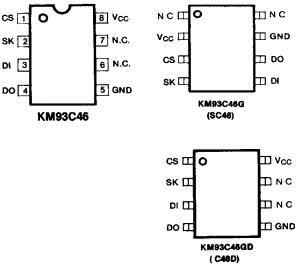

#### PIN CONFIGURATION

| Pin Name        | Pin Function       |  |  |

|-----------------|--------------------|--|--|

| CS              | Chip Select        |  |  |

| SK              | Serial Data Clock  |  |  |

| DI              | Serial Data Input  |  |  |

| DO              | Serial Data Output |  |  |

| N.C.            | No Connection      |  |  |

| V <sub>cc</sub> | Power Supply       |  |  |

| GND             | Ground             |  |  |

# **CMOS EEPROM**

### **ABSOLUTE MAXIMUM RATINGS\***

| Item  Voltage on Any Pin Relative to V <sub>ss</sub> |            | Symbol              | Rating      | Unit |  |

|------------------------------------------------------|------------|---------------------|-------------|------|--|

|                                                      |            | V <sub>IN</sub>     | -0.3 to 7.0 |      |  |

| Temperature Under Blas                               | Commercial | - T <sub>bias</sub> | -10 to +125 |      |  |

|                                                      | Industrial |                     | -65 to +150 | °C   |  |

| Storage Temperature                                  |            | T <sub>etg</sub>    | -65 to +150 | °C   |  |

<sup>\*</sup>Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. Functional operation should be restricted to the conditions as detailed in the operational sections of the data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

RECOMMENDED OPERATING CONDITIONS KM93C46  $T_A=0$  to 70°C, Voltages referenced to  $V_{88}$  KM93C461  $T_A=-40$  to 85°C, Voltages referenced to  $V_{88}$

| Item           | Symbol          | Min | Тур | Max | Unit |

|----------------|-----------------|-----|-----|-----|------|

| Supply Voltage | V <sub>cc</sub> | 4.5 | 5.0 | 5.5 | ٧    |

| Supply Voltage | V <sub>ss</sub> | 0   | 0   | 0   | ٧    |

### DC CHARACTERISTICS

(Recommended operating conditions unless otherwise noted)

| Parameter              | Symbol                             | Test Condition                                           | Min         | Max                          | Unit |  |

|------------------------|------------------------------------|----------------------------------------------------------|-------------|------------------------------|------|--|

| Operating Voltage      | Vcc                                |                                                          | 4.5         | 5.5                          | ٧    |  |

| Operating Current (DC) | l <sub>cc1</sub>                   | V <sub>CC</sub> = 5.5V, CS = 2.0V, SK = 2.0V             |             | 1                            | mA   |  |

| Operating Current (AC) | I <sub>CC2</sub>                   | V <sub>CC</sub> = 5.5V, f <sub>SK</sub> = 1MHz           |             | 3                            | mA   |  |

| Standby Current (TTL)  | I <sub>SB1</sub>                   | $V_{\infty} = 5.5V$ , $CS = 0.8V$                        |             | 250                          | μΑ   |  |

| Standby Current (CMOS) | I <sub>SB2</sub>                   | $V_{\infty} = 5.5V, CS = 0V$                             |             | 100                          | μΑ   |  |

| Input Voltage Levels   | V <sub>IL</sub><br>V <sub>IH</sub> |                                                          | -0.3<br>2.0 | 0.8<br>V <sub>cc</sub> + 0.3 | V    |  |

| Output Voltage Levels  | V <sub>OL</sub><br>V <sub>OH</sub> | $I_{OL} = 2.1 \text{mA}$<br>$I_{OH} = -400 \mu \text{A}$ | 2.4         | 0.4                          | V    |  |

| Input Leakage Current  | Iu                                 | V <sub>IN</sub> = 5.5V                                   |             | 10                           | μΑ   |  |

| Output Leakage Current | ILO                                | V <sub>OUT</sub> = 5.5V, CS = 0V                         |             | 10                           | μА   |  |

# INSTRUCTION SET FOR MODE SELECTION

| instruction | nstruction SB OP Code |    | Address Data |                  | Comment                     |  |  |

|-------------|-----------------------|----|--------------|------------------|-----------------------------|--|--|

| READ        | 1                     | 10 | A5A4A3A2A1A0 | D <sub>OUT</sub> | Read register A5A4A3A2A1A0  |  |  |

| WRITE       | 1                     | 01 | A5A4A3A2A1A0 | D15-D0           | Write register A5A4A3A2A1A0 |  |  |

| ERASE       | 1                     | 11 | A5A4A3A2A1A0 | _                | Erase register A5A4A3A2A1   |  |  |

| EWEN        | 1                     | 00 | 11XXXX       | _                | Erase/Write enable          |  |  |

| EWDS        | 1                     | 00 | 00XXXX       | _                | Erase/Write disable         |  |  |

| ERAL        | 1                     | 00 | 10XXXX       | _                | Erase all registers         |  |  |

| WRAL        | 1                     | 00 | 01XXXX       | D15-D0           | Write all registers         |  |  |

The KM93C46 provides 7 instructions as shown. Note that all the instructions start with a logic "1" start bit, and following 8 bits carry the OP code and the 6-bit address for 1 of 64, 16-bit registers.

| Value                                |  |  |  |  |

|--------------------------------------|--|--|--|--|

| 0.45V to 2.4V                        |  |  |  |  |

| 20 ns                                |  |  |  |  |

| 0.8V and 2.0V                        |  |  |  |  |

| 1 TTL Gate and C <sub>L</sub> =100pF |  |  |  |  |

|                                      |  |  |  |  |

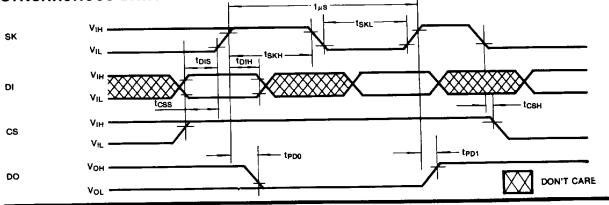

# **AC OPERATING CHARACTERISTICS**

KM93C46  $T_A = 0$  °C to 70 °C,  $V_{CC} = 5V \pm 10\%$ , unless otherwise noted. KM93C46l  $T_A = -40^{\circ}\text{C}$  to 85°C,  $V_{CC} = 5V \pm 10\%$ , unless otherwise noted.

| Parameter                            | Symbol                            | Test Condition                  | Min | Max | Unit |

|--------------------------------------|-----------------------------------|---------------------------------|-----|-----|------|

| SK Frequency                         | f <sub>SK</sub>                   |                                 |     | 1.0 | MHz  |

| SK High Time                         | tskH                              | (Note 1)                        | 500 |     | ns   |

| SK Low Time                          | tskl                              | (Note 1)                        | 250 |     | ns   |

| Chip Select Setup Time               | tcss                              |                                 | 50  |     | ns   |

| Chip Select Hold Time                | tсsн                              |                                 | 0   |     | ns   |

| Data Setup Time                      | t <sub>DIS</sub>                  |                                 | 150 |     | ns   |

| Data Hold Time                       | t <sub>DIH</sub>                  |                                 | 150 |     | ns   |

| Output High Delay Time               | t <sub>PD1</sub>                  | $V_{OL} = 0.8V, V_{OH} = 2.0V$  |     | 500 | ns   |

| Output Low Delay Time                | tepo                              | $V_{1L} = 0.45V, V_{1H} = 2.4V$ |     | 500 | ns   |

| Self-Timed Program Cycle Time        | t <sub>E/W</sub>                  |                                 |     | 10  | ms   |

| Min CS Low Time                      | tcs                               | (Note 2)                        | 250 |     | ns   |

| Rising Edge of CS to<br>Status Valid | t <sub>sv</sub>                   |                                 |     | 500 | ns   |

| Falling Edge of CS<br>to Dout High-Z | t <sub>OH</sub> , t <sub>IH</sub> |                                 |     | 100 | ns   |

Note 1: The SK frequency spec, specifies a minimum SK clock period of 1µs, therefore in a SK clock cycle  $t_{\text{SKH}} + t_{\text{SKL}}$  must be greater than or equal to  $1\mu s$ .

e.q., if  $t_{\text{SKL}}$  = 250ns then the minimum  $t_{\text{SKH}}$  = 750ns in order to meet the SK frequency specification.

Note 2: CS must be brought low for a minimum 250ns(tcs) between consecutive instruction cycles.

## TIMING DIAGRAMS SYNCHRONOUS DATA TIMING

SAMSUNG **ELECTRONICS**  79

# **CMOS EEPROM**

# TIMING DIAGRAMS (Continued) INSTRUCTION TIMING READ STANDBY HIGH-Z ton, tan D0 HIGH-Z CHECK STATUS STANDBY WRITE HIGH-Z BUSY t<sub>1H</sub> HIGH-Z EWEN EWDS ENABLE = 11 DISABLE = 00 ERASE < CHECK STATUS A5 HIGH-Z HIGH-Z BUSY **ERAL** CHECK STATUS STANDBY DI HIGH-Z HIGH-Z BUSY STANDBY WRAL CHECK STATUS HIGH-Z BUŞY SAMSUNG 80

This Material Copyrighted By Its Respective Manufacturer

**ELECTRONICS**

# **CMOS EEPROM**

#### **DEVICE OPERATION**

The KM93C46 is a 1K bit CMOS serial I/O EEPROM used with microcontrollers for non-volatile memory applications. The on-chip programming voltage generator allows user to use a single 5V power supply. The erase and write cycle of the KM93C46 is self-timed with the ready/busy status of the chip indicated at the DO pin. All the operations of the chip are preceded by two OP code bits, facilitating inherent protection against false writes. The DO pin is high-Z except for the read period and the ready/busy indication period to eliminate bus contention.

#### **READ**

After a read instruction and address set is received, low to high transition of the SK clock produces output data at DO pin. A dummy bit (logical "0") proceeds the 16 bit data output string.

#### **EWEN/EWDS**

The KM93C46 is at the erase/write disable (EWDS) state during the power-up period to protect against accidental distribution. After the power up period, the erase/write operation must be preceded by an erase/write enable (EWEN) operation. The erase/write enable (EWEN) mode is maintained until an erase/write disable (EWDS) operation is executed or  $V_{\rm CC}$  is removed from the part. Execution of the READ operation is independent of both EWEN and EWDS instructions

#### **ERASE**

Before a write cycle, an erase cycle need to be operated to reset the EEPROM cells to the "erase ' state. The chip starts the self-timed erase cycle by dropping CS low after an erase instruction and address set is input. The chip's ready/busy status is indicated at the DO pin by bringing CS high during erase cycle.

#### **WRITE**

The write operation is started by sequentially loading its instruction, address, and data set. After the last bit of data is input on the DI pin, CS must be brought low before the rising edge of the SK clock. This falling edge of CS initiates the self-timed write cycle. Like the erase operation, write cycle has the ready/busy function.

#### ERAL (chip erase)

Entire memory array is erased, i.e., logical "1" state, by this chip erase (ERAL) operation. The chip erase cycle is identical to the erase cycle except for different OP code.

#### WRAL (chip write)

The entire array needs to be erased before this chip write mode operation. Data given during this mode are written to all cells in the corresponding column simultaneously

#### READY / BUSY

The ready/busy status of the KM93C46 during all the self-timed programming cycle (erase, write, chip erase, chip write) is indicated at the DO pin. Bringing the CS pin high, after self-timed programming cycle has been initiated, will produce logic '0' at the DO pin if the chip is still programming and a logic '1' if the programming cycle has been completed.

# **CMOS EEPROM**

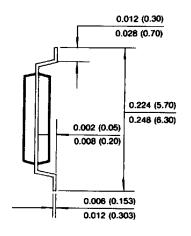

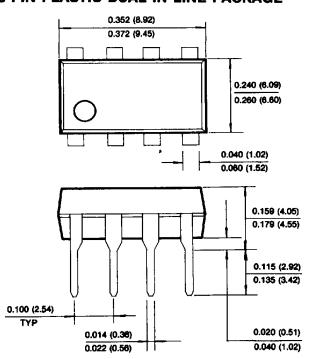

# **PACKAGE DIMENSIONS 8 PIN PLASTIC DUAL IN LINE PACKAGE**

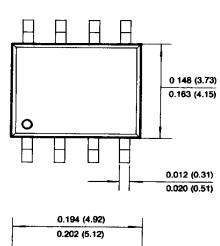

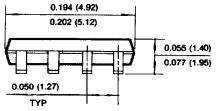

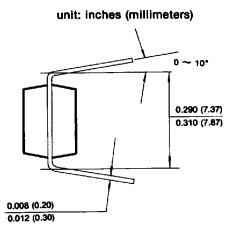

#### **8 PIN PLASTIC SMALL OUT LINE PACKAGE**