# ML6674

# **ATM 155Mbps UTP Transceiver**

#### **GENERAL DESCRIPTION**

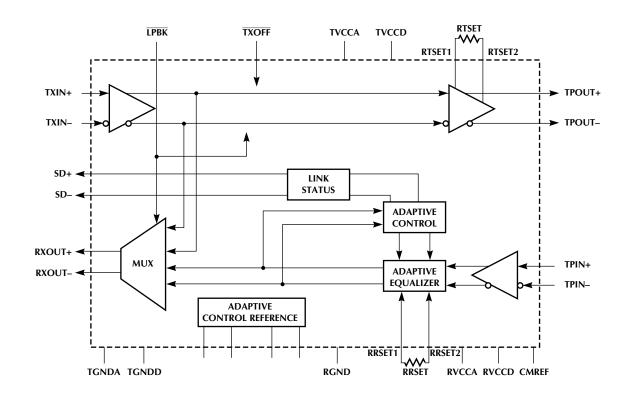

The ML6674 is a complete monolithic transceiver for 155Mbps NRZ encoded data transmission over category 5 unshielded twisted pair (UTP) and shielded twisted pair (STP) cables. The ML6674 is compliant with the ATM 155Mbps Twisted Pair Specification. The ML6674 includes the baseline restoration function and adaptive equalization which will accurately compensate for line losses exceeding 100m of UTP.

The ML6674 receive section consists of an equalizing filter with a feedback loop for controlling effective line compensation. The feedback loop contains a filter and detection block for determining the proper control signal. An ECL 100K compatible buffer at the output interfaces directly with ATM physical interface chips.

The ML6674 transmit section accepts ECL 100K compatible NRZ inputs.

#### **FEATURES**

- Complies with ATM Forum 155Mbps twisted pair specification

- Integrated baseline wander correction circuit

- Integrated adaptive equalization

- Transmitter can be externally turned off (high impedence) for true quiet line

- Operates over 100 meters of STP or category 5 UTP Twisted Pair Cable

- 32-pin PLCC and TQFP

#### **BLOCK DIAGRAM**

# ML6674

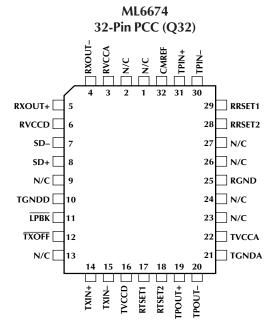

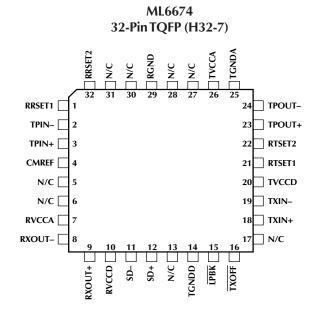

## PIN CONFIGURATION

## PIN DESCRIPTION

| NAME                                   | FUNCTION                                                                                                         | NAME              | FUNCTION                                                                                                                                  |

|----------------------------------------|------------------------------------------------------------------------------------------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| TX <sub>IN</sub> +, TX <sub>IN</sub> – | These differential ECL100K compatible inputs receive NRZ data from the PHY for transmission.                     | SD+, SD-          | These differential ECL100K<br>compatible outputs indicate the<br>presence of a data signal with an<br>amplitude exceeding a preset        |

| TPOUT+,<br>TPOUT–                      | Outputs from the NRZ buffer drive these differential current outputs. The                                        |                   | threshold.                                                                                                                                |

|                                        | transmitter filter/transformer module connects the media to these pins.                                          | TPIN+, TPIN–      | NRZ encoded data from the receiver filter/transformer module enters the Receiver through these                                            |

| LPBK                                   | This TTL input enables transmitter-<br>Receiver loopback internally when                                         |                   | pins.                                                                                                                                     |

|                                        | asserted low.                                                                                                    | RXOUT+,<br>RXOUT– | Differential ECL100K compatible<br>outputs provide NRZ encoded data                                                                       |

| TXOFF                                  | This TTL input forces the NRZ driver to<br>a high impedence state when asserted                                  |                   | to the PHY.                                                                                                                               |

|                                        | low and shuts off transmit bias currrent.                                                                        | RRSET1,<br>RRSET2 | Internal time constants controlling the equalizer's transfer function                                                                     |

| RTSET1,<br>RTSET2                      | An external 1% resistor connected between these pins controls the transmitter output current amplitude.          |                   | are set by an external resistor connected across these pins.                                                                              |

|                                        | $I_{OUT} = 32 \times 1.25 \text{V/RTSET}$                                                                        | CMREF             | This pin provides a DC common mode reference point for the                                                                                |

| TVCCA,<br>TVCCD                        | Separate analog and digital transmitter power supply pins help to                                                |                   | receiver inputs.                                                                                                                          |

|                                        | isolate sensitive circuitry from noise<br>generating digital functions. Both<br>supplies are nominally +5 volts. | RVCCA,<br>RVCCD   | Analog and digital supply pins are<br>separated to isolate clean and<br>noisy circuit functions. Both<br>supplies are nominally +5 volts. |

| TGNDA,<br>TGNDD                        | Analog and digital transmitter grounds provide separate return paths for clean and noisy signals.                | RGND              | Receiver ground.                                                                                                                          |

# ML6674

## ABSOLUTE MAXIMUM RATINGS

| Absolute maximum ratings are limits beyond which the life of the integrated circuit may be impaired. All voltages unless otherwise specified are measured with respect to ground. |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>CC</sub> Supply Voltage Range GND –0.3V to 6V                                                                                                                              |

| Input Voltage Range                                                                                                                                                               |

| Digital Inputs GND –0.3V to VCC + 0.3V                                                                                                                                            |

| Output Current                                                                                                                                                                    |

| TPOUT+/TPOUT-, SD±, RXOUT± 50mA                                                                                                                                                   |

| All other outputs 10mA                                                                                                                                                            |

| Junction Temperature                                                                                                                                                              |

|                                                                                                                                                                                   |

| Storage Temperature                  |          |

|--------------------------------------|----------|

| Lead Temperature (Soldering, 10 se   | c) 260°C |

| Thermal Resistance ( $\theta_{IA}$ ) |          |

| PLCC                                 |          |

| TQFP                                 | 80°C/W   |

### **OPERATING CONDITIONS**

| 5V ± 5%     |

|-------------|

| 0°C to 70°C |

| 2kΩ ± 1%    |

| 9.53kΩ ± 1% |

| < -0.5dB    |

|             |

### **ELECTRICAL CHARACTERISTICS**

Unless otherwise specified,  $T_A = T_{MIN}$  to  $T_{MAX}$ , VCC = 5V ±5%, RTSET = 2.0ký. (Note 1)

| PARAMETER                                                          | CONDITIONS                                       | MIN                    | TYP | MAX                    | UNITS |

|--------------------------------------------------------------------|--------------------------------------------------|------------------------|-----|------------------------|-------|

| DC Characteristics                                                 |                                                  | · · ·                  |     |                        |       |

| Supply Current                                                     |                                                  |                        |     |                        |       |

| RVCCD                                                              |                                                  |                        | 74  |                        | mA    |

| RVCCA                                                              |                                                  |                        | 65  |                        | mA    |

| TVCCD                                                              |                                                  |                        | 14  |                        | mA    |

| TVCCA                                                              |                                                  |                        | 6   |                        | mA    |

| RVCCD + RVCCA + TVCCD + TVCCA                                      |                                                  |                        |     | 185                    | mA    |

| TTL Inputs (TXOFF, LPBK)                                           |                                                  |                        |     |                        |       |

| V <sub>IL</sub> Input Low Voltage                                  |                                                  |                        |     | 0.8                    | V     |

| V <sub>IH</sub> Input High Voltage                                 |                                                  | 2.0                    |     |                        | V     |

| Differential Inputs (TPIN±, TXIN±)                                 |                                                  | i                      |     |                        |       |

| TPIN+, TPIN–<br>Common Mode Input Voltage                          |                                                  | 2.2                    |     | V <sub>CC</sub>        | V     |

| TPIN+, TPIN–<br>Differential Input Voltage                         |                                                  |                        |     | 1.5                    | V     |

| TPIN+, TPIN–<br>Differential Input Resistance                      |                                                  | 10                     |     |                        | kΩ    |

| TPIN+, TPIN-<br>Common Mode Input Current                          |                                                  |                        |     | +10                    | μA    |

| TXIN+, TXIN–<br>Input Voltage HIGH (V <sub>IH</sub> )              |                                                  | V <sub>CC</sub> -1.165 |     | V <sub>CC</sub> -0.88  | V     |

| TXIN+, TXIN–<br>Input Voltage LOW (V <sub>IL</sub> )               |                                                  | V <sub>CC</sub> -1.810 |     | V <sub>CC</sub> -1.475 | V     |

| TXIN+, TXIN–<br>Input Current LOW (I <sub>IL</sub> )               |                                                  | 0.5                    |     |                        | μA    |

| TXIN+, TXIN–<br>Input Current HIGH (I <sub>IH</sub> )              |                                                  |                        |     | 50                     | μA    |

| Differential Outputs (SD±, RXOUT±, TPOU                            | T±)                                              | t                      |     |                        |       |

| SD+, SD–, RXOUT+, RXOUT–<br>Output Voltage HIGH (V <sub>OH</sub> ) | Note 3                                           | V <sub>CC</sub> -1.025 |     | V <sub>CC</sub> -0.88  | V     |

| SD+, SD–, RXOUT+, RXOUT–<br>Output Voltage LOW (V <sub>OL</sub> )  | Note 3                                           | V <sub>CC</sub> -1.81  |     | V <sub>CC</sub> -1.62  | V     |

| TPOUT+, TPOUT–<br>Differential Output Current HIGH                 | V <sub>OUT</sub> = V <sub>CC</sub> ± 0.5, Note 2 | 19.0                   |     | 21.0                   | mA    |

## ELECTRICAL CHARACTERISTICS (CONTINUED)

| PARAMETER                                                                           | CONDITIONS                          | MIN  | ТҮР | MAX  | UNITS |

|-------------------------------------------------------------------------------------|-------------------------------------|------|-----|------|-------|

| Differential Outputs (SD±, RXOUT±, TPOUT                                            | ±) (Continued)                      |      |     | I    |       |

| TPOUT+, TPOUT–<br>DifferentialOutput Current LOW                                    | $V_{OUT} = V_{CC} \pm 0.5$ , Note 2 | 0    |     | 0.1  | mA    |

| TPOUT+, TPOUT–<br>Output Current Offset                                             |                                     |      |     | 0.5  | mA    |

| TPOUT+, TPOUT-V <sub>OUT</sub> = V <sub>CC</sub><br>Output Amplitude Error          | Note 2                              | -5.0 |     | 5.0  | %     |

| TPOUT+, TPOUT-V <sub>OUT</sub> = V <sub>CC</sub> ±1.1V<br>Output Voltage Compliance |                                     | -2.0 |     | +2.0 | %     |

| AC Characteristics                                                                  |                                     | I    |     |      |       |

| TPOUT+, TPOUT–<br>Rise/Fall Time                                                    |                                     | 1.5  | 2.0 | 2.5  | ns    |

| TPOUT+, TPOUT–<br>Output Jitter                                                     |                                     |      | 0.5 |      | ns    |

| RXOUT+, RXOUT–<br>Rise/Fall Time                                                    |                                     |      |     | 5    | ns    |

| RXOUT+, RXOUT–<br>Output Jitter                                                     |                                     |      | 2.0 |      | ns    |

Note 1. Limits are guaranteed by 100% testing, sampling, or correlation with worst-case test conditions.

Note 2. Output current amplitude is determined by  $I_{OUT} = 32 \times 1.25 V/RTSET$ .

Note 3. Output voltage levels are specified when terminated by  $50\Omega$  to V<sub>CC</sub>-2V or equivalent load.

4

## FUNCTIONAL DESCRIPTION

The ML6674 transceiver is a physical media dependent transceiver that allows the transmission and reception of 155 Mbps data over 100 meters over shielded twisted pair cable or category 5 unshielded twisted pair cable.

The transmit section accepts NRZ data, sending the information on a two pin current driven transmitter. The transmitted output passes through an external low pass filter and transformer before entering the connectors to the STP or UTP cable. The output amplitude of the transmitted signal is programmable through the external RTSET resistor.

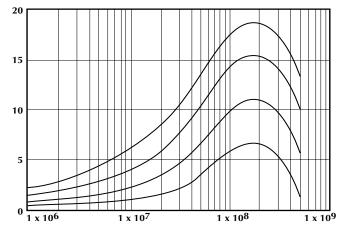

The receive section accepts NRZ coded data after it passes through an isolation transformer and band limiting filter. The adaptive equalizer is used to compensate for the amplitude and phase distortion incurred from the cable. The adaptive control section determines the signal amplitude (and therefore the cable length) and adjusts the equalizer accordingly. As the input signal amplitude diminishes, the amount of equalization increases until it reaches its maximum (Figure 1).

The receiver also includes the Baseline Wander correction circuitry. The circuit will compensate and track the DC baseline wander caused by DC imbalance of the received data. A 10pF capacitor can be connected between TPIN+ and TPIN- to improve Bit Error Rate.

The adaptive control block governs both the equalization level as well as the signal detection status. Signal detect is asserted when the equalizer control loop settles, or when loop back is asserted. When the input signal is small, the equalization will be at its maximum.

After the signal has been equalized, it is fed through the loopback multiplexer onto the RXOUT± pins.

Figure 1 shows a typical gain vs frequency plot of the adaptive equalizer for 0, 25, 50, 75 and 100 meter category 5 cable lengths.

#### TRANSMISSION

PECL level scrambled NRZ data is received by the ML6674 and the current driven transmitter then sent the data to the filter/transformer module. The transmit amplitude is controlled by one external resistor, RTSET.

$$I_{OUT} = \frac{32 \times 1.25 V}{RTSET}$$

For ATM UTP applications the transmit amplitude is 1V peak to peak. The termination at the transmitter output is 50ý. Therefore the transmit current  $I_{OUT} = 1/50 = 20$  mA. Thus,

$$\mathsf{RTSET} = \frac{32 \times 1.25\mathsf{V}}{20\mathsf{m}\mathsf{A}} = 2\mathsf{k}\Omega$$

The transmitter may be disabled via the TXOFF pin. When this pin is pulled low, the transmitter's output goes to a

high impedance state and no current flows through the transformer.

#### **ADAPTIVE EQUALIZATION**

During transmission of data over UTP (unshielded twisted pair), distortion and ISI are caused by dispersion in the cable. Equalization is used to overcome this signal corruption. However, the distortion is frequency dependent and cable length dependent. Therefore, in most practical cases, the TP port characteristic is unknown and it is impractical to tune the equalizer specifically to each individual port. Hence, adaptive equalizer is used in the TP-PMD to ensue proper compensation of the received signal.

By using adaptive equalizer, the receiver automatically compensates different length of cable without over equalizing or under equalizing the line. The ML6674 monitors the amplitude of the received signal to determine the cable length and adjust the equalizer accordingly. The input signal level is inversely proportional to the cable length. Therefore, as the signal level decreases, the amount of equalization is increased to compensate for the line loss.

#### ML6672 COMPATIBILITY

The ML6674 implements the Baseline Wander correction circuit, in addition to providing the functionality of the existing ML6672 device. The ML6674 is plug-compatible with the ML6672 with the following notes:

- In the ML6674 design, the RTSET resistor must be 2.0 k  $\Omega$

- In the ML6674 design, the following passive components used in the ML6672 design may be eliminated from the ML6674 design

- RSET resistor

- RTH resistor

- CAP1 capacitor

- CAP2 capacitor

Figure 1. Equalization Range

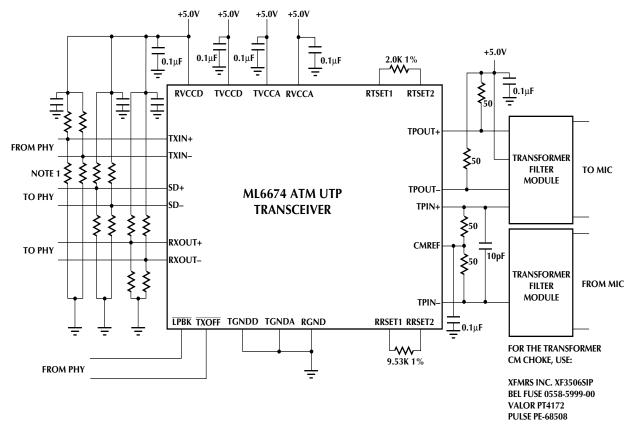

#### Application Example of ML6674 Configured for 1.0V<sub>P-P</sub> Transmit Amplitude on C5 UTP.

Note 1. Split 100K ECL terminations are  $82\Omega$  and  $130\Omega$  to VCC and GND respectively.

Note 2. Recommended power supply bypass capacitors are  $0.1\mu F$  with optional  $10\mu F$  tantalum in parallel.

Note 3. Transformer turns ratio is 1:1.

Note 4. LPBK and TXOFF inputs are active LOW.

6

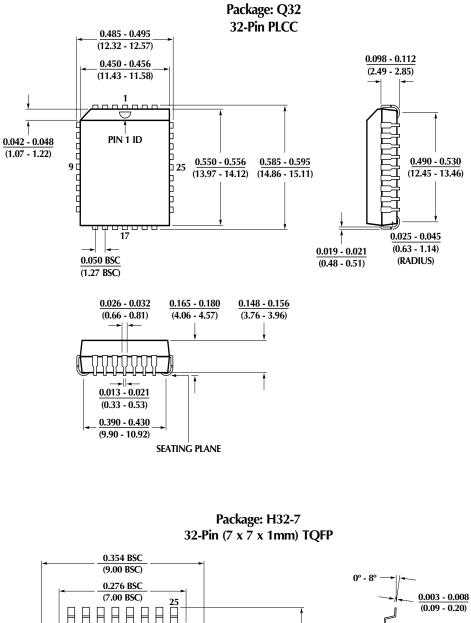

#### PHYSICAL DIMENSIONS inches (millimeters)

1 0 PIN 1 ID 0.276 BSC 0.354 BSC (7.00 BSC) (9.00 BSC) 0.018 - 0.030 1017 (0.45 - 0.75) H 9 SEATING PLANE 0.048 MAX 0.012 - 0.018 0.032 BSC (1.20 MAX) (0.8 BSC) (0.29 - 0.45) 0.037 - 0.041 (0.95 - 1.05)

Micro Linear

### ORDERING INFORMATION

| PART NUMBER | TEMPERATURE RANGE | PACKAGE             |

|-------------|-------------------|---------------------|

| ML6674CQ    | 0°C to 70°C       | 32-Pin PLCC (Q32)   |

| ML6674CH    | 0°C to 70°C       | 32-Pin TQFP (H32-7) |

#### **Micro Linear Corporation**

2092 Concourse Drive San Jose, CA 95131 Tel: 408/433-5200 Fax: 408/432-0295 www.microlinear.com

© Micro Linear 1999. Micro Linear is a registered trademark of Micro Linear Corporation. All other trademarks are the property of their respective owners.

Products described herein may be covered by one or more of the following U.S. patents: 4,897,611; 4,964,026; 5,027,116; 5,281,862; 5,283,483; 5,418,502; 5,508,570; 5,510,727; 5,523,940; 5,546,017; 5,559,470; 5,565,761; 5,592,128; 5,594,376; 5,652,479; 5,661,427; 5,663,874; 5,672,959; 5,689,167; 5,714,897; 5,717,798; 5,742,151; 5,747,977; 5,754,012; 5,757,174; 5,767,653; 5,777,514; 5,793,168; 5,798,635; 5,804,950; 5,808,455; 5,811,999; 5,818,207; 5,818,669; 5,825,165; 5,825,223; 5,838,723; 5.844,378; 5,844,941. Japan: 2,598,946; 2,619,299; 2,704,176; 2,821,714. Other patents are pending. Micro Linear makes no representations or warranties with respect to the accuracy, utility, or completeness of the contents of this publication and reserves the right to makes changes to specifications and product descriptions at any time without notice. No license, express or implied, by estoppel or otherwise, to any patents or other intellectual property rights is granted by this document. The circuits contained in this document are offered as possible applications only. Particular uses or applications may invalidate some of the specifications and/or product descriptions contained herein. The customer is urged to perform its own engineering review before deciding on a particular application. Micro Linear assumes no liability whatsoever, and disclaims any express or implied warranty, relating to sale and/or use of Micro Linear products including liability or warranties relating to merchantability, fitness for a particular purpose, or infringement of any intellectual property right. Micro Linear products are not designed for use in medical, life saving, or life sustaining applications.

8