# HYB25L256160AC

# **256-Mbit Mobile-RAM** 2.5V *V*<sub>DD</sub>

# **Memory Products**

Never stop thinking.

#### HYB25L256160AC

| <b>Revision Hi</b> | story: 2003-04-16                                                                                                                                                                                                                                                                              | V1.1       |  |  |  |  |  |  |  |  |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--|--|--|--|--|--|--|--|

| Previous Ve        | rsion: 2001-11-23                                                                                                                                                                                                                                                                              | V1.0       |  |  |  |  |  |  |  |  |

| Page               | Subjects (major changes since last version)                                                                                                                                                                                                                                                    |            |  |  |  |  |  |  |  |  |

| all                | applied new data sheet template Din-A4                                                                                                                                                                                                                                                         |            |  |  |  |  |  |  |  |  |

| Page 13f           | Temperature Compensated Self Refresh with On-Chip Temperature Sensor                                                                                                                                                                                                                           |            |  |  |  |  |  |  |  |  |

| Page 15            | Table Operation Definition extended by two rows "Clock Suspend Entry" and "Clock Suspend Exit"; Note 5 extended by "When this command is asserted during a burst cycle the device"                                                                                                             |            |  |  |  |  |  |  |  |  |

| Page 18            | "Self Refresh" description improved                                                                                                                                                                                                                                                            |            |  |  |  |  |  |  |  |  |

| Page 19            | "Simplified State Diagram" added                                                                                                                                                                                                                                                               |            |  |  |  |  |  |  |  |  |

| Page 20            | relaxed Absolute Maximum Ratings (+0.5/–0.7 V instead of ±0.3 V relative to $V_{DD}/V_{SS}$ )                                                                                                                                                                                                  |            |  |  |  |  |  |  |  |  |

| Page 20            | Note 4: relaxed over-/underswing delta to 2.0 V                                                                                                                                                                                                                                                |            |  |  |  |  |  |  |  |  |

| Page 20ff          | deleted $V_{\rm DD}$ and $V_{\rm DDQ}$ range above tables and partly replaced by note "(Reco<br>Operating Conditions unless otherwise noted)"                                                                                                                                                  | ommended   |  |  |  |  |  |  |  |  |

| Page 22            | PC133 replaced by -7.5                                                                                                                                                                                                                                                                         |            |  |  |  |  |  |  |  |  |

| Page 23f           | table operating currents updated, symbols changed from $I_{CC}$ to $I_{DD}$ , value type "max." added, $I_{DDC}$ named "self refresh current", $I_{DD1}$ description ("Single bank access cycles") updated $t_{CK}$ defined by Note 3 or set to infinity; Note 4: "assumed" replaced by "used" |            |  |  |  |  |  |  |  |  |

| Page 41            | revised timing diagram SPT03919-4                                                                                                                                                                                                                                                              |            |  |  |  |  |  |  |  |  |

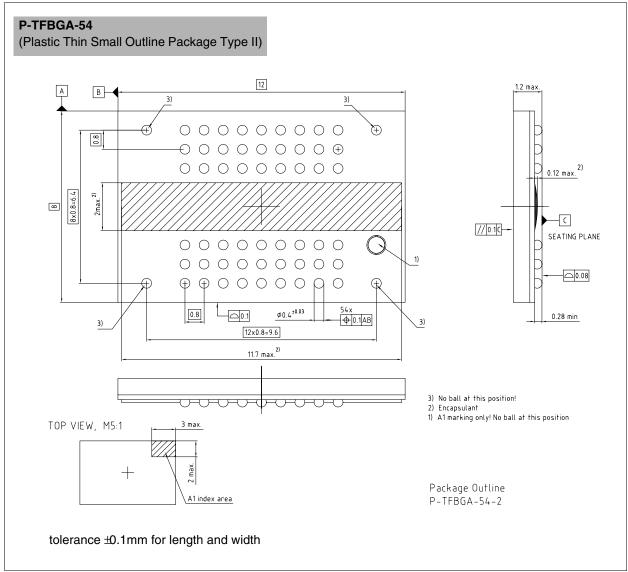

| Page 54            | TFBGA package outline moved to end , added "tolerance ±0.1mm for length                                                                                                                                                                                                                        | and width" |  |  |  |  |  |  |  |  |

#### We Listen to Your Comments

Any information within this document that you feel is wrong, unclear or missing at all? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to:

techdoc.mp@infineon.com

#### Edition 2003-04-16

Published by Infineon Technologies AG, St.-Martin-Strasse 53, 81669 München, Germany © Infineon Technologies AG 2003.

#### Attention please!

All Rights Reserved.

The information herein is given to describe certain components and shall not be considered as a guarantee of characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

Infineon Technologies is an approved CECC manufacturer.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office in Germany or our Infineon Technologies Representatives worldwide (www.infineon.com).

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

#### **Table of Contents**

# Page

| <b>1</b><br>1.1<br>1.2                                                                            | Overview         4           Features         4           Description         4                                                                                                                                                                                     |

|---------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2                                                                                                 | Pin Configuration                                                                                                                                                                                                                                                   |

| <b>3</b><br>3.1<br>3.2<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.3<br>3.3.1<br>3.3.2<br>3.4<br>3.5 | Functional Description10Initialization10Mode Register10Burst Length11Burst Type12Read Latency12Operating Mode12Extended Mode Register13Partial Array Self Refresh13Temperature Compensated Self Refresh with On-Chip Temperature Sensor15Simplified State Diagram19 |

| 4<br>4.1<br>4.2<br>4.3<br>5<br>6                                                                  | Electrical Characteristics20Operating Conditions20Timing Characteristics21Current Specification23Timing Diagrams25Package Outline54                                                                                                                                 |

#### HYB25L256160AC

# 256-Mbit Mobile-RAM Mobile-RAM

# 1 Overview

#### 1.1 Features

- 16 Mbits × 16 organisation

- Fully synchronous to positive clock edge

- Four internal banks for concurrent operation

- Data mask (DM) for byte control with write and read data

- Programmable CAS latency: 2 or 3

- Programmable burst length: 1, 2, 4, 8, or full page

- Programmable wrap sequence: sequential or interleaved

- Random column address every clock cycle (1-N rule)

- Deep power down mode

- Extended mode register for Mobile-RAM features

- · Temperature compensated self refresh with on-die temperature sensor

- · Partial array self refresh

- Power down and clock suspend mode

- · Automatic and controlled precharge command

- Auto refresh mode (CBR)

- 8192 refresh cycles / 64 ms

- Self-refresh with programmble refresh period

- Programmable power reduction feature by partial array activation during self-refresh

- $V_{\text{DDO}} = 1.8 \text{V or } 2.5 \text{ V}$

- V<sub>DD</sub> = 2.5 V

- P-TFBGA-54 package 9-by-6-ball array with 3 depopulated rows (12 x 8 mm<sup>2</sup>)

- Operating temperature range: commerical (0 °C to 70 °C)

| Part Number Speed Code      |      |                  | -7.5 | -8  | Unit |

|-----------------------------|------|------------------|------|-----|------|

| max. Clock Frequency        | @CL3 | $f_{CK3}$        | 133  | 125 | MHz  |

| min. Clock Period           | @CL3 | t <sub>CK3</sub> | 7.5  | 8.0 | ns   |

| min. Access Time from Clock | @CL3 | t <sub>AC3</sub> | 6.0  | 6.0 | ns   |

| min. Clock Period           | @CL2 | t <sub>CK2</sub> | 9.5  | 9.5 | ns   |

| min. Access Time from Clock | @CL2 | $t_{AC2}$        | 6.0  | 6.0 | ns   |

# Table 1Performance 1)

1) for VDDQ = 2.5 V; see Table 10 for VDDQ dependent performance

# 1.2 Description

The 256-Mbit Mobile-RAM is a new generation of low power, four bank synchronous DRAM organized as 4 banks x 4 Mbit x 16 with additional features for mobile applications. The synchronous Mobile-RAM achieves high speed data transfer rates by employing a chip architecture that prefetches multiple bits and then synchronizes the output data to a system clock.

The device adds new features to the industry standards set for synchronous DRAM products. Parts of the memory array can be selected for Self-Refresh and the refresh period during Self-Refresh is programmable in 4 steps which drastically reduces the self refresh current, depending on the case temperature of the components in the system application. In addition a "Deep Power Down Mode" is available. Operating the four memory banks in an

#### Overview

interleave fashion allows random access operation to occur at higher rate. A sequential and gapless data rate is possible depending on burst length, CAS latency and speed grade of the device.

The Mobile-RAM is housed in a FBGA "chip-size" package. The Mobile-RAM is available in the commerical (0 °C to 70 °C) temperature range.

Table 2Ordering Information

| Part Number <sup>1)</sup> | Function Code | Case Temperature Range     | Package    |

|---------------------------|---------------|----------------------------|------------|

| HYB25L256160AC-7.5        | PC133-333-522 | commerical (0 °C to 70 °C) | P-TFBGA-54 |

| HYB25L256160AC-8          | PC100-222-620 |                            |            |

1) HYB/E: designator for memory components for commercial/extended temperature range

25L: Mobile-RAM at  $V_{DD}$  = 2.5 V

256: 256-Mbit density 160: Product variation x16

160: Product Vari

A: Die revision A C: Package type FBGA

-7.5/8: speed grade - see Table 1

# **Pin Configuration**

# 2 Pin Configuration

|          | 1           | 2        | 3       |                 | 7    | 8    | 9      |

|----------|-------------|----------|---------|-----------------|------|------|--------|

|          | VSS         | DQ15     | VSSQ    | А               | VDDQ | DQ0  | VDD    |

|          | DQ14        | DQ13     | VDDQ    | В               | VSSQ | DQ2  | DQ1    |

|          | DQ12        | DQ11     | VSSQ    | С               | VDDQ | DQ4  | DQ3    |

|          | DQ10        | DQ9      | VDDQ    | D               | VSSQ | DQ6  | DQ5    |

|          | DQ8         | NC       | VSS     | Е               | VDD  | LDQM | DQ7    |

|          | UDQM        | CLK      | CKE     | F               | CAS  | RAS  | WE     |

|          | A12         | A11      | A9      | G               | BA0  | BA1  | CS     |

|          | A8          | A7       | A6      | Н               | A0   | A1   | A10/AP |

|          | VSS         | A5       | A4      | J               | A3   | A2   | VDD    |

|          |             |          |         |                 |      |      |        |

|          |             |          |         | < Top-view >    |      |      |        |

|          |             |          |         |                 |      |      |        |

| Figure 1 | Pin Configu | ration P | -TFBGA- | 54 (16 Mb × 16) |      |      |        |

# **Pin Configuration**

| Ταυ |        |       | itput Sign       |                                                                                                                                                                                                                     |  |  |  |  |  |  |  |  |

|-----|--------|-------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Pin | Symbol | Туре  | Polarity         | Function                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |

| F2  | CLK    | Input | Positive<br>Edge | <b>Clock</b><br>The system clock input. All of the SDRAM inputs are sampled on the rising edge<br>of the clock.                                                                                                     |  |  |  |  |  |  |  |  |

| F3  | CKE    | Input | Active<br>High   | <b>Clock Enable</b><br>CKE activates the CLK signal when high and deactivates the CLK signal when<br>low, thereby initiates either the Power Down mode, Suspend mode, or the Self<br>Refresh mode.                  |  |  |  |  |  |  |  |  |

| G9  | CS     | Input | Active<br>Low    | Chip Select<br>CS enables the command decoder when low and disables the command<br>decoder when high. When the command decoder is disabled, new commands<br>are ignored but previous operations continue.           |  |  |  |  |  |  |  |  |

| F8  | RAS    | Input | Active           | Command Inputs                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |

| F7  | CAS    |       | Low              | Sampled at the rising edge of the clock, $\overline{RAS}$ , $\overline{CAS}$ , and $\overline{WE}$ (along with $\overline{CS}$ )                                                                                    |  |  |  |  |  |  |  |  |

| F9  | WE     |       |                  | define the command to be executed by the SDRAM.                                                                                                                                                                     |  |  |  |  |  |  |  |  |

| G8  | BA1    | Input | Active           | Bank Address Inputs                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |

| G7  | BA0    |       | High             | BA0 and BA1 define to which bank an Active, Read, Write or Precharge command is being applied. BA0 and BA1 also determine if the mode register extended mode register is to be accessed during a MRS or EMRS cycle. |  |  |  |  |  |  |  |  |

| G1  | A12    | Input | Active           | Address Inputs                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |

| G2  | A11    |       | High             | During a Bank Activate command cycle, A12 - A0 define the row address                                                                                                                                               |  |  |  |  |  |  |  |  |

| H9  | A10/AP |       |                  | (RA12 - RA0) when sampled at the rising clock edge.<br>During a Read or Write command cycle, A8-A0 define the column address                                                                                        |  |  |  |  |  |  |  |  |

| G3  | A9     |       |                  | (CA8 - CA0) when sampled at the rising clock edge.                                                                                                                                                                  |  |  |  |  |  |  |  |  |

| H1  | A8     |       |                  | In addition to the column address, A10/AP is used to invoke autoprecharge                                                                                                                                           |  |  |  |  |  |  |  |  |

| H2  | A7     |       |                  | operation at the end of the burst read or write cycle. If AP is high, autoprecharge is selected and BA1, BA0 defines the bank to be precharged. If AP is low,                                                       |  |  |  |  |  |  |  |  |

| H3  | A6     |       |                  | autoprecharge is disabled.                                                                                                                                                                                          |  |  |  |  |  |  |  |  |

| J2  | A5     |       |                  | During a Precharge command cycle, AP is used in conjunction with BA1 and                                                                                                                                            |  |  |  |  |  |  |  |  |

| JЗ  | A4     |       |                  | BA0 to control which bank(s) to precharge. If AP is high, all four banks will be precharged regardless of the state of BA0 and BA1. If AP is low, then BA1 and                                                      |  |  |  |  |  |  |  |  |

| J7  | A3     |       |                  | BA0 are used to define which bank to precharge.                                                                                                                                                                     |  |  |  |  |  |  |  |  |

| J8  | A2     |       |                  |                                                                                                                                                                                                                     |  |  |  |  |  |  |  |  |

| H8  | A1     |       |                  |                                                                                                                                                                                                                     |  |  |  |  |  |  |  |  |

| H7  | A0     |       |                  |                                                                                                                                                                                                                     |  |  |  |  |  |  |  |  |

#### Table 3Input/Output Signals

# **Pin Configuration**

| Din                     | Symbol           | Type             | . e            | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------------------|------------------|------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                         | -                |                  | •              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| A2                      | DQ15             | Input/<br>Output | Active<br>High | <b>Data Input/Output</b><br>Data bus operates in the same manner as on conventional DRAMs.                                                                                                                                                                                                                                                                                                                                                                                                              |

| B1                      | DQ14             | Caiput           |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| B2                      | DQ13             | -                |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| C1                      | DQ12             | -                |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| C2                      | DQ11             | -                |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| D1                      | DQ10             | -                |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| D2                      | DQ9              | -                |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| E1                      | DQ8              | -                |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| E9                      | DQ7              | -                |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| D8                      | DQ6              | _                |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| D9                      | DQ5              | -                |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| C8                      | DQ4              | -                |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| C9                      | DQ3              | -                |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| B8                      | DQ2              | -                |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| B9                      | DQ1              |                  |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| A8                      | DQ0              |                  |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| F1                      | UDQM             | Input            | Active         | Data Input/Output Mask                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| E8                      | LDQM             |                  | High           | UDQM and LDQM are output disable signals during read mode and input mask<br>signals for write data. In Read mode, U/LDQM have a latency of two clock<br>cycles and control the output buffers like low active output enable signals. In<br>Write mode, U/LDQM have a latency of zero and operate as a word mask by<br>allowing input data to be written if it is low but blocks the write operation if the<br>respective DQM is high.<br>UDQM controls the upper byte and LDQM controls the lower byte. |

| E2                      | NC               | -                | _              | Not Connected<br>No internal electrical connection is present.                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| A7,<br>B3,<br>C7,<br>D3 | $V_{DDQ}$        | Supply           | -              | DQ Power Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| A3<br>B7<br>C3<br>D7    | V <sub>SSQ</sub> | Supply           |                | DQ Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| A9<br>E4<br>J9          | $V_{DD}$         | Supply           | _              | Power Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| A1<br>E3<br>J1          | V <sub>SS</sub>  | Supply           | _              | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

# Table 3 Input/Output Signals (cont'd)

## **Pin Configuration**

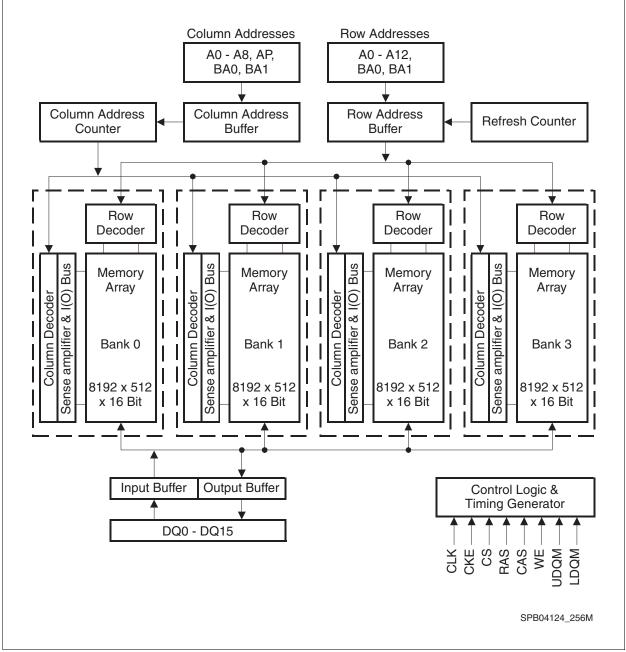

Figure 2 Block Diagram (16 Mbit × 16, 13 / 9 / 2 Addressing)

Note:

- 1. This Functional Block Diagram is intended to facilitate user understanding of the operation of the device; it does not represent an actual circuit implementation.

- 2. DQM is a unidirectional signal (input only), but is internally loaded to match the load of the bidirectional DQ signals.

# 3 Functional Description

The 256-Mbit Mobile-RAM is a new generation of low power, four bank synchronous DRAM organized as 4 banks  $\times$  4 Mbit  $\times$  16 with additional features for mobile applications. The synchronous Mobile-RAM achieves high speed data transfer rates by employing a chip architecture that prefetches multiple bits and then synchronizes the output data to a system clock.

The device adds new features to the industry standards set for synchronous DRAM products. Parts of the memory array can be selected for Self-Refresh and the refresh period during Self-Refresh is programmable in 4 steps which drastically reduces the self refresh current, depending on the case temperature of the components in the system application. In addition a "Deep Power Down Mode" is available. Operating the four memory banks in an interleave fashion allows random access operation to occur at higher rate. A sequential and gapless data rate is possible depending on burst length, CAS latency and speed grade of the device.

Prior to normal operation, the 256-Mbit Mobile-RAM must be initialized. The following sections provide detailed information covering device initialization, register definition, command descriptions and device operation.

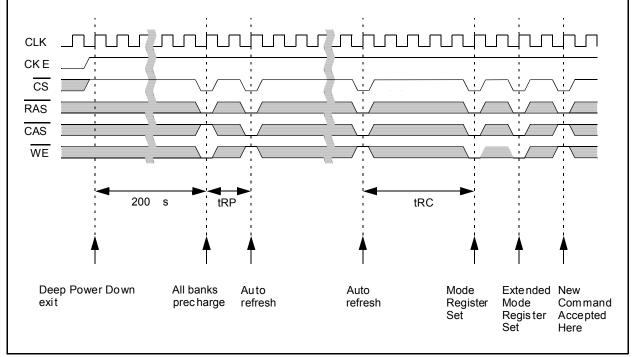

# 3.1 Initialization

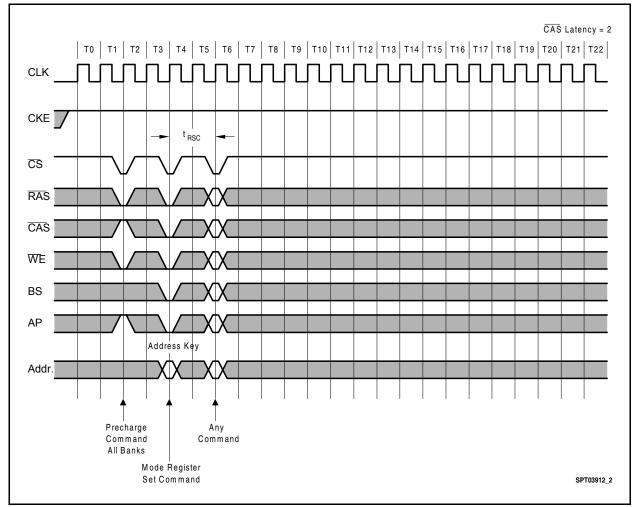

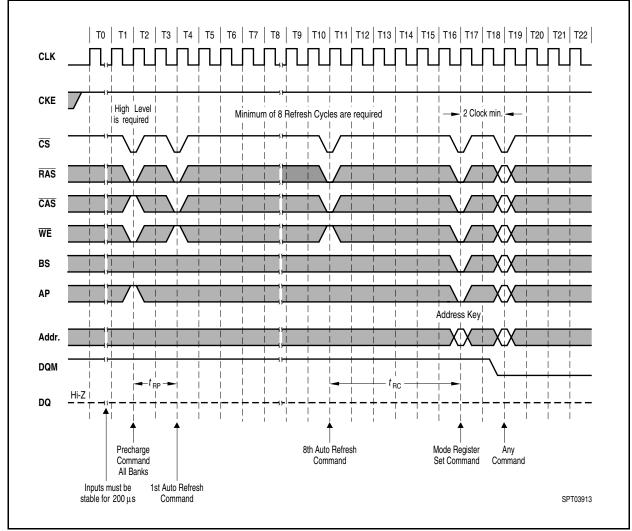

The default power on state of the mode register is supplier specific and may be undefined. The following power on and initialization sequence guarantees the device is preconditioned to each users specific needs. Like a conventional DRAM, the 256-Mbit Mobile-RAM must be powered up and initialized in a predefined manner.  $V_{DD}$  must be applied before or at the same time as  $V_{DDQ}$  to the specified voltage when the input signals are held in the "NOP" or "DESELECT" state. The power on voltage must not exceed  $V_{DD}$  + 0.3 V on any of the input pins or  $V_{DDQ}$  supplies. The CLK signal must be started at the same time. After power on, an initial pause of 200 ms is required followed by a precharge of all banks using the precharge command. To prevent data contention on the DQ bus during power on, it is required that the DQM and CKE pins be held high during the initial pause period. Once all banks have been precharged, the Mode Register Set Command must be issued to initialize the Mode Register. A minimum of eight Auto Refresh cycles (CBR) are also required. These may be done before or after programming the Mode Register. Failure to follow these steps may lead to unpredictable start-up modes. Mode Register Definition

# 3.2 Mode Register

The Mode Register designates the operation mode at the read or write cycle. This register is divided into four fields. A Burst Length Field to set the length of the burst, an Addressing Selection bit to program the column access sequence in a burst cycle (interleaved or sequential), and a CAS Latency Field to set the access time at clock cycle, an The mode set operation must be done before any activate command after the initial power up. Any content of the mode register can be altered by re-executing the mode set operation. All banks must be in precharged state and CKE must be high at least one clock before the mode set operation. After the mode register is set, a Standby or NOP command is required. Low signals of RAS, CAS, and WE at the positive edge of the clock activate the mode set operation. Address input data at this timing defines parameters to be set as shown in the previous table. BA0 and BA1 have to be set to "0" to enter the Mode Register.

| Mode F | Registe | r Defini | ition                                                 |                |                                                          | (BA                                      | [1:0] = | 00 <sub>B</sub> ) |          |           |          |          |         |                    |

|--------|---------|----------|-------------------------------------------------------|----------------|----------------------------------------------------------|------------------------------------------|---------|-------------------|----------|-----------|----------|----------|---------|--------------------|

| BA1    | BA0     | A12      | A11                                                   | A10            | A9                                                       | A8                                       | A7      | A6                | A5       | A4        | A3       | A2       | A1      | A0                 |

| 0      | 0       |          | I                                                     | МС             | DE                                                       | 1                                        | 1       |                   | CL       | 1         | вт       |          | BL      | 1                  |

| reg.   | addr    |          |                                                       | v              | V                                                        | 1                                        | 1       |                   | w        | 1         | w        |          | w       | i                  |

| Field  | Bits    | Туре     | Descr                                                 | iption         |                                                          |                                          |         |                   |          |           |          |          |         |                    |

| BL     | [2:0]   | w        | Number<br>Note: A<br>000 1<br>001 2<br>010 4<br>011 8 | 2<br>4         |                                                          |                                          |         |                   |          |           |          |          |         |                    |

| BT     | 3       | w        | 0 5                                                   |                | ial                                                      | nal addr                                 | ess sec | quence o          | of low o | rder ado  | dress bi | ts; see  | Chapte  | r 3.2.2            |

| CL     | [6:4]   | w        | Numbe                                                 | All other<br>2 | clocks                                                   |                                          |         | mand to<br>RESER  |          | ata valic | l windov | w; see ( | Chapter | <sup>.</sup> 3.2.3 |

| MODE   | [12:7]  | W        | See C                                                 | 0 Burs         | <b>3.2.4</b> .<br><i><sup>.</sup> bit con</i><br>st Reac | <i>nbinatio</i><br>I/Burst \<br>I/Single | Nrite   | RESER             | VED.     |           |          |          |         |                    |

### 3.2.1 Burst Length

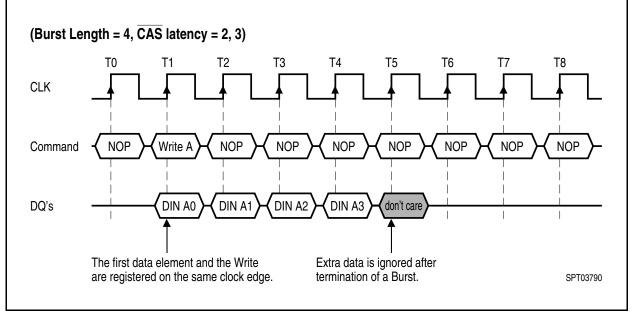

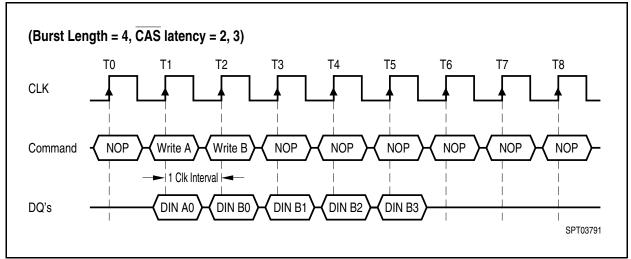

Read and write accesses to the 256-Mbit Mobile-RAM are burst oriented, with the burst length being programmable. The burst length determines the maximum number of column locations that can be accessed for a given Read or Write command. Burst lengths of 2, 4, or 8 locations are available for both the sequential and the interleaved burst types.

Reserved states should not be used, as unknown operation or incompatibility with future versions may result.

When a Read or Write command is issued, a block of columns equal to the burst length is effectively selected. All accesses for that burst take place within this block, meaning that the burst wraps within the block if a boundary is reached. The block is uniquely selected by Ai-A1 when the burst length is set to two, by Ai-A2 when the burst length is set to four and by Ai-A3 when the burst length is set to eight (where Ai is the most significant column address bit for a given configuration). The remaining (least significant) address bit(s) is (are) used to select the starting location within the block. The programmed burst length applies always to Read bursts and depending on A9 in Operating Mode also on Write bursts.

# 3.2.2 Burst Type

Accesses within a given burst may be programmed to be either sequential or interleaved; this is referred to as the burst type and is selected via bit A3. The ordering of accesses within a burst is determined by the burst length, the burst type and the starting column address, as shown in **Table 4**.

| Burst  | Start | ing Colun | nn Address | Order of A        | ccesses Within a Burst |

|--------|-------|-----------|------------|-------------------|------------------------|

| Length | A2    | A1        | A0         | Type = Sequential | Type = Interleaved     |

| 2      |       |           | 0          | 0-1               | 0-1                    |

|        |       |           | 1          | 1-0               | 1-0                    |

| 4      |       | 0         | 0          | 0-1-2-3           | 0-1-2-3                |

|        |       | 0         | 1          | 1-2-3-0           | 1-0-3-2                |

|        |       | 1         | 0          | 2-3-0-1           | 2-3-0-1                |

|        |       | 1         | 1          | 3-0-1-2           | 3-2-1-0                |

| 8      | 0     | 0         | 0          | 0-1-2-3-4-5-6-7   | 0-1-2-3-4-5-6-7        |

|        | 0     | 0         | 1          | 1-2-3-4-5-6-7-0   | 1-0-3-2-5-4-7-6        |

|        | 0     | 1         | 0          | 2-3-4-5-6-7-0-1   | 2-3-0-1-6-7-4-5        |

|        | 0     | 1         | 1          | 3-4-5-6-7-0-1-2   | 3-2-1-0-7-6-5-4        |

|        | 1     | 0         | 0          | 4-5-6-7-0-1-2-3   | 4-5-6-7-0-1-2-3        |

|        | 1     | 0         | 1          | 5-6-7-0-1-2-3-4   | 5-4-7-6-1-0-3-2        |

|        | 1     | 1         | 0          | 6-7-0-1-2-3-4-5   | 6-7-4-5-2-3-0-1        |

|        | 1     | 1         | 1          | 7-0-1-2-3-4-5-6   | 7-6-5-4-3-2-1-0        |

# Table 4Burst Definition

Note:

- 1. For a burst length of two, Ai-A1 selects the two-data-element block; A0 selects the first access within the block.

- 2. For a burst length of four, Ai-A2 selects the four-data-element block; A1-A0 selects the first access within the block.

- 3. For a burst length of eight, Ai-A3 selects the eight-data- element block; A2-A0 selects the first access within the block.

- 4. Whenever a boundary of the block is reached within a given sequence above, the following access wraps within the block.

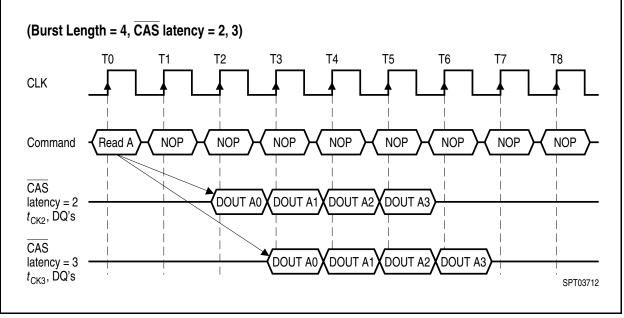

# 3.2.3 Read Latency

The Read latency, or CAS latency, is the delay, in clock cycles, between the registration of a Read command and the availability of the first burst of output data. The latency can be programmed 2 and 3 clocks.

If a Read command is registered at rising clock edge n, and the latency is m clocks, the data is available nominally coincident with rising clock edge n + m.

Reserved states should not be used as unknown operation or incompatibility with future versions may result.

# 3.2.4 Operating Mode

The normal operating mode is selected by issuing a Mode Register Set Command with bits A12-A7 set to zero, and bits A6-A0 set to the desired values. Burst Length for Write bursts is fixed to one by issuing a Mode Register Set command with bits A12-A10 and A8-A7 each set to zero, bit A9 set to one, and bits A0-A6 set to the desired values.

All other combinations of values for A12-A7 are reserved for future use and/or test modes. Test modes and reserved states should not be used as unknown operation or incompatibility with future versions may result.

# 3.3 Extended Mode Register

The Extended Mode Register controls functions beyond those controlled by the Mode Register. These additional functions are unique to Mobile RAMs and includes a refresh period field (TCSR) for Temperature Compensated Self Rrefresh and a Partial Array Self Refresh field (PASR).

The Extended Mode Register is programmed via the Mode Register Set command (with BA0 = 0 and BA1 = 1) and retains the stored information until it is programmed again or the device looses power. The Extended mode Register must be loaded when all banks are idle, and the controller must wait the specified time before initiating any subsequent operation. Violating either these requirements result in unspecified operation. Unused bit A12 to A5 have to be programmed to "0".

# 3.3.1 Partial Array Self Refresh

The PASR field is a power saving feature specific to Mobile-RAMs and is used to specify whether only one quarter or half of bank 0, one bank (bank 0), two banks (banks 0 + 1) or all four banks (default) of the SDRAM array are enabled for Self Refresh. Disabled banks will not be refreshed in Self Refresh mode and written data will get lost after a period defined by  $t_{REF}$ .

# 3.3.2 Temperature Compensated Self Refresh with On-Chip Temperature Sensor

DRAM devices store data as electrical charge in tiny capacitors that require a periodic refresh in order to retain the stored information. This refresh requirment heavily depends on the die temperatur: high temperature corresponds to short refresh period, and low temperature to long refresh period.

The Mobile-RAM is equipped with an on-chip temperature sensor which continuously monitors the current die temperature and adjusts the refresh period in self refresh mode accordingly. By default the on-chip temperature sensor is enabled (TCSR = 00, see Table "EMR" on Page 14); the other three TCSR settings use defined temperature values to adjust the self refresh period to with the on-chip temperature sensor being disabled.

| EMR<br>Extend | ed Mod | le Regi | ster Def | inition |                                                                       | (BA                                                             | [1:0] =                                          | 10 <sub>B</sub> )                    |                                    |                                |                                               |       |                                 |                   |

|---------------|--------|---------|----------|---------|-----------------------------------------------------------------------|-----------------------------------------------------------------|--------------------------------------------------|--------------------------------------|------------------------------------|--------------------------------|-----------------------------------------------|-------|---------------------------------|-------------------|

| BA1           | BA0    | A12     | A11      | A10     | A9                                                                    | A8                                                              | A7                                               | A6                                   | A5                                 | A4                             | A3                                            | A2    | A1                              | A0                |

| 1             | 0      |         | I        | I I     | МС                                                                    | DE                                                              | 1                                                | 1                                    | I                                  | тс                             | SR                                            | PASR  |                                 |                   |

| reg.          | ١      | N       | 1        | 1       | 1                                                                     | ,                                                               | N                                                |                                      | w                                  | 1                              |                                               |       |                                 |                   |

| Field         | Bit    | S       | Туре     | Des     | criptio                                                               | n <sup>1)</sup>                                                 |                                                  |                                      |                                    |                                |                                               |       |                                 |                   |

| PASR          | [2:0   | 0]      | w        |         | Chapt<br>bank<br>bank<br>bank<br>bank                                 | er 3.3.1<br>s to be<br>s to be<br>s to be<br>s to be<br>s to be | self refr<br>self refr<br>self refr<br>self refr | eshed:<br>eshed:<br>eshed:<br>eshed: | 2 of 4, E<br>1 of 4, E<br>0.5 of 4 | BA[1:0]<br>BA[1:0]<br>, BA[1:0 | = 00 <sup>°</sup> B<br>)] = 00 <sup>°</sup> B | & RA1 | 2 = 0 <sub>B</sub><br>[12:11] : | = 00 <sub>B</sub> |

| TCSR          | [4:    | 3]      | w        |         | 01 Maximum case temperature: 45°C, on-chip temperature sensor disable |                                                                 |                                                  |                                      |                                    |                                |                                               |       |                                 |                   |

| MODE          | [12    | :5]     | w        | Оре     | Operating Mode                                                        |                                                                 |                                                  |                                      |                                    |                                |                                               |       |                                 |                   |

00h Normal operation

1) All other bit combinations are RESERVED.

# 3.4 Commands

All of SDRAM operations are defined by states of control signals  $\overline{CS}$ ,  $\overline{RAS}$ ,  $\overline{CAS}$ ,  $\overline{WE}$ , and DQM at the positive edge of the clock. The following list shows the truth table for the operation commands.

| Operation                     | Device                        | CKE   | CKE | DQM | BA1 | AP= | Addr | CS | RAS | CAS | WE |

|-------------------------------|-------------------------------|-------|-----|-----|-----|-----|------|----|-----|-----|----|

|                               | State                         | n-1²) | n²) |     | BA0 | A10 |      |    |     |     |    |

| Bank Active                   | Idle <sup>3)</sup>            | Н     | Х   | Х   | V   | V   | V    | L  | L   | Н   | Н  |

| Bank Precharge                | Any                           | Н     | Х   | Х   | V   | L   | Х    | L  | L   | Н   | L  |

| Precharge All                 | Any                           | Н     | Х   | Х   | Х   | Н   | Х    | L  | L   | Н   | L  |

| Write                         | Active <sup>3)</sup>          | Н     | Х   | Х   | V   | L   | V    | L  | Н   | L   | L  |

| Write with Autoprecharge      | Active <sup>3)</sup>          | Н     | Х   | Х   | V   | Н   | V    | L  | Н   | L   | L  |

| Read                          | Active <sup>3)</sup>          | Н     | Х   | Х   | V   | L   | V    | L  | Н   | L   | Н  |

| Read with Autoprecharge       | Active <sup>3)</sup>          | Н     | Х   | Х   | V   | Н   | V    | L  | Н   | L   | Н  |

| Mode Register Set             | Idle                          | Н     | Х   | Х   | V   | V   | V    | L  | L   | L   | L  |

| No Operation                  | Any                           | Н     | Х   | Х   | Х   | Х   | Х    | L  | Н   | Н   | Н  |

| Burst Stop                    | Active                        | Н     | Х   | Х   | Х   | Х   | Х    | L  | Н   | Н   | L  |

| Device Deselect               | Any                           | Н     | Х   | Х   | Х   | Х   | Х    | Н  | Х   | Х   | Х  |

| Auto Refresh                  | Idle                          | Н     | Н   | Х   | Х   | Х   | Х    | L  | L   | L   | Н  |

| Self Refresh Entry            | Idle                          | Н     | L   | Х   | Х   | Х   | Х    | L  | L   | L   | Н  |

| Self Refresh Exit             | Idle                          | L     | н   |     |     |     | x    | Н  | Х   | Х   | Х  |

|                               | (Self Refresh)                |       |     | Х   | Х   | Х   |      | L  | Н   | Н   | Х  |

| Clock Suspend Entry           | Active <sup>4)</sup>          | Н     | L   | Х   | Х   | Х   | Х    | Х  | Х   | Х   | Х  |

| Clock Suspend Exit            | Active                        | L     | Н   | Х   | Х   | Х   | Х    | Х  | Х   | Х   | Х  |

| Power Down Entry              | Idle                          |       |     |     |     |     |      | Н  | Х   | Х   | Х  |

| (Precharge or active standby) | Active <sup>4)</sup>          | Н     | L   | Х   | Х   | Х   | Х    | L  | Н   | Н   | Н  |

| Power Down Exit               | Any                           |       |     |     |     |     |      | Н  | Х   | Х   | Х  |

|                               | (Power Down)                  | L     | Н   | Х   | Х   | Х   | Х    | L  | Н   | Н   | L  |

| Data Write/Output Enable      | Active                        | Н     | Х   | L   | Х   | Х   | Х    | Х  | Х   | Х   | Х  |

| Data Write/Output Disable     | Active                        | Н     | Х   | Н   | Х   | Х   | Х    | Х  | Х   | Х   | Х  |

| Deep Power Down Entry         | Idle                          | Н     | L   | Х   | Х   | Х   | х    | L  | Н   | н   | L  |

| Deep Power Down Exit          | Deep Power Down <sup>5)</sup> | L     | н   | Х   | Х   | Х   | Х    | Х  | Х   | Х   | Х  |

Table 5

Operation Definition<sup>1)</sup>

1) V = Valid, x = Don't Care, L = Low Level, H = High Level.

CKE<sub>n</sub> signal is input level when commands are provided, CKE<sub>n-1</sub> signal is input level one clock before the commands are provided.

3) This is the state of the banks designated by BA0, BA1 signals.

- 4) Power Down Mode can not be entered during a burst cycle. When this command is asserted during a burst cycle the device enters Clock Suspend Mode.

- 5) After Deep Power Down mode exit a full new initialisation of the memory device is mandatory.

#### Deselect

The Deselect function prevents new commands from being executed by the 256-Mbit Mobile-RAM. Operations already in progress are not affected.

#### No Operation (NOP)

The No Operation (NOP) command is used to perform a NOP to a 256-Mbit Mobile-RAM. This prevents unwanted commands from being registered during idle or wait states. Operations already in progress are not affected.

#### Mode Register Set

The mode registers are loaded via inputs A12-A0, BA1 and BA0. See mode register descriptions in Chapter 3.2. The Mode Register Set command can only be issued when all banks are idle and no bursts are in progress. A subsequent executable command cannot be issued until  $t_{MBD}$  is met.

#### Active

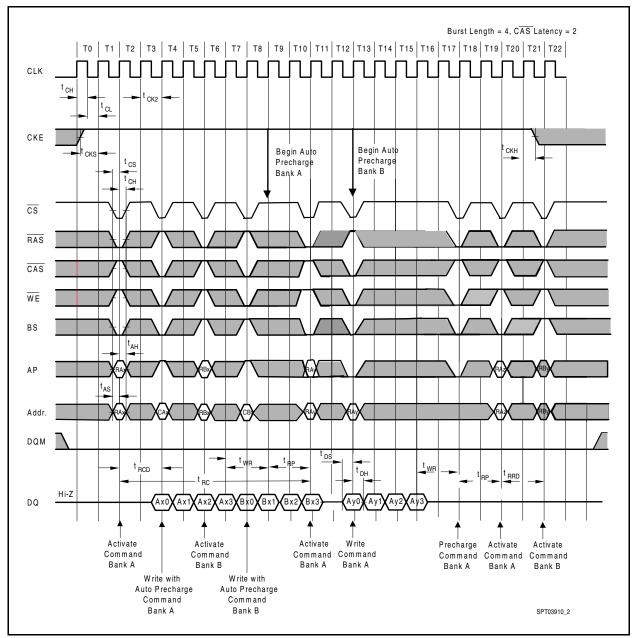

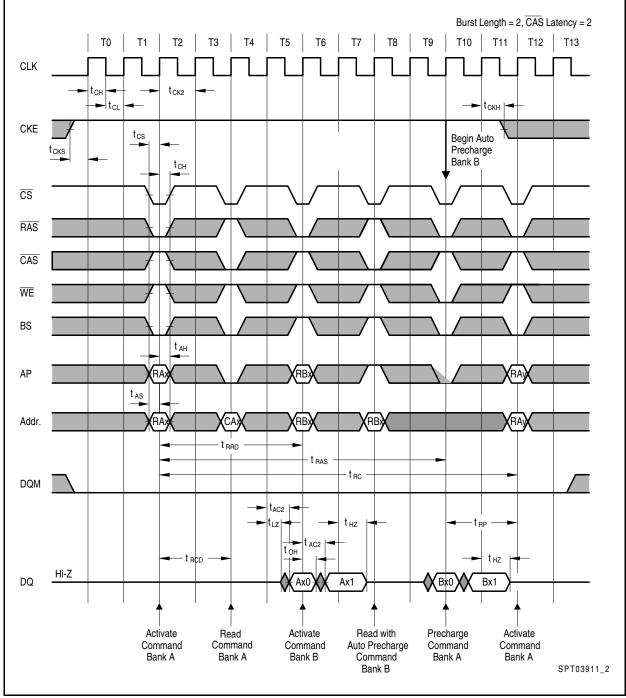

The Active command is used to open (or activate) a row in a particular bank for a subsequent access. This is called the start of a RAS cycle and occures when  $\overline{RAS}$  is low and both  $\overline{CAS}$  and  $\overline{WE}$  are high at the positive edge of the clock. The value on the BA1 and BA0 inputs selects the bank, and the address provided on inputs A12-A0 selects the row. This row remains active (or open) for accesses until a Precharge (or Read or Write with Auto Precharge) is issued to that bank. A Precharge (or Read or Write with Auto Precharge) command must be issued and completed before opening a different row in the same bank.

#### **Read and Write**

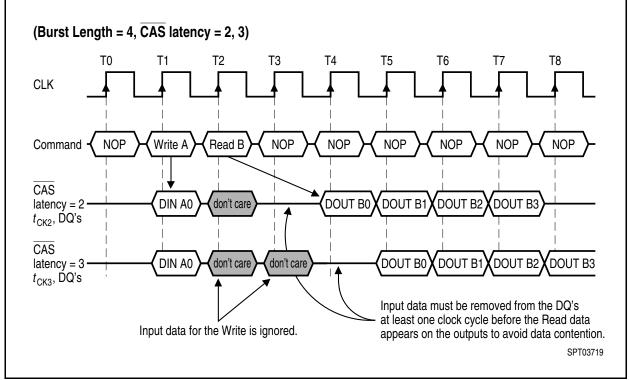

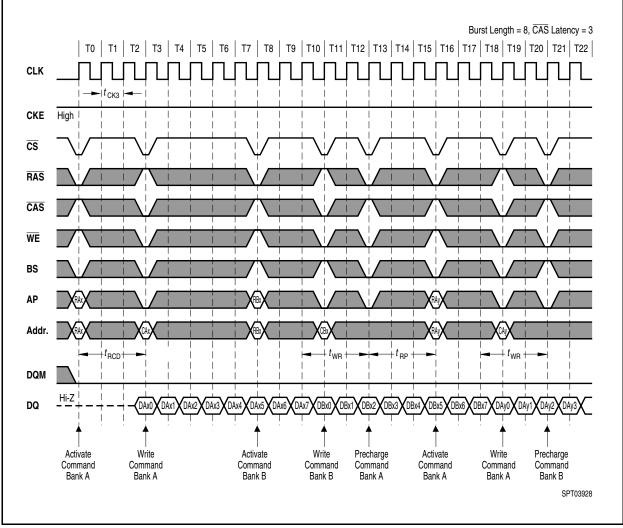

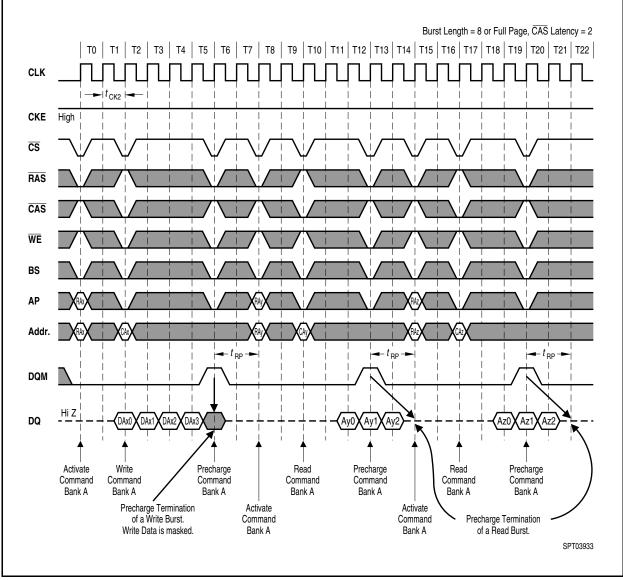

A CAS cycle is triggered by setting  $\overline{RAS}$  high and  $\overline{CAS}$  low at a clock timing after a necessary delay,  $t_{RCD}$ , from the  $\overline{RAS}$  timing. WE is used to define either a read (WE = H) or a write (WE = L) at this stage.

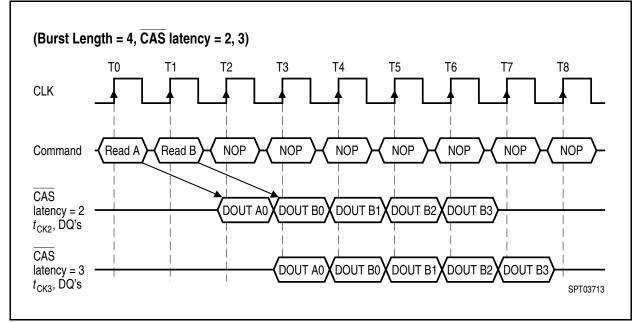

SDRAM provides a wide variety of fast access modes. In a single  $\overline{CAS}$  cycle, serial data read or write operations are allowed at up to a 133 MHz data rate. The numbers of serial data bits are the burst length programmed at the mode set operation, which is one of 1, 2, 4, 8 and full page. Column addresses are segmented by the burst length and serial data accesses are done within this boundary. The first column address to be accessed is supplied at the  $\overline{CAS}$  timing and the subsequent addresses are generated automatically by the programmed burst length and its sequence. For example, in a burst length of 8 with interleave sequence, if the first address is '2', then the rest of the burst sequence is 3, 0, 1, 6, 7, 4, and 5.

Full page burst operation is only possible using the sequential burst type and page length is a function of the I/O organisation and column addressing. Full page burst operation does not self terminate once the burst length has been reached. In other words, unlike burst length of 2, 4 and 8, full page burst continues until it is terminated using another command.

Similar to the page mode of conventional DRAM's, burst read or write accesses on any column address are possible once the RAS cycle latches the sense amplifiers. The maximum  $t_{RAS}$  or the refresh interval time limits the number of random column accesses. A new burst access can be done even before the previous burst ends. The interrupt operation at every clock cycle is supported. When the previous burst is interrupted, the remaining addresses are overridden by the new address with the full burst length. An interrupt which accompanies an operation change from a read to a write is possible by exploiting DQM to avoid bus contention.

When two or more banks are activated sequentially, interleaved bank read or write operations are possible. With the programmed burst length, alternate access and precharge operations on two or more banks can realize fast serial data access modes among many different pages. Once two or more banks are activated, column to column interleave operation can be performed between different pages. When the partial array activation is set, data will get lost when self-refresh is used in all non activated banks.

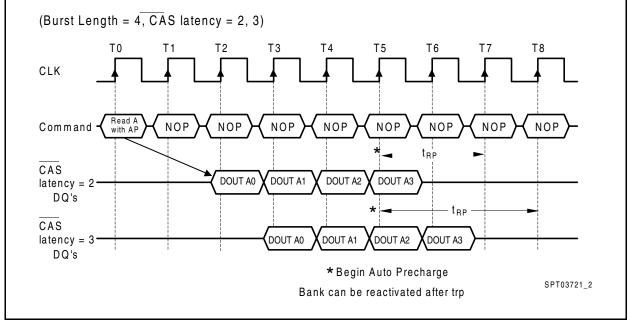

The Read command is used to initiate a burst read access to an active (open) row. The value on the BA1 and BA0 inputs selects the bank, and the address provided on inputs A9-A0 for x16 selects the starting column location. The value on input A10/AP determines whether or not Auto Precharge is used. If Auto Precharge is selected, the row being accessed is precharged at the end of the Read burst; if Auto Precharge is not selected, the row remains open for subsequent accesses.

The Write command is used to initiate a burst write access to an active (open) row. The value on the BA1 and BA0 inputs selects the bank, and the address provided on inputs A9-A0 for x16 selects the starting column location. The value on input A10/AP determines whether or not Auto Precharge is used. If Auto Precharge is selected, the row being accessed is precharged at the end of the Write burst; if Auto Precharge is not selected, the row remains open for subsequent accesses. Input data appearing on the DQs is written to the memory array subject to the DQM input logic level appearing coincident with the data. If a given DQM signal is registered low, the corresponding data is written to memory; if the DQM signal is registered high, the corresponding data inputs are ignored, and a Write is not executed to that byte/column location.

#### Precharge

The Precharge command is used to deactivate (close) the open row in a particular bank or the open row(s) in all banks. The bank(s) will be available for a subsequent row access a specified time ( $t_{RP}$ ) after the Precharge command is issued. When RAS and WE are low and CAS is high at a clock edge, it triggers the precharge operation. Input A10 determines whether one or all banks are to be precharged, and in the case where only one bank is to be precharged, inputs BA0, BA1 select the bank. Otherwise BA0, BA1 are treated as "Don't Care" (see **Table 6**). Once a bank has been precharged, it is in the idle state and must be activated prior to any Read or Write commands being issued to that bank. A precharge command is treated as a NOP if there is no open row in that bank, or if the previously open row is already in the process of precharging.

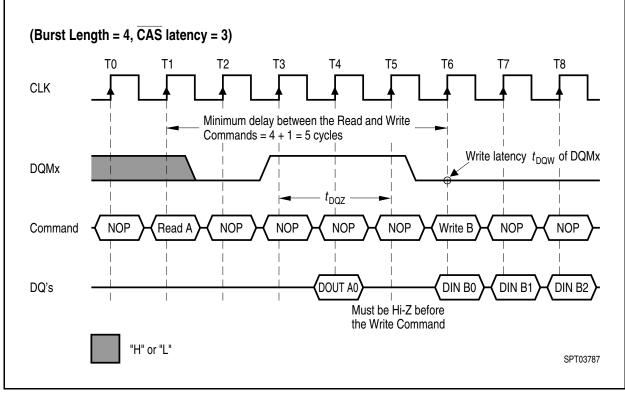

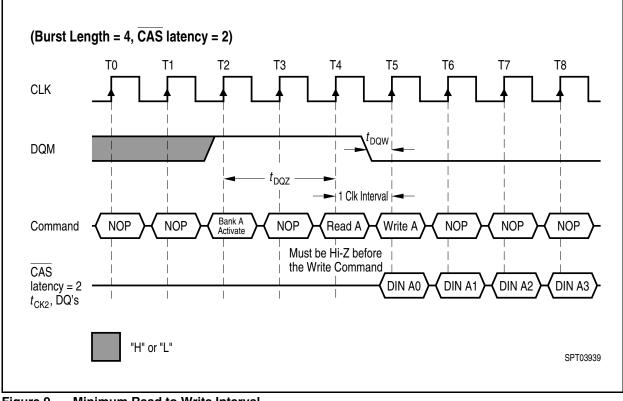

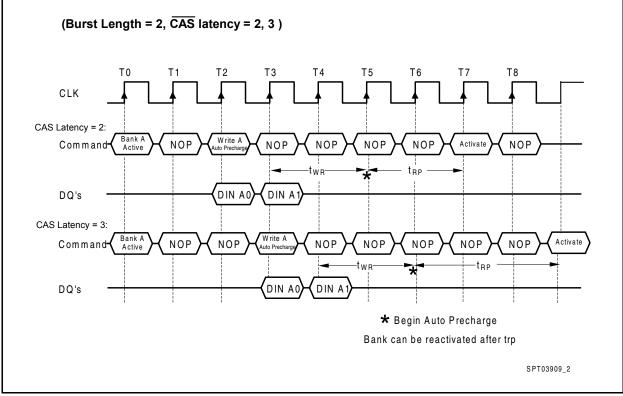

The precharge command can be imposed one clock before the last data out for  $\overline{CAS}$  latency = 2 and two clocks before the last data out for  $\overline{CAS}$  latency = 3. Writes require a time delay  $t_{WR}$  from the last data out to apply the precharge command.

| A10 | BA0 | BA1 |           |

|-----|-----|-----|-----------|

| 0   | 0   | 0   | Bank 0    |

| 0   | 0   | 1   | Bank 1    |

| 0   | 1   | 0   | Bank 2    |

| 0   | 1   | 1   | Bank 3    |

| 1   | x   | x   | all Banks |

Table 6 Bank Selection by Address Bits with Precharge

#### Auto Precharge

Auto Precharge is a feature which performs the same individual-bank precharge functions described above, but without requiring an explicit command. This is accomplished by using A10/AP to enable Auto Precharge in conjunction with a specific Read or Write command. A precharge of the bank/row that is addressed with the Read or Write command is automatically performed upon completion of the Read or Write burst. Auto Precharge is nonpersistent in that it is either enabled or disabled for each individual Read or Write command. Auto Precharge ensures that the precharge is initiated at the earliest valid stage within a burst. The user must not issue another command to the same bank until the precharge ( $t_{RP}$ ) is completed. This is determined as if an explicit Precharge operation after  $t_{WR}$  (Write recovery time) following the last data in.

#### **Burst Terminate**

Once a burst read or write operation has been initiated, there are several methods used to terminate the burst operation prematurely. These methods include using another Read or Write Command to interrupt an existing burst operation, using a Precharge Command to interrupt a burst cycle and close the active bank, or using the Burst Stop Command to terminate the existing burst operation but leave the bank open for future Read or Write Commands to the same page of the active bank. When interrupting a burst with another Read or Write Command care must be taken to avoid DQ contention. The Burst Stop Command, however, has the fewest restrictions making it the easiest method to use when terminating a burst operation before it has been completed. If a Burst Stop command is issued during a burst write operation, then any residual data from the burst write cycle will be ignored. Data that is presented on the DQ pins before the Burst Stop Command is registered will be written to the memory.

#### **Auto Refresh**

Auto Refresh is used during normal operation of the 256-Mbit Mobile-RAM and is analogous to CAS Before RAS (CBR) Refresh in previous DRAM types. This command is nonpersistent, so it must be issued each time a refresh is required. All banks must be precharged before applying any refresh mode. An on-chip address counter increments the word and the bank addresses. This makes the address bits "Don't Care" during an Auto Refresh command.

The chip enters the Auto Refresh mode, when  $\overline{RAS}$  and  $\overline{CAS}$  are held low and CKE and  $\overline{WE}$  are held high at a clock edge. The mode restores word line after the refresh and no external precharge command is necessary. A minimum  $t_{RC}$  time is required between two automatic refreshes in a burst refresh mode. The same rule applies to any access command after the automatic refresh operation.

In Auto-Refresh mode all banks are refreshed, independendly of the fact that the partial array self-refresh has been set or not.

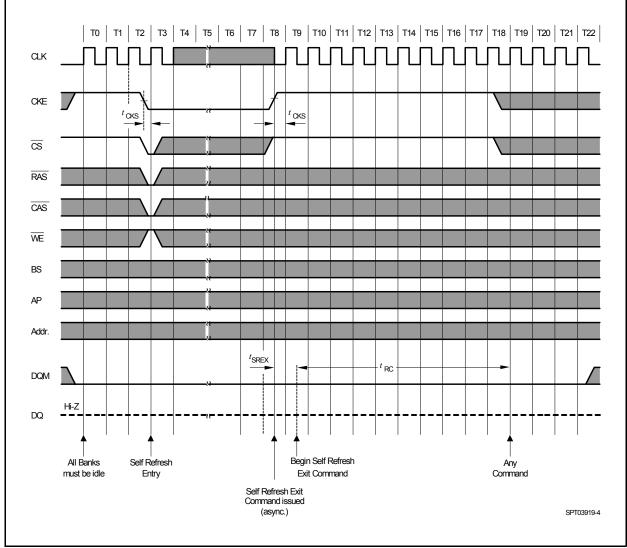

#### Self Refresh

The chip has an on-chip timer that is used when the Self Refresh mode is entered. The self-refresh command is asserted with RAS, CAS, and CKE low and WE high at a clock edge. All external control signals including the clock are disabled. Returning CKE to high enables the clock and initiates the refresh exit operation. After the exit command, at least one  $t_{RC}$  delay is required prior to any access command. The use of self refresh mode introduces the possibility that an iternally timed event can be missed when CKE is raised for exit from self refresh mode. Upon exit from self refresh an extra auto refresh command is recommended.

Low Power SDRAMs have the possibility to program the refresh period of the on-chip timer with the use of an appropriate extended MRS command, depending on the maximum operation case temperature in the application. In partial array self refresh mode only the selected banks will be refreshed. Data written to the non activated banks will get lost after a period defined by tref.

#### **DQM** Function

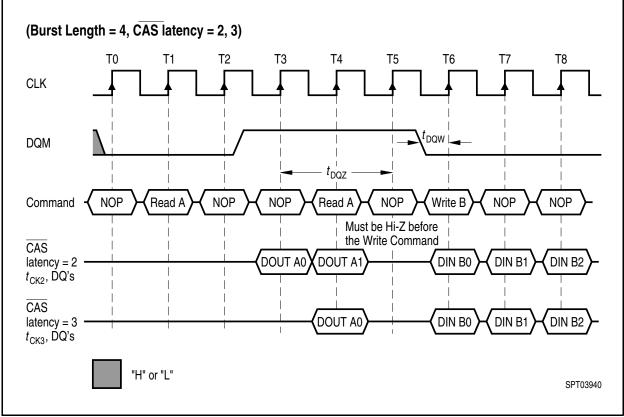

DQM has two functions for data I/O read and write operations. During reads, when it turns to "high" at a clock edge, data outputs are disabled and become high impedance after two clock periods (DQM Data Disable Latency  $t_{DQZ}$ ). It also provides a data mask function for writes. When DQM is activated, the write operation at the next clock is prohibited (DQM Write Mask Latency  $t_{DQW}$  = zero clocks).

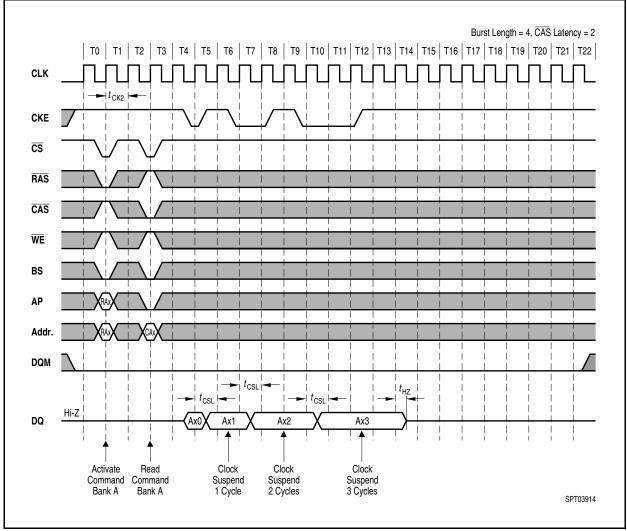

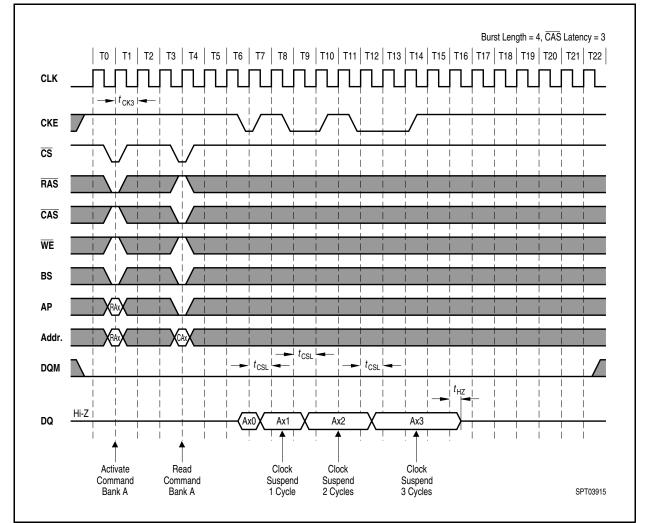

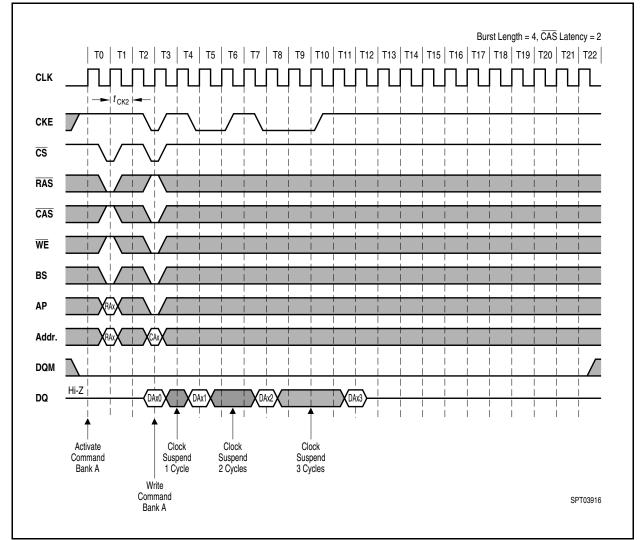

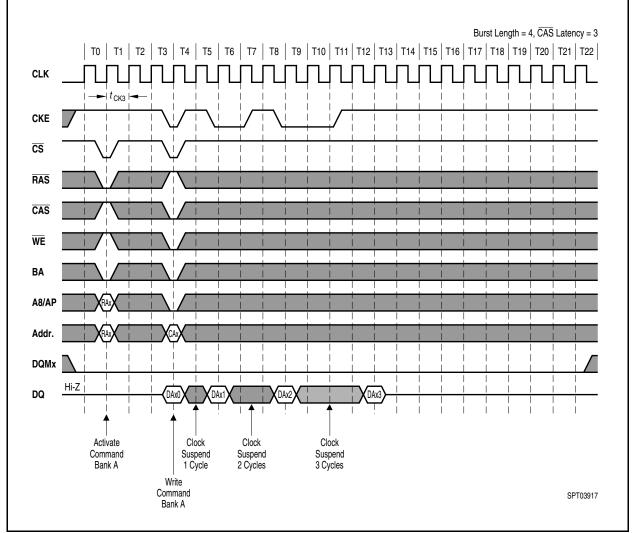

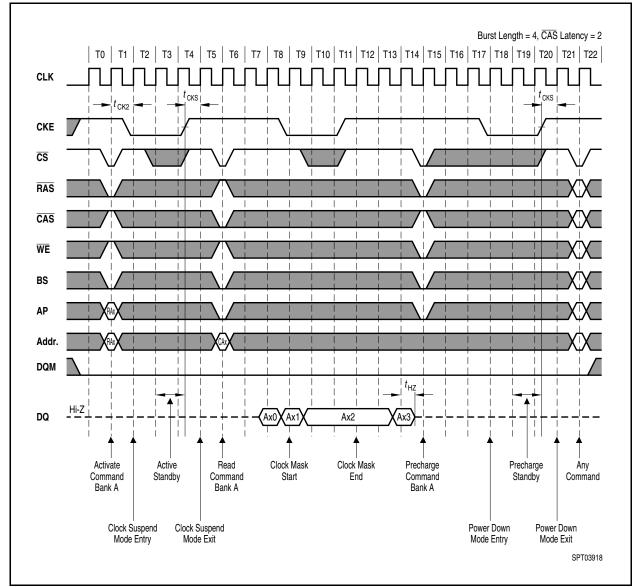

#### Suspend Mode

During normal access, CKE is held high enabling the clock. When CKE is low, it freezes the internal clock and extends data read and write operations. One clock delay is required for mode entry and exit (Clock Suspend Latency  $t_{CSL}$ ).

#### Power Down

In order to reduce standby power consumption, a power down mode is available. All banks must be precharged before the Mobile-RAM can enter the Power Down mode. Once the Power Down mode is initiated by holding CKE low, all receiver circuits except for CLK and CKE are gated off. The Power Down mode does not perform any refresh operations, therefore the device can't remain in Power Down mode longer than the Refresh period ( $t_{REF}$ ) of the device. Exit from this mode is performed by taking CKE "high". One clock delay is required for power down mode entry and exit.

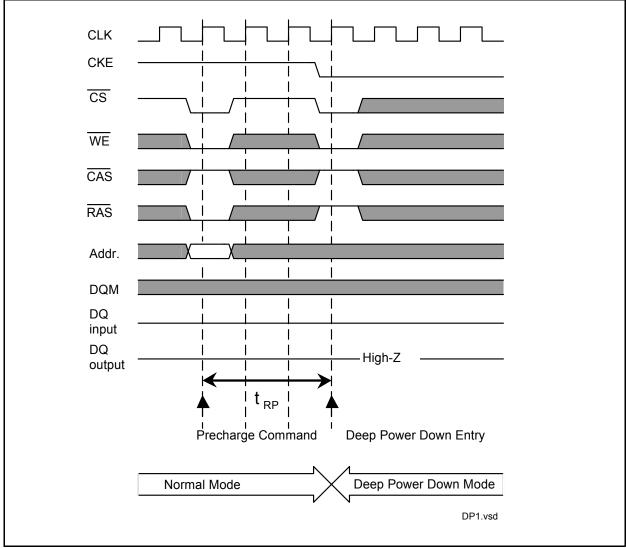

#### Deep Power Down Mode

The Deep Power Down Mode is an unique function on Mobile RAMs with very low standby currents.

All internal voltage generators inside the Mobile RAMs are stopped and all memory data is lost in this mode. To enter the Deep Power Down mode all banks must be precharged.

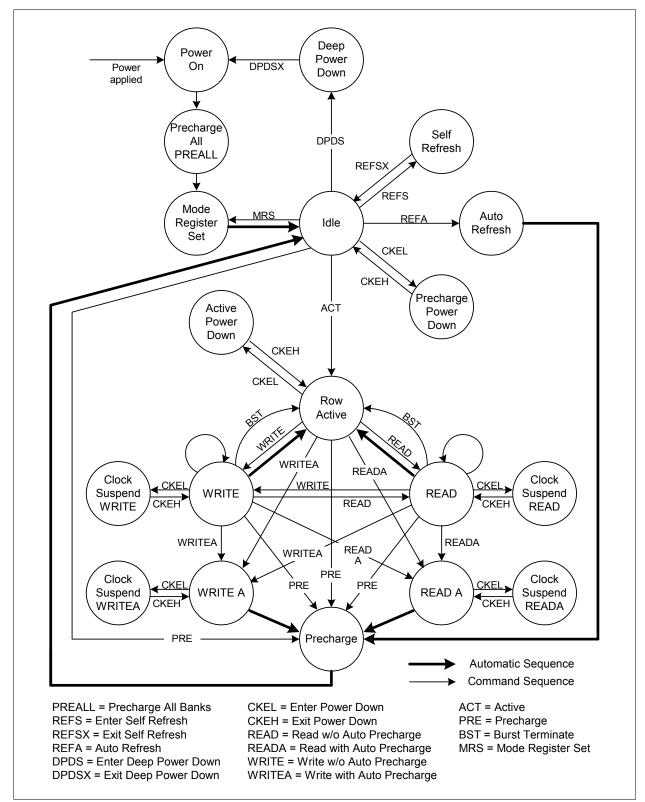

# 3.5 Simplified State Diagram

Figure 3 Simplified State Diagram

# 4 Electrical Characteristics

# 4.1 Operating Conditions

#### Table 7 Absolute Maximum Ratings

| Parameter                                                      | Symbol                    |      | Value | s                  | Unit | Note/<br>Test Condition |

|----------------------------------------------------------------|---------------------------|------|-------|--------------------|------|-------------------------|

|                                                                |                           | min. | typ.  | max.               |      |                         |

| Voltage on I/O pins relative to $V_{\rm SS}$                   | $V_{\rm IN},V_{\rm OUT}$  | -0.7 | —     | $V_{\rm DD}$ + 0.5 | V    | —                       |

| Voltage on I/O pins relative to $V_{\rm SS}$                   | $V_{\rm IN}, V_{\rm OUT}$ | -0.7 | _     | +3.6               | V    | —                       |

| Voltage on $V_{\rm DD}$ supply relative to $V_{\rm SS}$        | $V_{\rm DD}$              | -0.7 | —     | +3.6               | V    | —                       |

| Voltage on $V_{\text{DDQ}}$ supply relative to $V_{\text{SS}}$ | $V_{DDQ}$                 | -0.7 | —     | +3.6               | V    | —                       |

| Operating Case Temperature (commercial)                        | T <sub>CASE</sub>         | 0    | —     | +70                | °C   | —                       |

| Storage Temperature (Plastic)                                  | T <sub>STG</sub>          | -55  | —     | +150               | °C   | —                       |

| Power Dissipation                                              | P <sub>D</sub>            | _    | _     | 0.7                | W    | —                       |

| Short Circuit Output Current                                   | I <sub>OUT</sub>          | _    | 50    | —                  | mA   | —                       |

Attention: Stresses above those listed here may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Maximum ratings are absolute ratings; exceeding only one of these values may cause irreversible damage to the integrated circuit.

| Parameter                     | Symbol          | Va                          | lues Un             |    | Note/ Test Condition                                                                      |  |  |

|-------------------------------|-----------------|-----------------------------|---------------------|----|-------------------------------------------------------------------------------------------|--|--|

|                               |                 | min.                        | max.                |    |                                                                                           |  |  |

| Supply Voltage                | $V_{\rm DD}$    | +2.3                        | +2.9                | V  | —                                                                                         |  |  |

| I/O Supply Voltage            | $V_{DDQ}$       | +1.65                       | +2.9                | V  | 2)                                                                                        |  |  |

| Supply Voltage                | V <sub>SS</sub> | 0                           | 0                   | V  | —                                                                                         |  |  |

| I/O Supply Voltage            | $V_{\rm SSQ}$   | 0                           | 0                   | V  | —                                                                                         |  |  |

| Input High (Logic 1) Voltage  | $V_{IH}$        | $0.8 \times V_{\text{DDQ}}$ | $V_{\rm DDQ}$ + 0.3 | V  | 3)4)                                                                                      |  |  |

| Input Low (Logic 0) Voltage   | $V_{IL}$        | -0.3                        | +0.3                | V  | 3)4)                                                                                      |  |  |

| Output High (Logic 1) Voltage | V <sub>OH</sub> | $V_{\rm DDQ} - 0.2$         | —                   | V  | $I_{OH} = -0.1 \text{ mA}$                                                                |  |  |

| Output Low (Logic 0) Voltage  | V <sub>OL</sub> | _                           | +0.2                | V  | I <sub>OH</sub> = +0.1 mA                                                                 |  |  |

| Input Leakage Current         | I <sub>IL</sub> | -5                          | +5                  | μA | Any input 0 V $\leq V_{IN} \leq V_{DD}$ ;<br>all other pins not under test $V_{IN} = 0$ V |  |  |

| Output Leakage Current        | I <sub>OZ</sub> | -5                          | +5                  | μA | DQ is disabled; 0 V $\leq V_{OUT} \leq V_{DDQ}$                                           |  |  |

Table 8 Recommended Operating Conditions and DC Characteristics<sup>1)</sup>

1)  $0 \circ C \leq T_{CASE} \leq +70 \circ C$

2)  $V_{\rm DDQ} < V_{\rm DD} + 0.3 \, \rm V$

- 3) All voltages referenced to  $V_{SS}$

- 4)  $V_{\text{IH}}$  may overshoot to  $V_{\text{DDQ}}$  + 2.0 V for pulse width of < 4 ns.  $V_{\text{IL}}$  may undershoot to - 2.0 V for pulse width < 4 ns. Pulse width measured at 50% points with amplitude measured peak to DC reference

#### Table 9 Input and Output Capacitances

| Parameter                                    | Symbol          |      | Value | S    | Unit | Note/<br>Test Condition |

|----------------------------------------------|-----------------|------|-------|------|------|-------------------------|

|                                              |                 | min. | typ.  | max. |      |                         |

| Input Capacitance: CLK                       | C <sub>I1</sub> | -    | -     | 3.5  | pF   | 1)                      |

| Input Capacitance: All other input-only pins | $C_{l2}$        | -    | -     | 3.8  | pF   | 1)                      |

| Input/Output Capacitance: DQ                 | C <sub>IO</sub> | 4.0  | -     | 5.0  | pF   | 1)                      |

1) These values are guaranteed by design and are tested on a sample base only.  $V_{\text{DDQ}} = V_{\text{DD}} = 2.5 \text{ V} \pm 0.2 \text{ V}, f = 1 \text{ MHz}, T_{\text{CASE}} = 25 \degree \text{C}, V_{\text{OUT(DC)}} = V_{\text{DDQ}}/2, V_{\text{OUT}}$  (Peak to Peak) 0.2 V. Unused pins are tied to ground.

# 4.2 Timing Characteristics

#### Table 10 AC Timing Characteristics<sup>1)2)</sup>

| Parameter                             | Symbol           |      | -8     | -7.5 |        | Unit            | Note/ Test Condition                       |

|---------------------------------------|------------------|------|--------|------|--------|-----------------|--------------------------------------------|

|                                       |                  | min. | max.   | min. | max.   | 1               |                                            |