## Advanced CRT Controller (ACRTC)

The advanced CRT controller (ACRTC) CMOS VLSI microcomputer peripheral device can display both graphics and characters on raster-scan displays. It is a new generation CRT controller based on bitmapped technology. It executes high-level commands, like Line, Ellipse, Paint, Pattern, and Copy, issued by the MPU in screen X-Y coordinates, and performs the address translation necessary to draw into frame memory. It can draw in up to 64k colors, on three split screens and an independent window, and perform area clipping and hitting.

The ACRTC controls a CRT in one of three modes: character only, graphics only, and multiplexed character/graphics modes. Therefore, the ACRTC has many applications, from character-only displays to large full-graphics systems.

The ACRTC reduces CPU software overhead and enhances system throughput.

#### **Features**

- High-speed graphics

- Drawing rate: 408 ns/pixel max (color drawing)

- Commands: 38 commands including 23 graphic drawing commands

Dot, Line, Rectangle, Poly-line, Polygon, Circle, Ellipse, Paint, Copy, etc.

- -Colors: 16 bits/word

- 1, 2, 4, 8, 16 bits/pixel (5 types) Monochrome to 64k colors max

- -Pattern RAM: 32 bytes

- —Converts logical X-Y coordinates to physical address

- -Color operation and conditional drawing

- Drawing area control for hardware clipping and hitting

- Large frame-memory space

- —Maximum 2 Mbytes graphic memory and 128 kbytes character memory separate from the MPU memory

- —Maximum resolution: 4096×4096 pixels (1 bit/pixel mode)

- CRT display control

- —Split screens: three displays and one window

- -Zoom: 1 to 16 times

- -Scroll: vertical and horizontal

- Interleaved access mode for flashless display and superimposition

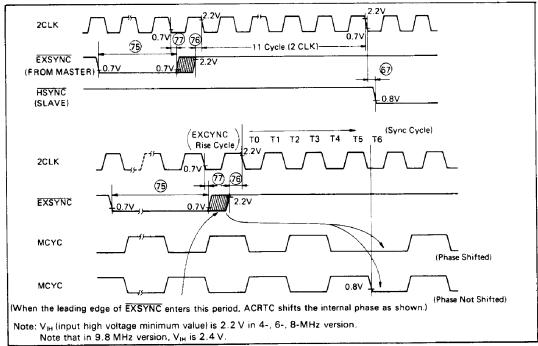

- External synchronization between ACRTCs or between ACRTC and external device (TV system or other controller)

- DMA interface

- Two programmable cursors

- Three scan modes

- -Non-interlaced

- -Interlace sync

- —Interlace sync and video

- Interrupt request to MPU

- 256 characters/line 32 raster/line, 4096 rasters/screen

- Maximum clock frequency: 9.8 MHz

- CMOS, single +5 V power supply

#### **Ordering Information**

| Part No.    | Clock Frequency (2CLK) | Package                    |  |  |  |  |

|-------------|------------------------|----------------------------|--|--|--|--|

| HD63484-4   | 4 MHz                  | DC-64                      |  |  |  |  |

| HD63484-6   | 6 MHz                  | (64-pin ceramic DIP)       |  |  |  |  |

| HD63484-8   | 8 MHz                  |                            |  |  |  |  |

| HD63484-98  | 9.8 MHz                |                            |  |  |  |  |

| HD63484P4   | 4 MHz                  | DP-64                      |  |  |  |  |

| HD63484P6   | 6 MHz                  | (64-pin plastic DIP)       |  |  |  |  |

| HD63484P8   | 8 MHz                  |                            |  |  |  |  |

| HD63484P98  | 9.8 MHz                |                            |  |  |  |  |

| HD63484CP4  | 4 MHz                  | CP-68                      |  |  |  |  |

| HD63484CP6* | 6 MHz                  | (68-pin plastic PLCC)      |  |  |  |  |

| HD63484CPB  | 8 MHz                  |                            |  |  |  |  |

| HD63484CP98 | 9.8 MHz                |                            |  |  |  |  |

| HD63484Y4   | 4 MHz                  | PC-68                      |  |  |  |  |

| HD63484Y6   | 6 MHz                  | (68-pin PGA)               |  |  |  |  |

| HD63484Y8   | 8 MHz                  | •                          |  |  |  |  |

| HD63484Y98  | 9.8 MHz                |                            |  |  |  |  |

| HD63484PS4  | 4 MHz                  | DP-64S                     |  |  |  |  |

| HD63484P\$6 | 6 MHz                  | (64-pin plastic shrink DIP |  |  |  |  |

| HD63484PS8  | 8 MHz                  |                            |  |  |  |  |

| HD63484PS98 | 9.8 MHz                |                            |  |  |  |  |

Note: Wide temperature range (-400° to +800°) version is available.

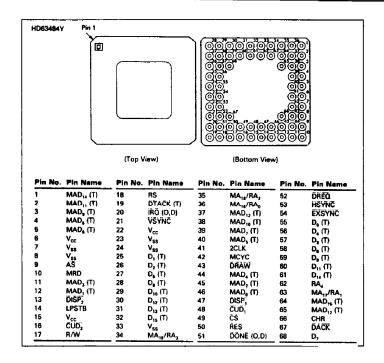

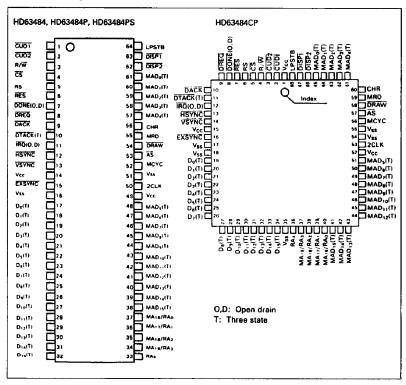

## Pin Arrangement

**OHITACHI**

## Pin Description

| D:- | MI  | L   |

|-----|-----|-----|

| rın | Num | Der |

|           |                                                                           |                 | 7 111 1401112            |                                       | <b>-</b> |                                                               |

|-----------|---------------------------------------------------------------------------|-----------------|--------------------------|---------------------------------------|----------|---------------------------------------------------------------|

| Group     | Mnenionic                                                                 | DIP             | PLCC                     | PGA                                   | 1/0      | Function                                                      |

| MPU       | RES                                                                       | 6               | 7                        | 50                                    | l        | ACRTC reset                                                   |

| Interface | D <sub>0</sub> -D <sub>15</sub> *                                         | 17-32           | 19-34                    | 25 <b>-32</b><br>55-61<br>68          | 1/0      | Data bus (three state)                                        |

|           | R/W                                                                       | 3               | 4                        | 17                                    | I        | Read/write strobe                                             |

|           | CS                                                                        | 4               | 5                        | 49                                    | 1        | Chip select                                                   |

|           | RS                                                                        | 5               | 6                        | 18                                    | 1        | Register select                                               |

|           | DTACK                                                                     | 10              | 11                       | 19                                    | 0        | Data transfer acknowledge (three state)                       |

|           | IRQ                                                                       | 11              | 12                       | 20                                    | 0        | Interrupt request (open drain)                                |

| DMAC      | DREQ                                                                      | 8               | 9                        | 52                                    | 0        | DMA request                                                   |

| Interface | DACK                                                                      | 9               | 10                       | 67                                    | 1        | DMA acknowledge                                               |

|           | DONE                                                                      | 7               | 8                        | 51                                    | 1/0      | DMA done (open drain)                                         |

| CRT       | 2CLK                                                                      | 50              | 53                       | 41                                    | ł        | ACRTC clock                                                   |

| Interface | MAD <sub>0</sub> -MAD <sub>15</sub> *                                     | 61-57,<br>48-38 | 65-61,<br>51-41          | 1-5, 11,12<br>37-40,44-<br>46, 64, 65 |          | Multiplexed frame buffer address/data bus                     |

|           | ĀS                                                                        | 53              | 57                       | 9                                     | 0        | Adress strobe                                                 |

|           | MA <sub>16</sub> /RA <sub>0</sub> -*<br>MA <sub>19</sub> /RA <sub>3</sub> | 37-34           | 40-37                    | 34-36                                 | 0        | Higher-order address bits/<br>character screen raster address |

|           | RA₄                                                                       | 33              | 36                       | 62                                    | 0        | High-order character screen raster address bit                |

|           | CHR                                                                       | 56              | 60                       | 66                                    | 0        | Graphic or character screen access                            |

|           | MCYC                                                                      | 52              | 56                       | 42                                    | 0        | Frame buffer memory access timing signal                      |

|           | MRD                                                                       | 55              | 59                       | 10                                    | 0        | Frame buffer memory read                                      |

|           | DRAW                                                                      | 54              | 58                       | 43                                    | 0        | Draw/refresh signal                                           |

|           | DISP1, DISP2                                                              | 63, 62          | 67, 66                   | 47, 13                                | 0        | Display enable                                                |

|           | CUD1, CUD2                                                                | 1,2             | 2,3                      | 48,16                                 |          | Cursor display                                                |

|           | VSYNC                                                                     | 13              | 14                       | 21                                    | 0        | CRT vertical sync pulse                                       |

|           | HSYNC                                                                     | 12              | 13                       | 53                                    |          | CRT horizontal sync pulse                                     |

|           | EXSYNC                                                                    | 15              | 16                       | 54                                    | 1/0      | External sync                                                 |

|           | LPSTB                                                                     | 64              | 68                       | 14                                    | ŀ        | Lightpen strobe                                               |

| Power     | V <sub>cc</sub>                                                           | 14, 49          | 1, 15, 52                | 6, 15, 22                             |          | +5 V                                                          |

| Supply    | V <sub>ss</sub>                                                           | 16, 51          | 17, 18,<br>35, 54,<br>55 | 7, 8, 23<br>24, 33                    |          | Ground                                                        |

<sup>\*:</sup> PGA pin numbers don't correspond to  $D_0$ - $D_{15}$ ,  $MAD_0$ - $MAD_{16}$ ,  $MA_{16}$ / $RA_0$ - $MA_{19}$ / $RA_3$ . Please refer to the pin arrangement.

#### **MPU** Interface

**RES** (Reset): RES is the MPU hardware reset.

$D_0$ - $D_{15}$  (Data Bus):  $D_0$ - $D_{15}$  are the bidirectional data bus to/from the host MPU or DMAC.  $D_0$ - $D_7$  are used in 8-bit data bus mode.

R/W (Read/Write): R/W input controls the direction of host/ACRTC transfers.

CS (Chip Select): CS input enables transfers between the host and the ACRTC.

**RS(Register Select):** RS input selects the ACRTC register to be accessed. It is usually connected to the least significant bit of the host address bus.

DTACK (Data Transfer Acknowledge): DTACK output provides asynchronous bus cycle timing. It is compatible with the HD68000 MPU DTACK output.

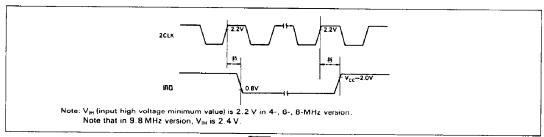

**IRQ** (Interrupt Request): IRQ output generates interrupt service requests to the host MPU.

#### **DMAC Interface**

**DREQ** (DMA Acknowledge): DACK receives DMA acknowledge timing from the host DMAC.

DONE (DMA Done): DONE terminates DMA transfer. It is compatible with the HD68450 DMAC DONE signal.

#### **CRT** Interface

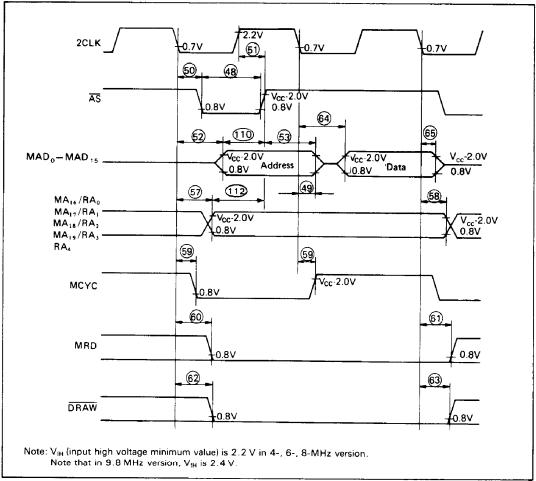

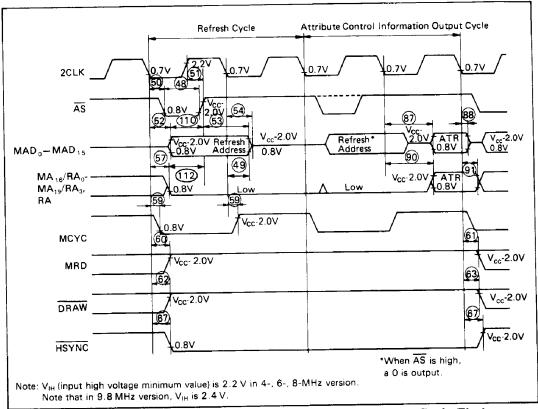

**2CLK** (**Dot Clock**): 2CLK is the basic ACRTC operating clock, twice the frequency of the dot clock.

${

m MAD_0\text{-}MAD_{15}}$  (Frame Memory Address/Data Bus):  ${

m MAD_0\text{-}MAD_{15}}$  are the multiplexed frame buffer address/data bus.

$\overline{\text{AS}}$  (Address Strobe): The  $\overline{\text{AS}}$  output demultiplexes the address/data bus (MAD<sub>0</sub>-MAD<sub>15</sub>).

MA<sub>16</sub>/RA<sub>0</sub>-MA<sub>19</sub>/RA<sub>3</sub> (Memory Address/Raster Address): MA<sub>16</sub>/RA<sub>0</sub>-MA<sub>19</sub>/RA<sub>3</sub> are the upper bits of the graphics screen address multiplexed with the lower bits of the character screen raster address.

RA4 (Raster Address): RA4 is the high bit

of the character screen raster address (up to 32 rasters).

**CHR** (Character): CHR output indicates whether a graphic or character screen is being accessed.

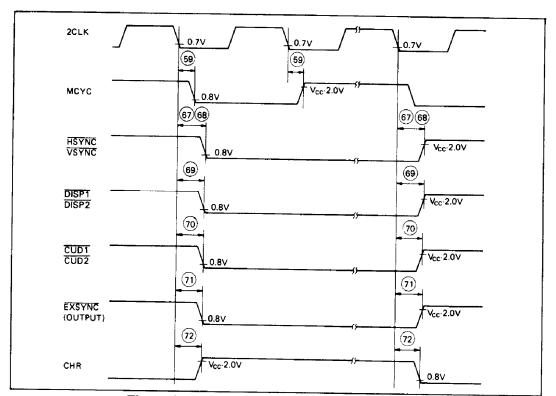

MCYC (Memory Cycle): MCYC is the frame buffer memory access timing output, one-half the frequency of 2CLK.

MRD (Memory Read): MRD output controls the frame buffer data bus direction.

**DRAW** (**Draw**): DRAW output differentiates between drawing and CRT display refresh cycles.

DISP1, DISP2 (Display 1, 2): The DISP1 and DISP2 programmable display enable outputs can enable, disable, and blank logical screens.

CUD1, CUD2 (Cursor Display 1, 2): CUD1 and CUD2 outputs provides cursor timing programmed by ACRTC parameters such as cursor definition, cursor mode, cursor address, etc.

VSYNC (Vertical Sync): VSYNC outputs the CRT vertical synchronization pulse.

**HSYNC** (Horizontal Sync): HSYNC outputs the CRT horizontal synchronization pulse.

**EXSYNC** (External Sync): EXSYNC allows synchronization between multiple ACRTCs and other video signal generators.

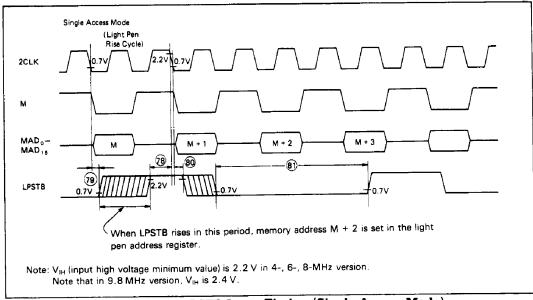

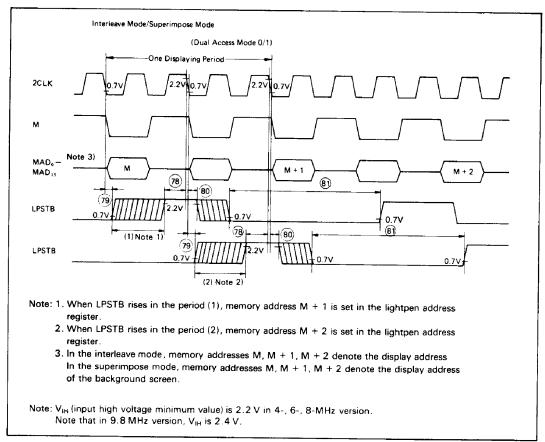

**LPSTB** (**Lightpen Strobe**): LPSTB is the lightpen input.

#### **Block Diagrams**

#### **ACRTC Functions**

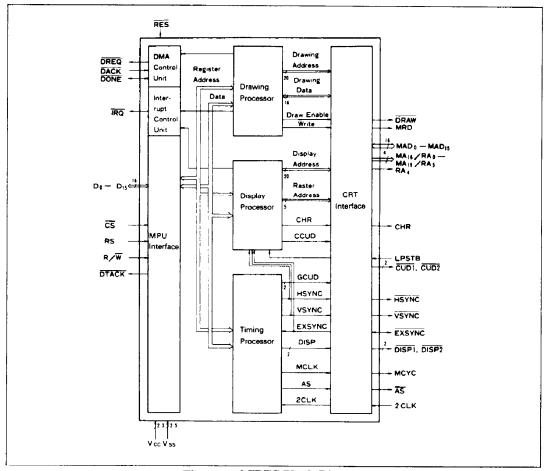

The ACRTC consists of 5 major functional blocks (figure 1). They operate in parallel to achieve maximum performance.

**MPU Interface:** The MPU interface interfaces asynchronously with the host MPU. Its functions include programmable interrupts handling, and DMA handshaking control.

**CRT Interface:** The CRT interface manages the frame buffer bus and the CRT timing input and output control signals. It also selects display refresh or drawing address outputs.

### **MHTACHI**

**Drawing Processor:** The drawing processor interprets commands and command parameters issued by the host bus (MPU and/or DMAC) and performs drawing operations on the frame buffer memory. It executes ACRTC drawing algorithms and converts logical X-Y addresses to physical frame buffer addresses.

It communicates with the host bus via separate 16-byte read and write FIFOs.

Display Processor: The display processor manages frame buffer refresh addressing based on the user-specified display screen organization. It combines and displays as many as 4 independent screen segments (3 horizontal split screens and 1 window) using an internal high-speed address calculation unit. It controls display refresh outputs in graphic (physical frame buffer address) or character (physical refresh memory address + row address) modes.

**Timing Processor:** The timing processor generates the CRT synchronization signals and signals used internally by the ACRTC.

Registers: The ACRTC registers that are visible to software are partitioned in the same way. They reside in the internal processor appropriate to their function. The registers in the display and timing processors are loaded with the basic display parameters during system initialization. During operation, the host communicates primarily with the ACRTC's drawing processor via the on-chip FIFOs.

#### High-Speed (= 9.8 MHz) Version of ACRTC

To keep up with the demand for improvements in the quality and resolution of CRT monitors, Hitachi has introduced a 9.8 MHz version of the HD63484 (ACRTC).

It can be used for:

- High-resolution displays such as in office workstations, business personal computers, and CAD/CAM displays.

- Applications requiring faster drawing than the current ACRTC with an 8-MHz 2CLK operation frequency.

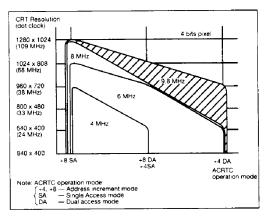

#### **High-Resolution Display**

As shown in figure A, the 9.8-MHz allows the following configurations for a 4-bit/pixel system:

- 1. CRT monitor with  $1024 \times 808$  dots, + 8 DA or + 4 SA

- 2. CRT monitor from  $800 \times 480$  to  $960 \times 720$  dots, +4 DA

Figure A. ACRTC Operation Frequency and Supportable CRT Display Range

#### **High-Speed Drawing Support**

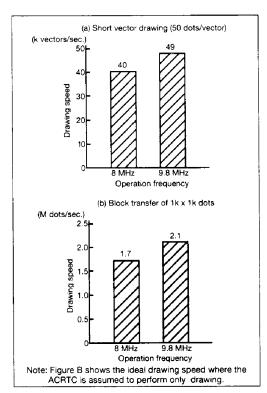

The ACRTC drawing speed depends on its operation frequency. Consequently it takes less time to draw with a 9.8-MHz clock than with an 8-MHz clock. Figure B compares drawing capabilities of the 9.8-MHz ACRTC and the 8-MHz ACRTC.

Figure B. Drawing Capability Comparison between 9.8-MHz and 8-MHz ACRTCs.

Figure 1 ACRTC Block Diagram

#### System Configuration

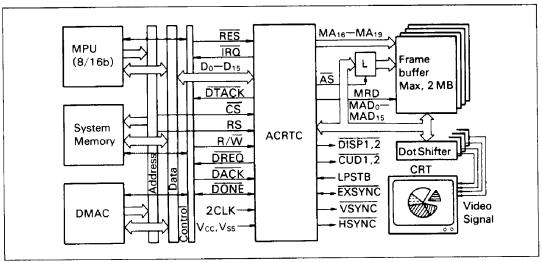

Current CRT controllers provide a single bus interface to the frame buffer that must be shared with the host MPU. However, refreshing large frame buffers, and accessing the frame buffer for drawing operations can quickly saturate the shared bus.

As shown in figure 2, the ACRTC uses separate host MPU and frame buffer interfaces. This allows the ACRTC full access to the frame buffer for display refresh and drawing operations and minimizes the ACRTC's use of the MPU system bus. A related benefit is that a large frame buffer (2 Mbyte for each ACRTC) can be used, even if the host MPU has a smaller address space or segment size restriction.

The ACRTC can use an external DMA controller. A DMA controller increases system throughput when many commands, parameters, and data must be transferred to the ACRTC. Advanced DMAC features, such as the HD68450 "chaining" modes can be used to develop powerful graphics system architectures.

However, more cost-sensitive or less performance-sensitive applications do not require a DMAC. The interface to the ACRTC can be handled under MPU software control.

While both ACRTC bus interfaces (host MPU and frame buffer) are 16 bits wide, the ACRTC also offers an 8-bit MPU mode for easy connection to popular 8-bit busses.

**OHITACHI**

Figure 2 System Configuration

## **Programming Model**

#### **Address Space**

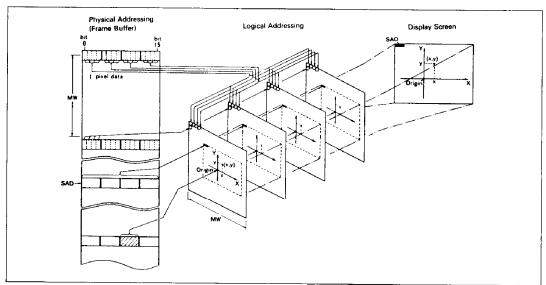

The ACRTC allows the host to issue commands in logical X-Y coordinates. The ACRTC converts these physical linear word addresses with bit field offsets in the frame buffer. Figure 3 shows the relationship between the logical X-Y screen address and the frame buffer memory, which is organized as sequential 16-bit words. The host may specify logical pixels of 1, 2, 4, 8, or 16 physical bits in the frame buffer. The system in figure 3 uses 4-bit logical pixels, allowing 16 colors or tones to be selected.

Up to four logical screens (upper, base, lower, and window) are mapped onto the ACRTC physical address space. The host specifies a logical screen physical start address, logical screen physical memory width (memory words per raster), logical pixel physical memory width (bit per pixel), and the logical origin physical address. Then the ACRTC converts logical pixel X-Y addresses issued by the host MPU or the ACRTC drawing processor to physical frame buffer addresses. The ACRTC also performs bit extraction and masking to map logical pixel

operations (for example, 4 bits), to 16-bit word frame buffer addresses.

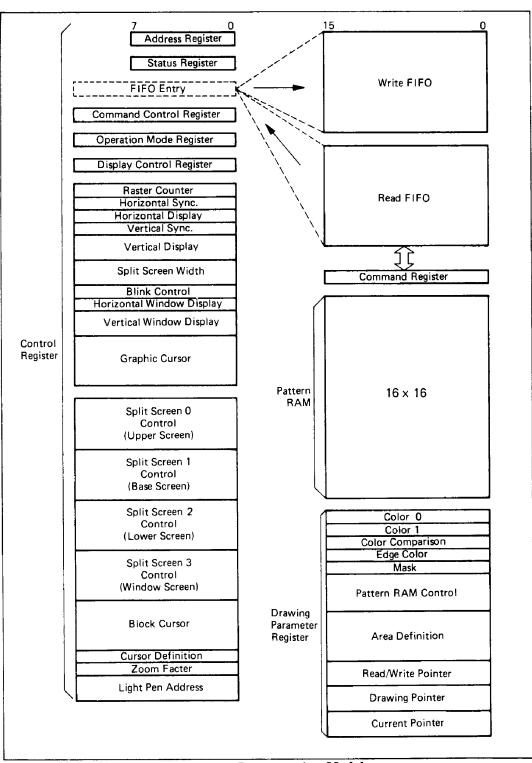

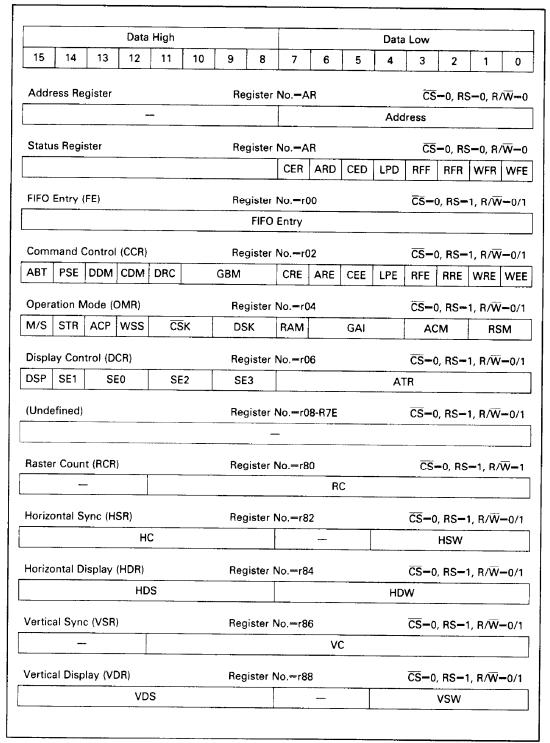

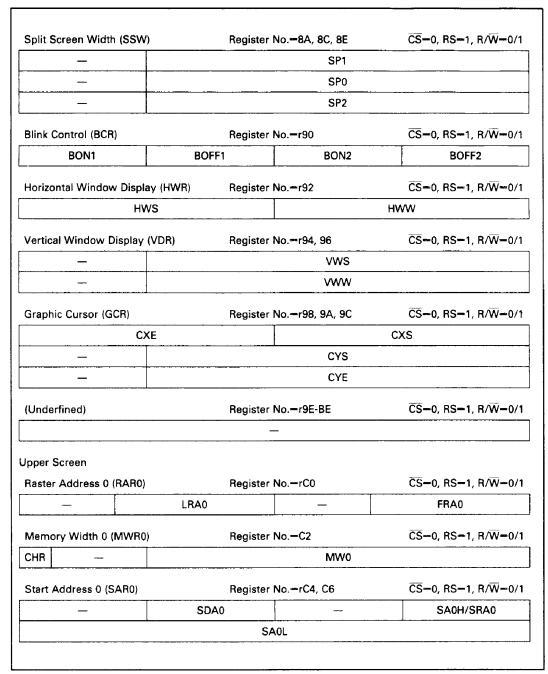

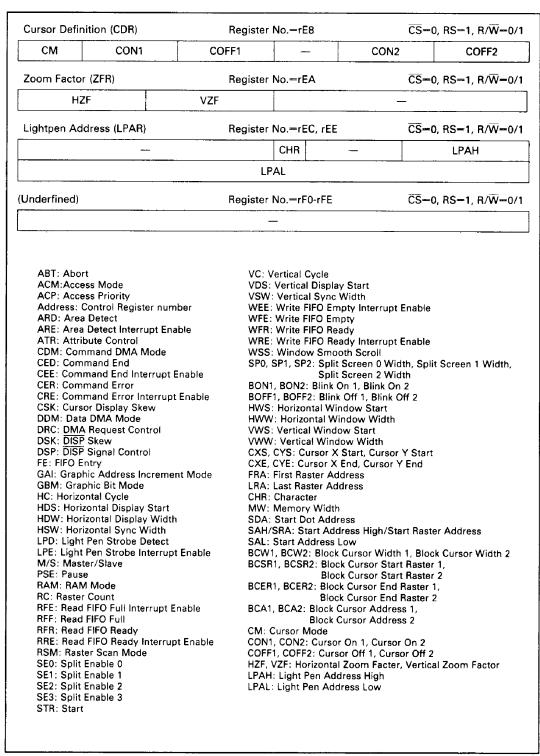

#### Registers

The ACRTC has over 200 bytes of accessible registers (figures 4, 5 and table 1). They are organized as hardware access, direct access, and FIFO access.

Hardware Access: The ACRTC is connected to the host MPU as a standard memory-mapped peripheral that occupies two word locations of the host's address space. The RS (register select) pin selects one of these two locations. When RS = 0 (low), read operations access the status register, and write operations access the address register.

The status register summarizes the ACRTC state. It monitors the overall state of the ACRTC for the host MPU.

When the MPU wants to access a direct access register, it puts the register's address

Figure 3. Logical/Physical Addressing

into the ACRTC address register.

**Direct Access:** The MPU accesses the direct access registers by first loading the register address into the address register. Then, when the MPU accesses the ACRTC with RS = 1 (high), the chosen register is accessed.

The FIFO entry register enables the MPU to access FIFO access registers using the ACRTC read and write FIFOs.

The command control register controls overall ACRTC operations, such as aborting or pausing commands, defining DMA protocols, and enabling/disabling interrupt sources.

The operation mode register defines basic parameters of ACRTC operation, such as frame buffer access mode, display or drawing priority, cursor and display timing skew factors, and raster scan mode.

The display control register independently enables and disables the four ACRTC logical address screens (upper, base, lower, and window). It also contains 8 user-defined video attribute bits.

The timing control RAM registers define ACRTC timing, including timing specifications for CRT control signals (HSYNC, VSYNC, etc), logical display screen size and

display period, and blink period.

The display control RAM contains registers which define logical screen display parameters, such as start address, raster address, and memory width. It also includes the cursor(s) definition, zoom factor, and lightpen registers.

FIFO Access: For high-performance drawing, key drawing processor registers are coupled to the host MPU via the ACRTC's 16-byte read and write FIFOs.

ACRTC commands are sent from the MPU via the write FIFO to the command register. As the ACRTC completes a command, the next command is automatically fetched from the write FIFO and put into the command register.

The pattern RAM defines drawing and painting patterns. It is accessed with the ACRTC's Read Pattern RAM (RPTN) and Write Pattern RAM (WPTN) register access commands.

The drawing parameter registers define detailed parameters of the drawing process, such as color data, area control (hitting/clipping), and pattern RAM pointers. The drawing parameter registers are accessed using the ACRTC's Read Parameter Register (RPR) and Write Parameter Register (WPR) commands.

#### **M**HITACHI

Figure 4. Programming Model

## **@HITACHI**

Figure 5. Hardware Access and Direct Access Registers

## **OHITACHI**

Figure 5. Hardware Access and Direct Access Registers (cont)

| 3 C                                                                                                                             |                                                                                                                    |                                                                                                                        |

|---------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| Base Screen                                                                                                                     |                                                                                                                    |                                                                                                                        |

| Raster Address 1 (RAR1)                                                                                                         | Register NorC8                                                                                                     | CS-0, RS-1, R/W-0/1                                                                                                    |

| _                                                                                                                               | LRA1 —                                                                                                             | - FRA1                                                                                                                 |

| Memory Width 1 (MWR1)                                                                                                           | Register NorCA                                                                                                     | CS-0, RS-1, R/W-0/1                                                                                                    |

| CHR —                                                                                                                           |                                                                                                                    | MW1                                                                                                                    |

| Start Address 1 (SAR1)                                                                                                          | Register NorCC, r                                                                                                  | rCE                                                                                                                    |

| _                                                                                                                               | SDA1                                                                                                               | - SA1H/SRA1                                                                                                            |

|                                                                                                                                 | SA1L                                                                                                               |                                                                                                                        |

| Lower Screen                                                                                                                    |                                                                                                                    |                                                                                                                        |

| Raster Address 2 (RAR2)                                                                                                         | Register NorD0                                                                                                     | CS−0, RS−1, R/W−0/1                                                                                                    |

|                                                                                                                                 | LRA2 —                                                                                                             | - FRA2                                                                                                                 |

| Memory Width 0 (MWR2)                                                                                                           | Register NorD2                                                                                                     | CC_0 BC_1 BAN_0/1                                                                                                      |

| CHR —                                                                                                                           |                                                                                                                    | CS-0, RS-1, R/W-0/1                                                                                                    |

|                                                                                                                                 |                                                                                                                    |                                                                                                                        |

| Start Address 0 (SAR2)                                                                                                          | Pogister No 124 1                                                                                                  | CC 0 DC 4 D04/ 0/4                                                                                                     |

| Otal Address o (DANZ)                                                                                                           | Register NorD4, D                                                                                                  | <del></del>                                                                                                            |

| — — — — — — — — — — — — — — — — — — —                                                                                           | SDA2                                                                                                               | _ SA2H/SRA2                                                                                                            |

| _                                                                                                                               |                                                                                                                    |                                                                                                                        |

| Window Screen                                                                                                                   | SDA2<br>SA2L                                                                                                       | — SA2H/SRA2                                                                                                            |

| _                                                                                                                               | SDA2  SA2L  Register NorD8                                                                                         |                                                                                                                        |

| Window Screen                                                                                                                   | SDA2<br>SA2L                                                                                                       | — SA2H/SRA2  — SA2H/SRA2  — SA2H/SRA2                                                                                  |

| Window Screen                                                                                                                   | SDA2  SA2L  Register NorD8                                                                                         | — SA2H/SRA2  — CS−0, RS−1, R/W−0/1  FRA3                                                                               |

| Window Screen Raster Address 3 (RAR3)                                                                                           | SDA2  SA2L  Register NorD8  LRA3  Register NorDA                                                                   | — SA2H/SRA2  — CS−0, RS−1, R/W−0/1  FRA3                                                                               |

| Window Screen Raster Address 3 (RAR3) — Memory Width 0 (MWR3)                                                                   | SDA2  SA2L  Register NorD8  LRA3  Register NorDA                                                                   | — SA2H/SRA2  ———————————————————————————————————                                                                       |

| Window Screen Raster Address 3 (RAR3) — Memory Width 0 (MWR3) CHR —                                                             | SDA2  SA2L  Register NorD8  LRA3  Register NorDA                                                                   | — SA2H/SRA2  ———————————————————————————————————                                                                       |

| Window Screen Raster Address 3 (RAR3) — Memory Width 0 (MWR3) CHR —                                                             | SDA2  SA2L  Register NorD8  LRA3  Register NorDA  Register NorDC, r                                                | — SA2H/SRA2  ———————————————————————————————————                                                                       |

| Window Screen Raster Address 3 (RAR3) — Memory Width 0 (MWR3) CHR —                                                             | SDA2  Register No.—rD8  LRA3  Register No.—rDA  Register No.—rDC, r                                                | — SA2H/SRA2    CS−0, RS−1, R/W−0/1     FRA3   CS−0, RS−1, R/W−0/1     MW3   DE   CS−0, RS−1, R/W−0/1     SA3H/SRA3     |

| Window Screen Raster Address 3 (RAR3)  —  Memory Width 0 (MWR3)  CHR —  Start Address 0 (SAR3)  —  Block Cursor 1 (BCUR1)       | SDA2  Register No.—rD8  LRA3  Register No.—rDA  Register No.—rDC, r  SDA3  SA3L                                    | — SA2H/SRA2    CS−0, RS−1, R/W−0/1     FRA3   CS−0, RS−1, R/W−0/1     MW3   DE   CS−0, RS−1, R/W−0/1     SA3H/SRA3     |

| Window Screen Raster Address 3 (RAR3)  —  Memory Width 0 (MWR3)  CHR —  Start Address 0 (SAR3)  —  Block Cursor 1 (BCUR1)       | SDA2  Register No.—rD8  LRA3  Register No.—rDA  Register No.—rDC, r  SDA3  SA3L  Register No.—rE0, rE              | — SA2H/SRA2  — SA2H/SRA2  — CS−0, RS−1, R/W−0/1  — FRA3  — CS−0, RS−1, R/W−0/1  — SA3H/SRA3  E2  — CS−0, RS−1, R/W−0/1 |

| Window Screen Raster Address 3 (RAR3)  —  Memory Width 0 (MWR3)  CHR —  Start Address 0 (SAR3)  —  Block Cursor 1 (BCUR1)       | SDA2  Register No.—rD8  LRA3  Register No.—rDA  Register No.—rDC, r  SDA3  SA3L  Register No.—rE0, rE              | — SA2H/SRA2    CS=0, RS=1, R/W=0/1     FRA3     CS=0, RS=1, R/W=0/1     MW3    DE                                      |

| Window Screen Raster Address 3 (RAR3)  —  Memory Width 0 (MWR3)  CHR —  Start Address 0 (SAR3)  —  Block Cursor 1 (BCUR1)  BCW1 | SDA2  Register No.—rD8  LRA3  Register No.—rDA  Register No.—rDC, r  SDA3  SA3L  Register No.—rE0, rE  BCSR1  BCA1 | — SA2H/SRA2    CS−0, RS−1, R/W−0/1     FRA3   CS−0, RS−1, R/W−0/1     MW3    DE                                        |

Figure 5. Hardware Access and Direct Access Registers (cont)

## **OHITACHI**

Figure 5. Hardware Access and Direct Access Registers (cont)

## **OHITACHI**

**Table 1. Drawing Parameter Registers**

| Register | Read/ |                     |       | D       | ata (H)  |     |    | _   |   |     | 1 | ata | (L | .)  |   |

|----------|-------|---------------------|-------|---------|----------|-----|----|-----|---|-----|---|-----|----|-----|---|

| No.      | Write | Name of Register    | Abbr. | 15 14 1 | 3 12 11  | 109 | 8  | 7   | 6 | 5   | 4 | 3   | 2  | 1   | 0 |

| Pr00     | R/W   | Color 0             | CLO   |         |          |     | (  | CLO |   |     |   |     |    |     |   |

| Pr01     | R/W   | Color 1             | CL1   | CL1     |          |     |    |     |   |     |   |     |    |     |   |

| Pr02     | R/W   | Color Comparison    | CCMP  |         |          |     | С  | СМ  | P |     |   |     |    |     |   |

| Pr03     | R/W   | Edge Color          | EDG   |         |          |     | E  | DG  |   |     |   |     |    |     |   |

| Pr04     | R/W   | Mask                | MASK  |         |          |     | М  | ASI | K |     |   |     |    |     |   |

| Pr05     | R/W   | Pattern RAM Control | PRC   | PPY     | PPY PZCY |     |    |     |   | PPX | ( | Ţ   | P  | ZC) | ( |

| 1        |       |                     |       | PSY     | '        |     |    |     |   | PSX | ( | _   |    | -   |   |

| Pr07     |       |                     |       | PEY     |          | PZY |    |     |   | PEX | ( |     |    | PZX |   |

| Pr08     | R/W   | Area Definition**   | ADR   | !       |          |     | Х  | MIN | 1 |     |   |     |    |     |   |

| Ţ        |       |                     |       |         |          |     | Υ  | MIN | 1 |     |   |     |    |     |   |

|          |       |                     |       |         |          |     | XI | MA) | Χ |     |   |     |    |     |   |

| Pr08     |       |                     |       |         |          |     | ΥI | MA) | X |     |   |     |    |     |   |

| Pr0C     | R/W   | Read Write Pointer  | RWP   | DN      |          |     |    |     |   |     | R | WP  | 1  |     |   |

| Pr0D     |       |                     |       |         |          | RW  | PL |     |   |     |   | Т   |    | _   | - |

| Pr0E     | _     | Undefined           | _     |         |          |     |    | _   |   |     |   |     |    |     |   |

| Pr0F     |       |                     |       |         |          |     |    | _   | _ |     |   |     |    |     |   |

| Pr010    | R     | Drawing Pointer     | DP    | DN      |          |     |    |     |   |     | 0 | PAI | 4  |     |   |

| Pr11     |       |                     |       |         |          | DP  | ΔL |     |   | -   |   | I   |    | DF  | D |

| Pr12     | R     | Current Pointer**   | СР    | X       |          |     |    |     |   |     |   |     |    |     |   |

| Pr13     |       |                     |       | Y       |          |     |    |     |   |     |   |     |    |     |   |

| Pr14     | _     | Undefined           | _     |         |          |     |    | _   |   |     |   |     | _  |     |   |

| Pr15     |       |                     |       |         |          |     |    | _   |   |     |   |     |    |     |   |

<sup>-:</sup> Always set to 0.

#### Drawing Parameter Register

- R: Register which can be read by Read Parameter Register Command (RPR)

- W: Register which can written into by Write Parameter Register Command (WPR)

- -: Access is not allowed

- CL0: Defines the color data used for the drawing when logical drawing data-0

- CL1: Defines the color data used for the drawing when logical drawing data=1

- CCMP: Defines the comparison color of the drawing operation

- PSX, PSY: Pattern Start Point

- PEX, PEY: Pattern End Point

- PPX, PPY: Pattern Scan Start Point

- PZX, PZY: Pattern Zoom

- PZCX, PZCY: Pattern Zoom Count

- XMIN, YMIN: Start point of Area definition XMAX, YMAX: End point of Area definition

- Dn: Screen Number

- RWPH: High-order 8 bits of Read Write Pointer Address RWPL: Low-order 12 bits of Read Write Pointer Address DPAH: High-order 8 bits of Drawing Pointer Address DPAL: Low-order 12 bits of Drawing Pointer Address

- **DPD: Drawing Pointer Dot Address**

- X, Y: Position indicated by Current Pointer on X-Y coodinate

#### (1) HITACHI

<sup>\*\*:</sup> Set two's complements for negative values of X and Y axis.

### **Display Functions**

#### Logical Display Screens

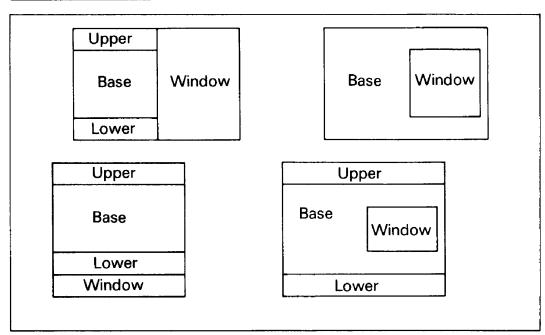

The ACRTC allows the frame buffer to be divided into four separate logical screens (table 2, figure 6).

In the simplest case, only the base screen parameters must be defined. Other screens may be selectively enabled, disabled, and blanked under software control.

The background screens (upper, base, and lower) split the screen into three horizontal partitions whose positions are fully programmable. A typical application might use the base screen for the bulk of user interac-

tion, using the lower screen for a "status line(s)" and the upper screen for "pulldown menus".

The window screen is unique, since the ACRTC usually gives it higher priority than the background screens. Thus, when the window, whose size and position is completely programmable, overlaps a background screen, the window is displayed. The exception is in the ACRTC superimposed mode, in which the window has the same priority as the background screens. In this mode, the window and background screens are "superimposed" on the display.

Table 2. Logical Screen

| Screen Number | Screen Name   | Screen Group       |

|---------------|---------------|--------------------|

| 0             | Upper screen  | Background screens |

| 1             | Base screen   |                    |

| 2             | Low screen    |                    |

| 3             | Window screen |                    |

Figure 6. Screen Combination Examples

#### Frame Memory Setup

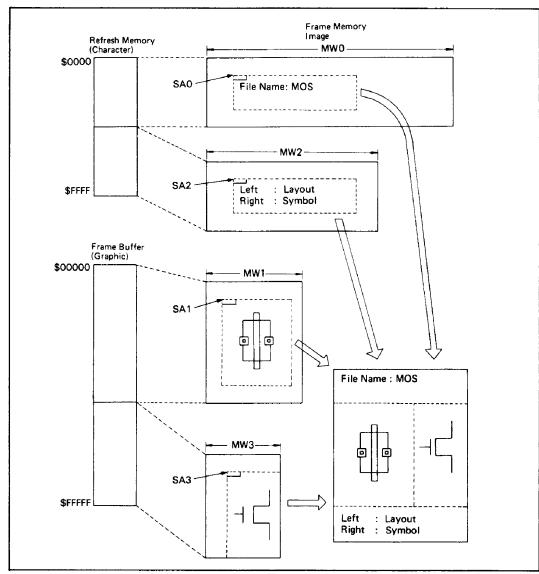

The ACRTC can have two independent frame memories, a 2-Mbyte frame buffer and a 128-kbyte refresh memory. The CHR output controls which memory is accessed.

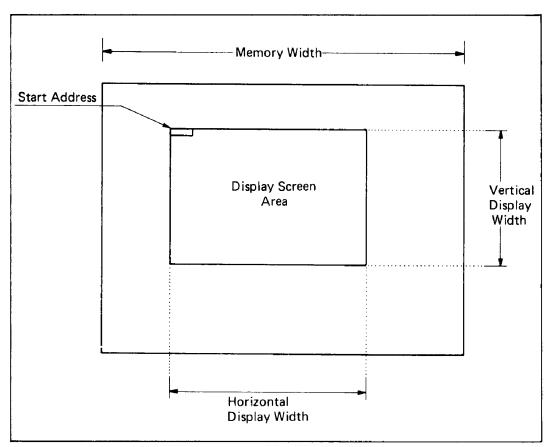

Frame memory width is defined by setting up the memory width register (MWR). The horizontal width is independently defined by the horizontal display register (HDR). The memory area can therefore be specified bigger than the display area (figure 7).

Figure 7. Frame Memory and Display Screen Area

### **Display Control**

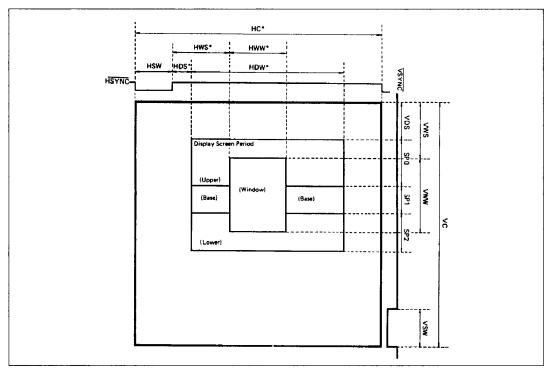

Figure 8 shows the relation between the frame memory and display screens. Each screen has its own memory width, vertical display width, and character/graphic attribution. These specifications are set by the control registers.

Horizontal display control registers are set in units of memory cycles. Vertical display control registers are set in units of rasters.

Note that display width of registers marked with an asterisk (\*) in figure 9 is:

(Display width) = (Register value) + 1 memory cycles

Figure 8. Frame Memory and Display Screens

**OHITACHI**

Figure 9. Display Screen Specification

#### Commands

The ACRTC has 38 commands classified into three groups (tables 3, 4):

- Register access

- Data transfer

- Graphic drawing

Five register access commands give the host MPU access to drawing processor drawing parameter registers and the pattern RAM.

Ten data transfer commands move data between the host system memory and the frame buffer, or within the frame buffer.

Twenty-three graphic drawing commands cause the ACRTC to draw. Parameters for these commands are specified using logical X-Y addressing.

All commands, parameters, and data are trasnferred via the ACRTC read and write FIFOs.

Assuming the ACRTC has been properly initialized, the MPU must perform two

steps to make the ACRTC draw:

- First the MPU must specify drawing parameters that define the details associated with the drawing. For example, to draw a figure or paint an area, the MPU must specify the drawing or painting pattern by initializing the ACRTC pattern RAM and related pointers. If clipping or hitting control are desired, the MPU must specify the area to be monitored during drawing by initilizing the area definition registers. Other drawing parameters include color, edge definition, etc.

- After the drawing parameters have been specified, the MPU issues a drawing command and any required command parameters, such as the CRCL (circle) command with a radius parameter

The ACRTC then performs the specified drawing operation by reading, modifying, and rewriting the contents of the frame buffer.

230

Table 3. ACRTC Command Table

| Type     | Mnemonic | Command Name              | # (words) | Operation Cycles *1                         |

|----------|----------|---------------------------|-----------|---------------------------------------------|

| Register | ORG      | Origin                    | 3         | 8                                           |

| Access   | WPR      | Write Parameter Register  | 2         | 6                                           |

| Command  | RPR      | Read Parameter Register   | 1         | 6                                           |

|          | WPTN     | Write Pattern RAM         | n+2       | 4n+8                                        |

|          | RPTN     | Read Pattern RAM          | 2         | 4n+10                                       |

| Data     | DRD      | DMA Read                  | 3         | $(4x+8)y+12[x\cdot y/8\uparrow]+(62\sim68)$ |

| Transfer | DWT      | DMA Write                 | 3         | (4x+8)y+16[x·y/81]+34                       |

| Command  | DMOD     | DMA Modify                | 3         | (4x+8)y+16[x·y/81]+34                       |

|          | RD       | Read                      | 1         | 12                                          |

|          | WT       | Write                     | 2         | 8                                           |

|          | MOD      | Modify                    | 2         | 8                                           |

|          | CLR      | Clear                     | 4         | (2x+8)y+12                                  |

|          | SCLR     | Selective Clear           | 4         | (4x+6)y+12                                  |

|          | CPY      | Сору                      | 5         | (6x+10)y+12                                 |

|          | SCPY     | Selective Copy            | 5         | (6x+10)y+12                                 |

| Graphic  | AMOVE    | Absolute Move             | 3         | 56                                          |

| Drawing  | RMOVE    | Relative Move             | 3         | 56                                          |

| Command  | ALINE    | Absolute Line             | 3         | P+L+18                                      |

|          | RLINE    | Relative Line             | 3         | P·L+18                                      |

|          | ARCT     | Absolute Rectangle        | 3         | 2P(A+B)+54                                  |

|          | RRCT     | Relative Rectangle        | 3         | 2P(A+B)+54                                  |

|          | APLL     | Absolute Polyline         | 2n+2      | Σ[P·L+16]+8                                 |

|          | RPLL     | Relative Polyline         | 2n+2      | Σ[P·L+16]+8                                 |

|          | APLG     | Absolute Polygon          | 2n+2      | Σ[P·L+16]+P·Lo+20                           |

|          | RPLG     | Relative Polygon          | 2n+2      | Σ[P·L+16]+P·Lo+20                           |

|          | CRCL     | Circle                    | 2         | 8d+66                                       |

|          | ELPS     | Ellipse                   | 4         | 10d+90                                      |

|          | AARC     | Absolute Arc              | 5         | 8d+18                                       |

|          | RARC     | Relative Arc              | 5         | 8d+18                                       |

|          | AEARC    | Absolute Ellipse Arc      | 7         | 10d+96                                      |

|          | REARC    | Relative Ellipse Arc      | 7         | 10d+96                                      |

|          | AFRCT    | Absolute Filled Rectangle | 3         | (P·A+8)B+18                                 |

|          | RFRCT    | Relative Filled Rectangle | 3         | (P-A+8)B+18                                 |

|          | PAINT    | Paint                     | 1         | (18A+102)B-58 *2                            |

|          | DOT      | Dot                       | 1         | 8                                           |

|          | PTN      | Pattern                   | 2         | (P·A+10)B+20                                |

|          | AGCPY    | Absolute Graphic Copy     | 5         | ((P+2)A+10)B+70                             |

|          | RGCPY    | Relative Graphic Copy     | 5         | ((P+2)A+10)B+70                             |

Notes: 1. 2CLK cycles.

- 2. Applies to rectangular figures. Time varies for other shapes.

- 3. Abbreviations

- n: Number of read/write data words

- x: Number of words in X direction

- y: Number of words in Y direction

- t: Round up

- P: Operation cycles—P=4 cycles when OPM=000-011;

P=6 cycles when OPM=100-111

- L, Lo: Number of dots in a straight line

- d: Total number of dots

- A: Number of dots in main scan direction

- B: Number of dots in sub scan direction

Table 4. Command Operation Codes and Parameters

| Type     | Mnemonic |   |   |   |   | 0  | pe  | ra  | tio | n | Co | de | )   |    |     |     |   |     | P     | aram    | eter  |        |     |

|----------|----------|---|---|---|---|----|-----|-----|-----|---|----|----|-----|----|-----|-----|---|-----|-------|---------|-------|--------|-----|

| Register | ORG      | 0 | 0 | 0 | 0 | 0  | 1   | 0   | 0   | 0 | 0  | ō  | 0   | 0  | (   | 0 0 | 0 | DPH | DPL   |         |       |        |     |

| Access   | WPR      | 0 | 0 | 0 | 0 | 1  | 0   | 0   | 0   | 0 | 0  | 0  |     |    | R   | N   |   | D   |       |         |       |        |     |

| Command  | RPR      | 0 | 0 | 0 | 0 | 1  | 1   | 0   | 0   | Ô | 0  | 0  |     |    | R   | N   |   |     |       |         |       |        |     |

|          | WPTN     | 0 | 0 | 0 | 1 | 1  | 0   | 0   | 0   | 0 | 0  | 0  | 0   |    | F   | PRA |   | n   | D1, . | , Dn    |       |        |     |

|          | RPTN     | 0 | 0 | 0 | 1 | 1  | 1   | 0   | 0   | 0 | 0  | 0  | 0   |    | F   | PRA |   | n   |       |         |       |        |     |

| Data     | DRD      | 0 | 0 | 1 | 0 | 0  | 1   | 0   | 0   | 0 | 0  | 0  | 0   | 0  | -{  | 0 0 | 0 | AX  | AY    |         |       |        |     |

| Transfer | DWT      | 0 | 0 | 1 | 0 | 1  | 0   | 0   | 0   | 0 | 0  | 0  | 0   | 0  | (   | 0 0 | 0 | AX  | AY    |         |       |        |     |

| Command  | DMOD     | 0 | 0 | 1 | 0 | 1  | 1   | 0   | 0   | 0 | 0  | 0  | 0   | 0  | (   | 0 M | М | AX  | AY    |         |       |        |     |

|          | RD       | 0 | 1 | 0 | 0 | 0  | 1   | 0   | 0   |   |    | 0  | 0   | 0  | (   | 0 0 | 0 | -   |       |         |       |        |     |

|          | WT       | 0 | 1 | 0 | 0 | 1  | 0   | 0   | 0   | 0 | 0  | 0  | 0   | 0  | (   | 0 0 | 0 | D   |       |         |       |        |     |

|          | MQD      | 0 | 1 | 0 | 0 | 1  | 1   | 0   | 0   |   |    | 0  | 0   | 0  | (   | 0 M | м | D   |       |         |       |        |     |

|          | CLR      | 0 | 1 | 0 | 1 | 1  | 0   | 0   | 0   | 0 | 0  | 0  | 0   | 0  | (   | 0 0 | 0 | D   | AX    | AY      |       |        |     |

|          | SCLR     | 0 | 1 | 0 | 1 | 1  | 1   | 0   | 0   | 0 | 0  | 0  | 0   | 0  | (   | O M | М | D   | AX    | AY      |       |        |     |

|          | CPY      | 0 | 1 | 1 | 0 | S  |     | OSC |     | 0 |    | 0  | 0   | 0  | -   | 0 0 | 0 | SAH | SAL   | AX      | ΑŸ    |        |     |

|          | SCPY     | 0 | 1 | 1 | 1 | S  |     | OSE | )   | 0 | 0  | 0  | 0   | Ö  | (   | 0 M | М | SAH | SAL   | AX      | AY    |        |     |

| Graphic  | AMOVE    | 1 | 0 | ō | 0 | 0  | ō   | 0   | 0   |   | 0  | 0  | 0   | 0  | - ( | 0 0 | 0 | X   | Y     |         |       |        |     |

| Drawing  | RMOVE    | 1 | 0 | 0 | 0 | 0  | 1   | 0   | 0   | 0 | 0  | 0  | 0   | 0  | -   | 0 0 | 0 | dΧ  | dΥ    |         |       |        |     |

| Command  | ALINE    | 1 | 0 | 0 | 0 | 1  | 0   | 0   |     |   | AR | EΑ | С   | OL | . 7 | ОРМ |   | Х   | Υ     |         |       | •      |     |

|          | RLINE    | 1 | 0 | 0 | 0 | 1  | 1   | 0   | 0   |   |    |    |     |    |     | ОРМ |   | dΧ  | dΥ    |         |       |        |     |

|          | ARCT     | 1 | 0 | 0 | 1 | 0  | 0   | 0   | 0   |   | AR | EΑ | C   | οī | _ ( | OPM |   | X   | Y     |         |       |        |     |

|          | RRCT     | 1 | 0 | 0 | 1 | 0  | 1   | 0   | 0   |   |    |    |     |    |     | ОРМ |   | dΧ  | dΥ    |         |       |        |     |

|          | APLL     | 1 | 0 | 0 | 1 | 1  | 0   | 0   | 0   |   | AR | EΑ | С   | Ōί | . 1 | ОРМ |   | n   | X1    | , Y1, . | . Xn, | Υn     |     |

|          | RPLL     | 1 | 0 | 0 | 1 | 1  | 1   | 0   | 0   |   | AR | EΑ | C   | ΟL | _ ( | ОРМ |   | n   |       |         |       | ı, dYn |     |

|          | APLG     | 1 | 0 | 1 | 0 | 0  | 0   | 0   | Ō   |   |    |    |     |    |     | OPM |   | n   | X1    | Y1, .   | , Xn, | Yn     |     |

|          | RPLG     | 1 | 0 | 1 | 0 | 0  | 1   | 0   | 0   |   | AR | EΑ | С   | ΟL |     | OPM |   | n   |       | dY1,.   |       |        |     |

|          | CRCL     | 1 | 0 | 1 | 0 | 1  | 0   | 0   | С   |   | AR | EΑ | C   | οι | _   | OPM | _ | r   |       |         |       |        |     |

|          | ELPS     | 1 | 0 | 1 | 0 | 1  | 1   | Ö   | c   |   | AR | EΑ | C   | Oι | _   | ОРМ |   | а   | b     | DX      |       |        |     |

|          | AARC     | 1 | 0 | 1 | 1 | 0  | 0   | 0   | С   |   | AR | EΑ | · C | Oι | _   | ОРМ |   | Хc  | Υc    | Xe      | Ye    |        |     |

|          | RARC     | 1 | 0 | 1 | 1 | 0  | 1   | 0   | С   |   | AR | EΑ | C   | Οl | L   | OPM | 1 | dXc | dΥ¢   | dXe     | dYe   |        |     |

|          | AEARC    | 1 | 0 | 1 | 1 | 1  | 0   | 0   | С   |   | AR | EA | C   | Οl | L   | OPM | ı | а   | b     | Хc      | Yc    | Хe     | Ye  |

|          | REARC    | 1 | 0 | 1 | 1 | 1  | 1   | 0   | С   |   | AR | EΑ | C   | Οl | L   | OPN | ı | а   | b     | dXc     | dYc   | dXe    | dYe |

|          | AFRCT    | 1 | 1 | 0 | 0 | 0  | 0   | 0   | 0   |   | AR | EA | V C | Οl | L   | OPN | Г | Х   | Υ     |         |       |        |     |

|          | RFRCT    | 1 | 1 | 0 | 0 | 0  | 1   | 0   | 0   |   | AR | EΑ | C   | OI | L   | OPN | 1 | dΧ  | dΥ    |         |       |        |     |

|          | PAINT    | 1 | 1 | 0 | 0 | 1  | 0   | 0   | Ε   |   | AR | EA | 0   | 0  | )   | 00  | 0 |     |       |         |       |        |     |

|          | DOT      | 1 | 1 | 0 | 0 | 1  | 1   | 0   | 0   |   | ΑR | EA | C   | Oi | L   | OPN | 1 |     |       |         |       |        |     |

|          | PTN      | 1 | 1 | 0 | 1 | SI |     | SI  |     |   | AR | EA | \ C | 01 | L   | OPN | 1 | SZ  |       |         |       |        |     |

|          | AGCPY    | 1 | 1 | 1 | 0 | s  | - [ | OSC | )   |   | AR | EA | ٠ 0 | (  | )   | OPN | 1 | Xs  | Υs    | DX      | DY    |        |     |

|          | RGCPY    | 1 | 1 | 1 | 1 | s  | _   | OSE |     |   |    |    |     |    |     | OPN |   | dXs | dYs   | DX      | DY    |        |     |

Notes: 1. Register access commands abbreviations

RN: Drawing parameter register number (\$0-\$13)

PRA: Pattern RAM read/write operation starting address (\$0-\$F)

DPH: Drawing pointer register ligh word (figure 29)

DPL: Drawing pointer register low word (figure 29)

DPAH: Higher 8 bits of drawing pointer address

DPAL: Lower 12 bits of drawing pointer address

DPD: Dot position in memory address

DPD: Dot position in memory address

2. Data transfer commands abbreviations

MM: Modify mode

S: Source scan direction (figure 30)

DSD: Destination scan direction (figure 31)

AX: Number of words in X direction—1

AY: Number of words in Y direction—1

D: Write data

SAH: Source start address high word (figure 32)

SAL: Source start address low word

3. Graphic drawing commands abbreviations

AREA: Area mode

CDL: Color mode

OPM: Operation mode

C: Circle drawing direction—C ≈ 0 for counterclockwise;

C = 1 for clockwise

```

E: Edge color definition—E = 0, edge color is data in edge color register;

E = 1, edge color is any color except data in color register

SL: Slant (figure 33)

SD: Scan direction (figure 30)

SD: Destination scan direction (figure 31)

Parameter abbreviations

X, X1, ..., Xn: Absolute X address from origin point

Y, Y1, ..., Yn: Absolute X address from origin point

dX: Relative X address from current pointer

dY: Relative Y address from current pointer

n: Number of nodes

dX1, ..., dXn: Relative X address from each node

dX1, ..., dXn: Relative X address from each node

r: Number of dots on radius

a, b: ratio of dX squared to dY squared in ellipse—a:b = dX2:dY2

DX: X-direction dot number

DY: Y-direction dot number

DY: Y-direction dot number

Xc: Absolute X address of center point of arc/ellipse

dXc: Relative X address from current point to center point of arc/ellipse

dXc: Relative X address from current point to center point of arc/ellipse

dXc: Relative X address from current point to ender point of arc/ellipse

dXe: Relative X address from current point to end point of arc/ellipse

dXe: Relative X address from current point to end point of arc/ellipse

dXe: Relative X address from current point to end point of arc/ellipse

dXe: Relative X address from current point to end point of arc/ellipse

dXe: Relative X address from current point to start point of arc/ellipse

dXs: Absolute X address from current point to start point of arc/ellipse

dXs: Relative X address from current point to start point of arc/ellipse

dXs: Relative X address from current point to start point of arc/ellipse

dXs: Relative X address from current point to start point of arc/ellipse

dXs: Relative X address from current point to start point of arc/ellipse

dXs: Relative X address from current point to start point of arc/ellipse

```

#### **Program Transfer**

For program transfer, the MPU specifies the FIFO entry address and then writes commands/parameters to the write FIFO under program control (RS = high,  $R/\overline{W}$ ,  $\overline{CS}$  = low). The MPU writes are normally synchronized with FIFO status by software polling or interrupt.

**Software Polling:** WFR, WFE interrupts are disabled.

- MPU program checks the SR (status register) for write FIFO ready flag (WFR)

1, then writes 1 command/parameter word.

- MPU program checks the SR (status register) for write FIFO empty flag (WFE)

1, then writes 1 to 8 command/parameter words.

**Interrupt Driven:** WFR, WFE interrupts are enabled.

- MPU WFR interrupt service routine writes 1 command/parameter word.

- MPU WFE interrupt service routine writes 1 to 8 command/parameter words.

Register Access Commands: When writing register access commands to an in-

itially empty write FIFO, the MPU does not have to synchronize to write FIFO status. The ACRTC can fetch and execute these commands faster than the MPU can issue them.

## **Command DMA Transfer**

Commands and parameters can be transferred from the MPU system memory by an external DMAC. The MPU initiates and terminates command DMA transfer under software control (CDM bit of CCR). Command DMA transfer can also be terminated by asserting the ACRTC DONE signal. DONE is an input in command DMA transfer mode.

In command DMA transfer mode, the ACRTC issues cycle stealing DMA requests to the DMAC when the write FIFO is ready. The DMA data is automatically sent from system memory to the ACRTC write FIFO regardless of the contents of the address register.

Make sure that the write FIFO is empty and all previous commands are terminated before starting the command DMA transfor.

Data DMA transfer cannot be executed in command DMA transfer mode.

Table 7. Graphic Drawing Commands

| Command | Function                                                                                                                                                                     |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AMOVE   | Move the current pointer (CP) to an absolute logical pixel X-Y address                                                                                                       |

| RMOVE   | Move the current pointer (CP) to a relative logical pixel X-Y address                                                                                                        |

| ALINE   | Draw a straight line from the current pointer (CP) to a command-specified end point in absolute coordinates                                                                  |

| RLINE   | Draw a straight line from the current pointer (CP) to a command-specified end point in relative corrdinates                                                                  |

| ARCT    | Draw a rectangle defined by the current pointer (CP) and a command-specified diagonal point in absolute coordinates                                                          |

| RRCT    | Draw a rectangle defined by the current pointer (CP) and a command-specified diagonal point in relative coordinates                                                          |

| APLL    | Draw a polyline (multiple contiguous segments) from the current pointer (CP) through command-specified points in absolute coordinates                                        |

| RPLL    | Draw a polyline (multiple contiguous segments) from the current pointer (CP) through command-specified points in relative coordinates                                        |

| APLG    | Draw a polygon which connects the current pointer (CP) and command-specified points in absolute coordinates                                                                  |

| RPLG    | Draw a polygon which connects the current pointer (CP) and command-specified points in relative coordinates                                                                  |

| CRCL    | Draw a circle of radius R placing the current pointer (CP) at the center                                                                                                     |

| ELPS    | Draw a ellipse whose shape is specifed by command parameters, placing the current pointer (CP) at the center                                                                 |

| AARC    | Draw an arc by using the current pointer (CP) as a start point with an end point and a center point in absolute coordinates                                                  |

| RARC    | Draw an arc by using the current pointer (CP) as a start point with an end point and a center point in relative coordinates                                                  |

| AEARC   | Draw an ellipse arc by using the current pointer (CP) as a start point with an end point and a center point in absolute coordinates                                          |

| REARC   | Draw an ellipse arc by using the current pointer (CP) as a start point with an end point and a center point in relative coordinates                                          |

| AFRCT   | Paint a rectangular area specifed by the current pointer (CP) and command parameters (absolute coordinates) according to a figure pattern stored in the pattern RAM (tiling) |

| RFRCT   | Paint a rectangular area specifed by the current point (CP) and command parameters (relative coordinates) according to a figure pattern stored in the pattern RAM (tiling)   |

| PAINT   | Paint a closed area surrounded by edge color using a figure pattern stored in the pattern RAM (tiling)                                                                       |

| DOT     | Mark a dot on the coordinates indicated by the current pointer (CP)                                                                                                          |

| PTN     | Draw a graphic pattern defined in the pattern RAM onto a rectangular area specifed by the current point (CP) and by the pattern size (rotation angle: 45°)                   |

| AGCPY   | Copy a rectangular area specifed by the absolute coordinates to the address specifed by the current pointer (CP) (rotation angle: 90°/mirror reflection)                     |

| RGCPY   | Copy a rectangular area specified by the relative coordinates to the address specified by the current pointer (CP) (rotation angle: 90°/mirror reflection)                   |

## **@HITACHI**

## Notes on System Design

### Power-On Sequence

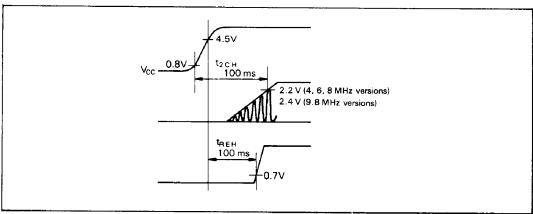

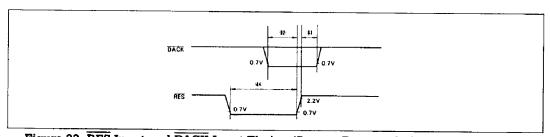

The conditions in figure 10 must be satisfied at power-on.

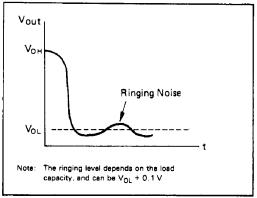

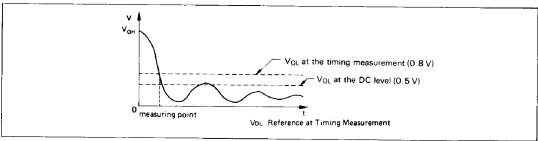

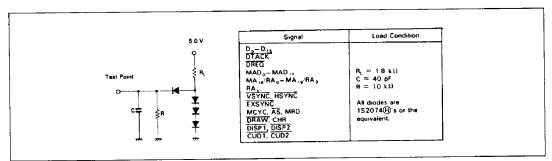

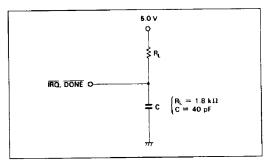

#### **Output Waveform**

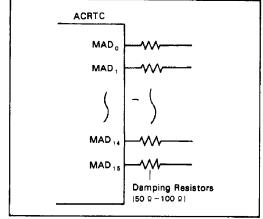

If excessive ringing (figure 11) occurs on CRT data buses, (MAD<sub>0</sub>-MAD<sub>15</sub>, MA<sub>16</sub>/RA<sub>0</sub>-MA<sub>19</sub>/RA<sub>4</sub>), damping resistors may be required as shown in figure 12.

Figure 10. Power-On Sequence

Figure 11. Ringing Noise

Figure 12. Damping Resistors

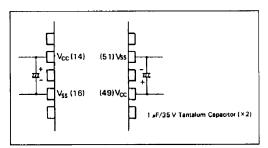

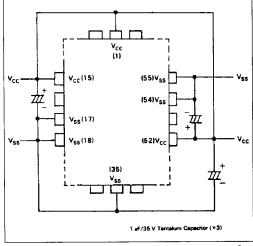

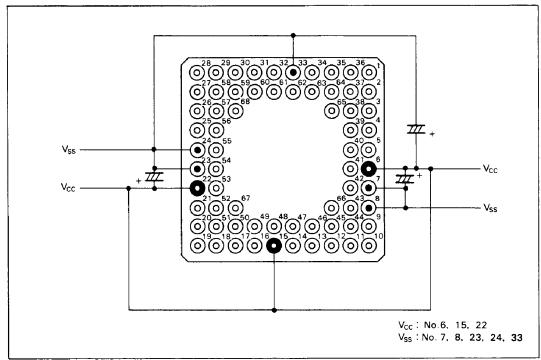

#### **Power Supply Circuit**

When laying out the  $V_{\text{CC}}$  and  $V_{\text{SS}}$  traces on

the circuit board, locate capacitors as close as possible to each power supply pin (figures 13, 14, 15).

Figure 13. Power Supply Circuit Example, 64-Pin DIP

Figure 14. Power Supply Circuit Example, 68-Pin PLCC

Figure 15. Power Supply Circuit Example 68-Pin PGA

**(1)** HITACHI

## **Absolute Maximum Ratings**

| İtem                           | Symbol                     | Rating                       | Unit |

|--------------------------------|----------------------------|------------------------------|------|

| Supply Voltage                 | V <sub>cc</sub> (Note 1)   | −0.3 to +7.0                 | ٧    |

| Input Voltage                  | V <sub>in</sub> (Note 1)   | -0.3 to V <sub>CC</sub> +0.3 | ٧    |

| Allowable Output Current       | II <sub>o</sub> I (Note 2) | 5                            | mA   |

| Total Allowable Output Current | Σ  <sub>0</sub>   (Note 3) | 120                          | mA   |

| Operating Temperature          | T <sub>opr</sub>           | 0 to +70                     | °C   |

| Storage Temperature            | T <sub>stg</sub>           | -55 to +150                  | °C   |

- Notes: 1. Referenced to  $V_{SS}=0\ V$ . 2. The maximum current that may be drawn from, or flow out of, one output, or one common input/output terminal.

- 3. The total sum of currents that may be drawn from, or flow out of, all output or common input/ output terminals.

- 4. Using an LSI beyond its maximum rating may result in its permanent destruction. LSIs should usually be used under recommended operating conditions. Exceeding any of these conditions may adversely affect reliability.

## **Recommended Operating Conditions**

| item              |                          | Symbol                 | Min  | Тур    | Max             | Unit |

|-------------------|--------------------------|------------------------|------|--------|-----------------|------|

| Supply Voltage    |                          | V <sub>cc</sub> (Note) | 4.75 | 5.0    | 5.25            | ٧    |

| Input Low Voltag  | е                        | V <sub>IL</sub> (Note) | 0    | ****** | 0.7             | ٧    |

| Input High Voltag | e (4, 6, 8 MHz versions) | V <sub>IH</sub> (Note) | 2.2  |        | V <sub>cc</sub> | V    |

|                   | (9.8 MHz version)        | V <sub>IH</sub> (Note) | 2.4  |        | V <sub>cc</sub> | V    |

| Operating Tempe   | erature                  | T <sub>opr</sub>       | 0    | 25     | 75              | °C   |

Note: Referenced to  $V_{SS} - 0 V$

## **Electrical Characteristics DC** Characteristics

( $V_{CC}$ =5.0V  $\pm$  5%,  $V_{SS}$ =0V, Ta=0°C to +70°C unless otherwise noted)

| Item                          |                                                                                                                                                                                                                                                                          | Symbol           | Min                     | Max             | Unit | Test<br>Condition                              |

|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------------|-----------------|------|------------------------------------------------|

| Input High Level<br>Voltage   | All inputs                                                                                                                                                                                                                                                               | V <sub>IH</sub>  | 2.2                     | V <sub>cc</sub> | ٧    | 4, 6, 8 MHz<br>versions                        |

|                               |                                                                                                                                                                                                                                                                          |                  | 2.4                     | V <sub>cc</sub> | ٧    | 9.8 MHz ★<br>version                           |

| Input Low Level<br>Voltage    | All inputs                                                                                                                                                                                                                                                               | V <sub>IL</sub>  | -0.3                    | 0.7             | ٧    |                                                |

| Input Leak Current            | R/W, CS, RS, RES, DACK,<br>2CLK, LPSTB                                                                                                                                                                                                                                   | l <sub>in</sub>  | -2.5                    | 2.5             | μА   | V <sub>in</sub> =0.4 to V <sub>CC</sub>        |

| Hi-Z Input Current            | D <sub>0</sub> -D <sub>15</sub> , MAD <sub>0</sub> -MAD <sub>15</sub> ,<br>EXSYNC                                                                                                                                                                                        | I <sub>TSI</sub> | -10                     | 10              | μΑ   | V <sub>in</sub> =0.4 to V <sub>CC</sub>        |

| Output High Level<br>Voltage  | D <sub>0</sub> -D <sub>15</sub> , MAD <sub>0</sub> -MAD <sub>15</sub> ,<br>CUD1, CUD2, DREQ,<br>DTACK, HSYNC, VSYNC,<br>EXSYNC, MRD, DRAW,<br>AS, DISP1, DISP2, CHR,<br>MCYC, RA <sub>4</sub> , MA <sub>16</sub> /RA <sub>0</sub> -<br>MA <sub>19</sub> /RA <sub>3</sub> | V <sub>OH</sub>  | V <sub>cc</sub><br>-1.0 |                 | μΑ   | I <sub>OH</sub> ——400μΑ                        |

| Output Low Level<br>Voltage   | D <sub>0</sub> -D <sub>15</sub> , MAD <sub>0</sub> -MAD <sub>15</sub> ,<br>CUD1, CUD2, DREQ,<br>DTACK, HSYNC, VSYNC,<br>EXSYNC, MRD, DRAW,<br>AS, DISP1, DISP2, CHR,<br>MCYC, RA <sub>4</sub> , MA <sub>16</sub> /RA <sub>0</sub> -<br>MA <sub>19</sub> /RA <sub>3</sub> | V <sub>OL</sub>  |                         | 0.5             | V    | l <sub>oL</sub> −2.2mA                         |

|                               | IRQ, DONE                                                                                                                                                                                                                                                                | VOL              |                         | 0.5             | ٧    | I <sub>OL</sub> -2.5 mA                        |

| Output Leak<br>Current (Hi-Z) | IRQ, DONE                                                                                                                                                                                                                                                                | I <sub>LOD</sub> |                         | 10              | μА   | V <sub>OH</sub> -V <sub>CC</sub>               |

| Input Capacitance             | D <sub>0</sub> -D <sub>15</sub> , MAD <sub>0</sub> -MAD <sub>15</sub> , EX-<br>SYNC, R/W, CS, RS, RES,<br>DACK, 2CLK, LPSTB                                                                                                                                              | C <sub>in</sub>  |                         | 17              | pF   | V <sub>in</sub> =0 V,<br>Ta=25°C,<br>f=1.0 MHz |

| Output Capacitance            | ĨŔQ, DONE                                                                                                                                                                                                                                                                | C <sub>out</sub> |                         | 15              | pF   | V <sub>in</sub> =0 V,<br>Ta=25°C,<br>f=1.0 MHz |

| Current Consumption           |                                                                                                                                                                                                                                                                          | I <sub>cc</sub>  |                         | 60              | mΑ   | 4 MHz version                                  |

|                               |                                                                                                                                                                                                                                                                          |                  |                         | 80              | mA   | 6 MHz version                                  |

|                               |                                                                                                                                                                                                                                                                          |                  |                         | 100             | mA   | 8 MHz version                                  |

|                               |                                                                                                                                                                                                                                                                          |                  |                         | 120             | mA   | 9.8 MHz version                                |

239

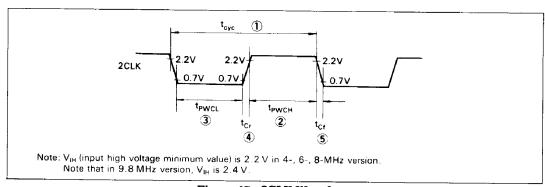

# AC Characteristics (V $_{\rm CC}$ =5.0V $\pm$ 5%, V $_{\rm SS}$ =0V, Ta=0 to +70°C unless otherwise noted) Clock Timing

| No. | Item                            | Symbol | 4 MHz<br>Version |      | 6 MHz<br>Version |      | 8 MHz<br>Version |      | 9.8 MHz<br>Version |      | Unit | Reference<br>Figure |

|-----|---------------------------------|--------|------------------|------|------------------|------|------------------|------|--------------------|------|------|---------------------|

|     |                                 |        | Min              | Max  | Min              | Max  | Min              | Max  | Min                | Max  | 1    | Number              |

|     | Operation Frequency of 2CLK     | f      | 1                | 4    | 1                | 6    | 1                | 8    | 1                  | 9.8  | MHz  |                     |

| 1   | Clock Cycle Time                | tcyc   | 250              | 1000 | 167              | 1000 | 125              | 1000 | 102                | 1000 | ns   | 1                   |

| 2   | Clock High Level Pulse<br>Width | tPWCH  | 115              | 500  | 75               | 500  | 55               | 500  | 46                 | 500  | ns   | 17                  |

| 3   | Clock Low Level Pulse<br>Width  | tPWCL  | 115              | 500  | 75               | 500  | 55               | 500  | 46                 | 500  | ns   |                     |

| 4   | Clock Rise Time                 | tor    | _                | 10   | _                | 10   |                  | 10   |                    | 5    | ns   |                     |

| 5   | Clock Fall Time                 | tcf    |                  | 10   |                  | 10   | _                | 10   |                    | 5    | ns   |                     |

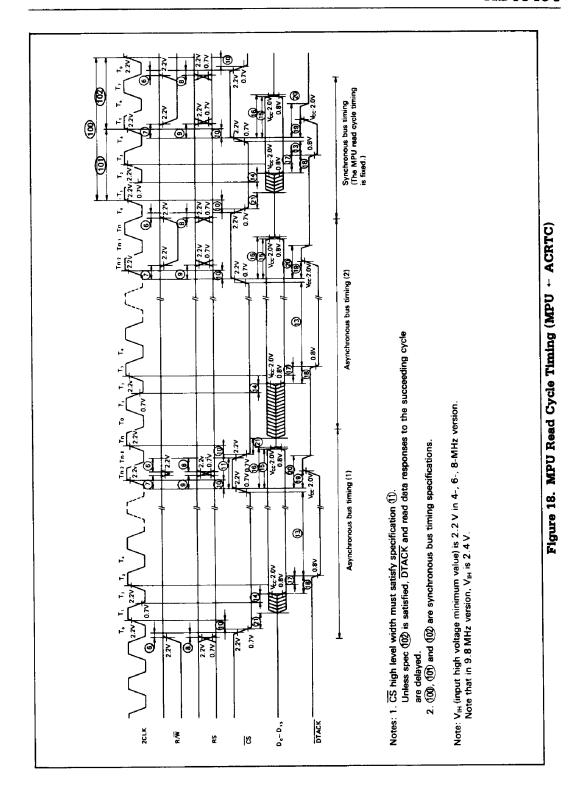

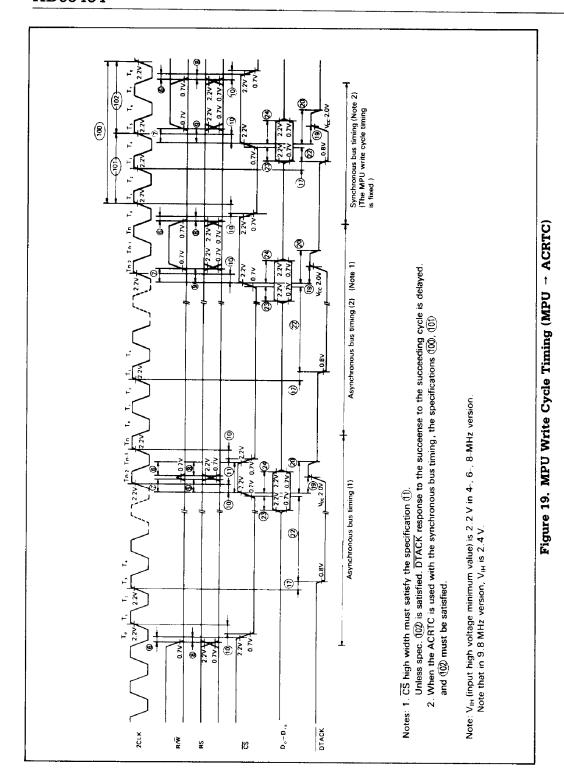

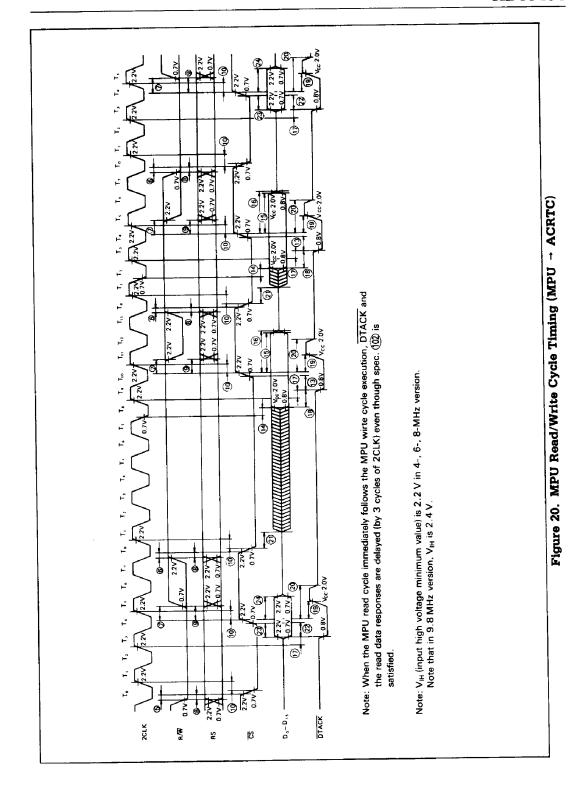

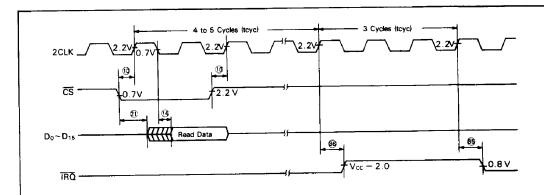

## MPU Read/Write Cycle Timing

| No. | ltem                                | Symbol |             | MHz<br>sion |     | //Hz<br>sion | l . | VIHz<br>rsion |     | MHz<br>sion | Unit | Reference<br>Figure |