# 2K x 8 Dual-Port Static RAM

#### **Features**

- True Dual-Ported memory cells which allow simultaneous reads of the same memory location

- 2K x 8 organization

- 0.65-micron CMOS for optimum speed/power

- · High-speed access: 15 ns

- Low operating power: I<sub>CC</sub> = 110 mA (max.)

- · Fully asynchronous operation

- Automatic power-down

- Master CY7C132/CY7C136 easily expands data bus width to 16 or more bits using slave CY7C142/CY7C146

- BUSY output flag on CY7C132/CY7C136; BUSY input on CY7C142/CY7C146

- INT flag for port-to-port communication (52-pin PLCC/PQFP versions)

- Available in 48-pin DIP (CY7C132/142), 52-pin PLCC and 52-pin TQFP (CY7C136/146)

- · Pb-Free packages available

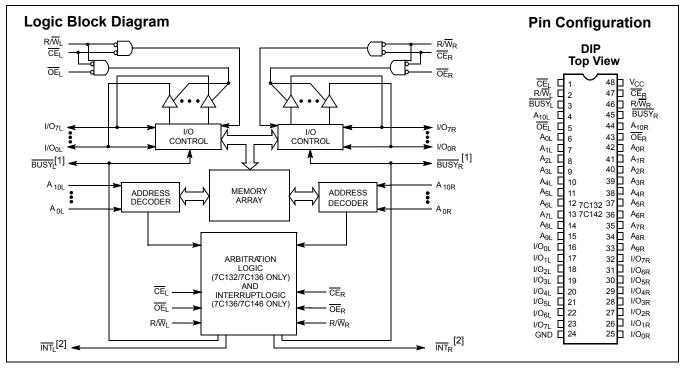

#### **Functional Description**

The CY7C132/CY7C136/CY7C142 and CY7C146 are high-speed CMOS 2K by 8 dual-port static RAMs. Two ports are provided to permit independent access to any location in memory. The CY7C132/ CY7C136 can be utilized as either a standalone 8-bit dual-port static RAM or as a MASTER dual-port RAM in conjunction with the CY7C142/CY7C146 SLAVE dual-port device in systems requiring 16-bit or greater word widths. It is the solution to applications requiring shared or buffered data such as cache memory for DSP, bit-slice, or multiprocessor designs.

Each port has <u>independent</u> control pin<u>s</u>; chip <u>enable</u> (CE), write enable (R/W), and output enable (OE). BUSY flags are provided on each port. In addition, an interrupt flag (INT) is provided on each port of the 52-pin PLCC version. BUSY signals that the port is trying to access the same location currently <u>being</u> accessed by the other port. On the PLCC version, INT is an interrupt flag indicating that data has been placed in a unique location (7FF for the left port and 7FE for the right port).

An automatic power-down feature is controlled independently on each port by the chip enable (CE) pins.

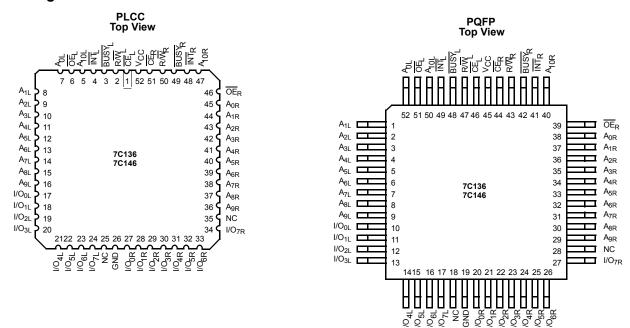

The CY7C132/CY7C142 are available in 48-pin DIP. The CY7C136/CY7C146 are available in 52-pin PLCC and PQFP.

#### Notes:

- CY7C132/CY7C136 (Master): BUSY is open drain output and requires pull-up resistor. CY7C142/CY7C146 (Slave): BUSY is input.

- 2. Open drain outputs; pull-up resistor required.

Cypress Semiconductor Corporation Document #: 38-06031 Rev. \*C

198 Champion Court •

San Jose, CA 95134-1709

-1709 • 408-943-2600 Revised September 1, 2005

## **Pin Configurations**

#### **Selection Guide**

|                           |           | 7C136-15 <sup>[3]</sup><br>7C146-15 | 7C132-25 <sup>[3]</sup><br>7C136-25<br>7C142-25<br>7C146-25 | 7C132-30<br>7C136-30<br>7C142-30<br>7C146-30 | 7C132-35<br>7C136-35<br>7C142-35<br>7C146-35 | 7C132-45<br>7C136-45<br>7C142-45<br>7C146-45 | 7C132-55<br>7C136-55<br>7C142-55<br>7C146-55 | Unit |

|---------------------------|-----------|-------------------------------------|-------------------------------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|------|

| Maximum Access Time       |           | 15                                  | 25                                                          | 30                                           | 35                                           | 45                                           | 55                                           | ns   |

| Maximum Operating Current | Com'l/Ind | 190                                 | 170                                                         | 170                                          | 120                                          | 120                                          | 110                                          | mA   |

| Maximum Operating Current | Military  |                                     |                                                             |                                              | 170                                          | 170                                          | 120                                          | mA   |

| Maximum Standby Current   | Com'l/Ind | 75                                  | 65                                                          | 65                                           | 45                                           | 45                                           | 35                                           | mA   |

|                           | Military  |                                     |                                                             |                                              | 65                                           | 65                                           | 45                                           |      |

Shaded areas contain preliminary information.

**Note:**3. 15 and 25-ns version available in PQFP and PLCC packages only.

## **Maximum Ratings**

(Above which the useful life may be impaired. For user guidelines, not tested.) Storage Temperature ......-65°C to +150°C Ambient Temperature with Supply Voltage to Ground Potential (Pin 48 to Pin 24).....-0.5V to +7.0V DC Voltage Applied to Outputs in High-Z State ......-0.5V to +7.0V

| DC Input Voltage                                       | 3.5V to +7.0V |

|--------------------------------------------------------|---------------|

| Output Current into Outputs (LOW)                      | 20 mA         |

| Static Discharge Voltage(per MIL-STD-883, Method 3015) | > 2001V       |

| Latch-up Current                                       | > 200 mA      |

#### **Operating Range**

| Range                   | Ambient Temperature | V <sub>cc</sub> |

|-------------------------|---------------------|-----------------|

| Commercial              | 0°C to +70°C        | 5V ± 10%        |

| Industrial              | -40°C to +85-C      | 5V ± 10%        |

| Military <sup>[4]</sup> | –55°C to +125°C     | 5V ± 10%        |

#### Electrical Characteristics Over the Operating Range<sup>[5]</sup>

|                  |                                             |                                                                                                                                  |       |            |      | 7C136 | 5-25,30<br>42-30 | 7C130 | 2-35,45<br>6-35,45<br>2-35,45<br>6-35,45 | 7C1  | 32-55<br>36-55<br>42-55<br>46-55 |      |

|------------------|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-------|------------|------|-------|------------------|-------|------------------------------------------|------|----------------------------------|------|

| Parameter        | Description                                 | Test Conditions                                                                                                                  |       | Min.       | Max. | Min.  | Max.             | Min.  | Max.                                     | Min. | Max.                             | Unit |

| V <sub>OH</sub>  | Output HIGH voltage                         | $V_{CC}$ = Min., $I_{OH}$ = -4.0 mA                                                                                              |       | 2.4        |      | 2.4   |                  | 2.4   |                                          | 2.4  |                                  | V    |

| V <sub>OL</sub>  | Output LOW voltage                          | I <sub>OL</sub> = 4.0 mA                                                                                                         |       |            | 0.4  |       | 0.4              |       | 0.4                                      |      | 0.4                              | V    |

|                  |                                             | I <sub>OL</sub> = 16.0 mA <sup>[6]</sup>                                                                                         |       |            | 0.5  |       | 0.5              |       | 0.5                                      |      | 0.5                              |      |

| V <sub>IH</sub>  | Input HIGH voltage                          |                                                                                                                                  |       | 2.2        |      | 2.2   |                  | 2.2   |                                          | 2.2  |                                  | V    |

| $V_{IL}$         | Input LOW voltage                           |                                                                                                                                  |       |            | 8.0  |       | 8.0              |       | 0.8                                      |      | 8.0                              | V    |

| I <sub>IX</sub>  | Input load current                          | $GND \leq V_I \leq V_CC$                                                                                                         |       | -5         | +5   | -5    | +5               | -5    | +5                                       | -5   | +5                               | μА   |

| I <sub>OZ</sub>  | Output leakage current                      | GND $\leq$ V <sub>O</sub> $\leq$ V <sub>CC</sub> , Output Dis                                                                    | abled | <b>–</b> 5 | +5   | -5    | +5               | -5    | +5                                       | -5   | +5                               | μА   |

| I <sub>OS</sub>  | Output short circuit current <sup>[7]</sup> | V <sub>CC</sub> = Max., V <sub>OUT</sub> = GND                                                                                   |       |            | -350 |       | -350             |       | -350                                     |      | -350                             | mA   |

| I <sub>CC</sub>  | V <sub>CC</sub> Operating                   | $\overline{CE} = V_{IL}$ , Outputs Open, f = $f_{MAX}^{[8]}$                                                                     | Com'l |            | 190  |       | 170              |       | 120                                      |      | 110                              | mA   |

|                  | Supply Current                              | †MAX <sup>[O]</sup>                                                                                                              | Mil   |            |      |       |                  |       | 170                                      |      | 120                              |      |

| I <sub>SB1</sub> | Standby current both                        | $\overline{CE}_L$ and $\overline{CE}_R \ge V_{IH}$ ,<br>$f = f_{MAX}^{[8]}$                                                      | Com'l |            | 75   |       | 65               |       | 45                                       |      | 35                               | mA   |

|                  | ports, TTL Inputs                           | $t = t_{MAX}^{O_j}$                                                                                                              | Mil   |            |      |       |                  |       | 65                                       |      | 45                               |      |

| I <sub>SB2</sub> | Standby Current                             | $\overline{CE}_L$ or $\overline{CE}_R \ge V_{IH}$ ,                                                                              | Com'l |            | 135  |       | 115              |       | 90                                       |      | 75                               | mA   |

|                  | One Port,<br>TTL Inputs                     | Active Port Outputs Open, f = f <sub>MAX</sub> <sup>[8]</sup>                                                                    | Mil   |            |      |       |                  |       | 115                                      |      | 90                               |      |

| I <sub>SB3</sub> | Standby Current                             | Both Ports CE <sub>L</sub> and                                                                                                   | Com'l |            | 15   |       | 15               |       | 15                                       |      | 15                               | mA   |

|                  | Both Ports,<br>CMOS Inputs                  | $CE_R \ge V_{CC} - 0.\overline{2}V$ ,<br>$V_{IN} \ge V_{CC} - 0.2V$ or<br>$V_{IN} \le 0.2V$ , $f = 0$                            | Mil   |            |      |       |                  |       | 15                                       |      | 15                               |      |

| I <sub>SB4</sub> | Standby Current                             | One Port $\overline{CE}_L$ or $\overline{CE}_R > V_{CC} -$                                                                       | Com'l |            | 125  |       | 105              |       | 85                                       |      | 70                               | mA   |

|                  | One Port,<br>CMOS Inputs                    | 0.2V, $V_{\text{IN}} > V_{\text{CC}}^{-} - 0.2V$ or $V_{\text{IN}} <$ 0.2V, Active Port Outputs Open, $f = f_{\text{MAX}}^{[8]}$ | Mil   |            |      |       |                  |       | 105                                      |      | 85                               |      |

## Capacitance<sup>[9]</sup>

| Parameter        | Description        | Test Conditions                   | Max. | Unit |

|------------------|--------------------|-----------------------------------|------|------|

| C <sub>IN</sub>  | Input Capacitance  | T <sub>A</sub> = 25°C, f = 1 MHz, | 15   | pF   |

| C <sub>OUT</sub> | Output Capacitance | $V_{CC} = 5.0V$                   | 10   | pF   |

Shaded areas contain preliminary information.

#### Notes:

- 4. T<sub>A</sub> is the "instant on" case temperature.

5. See the last page of this specification for Group A subgroup testing information.

6. BUSY and INT pins only.

- 7. Duration of the short circuit should not exceed 30 seconds.

- 8. At f = f<sub>MAX</sub>, address and data inputs are cycling at the maximum frequency of read cycle of 1/t<sub>rc</sub> and using AC Test Waveforms input levels of GND to 3V.

9. This parameter is guaranteed but not tested.

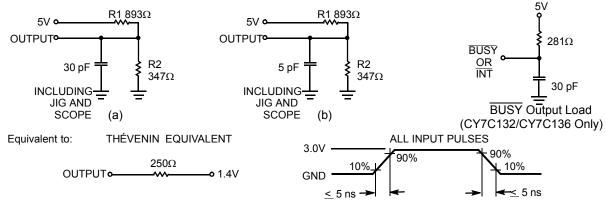

#### **AC Test Loads and Waveforms**

Switching Characteristics Over the Operating Range (Speeds -15, -25, -30) [5, 10]

|                            |                                          |      | 6-15 <sup>[3]</sup><br>46-15 | 7C1:<br>7C1 | 2-25 <sup>[3]</sup><br>36-25<br>42-25<br>46-25 | 7C132-30<br>7C136-30<br>7C142-30<br>7C146-30 |      |      |  |

|----------------------------|------------------------------------------|------|------------------------------|-------------|------------------------------------------------|----------------------------------------------|------|------|--|

| Parameter                  | Description                              | Min. | Max.                         | Min.        | Max.                                           | Min.                                         | Max. | Unit |  |

| Read Cycle                 |                                          |      |                              |             |                                                |                                              |      |      |  |

| t <sub>RC</sub>            | Read Cycle Time                          | 15   |                              | 25          |                                                | 30                                           |      | ns   |  |

| t <sub>AA</sub>            | Address to Data Valid <sup>[11]</sup>    |      | 15                           |             | 25                                             |                                              | 30   | ns   |  |

| t <sub>OHA</sub>           | Data Hold from Address Change            | 0    |                              | 0           |                                                | 0                                            |      | ns   |  |

| t <sub>ACE</sub>           | CE LOW to Data Valid <sup>[11]</sup>     |      | 15                           |             | 25                                             |                                              | 30   | ns   |  |

| t <sub>DOE</sub>           | OE LOW to Data Valid <sup>[11]</sup>     |      | 10                           |             | 15                                             |                                              | 20   | ns   |  |

| t <sub>LZOE</sub>          | OE LOW to Low Z <sup>[9, 12]</sup>       | 3    |                              | 3           |                                                | 3                                            |      | ns   |  |

| t <sub>HZOE</sub>          | OE HIGH to High Z <sup>[9, 12, 13]</sup> |      | 10                           |             | 15                                             |                                              | 15   | ns   |  |

| t <sub>LZCE</sub>          | CE LOW to Low Z <sup>[9, 12]</sup>       | 3    |                              | 5           |                                                | 5                                            |      | ns   |  |

| t <sub>HZCE</sub>          | CE HIGH to High Z <sup>[9, 12, 13]</sup> |      | 10                           |             | 15                                             |                                              | 15   | ns   |  |

| t <sub>PU</sub>            | CE LOW to Power-Up <sup>[9]</sup>        | 0    |                              | 0           |                                                | 0                                            |      | ns   |  |

| t <sub>PD</sub>            | CE HIGH to Power-Down <sup>[9]</sup>     |      | 15                           |             | 25                                             |                                              | 25   | ns   |  |

| Write Cycle <sup>[14</sup> | 4]                                       | •    | •                            | •           | •                                              | •                                            | •    |      |  |

| t <sub>WC</sub>            | Write Cycle Time                         | 15   |                              | 25          |                                                | 30                                           |      | ns   |  |

| t <sub>SCE</sub>           | CE LOW to Write End                      | 12   |                              | 20          |                                                | 25                                           |      | ns   |  |

| t <sub>AW</sub>            | Address Set-up to Write End              | 12   |                              | 20          |                                                | 25                                           |      | ns   |  |

| t <sub>HA</sub>            | Address Hold from Write End              | 2    |                              | 2           |                                                | 2                                            |      | ns   |  |

| t <sub>SA</sub>            | Address Set-up to Write Start            | 0    |                              | 0           |                                                | 0                                            |      | ns   |  |

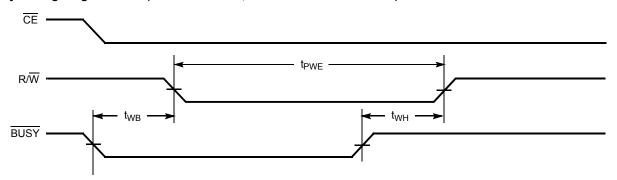

| t <sub>PWE</sub>           | R/W Pulse Width                          | 12   |                              | 15          |                                                | 25                                           |      | ns   |  |

| t <sub>SD</sub>            | Data Set-up to Write End                 | 10   |                              | 15          |                                                | 15                                           |      | ns   |  |

| t <sub>HD</sub>            | Data Hold from Write End                 | 0    |                              | 0           |                                                | 0                                            |      | ns   |  |

| t <sub>HZWE</sub>          | R/W LOW to High Z [9]                    |      | 10                           |             | 15                                             |                                              | 15   | ns   |  |

| t <sub>LZWE</sub>          | R/W HIGH to Low Z [9]                    | 0    |                              | 0           |                                                | 0                                            |      | ns   |  |

Shaded areas contain preliminary information.

<sup>10.</sup> Test conditions assume signal transition times of 5 ns or less, timing reference levels of 1.5V, input pulse levels of 0 to 3.0V and output loading of the specified  $l_{OL}/l_{OH}$ , and 30-pF load capacitance.

11. AC test conditions use  $V_{OH} = 1.6V$  and  $V_{OL} = 1.4V$ .

12. At any given temperature and voltage condition for any given device,  $t_{HZCE}$  is less than  $t_{LZCE}$  and  $t_{HZOE}$  is less than  $t_{LZOE}$ .

13.  $t_{LZCE}$ ,  $t_{LZWE}$ ,  $t_{HZOE}$ ,  $t_{HZOE}$ ,  $t_{HZCE}$ , and  $t_{HZWE}$  are tested with  $C_L = 5\underline{DF}$  as in (b) of AC Test Loads. Transition is measured ±500 mV from steady-state voltage.

14. The internal write time of the memory is defined by the overlap of CE LOW and R/W LOW. Both signals must be LOW to initiate a write and either signal can terminate a write by going HIGH. The data input setup and hold timing should be referenced to the rising edge of the signal that terminates the write.

# Switching Characteristics Over the Operating Range (Speeds -15, -25, -30) (continued)<sup>[5, 10]</sup>

|                   |                                                 | 7C13<br>7C1 | 6-15 <sup>[3]</sup><br>46-15 | 7C1<br>7C1 | 2-25 <sup>[3]</sup><br>36-25<br>42-25<br>46-25 | 7C1:<br>7C1 | 32-30<br>36-30<br>42-30<br>46-30 |      |

|-------------------|-------------------------------------------------|-------------|------------------------------|------------|------------------------------------------------|-------------|----------------------------------|------|

| Parameter         | Description                                     | Min.        | Max.                         | Min.       | Max.                                           | Min.        | Max.                             | Unit |

| Busy/Interrup     | ot Timing                                       | •           | •                            |            | •                                              |             |                                  |      |

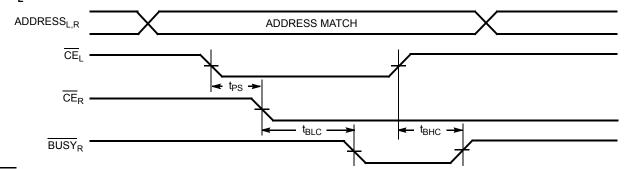

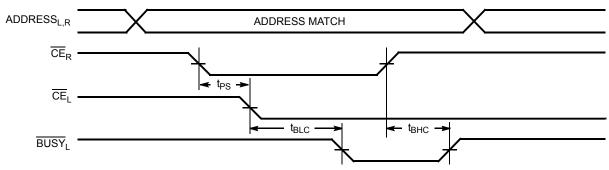

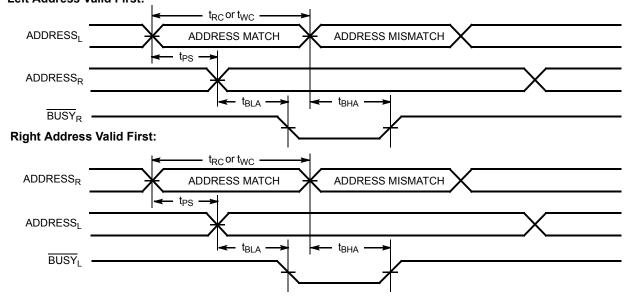

| t <sub>BLA</sub>  | BUSY LOW from Address Match                     |             | 15                           |            | 20                                             |             | 20                               | ns   |

| t <sub>BHA</sub>  | BUSY HIGH from Address Mismatch <sup>[15]</sup> |             | 15                           |            | 20                                             |             | 20                               | ns   |

| t <sub>BLC</sub>  | BUSY LOW from CE LOW                            |             | 15                           |            | 20                                             |             | 20                               | ns   |

| t <sub>BHC</sub>  | BUSY HIGH from CE HIGH <sup>[15]</sup>          |             | 15                           |            | 20                                             |             | 20                               | ns   |

| t <sub>PS</sub>   | Port Set Up for Priority                        | 5           |                              | 5          |                                                | 5           |                                  | ns   |

| t <sub>WB</sub>   | R/W LOW after BUSY LOW <sup>[16]</sup>          | 0           |                              | 0          |                                                | 0           |                                  | ns   |

| t <sub>WH</sub>   | R/W HIGH after BUSY HIGH                        | 13          |                              | 20         |                                                | 30          |                                  | ns   |

| t <sub>BDD</sub>  | BUSY HIGH to Valid Data                         |             | 15                           |            | 25                                             |             | 30                               | ns   |

| t <sub>DDD</sub>  | Write Data Valid to Read Data Valid             |             | Note 17                      |            | Note 17                                        |             | Note 17                          | ns   |

| t <sub>WDD</sub>  | Write Pulse to Data Delay                       |             | Note 17                      |            | Note 17                                        |             | Note 17                          | ns   |

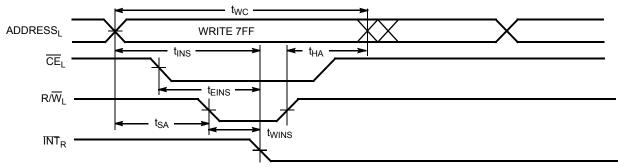

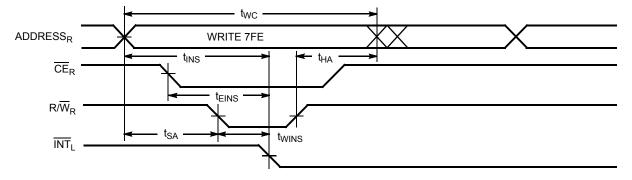

| Interrupt Tim     | ing <sup>[18]</sup>                             | •           | •                            |            | •                                              |             |                                  |      |

| t <sub>WINS</sub> | R/W to INTERRUPT Set Time                       |             | 15                           |            | 25                                             |             | 25                               | ns   |

| t <sub>EINS</sub> | CE to INTERRUPT Set Time                        |             | 15                           |            | 25                                             |             | 25                               | ns   |

| t <sub>INS</sub>  | Address to INTERRUPT Set Time                   |             | 15                           |            | 25                                             |             | 25                               | ns   |

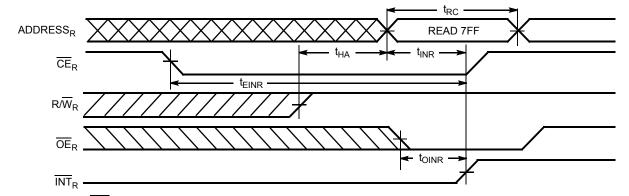

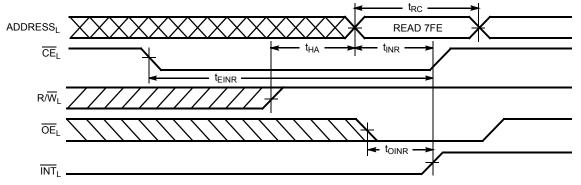

| t <sub>OINR</sub> | OE to INTERRUPT Reset Time <sup>[15]</sup>      |             | 15                           |            | 25                                             |             | 25                               | ns   |

| t <sub>EINR</sub> | CE to INTERRUPT Reset Time <sup>[15]</sup>      |             | 15                           |            | 25                                             |             | 25                               | ns   |

| t <sub>INR</sub>  | Address to INTERRUPT Reset Time <sup>[15]</sup> |             | 15                           |            | 25                                             |             | 25                               | ns   |

## Switching Characteristics Over the Operating Range (Speeds -35, -45, -55) [5, 10]

|                   |                                          | 7C1: | 32-35<br>36-35<br>42-35<br>46-35 | 7C1:<br>7C1 | 32-45<br>36-45<br>42-45<br>46-45 | 7C1:<br>7C1 | 32-55<br>36-55<br>42-55<br>46-55 |      |

|-------------------|------------------------------------------|------|----------------------------------|-------------|----------------------------------|-------------|----------------------------------|------|

| Parameter         | Description                              | Min. | Max.                             | Min.        | Max.                             | Min.        | Max.                             | Unit |

| Read Cycle        |                                          |      | •                                | •           | •                                | •           | •                                | •    |

| t <sub>RC</sub>   | Read Cycle Time                          | 35   |                                  | 45          |                                  | 55          |                                  | ns   |

| t <sub>AA</sub>   | Address to Data Valid <sup>[11]</sup>    |      | 35                               |             | 45                               |             | 55                               | ns   |

| t <sub>OHA</sub>  | Data Hold from Address Change            | 0    |                                  | 0           |                                  | 0           |                                  | ns   |

| t <sub>ACE</sub>  | CE LOW to Data Valid <sup>[11]</sup>     |      | 35                               |             | 45                               |             | 55                               | ns   |

| t <sub>DOE</sub>  | OE LOW to Data Valid <sup>[11]</sup>     |      | 20                               |             | 25                               |             | 25                               | ns   |

| t <sub>LZOE</sub> | OE LOW to Low Z <sup>[9, 12]</sup>       | 3    |                                  | 3           |                                  | 3           |                                  | ns   |

| t <sub>HZOE</sub> | OE HIGH to High Z <sup>[9, 12, 13]</sup> |      | 20                               |             | 20                               |             | 25                               | ns   |

| t <sub>LZCE</sub> | CE LOW to Low Z <sup>[9, 12]</sup>       | 5    |                                  | 5           |                                  | 5           |                                  | ns   |

| t <sub>HZCE</sub> | CE HIGH to High Z <sup>[9, 12, 13]</sup> |      | 20                               |             | 20                               |             | 25                               | ns   |

| t <sub>PU</sub>   | CE LOW to Power-Up <sup>[9]</sup>        | 0    |                                  | 0           |                                  | 0           |                                  | ns   |

| t <sub>PD</sub>   | CE HIGH to Power-Down <sup>[9]</sup>     |      | 35                               |             | 35                               |             | 35                               | ns   |

<sup>15.</sup> These parameters are measured from the input signal changing, until the output pin goes to a high-impedance state.

16. CY7C142/CY7C146 only.

17. A write operation on Port A, where Port A has priority, leaves the data on Port B's outputs undisturbed until one access time after one of the following: BUSY on Port B goes HIGH. Port B's address toggled.

CE for Port B is toggled.

R/W for Port B is toggled during valid read.

<sup>18. 52-</sup>pin PLCC and PQFP versions only.

# Switching Characteristics Over the Operating Range (Speeds -35, -45, -55) (continued)<sup>[5, 10]</sup>

|                           |                                                 | 7C1<br>7C1 | 32-35<br>36-35<br>42-35<br>46-35 | 7C1:<br>7C1 | 32-45<br>36-45<br>42-45<br>46-45 | 7C1:<br>7C1: | 32-55<br>36-55<br>42-55<br>46-55 |      |

|---------------------------|-------------------------------------------------|------------|----------------------------------|-------------|----------------------------------|--------------|----------------------------------|------|

| Parameter                 | Parameter Description                           |            | Max.                             | Min.        | Max.                             | Min.         | Max.                             | Unit |

| Write Cycle <sup>[1</sup> | 4]                                              | •          |                                  |             |                                  |              |                                  |      |

| t <sub>WC</sub>           | Write Cycle Time                                | 35         |                                  | 45          |                                  | 55           |                                  | ns   |

| t <sub>SCE</sub>          | CE LOW to Write End                             | 30         |                                  | 35          |                                  | 40           |                                  | ns   |

| t <sub>AW</sub>           | Address Set-up to Write End                     | 30         |                                  | 35          |                                  | 40           |                                  | ns   |

| t <sub>HA</sub>           | Address Hold from Write End                     | 2          |                                  | 2           |                                  | 2            |                                  | ns   |

| t <sub>SA</sub>           | Address Set-up to Write Start                   | 0          |                                  | 0           |                                  | 0            |                                  | ns   |

| t <sub>PWE</sub>          | R/W Pulse Width                                 | 25         |                                  | 30          |                                  | 30           |                                  | ns   |

| t <sub>SD</sub>           | Data Set-up to Write End                        | 15         |                                  | 20          |                                  | 20           |                                  | ns   |

| t <sub>HD</sub>           | Data Hold from Write End                        | 0          |                                  | 0           |                                  | 0            |                                  | ns   |

| t <sub>HZWE</sub>         | R/W LOW to High Z [9]                           |            | 20                               |             | 20                               |              | 25                               | ns   |

| t <sub>LZWE</sub>         | R/W HIGH to Low Z [9]                           | 0          |                                  | 0           |                                  | 0            |                                  | ns   |

| Busy/Interru              | pt Timing                                       |            | •                                |             |                                  |              | •                                |      |

| t <sub>BLA</sub>          | BUSY LOW from Address Match                     |            | 20                               |             | 25                               |              | 30                               | ns   |

| t <sub>BHA</sub>          | BUSY HIGH from Address Mismatch <sup>[15]</sup> |            | 20                               |             | 25                               |              | 30                               | ns   |

| t <sub>BLC</sub>          | BUSY LOW from CE LOW                            |            | 20                               |             | 25                               |              | 30                               | ns   |

| t <sub>BHC</sub>          | BUSY HIGH from CE HIGH <sup>[15]</sup>          |            | 20                               |             | 25                               |              | 30                               | ns   |

| t <sub>PS</sub>           | Port Set Up for Priority                        | 5          |                                  | 5           |                                  | 5            |                                  | ns   |

| t <sub>WB</sub>           | R/W LOW after BUSY LOW <sup>[16]</sup>          | 0          |                                  | 0           |                                  | 0            |                                  | ns   |

| t <sub>WH</sub>           | R/W HIGH after BUSY HIGH                        | 30         |                                  | 35          |                                  | 35           |                                  | ns   |

| t <sub>BDD</sub>          | BUSY HIGH to Valid Data                         |            | 35                               |             | 45                               |              | 45                               | ns   |

| t <sub>DDD</sub>          | Write Data Valid to Read Data Valid             |            | Note 17                          |             | Note 17                          |              | Note 17                          | ns   |

| t <sub>WDD</sub>          | Write Pulse to Data Delay                       |            | Note 17                          |             | Note 17                          |              | Note 17                          | ns   |

| Interrupt Tim             | ning <sup>[18]</sup>                            |            |                                  |             |                                  |              |                                  |      |

| t <sub>WINS</sub>         | R/W to INTERRUPT Set Time                       |            | 25                               |             | 35                               |              | 45                               | ns   |

| t <sub>EINS</sub>         | CE to INTERRUPT Set Time                        |            | 25                               |             | 35                               |              | 45                               | ns   |

| t <sub>INS</sub>          | Address to INTERRUPT Set Time                   |            | 25                               |             | 35                               |              | 45                               | ns   |

| t <sub>OINR</sub>         | OE to INTERRUPT Reset Time <sup>[15]</sup>      |            | 25                               |             | 35                               |              | 45                               | ns   |

| t <sub>EINR</sub>         | CE to INTERRUPT Reset Time <sup>[15]</sup>      |            | 25                               |             | 35                               |              | 45                               | ns   |

| t <sub>INR</sub>          | Address to INTERRUPT Reset Time <sup>[15]</sup> |            | 25                               |             | 35                               |              | 45                               | ns   |

## **Switching Waveforms**

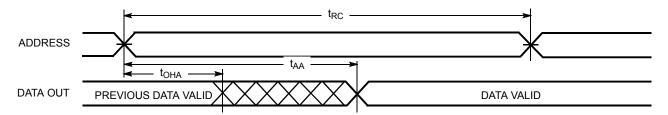

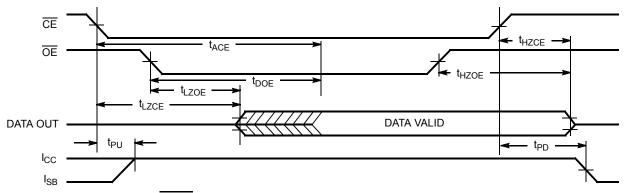

Read Cycle No. 1 (Either Port-Address Access)<sup>[19, 20]</sup>

## Read Cycle No. 2 (Either Port- $\overline{\text{CE}}/\overline{\text{OE}})^{[19,\ 21]}$

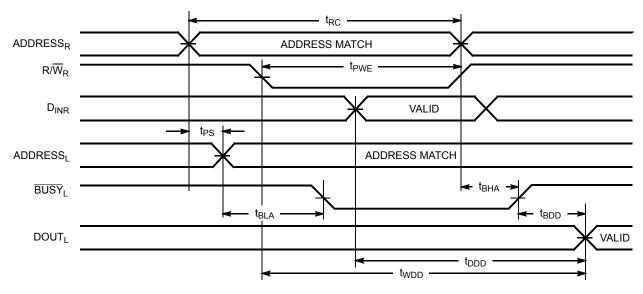

## Read Cycle No. 3 (Read with BUSY Master: CY7C132 and CY7C136)

**Notes:** 19. R/W is HIGH for read cycle.

20. Device is continuously selected,  $\overline{\text{CE}} = \text{V}_{\text{IL}}$  and  $\overline{\text{OE}} = \text{V}_{\text{IL}}$ . 21. Address valid prior to or coincident with  $\overline{\text{CE}}$  transition LOW.

[+] Feedback

# Switching Waveforms (continued)

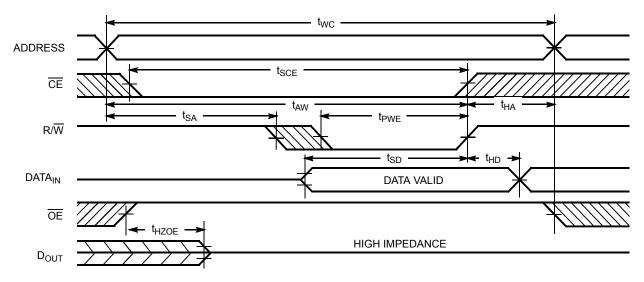

## Write Cycle No.1 (OE Three-States Data I/Os—Either Port)[14, 22]

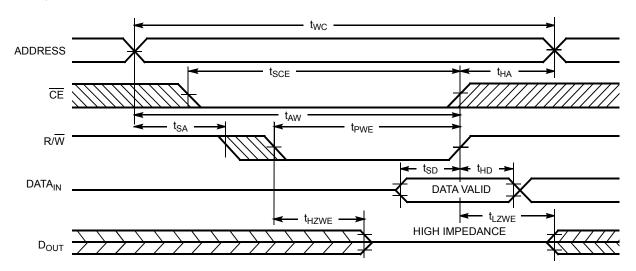

## Write Cycle No. 2 (R/W Three-States Data I/Os—Either Port)[14, 23]

#### Notes:

22. If  $\overline{\text{CE}}$  is LOW during a R/ $\overline{\text{W}}$  controlled write cycle, the write pulse width must be the larger of  $t_{\text{PWE}}$  or  $t_{\text{HZWE}} + t_{\text{SD}}$  to allow the data I/O pins to enter high impedance and fo<u>r</u> data to be placed on the bus for the required  $t_{\text{SD}}$ .

23. If the  $\overline{\text{CE}}$  LOW transition occurs simultaneously with or after the R/ $\overline{\text{W}}$  LOW transition, the outputs remain in a high-impedance state.

# Switching Waveforms (continued)

## Busy Timing Diagram No. 1 (CE Arbitration)

## CE<sub>L</sub> Valid First:

## **CE**<sub>R</sub> Valid First:

#### **Busy Timing Diagram No. 2 (Address Arbitration)**

### Left Address Valid First:

## Switching Waveforms (continued)

Busy Timing Diagram No. 3 (Write with BUSY, Slave: CY7C142/CY7C146)

# Interrupt Timing Diagrams<sup>[18]</sup>

## Left Side Sets $\overline{\text{INT}}_{\text{R}}$ :

## Right Side Clears INT<sub>R</sub>:

## Right Side Sets $\overline{INT}_L$ :

## Interrupt Timing Diagrams<sup>[18]</sup> (continued)

Right Side Clears INT<sub>L</sub>:

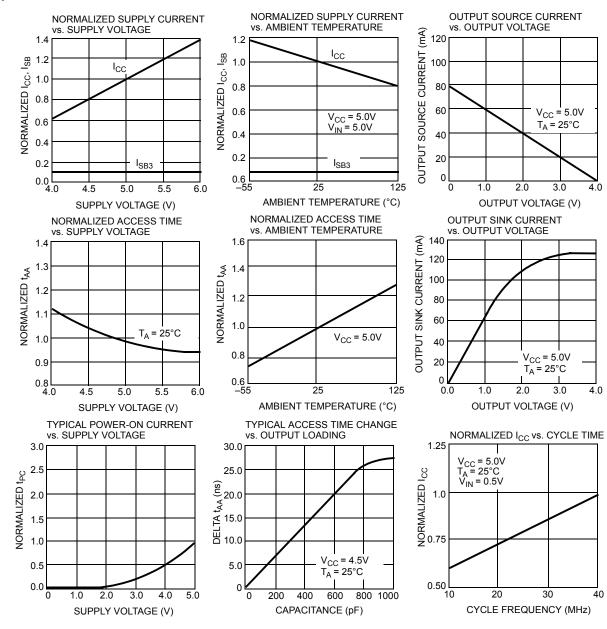

#### Typical DC and AC Characteristics

Document #: 38-06031 Rev. \*C

# **Ordering Information**

| Speed<br>(ns) | Ordering Code | Package<br>Name | Package Type                                | Operating<br>Range |

|---------------|---------------|-----------------|---------------------------------------------|--------------------|

| 30            | CY7C132-30PC  | P25             | 48-Lead (600-Mil) Molded DIP                | Commercial         |

|               | CY7C132-30PI  | P25             | 48-Lead (600-Mil) Molded DIP                | Industrial         |

| 35            | CY7C132-35PC  | P25             | 48-Lead (600-Mil) Molded DIP                | Commercial         |

|               | CY7C132-35PI  | P25             | 48-Lead (600-Mil) Molded DIP                | Industrial         |

|               | CY7C132-35DMB | D26             | 48-Lead (600-Mil) Sidebraze DIP             | Military           |

| 45            | CY7C132-45PC  | P25             | 48-Lead (600-Mil) Molded DIP                | Commercial         |

|               | CY7C132-45PI  | P25             | 48-Lead (600-Mil) Molded DIP                | Industrial         |

|               | CY7C132-45DMB | D26             | 48-Lead (600-Mil) Sidebraze DIP             | Military           |

| 55            | CY7C132-55PC  | P25             | 48-Lead (600-Mil) Molded DIP                | Commercial         |

|               | CY7C132-55PI  | P25             | 48-Lead (600-Mil) Molded DIP                | Industrial         |

|               | CY7C132-55DMB | D26             | 48-Lead (600-Mil) Sidebraze DIP             | Military           |

| 15            | CY7C136-15JC  | J69             | 52-Lead Plastic Leaded Chip Carrier         | Commercial         |

|               | CY7C136-15NC  | N52             | 52-Pin Plastic Quad Flatpack                |                    |

| 25            | CY7C136-25JC  | J69             | 52-Lead Plastic Leaded Chip Carrier         | Commercial         |

|               | CY7C136-25JXC | J69             | 52-Lead Pb-Free Plastic Leaded Chip Carrier |                    |

|               | CY7C136-25NC  | N52             | 52-Pin Plastic Quad Flatpack                |                    |

|               | CY7C136-25NXC | N52             | 52-Pin Pb-Free Plastic Quad Flatpack        |                    |

| 30            | CY7C136-30JC  | J69             | 52-Lead Plastic Leaded Chip Carrier         | Commercial         |

|               | CY7C136-30NC  | N52             | 52-Pin Plastic Quad Flatpack                |                    |

|               | CY7C136-30JI  | J69             | 52-Lead Plastic Leaded Chip Carrier         | Industrial         |

| 35            | CY7C136-35JC  | J69             | 52-Lead Plastic Leaded Chip Carrier         | Commercial         |

|               | CY7C136-35NC  | N52             | 52-Pin Plastic Quad Flatpack                |                    |

|               | CY7C136-35JI  | J69             | 52-Lead Plastic Leaded Chip Carrier         | Industrial         |

|               | CY7C136-35LMB | L69             | 52-Square Leadless Chip Carrier             | Military           |

| 45            | CY7C136-45JC  | J69             | 52-Lead Plastic Leaded Chip Carrier         | Commercial         |

|               | CY7C136-45NC  | N52             | 52-Pin Plastic Quad Flatpack                |                    |

|               | CY7C136-45JI  | J69             | 52-Lead Plastic Leaded Chip Carrier         | Industrial         |

|               | CY7C136-45LMB | L69             | 52-Square Leadless Chip Carrier             | Military           |

| 55            | CY7C136-55JC  | J69             | 52-Lead Plastic Leaded Chip Carrier         | Commercial         |

|               | CY7C136-55JXC | J69             | 52-Lead Pb-Free Plastic Leaded Chip Carrier |                    |

|               | CY7C136-55NC  | N52             | 52-Pin Plastic Quad Flatpack                |                    |

|               | CY7C136-55NXC | N52             | 52-Pin Pb-Free Plastic Quad Flatpack        |                    |

|               | CY7C136-55JI  | J69             | 52-Lead Plastic Leaded Chip Carrier         | Industrial         |

|               | CY7C136-55JXI | J69             | 52-Lead Pb-Free Plastic Leaded Chip Carrier |                    |

|               | CY7C136-55NI  | N52             | 52-Pin Plastic Quad Flatpack                |                    |

|               | CY7C136-55NXI | N52             | 52-Pin Pb-Free Plastic Quad Flatpack        |                    |

|               | CY7C136-55LMB | L69             | 52-Square Leadless Chip Carrier             | Military           |

| 30            | CY7C142-30PC  | P25             | 48-Lead (600-Mil) Molded DIP                | Commercial         |

|               | CY7C142-30PI  | P25             | 48-Lead (600-Mil) Molded DIP                | Industrial         |

| 35            | CY7C142-35PC  | P25             | 48-Lead (600-Mil) Molded DIP                | Commercial         |

|               | CY7C142-35PI  | P25             | 48-Lead (600-Mil) Molded DIP                | Industrial         |

|               | CY7C142-35DMB | D26             | 48-Lead (600-Mil) Sidebraze DIP             | Military           |

## Ordering Information (continued)

| Speed<br>(ns) | Ordering Code | Package<br>Name | Package Type                                | Operating<br>Range |

|---------------|---------------|-----------------|---------------------------------------------|--------------------|

| 45            | CY7C142-45PC  | P25             | 48-Lead (600-Mil) Molded DIP                | Commercial         |

|               | CY7C142-45PI  | P25             | 48-Lead (600-Mil) Molded DIP                | Industrial         |

|               | CY7C142-45DMB | D26             | 48-Lead (600-Mil) Sidebraze DIP             | Military           |

| 55            | CY7C142-55PC  | P25             | 48-Lead (600-Mil) Molded DIP                | Commercial         |

|               | CY7C142-55PI  | P25             | 48-Lead (600-Mil) Molded DIP                | Industrial         |

|               | CY7C142-55DMB | D26             | 48-Lead (600-Mil) Sidebraze DIP             | Military           |

| 15            | CY7C146-15JC  | J69             | 52-Lead Plastic Leaded Chip Carrier         | Commercial         |

|               | CY7C146-15NC  | N52             | 52-Pin Plastic Quad Flatpack                |                    |

| 25            | CY7C146-25JC  | J69             | 52-Lead Plastic Leaded Chip Carrier         | Commercial         |

|               | CY7C146-25JXC | J69             | 52-Lead Pb-Free Plastic Leaded Chip Carrier |                    |

|               | CY7C146-25NC  | N52             | 52-Pin Plastic Quad Flatpack                |                    |

| 30            | CY7C146-30JC  | J69             | 52-Lead Plastic Leaded Chip Carrier         | Commercial         |

|               | CY7C146-30NC  | N52             | 52-Pin Plastic Quad Flatpack                |                    |

|               | CY7C146-30JI  | J69             | 52-Lead Plastic Leaded Chip Carrier         | Industrial         |

| 35            | CY7C146-35JC  | J69             | 52-Lead Plastic Leaded Chip Carrier         | Commercial         |

|               | CY7C146-35NC  | N52             | 52-Pin Plastic Quad Flatpack                |                    |

|               | CY7C146-35JI  | J69             | 52-Lead Plastic Leaded Chip Carrier         | Industrial         |

|               | CY7C146-35LMB | L69             | 52-Square Leadless Chip Carrier             | Military           |

| 45            | CY7C146-45JC  | J69             | 52-Lead Plastic Leaded Chip Carrier         | Commercial         |

|               | CY7C146-45NC  | N52             | 52-Pin Plastic Quad Flatpack                |                    |

|               | CY7C146-45JI  | J69             | 52-Lead Plastic Leaded Chip Carrier         | Industrial         |

|               | CY7C146-45LMB | L69             | 52-Square Leadless Chip Carrier             | Military           |

| 55            | CY7C146-55JC  | J69             | 52-Lead Plastic Leaded Chip Carrier         | Commercial         |

|               | CY7C146-55JXC | J69             | 52-Lead Pb-Free Plastic Leaded Chip Carrier |                    |

|               | CY7C146-55NC  | N52             | 52-Pin Plastic Quad Flatpack                |                    |

|               | CY7C146-55JI  | J69             | 52-Lead Plastic Leaded Chip Carrier         | Industrial         |

|               | CY7C146-55LMB | L69             | 52-Square Leadless Chip Carrier             | Military           |

## **MILITARY SPECIFICATIONS**

#### **Group A Subgroup Testing—DC Characteristics**

| Parameter            | Subgroups |

|----------------------|-----------|

| V <sub>OH</sub>      | 1, 2, 3   |

| V <sub>OL</sub>      | 1, 2, 3   |

| V <sub>IH</sub>      | 1, 2, 3   |

| V <sub>IL</sub> Max. | 1, 2, 3   |

| I <sub>IX</sub>      | 1, 2, 3   |

| I <sub>OZ</sub>      | 1, 2, 3   |

| I <sub>CC</sub>      | 1, 2, 3   |

| I <sub>SB1</sub>     | 1, 2, 3   |

| I <sub>SB2</sub>     | 1, 2, 3   |

| I <sub>SB3</sub>     | 1, 2, 3   |

| I <sub>SB4</sub>     | 1, 2, 3   |

#### **Switching Characteristics**

| Parameter                       | Subgroups       |  |  |  |

|---------------------------------|-----------------|--|--|--|

| Read Cycle                      |                 |  |  |  |

| t <sub>RC</sub>                 | 7, 8, 9, 10, 11 |  |  |  |

| t <sub>AA</sub>                 | 7, 8, 9, 10, 11 |  |  |  |

| t <sub>ACE</sub>                | 7, 8, 9, 10, 11 |  |  |  |

| t <sub>DOE</sub>                | 7, 8, 9, 10, 11 |  |  |  |

| Write Cycle                     |                 |  |  |  |

| t <sub>WC</sub>                 | 7, 8, 9, 10, 11 |  |  |  |

| t <sub>SCE</sub>                | 7, 8, 9, 10, 11 |  |  |  |

| t <sub>AW</sub>                 | 7, 8, 9, 10, 11 |  |  |  |

| t <sub>HA</sub>                 | 7, 8, 9, 10, 11 |  |  |  |

| t <sub>SA</sub>                 | 7, 8, 9, 10, 11 |  |  |  |

| t <sub>PWE</sub>                | 7, 8, 9, 10, 11 |  |  |  |

| t <sub>SD</sub>                 | 7, 8, 9, 10, 11 |  |  |  |

| t <sub>HD</sub>                 | 7, 8, 9, 10, 11 |  |  |  |

| Busy/Interrupt Timing           |                 |  |  |  |

| t <sub>BLA</sub>                | 7, 8, 9, 10, 11 |  |  |  |

| t <sub>BHA</sub>                | 7, 8, 9, 10, 11 |  |  |  |

| t <sub>BLC</sub>                | 7, 8, 9, 10, 11 |  |  |  |

| t <sub>BHC</sub>                | 7, 8, 9, 10, 11 |  |  |  |

| t <sub>PS</sub>                 | 7, 8, 9, 10, 11 |  |  |  |

| t <sub>WINS</sub>               | 7, 8, 9, 10, 11 |  |  |  |

| t <sub>EINS</sub>               | 7, 8, 9, 10, 11 |  |  |  |

| t <sub>INS</sub>                | 7, 8, 9, 10, 11 |  |  |  |

| t <sub>OINR</sub>               | 7, 8, 9, 10, 11 |  |  |  |

| t <sub>EINR</sub>               | 7, 8, 9, 10, 11 |  |  |  |

| t <sub>INR</sub>                | 7, 8, 9, 10, 11 |  |  |  |

| BUSY TIMING                     |                 |  |  |  |

| t <sub>WB</sub> <sup>[24]</sup> | 7, 8, 9, 10, 11 |  |  |  |

| t <sub>WH</sub>                 | 7, 8, 9, 10, 11 |  |  |  |

| t <sub>BDD</sub>                | 7, 8, 9, 10, 11 |  |  |  |

Note: 24. CY7C142/CY7C146 only.

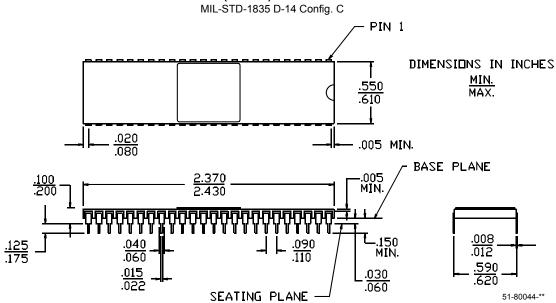

#### **Package Diagrams**

## 48-Lead (600-Mil) Sidebraze DIP D26

#### 52-Lead Plastic Leaded Chip Carrier J69 52-Lead Pb-Free Plastic Leaded Chip Carrier J69

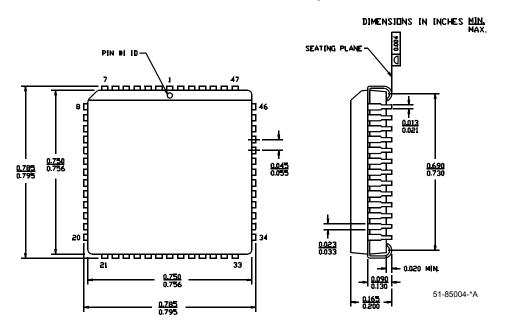

#### Package Diagrams (continued)

Document #: 38-06031 Rev. \*C

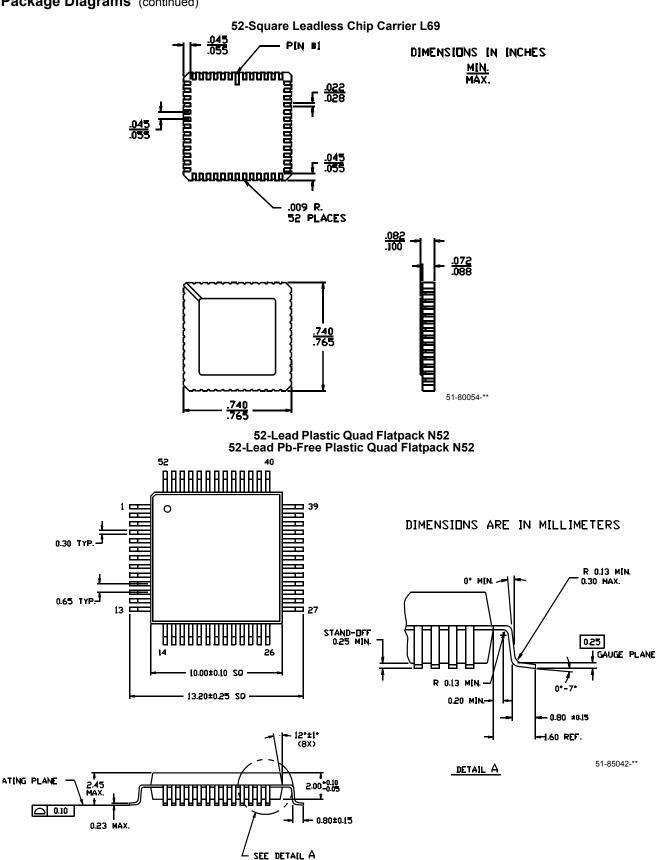

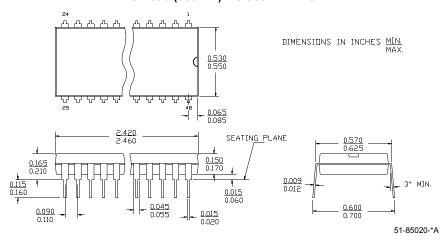

## Package Diagrams (continued)

#### 48-Lead (600-Mil) Molded DIP P25

All product and company names mentioned in this document are the trademarks of their respective holders.

# **Document History Page**

| Document Title: CY7C132/CY7C136/CY7C142/CY7C146 2K x 8 Dual Port Static RAM Document Number: 38-06031 |         |            |                    |                                                                                                                                                          |

|-------------------------------------------------------------------------------------------------------|---------|------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| REV.                                                                                                  | ECN NO. | Issue Date | Orig. of<br>Change | Description of Change                                                                                                                                    |

| **                                                                                                    | 110171  | 10/21/01   | SZV                | Change from Spec number: 38-06031                                                                                                                        |

| *A                                                                                                    | 128959  | 09/03/03   | JFU                | Added CY7C136-55NI to Order Information                                                                                                                  |

| *B                                                                                                    | 236748  | See ECN    | YDT                | Removed cross information from features section                                                                                                          |

| *C                                                                                                    | 393184  | See ECN    | YIM                | Added Pb-Free Logo Added Pb-Free parts to ordering information: CY7C136-25JXC, CY7C136-25NXC, CY7C136-55JXC, CY7C136-55JXC, CY7C136-55JXC, CY7C136-55JXC |