# **PRODUCT OVERVIEW**

### S3C24A0

### AN APPLICATION PROCESSOR FOR 2.5G/3G MOBILE PHONES

### SOC R&D CENTER SAMSUNG ELECTRONICS CORP.

1-1

S3C24A0 RISC MICROPROCESSOR

## CONTENTS

**CH1. INTRODUCTION** CH2. SROM CH3. SDRAM CH4. NAND CH5. BUS MATRIX **CH6. INTERRUPT** CH7. PWM TIMER **CH8. WATCH DOG TIMER** CH9. DMA **CH10. RTC** CH11. UART CH12. IRDA **CH13. IIC CH14. IIS** CH15. SPI CH16. AC97 CH17. USB HOST CH18. USB DEVICE CH19. MODEM CH20. GPIO CH21. CAMERA CH22. MPEG4-OVERVIEW **CH23. MOTION ESTIMATION** CH24. MOTION COMPENSATION CH25. DCTQ CH26. VLX CH27. POST CH28. LCD CH29. KEYPAD CH30. ADC & TOUCH CH31. SD/MMC **CH32. MEMORY STICK** CH33. CLOCK & POWER **CH34. MECHANICAL DATA**

Preliminary product information describes products that are in development,

# INTRODUCTION (PRELIMINARY)

#### **1.1 ARCHITECTURAL OVERVIEW**

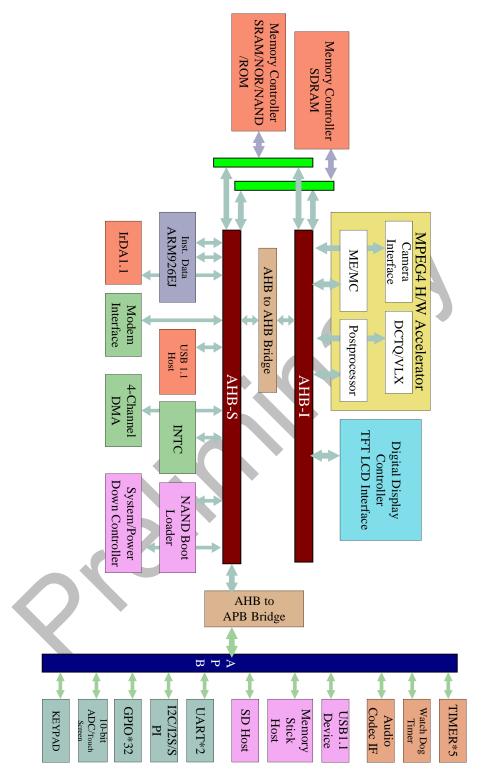

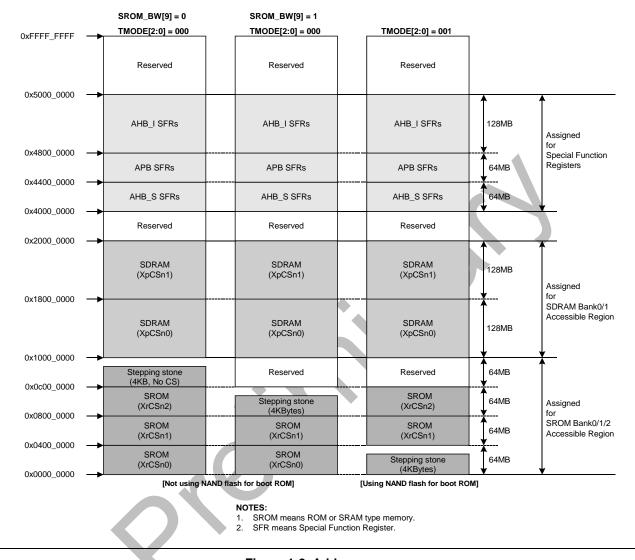

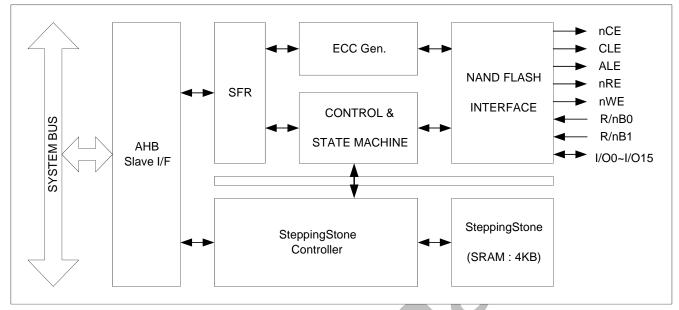

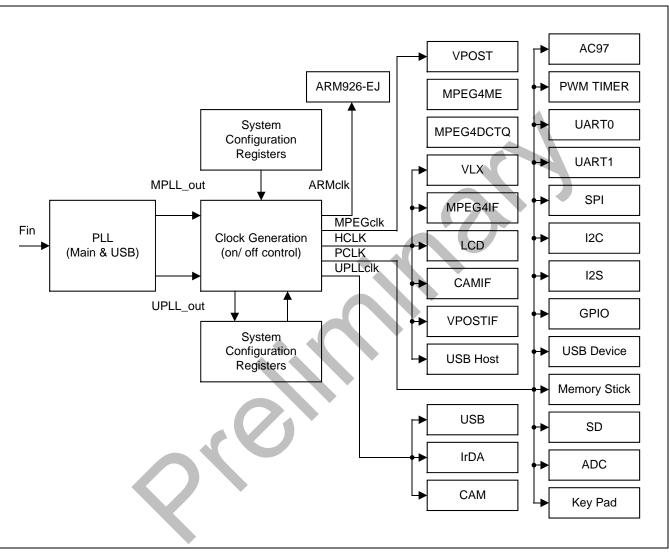

The S3C24A0 is a 16/32-bit RISC microprocessor, which is designed to provide a cost-effective, low power, and high performance micro-controller solution for mobile phones and general applications. To provide a sufficient H/W performance for the 2.5G & 3G communication services, the S3C24A0 adopts dual-32-bit bus architecture and includes many powerful hardware accelerators for the motion video processing, serial communications, and etc. For the real time video conferencing, an optimized MPEG4 H/W Encoder/Decoder is integrated. To reduce total system cost and enhance overall functionality, the S3C24A0 also includes following components: separate 16KB Instruction and 16KB Data Cache, MMU to handle virtual memory management, LCD controller (TFT), Camera Interface, MPEG-4 ME, MC, DCTQ, NAND Flash Boot loader, System Manager (power management & etc.), SDRAM controller, 2-ch UART, 4-ch DMA, 4-ch Timers, General I/O Ports, IIC-BUS interface, USB Host, SD Host & Multi-Media Card Interface, Memory Stick Interface, PLL for clock generation & etc. The S3C24A0 can be used as a most powerful Application Processor for mobiles phones. For this application, the S3C24A0 has a Modem Interface to communicate with various Modem Chips.

The S3C24A0 is developed using an ARM926EJ-S core, advanced 0.13um CMOS standard cells and memory compliers. Its low-power, simple, elegant and fully static-design scheme is particularly suitable for cost-sensitive and power-sensitive applications. Also, the S3C24A0 adopts a de-facto standard bus architecture – the AMBA (Advanced Microcontroller Bus Architecture).

One of outstanding features of the S3C24A0 is its CPU core, a 16/32-bit ARM926EJ-S RISC processor designed by ARM, Ltd. The ARM926EJ-S is a single chip MCU and Java enabled microprocessor. The ARM926EJ-S also implements the MMU, the AMBA BUS, and the Harvard cache architecture with separate 16KB instruction and 16KB data caches, each cache with an 8-word line length.

By providing a complete set of common system peripherals, the S3C24A0 minimizes overall system costs and eliminates the need to configure additional components.

#### **1.2 FEATURES**

This section summarizes the features of the S3C24A0. Figure 1-1 is an overall block diagram of the S3C24A0.

#### 1.2.1 Microprocessor and Overall Architecture

- SoC (System-on-Chip) for mobile phones and general embedded applications.

- 16/32-Bit RISC architecture and powerful instruction set with ARM926EJ-S CPU core. •

- ARM's Jazelle Java technology

- Enhanced ARM architecture MMU to support WinCE, Symbian and Linux

- Instruction cache, data cache, write buffer and Physical address TAG RAM to reduce the effect of main memory bandwidth and latency on performance

ELECTRONICS

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available.

Downloaded from Elcodis.com electronic components digriphion Specifications and information herein are subject to change without notice.

- 4 way set-associative cache with I-Cache (16KB) and D-Cache (16KB).

- 8-words per line with one valid bit and two dirty bits per line

- Pseudo random or round robin replacement algorithm.

- Write through or write back cache operation to update the main memory. •

- The write buffer can hold 16 words of data and four addresses. •

- ARM926EJ-S core supports the ARM debug architecture

- Internal AMBA (Advanced Microcontroller Bus Architecture) (AMBA2.0, AHB/APB)

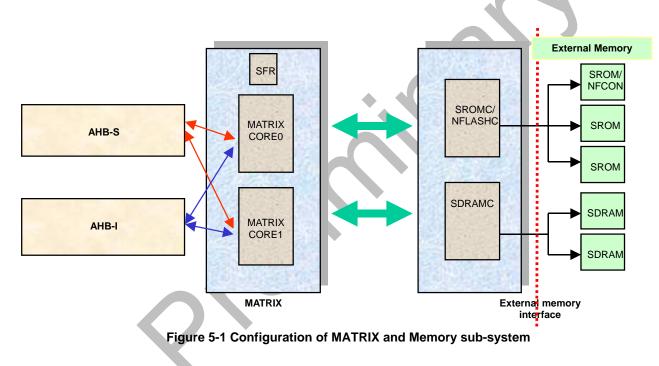

- Dual AHB bus for high-performance processing (AHB-I & AHB-S)

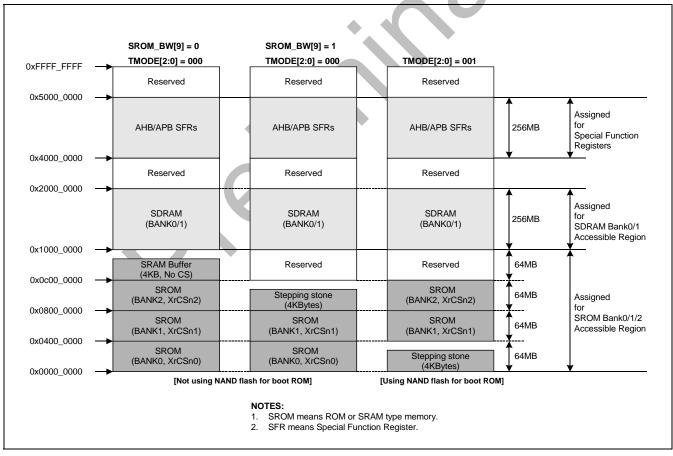

#### 1.2.2 Memory Subsystem

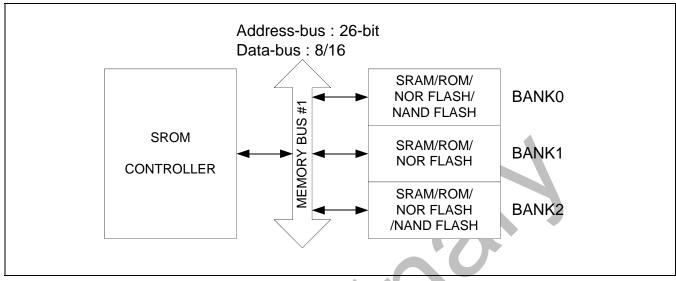

- High bandwidth Memory subsystem with two access channels (accesses from two AHB buses) and threechannel memory ports

- Double the bandwidth with the simultaneous access capability

- ROM/SRAM/NOR-Flash/NAND-Flash channel

- One SDRAM channels

- Up to 1GB Address space

- Low-power SDRAM interface support : Mobile SDRAM function

- DS : Driver Strength Control

- TCSR : Temperature Compensated Self-Refresh Control

- PASR : Partial Array Self-Refresh Control

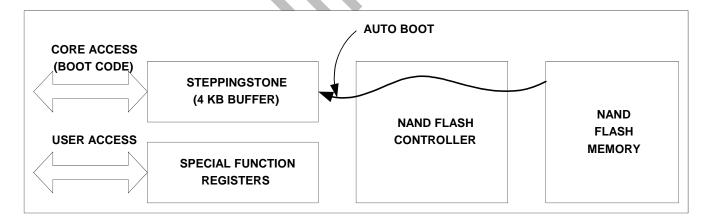

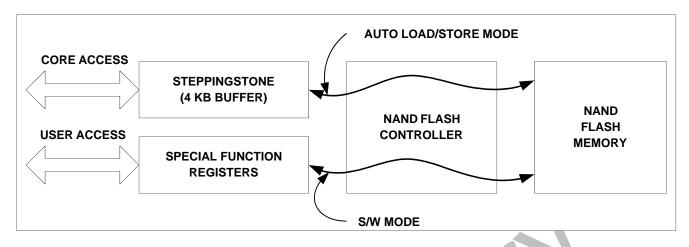

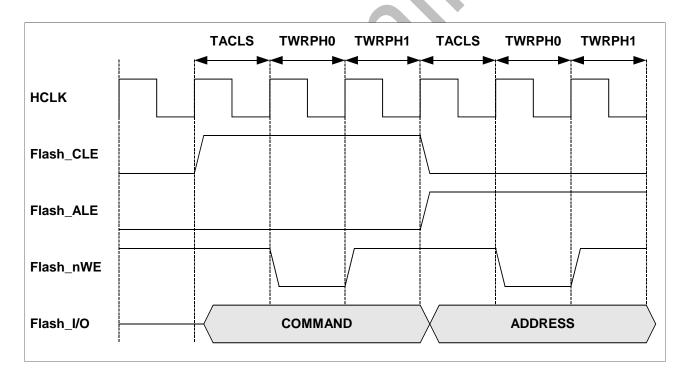

- NAND Flash Boot Loader with the ECC circuitry to support booting from NAND Flash

- 4KB Stepping Stone

- Support 1G, 2G bit NAND Flash

#### **1.2.3 General Peripherals**

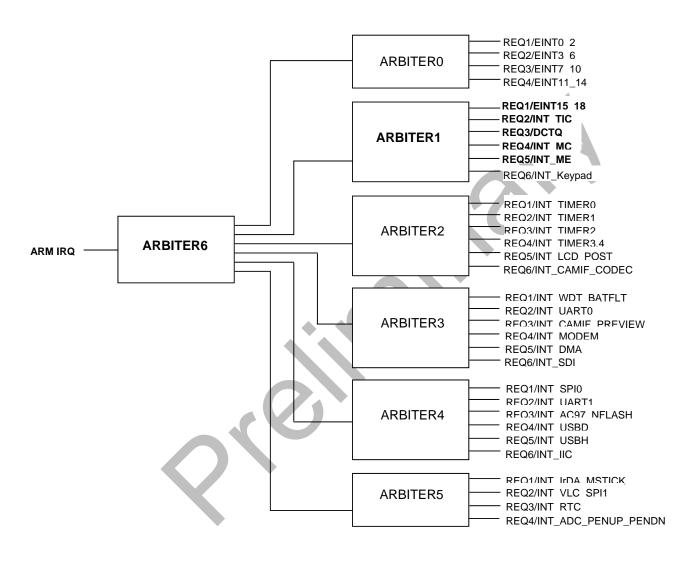

- Interrupt Controller

- 61 Interrupt sources (1 Watch Dog Timer, 5 Timer, 6 UART, 18 External Interrupts, 4 DMA, 2 RTC, 3 ADC, 1 I2C, 1 AC97, 1 NAND Flash, 1 IrDA, 1 Memory Stick, 2 SPI, 1 SDI, 2 USB (Host and Device), 1 Keypad, 1 Modem Interface, 2 Camera Interface, 4 MPEG, 2 LCD, 1 Battery Fault, 1 Post)

- Level/Edge mode on external interrupt source.

- Programmable polarity of edge and level.

- Supports FIQ (Fast Interrupt request) for very urgent interrupt request.

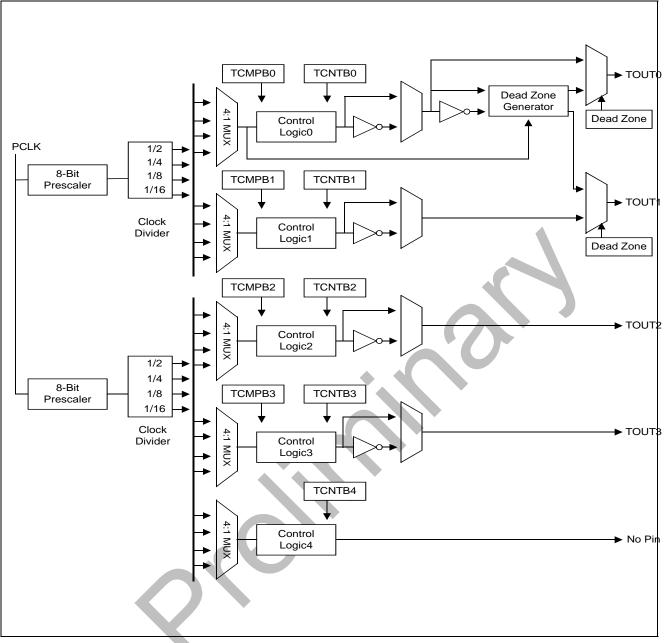

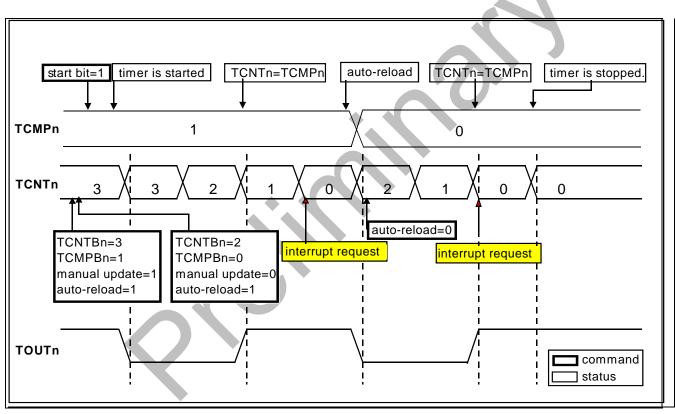

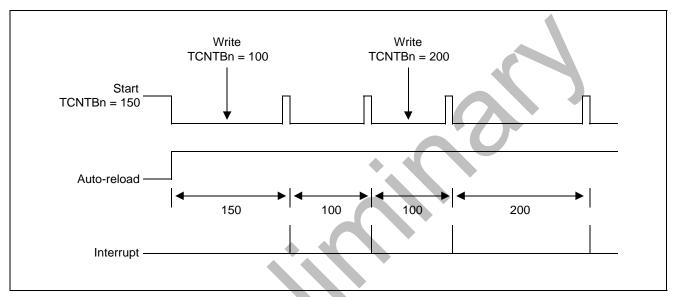

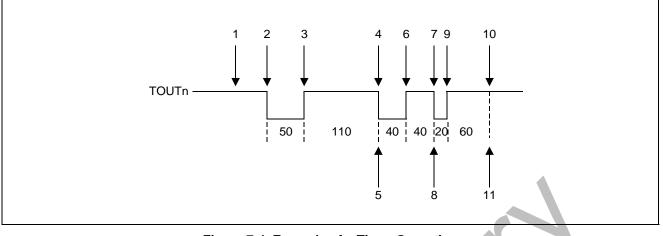

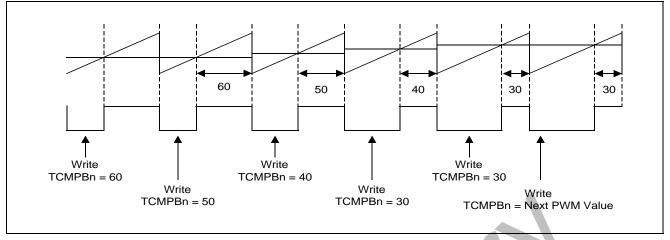

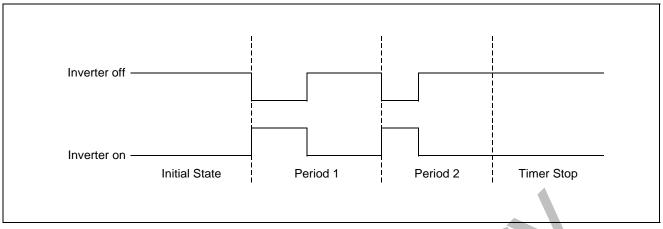

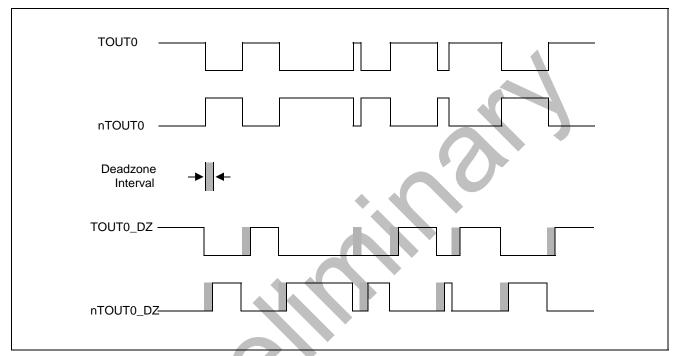

- Timer with PWM (Pulse Width Modulation)

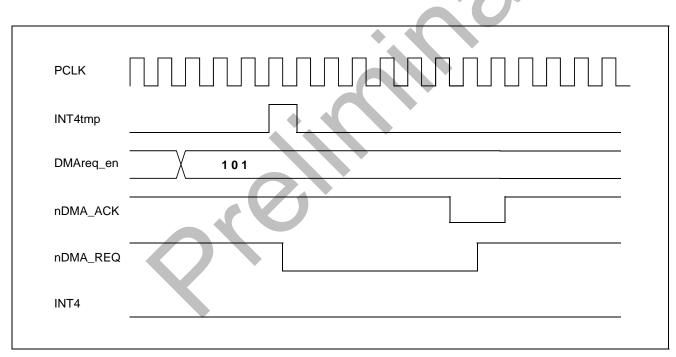

- 4-ch 16-bit Timer with PWM / 1-ch 16-bit internal timer with DMA-based or interrupt-based operation \_

- Programmable duty cycle, frequency, and polarity

- Dead-zone generation.

- Support external clock source.

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available.

Downloaded from Elcodis.com electronic components distributor. Specifications and information herein are subject to change without notice.

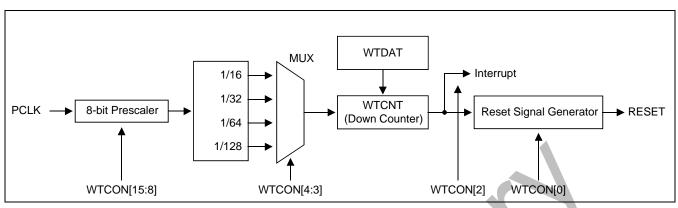

- 16-bit Watchdog Timer.

- Interrupt request or system reset at time-out.

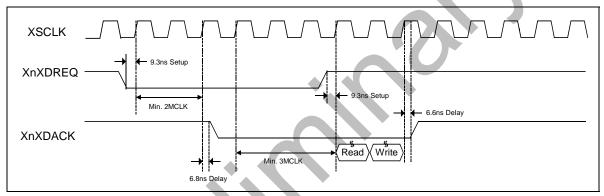

- 4-ch DMA controller.

- Support memory to memory, IO to memory, memory to IO, and IO to IO

- Burst transfer mode to enhance the transfer rate.

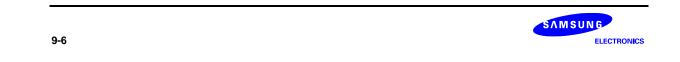

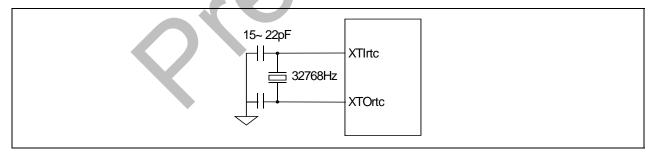

- RTC (Real Time Clock)

- Full clock feature: msec, sec, min, hour, day, date, week, month, year.

- 32.768 KHz operation

- Alarm interrupt

- Time-tick interrupt

#### **1.2.4 Serial Communication**

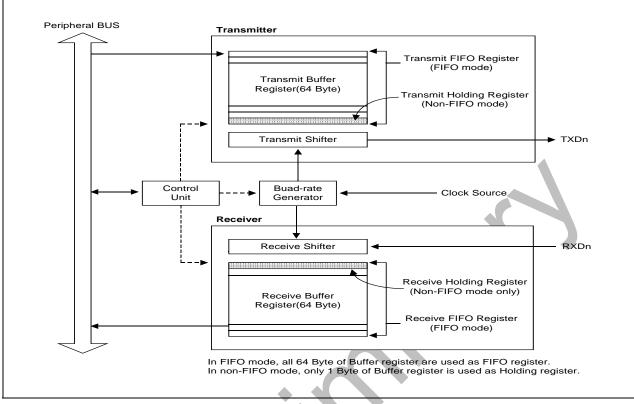

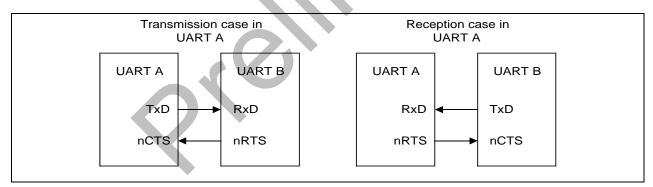

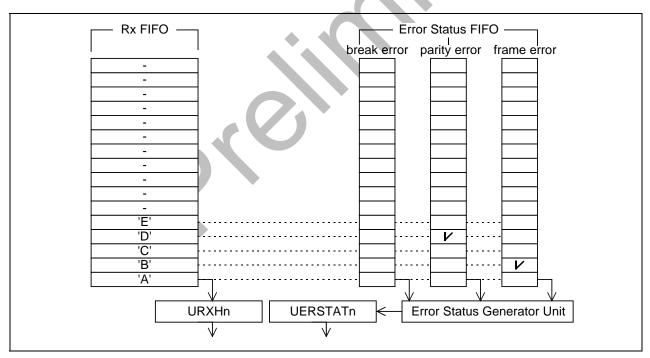

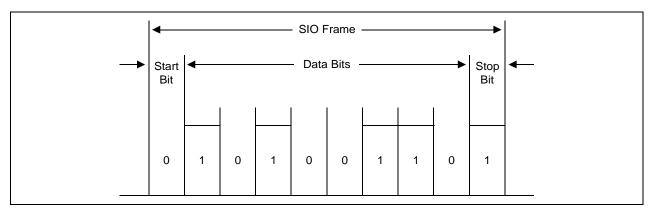

- UART

- 2-channel UART with DMA-based or interrupt-based operation

- Supports 5-bit, 6-bit, 7-bit, or 8-bit serial data transmit/receive

- Supports external clock for the UART operation (XuCLK)

- Programmable baud rate

- Supports IrDA 1.0

- Loop back mode for testing

- Each channel has internal 64-byte Tx FIFO and 64-byte Rx FIFO

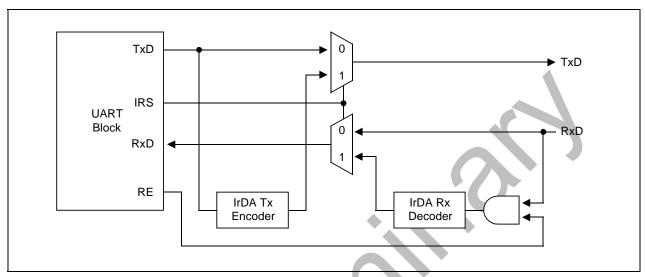

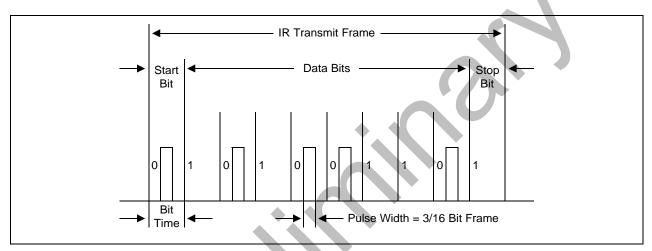

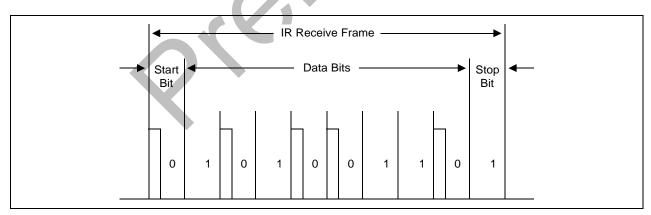

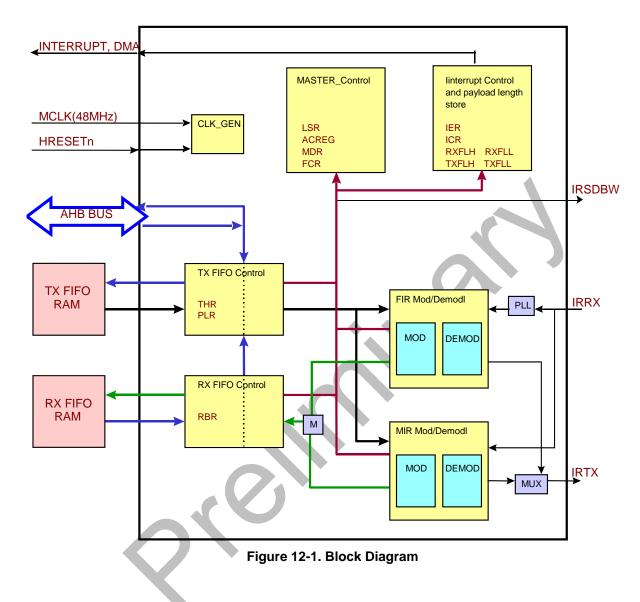

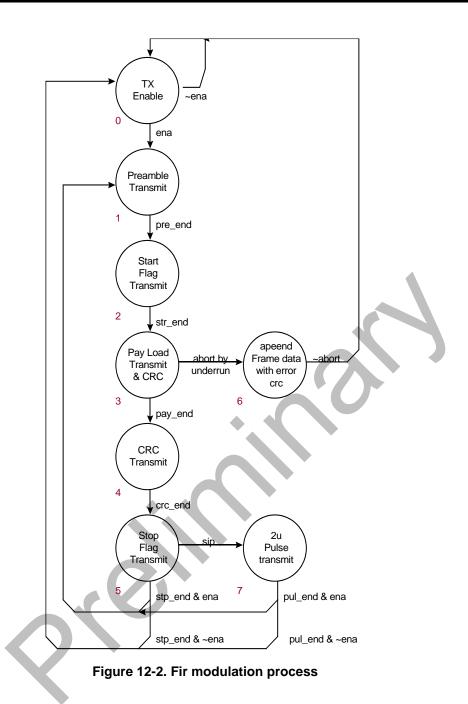

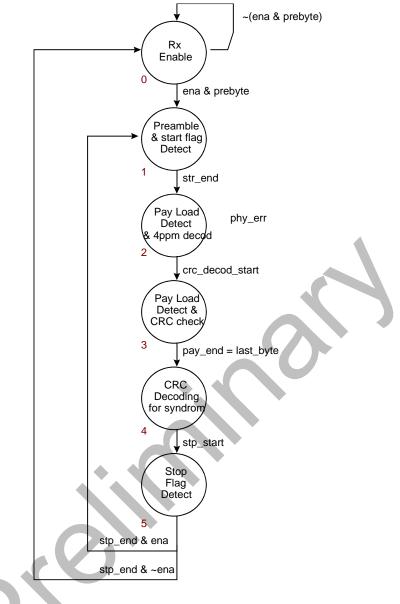

- IrDA

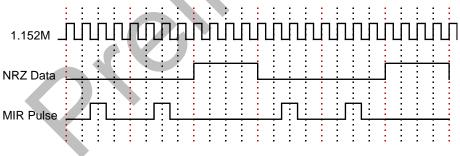

- Support IrDA 1.1 (1.152Mbps and 4Mbps)

- Support FIFO operation in the MIR and FIR mode

- -Configurable FIFO Size (16-byte or 64-byte)

- Support Back-to-Back Transactions -

- Support Software Selection Temic-IBM or HP Transceiver -

- Support Little-endian access

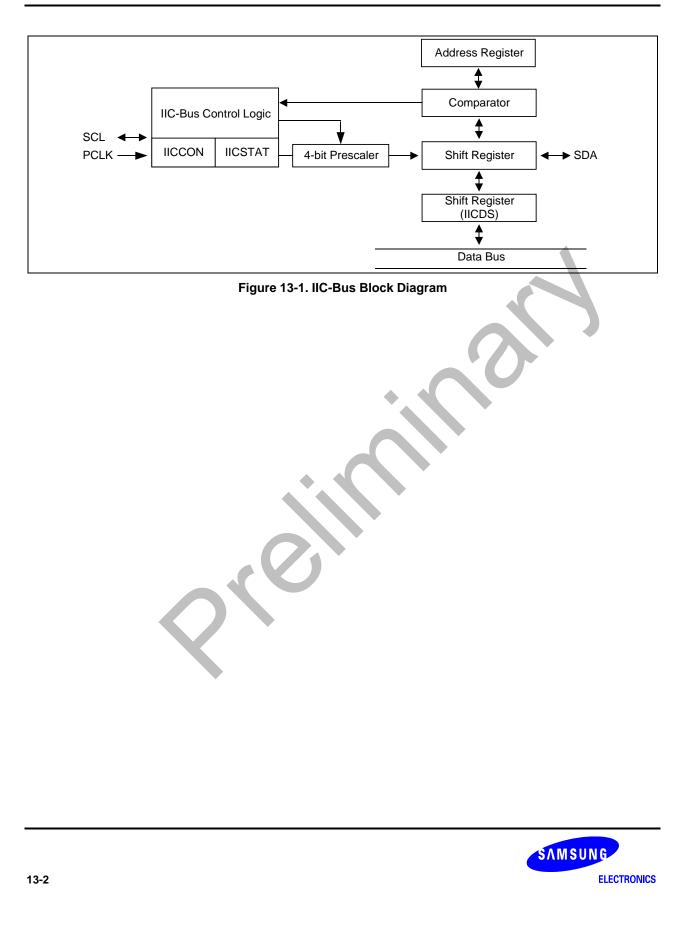

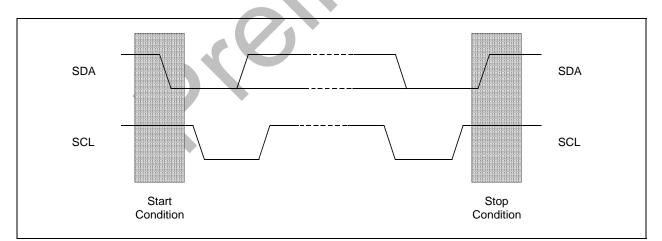

- IIC-Bus Interface

- 1-ch Multi-Master IIC-Bus

- Serial, 8-bit oriented and bi-directional data transfers can be made at up to 100 Kbit/s in the standard mode

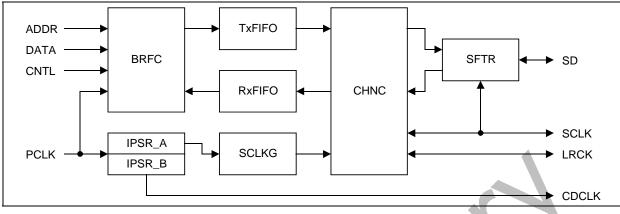

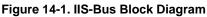

- IIS-Bus Interface

- 1-ch IIS-bus for the audio-codec interface with DMA-based operation

- Serial, 8/16-bit per channel data transfers

- 128 Bytes (64-Byte + 64-Byte) FIFO for receive/transmit

- Supports IIS format and MSB-justified data format

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available.

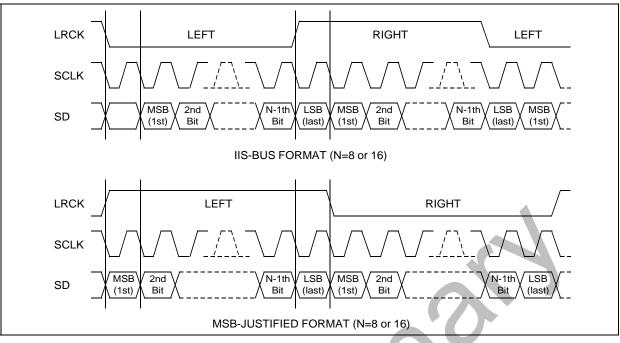

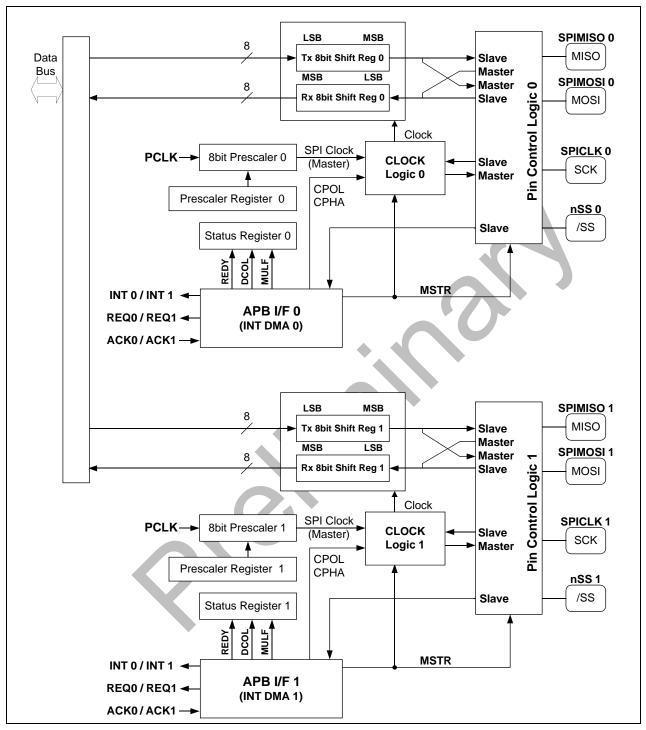

- SPI Interface

- 2-ch Serial Peripheral Interface Protocol version 2.11 compatible

- 2x8 bits Shift register for receive/transmit.

- DMA-based or interrupt-based operation.

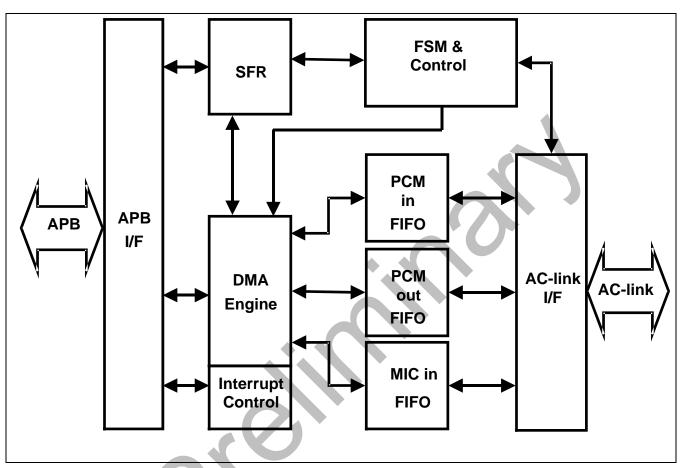

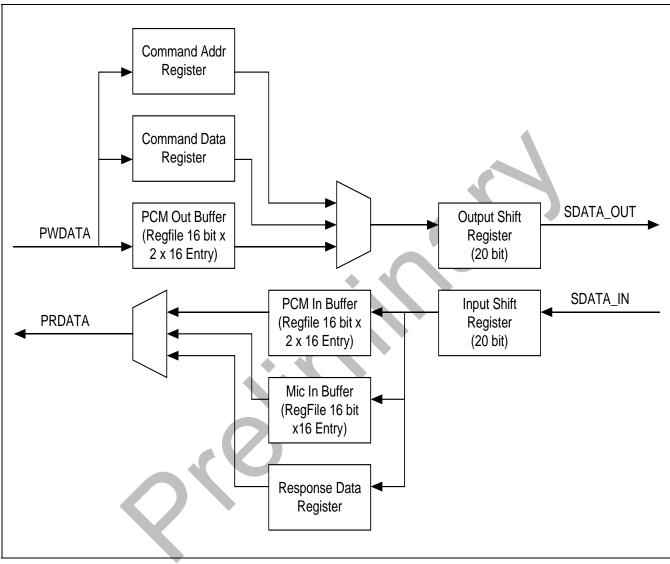

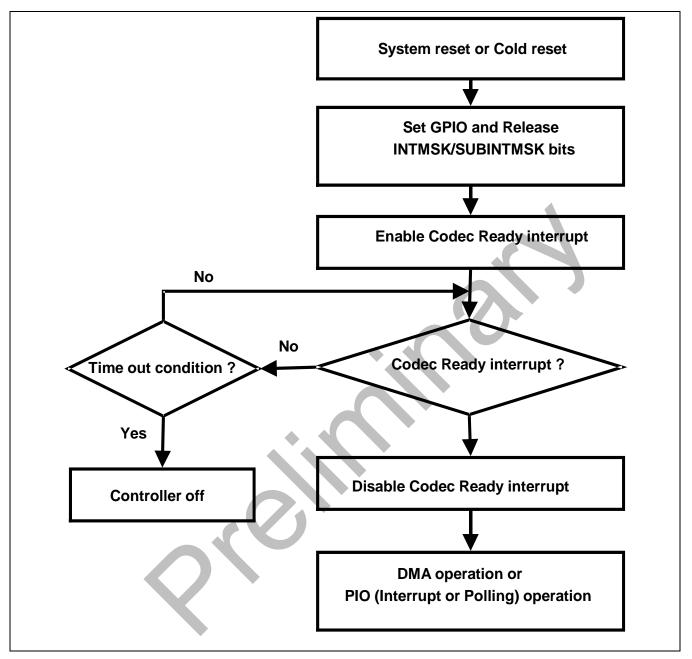

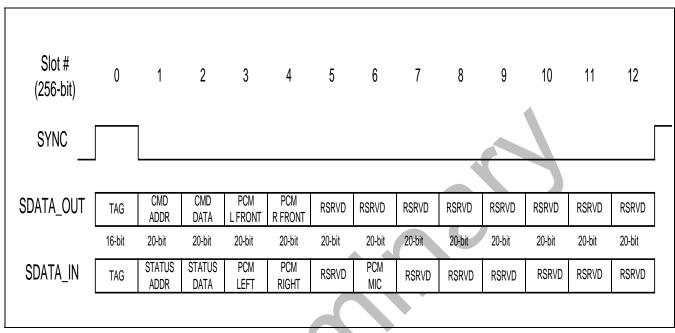

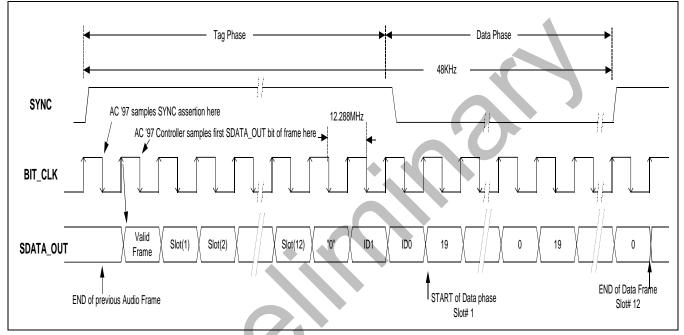

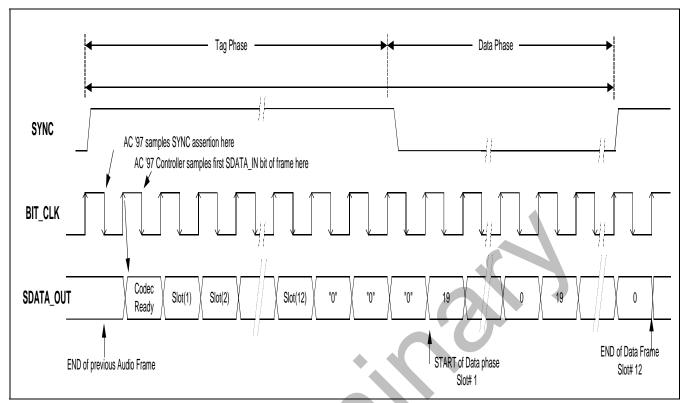

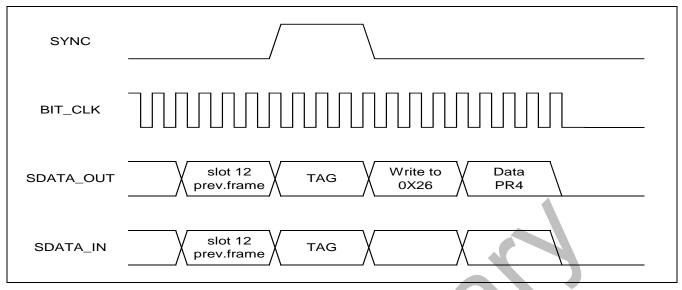

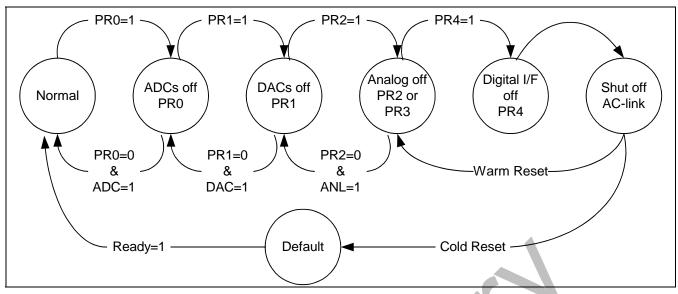

- AC97 Audio-CODEC Interface

- 48KHz 16-bit sampling

- 1-ch stereo PCM inputs / 1-ch stereo PCM outputs / 1-ch MIC input

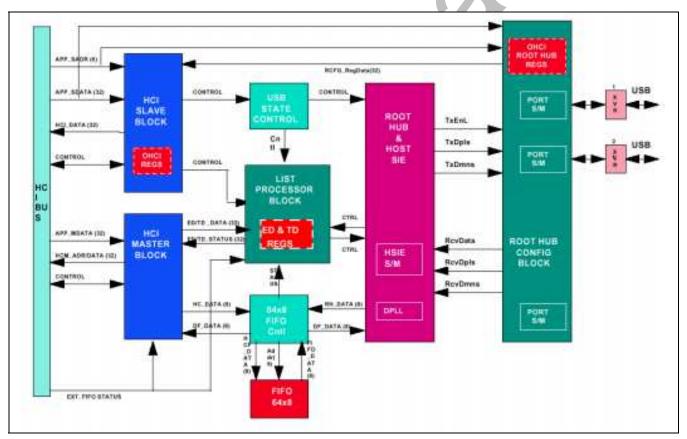

- USB Host

- 2-port USB Host

- Complies with OHCI Rev. 1.0

- Compatible with the USB Specification version 1.1

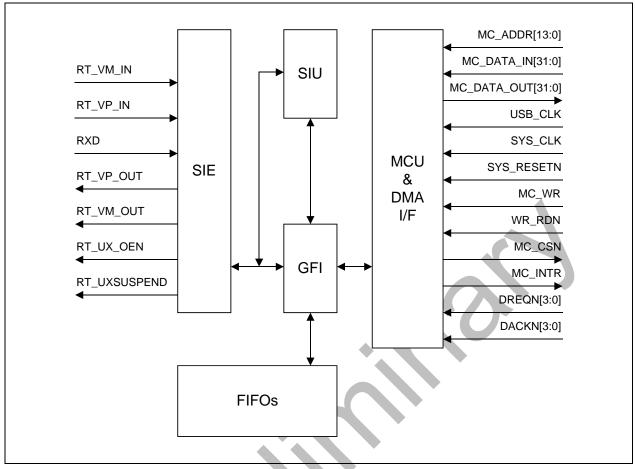

- USB Device

- 1-port USB Device

- 5 End-points for USB Device

- Compatible with the USB Specification version 1.1

#### **1.2.5 Parallel Communication**

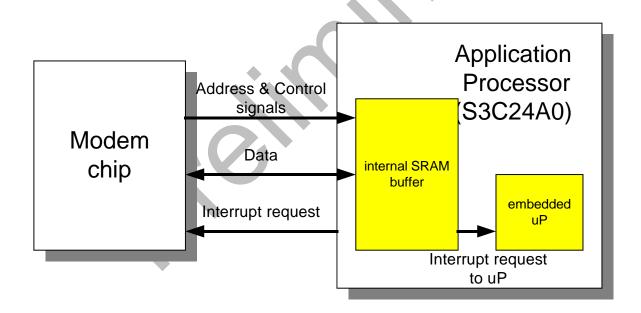

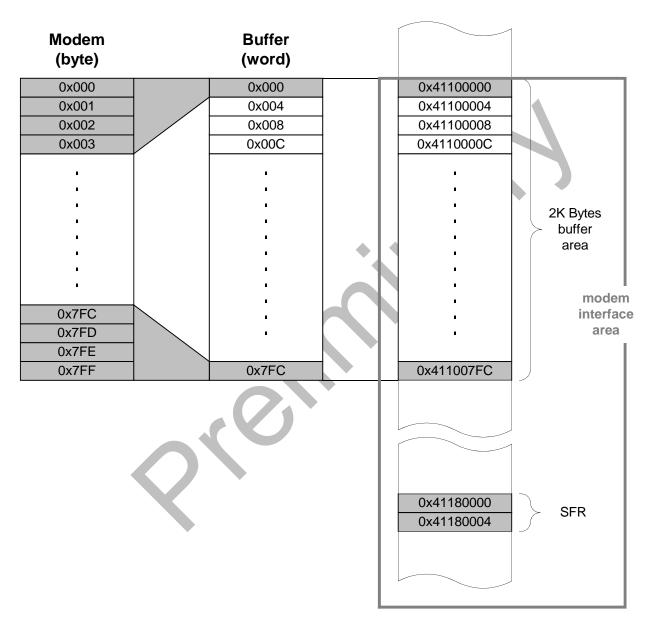

- Modem Chip Interface

- 8-bit Asynchronous SRAM interface-style interface

- On-chip 2KB dual-ported SRAM buffer

- Interrupt Request for Data Exchange

- Programmable Interrupt Port Address

- 32-bit GPIO

- Fully configurable 32-bit GPIO

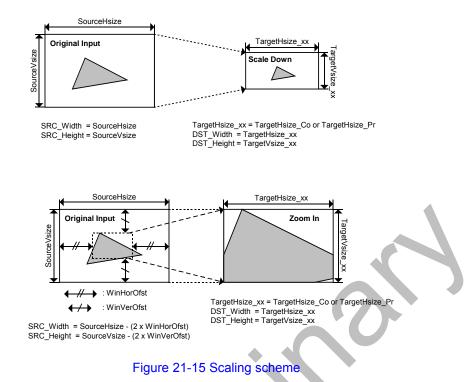

#### 1.2.6 Image and Video Processing

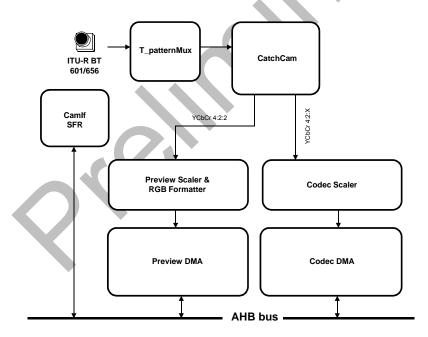

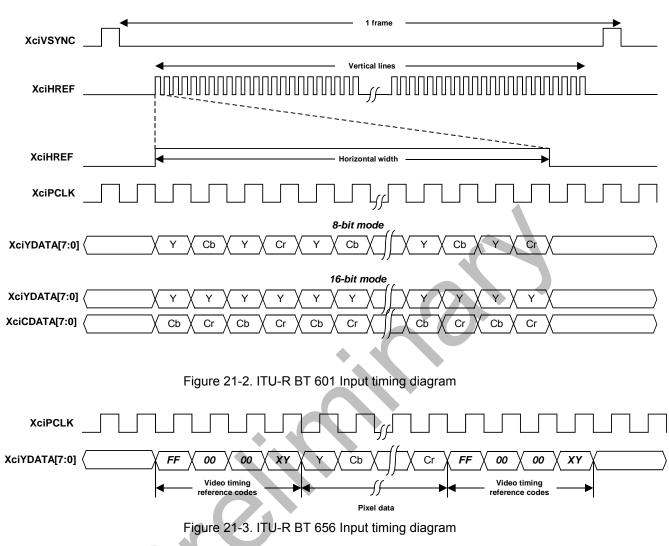

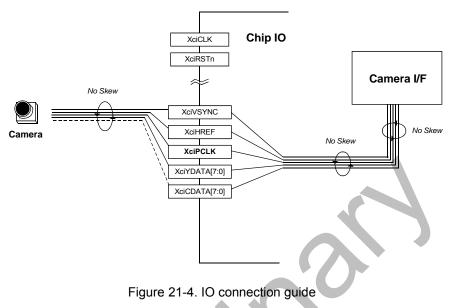

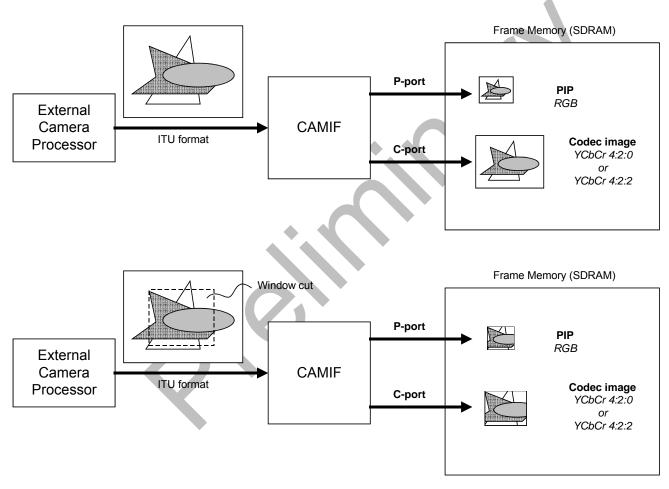

- Camera Inteface

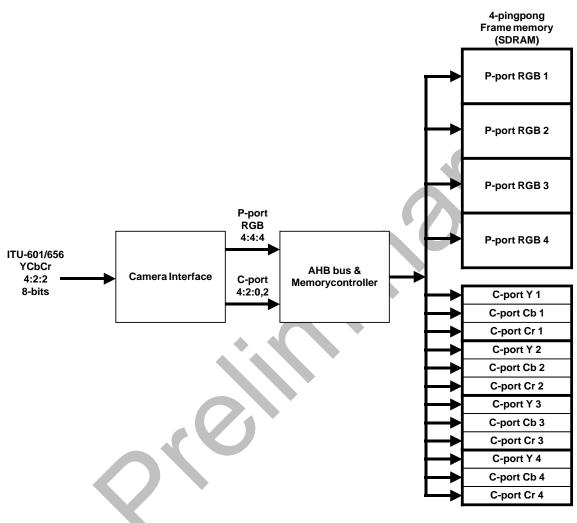

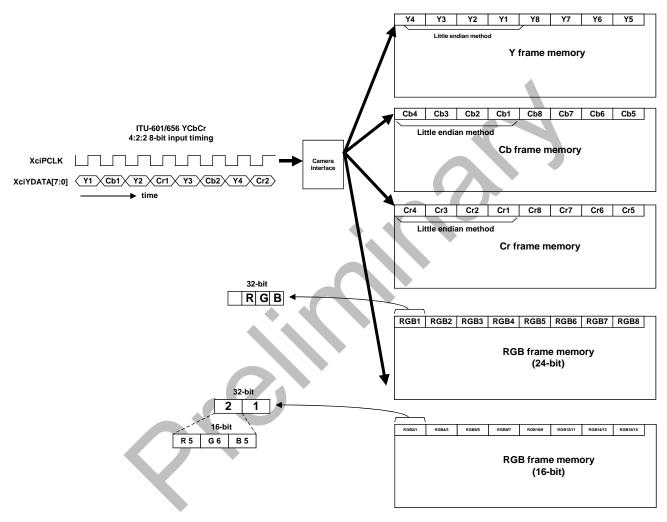

- ITU601/ITU656 YCbCr 4:2:2 8/16-bit mode

- Image down scaling capability for variable applications

- Digital Zoom-In

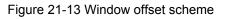

- Image X, Y-flip, 180 rotation

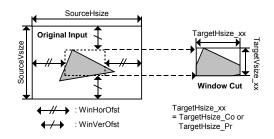

- Input Image Window Cut

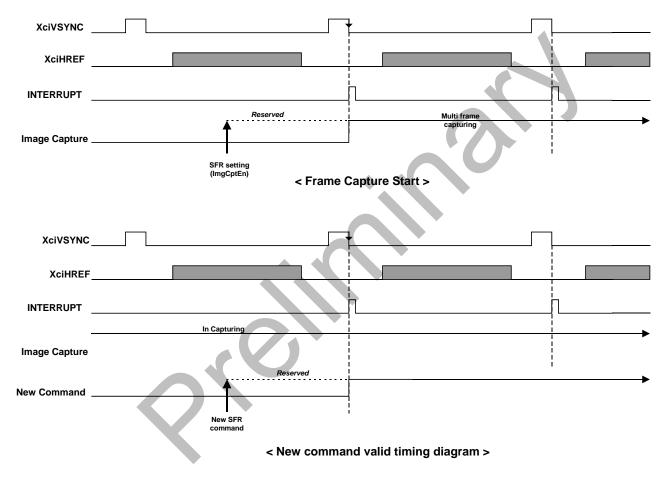

- Two master for dedicated DMA operation

- Programmable burst length for DMA operation

- Programmable polarity of video sync signals

- Wide horizontal line buffer (maximum 2048 pixel) -

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available.

Up to 4M pixel resolution support for scaled image (image preview or motion video capturing) and 16M pixel for unscaled image (JPEG)

- Format conversion from YCrCb 4:2:2 to 4:2:0 for codec, and to RGB 4:4:4 for preview

- Hardware Accelerated MPEG4 Video Encoding/Decoding

- A AHB Interface

- Realtime MPEG-4 Video Encoding & Decoding

- Up to Simple Profile at Level 3 (352x288 at 30fps)

- Supports H.263 Base Line

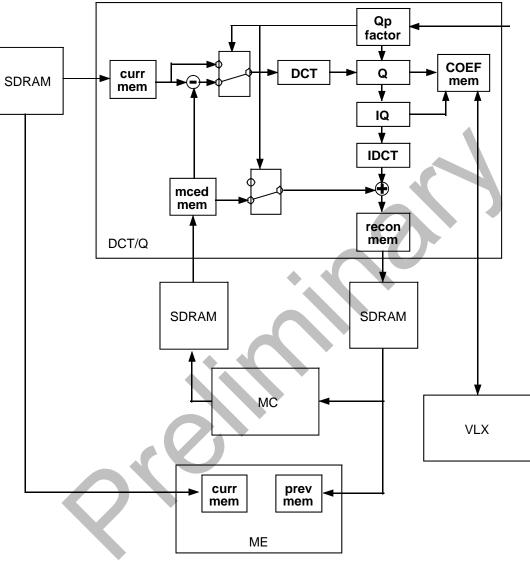

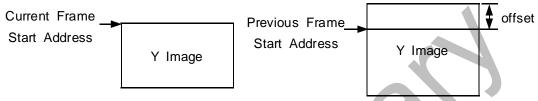

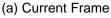

- MPEG-4 ME (Motion Estimation)

- Highly optimized hard-wired engine

- Unrestricted Mode and Advanced Prediction Mode (4MV)

- Use the advanced MRMCS algorithm

- Half-pel search

- Programmable Image size up to 2048x2048

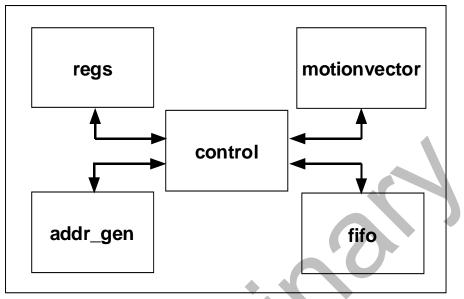

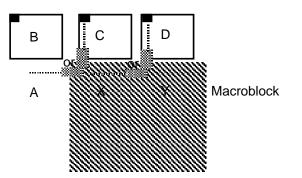

- Padding for Macro-block basis

- Search Range : [-16, 15.5]

- Intra/Inter Mode Decision MC (Motion Compensation)

- MC (Motion Compensation)

- Highly optimized hard-wired engine

- Unrestricted Mode and Advanced Prediction Mode (4MV)

- Half-pel search

- Programmable Image size up to 2048x2048

- Dedicated DMA

- Macroblock-based Pading

- Search Range : [-64, 63.5]

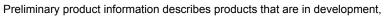

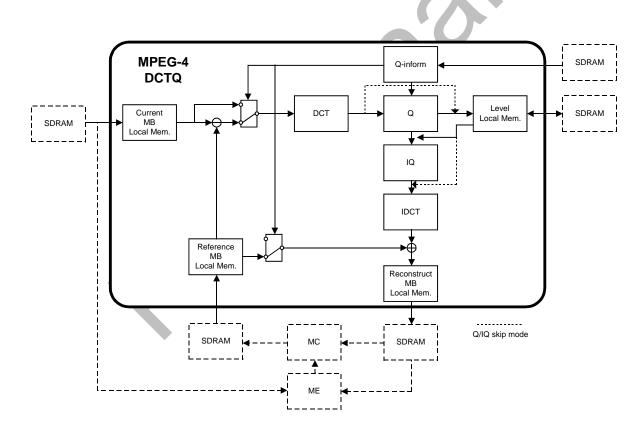

- DCTQ

- DCT/IDCT/Q/IQ operations AMBA AHB Interface

- Support MPEG-4 Simple Profile Level 3 / H.263 Base-Line Support programmable image size up to 4096x4096

- Macroblock-based processing

- Rate Control by Qp Information

- Local DMA

- Support MPEG-4 Encoding / Decoding

- Support JPEG DCT / IDCT Operation

- Operation unit : 1MB(MacroBlock) ~ 1 Frame

SAMSUNG **ELECTRONICS**

1-7

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available. Downloaded from Elcodis.com electronic components distributor. Specifications and information herein are subject to change without notice.

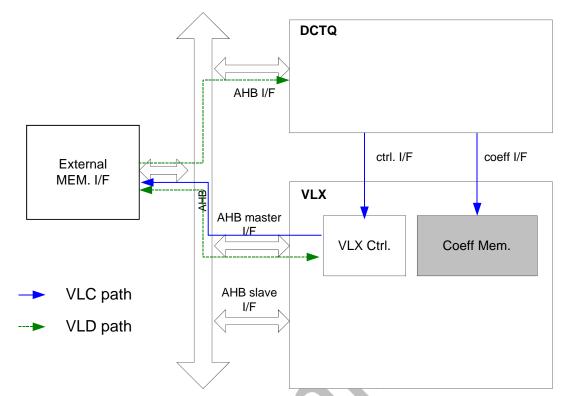

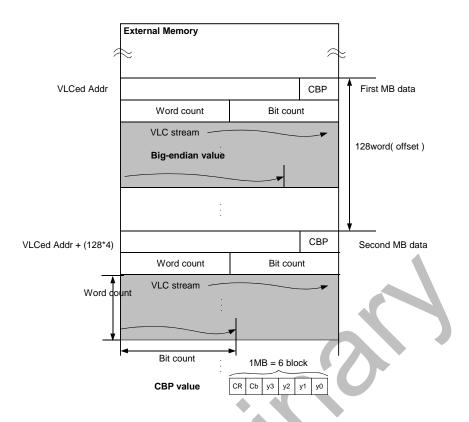

- VLX

- VLC/VLD operations

- AMBA AHB Interface

- Support MPEG4 Simple Profile Level 3/ H.263. Baseline

- Macro block-based processing

- Dedicated DMA

- Only DCTQ coefficient VLC/VLD operation

- Only DC prediction operation in VLC

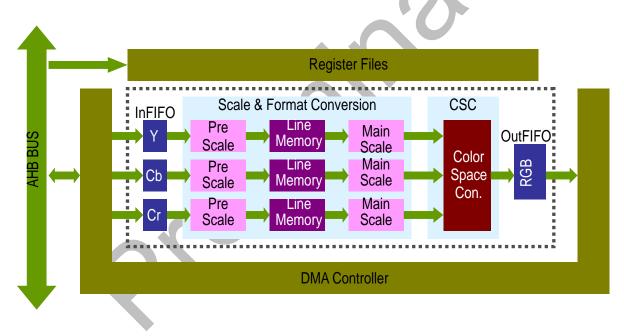

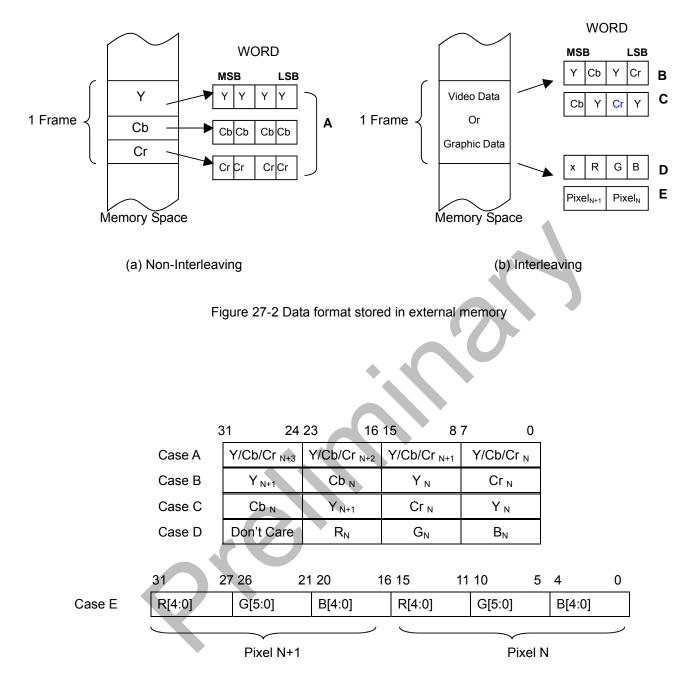

- Post Processor

- Dedicate DMA with Offset Address

- 3 Channel Scaling Pipelines for Video/Graphis Signal

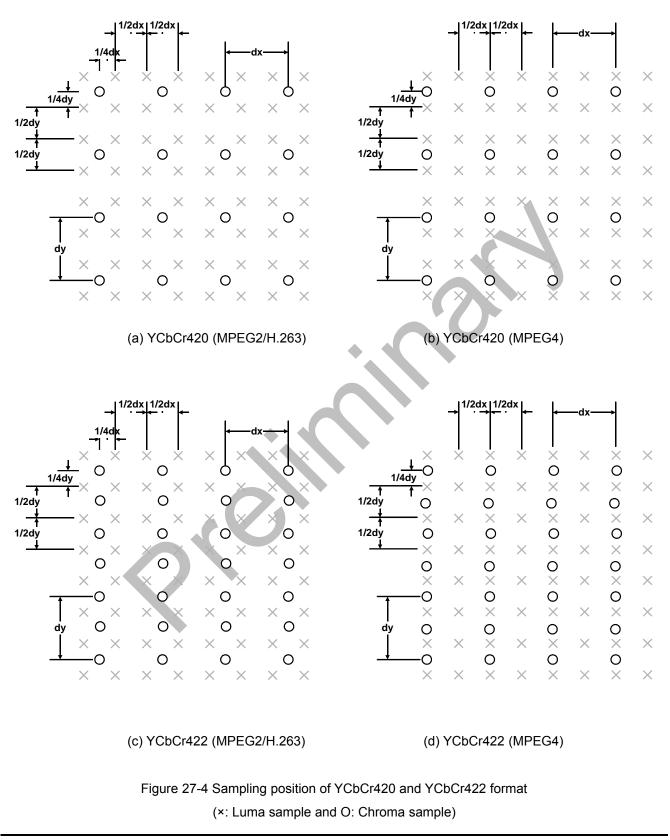

- Input Format : YCbCr4:2:0, YCbCr4:2:2, or RGB 16b/24b

- Output Format : RGB 16b/24b

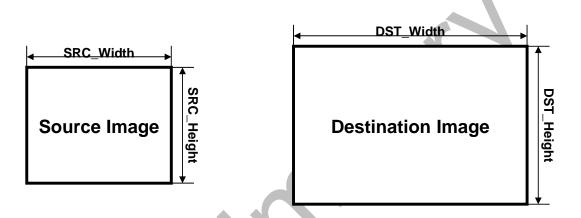

- Programmable Image Size (Source up to 4096x4096, Destination up to 2048x2048)

- Programmable Scale Ratio (Up-scale: up to Max. Destination Size, Down-scale: ~>1/64 in X & Y)

- Format Conversion for Video Signal (YCbCr4:2:0 or YCbCr4:2:2)

- Color Space Conversion (YCbCr2RGB)

- Separate Processing Clock from AHB Interface Clock

#### 1.2.7 Display Control

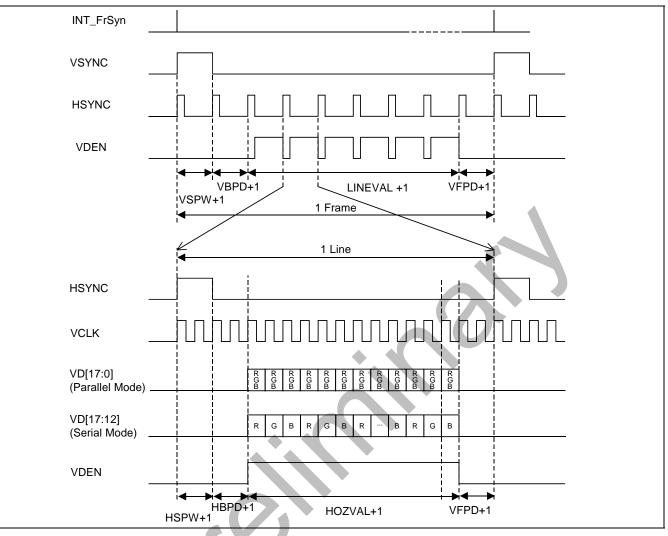

- TFT LCD Interface

- 18-bit Parallel or 6bit\*3 Interface

- 1/2/4/8-bpp Palletized or 8/16/18-bpp Non-Palletized Color-TFF support

- Supports 640x480, 320x240, 176x192 and others

- Up to 16 Mbyte virtual screen size

- Supports Multiple Virtual Display Screen (Supports Hardware Horizontal/Vertical Scrolling)

- Programmable timing control for different display panels

- Dual Buffer

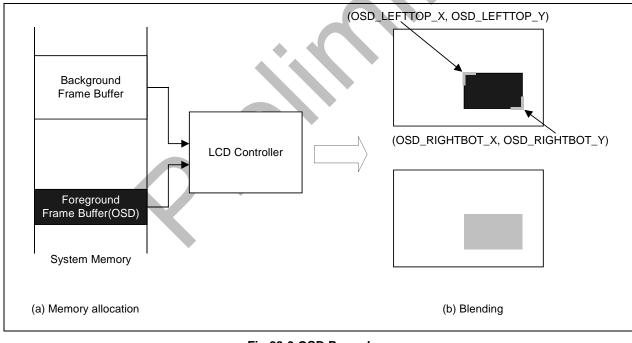

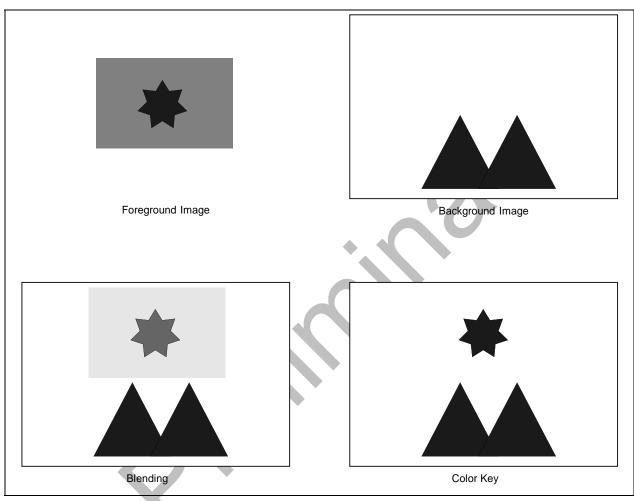

- OSD (On Screen Display)

- Realtime overlay plane multiplexing

- Programmable OSD window positioning

- Per-pixel alpha blending for 18-bpp OSD images

- Fixed alpha-value for 8-/16-/18-bpp OSD image

- 256-level alpha blending

- 24-bit color key support

- Dual buffer

1-8

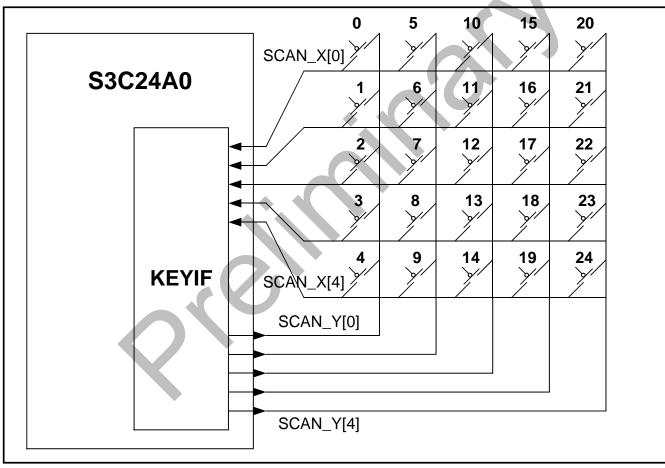

#### 1.2.8 Input Devices

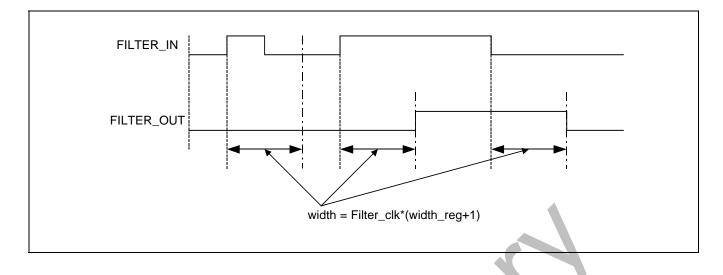

- Keypad Interface

- Provides internal debouncing filter

- 5-input, 5-output pins for key scan in/out

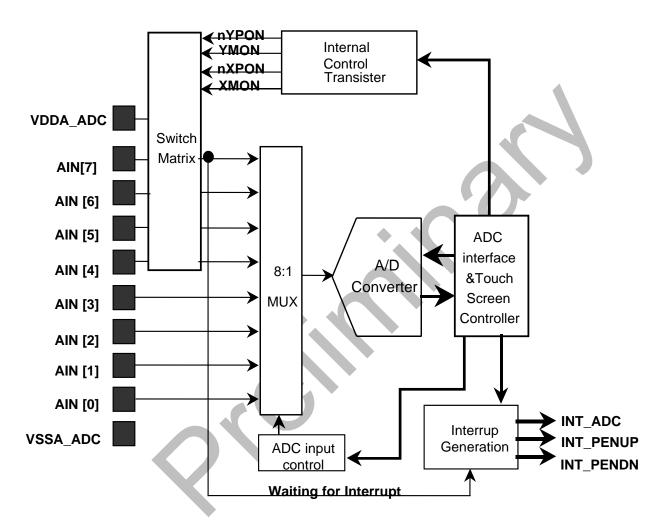

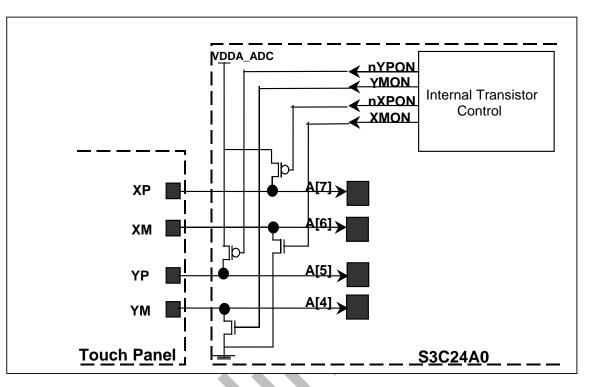

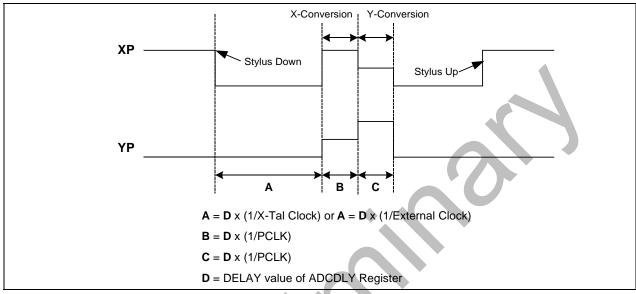

- A/D Converter and Touch Screen Interface

- 8-ch multiplexed ADC

- Max. 500K samples/sec and 10-bit resolution

#### 1.2.9 Storage Devices

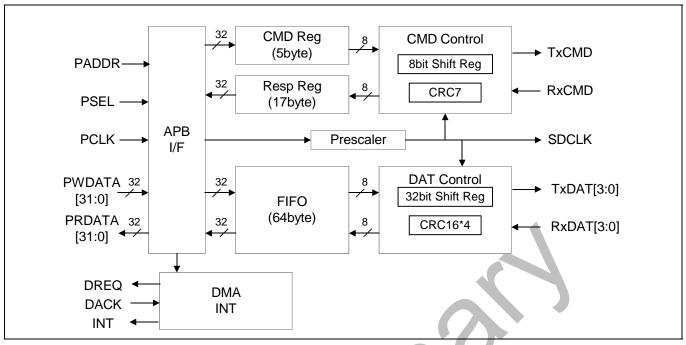

- SD Host

- Compatible with SD Memory Card Protocol version 1.0

- Compatible with SDIO Card Protocol version 1.0

- 64 Bytes FIFO for Tx/Rx

- DMA based or Interrupt based operation

- Compatible with Multimedia Card Protocol version 2.11

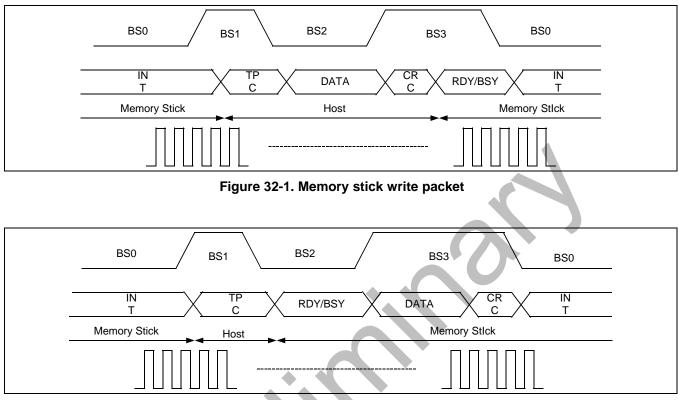

- Memory Stick Host

- Memory Stick version 1.3 compliant

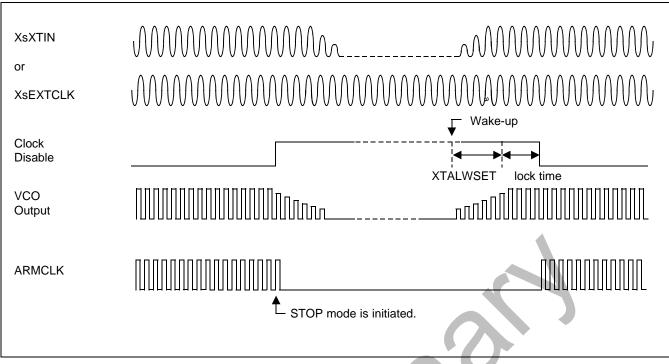

#### 1.2.10 System Management

- Little Endian format support

- System operating clock generation

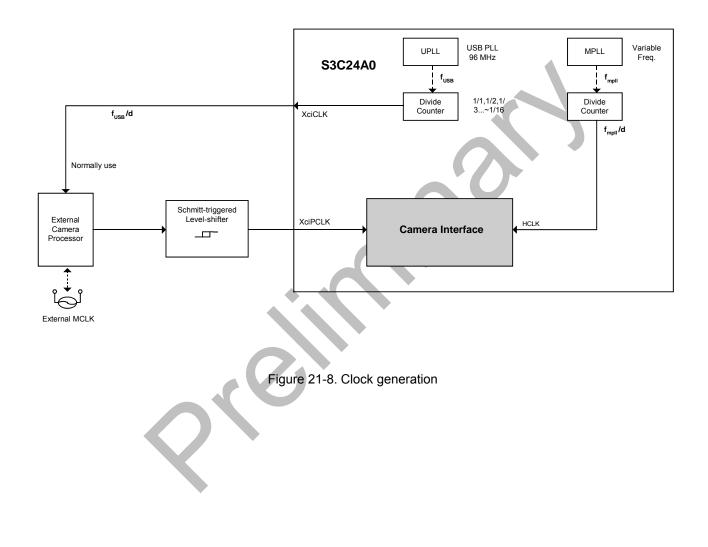

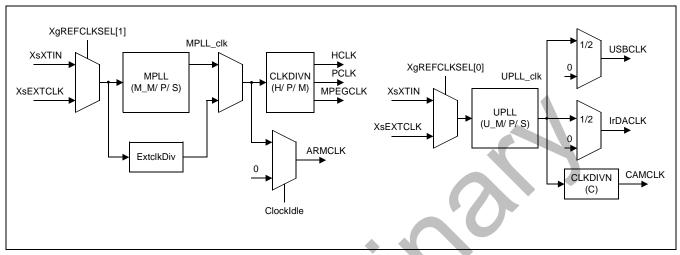

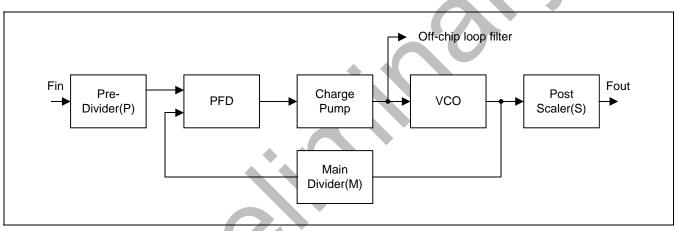

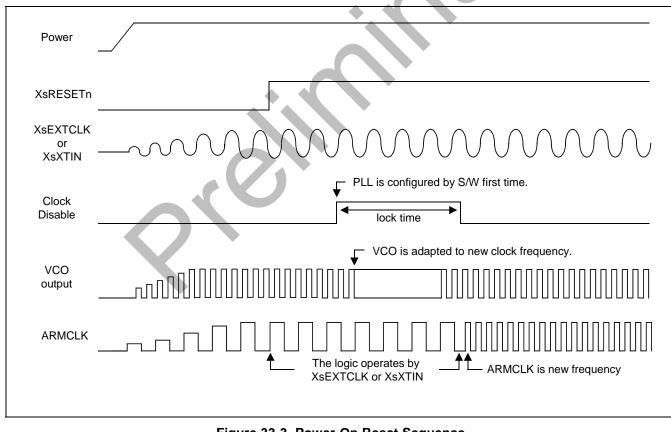

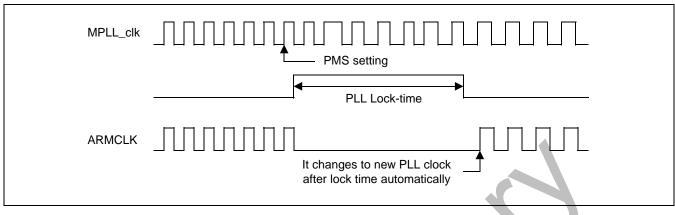

- Two on-chip PLLs, MPLL & UPLL

- MPLL generates the system reference clock, 200MHz@1.2V

- UPLL generates clocks for the USB Host/Device, IrDA and Camera

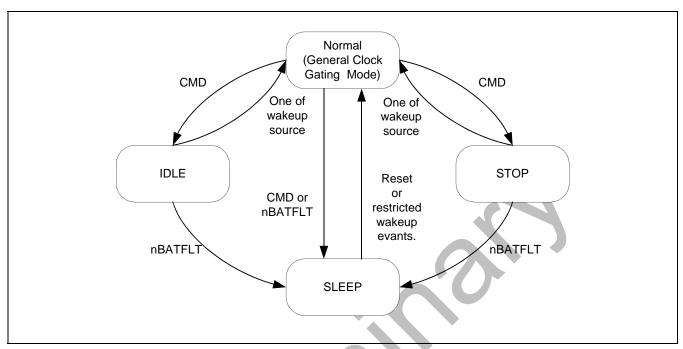

- Power Management

- Clock-off control for individual components

- Various power-down modes are available such as IDLE, STOP and SLEEP

- Wake-up by one of external interrupts or by the RTC alarm interrupt, etc.

#### **1.2.11 Electrical Characteristics**

- Operating Conditions

- - Supply Voltage for Logic Core: 1.25V +/- 0.05V

- External Memory Interface: 1.8V / 2.5V / 3.3V

- - External I/O Interface: 3.3V

- Operational Frequency

- - Max. 200MHz@1.25V

Preliminary product information describes products that are in development,

Downloaded from Elcodis.com electronic component distributors and information herein are subject to change without notice.

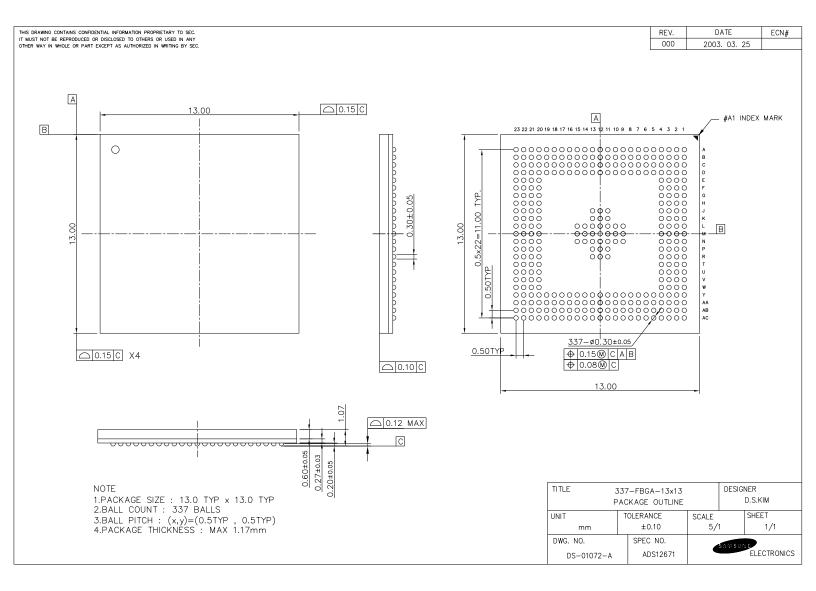

#### 1.2.12 Package

• 337-pin FBGA (0.5mm pitch, 13mm x 13mm)

Figure 1-1 An Overall Block Diagram of the S3C24A0

1-11

Preliminary product information describes products that are in development,

Downloaded from Elcodis.com electronic components distributors and information deta and associated errata are not yet available. Specifications and information herein are subject to change without notice.

BSW rv0.1-0417-N01

#### 1.3.2 Pin Assignment

|   |                                                      | #A1 INDEX MARK |

|---|------------------------------------------------------|----------------|

| ſ |                                                      | <b>Y</b> a     |

|   |                                                      | 8              |

|   |                                                      | E<br>F<br>Q    |

|   |                                                      | к<br>К         |

|   | 0000 0000000 0000<br>0000 000000 0000<br>0000 000000 | L<br>          |

|   |                                                      | F<br>R<br>T    |

|   |                                                      |                |

|   |                                                      | 7<br>74<br>78  |

|   | 000000000000000000000000000000000000000              | AC             |

|   |                                                      |                |

|   | ( BOTTOM VIEW )                                      |                |

337-Pin FBGA Pin Assignment

Preliminary product information describes products that are in development, for which full characterization data and associated errata are not yet available. Downloaded from Elcodis.com electronic componing distributions and information herein are subject to change without notice.

| Pin<br>Number | Pin Name    | Pin<br>Number | Pin Name    | Pin<br>Number | Pin Name    |

|---------------|-------------|---------------|-------------|---------------|-------------|

| A01           | XCIYDATA[4] | B11           | XRDATA[1]   | C21           | XRADDR [21] |

| A02           | VSS_B       | B12           | XRDATA[3]   | C22           | XFNFPS      |

| A03           | XCICDATA[0] | B13           | XRDATA[7]   | C23           | XFNFADV     |

| A04           | XCIYDATA[7] | B14           | XRADDR[5]   | D01           | XJTDO       |

| A05           | XCIPCLK     | B15           | XRNWBE[0]   | D02           | XJTDI       |

| A06           | XVVD[5]     | B16           | XRWEN       | D03           | XVVD[2]     |

| A07           | XVVD[7]     | B17           | XRCSN[2]    | D04           | XCIRSTN     |

| A08           | XVVCLK      | B18           | XRDATA[14]  | D05           | XCIYDATA[5] |

| A09           | XVDEN       | B19           | XRADDR[11]  | D06           | XCIVSYNC    |

| A10           | XCICDATA[7] | B20           | XRADDR[15]  | D07           | XVVD[13]    |

| A11           | XRDATA[0]   | B21           | XRADDR[22]  | D08           | XVVD[14]    |

| A12           | XRDATA[5]   | B22           | XFALE       | D09           | XCICDATA[5] |

| A13           | XRADDR [3]  | B23           | XFNFACYC    | D10           | XJRTCK      |

| A14           | XRADDR [7]  | C01           | XJTMS       | D11           | XVVSYNC     |

| A15           | XRNWBE[1]   | C02           | XJTRSTN     | D12           | XVVD[19]    |

| A16           | XRDATA[8]   | C03           | XCICLK      | D13           | XVVD[22]    |

| A17           | XRDATA[13]  | C04           | XCICDATA[1] | D14           | XRADDR [4]  |

| A18           | XRADDR [10] | C05           | XVVD[4]     | D15           | XRADDR [2]  |

| A19           | XRADDR [16] | C06           | XCIHREF     | D16           | XRADDR [0]  |

| A20           | XRADDR [17] | C07           | XCICDATA[4] | D17           | XRADDR [14] |

| A21           | XRADDR[20]  | C08           | XCICDATA[6] | D18           | XRADDR [19] |

| A22           | XRADDR [23] | C09           | XVHSYNC     | D19           | XFCLE       |

| A23           | XFRNB[0]    | C10           | XVVD[20]    | D20           | XRADDR [8]  |

| B01           | XJTCK       | C11           | XVVD[23]    | D21           | XRADDR [12] |

| B02           | XCIYDATA[0] | C12           | VDD_C       | D22           | XFNFBW      |

| B03           | XCIYDATA[2] | C13           | XRDATA[6]   | D23           | XRADDR [25] |

| B04           | XCIYDATA[6] | C14           | XRADDR[1]   | E01           | XGPIO[31]   |

| B05           | XCICDATA[2] | C15           | XRADDR [6]  | E02           | X2CSDA      |

| B06           | XCICDATA[3] | C16           | XRWAITN     | E03           | X2CSCL      |

| B07           | XVVD[11]    | C17           | XRCSN[1]    | E04           | XCIYDATA[1] |

| B08           | XVVD[15]    | C18           | XRDATA[10]  | E20           | XFRNB[1]    |

| B09           | XVVD[18]    | C19           | XRDATA[12]  | E21           | XRADDR [24] |

| B10           | XVVD[21]    | C20           | XRADDR [9]  | E22           | XPDATA[2]   |

Table 1-1. 337-Pin FBGA Pin Assignments - Pin Number Order

1-13

| Pin<br>Number | Pin Name    | Pin Pin Name Number No. 100 Pin Name N |            | Pin<br>Number | Pin Name       |

|---------------|-------------|----------------------------------------|------------|---------------|----------------|

| E23           | XPDATA[1]   | J21                                    | VDD_A      | M09           | VSS_B          |

| F01           |             | J21                                    |            | M09<br>M10    | VOS_B<br>VDD F |

|               | XGPIO[28]   |                                        | XPDQM[3]   |               |                |

| F02           | XGPIO[29]   | J23                                    | XPDATA[8]  | M11           | VSS            |

| F03           | XGPIO[30]   | K01                                    | XGPIO[11]  | M12           | VSS            |

| F04           | XCIYDATA[3] | K02                                    | XGPIO[14]  | M13           | VSS            |

| F20           | XRADDR [18] | K03                                    | XGPIO[16]  | M14           | VDD_A          |

| F21           | XPDATA[0]   | K04                                    | XVVD[12]   | M15           | VSS_D          |

| F22           | XPDATA[6]   | K11                                    | VDD_B      | M20           | XPADDR[2]      |

| F23           | XPDATA[3]   | K12                                    | VSS        | M21           | XPDATA[15]     |

| G01           | XGPIO[24]   | K13                                    | VSS_E      | M22           | XPADDR[1]      |

| G02           | XGPIO[26]   | K20                                    | XRDATA[11] | M23           | XPADDR[3]      |

| G03           | XGPIO[27]   | K21                                    | XPDATA[9]  | N01           | X97SYNC        |

| G04           | XVVD[3]     | K22                                    | XPDATA[10] | N02           | X97RESETN      |

| G20           | XRADDR [13] | K23                                    | XPDATA[11] | N03           | XGPIO[4]       |

| G21           | XPDATA[5]   | L01                                    | XGPIO[7]   | N04           | XGPIO[8]       |

| G22           | XPDQM[0]    | L02                                    | XGPIO[10]  | N09           | VDD_A          |

| G23           | XPDATA[7]   | L03                                    | XGPIO[12]  | N10           | VDD_B          |

| H01           | XGPIO[20]   | L04                                    | XGPIO[21]  | N11           | VSS            |

| H02           | XGPIO[23]   | L09                                    | VDD_C      | N12           | VSS            |

| H03           | XGPIO[22]   | L10                                    | VDD_C      | N13           | VSS            |

| H04           | XVVD[6]     | L11                                    | VSS        | N14           | VSS_D          |

| H20           | XPDATA[4]   | L12                                    | VSS        | N15           | VDD_D          |

| H21           | VDD_D       | L13                                    | VSS        | N20           | XRDATA[9]      |

| H22           | XPDQM[1]    | L14                                    | VDD_E      | N21           | XPADDR[4]      |

| H23           | XPDQM[2]    | L15                                    | VSS_D      | N22           | XPADDR[5]      |

| J01           | XGPIO[17]   | L20                                    | XPDATA[14] | N23           | XPADDR[6]      |

| J02           | XGPIO[18]   | L21                                    | XPDATA[12] | P01           | XURTSN         |

| J03           | XGPIO[25]   | L22                                    | XPDATA[13] | P02           | X97SDO         |

| J04           | XVVD[10]    | L23                                    | XPADDR[0]  | P03           | X97BITCLK      |

| J11           | VSS_B       | M01                                    | XGPIO[0]   | P04           | XGPIO[5]       |

| J12           | VSS_E       | M02                                    | XGPIO[6]   | P11           | VSS_B          |

| J13           | VDD_E       | M03                                    | VDD_B      | P12           | VDD_F          |

| J20           | XRDATA[15]  | M04                                    | XGPIO[19]  | P13           | VSS_D          |

Table 1-1. 337-Pin FBGA Pin Assignments - Pin Number Order

1-14

| Pin<br>Number | Pin Name    | Pin<br>Number | Pin Name         | Pin<br>Number | Pin Name       |

|---------------|-------------|---------------|------------------|---------------|----------------|

| P20           | XRCSN[0]    | V03           | XGTMODE[3]       | Y20           | VDD_D          |

| P21           | XPDATA[16]  | V04           | XUCLK            | Y21           | XPDATA[25]     |

| P22           | XPADDR[7]   | V20           | XRDATA[2]        | Y22           | XPDATA[27]     |

| P23           | XPDATA[18]  | V21           | XPDATA[29]       | Y23           | XPDATA[26]     |

| R01           | XGTMODE[2]  | V22           | XPWEN            | AA01          | XRTCXTI        |

| R02           | XURXD       | V23           | XPCASN           | AA02          | XGREFCLKSEL[0] |

| R03           | XGPIO[2]    | W01           | XGTMODE[1]       | AA03          | XGPWROFFN      |

| R04           | XGPIO[15]   | W02           | XSPIMISO         | AA04          | XADCAIN[5]     |

| R11           | VDD_A       | W03           | XSPISSIN[0]      | AA05          | XADCAVREF      |

| R12           | VDD_B       | W04           | X2SCLK           | AA06          | XADCAIN[2]     |

| R13           | VSS_D       | W20           | VDD_D            | AA07          | GND10          |

| R20           | XROEN       | W21           | VDD_A            | AA08          | VDD13          |

| R21           | XPDATA[17]  | W22           | XPCSN[0]         | AA09          | XSRESETN       |

| R22           | XPDATA[19]  | W23           | XPCSN[1]         | AA10          | XSXTOUT        |

| R23           | XPSCLK      | Y01           | XSWRESETN        | AA11          | XUSDP[0]       |

| T01           | X2SCDCLK    | Y02           | XGTMODE[0]       | AA12          | XUSDN[0]       |

| T02           | XUCTSN      | Y03           | XSPICLK          | AA13          | XMSBS          |

| Т03           | X97SDI      | Y04           | X2SDI            | AA14          | XMIWEN         |

| T04           | XGPIO[13]   | Y05           | XGBATFLTN        | AA15          | XMIADR[8]      |

| T20           | XPDATA[24]  | Y06           | XGPIO[1]         | AA16          | XMIADR[6]      |

| T21           | XPDATA[20]  | Y07           | XGPIO[3]         | AA17          | XMIDATA[6]     |

| T22           | XPDATA[21]  | Y08           | VDD15            | AA18          | VDD_A          |

| T23           | XPDATA[23]  | Y09           | XSRSTOUTN        | AA19          | XMIDATA[2]     |

| U01           | X2SDO       | Y10           | XUDDP            | AA20          | XMIADR[0]      |

| U02           | X2SLRCK     | Y11           | XSDDAT[3]        | AA21          | VDD_D          |

| U03           | XUTXD       | Y12           | VDD20(VDDpadUSB) | AA22          | XPDATA[31]     |

| U04           | XGPIO[9]    | Y13           | XMSSDIO          | AA23          | XPDATA[28]     |

| U20           | XRDATA[4]   | Y14           | XMSPI            | AB01          | VDD10          |

| U21           | XPDATA[22]  | Y15           | XMICSN           | AB02          | XADCAIN[7]     |

| U22           | XPCKE       | Y16           | XMIADR[10]       | AB03          | XRTCXTO        |

| U23           | XPRASN      | Y17           | XPADDR[13]       | AB04          | XGREFCLKSEL[1] |

| V01           | XSPIMOSI    | Y18           | XMIADR[4]        | AB05          | XADCAIN[0]     |

| V02           | XSPISSIN[1] | Y19           | XMIADR[2]        | AB06          | VDD11          |

Table 1-1. 337-Pin FBGA Pin Assignments - Pin Number Order

1-15

|               |                  |               | -            |               |            |

|---------------|------------------|---------------|--------------|---------------|------------|

| Pin<br>Number | Pin Name         | Pin<br>Number | Pin Name     | Pin<br>Number | Pin Name   |

| AB07          | GND12            | AB21          | XPADDR[11]   | AC12          | XSDDAT[2]  |

| AB08          | XSUPLLCAP        | AB22          | XPDATA[30]   | AC13          | XSDDAT[0]  |

| AB09          | XSEXTCLK         | AB23          | XPADDR[8]    | AC14          | XMIADR[9]  |

| AB10          | XUSDP[1]         | AC01          | GND9(VSSrtc) | AC15          | XMIADR[5]  |

| AB11          | XUDDN            | AC02          | XADCAIN[6]   | AC16          | XMIDATA[5] |

| AB12          | XSDDAT[1]        | AC03          | XADCAIN[4]   | AC17          | XMIDATA[3] |

| AB13          | GND19(VSSpadUSB) | AC04          | XADCAIN[3]   | AC18          | XMIDATA[1] |

| AB14          | XMIOEN           | AC05          | XADCAIN[1]   | AC19          | XMIADR[3]  |

| AB15          | XMIADR[7]        | AC06          | XSMPLLCAP    | AC20          | XPADDR[14] |

| AB16          | XMIDATA[7]       | AC07          | GND14        | AC21          | XPADDR[12] |

| AB17          | XMIDATA[4]       | AC08          | XGMONHCLK    | AC22          | XPADDR[10] |

| AB18          | XMIIRQN          | AC09          | XSXTIN       | AC23          | XPADDR[9]  |

| AB19          | XMIDATA[0]       | AC10          | XUSDN[1]     |               |            |

| AB20          | XMIADR[1]        | AC11          | XMSSCLKO     |               |            |

Table 1-1. 337-Pin FBGA Pin Assignments – Pin Number Order

| Pin<br>Number | Name        | Default Function | I/O | I/O state@ Reset mode<br>(Data/En/PullupEn)<br>En(L)=>output<br>PullupEn(L)=>PullUp | I/O<br>State@SLEEP<br>mode | I/O<br>State@STOP<br>mode | Cell Type<br>(24A0A) |

|---------------|-------------|------------------|-----|-------------------------------------------------------------------------------------|----------------------------|---------------------------|----------------------|

| AA7           | VSSadc      | VSSadc           | Р   | Р                                                                                   | Р                          | Р                         | Р                    |

| AB7           | VSSMpll     | VSSMpll          | Р   | Р                                                                                   | Р                          | Р                         | Р                    |

| AC7           | VSSUpII     | VSSUpII          | Р   | Р                                                                                   | Р                          | Р                         | Р                    |

| AB13          | VSSpadUSB   | VSSpadUSB        | Р   | Р                                                                                   | Р                          | Р                         | Р                    |

| AC1           | VSSrtc      | VSSrtc           | Р   | Р                                                                                   | Р                          | Р                         | Р                    |

| AA18          | VDDlogic    | VDDlogic         | Р   | Р                                                                                   | Р                          | Р                         | Р                    |

| J21           | VDDlogic    | VDDlogic         | Р   | Р                                                                                   | Р                          | Р                         | Р                    |

| M14           | VDDlogic    | VDDlogic         | Р   | Р                                                                                   | Р                          | Р                         | Р                    |

| N9            | VDDlogic    | VDDlogic         | Ρ   | Р                                                                                   | Р                          | Р                         | Р                    |

| R11           | VDDlogic    | VDDlogic         | Ρ   | Р                                                                                   | Р                          | P                         | Р                    |

| W21           | VDDlogic    | VDDlogic         | Ρ   | Р                                                                                   | Р                          | Р                         | Р                    |

| K11           | VDDpadIO    | VDDpadIO         | Ρ   | Р                                                                                   | Р                          | Р                         | Р                    |

| M3            | VDDpadIO    | VDDpadIO         | Ρ   | Р                                                                                   | P                          | Р                         | Р                    |

| N10           | VDDpadIO    | VDDpadIO         | Ρ   | Р                                                                                   | Р                          | Р                         | Р                    |

| R12           | VDDpadIO    | VDDpadIO         | Ρ   | P                                                                                   | Р                          | Р                         | Р                    |

| C12           | VDDarm      | VDDarm           | Ρ   | Р                                                                                   | P                          | Р                         | Р                    |

| L10           | VDDarm      | VDDarm           | Ρ   | Р                                                                                   | Р                          | Р                         | Р                    |

| L9            | VDDarm      | VDDarm           | Ρ   | Р                                                                                   | Р                          | Р                         | Р                    |

| AA21          | VDDpadSDRAM | VDDpadSDRAM      | Р   | Р                                                                                   | Р                          | Р                         | Р                    |

| H21           | VDDpadSDRAM | VDDpadSDRAM      | Р   | Р                                                                                   | Р                          | Р                         | Р                    |

| N14           | VSS         | VSS              | Р   | Р                                                                                   | Р                          | Р                         | Р                    |

| N15           | VDDpadSDRAM | VDDpadSDRAM      | Р   | Р                                                                                   | Р                          | Р                         | Р                    |

| W20           | VDDpadSDRAM | VDDpadSDRAM      | Р   | Р                                                                                   | Р                          | Р                         | Р                    |

| Y20           | VDDpadSDRAM | VDDpadSDRAM      | Р   | Р                                                                                   | Р                          | Р                         | Р                    |

| J13           | VDDpadFlash | VDDpadFlash      | Р   | Р                                                                                   | Р                          | Р                         | Р                    |

| L14           | VDDpadFlash | VDDpadFlash      | Ρ   | Р                                                                                   | Р                          | Р                         | Р                    |

| M10           | VDDalive    | VDDalive         | Ρ   | Р                                                                                   | Р                          | Р                         | Р                    |

| P12           | VDDalive    | VDDalive         | Ρ   | Р                                                                                   | Р                          | Р                         | Р                    |

| AB1           | VDDrtc      | VDDrtc           | Ρ   | Р                                                                                   | Р                          | Р                         | Р                    |

| AB6           | VDDadc      | VDDadc           | Ρ   | Р                                                                                   | Р                          | Р                         | Р                    |

| AA8           | VDDMpll     | VDDMpll          | Ρ   | Р                                                                                   | Р                          | Р                         | Р                    |

| Y8            | VDDupll     | VDDupll          | Ρ   | Р                                                                                   | Р                          | Р                         | Р                    |

| Y12           | VDDpadUSB   | VDDpadUSB        | Р   | Р                                                                                   | Р                          | Р                         | Р                    |

| K12           | VSS         | VSS              | Ρ   | Р                                                                                   | Р                          | Р                         | Р                    |

| L11           | VSS         | VSS              | Р   | Р                                                                                   | Р                          | Р                         | Р                    |

| L12           | VSS         | VSS              | Р   | Р                                                                                   | Р                          | Р                         | Р                    |

| L13           | VSS         | VSS              | Ρ   | Р                                                                                   | Р                          | Р                         | Р                    |

#### Table 1-2. 337-Pin FBGA Pin Assignments

1-17

| Pin<br>Number | Name        | Default<br>Function | I/O | I/O state@ Reset mode<br>(Data/En/PullupEn)<br>En(L)=>output<br>PullupEn(L)=>PullUp | I/O<br>State@SLEEP<br>mode | I/O<br>State@STOP<br>mode | Cell Type<br>(24A0A) |

|---------------|-------------|---------------------|-----|-------------------------------------------------------------------------------------|----------------------------|---------------------------|----------------------|

| M11           | VSS         | VSS                 | Р   | Р                                                                                   | Р                          | Р                         | Р                    |

| M12           | VSS         | VSS                 | Р   | Р                                                                                   | Р                          | Р                         | Р                    |

| M13           | VSS         | VSS                 | Р   | Р                                                                                   | Р                          | Р                         | Р                    |

| N11           | VSS         | VSS                 | Р   | Р                                                                                   | Р                          | Р                         | Р                    |

| N12           | VSS         | VSS                 | Р   | Р                                                                                   | Р                          | Р                         | Р                    |

| N13           | VSS         | VSS                 | Р   | Р                                                                                   | Р                          | Р                         | Р                    |

| A2            | VSSpadIO    | VSSpadIO            | Р   | Р                                                                                   | Р                          | Р                         | Р                    |

| J11           | VSSpadIO    | VSSpadIO            | Р   | Р                                                                                   | Р                          | Р                         | Р                    |

| M9            | VSSpadIO    | VSSpadIO            | Р   | Р                                                                                   | Р                          | Р                         | Р                    |

| P11           | VSSpadIO    | VSSpadIO            | Р   | Р                                                                                   | Р                          | Р                         | Р                    |

| L15           | VSSpadSDRAM | VSSpadSDRAM         | Р   | Р                                                                                   | Р                          | Р                         | P                    |

| M15           | VSSpadSDRAM | VSSpadSDRAM         | Р   | Р                                                                                   | P                          | Р                         | Р                    |

| P13           | VSSpadSDRAM |                     | Р   | Р                                                                                   | Р                          | Р                         | Р                    |

| R13           | VSSpadSDRAM | VSSpadSDRAM         | Р   | Р                                                                                   | Р                          | Р                         | Р                    |

| J12           | VSSpadFlash | VSSpadFlash         | Р   | Р                                                                                   | Р                          | Р                         | Р                    |

| K13           | VSSpadFlash | VSSpadFlash         | Р   | Р                                                                                   | Р                          | Р                         | Р                    |

| E3            | X2cSCL      | X2cSCL              | I/O | I/H                                                                                 | L or I                     | Н                         | phbsud8sm            |

| E2            | X2cSDA      | X2cSDA              | I/O | I/H                                                                                 | L or I                     | Н                         | phbsud8sm            |

| T1            | X2sCDCLK    | X2sCDCLK            | 0   | H or L/L                                                                            | Hi-z or H or L             | Н                         | phot8                |

| W4            | X2sCLK      | X2sCLK              | I/O | ULIL                                                                                | H or L or I                | L                         | phbsu100ct8sm        |

| Y4            | X2sDI       | X2sDI               | 1   |                                                                                     | -                          | -                         | phisu                |

| U1            | X2sDO       | X2sDO               | 0   | L/L                                                                                 | Hi-z or H or L             | L                         | phot8                |

| U2            | X2sLRCK     | X2sLRCK             | 1/0 | H/L/L                                                                               | H or L or I                | Pre                       | phbsu100ct8sm        |

| P3            | X97BITCLK   | X97BITCLK           | Ι   |                                                                                     | -                          | -                         | phis                 |

| N2            | X97RESETn   | X97RESETn           | 0   | L/L                                                                                 | Hi-z or H or L             | Н                         | phot8                |

| Т3            | X97SDI      | X97SDI              | Ι   | I                                                                                   | -                          | -                         | phisu                |

| P2            | X97SDO      | X97SDO              | 0   | L/L                                                                                 | Hi-z or H or L             | L                         | phot8                |

| N1            | X97SYNC     | X97SYNC             | 0   | L/L                                                                                 | Hi-z or H or L             | L                         | phot8                |

| AB5           | XadcAIN[0]  | XadcAIN[0]          | Ain | I                                                                                   | -                          | -                         | phiar10_abb          |

| AC5           | XadcAIN[1]  | XadcAIN[1]          | Ain | Ι                                                                                   | -                          | -                         | phiar10_abb          |

| AA6           | XadcAIN[2]  | XadcAIN[2]          | Ain | Ι                                                                                   | -                          | -                         | phiar10_abb          |

1-18

| Pin<br>Number | Name        | Default<br>Function | I/O | I/O state@ Reset mode<br>(Data/En/PullupEn)<br>En(L)=>output<br>PullupEn(L)=>PullUp | I/O<br>State@SLEEP<br>mode | I/O<br>State@STOP<br>mode | Cell Type<br>(24A0A) |

|---------------|-------------|---------------------|-----|-------------------------------------------------------------------------------------|----------------------------|---------------------------|----------------------|

| AC4           | XadcAIN[3]  | XadcAIN[3]          | Ain | I                                                                                   | -                          | -                         | phiar10_abb          |

| AC3           | XadcAIN[4]  | XadcAIN[4]          | Ain | I                                                                                   | -                          | -                         | phiar10_abb          |

| AA4           | XadcAIN[5]  | XadcAIN[5]          | Ain | I                                                                                   | -                          | -                         | phiar10_abb          |

| AC2           | XadcAIN[6]  | XadcAIN[6]          | Ain | I                                                                                   | -                          | -                         | phiar10_abb          |

| AB2           | XadcAIN[7]  | XadcAIN[7]          | Ain |                                                                                     | -                          | -                         | phiar10_abb          |

| AA5           | XadcAVREF   | XadcAVREF           | Ain |                                                                                     | -                          | -                         | phia_abb             |

| A3            | XciCDATA[0] | XciCDATA[0]         | Ι   | I/H/L                                                                               | -                          | · ·                       | phbsu100ct8sm        |

| C4            | XciCDATA[1] | XciCDATA[1]         | Ι   | I/H/L                                                                               | -                          | · ·                       | phbsu100ct8sm        |

| B5            | XciCDATA[2] | XciCDATA[2]         | I   | I/H/L                                                                               | -                          | . )                       | phbsu100ct8sm        |

| B6            | XciCDATA[3] | XciCDATA[3]         | Ι   | I/H/L                                                                               | - 7                        | -                         | phbsu100ct8sm        |

| C7            | XciCDATA[4] | XciCDATA[4]         | I   | I/H/L                                                                               |                            | -                         | phbsu100ct8sm        |

| D9            | XciCDATA[5] | XciCDATA[5]         | I   | I/H/L                                                                               |                            | -                         | phbsu100ct8sm        |

| C8            | XciCDATA[6] | XciCDATA[6]         | 1   | I/H/L                                                                               | -                          | _                         | phbsu100ct8sm        |

| A10           | XciCDATA[7] | XciCDATA[7]         | I   | I/H/L                                                                               | -                          | -                         | phbsu100ct8sm        |

| C3            | XciCLK      | XciCLK              | 0   | L/L                                                                                 | Hi-z or H or L             | L                         | phot12sm             |

| C6            | XciHREF     | XciHREF             | -   |                                                                                     | -                          | -                         | phis                 |

| A5            | XciPCLK     | XciPCLK             | I   |                                                                                     | -                          | -                         | phis                 |

| D4            | XciRSTn     | XciRSTn             | 0   | L/L                                                                                 | Hi-z or H or L             | Pre                       | phot8                |

| D6            | XciVSYNC    | XciVSYNC            | 1   | I                                                                                   | -                          | -                         | phis                 |

| B2            | XciYDATA[0] | XciYDATA[0]         | )   | _                                                                                   | -                          | -                         | phis                 |

| E4            | XciYDATA[1] | XciYDATA[1]         | -   |                                                                                     | -                          | -                         | phis                 |

| B3            | XciYDATA[2] | XciYDATA[2]         | Ι   |                                                                                     | -                          | -                         | phis                 |

| F4            | XciYDATA[3] | XciYDATA[3]         | Ι   | Ι                                                                                   | -                          | -                         | phis                 |

| A1            | XciYDATA[4] | XciYDATA[4]         | Ι   | Ι                                                                                   | -                          | -                         | phis                 |

| D5            | XciYDATA[5] | XciYDATA[5]         | Ι   | Ι                                                                                   | -                          | -                         | phis                 |

| B4            | XciYDATA[6] | XciYDATA[6]         | Ι   | l                                                                                   | -                          | -                         | phis                 |

| A4            | XciYDATA[7] | XciYDATA[7]         | Ι   | l                                                                                   | -                          | -                         | phis                 |

| B22           | XfALE       | XfALE               | 0   | L/L                                                                                 | Hi-z or H or L             | L                         | phot8                |

| D19           | XfCLE       | XfCLE               | 0   | L/L                                                                                 | Hi-z or H or L             | L                         | phot8                |

1-19

S3C24A0 RISC MICROPROCESSOR

| Pin<br>Number | Name                            | Default<br>Function | I/O | I/O state@ Reset<br>mode<br>(Data/En/PullupEn)<br>En(L)=>output<br>PullupEn(L)=>PullU<br>p | I/O<br>State@SLEEP<br>mode | I/O<br>State@STOP<br>mode | Cell Type<br>(24A0A) |

|---------------|---------------------------------|---------------------|-----|--------------------------------------------------------------------------------------------|----------------------------|---------------------------|----------------------|

| B23           | XfNFACYC                        | XfNFACYC            | Ι   | I                                                                                          | -                          | -                         | phis                 |

| C23           | XfNFADV                         | XfNFADV             | Ι   | ļ                                                                                          | -                          | -                         | phis                 |

| D22           | XfNFBW                          | XfNFBW              | Ι   | I                                                                                          | -                          | -                         | phis                 |

| C22           | XfNFPS                          | XfNFPS              | Ι   | -                                                                                          | -                          | -                         | phis                 |

| A23           | XfRnB[0]                        | XfRnB[0]            | Ι   | Ι                                                                                          | -                          | -                         | phisu                |

| E20           | XfRnB[1]                        | XfRnB[1]            | Ι   | I                                                                                          | -                          | -                         | phisu                |

| Y5            | XgBATFLT                        | XgBATFLT            | Ι   | Н                                                                                          | -                          | -                         | phis                 |

| AC8           | XgMONHCLK                       | XgMONHCLK           | 0   | L/L                                                                                        | Hi-z or H or L             | Ļ                         | phot8                |

| M1            | XgpIO[0]/EINT0                  | XgpIO[0]            | I/O | I/H/L                                                                                      | H or L or I                | -                         | phbsu100ct8s<br>m    |

| Y6            | XgpIO[1]/EINT1                  | XgpIO[1]            | I/O | I/H/L                                                                                      | H or L or I                | -                         | phbsu100ct8s<br>m    |

| L2            | XgpIO[10]/YMON                  | XgpIO[10]           | I/O | I/H/L                                                                                      | H or L or I                | -                         | phbsu100ct8s<br>m    |

| K1            | XgpIO[11]/EINT11                | XgpIO[11]           | I/O | I/H/L                                                                                      | H or L or I                | -                         | phbsu100ct8s<br>m    |

| L3            | XgpIO[12]/EINT12/XMON           | XgpIO[12]           | I/O | I/H/L                                                                                      | H or L or I                | -                         | phbsu100ct8s<br>m    |

| T4            | XgpIO[13]/EINT13/XPON           | XgpIO[13]           | 1/0 | I/H/L                                                                                      | H or L or I                | -                         | phbsu100ct8s<br>m    |

| K2            | XgpIO[14]/EINT14/RTC_ALMINT     | XgplO[14]           | 1/0 | I/H/L                                                                                      | H or L or I                | -                         | phbsu100ct8s<br>m    |

| R4            | XgpIO[15]/EINT15/XspiMOSI       | XgpIO[15]           | 1/0 | I/H/L                                                                                      | H or L or I                | -                         | phbsu100ct8s<br>m    |

| K3            | XgpIO[16]/EINT16/XspiMISO       | XgplO[16]           | I/O | I/H/L                                                                                      | H or L or I                | -                         | phbsu100ct8s<br>m    |

| J1            | XgpIO[17]/EINT17/XspiCLK        | XgpIO[17]           | I/O | I/H/L                                                                                      | H or L or I                | -                         | phbsu100ct8s<br>m    |

| J2            | XgpIO[18]/EINT18/XkpROW0        | XgpIO[18]           | I/O | I/H/L                                                                                      | H or L or I                | -                         | phbsu100ct8s<br>m    |

| M4            | XgpIO[19]/PWM_ECLK/XkpROW<br>1  | XgplO[19]           | I/O | I/H/L                                                                                      | H or L or I                | -                         | phbsu100ct8s<br>m    |

| R3            | XgpIO[2]/EINT2/PWM_TOUT0        | XgpIO[2]            | I/O | I/H/L                                                                                      | H or L or I                | -                         | phbsu100ct8s<br>m    |

| H1            | XgpIO[20]/PWM_TOUT0/<br>XkpROW2 | XgplO[20]           | I/O | I/H/L                                                                                      | H or L or I                | -                         | phbsu100ct8s<br>m    |

| L4            | XgpIO[21]/PWM_TOUT1/<br>XkpROW3 | XgpIO[21]           | I/O | I/H/L                                                                                      | H or L or I                | -                         | phbsu100ct8s<br>m    |

#### Table 1-2. 337-Pin FBGA Pin Assignments

1-20

Preliminary product information describes products that are in development,

Downloaded from Elcodis.com electronic components difficultions and information deconsect products that are not yet available. Specifications and information herein are subject to change without notice.

| PRELIMINARY PRO | DUCT OVERVIEW |

|-----------------|---------------|

|-----------------|---------------|

| Pin<br>Number | Name                              | Default Function | I/O | I/O state@ Reset<br>mode<br>(Data/En/PullupEn)<br>En(L)=>output<br>PullupEn(L)=>PullU<br>p | I/O<br>State@SLEEP<br>mode | I/O<br>State@STOP<br>mode | Cell Type<br>(24A0A) |

|---------------|-----------------------------------|------------------|-----|--------------------------------------------------------------------------------------------|----------------------------|---------------------------|----------------------|

| H3            | XgpIO[22]/PWM_TOUT2/XkpROW4       | XgpIO[22]        | I/O | I/H/L                                                                                      | H or L or I                | -                         | phbsu100ct8։<br>m    |

| H2            | XgpIO[23]/PWM_TOUT3/XkpCOL0       | XgpIO[23]        | I/O | I/H/L                                                                                      | H or L or I                | -                         | phbsu100ct8:<br>m    |

| G1            | XgpIO[24]/EXTDMA_REQ0/<br>XkpCOL1 | XgpIO[24]        | I/O | I/H/L                                                                                      | H or L or I                | -                         | phbsu100ct8:<br>m    |

| J3            | XgpIO[25]/EXTDMA_REQ1/<br>XkpCOL2 | XgpIO[25]        | I/O | I/H/L                                                                                      | H or L or I                | -                         | phbsu100ct8:<br>m    |

| G2            | XgpIO[26]/EXTDMA_ACK0/<br>XkpCOL3 | XgpIO[26]        | I/O | I/H/L                                                                                      | H or L or I                | -                         | phbsu100ct8:<br>m    |

| G3            | XgpIO[27]/EXTDMA_ACK1/XkpCOL4     | XgpIO[27]        | I/O | I/H/L                                                                                      | H or L or I                | -                         | phbsu100ct8:<br>m    |

| F1            | XgpIO[28]/XuCTSn1/RTC_ALMINT      | XgpIO[28]        | I/O | l/H/L                                                                                      | H or L or I                | -                         | phbsu100ct8:<br>m    |

| F2            | XgpIO[29]/XuRTSn1/IrDA_SDBW       | XgpIO[29]        | 1/0 | I/H/L                                                                                      | H or L or I                | -                         | phbsu100ct8:<br>m    |

| Y7            | XgpIO[3]/EINT3/PWM_TOUT1          | XgpIO[3]         | 1/0 | I/H/L                                                                                      | H or L or I                | -                         | phbsu100ct8:<br>m    |

| F3            | XgplO[30]/XuTXD1/lrDA_TXD         | XgpIO[30]        | 1/0 | I/H/L                                                                                      | H or L or I                | -                         | phbsu100ct8:<br>m    |

| E1            | XgplO[31]/XuRXD1/ IrDA_RXD        | XgplO[31]        | 1/0 | I/H/L                                                                                      | H or L or I                | -                         | phbsu100ct8:<br>m    |

| N3            | XgpIO[4]/EINT4/PWM_TOUT2          | XgpIO[4]         | I/O | I/H/L                                                                                      | H or L or I                | -                         | phbsu100ct8։<br>m    |

| P4            | XgpIO[5]/EINT5/ PWM_TOUT3         | XgpIO[5]         | I/O | I/H/L                                                                                      | H or L or I                | -                         | phbsu100ct8៖<br>m    |

| M2            | XgpIO[6]/EINT6/EXTDMA_REQ0        | XgpIO[6]         | I/O | I/H/L                                                                                      | H or L or I                | -                         | phbsu100ct8։<br>m    |

| L1            | XgpIO[7]/EINT7 EXTDMA_REQ1        | XgpIO[7]         | I/O | I/H/L                                                                                      | H or L or I                | -                         | phbsu100ct8։<br>m    |

| N4            | XgpIO[8]/EINT8/ EXTDMA_ACK0       | XgpIO[8]         | I/O | I/H/L                                                                                      | H or L or I                | -                         | phbsu100ct8։<br>m    |

| U4            | XgpIO[9]/EINT9 EXTDMA_ACK1        | XgpIO[9]         | I/O | I/H/L                                                                                      | H or L or I                | -                         | phbsu100ct8:<br>m    |

| AA3           | XgPWROFFn                         | XgPWROFFn        | 0   | Н                                                                                          | L                          | Н                         | phob8                |

| AA2           | XgREFCLKSEL[0]                    | XgREFCLKSEL[0]   | Ι   | Н                                                                                          | -                          | -                         | phis                 |

| AB4           | XgREFCLKSEL[1]                    | XgREFCLKSEL[1]   | I   | Н                                                                                          | -                          | -                         | phis                 |

#### Table 1-2. 337-Pin FBGA Pin Assignments

1-21

S3C24A0 RISC MICROPROCESSOR

| Pin<br>Number | Name       | Default<br>Function | I/O | I/O state@ Reset mode<br>(Data/En/PullupEn)<br>En(L)=>output<br>PullupEn(L)=>PullUp | I/O<br>State@SLEEP<br>mode | I/O<br>State@STOP<br>mode | Cell Type<br>(24A0A) |

|---------------|------------|---------------------|-----|-------------------------------------------------------------------------------------|----------------------------|---------------------------|----------------------|

| Y2            | XgTMODE[0] | XgTMODE[0]          | I   | I                                                                                   | -                          | -                         | phis                 |

| W1            | XgTMODE[1] | XgTMODE[1]          | I   | I                                                                                   | -                          | -                         | phis                 |

| R1            | XgTMODE[2] | XgTMODE[2]          | Ι   | I                                                                                   | -                          | -                         | phis                 |

| V3            | XgTMODE[3] | XgTMODE[3]          | Ι   | 1                                                                                   | -                          | -                         | phis                 |

| D10           | XjRTCK     | XjRTCK              | 0   | L                                                                                   | -                          | -                         | phob8                |

| B1            | XjTCK      | XjTCK               | Ι   | I                                                                                   | -                          | -                         | phis                 |

| D2            | XjTDI      | XjTDI               | Ι   | I                                                                                   | -                          | -                         | phisu                |

| D1            | XjTDO      | XjTDO               | 0   | I/H                                                                                 | Hi-z or H or L             | Hi-z                      | phot8                |

| C1            | XjTMS      | XjTMS               | Ι   | 1                                                                                   | -                          | -                         | phisu                |

| C2            | XjTRSTn    | XjTRSTn             | I   | I                                                                                   | -                          | -                         | phisu                |

| AA20          | XmiADR[0]  | XmiADR[0]           | I   | I/H/L                                                                               | -                          | -                         | phbsu100ct8sm        |

| AB20          | XmiADR[1]  | XmiADR[1]           | I   | I/H/L                                                                               | -                          | -                         | phbsu100ct8sm        |

| Y16           | XmiADR[10] | XmiADR[10]          | I   | I/H/L                                                                               |                            | -                         | phbsu100ct8sm        |

| Y19           | XmiADR[2]  | XmiADR[2]           | I   | I/H/L                                                                               |                            | -                         | phbsu100ct8sm        |

| AC19          | XmiADR[3]  | XmiADR[3]           | I   | I/H/L                                                                               | -                          | -                         | phbsu100ct8sm        |

| Y18           | XmiADR[4]  | XmiADR[4]           | I   | I/H/L                                                                               | -                          | -                         | phbsu100ct8sm        |

| AC15          | XmiADR[5]  | XmiADR[5]           | I   | I/H/L                                                                               | -                          | -                         | phbsu100ct8sm        |

| AA16          | XmiADR[6]  | XmiADR[6]           | I   | I/H/L                                                                               | -                          | -                         | phbsu100ct8sm        |

| AB15          | XmiADR[7]  | XmiADR[7]           | I   | I/H/L                                                                               | -                          | -                         | phbsu100ct8sm        |

| AA15          | XmiADR[8]  | XmiADR[8]           | 1   | I/H/L                                                                               | -                          | -                         | phbsu100ct8sm        |

| AC14          | XmiADR[9]  | XmiADR[9]           | 1   | I/H/L                                                                               | -                          | -                         | phbsu100ct8sm        |

| Y15           | XmiCSn     | XmiCSn              | I   |                                                                                     | -                          | -                         | phisu                |

| AB19          | XmiDATA[0] | XmiDATA[0]          | 1/0 | I/H/L                                                                               | H or L or I                | -                         | phbsu100ct8sm        |

| AC18          | XmiDATA[1] | XmiDATA[1]          | I/O | I/H/L                                                                               | H or L or I                | -                         | phbsu100ct8sm        |

| AA19          | XmiDATA[2] | XmiDATA[2]          | 1/0 | I/H/L                                                                               | H or L or I                | -                         | phbsu100ct8sm        |

| AC17          | XmiDATA[3] | XmiDATA[3]          | I/O | I/H/L                                                                               | H or L or I                | -                         | phbsu100ct8sm        |

| AB17          | XmiDATA[4] | XmiDATA[4]          | I/O | I/H/L                                                                               | H or L or I                | -                         | phbsu100ct8sm        |

| AC16          | XmiDATA[5] | XmiDATA[5]          | I/O | I/H/L                                                                               | H or L or I                | -                         | phbsu100ct8sm        |

| AA17          | XmiDATA[6] | XmiDATA[6]          | I/O | I/H/L                                                                               | H or L or I                | -                         | phbsu100ct8sm        |

| AB16          | XmiDATA[7] | XmiDATA[7]          | I/O | I/H/L                                                                               | H or L or I                | -                         | phbsu100ct8sm        |

#### Table 1-2. 337-Pin FBGA Pin Assignments

1-22

| Pin<br>Number | Name       | Default<br>Function | I/O | I/O state@ Reset mode<br>(Data/En/PullupEn)<br>En(L)=>output<br>PullupEn(L)=>PullUp | I/O<br>State@SLEEP<br>mode | I/O<br>State@STOP<br>mode | Cell Type<br>(24A0A) |

|---------------|------------|---------------------|-----|-------------------------------------------------------------------------------------|----------------------------|---------------------------|----------------------|

| AB18          | XmilRQn    | XmilRQn             | 0   | H/L                                                                                 | Hi-z or H or L             | н                         | phot8                |

| AB14          | XmiOEn     | XmiOEn              | I   | I                                                                                   | -                          | -                         | phisu                |

| AA14          | XmiWEn     | XmiWEn              | Ι   | I                                                                                   | -                          | -                         | phisu                |

| AA13          | XmsBS      | XmsBS               | 0   | L/L                                                                                 | Hi-z or H or L             | L                         | phot8                |

| Y14           | XmsPl      | XmsPI               | I   |                                                                                     | -                          | -                         | phis                 |

| AC11          | XmsSCLKO   | XmsSCLKO            | 0   | H/L                                                                                 | Hi-z or H or L             | н                         | phot8                |

| Y13           | XmsSDIO    | XmsSDIO             | I/O | I/H/L                                                                               | H or L or I                | -                         | phbsu100ct12s<br>m   |

| L23           | XpADDR[0]  | XpADDR[0]           | 0   | L/L                                                                                 | Hi-z or H or L             | Pre                       | phot12sm             |

| M22           | XpADDR[1]  | XpADDR[1]           | 0   | L/L                                                                                 | Hi-z or H or L             | Pre                       | phot12sm             |

| AC22          | XpADDR[10] | XpADDR[10]          | 0   | L/L                                                                                 | Hi-z or H or L             | Pre                       | phot12sm             |

| AB21          | XpADDR[11] | XpADDR[11]          | 0   | L/L                                                                                 | Hi-z or H or L             | Pre                       | phot12sm             |

| AC21          | XpADDR[12] | XpADDR[12]          | 0   | L/L                                                                                 | Hi-z or H or L             | Pre                       | phot12sm             |

| Y17           | XpADDR[13] | XpADDR[13]          | 0   | L/L                                                                                 | Hi-z or H or L             | Pre                       | phot12sm             |

| AC20          | XpADDR[14] | XpADDR[14]          | 0   | L/L                                                                                 | Hi-z or H or L             | Pre                       | phot12sm             |

| M20           | XpADDR[2]  | XpADDR[2]           | 0   | L/L                                                                                 | Hi-z or H or L             | Pre                       | phot12sm             |

| M23           | XpADDR[3]  | XpADDR[3]           | 0   | L/L                                                                                 | Hi-z or H or L             | Pre                       | phot12sm             |

| N21           | XpADDR[4]  | XpADDR[4]           | 0   | L/L                                                                                 | Hi-z or H or L             | Pre                       | phot12sm             |

| N22           | XpADDR[5]  | XpADDR[5]           | 0   | L/L                                                                                 | Hi-z or H or L             | Pre                       | phot12sm             |

| N23           | XpADDR[6]  | XpADDR[6]           | 0   | L/L                                                                                 | Hi-z or H or L             | Pre                       | phot12sm             |

| P22           | XpADDR[7]  | XpADDR[7]           | 0   | L/L                                                                                 | Hi-z or H or L             | Pre                       | phot12sm             |

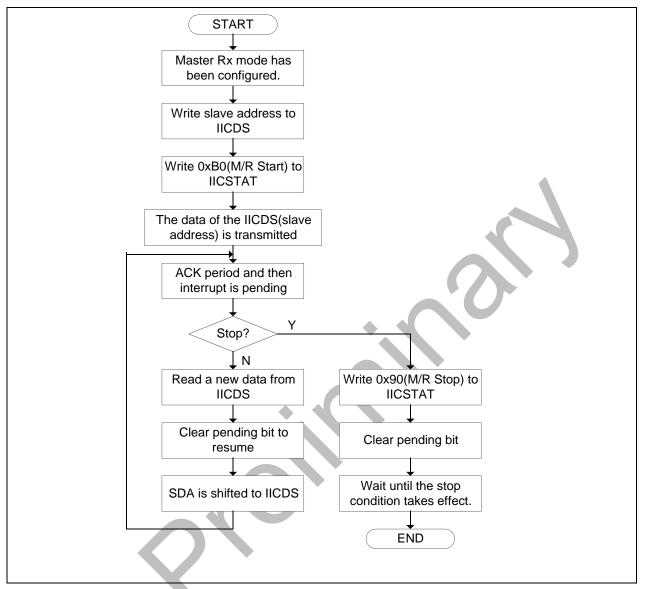

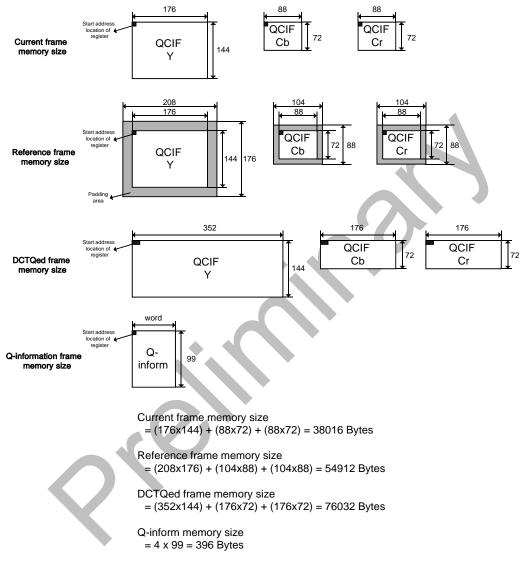

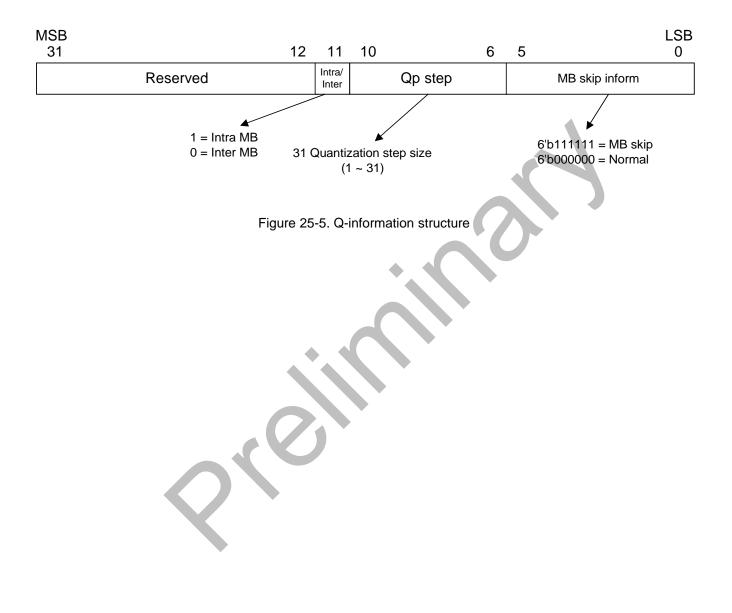

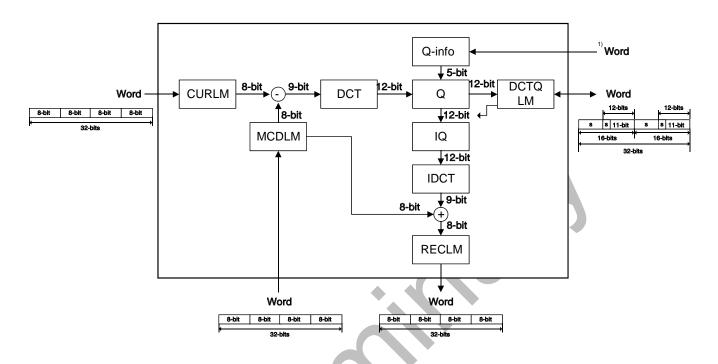

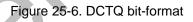

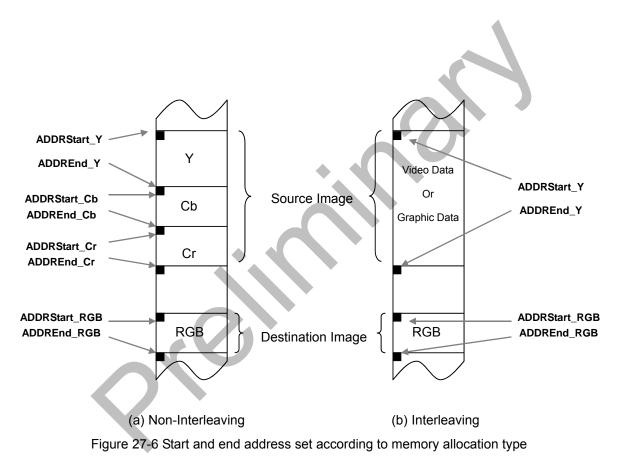

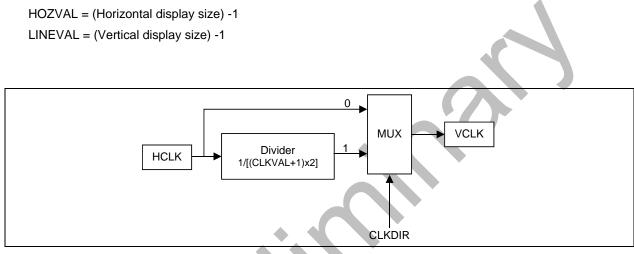

| AB23          | XpADDR[8]  | XpADDR[8]           | 0   | L/L                                                                                 | Hi-z or H or L             | Pre                       | phot12sm             |