### LM96000

# **Hardware Monitor with Integrated Fan Control**

### **General Description**

The LM96000, hardware monitor, has a two wire digital interface compatible with SMBus 2.0. Using an 8-bit  $\Sigma\Delta$  ADC, the LM96000 measures:

- the temperature of two remote diode connected transistors as well as its own die

- the VCCP, 2.5V, 3.3VSBY, 5.0V, and 12V supplies (internal scaling resistors).

To set fan speed, the LM96000 has three PWM outputs that are each controlled by one of three temperature zones. High and low PWM frequency ranges are supported. The LM96000 includes a digital filter that can be invoked to smooth temperature readings for better control of fan speed. The LM96000 has four tachometer inputs to measure fan speed. Limit and status registers for all measured values are included.

#### **Features**

- 2-wire, SMBus 2.0 compliant, serial digital interface

- 8-bit Σ∆ ADC

- Monitors VCCP, 2.5V, 3.3 VSBY, 5.0V, and 12V motherboard/processor supplies

- Monitors 2 remote thermal diodes

- Programmable autonomous fan control based on temperature readings

- Noise filtering of temperature reading for fan control

- 1.0°C digital temperature sensor resolution

- 3 PWM fan speed control outputs

- Provides high and low PWM frequency ranges

- 4 fan tachometer inputs

- Monitors 5 VID control lines

- 24-pin TSSOP package

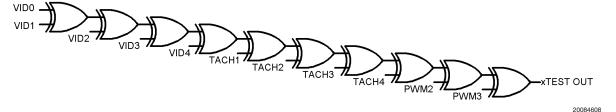

- XOR-tree test mode

### **Key Specifications**

Voltage Measurement Accuracy

Besolution

Temperature Sensor Accuracy

±2% FS (max)

8-bits, 1°C

±3°C (max)

■ Temperature Range

LM96000 Operational

Remote Temp Accuracy

O°C to +85°C

O°C to +125°C

Power Supply Voltage +3.0V to +3.6VPower Supply Current 0.53 mA

# Power Supply CurrentApplications

- Desktop PC

- Microprocessor based equipment (e.g. Base-stations, Routers, ATMs, Point of Sales)

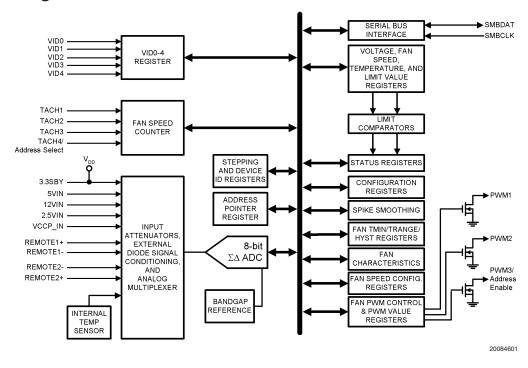

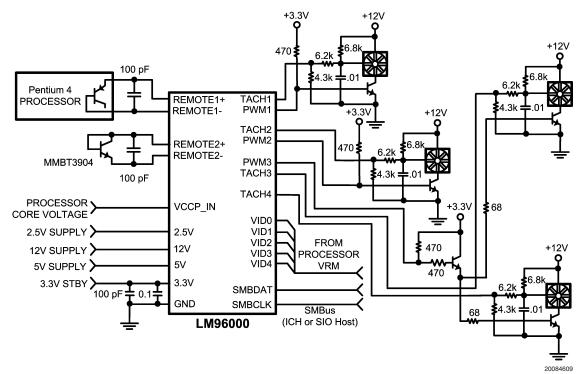

### **Block Diagram**

© 2004 National Semiconductor Corporation

DS200846

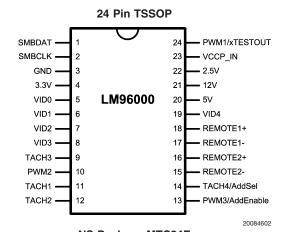

# **Connection Diagram**

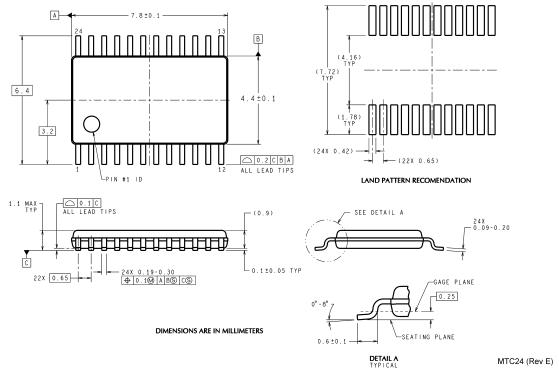

NS Package MTC24E

Top View

LM96000CIMT (61 units per rail), or

LM96000CIMTX (2500 units per tape and reel)

### **Pin Descriptions**

|                | Symbol  | Pin | Туре                        | Name and Function/Connection                                                                                                                                                                                                                                                                                                              |

|----------------|---------|-----|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SMBus          | SMBDAT  | 1   | Digital I/O<br>(Open-Drain) | System Management Bus Data. Open-drain output. 5V tolerant, SMBus 2.0 compliant.                                                                                                                                                                                                                                                          |

| SME            | SMBCLK  | 2   | Digital Input               | System Management Bus Clock. Tied to Open-drain output. 5V tolerant, SMBus 2.0 compliant.                                                                                                                                                                                                                                                 |

| (0)            | VID0    | 5   | Digital Input               | Voltage identification signal from the processor. This value is read in the VID0–VID4 Status Register.                                                                                                                                                                                                                                    |

| ) Lines        | VID1    | 6   | Digital Input               | Voltage identification signal from the processor. This value is read in the VID0–VID4 Status Register.                                                                                                                                                                                                                                    |

| Processor VID  | VID2    | 7   | Digital Input               | Voltage identification signal from the processor. This value is read in the VID0–VID4 Status Register.                                                                                                                                                                                                                                    |

| Proces         | VID3    | 8   | Digital Input               | Voltage identification signal from the processor. This value is read in the VID0-VID4 Status Register.                                                                                                                                                                                                                                    |

|                | VID4    | 19  | Digital Input               | Voltage identification signal from the processor. This value is read in the VID0-VID4 Status Register.                                                                                                                                                                                                                                    |

| Power          | 3.3V    | 4   | POWER                       | +3.3V pin. Can be powered by +3.3V Standby power if monitoring in low power states is required. This pin also serves as the analog input to monitor the 3.3V supply. This pin should be bypassed with a 0.1µf capacitor in parallel with 100pf. A bulk capacitance of approximately 10µf needs to be in the near vicinity of the LM96000. |

|                | GND     | 3   | GROUND                      | Ground for all analog and digital circuitry.                                                                                                                                                                                                                                                                                              |

| uts            | 5V      | 20  | Analog Input                | Analog input for +5V monitoring.                                                                                                                                                                                                                                                                                                          |

| Voltage Inputs | 12V     | 21  | Analog Input                | Analog input for +12V monitoring.                                                                                                                                                                                                                                                                                                         |

| tage           | 2.5V    | 22  | Analog Input                | Analog input for +2.5V monitoring.                                                                                                                                                                                                                                                                                                        |

| Vol            | VCCP_IN | 23  | Analog Input                | Analog input for VCCP (processor voltage) monitoring.                                                                                                                                                                                                                                                                                     |

# Pin Descriptions (Continued)

|                       | Symbol        | Pin | Туре               | Name and Function/Connection                                         |

|-----------------------|---------------|-----|--------------------|----------------------------------------------------------------------|

|                       | Remote1+      | 18  | Remote Thermal     | Positive input (current source) from the first remote thermal diode. |

|                       |               |     | Diode Positive     | Serves as the positive input into the A/D. Connected to              |

|                       |               |     | Input              | THERMDA pin of Pentium processor or the base of a diode              |

|                       |               |     |                    | connected MMBT3904 NPN transistor.                                   |

|                       | Remote1-      | 17  | Remote Thermal     | Negative input (current sink) from the first remote thermal diode.   |

|                       |               |     | Diode Negative     | Serves as the negative input into the A/D. Connected to              |

| σ                     |               |     | Input              | THERMDC pin of Pentium processor or the emmiter of a diode           |

| Remote                |               |     |                    | connected MMBT3904 NPN transistor.                                   |

| Rer                   | Remote2+      | 16  | Remote Thermal     | Positive input (current source) from the first remote thermal diode. |

|                       |               |     | Diode Positive     | Serves as the positive input into the A/D. Connected to              |

|                       |               |     | Output             | THERMDA pin of Pentium processor or the base of a diode              |

|                       |               |     |                    | connected MMBT3904 NPN transistor.                                   |

|                       | Remote2-      | 15  | Remote Thermal     | Negative input (current sink) from the first remote thermal diode.   |

|                       |               |     | Diode Negative     | Serves as the negative input into the A/D. Connected to              |

|                       |               |     | Input              | THERMDC pin of Pentium processor or the emmiter of a diode           |

| 10                    | T40111        |     | B                  | connected MMBT3904 NPN transistor.                                   |

| onts                  | TACH1         | 11  | Digital Input      | Input for monitoring tachometer output of fan 1.                     |

| ļ <u>i</u>            | TACH2         | 12  | Digital Input      | Input for monitoring tachometer output of fan 2.                     |

| ter                   |               |     | 19.1               |                                                                      |

| ome                   | TACH3         | 9   | Digital Input      | Input for monitoring tachometer output of fan 3.                     |

| Fan Tachometer Inputs | TACH4/Address | 14  | Digital Input      | Input for monitoring tachometer output of fan 4. If in Address       |

|                       | Select        |     | Digital Inpat      | Select Mode, determines the SMBus address of the LM96000.            |

| E                     |               |     |                    |                                                                      |

|                       | PWM1/xTest    | 24  | Digital Open-Drain | Fan speed control 1. When in XOR tree test mode, functions as        |

| <u>-</u>              | Out           |     | Output             | XOR Tree output.                                                     |

| l <b>Ť</b>            | PWM2          | 10  | Digital Open-Drain | Fan speed control 2.                                                 |

| ပိ                    |               |     | Output             |                                                                      |

| Fan Control           | PWM3/Address  | 13  | Digital Open-Drain | Fan speed control 3. Pull to ground at power on to enable            |

| <b>"</b>              | Enable        |     | Output             | Address Select Mode (Address Select pin controls SMBus               |

|                       |               |     |                    | address of the device).                                              |

### **Absolute Maximum Ratings** (Notes 1, 2)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Supply Voltage, V+ -0.5V to 6.0V Voltage on Any Digital Input or -0.5V to 6.0V Output Pin Voltage on 12V Analog Input -0.5V to 16V Voltage on 5V Analog Input -0.5V to 6.66V Voltage on Remote1+, Remote2+, -0.5V to (V+ + 0.05V) Current on Remote1-, Remote2-±1 mA -0.5V to 6.0V Voltage on Other Analog Inputs Input Current on Any Pin (Note 3) +5 mA Package Input Current (Note 3) ±20 mA Package Dissipation at T<sub>A</sub> = 25°C See (Note 5) ESD Susceptibility (Note 4) Human Body Model 2500V Machine Model 250V

Storage Temperature -65°C to +150°C

Soldering process must comply with National's reflow temperature profile specifications. Refer to www.national.com/packaging/. (Note 6)

### Operating Ratings (Notes 1, 2)

$\label{eq:local_local_local_local_local_local} \begin{tabular}{ll} LM96000 & Operating Temperature & 0 ^ C \le T_A \le +85 ^ C \\ Range & & & & & & & & & \\ Remote & Diode Temperature Range & & & & & & & & \\ Remote & Diode Temperature Range & & & & & & & & \\ Supply & Voltage & (3.3V nominal) & & & & & & & & \\ V_{IN} & Voltage & Range & & & & & & & \\ \end{tabular}$

### **DC Electrical Characteristics**

The following specifications apply for V+ = 3.0V to 3.6V, and all analog input source impedance  $R_S = 50\Omega$  unless otherwise specified in conditions. **Boldface limits apply for T<sub>A</sub> = T<sub>J</sub> over T<sub>MIN</sub> =0°C to T<sub>MAX</sub>=85°C;** all other limits T<sub>A</sub> = T<sub>J</sub>= 25°C. T<sub>A</sub> is the ambient temperature of the LM96000; T<sub>J</sub> is the junction temperature of the LM96000; T<sub>D</sub> is the thermal diode junction temperature.

| Symbol          | Parameter                                           | Conditions                                               | Typical  | Limits   | Units      |

|-----------------|-----------------------------------------------------|----------------------------------------------------------|----------|----------|------------|

|                 |                                                     |                                                          | (Note 7) | (Note 8) | (Limits)   |

| POWER SU        | PPLY CHARACTERISTICS                                |                                                          | •        | •        | •          |

|                 | Supply Current (Note 9)                             | Converting, Interface and Fans Inactive, Peak Current    | 1.8      | 3.5      | mA (max)   |

|                 |                                                     | Converting, Interface and Fans Inactive, Average Current | 0.53     |          | mA         |

|                 | Power-On Reset Threshold Voltage                    |                                                          |          | 1.6      | V (min)    |

|                 |                                                     |                                                          |          | 2.8      | V (max)    |

| TEMPERAT        | URE TO DIGITAL CONVERTER CHARACTERISTICS            | S                                                        |          |          |            |

|                 | Resolution                                          |                                                          | 1 8      |          | °C<br>Bits |

|                 | Temperature Accuracy (See (Note 10) for Thermal     | T <sub>D</sub> =25°C                                     |          | ±2.5     | °C (max)   |

|                 | Diode Processor Type)                               | T <sub>D</sub> =0°C to 100°C                             | ±1       | ±3       | °C (max)   |

|                 |                                                     | T <sub>D</sub> =100°C to 125°C                           |          | ±4       | °C (max)   |

|                 | Temperature Accuracy using Internal Diode (Note 11) |                                                          | ±1       | ±3       | °C (max)   |

| I <sub>DS</sub> | External Diode Current Source                       | High Level                                               | 188      | 280      | μA (max)   |

|                 |                                                     | Low Level                                                | 11.75    |          | μA         |

|                 | External Diode Current Ratio                        |                                                          | 16       |          |            |

| ANALOG TO       | D DIGITAL CONVERTER CHARACTERISTICS                 |                                                          | •        |          | '          |

| TUE             | Total Unadjusted Error(Note 12)                     |                                                          |          | ±2       | %FS (max)  |

| DNL             | Differential Non-linearity                          |                                                          | 1        |          | LSB        |

|                 | Power Supply Sensitivity                            |                                                          | ±1       |          | %/V        |

|                 | Total Monitoring Cycle Time (Note 13)               | All Voltage and<br>Temperature readings                  | 182      | 200      | ms (max)   |

### DC Electrical Characteristics (Continued)

The following specifications apply for V+ = 3.0V to 3.6V, and all analog input source impedance  $R_S = 50\Omega$  unless otherwise specified in conditions. **Boldface limits apply for T\_A = T\_J over T\_{MIN} = 0^{\circ}C to T\_{MAX} = 85^{\circ}C; all other limits T\_A = T\_J = 25^{\circ}C. T\_A is the ambient temperature of the LM96000; T\_J is the junction temperature of the LM96000; T\_D is the thermal diode junction temperature.**

| Symbol            | Parameter                           | Conditions                | Typical  | Limits   | Units    |

|-------------------|-------------------------------------|---------------------------|----------|----------|----------|

|                   |                                     |                           | (Note 7) | (Note 8) | (Limits) |

|                   | Input Resistance, all analog inputs |                           | 210      | 140      | kΩ (min) |

|                   |                                     |                           |          | 400      | kΩ (max) |

| DIGITAL O         | UTPUT: PWM1, PWM2, PWM3, XTESTOUT   |                           |          |          | •        |

| I <sub>OL</sub>   | Logic Low Sink Current              | V <sub>OL</sub> =0.4V     |          | 8        | mA (min) |

| V <sub>OL</sub>   | Logic Low Level                     | $I_{OUT} = +8 \text{ mA}$ |          | 0.4      | V (max)  |

| SMBUS OF          | EN-DRAIN OUTPUT: SMBDAT             |                           |          | •        | •        |

| V <sub>OL</sub>   | Logic Low Output Voltage            | $I_{OUT} = +4 \text{ mA}$ |          | 0.4V     | V (max)  |

| I <sub>OH</sub>   | High Level Output Current           | V <sub>OUT</sub> = V+     | 0.1      | 10       | μA (max) |

| SMBUS IN          | PUTS: SMBCLK. SMBDAT                |                           | ·        |          | •        |

| V <sub>IH</sub>   | Logic Input High Voltage            |                           |          | 2.1      | V (min)  |

| V <sub>IL</sub>   | Logic Input Low Voltage             |                           |          | 0.8      | V (max)  |

| V <sub>HYST</sub> | Logic Input Hysteresis Voltage      |                           | 300      |          | mV       |

| DIGITAL IN        | PUTS: ALL                           |                           |          |          |          |

| V <sub>IH</sub>   | Logic Input High Voltage            |                           |          | 2.1      | V (min)  |

| V <sub>IL</sub>   | Logic Input Low Voltage             |                           |          | 0.8      | V (max)  |

| V <sub>TH</sub>   | Logic Input Threshold Voltage       |                           | 1.5      |          | V        |

| I <sub>IH</sub>   | Logic High Input Current            | V <sub>IN</sub> = V+      | 0.005    | 10       | μA (max) |

| I <sub>IL</sub>   | Logic Low Input Current             | V <sub>IN</sub> = GND     | -0.005   | -10      | μA (max) |

| C <sub>IN</sub>   | Digital Input Capacitance           |                           | 20       |          | pF       |

### **AC Electrical Characteristics**

The following specifications apply for V+ = 3.0V to 3.6V unless otherwise specified in conditions. **Boldface limits apply for T<sub>A</sub>** =  $T_J$  over  $T_{MIN}$  =0°C to  $T_{MAX}$ =85°C; all other limits  $T_A$  = $T_J$ = 25°C.

| Symbol           | Parameter                      | Conditions          | Typical  | Limits   | Units     |

|------------------|--------------------------------|---------------------|----------|----------|-----------|

|                  |                                |                     | (Note 7) | (Note 8) | (Limits)  |

| TACHOME          | TER ACCURACY                   | '                   | 1        |          |           |

|                  | Fan Count Accuracy             |                     |          | ±10      | % (max)   |

|                  | Fan Full-Scale Count           |                     |          | 65536    | (max)     |

|                  | Fan Counter Clock Frequency    |                     | 90       |          | kHz       |

|                  | Fan Count Conversion Time      |                     | 0.7      | 1.4      | sec (max) |

| FAN PWM          | ОИТРИТ                         | •                   |          |          |           |

|                  | Frequency Setting Accuracy     |                     |          | ±10      | % (max)   |

|                  | Frequency Range                |                     | 10       |          | Hz        |

|                  |                                |                     | 30       |          | kHz       |

|                  | Duty-Cycle Range               | Low frequency range |          | 0 to 100 | % (max)   |

|                  | Duty-Cycle Resolution (8-bits) |                     | 0.390625 |          | %         |

|                  | Spin-Up Time Interval Range    |                     | 100      |          | ms ms     |

|                  |                                |                     | 4000     |          |           |

|                  | Spin-Up Time Interval Accuracy |                     |          | ±10      | % (max)   |

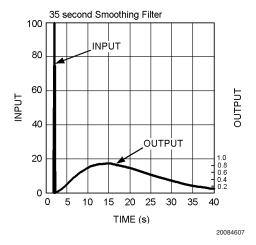

| SPIKE SM         | OOTHING FILTER                 |                     | •        |          | •         |

|                  | Time Interval Deviation        |                     |          | ±10      | % (max)   |

|                  | Time Interval Range            |                     | 35       |          | sec       |

|                  |                                |                     | 0.8      |          | sec       |

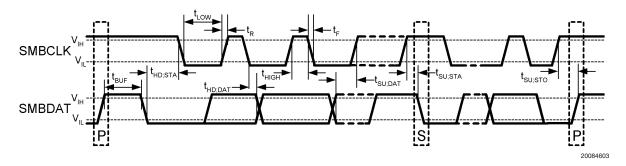

| SMBUS TI         | MING CHARACTERISTICS           |                     | ·        |          |           |

| f <sub>SMB</sub> | SMBus Operating Frequency      |                     |          | 10       | kHz (min) |

|                  |                                |                     |          | 100      | kHz (max) |

### AC Electrical Characteristics (Continued)

The following specifications apply for V+ = 3.0V to 3.6V unless otherwise specified in conditions. **Boldface limits apply for T<sub>A</sub>** =  $T_J$  over  $T_{MIN}$  =0°C to  $T_{MAX}$ =85°C; all other limits  $T_A$  = $T_J$ = 25°C.

| Symbol               | Parameter                               | Conditions | Typical  | Limits   | Units    |

|----------------------|-----------------------------------------|------------|----------|----------|----------|

|                      |                                         |            | (Note 7) | (Note 8) | (Limits) |

| f <sub>BUF</sub>     | SMBus Free Time Between Stop And        |            |          | 4.7      | μs (min) |

|                      | Start Condition                         |            |          |          |          |

| t <sub>HD_STA</sub>  | Hold Time After (Repeated) Start        |            |          | 4.0      | μs (min) |

|                      | Condition (after this period, the first |            |          |          |          |

|                      | clock is generated)                     |            |          |          |          |

| t <sub>SU:STA</sub>  | Repeated Start Condition Setup Time     |            |          | 4.7      | μs (min) |

| t <sub>su:sto</sub>  | Stop Condition Setup Time               |            |          | 4.0      | μs (min) |

| t <sub>HD:DAT</sub>  | Data Output Hold Time                   |            |          | 300      | ns (min) |

|                      |                                         |            |          | 930      | ns (max) |

| t <sub>SU:DAT</sub>  | Data Input Setup Time                   |            |          | 250      | ns (min) |

| t <sub>TIMEOUT</sub> | Data And Clock Low Time To Reset        |            |          | 25       | ms (min) |

|                      | Of SMBus Interface Logic(Note 14)       |            |          | 35       | ms (max) |

| $t_{LOW}$            | Clock Low Period                        |            |          | 4.7      | μs (min) |

| t <sub>HIGH</sub>    | Clock High Period                       |            |          | 4.0      | μs (min) |

|                      |                                         |            |          | 50       | μs (max) |

| t <sub>F</sub>       | Clock/Data Fall Time                    |            |          | 300      | ns (max) |

| t <sub>R</sub>       | Clock/Data Rise Time                    |            |          | 1000     | ns (max) |

| t <sub>POR</sub>     | Time from Power-On-Reset to             | V+ > 2.8V  |          | 500      | ms (max) |

|                      | LM96000 Reset and Operational           |            |          |          |          |

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional, but do not guarantee specific performance limits. For guaranteed specifications and test conditions, see the Electrical Characteristics. The guaranteed specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions.

Note 2: All voltages are measured with respect to GND, unless otherwise noted.

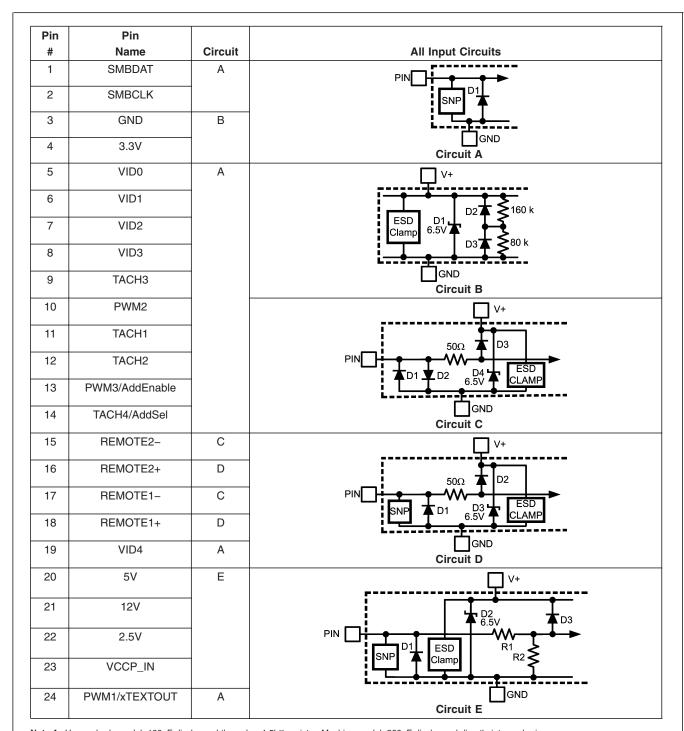

Note 3: When the input voltage  $(V_{IN})$  at any pin exceeds the power supplies  $(V_{IN} \le GND \text{ or } V_{IN} > V_{+})$ , the current at that pin should be limited to 5mA. The 20mA maximum package input current rating limits the number of pins that can safely exceed the power supplies with an input current of 5mA to four. Parasitic components and/or ESD protection circuitry are shown below for the LM96000's pins. The nominal breakdown voltage the zener is 6.5V. Care should be taken not to forward bias the parasitic diode D1 present on pins D+ and D-. Doing so by more that 50 mV may corrupt temperature measurements. SNP stands for snap-back device.

$\textbf{Note 4:} \ \ \text{Human body model, 100pF discharged through a 1.5k} \\ \Omega \ \ \text{resistor. Machine model, 200pF discharged directly into each pin.} \\$

Note 5: Thermal resistance junction-to-ambient when attached to a double-sided printed circuit board with 1 oz. foil is 113 °C/W.

Note 6: Reflow temperature profiles are different for packages containing lead (Pb) than for those that do not.

Note 7: Typicals are at  $T_A = 25^{\circ}C$  and represent most likely parametric norm.

Note 8: Limits are guaranteed to National's AOQL (Average Outgoing Quality Level).

$\textbf{Note 9:} \ \ \textbf{The average current can be calculated from the peak current using the following equation:}$

Quiescent current will not increase substantially with an SMBus transaction.

**Note 10:** The accuracy of the LM96000CIMT is guaranteed when using the thermal diode of Intel Pentium 4 90nm processors or any thermal diode with a non-ideality of 1.011 and series resistance of  $3.33\Omega$ . When using a 2N3904 type transistor as a thermal diode the error band will be typically shifted by -?\*C.

Note 11: Local temperature accuracy does not include the effects of self-heating. The rise in temperature due to self-heating is the product of the internal power dissipation of the LM96000 and the thermal resistance. See (Note 5) for the thermal resistance to be used in the self-heating calculation.

Note 12: TUE, total unadjusted error, includes ADC gain, offset, linearity and reference errors. TUE is defined as the "actual Vin" to achieve a given code transition minus the "theoretical Vin" for the same code. Therefore, a positive error indicates that the input voltage is greater than the theoretical input voltage for a given code. If the theoretical input voltage was applied to an LM96000 that has positive error, the LM96000's reading would be less than the theoretical.

Note 13: This specification is provided only to indicate how often temperature and voltage data is updated. The LM96000 can be read at any time without regard to conversion state (and will yield last conversion result).

Note 14: Holding the SMBDAT and/or SMBCLK lines Low for a time interval greater than t<sub>TIMEOUT</sub> will reset the LM96000's SMBus state machine, therefore setting the SMBDAT pin to a high impedance state.

### **Functional Description**

#### **1.0 SMBUS**

The LM96000 is compatible with devices that are compliant to the SMBus 2.0 specification. More information on this bus can be found at: http://www.smbus.org/. Compatibility of SMBus2.0 to other buses is discussed in the SMBus 2.0 specification.

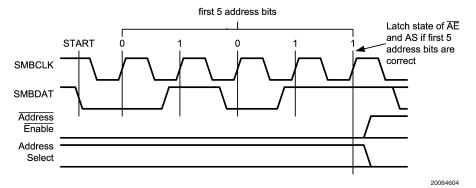

#### 1.1 Addressing

LM96000 is designed to be used primarily in desktop systems that require only one monitoring device.

If only one LM96000 is used on the motherboard, the designer should be sure that the Address Enable/PWM3 pin is High during the first SMBus communication addressing the LM96000. Address Enable/PWM3 is an open drain I/O pin that at power-on defaults to the input state of Address Enable. A maximum of 10k pull-up resistance on Address Enable/PWM3 is required to assure that the SMBus address of the device will be locked at 010 1110b, which is the default address of the LM96000.

During the first SMBus communication TACH4 and PWM3 can be used to change the SMBus address of the LM96000 to 0101101b or 0101100b. LM96000 address selection procedure:

A 10  $k\Omega$  pull-down resistor to ground on the Address Enable/PWM3 pin is required. Upon power up, the LM96000 will be placed into Address Enable mode and assign itself an SMBus address according to the state of the Address Select input. The LM96000 will latch the address during the first valid SMBus transaction in which the first five bits of the targeted address match those of the LM96000 address, 0 1011b. This feature eliminates the possibility of a glitch on the SMBus interfering with address selection. When the PWM3/Address Enable pin is not used to change the SMBus address of the LM96000, it will remain in a high state until the first communication with the LM96000. After the first SMBus transaction is completed PWM3 and TACH4 will return to normal operation.

| Address Enable | Address Select | Board Implementation                                     | SMBus Address  |

|----------------|----------------|----------------------------------------------------------|----------------|

| 0              | 0              | Pulled to ground through a 10 $k\Omega$ resistor         | 010 1100b, 2Ch |

| 0              | 1              | Pulled to 3.3V or to GND through a 10 $k\Omega$ resistor | 010 1101b, 2Dh |

| 1              | Х              | Pulled to 3.3V through a 10 kΩ resistor                  | 010 1110b, 2Eh |

In this way, up to three LM96000 devices can exists on an SMBus at any time. Multiple LM96000 devices can be used to monitor additional processors and temperature zones. When using the non-default addresses additional circuitry will be required if TACH4 and PWM3 require to function correctly. Such circuitry could consist of GPIO pins from a micro-controller. During the first communication the micro-controller would drive the Address Enable and Address Select pins to the proper state for the required address. After the first SMBus communication the micro-controller would drive it's pins into TRISTATE allowing TACH4 and PWM3 to operate correctly.

### 2.0 FAN REGISTER DEVICE SET-UP

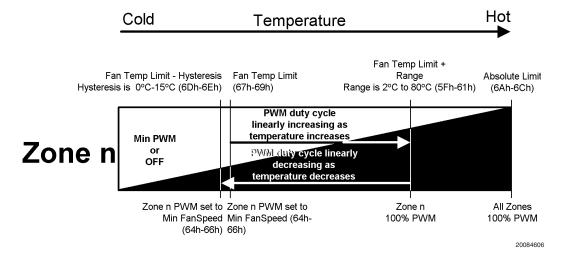

The BIOS will follow the following steps to configure the fan registers on the LM96000. The registers corresponding to each function are listed. All steps may not be necessary if default values are acceptable. Regardless of all changes made by the BIOS to the fan limit and parameter registers during configuration, the LM96000 will continue to operate based on default values until the START bit (bit 0), in the Ready/Lock/Start/Override register (address 40h), is set. Once the fan mode is updated, by setting the START bit to 1, the LM96000 will operate using the values that were set by the BIOS in the fan control limit and parameter registers (address 5Ch through 6Eh).

- 1. Set limits and parameters (not necessarily in this order):

- [5F-61h] Set PWM frequencies and auto fan control range.

- [62-63h] Set spike smoothing and min/off.

- [5C-5Eh] Set the fan spin-up delays.

- [5C-5Eh] Match each fan with a corresponding thermal zone.

- [67-69h] Set the fan temperature limits.

- [6A-6Ch] Set the temperature absolute limits.

- [64-66h] Set the PWM minimum duty cycle.

- [6D-6Eh] Set the temperature Hysteresis values.

- 2. [40h] Set bit 0 (START) to update fan control and limit register values and start fan control based on these new values.

- 3. [40h] Set bit 1 (LOCK) to lock the fan limit and parameter registers (optional).

#### 3.0 AUTO FAN CONTROL OPERATING MODE

The LM96000 includes the circuitry for automatic fan control. In Auto Fan Mode, the LM96000 will automatically adjust the PWM duty cycle of the PWM outputs. PWM outputs are assigned to a thermal zone based on the fan configuration registers. It is possible to have more than one PWM output assigned to a thermal zone. For example, PWM outputs 2 and 3, connected to two chassis fans, may both be controlled by thermal zone 2. At any time, the temperature of a zone exceeds its absolute limit, all PWM outputs will go to 100% duty cycle to provide maximum cooling to the system.

#### 4.0 REGISTER SET

| Register<br>Address | Read/<br>Write | Register<br>Name            | Bit 7<br>(MSB) | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1  | Bit 0<br>(LSB) | Default<br>Value | Lock? |

|---------------------|----------------|-----------------------------|----------------|-------|-------|-------|-------|-------|--------|----------------|------------------|-------|

| 20h                 | R              | 2.5V                        | 7              | 6     | 5     | 4     | 3     | 2     | 1      | 0              | N/A              |       |

| 21h                 | R              | VCCP_IN                     | 7              | 6     | 5     | 4     | 3     | 2     | 1      | 0              | N/A              |       |

| 22h                 | R              | 3.3V                        | 7              | 6     | 5     | 4     | 3     | 2     | 1      | 0              | N/A              |       |

| 23h                 | R              | 5V                          | 7              | 6     | 5     | 4     | 3     | 2     | 1      | 0              | N/A              |       |

| 24h                 | R              | 12V                         | 7              | 6     | 5     | 4     | 3     | 2     | 1      | 0              | N/A              |       |

| 25h                 | R              | Processor (Zone1) Temp      | 7              | 6     | 5     | 4     | 3     | 2     | 1      | 0              | N/A              |       |

| 26h                 | R              | Internal (Zone2) Temp       | 7              | 6     | 5     | 4     | 3     | 2     | 1      | 0              | N/A              |       |

| 27h                 | R              | Remote (Zone3) Temp         | 7              | 6     | 5     | 4     | 3     | 2     | 1      | 0              | N/A              |       |

| 28h                 | R              | Tach1 LSB                   | 7              | 6     | 5     | 4     | 3     | 2     | LEVEL1 | LEVEL0         | N/A              |       |

| 29h                 | R              | Tach1 MSB                   | 15             | 14    | 13    | 12    | 11    | 10    | 9      | 8              | N/A              |       |

| 2Ah                 | R              | Tach2 LSB                   | 7              | 6     | 5     | 4     | 3     | 2     | LEVEL1 | LEVEL0         | N/A              |       |

| 2Bh                 | R              | Tach2 MSB                   | 15             | 14    | 13    | 12    | 11    | 10    | 9      | 8              | N/A              |       |

| 2Ch                 | R              | Tach3 LSB                   | 7              | 6     | 5     | 4     | 3     | 2     | LEVEL1 | LEVEL0         | N/A              |       |

| 2Dh                 | R              | Tach3 MSB                   | 15             | 14    | 13    | 12    | 11    | 10    | 9      | 8              | N/A              |       |

| 2Eh                 | R              | Tach4 LSB                   | 7              | 6     | 5     | 4     | 3     | 2     | LEVEL1 | LEVEL0         | N/A              |       |

| 2Fh                 | R              | Tach4 MSB                   | 15             | 14    | 13    | 12    | 11    | 10    | 9      | 8              | N/A              |       |

| 30h                 | R/W            | Fan1 Current PWM Duty       | 7              | 6     | 5     | 4     | 3     | 2     | 1      | 0              | N/A              |       |

| 31h                 | R/W            | Fan2 Current PWM Duty       | 7              | 6     | 5     | 4     | 3     | 2     | 1      | 0              | N/A              |       |

| 32h                 | R/W            | Fan3 Current PWM Duty       | 7              | 6     | 5     | 4     | 3     | 2     | 1      | 0              | N/A              |       |

| 3Eh                 | R              | Company ID                  | 7              | 6     | 5     | 4     | 3     | 2     | 1      | 0              | 01h              |       |

| 3Fh                 | R              | Version/Stepping            | VER3           | VER2  | VER1  | VER0  | STP3  | STP2  | STP1   | STP0           | 68h              |       |

| 40h                 | R/W            | Ready/Lock/Start/Override   | RES            | RES   | RES   | RES   | OVRID | READY | LOCK   | START          | 00h              |       |

| 41h                 | R              | Interrupt Status Register 1 | ERR            | ZN3   | ZN2   | ZN1   | 5V    | 3.3V  | VCCP   | 2.5V           | 00h              |       |

| 42h                 | R              | Interrupt Status Register 2 | ERR2           | ERR1  | FAN4  | FAN3  | FAN2  | FAN1  | RES    | 12V            | 00h              |       |

| 43h                 | R              | VID0-4                      | RES            | RES   | RES   | VID4  | VID3  | VID2  | VID1   | VID0           | N/A              |       |

| 44h                 | R/W            | 2.5V Low Limit              | 7              | 6     | 5     | 4     | 3     | 2     | 1      | 0              | 00h              |       |

| 45h                 | R/W            | 2.5V High Limit             | 7              | 6     | 5     | 4     | 3     | 2     | 1      | 0              | FFh              |       |

| 46h                 | R/W            | VCCP Low Limit              | 7              | 6     | 5     | 4     | 3     | 2     | 1      | 0              | 00h              |       |

| 47h                 | R/W            | VCCP High Limit             | 7              | 6     | 5     | 4     | 3     | 2     | 1      | 0              | FFh              |       |

| 48h                 | R/W            | 3.3V Low Limit              | 7              | 6     | 5     | 4     | 3     | 2     | 1      | 0              | 00h              |       |

| Register<br>Address | Read/<br>Write | Register<br>Name                | Bit 7<br>(MSB) | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0<br>(LSB) | Default<br>Value | Lock?    |

|---------------------|----------------|---------------------------------|----------------|-------|-------|-------|-------|-------|-------|----------------|------------------|----------|

| 49h                 | R/W            |                                 | (IVISB)        | 6     | 5     | 4     | 3     | 2     | 1     | (LSB)          | FFh              |          |

| 4911<br>4Ah         | R/W            | 3.3V High Limit 5V Low Limit    | 7              | 6     | 5     | 4     | 3     | 2     | 1     | 0              | 00h              |          |

| 4Bh                 | R/W            | 5V High Limit                   | 7              | 6     | 5     | 4     | 3     | 2     | 1     | 0              | FFh              |          |

| 4Ch                 | R/W            | 12V Low Limit                   | 7              | 6     | 5     | 4     | 3     | 2     | 1     | 0              | 00h              |          |

|                     | R/W            |                                 | 7              | 6     |       | 4     |       |       |       |                | FFh              |          |

| 4Dh                 |                | 12V High Limit                  |                |       | 5     |       | 3     | 2     | 1     | 0              |                  |          |

| 4Eh                 | R/W            | Processor (Zone1) Low<br>Temp   | 7              | 6     | 5     | 4     | 3     | 2     | 1     | 0              | 81h              |          |

| 4Fh                 | R/W            | Processor (Zone1) High<br>Temp  | 7              | 6     | 5     | 4     | 3     | 2     | 1     | 0              | 7Fh              |          |

| 50h                 | R/W            | Internal (Zone2) Low<br>Temp    | 7              | 6     | 5     | 4     | 3     | 2     | 1     | 0              | 81h              |          |

| 51h                 | R/W            | Internal (Zone2) High<br>Temp   | 7              | 6     | 5     | 4     | 3     | 2     | 1     | 0              | 7Fh              |          |

| 52h                 | R/W            | Remote (Zone3) Low<br>Temp      | 7              | 6     | 5     | 4     | 3     | 2     | 1     | 0              | 81h              |          |

| 53h                 | R/W            | Remote (Zone3) High<br>Temp     | 7              | 6     | 5     | 4     | 3     | 2     | 1     | 0              | 7Fh              |          |

| 54h                 | R/W            | Tach1 Minimum LSB               | 7              | 6     | 5     | 4     | 3     | 2     | 1     | 0              | FFh              |          |

| 55h                 | R/W            | Tach1 Minimum MSB               | 15             | 14    | 13    | 12    | 11    | 10    | 9     | 8              | FFh              |          |

| 56h                 | R/W            | Tach2 Minimum LSB               | 7              | 6     | 5     | 4     | 3     | 2     | 1     | 0              | FFh              |          |

| 57h                 | R/W            | Tach2 Minimum MSB               | 15             | 14    | 13    | 12    | 11    | 10    | 9     | 8              | FFh              |          |

| 58h                 | R/W            | Tach3 Minimum LSB               | 7              | 6     | 5     | 4     | 3     | 2     | 1     | 0              | FFh              |          |

| 59h                 | R/W            | Tach3 Minimum MSB               | 15             | 14    | 13    | 12    | 11    | 10    | 9     | 8              | FFh              |          |

| 5Ah                 | R/W            | Tach4 Minimum LSB               | 7              | 6     | 5     | 4     | 3     | 2     | 1     | 0              | FFh              |          |

| 5Bh                 | R/W            | Tach4 Minimum MSB               | 15             | 14    | 13    | 12    | 11    | 10    | 9     | 8              | FFh              |          |

| 5Ch                 | R/W            | Fan1 Configuration              | ZON2           | ZON1  | ZON0  | INV   | RES   | SPIN2 | SPIN1 | SPIN0          | 62h              | <u></u>  |

| 5Dh                 | R/W            | Fan2 Configuration              | ZON2           | ZON1  | ZON0  | INV   | RES   | SPIN2 | SPIN1 | SPIN0          | 62h              | <u></u>  |

| 5Eh                 | R/W            | Fan3 Configuration              | ZON2           | ZON1  | ZON0  | INV   | RES   | SPIN2 | SPIN1 | SPIN0          | 62h              | <u></u>  |

| 5Fh                 | R/W            | Fan1 Range/Frequency            | RAN3           | RAN2  | RAN1  | RAN0  | HLFRQ | FRQ2  | FRQ1  | FRQ0           | C4h              | <u></u>  |

| 60h                 | R/W            | Fan2 Range/Frequency            | RAN3           | RAN2  | RAN1  | RAN0  | HLFRQ | FRQ2  | FRQ1  | FRQ0           | C4h              | <u></u>  |

| 61h                 | R/W            | Fan3 Range/Frequency            | RAN3           | RAN2  | RAN1  | RAN0  | HLFRQ | FRQ2  | FRQ1  | FRQ0           | C4h              | 1        |

| 62h                 | R/W            | Min/Off, Zone1 Spike Smoothing  | OFF3           | OFF2  | OFF1  | RES   | ZN1E  | ZN1-2 | ZN1-1 | ZN1-0          | 00H              | ~        |

| 63h                 | R/W            | Zone2, Zone3 Spike<br>Smoothing | ZN2E           | ZN2-2 | ZN2-1 | ZN2-0 | ZN3E  | ZN3-2 | ZN3-1 | ZN3-0          | 00h              | ~        |

| 64h                 | R/W            | Fan1 PWM Minimum                | 7              | 6     | 5     | 4     | 3     | 2     | 1     | 0              | 80h              | <b>/</b> |

| 65h                 | R/W            | Fan2 PWM Minimum                | 7              | 6     | 5     | 4     | 3     | 2     | 1     | 0              | 80h              | <b>/</b> |

| 66h                 | R/W            | Fan3 PWM Minimum                | 7              | 6     | 5     | 4     | 3     | 2     | 1     | 0              | 80h              | <b>/</b> |

| 67h                 | R/W            | Zone1 Fan Temp Limit            | 7              | 6     | 5     | 4     | 3     | 2     | 1     | 0              | 5Ah              | <b>/</b> |

| 68h                 | R/W            | Zone2 Fan Temp Limit            | 7              | 6     | 5     | 4     | 3     | 2     | 1     | 0              | 5Ah              | <i>I</i> |

| 69h                 | R/W            | Zone3 Fan Temp Limit            | 7              | 6     | 5     | 4     | 3     | 2     | 1     | 0              | 5Ah              | <i>I</i> |

| 6Ah                 | R/W            | Zone1 Temp Absolute Limit       | 7              | 6     | 5     | 4     | 3     | 2     | 1     | 0              | 64h              | /        |

| 6Bh                 | R/W            | Zone2 Temp Absolute Limit       | 7              | 6     | 5     | 4     | 3     | 2     | 1     | 0              | 64h              | ~        |

| 6Ch                 | R/W            | Zone3 Temp Absolute<br>Limit    | 7              | 6     | 5     | 4     | 3     | 2     | 1     | 0              | 64h              | ~        |

| 6Dh                 | R/W            | Zone1, Zone2 Hysteresis         | H1-3           | H1-2  | H1-1  | H1-0  | H2-3  | H2-2  | H2-1  | H2-0           | 44h              | <b>/</b> |

| 6Eh                 | R/W            | Zone3 Hysteresis                | H3-3           | H3-2  | H3-1  | H3-0  | RES   | RES   | RES   | RES            | 40h              | 1        |

| Register | Read/ | Register             | Bit 7 | Bit 6 | Bit 5  | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Default | Lock?    |

|----------|-------|----------------------|-------|-------|--------|--------|-------|-------|-------|-------|---------|----------|

| Address  | Write | Name                 | (MSB) |       |        |        |       |       |       | (LSB) | Value   |          |

| 6Fh      | R/W   | XOR Test Tree Enable | RES   | RES   | RES    | RES    | RES   | RES   | RES   | XEN   | 00h     | <b>/</b> |

| 74h      | R/W   | Tach Monitor Mode    | RES   | RES   | T3/4-1 | T3/4-0 | T2-1  | T2-0  | T1-1  | T1-0  | 00h     |          |

| 75h      | R/W   | Fan Spin-up Mode     | RES   | RES   | RES    | RES    | RES   | PWM3  | PWM2  | PWM1  | 7h      | <b>/</b> |

|          |       |                      |       |       |        |        |       | SU    | SU    | SU    |         |          |

Note: Reserved bits will always return 0 when read.

#### 4.1 Register 20-24h: Voltage Reading

| Register<br>Address | Read/<br>Write | Register<br>Name | Bit 7<br>(MSB) | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0<br>(LSB) | Default<br>Value |

|---------------------|----------------|------------------|----------------|-------|-------|-------|-------|-------|-------|----------------|------------------|

| 20h                 | R              | 2.5V             | 7              | 6     | 5     | 4     | 3     | 2     | 1     | 0              | N/A              |

| 21h                 | R              | VCCP             | 7              | 6     | 5     | 4     | 3     | 2     | 1     | 0              | N/A              |

| 22h                 | R              | 3.3V             | 7              | 6     | 5     | 4     | 3     | 2     | 1     | 0              | N/A              |

| 23h                 | R              | 5V               | 7              | 6     | 5     | 4     | 3     | 2     | 1     | 0              | N/A              |

| 24h                 | R              | 12V              | 7              | 6     | 5     | 4     | 3     | 2     | 1     | 0              | N/A              |

The Register Names difine the typical input voltage at which the reading is 3/4 full scale or C0h.

The Voltage Reading registers are updated automatically by the LM96000 at a minimum frequency of 4 Hz. These registers are read only — a write to these registers has no effect.

#### 4.2 Register 25-27h: Temperature Reading

| Register | Read/ | Register               | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Default |

|----------|-------|------------------------|-------|-------|-------|-------|-------|-------|-------|-------|---------|

| Address  | Write | Name                   | (MSB) |       |       |       |       |       |       | (LSB) | Value   |

| 25h      | R     | Processor (Zone1) Temp | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     | N/A     |

| 26h      | R     | Internal (Zone2) Temp  | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     | N/A     |

| 27h      | R     | Remote (Zone3) Temp    | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     | N/A     |

The Temperature Reading registers reflect the current temperatures of the internal and remote diodes. Processor (Zone1) Temp register reports the temperature measured by the thermal diode connected to the Remote1– and Remote1+ pins, Remote (Zone3) Temp register reports the temperature measured by the thermal diode connected to the the Remote2– and Remote2+ pins, and the Internal (Zone2) Temp register reports the temperature measured by the internal (junction) temperature sensor. Temperatures are represented as 8 bit, 2's complement, signed numbers, in Celsius, as shown below in *Table 1*. The Temperature Reading register will return a value of 80h if the remote diode pins are not used by the board designer or are not functioning properly. This reading will cause the zone limit bit(s) (bits 6 and 4) in the Interrupt Status Register (41h) and the remote diode fault status bit(s) (bit 6 or 7) in the Interrupt Status Register 2 (42h) to be set. The Temperature Reading registers are updated automatically by the LM96000 at a minimum frequency of 4 Hz. These registers are read only — a write to these registers has no effect.

TABLE 1. Temperature vs Register Reading

| Temperature | Reading (Dec) | Reading (Hex) |

|-------------|---------------|---------------|

| −127°C      | -127          | 81h           |

|             |               |               |

|             |               |               |

|             |               |               |

| −50°C       | -50           | CEh           |

TABLE 1. Temperature vs Register Reading (Continued)

| Temperature    | Reading (Dec) | Reading (Hex) |

|----------------|---------------|---------------|

|                |               |               |

| •              | •             |               |

|                |               |               |

| 0°C            | 0             | 00h           |

|                |               |               |

| •              | •             |               |

|                |               |               |

| 127°C          | 127           | 7Fh           |

| (SENSOR ERROR) |               | 80h           |

#### 4.3 Register 28-2Fh: Fan Tachometer Reading

| Register<br>Address | Read/<br>Write | Register<br>Name | Bit 7<br>(MSB) | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1  | Bit 0<br>(LSB) | Default<br>Value |

|---------------------|----------------|------------------|----------------|-------|-------|-------|-------|-------|--------|----------------|------------------|

| 28h                 | R              | Tach1 LSB        | 7              | 6     | 5     | 4     | 3     | 2     | LEVEL1 | LEVEL0         | N/A              |

| 29h                 | R              | Tach1 MSB        | 15             | 14    | 13    | 12    | 11    | 10    | 9      | 8              | N/A              |

| 2Ah                 | R              | Tach2 LSB        | 7              | 6     | 5     | 4     | 3     | 2     | LEVEL1 | LEVEL0         | N/A              |

| 2Bh                 | R              | Tach2 MSB        | 15             | 14    | 13    | 12    | 11    | 10    | 9      | 8              | N/A              |

| 2Ch                 | R              | Tach3 LSB        | 7              | 6     | 5     | 4     | 3     | 2     | LEVEL1 | LEVEL0         | N/A              |

| 2Dh                 | R              | Tach3 MSB        | 15             | 14    | 13    | 12    | 11    | 10    | 9      | 8              | N/A              |

| 2Eh                 | R              | Tach4 LSB        | 7              | 6     | 5     | 4     | 3     | 2     | LEVEL1 | LEVEL0         | N/A              |

| 2Fh                 | R              | Tach4 MSB        | 15             | 14    | 13    | 12    | 11    | 10    | 9      | 8              | N/A              |

The Fan Tachometer Reading registers contain the number of 11.111 µs periods (90 kHz) between full fan revolutions. The results are based on the time interval of two tachometer pulses, since most fans produce two tachometer pulses per full revolution. These registers will be updated at least once every second.

The value, for each fan, is represented by a 16-bit unsigned number.

The Fan Tachometer Reading registers will always return an accurate fan tachometer measurement, even when a fan is disabled or non-functional.

The least two significant bits (LEVEL1 and LEVEL2) of the least significant byte are used to indicate the accuracy level of the tachometer reading. The accuracy ranges from most to least accurate. [LEVEL1:LEVEL2]=11indicates a most accurate value, [LEVEL1:LEVEL2]=01 indicates the least accurate value and [LEVEL1:LEVEL2]=00 is reserved for future use.

FF FFh indicates that the fan is not spinning, or that the tachometer input is not connected to a valid signal. These registers are read only — a write to these registers has no effect.

When the LSByte of the LM96000 16-bit register is read, the other byte (MSByte) is latched at the current value until it is read. At the end of the MSByte read the Fan Tachometer Reading registers are updated.

During spin-up, the PWM duty cycle reported is 0%.

#### 4.4 Register 30-32h: Current PWM Duty

| Register | Read/ | Register              | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Default |

|----------|-------|-----------------------|-------|-------|-------|-------|-------|-------|-------|-------|---------|

| Address  | Write | Name                  | (MSB) |       |       |       |       |       |       | (LSB) | Value   |

| 30h      | R/W   | Fan1 Current PWM Duty | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     | N/A     |

| 31h      | R/W   | Fan2 Current PWM Duty | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     | N/A     |

| 32h      | R/W   | Fan3 Current PWM Duty | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     | N/A     |

The Current PWM Duty registers store the current duty cycle at each PWM output. At initial power-on, the PWM duty cycle is 100% and thus, when read, this register will return FFh. After the Ready/Lock/Start/Override register Start bit is set, this register and the PWM signals will be updated based on the algorithm described in the Auto Fan Control Operating Mode section.

When read, the Current PWM Duty registers return the current PWM duty cycle. These registers are read only unless the fan is in manual (test) mode, in which case a write to these registers will directly control the PWM duty cycle for each fan. The PWM duty cycle is represented as shown in the following table.

| <b>Current Duty</b> | Value (Decimal) | Value (Hex) |

|---------------------|-----------------|-------------|

| 0%                  | 0               | 00h         |

| Current Duty | Value (Decimal) | Value (Hex) |

|--------------|-----------------|-------------|

| 0.3922%      | 1               | 01h         |

|              |                 |             |

|              |                 |             |

|              |                 |             |

| 25.098%      | 64              | 40h         |

|              |                 |             |

|              |                 |             |

|              |                 |             |

| 50.196%      | 128             | 80h         |

|              |                 |             |

|              |                 |             |

|              |                 |             |

| 100%         | 255             | FFh         |

### 4.5 Register 3Eh: Company ID

| Register<br>Address | Read/<br>Write | Register<br>Name | Bit 7<br>(MSB) | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0<br>(LSB) | Default<br>Value |

|---------------------|----------------|------------------|----------------|-------|-------|-------|-------|-------|-------|----------------|------------------|

| 3Eh                 | R              | Company ID       | 7              | 6     | 5     | 4     | 3     | 2     | 1     | 0              | 01h              |

The company ID register contains the company identification number. For National Semiconductor this is 01h. This number is assigned by Intel and is a method for uniquely identifying the part manufacturer. This register is read only — a write to this register has no effect.

### 4.6 Register 3Fh: Version/Stepping

| Register<br>Address | Read/<br>Write | Register<br>Name | Bit 7<br>(MSB) | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0<br>(LSB) | Default<br>Value |

|---------------------|----------------|------------------|----------------|-------|-------|-------|-------|-------|-------|----------------|------------------|

| 3Fh                 | R              | Version/Stepping | VER3           | VER2  | VER1  | VER0  | STP3  | STP2  | STP1  | STP0           | 68h              |

The four least significant bits of the Version/Stepping register [3.0] contain the current stepping of the LM96000 silicon. The four most significant bits [7.4] reflect the LM96000 base device number when set to a value of 0110b. For the LM96000, this register will read 01101000b (68h). Bit 3 of the stepping field is set to indicate that the LM96000 is a super-set of the LM85 family of products.

The register is used by application software to identify which device in the hardware monitor family of ASICs has been implemented in the given system. Based on this information, software can determine which registers to read from and write to. Further, application software may use the current stepping to implement work-arounds for bugs found in a specific silicon stepping.

This register is read only — a write to this register has no effect.

#### 4.7 Register 40h: Ready/Lock/Start/Override

| Register<br>Address | Read/<br>Write | Register<br>Name          | Bit 7<br>(MSB) | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0<br>(LSB) | Default<br>Value |

|---------------------|----------------|---------------------------|----------------|-------|-------|-------|-------|-------|-------|----------------|------------------|

|                     |                |                           | (              |       |       |       |       |       |       | ()             |                  |

| 40h                 | R/W            | Ready/Lock/Start/Override | RES            | RES   | RES   | RES   | OVRID | READY | LOCK  | START          | 00h              |

| Bit | Name     | R/W | Default | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----|----------|-----|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | START    | R/W | 0       | When software writes a 1 to this bit, the LM96000 fan monitoring and PWM output control functions will use the values set in the fan control limit and parameter registers (address 5Ch through 6Eh). Before this bit is set, the LM96000 will not update the used register values, the default values will remain in effect. Whenever this bit is set to 0, the LM96000 fan monitoring and PWM output control functions use the default fan limits and parameters, regardless of the current values in the limit and parameter registers (5C through 6Eh). The LM96000 will preserve the values currently stored in the limit and parameter registers when this bit is set or cleared. This bit is not effected by the state of the Lock bit.  It is expected that all limit and parameter registers will be set by BIOS or application software prior to setting this bit. |

| 1   | LOCK     | R/W | 0       | Setting this bit to 1 locks specified limit and parameter registers. Once this bit is set, limit and parameter registers become read only and will remain locked until the device is powered off. This register bit becomes read only once it is set.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2   | READY    | R   | 0       | The LM96000 sets this bit automatically after the part is fully powered up, has completed the power-up-reset process, and after all A/D converters are properly functioning.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 3   | OVRID    | R/W |         | If this bit is set to 1, all PWM outputs will go to 100% duty cycle regardless of whether or not the lock bit is set. The OVRID bit has precedence over the disabled mode. Therefore, when OVRID is set the PWM will go to 100% even if the PWM is in the disabled mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 4–7 | Reserved | R   | 0       | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

#### 4.8 Register 41h: Interrupt Status Register 1

| Register<br>Address | Read/<br>Write | Register<br>Name   | Bit 7<br>(MSB) | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0<br>(LSB) | Default<br>Value |

|---------------------|----------------|--------------------|----------------|-------|-------|-------|-------|-------|-------|----------------|------------------|

| 41h                 | R              | Interrupt Status 1 | ERR            | ZN3   | ZN2   | ZN1   | 5V    | 3.3V  | VCCP  | 2.5V           | 00h              |

The Interrupt Status Register 1 bits will be automatically set, by the LM96000, whenever a fault condition is detected. A fault condition is detected whenever a measured value is outside the window set by its limit registers. ZN3 and ZN1 bits will be set when a diode fault condition, such as a disconect or short, is detected. More than one fault may be indicated in the interrupt register when read. This register will hold a set bit(s) until the event is read by software. The contents of this register will be cleared (set to 0) automatically by the LM96000 after it is read by software, if the fault condition is no longer exists. Once set, the Interrupt Status Register 1 bits will remain set until a read event occurs, even if the fault condition no longer exists

This register is read only — a write to this register has no effect.

| Bit | Name       | R/W | Default | Description                                                                 |

|-----|------------|-----|---------|-----------------------------------------------------------------------------|

| 0   | 2.5V_Error | R   | 0       | The LM96000 automatically sets this bit to 1 when the 2.5V input voltage    |

|     |            |     |         | is less than or equal to the limit set in the 2.5V Low Limit register or    |

|     |            |     |         | greater than the limit set in the 2.5V High Limit register.                 |

| 1   | VCCP_Error | R   | 0       | The LM96000 automatically sets this bit to 1 when the VCCP input voltage    |

|     |            |     |         | is less than or equal to the limit set in the VCCP Low Limit register or    |

|     |            |     |         | greater than the limit set in the VCCP High Limit register.                 |

| 2   | 3.3V_Error | R   | 0       | The LM96000 automatically sets this bit to 1 when the 3.3V input voltage    |

|     |            |     |         | is less than or equal to the limit set in the 3.3V Low Limit register or    |

|     |            |     |         | greater than the limit set in the 3.3V High Limit register.                 |

| 3   | 5V_Error   | R   | 0       | The LM96000 automatically sets this bit to 1 when the 5V input voltage is   |

|     |            |     |         | less than or equal to the limit set in the 5V Low Limit register or greater |

|     |            |     |         | than the limit set in the 5V High Limit register.                           |

| Bit | Name                          | R/W | Default | Description                                                                                                                                                                                                                                                                                                                         |

|-----|-------------------------------|-----|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4   | Zone 1 Limit<br>Exceeded      | R   | 0       | The LM96000 automatically sets this bit to 1 when the temperature input measured by the Remote1– and Remote1+ inputs is less than or equal to the limit set in the Processor (Zone1) Low Temp register or more than the limit set in the Processor (Zone1) High Temp register. This bit will be set when a diode fault is detected. |

| 5   | Zone 2 Limit<br>Exceeded      | R   | 0       | The LM96000 automatically sets this bit to 1 when the temperature input measured by the internal temperature sensor is less than or equal to the limit set in the Internal (Zone2) Low Temp register or greater than the limit set in the Internal (Zone2) High Temp register.                                                      |

| 6   | Zone 3 Limit<br>Exceeded      | R   | 0       | The LM96000 automatically sets this bit to 1 when the temperature input measured by the Remote2– and Remote2+ inputs is less than or equal to the limit set in the Internal (Zone2) Low Temp register or greater than the limit set in the Remote (Zone3) High Temp register. This bit will be set when a diode fault is detected.  |

| 7   | Error in Status<br>Register 2 | R   | 0       | If there is a set bit in Status Register 2, this bit will be set to 1.                                                                                                                                                                                                                                                              |

### 4.9 Register 42h: Interrupt Status Register 2

| Register | Read/ | Register                    | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Default |

|----------|-------|-----------------------------|-------|-------|-------|-------|-------|-------|-------|-------|---------|

| Address  | Write | Name                        | (MSB) |       |       |       |       |       |       | (LSB) | Value   |

| 42h      | R     | Interrupt Status Register 2 | ERR2  | ERR1  | FAN4  | FAN3  | FAN2  | FAN1  | RES   | 12V   | 00h     |

The Interrupt Status Register 2 bits will be automatically set, by the LM96000, whenever a fault condition is detected. Interrupt Status Register 2 identifies faults caused by temperature sensor error, fan speed droping below minimum set by the tachometer minimum register, the 12V input voltage going outside the window set by its limit registers. Interrupt Status Register 2 will hold a set bit until the event is read by software. The contents of this register will be cleared (set to 0) automatically by the LM96000 after it is ready by software, if fault condition no longer exists. Once set, the Interrupt Status Register 2 bits will remain set until a read event occurs, even if the fault no longer exists

This register is read only — a write to this register has no effect.

| Bit | Name                    | R/W | Default | Description                                                                                                                                                                                                                                      |

|-----|-------------------------|-----|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | +12V_Error              | R   | 0       | The LM96000 automatically sets this bit to 1 when the 12V input voltage either falls below the limit set in the 12V Low Limit register or exceeds the limit set in the 12V High Limit register.                                                  |

| 1   | Reserved                | R   | 0       | Reserved                                                                                                                                                                                                                                         |

| 2   | Fan1 Stalled            | R   | 0       | The LM96000 automatically sets this bit to 1 when the TACH1 input reading is above the value set in the Tach1 Minimum MSB and LSB registers.                                                                                                     |

| 3   | Fan2 Stalled            | R   | 0       | The LM96000 automatically sets this bit to 1 when the TACH2 input reading is above the value set in the Tach2 Minimum MSB and LSB registers.                                                                                                     |