# 82562ET 10/100 Mbps Platform LAN Connect (PLC)

**Networking Silicon**

#### **Datasheet**

## **Product Features**

- IEEE 802.3 10BASE-T/100BASE-TX compliant physical layer interface

- IEEE 802.3u Auto-Negotiation support

- Digital Adaptive Equalization control

- Link status interrupt capability

- XOR tree mode support

- 3-port LED support (speed, link and activity)

- 10BASE-T auto-polarity correction

- LAN Connect Interface

- Diagnostic loopback mode

- 1:1 transmit transformer ratio support

- Low power (less than 300 mW in active transmit mode)

- Reduced power in "unplugged mode" (less than 50 mW)

- Automatic detection of "unplugged mode"

- 3.3 V device

- 48-pin Shrink Small Outline Package

Information in this document is provided in connection with Intel® products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel® products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The 82562ET PLC may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Copyright © 2003, Intel Corporation

\* Other brands and names are the property of their respective owners.

## Revision History

| Revision | Revision Date | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.3      | March 2003    | Added product ordering code in Section 1.0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1.2      | October 2001  | Removed confidential status.  Removed sections: "Physical Layer Interface Functionality" and "Platform LAN Connect".  Changed "Electrical and Timing Specifications" section to "Voltage and Temperature Specifications" and removed timing specifications.                                                                                                                                                                                                                                                                                                      |

| 1.1      | June 2000     | Advance Information Datasheet release (Intel Confidential).  On cover page, replaced Boundary Scan Support with XOR tree mode support. Added bullet for LAN Connect I/F.  Pg. 3, added a Solution Block Diagram as included in OR-2338 Pg. 4 but replaced EM with ET in diagram.  Pg. 11, removed Figure 4, "NRZ to MLT-3 Encoding Diagram".  Pg. 35, changed the Rev. number on the 82562 Pinout symbol to 1.0.                                                                                                                                                 |

| 1.0      | May 2000      | <ul> <li>Advance Information Datasheet release (Intel Secret).</li> <li>Modified Table 1 "82562ET Hardware Configuration" to add one row for XOR Tree and include column for comments.</li> <li>Updated the descrition of the Activity LED signal in Section 3.6, "LED Pins".</li> <li>Revised Section 3.7, "Miscellaneous Control Pins" to reflect references to Table 1 "82562ET Hardware Configuration".</li> <li>Updated Section 4.0, "Voltage and Temperature Specifications".</li> <li>Replaced diagrams in Section 5.1, "Package Information".</li> </ul> |

| 0.6      | Nov. 1999     | Corrected Figure 4 "NRZ to MLT-3 Encoding Diagram on Pg. 11 to reflect correct signal transitions.  Removed "10BASE-T Error Detection and Reporting" section since the 82562 does not do 10BASE-T error reporting.                                                                                                                                                                                                                                                                                                                                               |

| 0.55     | Sept. 1999    | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

iv Datasheet

| 1.0 | Introd                                               | uction                                                                                                                                                                                      | 1              |  |  |  |

|-----|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--|--|--|

|     | 1.1<br>1.2<br>1.3                                    | OverviewFeatures                                                                                                                                                                            | 1              |  |  |  |

| 2.0 | 82562                                                | PET Architectural Overview                                                                                                                                                                  | 3              |  |  |  |

| 3.0 | 82562                                                | 2ET Signal Descriptions                                                                                                                                                                     | 5              |  |  |  |

|     | 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8 | Signal Type Definitions Twisted Pair Ethernet (TPE) Pins External Bias Pins Clock Pins Platform LAN Connect Interface Pins LED Pins Miscellaneous Control Pins Power and Ground Connections |                |  |  |  |

| 4.0 | Voltag<br>4.1<br>4.2                                 | ge and Temperature Specifications  Absolute Maximum Ratings                                                                                                                                 | 99<br>99<br>10 |  |  |  |

| 5.0 | Packa<br>5.1<br>5.2                                  | Package Information                                                                                                                                                                         | 13<br>14       |  |  |  |

vi Datasheet

## 1.0 Introduction

#### 1.1 Overview

The Intel<sup>®</sup> 82562ET is a highly-integrated Platform LAN Connect device designed for 10 or 100 Mbps Ethernet systems. It is based on the IEEE 10BASE-T and 100BASE-TX standards. The IEEE 802.3u standard for 100BASE-TX defines networking over two pairs of Category 5 unshielded twisted pair cable or Type 1 shielded twisted pair cable.

The 82562ET complies with the IEEE 802.3u Auto-Negotiation standard and the IEEE 802.3x Full Duplex Flow Control standard. The 82563ET also includes a PHY interface compliant to the current platform LAN connect interface.

#### 1.2 Features

- IEEE 802.3 10BASE-T/100BASE-TX compliant physical layer interface

- IEEE 802.3u Auto-Negotiation support

- Digital Adaptive Equalization control

- · Link status interrupt capability

- XOR Tree mode support for board testing

- 3-port LED support (speed, link and activity)

- 10BASE-T auto-polarity correction

- Diagnostic loopback mode

- 1:1 transmit transformer ratio support

- Low power (less than 300 mW in active transmit mode)

- Reduced power in "unplugged mode" (less than 50 mW)

- Automatic detection of "unplugged mode"

- 3.3 V device

- 48-pin Shrink Small Outline Package

- Platform LAN connect interface support

### 1.3 References

- IEEE 802.3 Standard for Local and Metropolitan Area Networks, Institute of Electrical and Electronics Engineers

- 82555 10/100 Mbps LAN Physical Layer Interface Datasheet, Intel Corporation

- LAN Connect Interface Specification, Intel Corporation

## 1.4 Product Code

The product ordering code for the 82562ET is: DA82562ET.

## 2.0 82562ET Architectural Overview

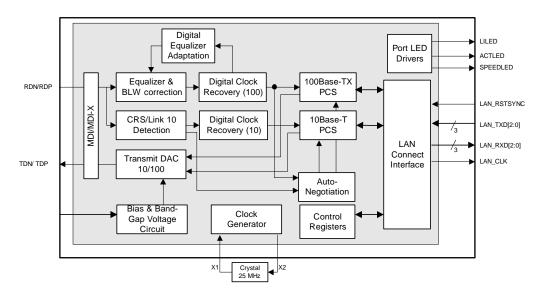

The 82562ET is a highly integrated Platform LAN Connect device that combines a 10BASE-T and 100BASE-TX physical layer interfaces. The 82562ET supports a single interface fully compliant with the IEEE 802.3 standard. Figure 1 provides a block diagram of the 82562ET architecture.

Figure 1. 82562ET Block Diagram

The 8252ET is a 3.3 V device in a 48-pin Shrink Small Outline Package (SSOP). This document describes the architecture of the device in all modes of operation.

Four pins, test Enable (TESTEN), Test Clock (ISOL\_TCK), Test Input (ISOL\_TI), and Test Execute (ISOL\_EX), define the general operation of the device. Table 1 shows the pin settings for the different modes of operation.

Table 1. 82562ET Hardware Configuration

| Mode of Operation                | TESTEN | ISOL_TCK | ISOL_TI | ISOL_EX | Comments                                                     |

|----------------------------------|--------|----------|---------|---------|--------------------------------------------------------------|

| Normal operating mode            | 0      | 0        | 0       | 0       | The ISOL_TCK, ISOL_TI, and ISOL_EX pins can remain floating. |

| Isolate mode (Tri-state and full | 0      | 1        | 1       | 1       | The device is in tri-state and power-down mode.              |

| power-down mode)                 | 1      | 1        | 1       | 1       | The device is in tri-state and the fully powered down.       |

| XOR Tree                         | 1      | 0        | 0       | 0       | The XOR Tree is used for board testing and tri-state mode.   |

NOTE: Combinations not shown in Table 1 are reserved and should not be used.

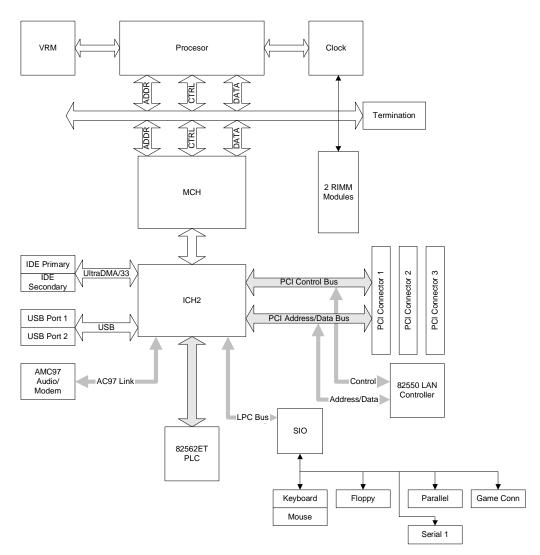

Figure 2. 82562ET Solution Overview

#### **82562ET Signal Descriptions** 3.0

#### 3.1 **Signal Type Definitions**

| Туре | Name                      | Description                                                                              |

|------|---------------------------|------------------------------------------------------------------------------------------|

| I    | Input                     | Input pin to the 82562ET.                                                                |

| 0    | Output                    | Output pin from the 82562ET.                                                             |

| I/O  | Input/Output              | Multiplexed input and output pin to and from the 82562ET.                                |

| MLT  | Multi-level<br>analog I/O | Multi-level analog pin used for input and output.                                        |

| В    | Bias                      | Bias pin used for ground connection through a resistor or an external voltage reference. |

| DPS  | Digital Power<br>Supply   | Digital power or ground pin for the 82562ET.                                             |

| APS  | Analog Power<br>Supply    | Analog power or ground pin for the 82562ET.                                              |

#### 3.2 Twisted Pair Ethernet (TPE) Pins

| Pin Name   | Pin<br>Number | Туре | Description                                                                                                                                                                                                                                                                                                                            |

|------------|---------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TDP<br>TDN | 10<br>11      | MLT  | <b>Transmit Differential Pair.</b> The transmit differential pair sends serial bit streams to the unshielded twisted pair (UTP) cable. The differential pair is a two-level signal in 10BASE-T (Manchester) mode and a three-level signal in 100BASE-TX mode (MLT-3). These signals directly interface with the isolation transformer. |

| RDP<br>RDN | 15<br>16      | MLT  | Receive Differential Pair. The receive differential pair receive the serial bit stream from an unshielded twisted pair (UTP) cable. The differential pair is a two-level signal in 10BASE-T mode (Manchester) or a three-level signal in 100BASE-TX mode (MLT-3). These signals directly interface with an isolation transformer.      |

#### 3.3 **External Bias Pins**

| Pin Name | Pin<br>Number | Туре | Description                                                                                                  |

|----------|---------------|------|--------------------------------------------------------------------------------------------------------------|

| RBIAS10  | 4             | В    | Bias Reference Resistor 10. This pin should be connected to a 549 $\Omega$ pull-down resistor. $^{\rm a}$    |

| RBIAS100 | 5             | В    | Bias reference Resistor 100. This pin should be connected to a 619 $\Omega$ pull-down resistor. <sup>b</sup> |

a. 549  $\Omega$  for RBIAS10 is only a recommended value and should be fine tuned for various designs. b. 619  $\Omega$  for RBIAS100 is only a recommended value and should be fine tuned for various designs.

## 3.4 Clock Pins

| Pin Name | Pin<br>Number | Туре | Description                                                                                                                                                                                                              |

|----------|---------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| X1       | 46            | I    | Crystal Input Clock. X1 and X2 can be driven by an external 25 MHz crystal of 50 PPM or better. Otherwise, X1 is driven by an external metal-oxide semiconductor (MOS) level 25 MHz oscillator when X2 is left floating. |

| X2       | 47            | 0    | Crystal Output Clock. X1 and X2 can be driven by an external 25 MHz crystal of 50 PPM or better.                                                                                                                         |

## 3.5 Platform LAN Connect Interface Pins

| Pin Name         | Pin<br>Number | Туре | Description                                                                                                                                                                                                                                                                                                                          |

|------------------|---------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LAN_CLK          | 39            | 0    | LAN Connect Clock. The LAN Connect Clock is driven by the 82562ET on two frequencies depending on operation speed. When the 82562ET is in 100BASE-TX mode, LAN_CLK drives a 50 MHz clock. Otherwise, LAN_CLK drives a 5 MHz clock for 10BASE-T. The LAN_CLK does not stop during normal operation.                                   |

| LAN_<br>RSTSYNC  | 42            | I    | Reset/Synchronize. This is a multiplexed pin and is driven by the Media Access Control (MAC) layer device. Its functions are:                                                                                                                                                                                                        |

|                  |               |      | <ul> <li>Reset. When this pin is asserted beyond one LAN Connect clock<br/>period, the 82562ET uses this signal Reset. To ensure reset of the<br/>82562ET, the Reset signal should remain active for at least 500<br/>µseconds.</li> </ul>                                                                                           |

|                  |               |      | <ul> <li>Synchronize. When this pin is activated synchronously, for only one<br/>LAN Connect clock period, it is used to synchronize the MAC and PHY<br/>on LAN Connect word boundaries.</li> </ul>                                                                                                                                  |

| LAN_<br>TXD[2:0] | 45, 44,<br>43 | I    | LAN Connect Transmit Data. The LAN Connect transmit pins are used to transfer data from the MAC device to the 82562ET. These pins are used to move transmitted data and real time control and management data. They also transmit out of band control data from the MAC to the PHY. The pins should be fully synchronous to LAN_CLK. |

| LAN_<br>RXD[2:0] | 37, 35,<br>34 | 0    | LAN Connect Receive Data. The LAN Connect receive pins are used to transfer data from the 82562ET to the MAC device. These pins are used to move received data and real time control and management data. They also move out of band control data from the PHY to the MAC. These pins are synchronous to LAN_CLK.                    |

## 3.6 LED Pins

| Pin Name | Pin<br>Number | Туре | Description                                                                                                                                                                                                                                                        |

|----------|---------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LILED#   | 27            | 0    | <b>Link Integrity LED.</b> The LED is active low and the Link Integrity LED pin indicates link status in either 10BASE-T or 100BASE-TX mode. If a link is present in either mode, the LILED is asserted.                                                           |

| ACTLED#  | 32            | 0    | Activity LED. The LED is active low and the Activity LED signal indicates either receive or transmit activity. When no activity is present, the LED is off. The Activity LED will flicker when activity is present. The flicker rate depends on the activity load. |

|          |               |      | The individual address LED control bit (Word A hexadecimal, bit 4) in the ICH2 EEPROM can select the ACTLED# behavior. It controls the Activity LED (ACTLED) functionality in Wake on LAN (WOL) mode.                                                              |

|          |               |      | 0 = In WOL mode, the ACTLED is activated by the transmission and<br>reception of broadcast and individual address match packets.                                                                                                                                   |

|          |               |      | 1 = In WOL mode, the ACTLED is activated by the transmission and<br>reception of individual address match packets only.                                                                                                                                            |

|          |               |      | This bit is configured by the OEM and is activated by a transmission and reception of individual address match packets.                                                                                                                                            |

| SPDLED#  | 31            | 0    | <b>Speed LED.</b> The LED is active low and the Speed LED signal indicates the speed of operation, either 10 Mbps or 100 Mbps. The Speed LED is on during 100BASE-TX operation and off in 10BASE-T mode.                                                           |

## 3.7 Miscellaneous Control Pins

| Pin Name | Pin<br>Number | Туре | Description                                                                                                                                                                                                                                                                                  |

|----------|---------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADV10    | 41            | I    | Advertise 10 Mbps Only. The Advertise 10 Mbps Only signal is asserted high, and the 82562ET advertises only 10BASE-T technology during Auto-Negotiation processes in this state. Otherwise, the 82562ET advertises all of its technologies.  Note: ADV10 has an internal pull-down resistor. |

|          |               |      | Troto. ABY To flad all internal pain down foolote.                                                                                                                                                                                                                                           |

| ISOL_TCK | 30            | I    | <b>Test Clock.</b> The Test Clock signal sets the device into asynchronous test mode in conjunction with the Test Input, Test Execute and Test Enable pins (refer to Table 1).                                                                                                               |

|          |               |      | In the manufacturing test mode, it acts as the test clock.                                                                                                                                                                                                                                   |

|          |               |      | Note: ISOL_TCK has an internal pull-down resistor.                                                                                                                                                                                                                                           |

| ISOL_TI  | 28            | I    | <b>Test Input.</b> The Test Input signal sets the device into asynchronous test mode in conjunction with the Test Clock, Test Execute and Test Enable pins (refer to Table 1).                                                                                                               |

|          |               |      | In the manufacturing test mode, it acts as the test data input pin.                                                                                                                                                                                                                          |

|          |               |      | Note: ISOL_TI has an internal pull-down resistor.                                                                                                                                                                                                                                            |

| Pin Name | Pin<br>Number | Туре | Description                                                                                                                                                                       |

|----------|---------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ISOL_TEX | 29            | I    | <b>Test Execute.</b> The Test Execute signal sets the device into asynchronous test mode in conjunction with the Test Clock, Test Input, and Test Enable pins (refer to Table 1). |

|          |               |      | In the manufacturing test mode, it places the command that was entered through the TI pin in the instruction register.  Note: ISOL TEX has an internal pull-down resistor.        |

| TOUT     | 26            | 0    | Test Output. The Test Output pin is used for Boundary XOR scan output.                                                                                                            |

|          | 20            |      | In the manufacturing test mode, it acts as the test output port.                                                                                                                  |

| TESTEN   | 21            | I    | <b>Test Enable.</b> The Test Enable pin is used to enable test mode and should be pulled down to V <sub>SS</sub> to allow XOR Tree test mode.                                     |

## 3.8 Power and Ground Connections

| Pin Name     | Pin<br>Number    | Туре | Description                                                                                  |

|--------------|------------------|------|----------------------------------------------------------------------------------------------|

| VCC          | 1, 25            | DPS  | <b>Digital 3.3 V Power.</b> These pins should be connected to the main digital power supply. |

| VCCP<br>VCCA | 36, 40<br>2,     |      | роло. одругу.                                                                                |

| VCCA2        | 7,               |      |                                                                                              |

| VCCT         | 9, 12,           |      |                                                                                              |

|              | 14, 17           |      |                                                                                              |

| VSS          | 8, 13, 18        | DPS  | <b>Digital Ground.</b> These pins should be connected to the main digital ground.            |

| VSSP         | 24, 48<br>33, 38 |      | g                                                                                            |

| VSSA         | 3                |      |                                                                                              |

|              | _                |      |                                                                                              |

| VSSA2        | 6                |      |                                                                                              |

| VCCR         | 19, 23           | APS  | Analog Power.                                                                                |

| VSSR         | 20, 22           | APS  | Analog Ground. These pins should not be isolated from the main digital.                      |

## 4.0 Voltage and Temperature Specifications

## 4.1 Absolute Maximum Ratings

Maximum ratings are listed below:

| Case Temperature under Bias                    | 0 C to 135 C              |

|------------------------------------------------|---------------------------|

| Storage Temperature                            | 65 C to 150 C             |

| Supply Voltage with respect to V <sub>SS</sub> | 0.5 V to 3.45 V           |

| Output Voltages                                | 0.50 V to 3.45 V          |

| Input Voltages                                 | V <sub>CC</sub> to 3.45 V |

Stresses above the listed absolute maximum ratings may cause permanent damage to the 82562ET device. This is a stress rating only and functional operations of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## 4.2 DC Characteristics

#### Table 2. General DC Specifications

| Symbol          | Parameter            | Condition                           | Min | Typical | Max  | Units | Notes |

|-----------------|----------------------|-------------------------------------|-----|---------|------|-------|-------|

| V <sub>CC</sub> | Supply Voltage       |                                     | 3.0 | 3.3     | 3.45 | V     |       |

| Т               | Temperature          | Minimum/Maximum Case<br>Temperature | 0   |         | 85   | С     |       |

|                 | Power<br>Consumption | 10/100Mbps (transmitter on)         |     | 300     |      | mW    |       |

| Р               |                      | Reduced Power                       |     | 50      |      | mW    |       |

|                 |                      | Auto-Negotiation                    |     | 200     |      | mW    |       |

### 4.2.1 X1 Clock DC Specifications

#### Table 3. X1 Clock DC Specifications

| Symbol            | Parameter                 | Condition                             | Min | Typical | Max | Units | Notes |

|-------------------|---------------------------|---------------------------------------|-----|---------|-----|-------|-------|

| V <sub>IL</sub>   | Input Low Voltage         |                                       |     |         | 0.8 | V     |       |

| V <sub>IH</sub>   | Input High<br>Voltage     |                                       | 2.0 |         |     | V     |       |

| I <sub>ILIH</sub> | Input Leakage<br>Currents | 0 < V <sub>IN</sub> < V <sub>CC</sub> |     |         | ±10 | μΑ    |       |

| C <sub>I</sub>    | Input<br>Capacitance      |                                       |     |         | 8   | pF    | 1     |

#### NOTES:

<sup>1.</sup> This characteristic is only characterized, not tested. It is valid for digital pins only.

## 4.2.2 LAN Connect Interface DC Specifications

#### Table 4. LAN Connect Interface DC Specifications

| Symbol           | Parameter                      | Condition                              | Min                 | Typical | Max                    | Units | Notes |

|------------------|--------------------------------|----------------------------------------|---------------------|---------|------------------------|-------|-------|

| V <sub>CCJ</sub> | Input/Output<br>Supply Voltage |                                        | 3.0                 |         | 3.45                   | V     |       |

| V <sub>IL</sub>  | Input Low Voltage              |                                        | -0.5                |         | 0.3V <sub>CCJ</sub>    | V     |       |

| V <sub>IH</sub>  | Input High<br>Voltage          |                                        | 0.6V <sub>CCJ</sub> |         | V <sub>CCJ</sub> + 0.5 | V     |       |

| I <sub>IL</sub>  | Input Leakage<br>Current       | 0 < V <sub>IN</sub> < V <sub>CCJ</sub> |                     |         | ±10                    | μΑ    |       |

| V <sub>OL</sub>  | Output Low<br>Voltage          | I <sub>OUT</sub> = 1500 μA             |                     |         | 0.1V <sub>CCJ</sub>    | V     |       |

| V <sub>OH</sub>  | Output High<br>Voltage         | I <sub>OUT</sub> = -500 μA             | 0.9V <sub>CCJ</sub> |         |                        | ٧     |       |

| C <sub>IN</sub>  | Input Pin<br>Capacitance       |                                        |                     |         | 8                      | pF    | 1     |

#### NOTES:

## 4.2.3 LED DC Specifications

#### Table 5. LED DC Specifications

| Symbol             | Parameter              | Condition                 | Min | Typical | Max | Units | Notes |

|--------------------|------------------------|---------------------------|-----|---------|-----|-------|-------|

| V <sub>OLLED</sub> | Output Low<br>Voltage  | I <sub>OUT</sub> = 10 mA  |     |         | 0.7 | V     |       |

| V <sub>OHLED</sub> | Output High<br>Voltage | I <sub>OUT</sub> = -10 mA | 2.4 |         |     | ٧     |       |

## 4.2.4 10BASE-T Voltage and Current DC Specifications

#### Table 6. 10BASE-T Transmitter

| Symbol            | Parameter                           | Condition              | Min | Typical | Max | Units | Notes |

|-------------------|-------------------------------------|------------------------|-----|---------|-----|-------|-------|

| V <sub>OD10</sub> | Output Differential<br>Peak Voltage | R <sub>L</sub> = 100 Ω | 2.2 |         | 2.8 | V     | 1     |

**NOTES:**Current is measured between the transmit differential pins (TDP and TDN) at 3.3 V. 1. R<sub>L</sub> is the resistive load measured across the transmit differential pins, TDP and TDN.

<sup>1.</sup> This characteristic is only characterized, not tested. It is valid for digital pins only.

#### Table 7. 10BASE-T Receiver

| Symbol             | Parameter                                    | Condition          | Min | Typical           | Max  | Units | Notes |

|--------------------|----------------------------------------------|--------------------|-----|-------------------|------|-------|-------|

| R <sub>ID10</sub>  | Input Differential<br>Resistance             | DC                 | 10  |                   |      | ΚΩ    | 1     |

| V <sub>IDA10</sub> | Input Differential<br>Accept Peak<br>Voltage | 5 MHz ≤ f ≤ 10 MHz | 585 |                   | 3100 | mV    |       |

| V <sub>IDR10</sub> | Input Differential<br>Reject Peak<br>Voltage | 5 MHz ≤ f ≤ 10 MHz |     |                   | 300  | mV    |       |

| V <sub>ICM10</sub> | Input Common<br>Mode Voltage                 |                    |     | V <sub>CC/2</sub> |      | V     |       |

#### NOTES

## 4.2.5 100BASE-TX Voltage and Current DC Specifications

#### Table 8. 100BASE-TX Transmitter

| Symbol             | Parameter                           | Condition              | Min  | Typical | Max  | Units | Notes |

|--------------------|-------------------------------------|------------------------|------|---------|------|-------|-------|

| V <sub>OD100</sub> | Output Differential<br>Peak Voltage | R <sub>L</sub> = 100 Ω | 0.95 | 1.0     | 1.05 | ٧     | 1     |

$\textbf{NOTES:} \textbf{Current is measured between the transmit differential pins (TDP and TDN) at 3.3 \ V.}$

#### Table 9. 100BASE-TX Receiver

| Symbol              | Parameter                                    | Condition | Min | Typical           | Max  | Units | Notes |

|---------------------|----------------------------------------------|-----------|-----|-------------------|------|-------|-------|

| R <sub>ID100</sub>  | Input Differential<br>Resistance             | DC        | 10  |                   |      | ΚΩ    | 1     |

| V <sub>IDA100</sub> | Input Differential<br>Accept Peak<br>Voltage |           | 500 |                   | 1200 | mV    |       |

| V <sub>IDR100</sub> | Input Differential<br>Reject Peak<br>Voltage |           |     |                   | 100  | mV    |       |

| V <sub>ICM100</sub> | Input Common<br>Mode Voltage                 |           |     | V <sub>CC/2</sub> |      | V     |       |

#### NOTES:

<sup>1.</sup> The input differential resistance is measured across the receive differential pins, RDP and RDN.

<sup>1.</sup>  $R_L$  is the resistive load measured across the transmit differential pins, TDP and TDN.

<sup>1.</sup> The input differential resistance is measured across the receive differential pins, RDP and RDN.

#### **Package and Pinout Information** 5.0

#### **Package Information** 5.1

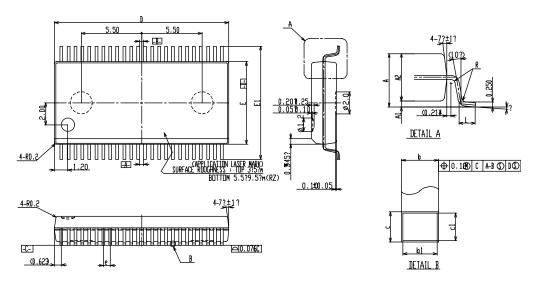

The 82562ET is a 48-pin Shrink Small Outlying Package (SSOP). The Package dimensions are shown in Figure 3. More information on Intel device packaging is available in the Intel Packaging Handbook, which is available from the Intel Literature Center or your local sales office.

Figure 3. Dimension Diagram for the 82562ET 48-pin SSOP

| SYMBOL  | CUM   | AMON DIMENSI | UNS   |

|---------|-------|--------------|-------|

| 2 IMDUL | MIN   | NDM          | MAX   |

| A       | 2.44  | 2.59         | 2.74  |

| A1      | 0.20  | 0.30         | 0.40  |

| A2      | 2.24  | 2.29         | 2.34  |

| b       | 0.22  | _            | 0.30  |

| b1      | 0.22  | 0.25         | 0.28  |

| С       | 0.18  | _            | 0.25  |

| c1      | 0.18  | 0.20         | 0.22  |

| D       | 15.75 | 15.85        | 15.95 |

| E       | 7.45  | 7.50         | 7.55  |

| E1      | 10.16 | 10.285       | 10.41 |

| L       | 0.70  | 0.80         | 0.90  |

| е       |       | 0.635 BS     | 30    |

| R       | 0.10  | 0.20         | 0.30  |

| 3       | 0?    | 5?           | 8?    |

#### NOTES)

- ALL DIMENSIONS ARE IN MILLINETERS. (AMGLES IN DEGREES)

DIMENSIONS 10/100ES NOT INCLUDE BURRS.

HOWER, DIMENSION INCLUDING PROTRUSIONS OR GATE BURRS

SHALL BE MAX. 0.20Mm.

JIDMENSION 721/200ES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION INTERLEAD FLASH OR PROTRUSION SHALL NOT EXCERD 0.25 PER SIDE.

## 5.2 Pinout Information

## 5.2.1 82562ET Pin Assignments

Table 10. 82562ET Pin Assignments

| Pin<br>Number | Pin Name    |

|---------------|----------|---------------|----------|---------------|----------|---------------|-------------|

| 1             | VCC      | 13            | VSS      | 25            | VCC      | 37            | LAN_RXD2    |

| 2             | VCCA     | 14            | VCCT     | 26            | TOUT     | 38            | VSSP        |

| 3             | VSSA     | 15            | RDP      | 27            | LILED    | 39            | LAN_CLK     |

| 4             | RBIAS10  | 16            | RDN      | 28            | ISOL_TI  | 40            | VCCP        |

| 5             | RBIAS100 | 17            | VCCT     | 29            | ISOL_TEX | 41            | ADV10       |

| 6             | VSSA2    | 18            | VSS      | 30            | ISOL_TCK | 42            | LAN_RSTSYNC |

| 7             | VCCA2    | 19            | VCCR     | 31            | SPDLED   | 43            | LAN_TXD0    |

| 8             | VSS      | 20            | VSSR     | 32            | ACTLED   | 44            | LAN_TXD1    |

| 9             | VCCT     | 21            | TESTEN   | 33            | VSSP     | 45            | LAN_TXD2    |

| 10            | TDP      | 22            | VSSR     | 34            | LAN_RXD0 | 46            | X1          |

| 11            | TDN      | 23            | VCCR     | 35            | LAN_RXD1 | 47            | X2          |

| 12            | VCCT     | 24            | VSS      | 36            | VCCP     | 48            | VSS         |

## 5.2.2 82562ET Shrink Small Outlying Package Diagram

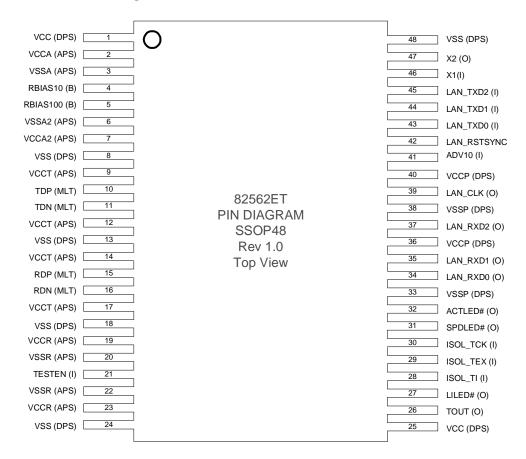

Figure 4. 82562ET Pin Out Diagram