**High Current MOSFET Driver**

April 1994

| _ | <br>٠. | <br>90 |

|---|--------|--------|

|   |        |        |

| • | Fast Fall Times                      |

|---|--------------------------------------|

| • | No Supply Current in Quiescent State |

| • | Peak Source Current6A                |

| • | Peak Sink Current30A                 |

|   | High Frequency Operation300kHz       |

|   |                                      |

#### **Applications**

- Switch Mode Power Supplies

- DC/DC Converters

- Motor Controllers

- Uninterruptible Power Supplies

#### Ordering Information

| PART<br>NUMBER | TEMPERATURE<br>RANGE | PACKAGE                 |

|----------------|----------------------|-------------------------|

| HV400IP        | -40°C to +85°C       | 8 Lead Plastic DIP      |

| HV400IB        | -40°C to +85°C       | 8 Lead Plastic SOIC (N) |

| HV400MJ/883    | -55°C to +125°C      | 8 Lead Ceramic SBDIP    |

#### Description

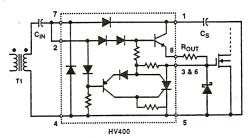

The HV400 is a single monolithic, non-inverting high current driver designed to drive large capacitive loads at high slew rates. The device is optimized for driving single or parallel connected N-channel power MOSFETs with total gate charge from 5nC to >1000nC. It features two output stages pinned out separately allowing independent control of the MOSFET gate rise and fall times. The current sourcing output stage is an NPN capable of 6A. An SCR provides over 30A of current sinking. The HV400 achieves rise and fall times of 54ns and 16ns respectively driving a 10,000pF load.

Special features are included in this part to provide a simple, high speed gate drive circuit for power MOSFETs. The HV400 requires no quiescent supply current, however, the input current is approximately 15mA while in the high state. With the internal current steering diodes (pin 7) and an external capacitor, both the timing and MOSFET gate power come from the same pulse transformer; no special external supply is required for high side switches. No high voltage diode is required to charge the bootstrap capacitor.

The HV400 in combination with the MOSFET and pulse transformer makes an isolated power switch building block for applications such as high side switches, secondary side regulation and synchronous rectification. The HV400 is also suitable for driving IGBTs, MCTs, BJTs and small GTOs.

The HV400 is a type of buffer; it does not have input logic level switching threshold voltages. This single stage design achieves propagation delays of 20ns. The output NPN begins to source current when the voltage on pin 2 is approximately 2V more positive than the voltage at pin 8.

The output SCR switches on when the input pin 2 voltage is 1V more negative than the voltage at pins 3/6. Due to the use of the SCR for current sinking, once the output switches low, the input must not go high again until all the internal SCR charge has dissipated, 0.5µs - 1.5µs later.

CAUTION: These devices are sensitive to electrostatic discharge. Users should follow proper I.C. Handling Procedures. Copyright @ Harris Corporation 1994 3-18

File Number 2850.

#### Specifications HV400

| Absolute Maximum Ratings                                                                                                                                                                                                                                                                                       | Thermal Information                                                                                                                                                                                                                      |                                    |                                                                   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-------------------------------------------------------------------|

| Voltage Between Pin1 and Pin 4/5       35V         Input Voltage Pin 7 (Max)       Pin 1 + 1.5V         Input Voltage Pin 7 (Min)       Pin 4/5 - 1.5V         Input Voltage Pin 2 to Pin 4/5       +/- 35V         Input Voltage Pin 2 to Pin 6       -35V         Maximum Clamp Current (Pin 7)       ±300mA | Thermal Resistance PDIP SOIC SBDIP Power Dissipation at T <sub>A</sub> = +25°C PDIP SOIC SBIP Operating Temperature Range HV400IP/IB HV400MJ/883 Lead Temperature (Soldering 10s) Maximum Junction Temperature Storage Temperature Range | 40°C < 1<br>-55°C < T <sub>A</sub> | 0.7W<br>2.33W<br>$\Gamma_A$ < +85°C<br>+125°C<br>+265°C<br>+150°C |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

# DC Electrical Specifications V<sub>SUPPLY</sub> = 15V

| PARAMETERS                                          | SYMBOL           | CONDITIONS                                                                          | TEMPERATURE           | MIN      | TYP       | MAX   | UNITS         |

|-----------------------------------------------------|------------------|-------------------------------------------------------------------------------------|-----------------------|----------|-----------|-------|---------------|

| INPUT (PIN 2)                                       |                  |                                                                                     |                       | <u> </u> |           |       | 1 5           |

| Input High Differential Voltage<br>(Pin 2 - Pin 8)  | V <sub>IH</sub>  | V <sub>OUT</sub> = 0V, I <sub>OUT</sub> HI = 10mA                                   | +25°C                 | 0.6      | 1.7       | 2.8   | V             |

|                                                     |                  |                                                                                     | Full                  | . 0.5    | -         | 3.5   | V             |

| Input Low Differential Voltage<br>(Pin 2 - Pin 3/6) | V <sub>IL</sub>  | V <sub>OUT</sub> = 12V, I <sub>OUT</sub> LO = -3mA                                  | +25°C                 | -1.1     | -0.9      | -0.8  | V             |

|                                                     |                  |                                                                                     | Full                  | -1.26    | -         | -0.65 | V             |

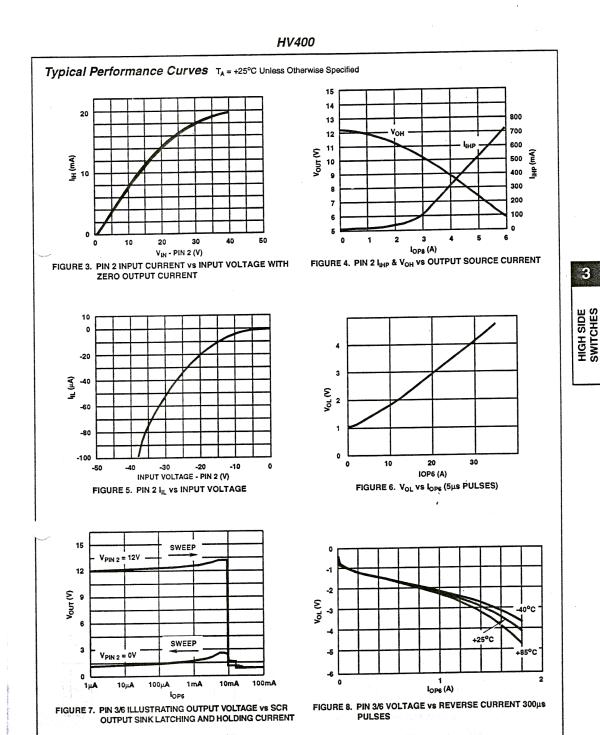

| Input High Current                                  | Iн               | V <sub>PIN 1, 2</sub> = 30V, I <sub>SOURCE</sub> = 0                                | +25°C                 | 15       | 18        | 20    | mA            |

|                                                     |                  |                                                                                     | Full                  | 15       |           | 22    | mA            |

| Input High Current Peak                             | I <sub>IHP</sub> | I <sub>SOURCE</sub> = 6A, 1μs pulse,<br>V <sub>IN</sub> = 9V, V <sub>OUT</sub> = 0V | +25°C                 |          | 700       |       | mA            |

| Input Low Current                                   | I <sub>IL</sub>  | V <sub>PIN 2</sub> = -30V                                                           | +25°C                 | -80      | -50       |       | μА            |

|                                                     |                  |                                                                                     | Full                  | -120     |           |       | μА            |

| SOURCE OUTPUT (PIN 8)                               |                  |                                                                                     |                       |          |           |       |               |

| High Output Voltage                                 | V <sub>OH</sub>  | V <sub>IN</sub> = +V, I <sub>OUT</sub> = 150mA                                      | +25°C                 | 12.1     | 12.8      | 13.4  | V             |

|                                                     |                  |                                                                                     | Full                  | 12.0     |           | 13.5  | ٧             |

| Peak Output Current                                 | I <sub>OP8</sub> | V <sub>IN</sub> = 9V, 1μs Pulse,<br>V <sub>OUT</sub> = 0V                           | +25°C                 | •        | 6         | 1     | Α             |

| Output Low Leakage                                  | l <sub>OL</sub>  | V <sub>OUT</sub> = 0V, V <sub>IN</sub> = 0V                                         | +25°C                 | 0        | 10        | 50    | μА            |

|                                                     |                  |                                                                                     | Full                  |          | 4         | 55    | μА            |

| SINK OUTPUT (PIN 3/6)                               |                  |                                                                                     |                       |          |           |       | $\overline{}$ |

| Low Output Voltage                                  | V <sub>OL</sub>  | V <sub>IN</sub> = 0V, I <sub>OUT</sub> = -150mA                                     | +25°C                 | 0.8      | 0.89      | 1.0   | V             |

|                                                     |                  |                                                                                     | Full                  | 0.8      |           | 1.05  | ٧.            |

| Peak Output Current                                 | lope             | V <sub>IN</sub> = 0V, 5μs Pulse,<br>V <sub>OUT</sub> = 4V                           | +25°C                 |          | 30        |       | Α             |

| Output High Leakage                                 | loн              | V <sub>IN</sub> = 15V                                                               | +25°C                 | 0        | 0.3       | 2     | μА            |

|                                                     |                  |                                                                                     | Full                  | 0        |           | 13.5  | μА            |

| DIODES D1 AND D7 (PIN 7)                            |                  |                                                                                     | and the weeks were to |          |           |       |               |

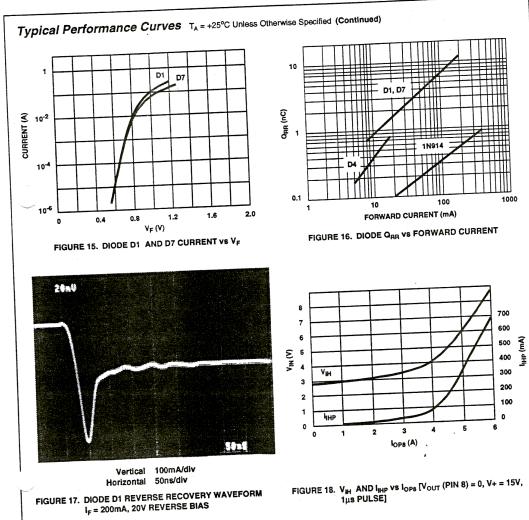

| Forward Voltage                                     | VF               | I <sub>D</sub> = 100mA                                                              | +25°C                 | 0.8      | 1.03      | 1.4   | V             |

|                                                     |                  |                                                                                     | Full                  | 0.8      | NE COLUMN | 1.6   | V             |

| Reverse Leakage Current                             | I <sub>R</sub>   | V <sub>R</sub> = 30V                                                                | +25°C                 | 0        | 0.1       | 1     | μА            |

|                                                     | And part         |                                                                                     | Full .                | 0        |           | 1     | μА            |

| Diode (Pin 7) Stored Charge                         | Q <sub>RR</sub>  | I <sub>D</sub> = 100mA                                                              | +25°C                 |          | 6.5       | (1)   | nC .          |

NOTE: Limits are 100% tested at +25°C; limits over the full temperature range are guaranteed but not tested.

### Specifications HV400

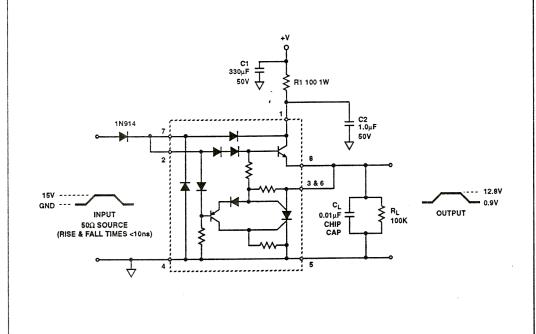

#### Switching Time Specifications V<sub>SUPPLY</sub> = 15V

| PARAMETERS            | SYMBOL          | CONDITIONS                 | TEMPERATURE | MIN | TYP | MAX  | UNITS |

|-----------------------|-----------------|----------------------------|-------------|-----|-----|------|-------|

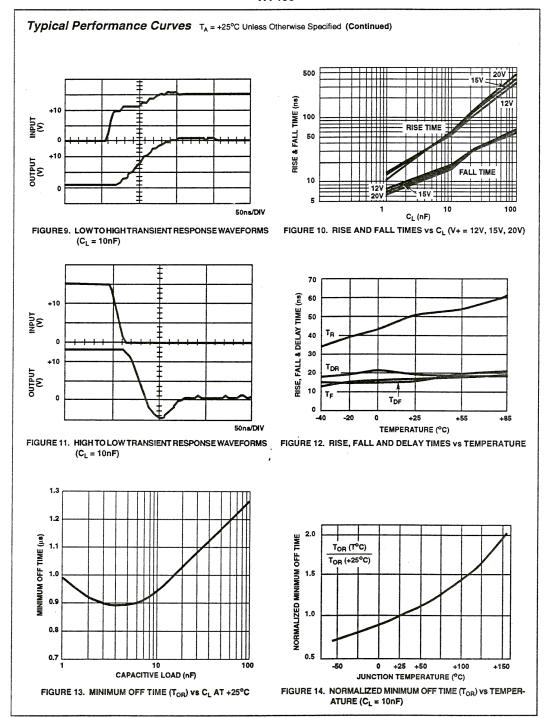

| Rise Time             | T <sub>R</sub>  | See Switching Test Circuit | Full        |     | 50  | 66   | ns    |

| Fall Time             | T <sub>F</sub>  | See Switching Test Circuit | Full        |     | 15  | 24   | ns    |

| Delay Time (Lo to Hi) | T <sub>DR</sub> | See Switching Test Circuit | Full        |     | 20  | 25   | ns    |

| Delay Time (Hi to Lo) | T <sub>DF</sub> | See Switching Test Circuit | Full        |     | 17  | 28   | ns    |

| Minimum Off Time      | T <sub>OR</sub> | See Switching Test Circuit | Full        |     | 900 | 1500 | ns    |

#### NOTES:

- 1. Switching times are guaranteed but not tested

- 2. Typical values are for +25°C

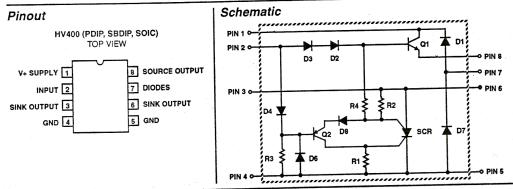

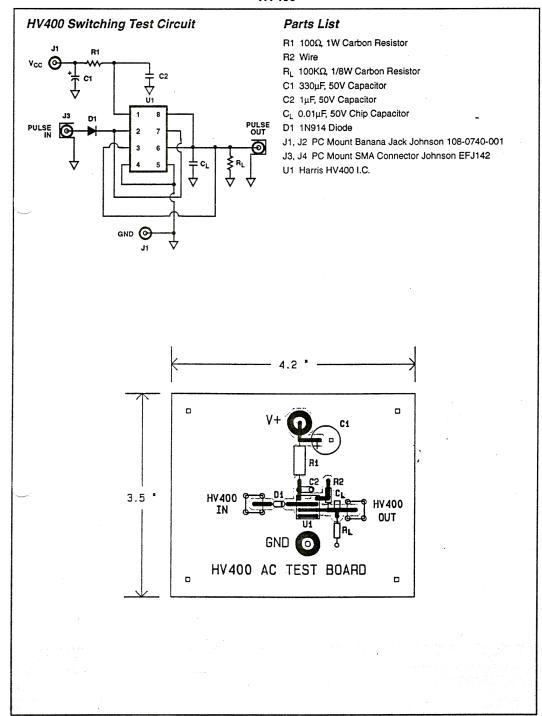

#### Switching Diagram and Test Circuit

HIGH SIDE SWITCHES

| SYMBOL           | DESCRIPTION                                                                                                   |

|------------------|---------------------------------------------------------------------------------------------------------------|

| OC INPUT PA      | RAMETERS                                                                                                      |

| V <sub>IH</sub>  | The differential voltage between the input (Pin 2) to the output (Pin 8) required to source 10mA              |

| V <sub>IL</sub>  | The differential voltage between the input (Pin 2) to the output (Pins 3, 6) required to sink 3mA             |

| I <sub>IH</sub>  | The current required to maintain the input (Pin 2) high with I <sub>OUT</sub> = 0A                            |

| I <sub>IHP</sub> | The input (Pin 2) current for a given pulsed output current                                                   |

| I <sub>IL</sub>  | The current require to maintain the input (Pin 2) low                                                         |

| OC OUTPUT        | PARAMETERS                                                                                                    |

| V <sub>OH</sub>  | The output (Pin 8) voltage with input (Pin 2) = V+                                                            |

| I <sub>OP8</sub> | The pulsed peak source current form output (Pin 8)                                                            |

| l <sub>OL</sub>  | The output (Pin 8) leakage current with the input (Pin 2) = Ground                                            |

| V <sub>OL</sub>  | The output (Pins 3, 6) voltage with the input (Pin 2) = Ground                                                |

| I <sub>OP6</sub> | The pulsed peak sink current into output (Pins 3, 6)                                                          |

| Іон              | The output (Pins 3, 6) leakage current with the input (Pin 2) = V+                                            |

| V <sub>F</sub>   | The forward voltage of diode D1 or D7                                                                         |

| I <sub>R</sub>   | The reverse leakage current of diode D1 or D7                                                                 |

| Q <sub>RR</sub>  | The time integral of the reverse current at turn off                                                          |

| AC PARAME        | TERS (See Switching Time Specifications)                                                                      |

| TR               | The low to high transition of the output                                                                      |

| T <sub>F</sub>   | The high to low transition of the output                                                                      |

| T <sub>DR</sub>  | The output propagation delay from the input (Pin 2) rising edge                                               |

| T <sub>DF</sub>  | The output propagation delay from the input (Pin 2) falling edge                                              |

| Tor              | The minimum time required after an output high to low transition before the next input low to high transition |

#### Application Information

#### **Circuit Operation**

The HV400's operation is easily explained by referring to the schematic. The control signal is applied to pin 2. If the control signal is about 2V above pin 8, the output NPN Q1 turns on charging the MOSFET gate from a capacitor connected to pin 1. Resistor R4 helps keep the SCR off by applying a reverse bias to the SCR anode gate.

When the control input drops about 1V below pin 3/6, PNP Q2 turns on which triggers the SCR by driving both the anode and cathode gates. The SCR discharges the MOSFET gate and when its current becomes less than 10mA, it turns off. Transistor Q2 conducts any gate leakage currents, through resistors R1 and R2, once the SCR turns off. Figure 7 shows the output characteristics before the SCR turns on and after it turns off. When the SCR turns on, resistor R4 provides a path to remove Q1 base charge. Resistor R3 provides the base current for Q2 to reduce the turn off delay time. Resistors R1 and R2 reduce the SCR recovery time.

The two diodes connected to the diode input pin 7 provide some operation flexibility. With pins 2 and 7 connected together, diode D1 provides a path to recharge the storage capacitor once the MOSFET gate is pulled high and, along with diodes D2 and D3, keeps Q1 from going into hard saturation which would increase delay times. Diode D7 would clamp the input near ground and provide a current path if an input DC blocking capacitor is used.

Alternatively, pin 7 can be connected to pin 6 so that the SCR and NPN Q1 don't have to pass reverse current if the output "rings" above the supply or below ground. When high performance diodes are required, pin 7 can be left disconnected and external diodes substituted.

The diodes in series with pin 2 decouple the input from the output during negative going transitions. The absence of input current turns off Q1 and allows Q2 to trigger the SCR. Diode D8 turns off Q2 once the SCR turns on pulling the output low, otherwise Q2 would saturate and slow down circuit operation. In addition, the diodes D2, D3 and D8 improve noise immunity by adding about 2.5V of input hysteresis.

The HV400 is capable of large output currents but only for brief durations due to power dissipation.

#### **Circuit Board Layout**

PC board layout is very important. Pins 3 and 6 should be connected together as should pins 4 and 5. Otherwise the internal interconnect impedance is doubled and only half of the bond wires are used which would degrade the reliability.

The bootstrap capacitor should hold at least 10x the charge of the MOSFET and should be connected between pins 1 and 4/5 with minimum lead lengths and spacings. Likewise, the HV400 should be as close to the MOSFET as possible. Any long PC traces (parasitic inductances) between the MOSFET gate and pins 8 or 3/6 or between the source and

pins 4/5 should be avoided. Inductance between the HV400 and the MOSFET limit the MOSFET switching time. If they are too large, the HV400 may operate erratically as discussed below.

#### **Cross Conduction Faults**

It is possible to have both Q1 and the SCR on at the same time resulting in very large cross conduction currents. The SCR has larger current capacity so the output goes low and the storage capacitor is discharged. The conditions that cause cross conduction and precautions are discussed below.

#### Minimum Off Time

The SCR requires a recovery time before voltage can be reapplied without it switching back on. Figure 13 shows how this SCR recovery time, called "minimum off time" ( $T_{OR}$ ), is a function of the load capacitance. If the input voltage goes high before this recovery time is complete, the SCR will switch back on.

Note that reverse current flowing through the SCR, for example due to load inductance ringing, extends the minimum off time. Since the minimum off time is really dependent upon how much stored charge remains in the SCR when the anode (pin 3/6) is taken positive, it may vary for different applications. Figure 13 indirectly shows that the minimum off time increases with larger currents. It also increases at elevated temperatures as shown in Figure 14. Excessive ringing increases the minimum off time since the stored charge doesn't begin to dissipate until the current drops below 10mA for the last time. Rising anode voltage acts on the internal SCR capacitance to generate its own triggering current. The excess stored charge increases this capacitance. Faster rise times and/or higher voltages also increase the amount of internal trigger current from the internal capacitance so applications with larger dV/dt require longer minimum off times.

The minimum off time must be considered for all occurrences of SCR current. For example, in a half bridge switch mode power supply, there are two MOSFET's connected to the transformer primary. Assume that the high side MOSFET switch is off. When the low side MOSFET switch is turned on, the HV400 driving the high side MOSFET will have to sink gate current from  $C_{\rm gd}$  and will have to source gate current when the low side MOSFET switches back off. Both of these current pulses will try to flow through pin 3/6 since the pin 8 output is turned off. Sourcing current from pins 3/6 through the SCR is possible, the pin 3/6 voltage becoming negative with respect to pins 4/5 (See Figure 8). But a better practice would be to connect a Schottky diode between pins 4/5 (anode) and 3/6 (cathode) so reverse current does not flow through the SCR.

#### Faise SCR Triggering

The SCR may be triggered inadvertently. The output may overshoot the input due to inductive loading or over driving the output NPN (allowing it to saturate). Whenever pin 6 is more positive than pin 2 by 1V, the SCR is triggered on. Also,

3

HIGH SIDE SWITCHES if the output rises too rapidly, greater than 0.5V/nS, the SCR may self trigger. Both issues are resolved by minimizing the load inductance and inserting sufficient resistance, usually 0.1 to 10 ohms, between pin 8 and the load.

A very fast negative going input voltage can result in minimum off times of about 2.5µs. If the output can not keep up with the falling input, the stored charge of diode D4 is transferred into the base of Q2. This excess charge in Q2 must have time to dissipate. Otherwise, when pin 3/6 goes positive, Q2 will turn on and trigger the SCR. An external diode in series with pin 2, as shown in Figure 1, will prevent D4 from discharging into the base of Q2 but that will also reduce the output voltage by the forward voltage of that diode.

#### Internal Diodes

The internal diodes connected to pin 7 are provided for convenience but may not be suitable for large currents. Since they are part of the integrated circuit, they are physically small, operate at high current densities, and have long recovery times. Figure 15 shows that their forward characteristics degrade above 100mA. In addition, Figure 16 shows their reverse recovery charge as a function of forward current. The product of this charge, the applied reverse voltage and the frequency is the additional power dissipation due to the diodes. For stored charge calculations, use the peak forward current within 100ns of the application of reverse bias. In addition to the extra power dissipation, the capacitance of these diodes may extend the switching delay times.

#### **Power Dissipation Calculations**

The power required to drive the MOSFET is the product of its total gate charge times the gate supply voltage (maximum voltage on HV400 pin 1, 2 or 7) times the frequency. Assuming that the MOSFET gate resistance is negligible, this power is dissipated within the HV400. If resistors are placed between the HV400 and the MOSFET, then some of the power is dissipated in the resistors, the percentage depending upon the ratio of resistors to HV400 output impedance.

There are two other sources of power dissipation to consider. First there is the power in R3 which is the product of the input pin 2 current and voltage (with no output current) times the duty cycle. Second is the product of the pin 7 diode stored charge, which is dependent upon the forward current, times the applied diode reverse voltage times the frequency. This information is available from figures 3 and 16 in this data sheet.

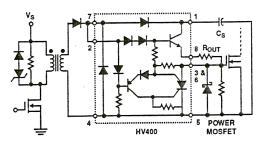

#### **Applications Circuits**

The HV400 was designed to interface a pulse transformer to a power MOSFET. There must be some means to balance the transformer volt-second product over a cycle. The unipolar drive shown in Figure 1 lets the core magnetization inductance reverse the primary and secondary voltages. The zener diode on the primary side limits this voltage and must

be capable of dissipating the energy stored in the transformer. The load may be connected to either the power MOSFET drain or source.

FIGURE 1. UNIPOLAR DRIVE

A diode is added in series with pins 2 and 7 to allow the transformer secondary to go negative. The charge storage of the pin 7 diode may cause the turn off delay time to be too long. Alternatively, pin 7 could be left disconnected and a second external diode connected between the transformer (anode) and pin 1 (cathode). In some applications the diode in series with pin 2 may be unnecessary but the -35V input to output or ground maximum rating should be observed.

Sometimes the volt-second balance is achieved by a pushpull drive on the pulse transformer primary. This is especially useful if there are two secondary windings driving two HV400's out of phase such as in a half-bridge configuration

Other times it is more convenient to achieve volt-second balance by using capacitors to block DC in the primary and secondary windings as shown in Figure 2. The pin 7 diodes provide a path for discharging the secondary side DC blocking capacitor. Both capacitors, C<sub>IN</sub> and C<sub>S</sub>, should be at least 10 times the equivalent MOSFET gate capacitance.

The HV400 can be used as a current booster for low side switches by connecting directly to the PWM output. The circuit would be similar to the switching time test circuit.

It is worth restating that some consideration (and experimentation) should be given to the choice of external components, i.e. resistors, capacitors and diodes, to optimize performance in a given application.

FIGURE 2. BIPOLAR DRIVE WITH DC BLOCKING CAPACITOR

HIGH SIDE SWITCHES

# This datasheet has been downloaded from:

www.EEworld.com.cn

Free Download

Daily Updated Database

100% Free Datasheet Search Site

100% Free IC Replacement Search Site

Convenient Electronic Dictionary

Fast Search System

www.EEworld.com.cn

All Datasheets Cannot Be Modified Without Permission

Copyright © Each Manufacturing Company