# LM1296

# Raster Geometry Correction System for Multi-Frequency Displays

#### **General Description**

The LM1296 is a monolithic IC for use in the raster scanning circuitry of a multi-frequency CRT monitor. The IC provides an S-corrected sawtooth waveform and a variable DC output voltage. These two outputs drive the vertical deflection amplifier. It also provides another waveform for East-West geometry correction which includes pincushion, corner, and trapezoid controls. The geometry correction is controlled by DC input voltages from 0V to 4V.

The raster height and the raster vertical position can be controlled by two DC voltage input pins that adjust the sawtooth waveform amplitude and the variable DC output voltage. The East-West correction of the LM1296 has height tracking and vertical position tracking capabilities. As the height or position of the raster is adjusted the geometry correction is maintained by the chip automatically.

The LM1296 is packaged in a 16-pin plastic DIP package.

- Accepts either polarity of V sync

- DC-controlled correction terms

- Raster vertical position control

- Vertical S-correction (linearity) control

- East-West pincushion control

- East-West trapezoid control

- East-West corner control

- Provides both polarities of correction output

- East-West correction tracks raster vertical position and height

- Compatible with LM1290 and LM1292 horizontal PLL

#### **Applications**

■ Vertical deflection of monitors

#### **Features**

■ Vertical scanning frequency 50 Hz-165 Hz

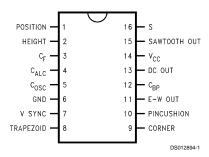

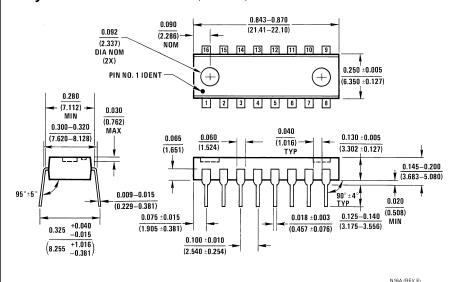

#### **Connection Diagram**

FIGURE 1. Order Number LM1296N See NS Package Number N16A

**Absolute Maximum Ratings** (Notes 3, 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

Supply Voltage (V<sub>CC</sub>) 15V

Input Voltage (V<sub>IN</sub>)

Pins 1, 2, 8, 9, 10, 16  $0 \text{V} \leq \text{V}_{\text{IN}} \leq 5 \text{V}$

Power Dissipation (P<sub>D</sub>) Above 25°C, Derate

Based on  $\theta_{JA}$  and  $T_J$  (Note 4) 1.5W Thermal Resistance ( $\theta_{JA}$ ) 81°C/W

Junction Temperature (T<sub>JMAX</sub>) 150°C ESD Susceptibility (Note 5) 2 kV Storage Temperature -65°C to +150°C Lead Temperature (Soldering 10 sec.) 265°C

# Operating Ratings(Note 2)

Supply Voltage (V<sub>CC</sub>)  $10.8V \leq V_{CC} \leq 13.2V$

Input Voltage (V<sub>IN</sub>)

Pins 1, 2, 8, 9, 10, 16  $0V \le V_{IN} \le 4V$

Output Current (I<sub>OUT</sub>)

Pins 11, 13, 15 -2 mA  $\leq$  I $_{OUT} \leq$  2 mA 0°C to +70°C Temperature Range (T<sub>A</sub>)

#### **Electrical Characteristics**

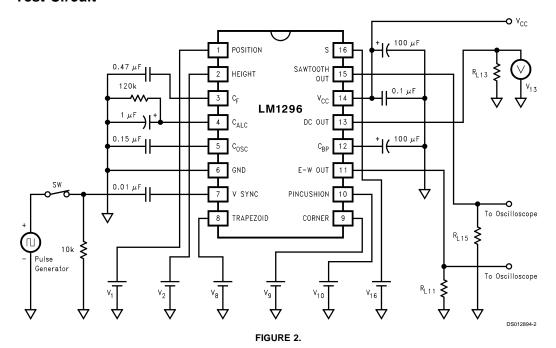

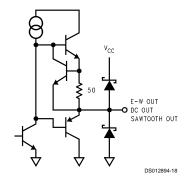

See Test Circuit (Figure 2),  $V_{CC}$  = 12V;  $V_2$  = 4V;  $V_{16}$  = 4V;  $V_{RDCV}$  = 0V (Note 6);  $T_A$  = 25°C unless otherwise specified

| Symbol            | Parameter                                           | Conditions                                            | Min      | Тур      | Max      | Units           |

|-------------------|-----------------------------------------------------|-------------------------------------------------------|----------|----------|----------|-----------------|

|                   |                                                     |                                                       | (Note 8) | (Note 7) | (Note 8) |                 |

| I <sub>cc</sub>   | Supply Current                                      | Pins 11, 13, 15 Loaded, 2mA                           |          | 26       | 32       | mA              |

| V SYNC            | Vertical Sync Input Sensitivity (Pin 7)             | 1% or 99% Duty Cycle                                  |          |          |          |                 |

|                   |                                                     | Rectangular Waveform                                  |          | 1        |          | $V_{PP}$        |

|                   |                                                     | AC-Coupled to Pin 7                                   |          |          |          |                 |

|                   |                                                     | Through 0.01 µF Cap.                                  |          |          |          |                 |

| f <sub>MIN</sub>  | Minimum Lock Frequency                              | C <sub>OSC</sub> = 0.15 μF                            |          |          | 50       | Hz              |

| f <sub>MAX</sub>  | Maximum Lock Frequency                              | C <sub>OSC</sub> = 0.15 μF                            | 165      |          |          | Hz              |

| f <sub>FR</sub>   | Free Run Frequency                                  | $V_7 = 4V \text{ or } 0V$                             |          | 40       |          | Hz              |

| R <sub>IN1</sub>  | Input Resistance (Pin 1)                            |                                                       |          | 25       |          | kΩ              |

| R <sub>IN2</sub>  | Input Resistance (Pin 2)                            | V <sub>2</sub> = 1V                                   |          | 12       |          | kΩ              |

| R <sub>IN3</sub>  | Input Resistance (Pins 8, 9, 10)                    |                                                       |          | 50       |          | kΩ              |

| R <sub>IN4</sub>  | Input Resistance (Pin 16)                           |                                                       |          | 50       |          | kΩ              |

| V <sub>O15</sub>  | SAWTOOTH OUT (Pin 15)                               | $V_2 = 4V, V_{16} = 0V$                               |          | 1.8      |          |                 |

|                   | Output Amplitude ( $R_{L15} = 5 \text{ k}\Omega$ )  | $V_2 = 4V, V_{16} = 4V$                               |          | 3.1      |          | $V_{PP}$        |

|                   |                                                     | $V_2 = 0V, V_{16} = 0V$                               |          | 1        |          |                 |

|                   |                                                     | $V_2 = 0V, V_{16} = 4V$                               |          | 1.7      |          |                 |

| V <sub>DC15</sub> | SAWTOOTH OUT (Pin 15)                               | $V_2 = 0V \text{ to } 4V, V_{16} = 0V \text{ to } 4V$ |          | 3.9      |          | V               |

|                   | Output DC Voltage ( $R_{L15} = 5 \text{ k}\Omega$ ) |                                                       |          |          |          |                 |

| k <sub>TEMP</sub> | SAWTOOTH OUT (Pin 15)                               | (Note 9)                                              |          | 1.5      |          | %               |

|                   | Temperature Stability                               |                                                       |          |          |          |                 |

| k <sub>S</sub>    | S-Correction of Sawtooth Output (Pin 15)            | V <sub>2</sub> = 4V, V <sub>16</sub> = 4V             |          | 0.5      |          | %               |

|                   |                                                     | $V_2 = 4V, V_{16} = 0V$                               |          | 2        |          |                 |

| V <sub>RDCV</sub> | Relative DC Voltage between                         | V <sub>1</sub> = 4V                                   |          | -200     |          | mV              |

|                   | DC OUT (Pin 13) and                                 | V <sub>1</sub> = 1.5V                                 |          | 200      |          |                 |

|                   | SAWTOOTH OUT (Pin 15)                               |                                                       |          |          |          |                 |

|                   | $V_{RDCV} = V_{13} - V_{DC15}$                      |                                                       |          |          |          |                 |

|                   | $(R_{L13} = 5 k\Omega)$                             |                                                       |          |          |          |                 |

| V <sub>TRAP</sub> | Trapezoid Correction                                | $V_2 = 4V, V_8 = 0V$                                  |          | 0.87     |          | $V_{PP}$        |

|                   | Output Waveform Amplitude                           | $V_2 = 4V, V_8 = 4V$                                  |          | 0.73     |          |                 |

|                   | (Pin 11, $R_{L11} = 5 kΩ$ )                         | Pincushion and Corner                                 |          |          |          |                 |

|                   |                                                     | Corrections are Null                                  |          |          |          |                 |

| $V_{PIN}$         | Pincushion Correction                               | $V_2 = 4V, V_{10} = 0V$                               |          | 1.9      |          | V <sub>PP</sub> |

|                   | Output Waveform Amplitude                           | $V_2 = 4V, V_{10} = 4V$                               |          | 1.45     |          |                 |

|                   | (Pin 11, $R_{L11} = 5 kΩ$ )                         | Trapezoid and Corner                                  |          |          |          |                 |

|                   |                                                     | Corrections are Null                                  |          |          |          |                 |

### **Electrical Characteristics** (Continued)

See Test Circuit (Figure 2), V<sub>CC</sub> = 12V; V<sub>2</sub> = 4V; V<sub>16</sub> = 4V; V<sub>RDCV</sub> = 0V (Note 6); T<sub>A</sub> = 25°C unless otherwise specified

| Symbol            | Parameter                  | Conditions                  | Min      | Тур      | Max      | Units           |

|-------------------|----------------------------|-----------------------------|----------|----------|----------|-----------------|

|                   |                            |                             | (Note 8) | (Note 7) | (Note 8) |                 |

| V <sub>CNR</sub>  | Corner Correction          | $V_2 = 4V, V_9 = 0V$        |          | 1.1      |          | V <sub>PP</sub> |

|                   | Output Waveform Amplitude  | $V_2 = 4V, V_9 = 4V$        |          | 0.8      |          |                 |

|                   | (Pin 11, $R_{L11}$ = 5 kΩ) | Trapezoid and Pincushion    |          |          |          |                 |

|                   |                            | Corrections are Null        |          |          |          |                 |

| V <sub>DC11</sub> | E-W OUT                    | Trapezoid, Pincushion, and  |          | 4.1      |          | V               |

|                   | Output Offset Voltage      | Corner Correction Waveforms |          |          |          |                 |

|                   | (Pin 11, $R_{L11}$ = 5 kΩ) | are Null                    |          |          |          |                 |

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur.

Note 2: Operating Ratings indicate conditions for which the device is functional, but do not guarantee specific performance limits. For guaranteed specifications and test conditions, see the Electrical Characteristics. The guaranteed specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions.

Note 3: All voltages are measured with respect to GND, unless otherwise specified.

Note 4: The maximum power dissipation must be derated at elevated temperatures and is dictated by  $T_{JMAX}$ ,  $\theta_{JA}$  and the ambient temperature,  $T_A$ . The maximum allowable power dissipation at any elevated temperature is  $P_D = (T_{JMAX} - T_A)/\theta_{JA}$  or the number given in the Absolute Maximum Ratings, whichever is lower. For this device,  $T_{JMAX} = 150$ °C. The typical thermal resistance  $(\theta_{JA})$  of the LM1296 is 81°C/W.

Note 5: Human Body model, 100 pF capacitor discharged through a 1.5  $k\Omega$  resistor.

Note 6: Adjust  $V_1$  until  $V_{RDCV}$  = 0V, where  $V_{RDCV}$  =  $V_{13}$  -  $V_{DC15}$ .

Note 7: Typical specifications are specified at TA = 25°C and represent most likely parametric norm.

Note 8: Tested limits are guaranteed to National's AOQL (Average Outgoing Quality Level).

**Note 9:** Amplitude stability versus ambient temperature is defined by  $|V_{70} - V_{25}|/V_{25} \times 100\%$ , where  $V_{70}$  and  $V_{25}$  are the output sawtooth peak-to-peak amplitudes at 70°C and 25°C respectively.

#### **Test Circuit**

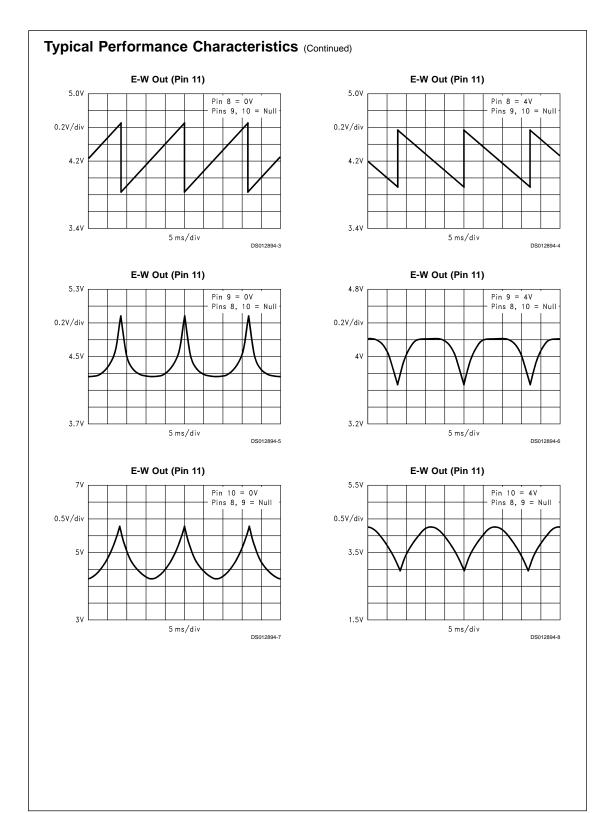

#### **Typical Performance Characteristics**

$T_A = 25^{\circ}C$ ,  $f_v = 60$  Hz,  $V_2 = 4V$ ,  $V_{16} = 4V$ ,  $V_{RDCV} = 0V$ ,  $V_{8,9,10} = Set$  for null correction waveforms, unless otherwise specified

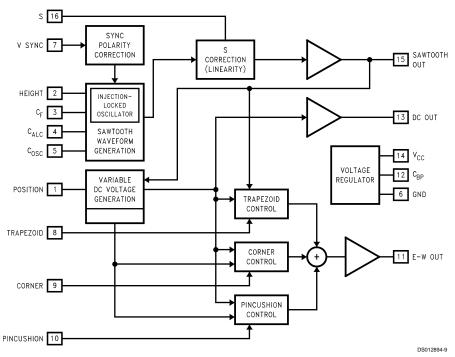

#### **Block Diagram**

FIGURE 3.

#### **Functional Description**

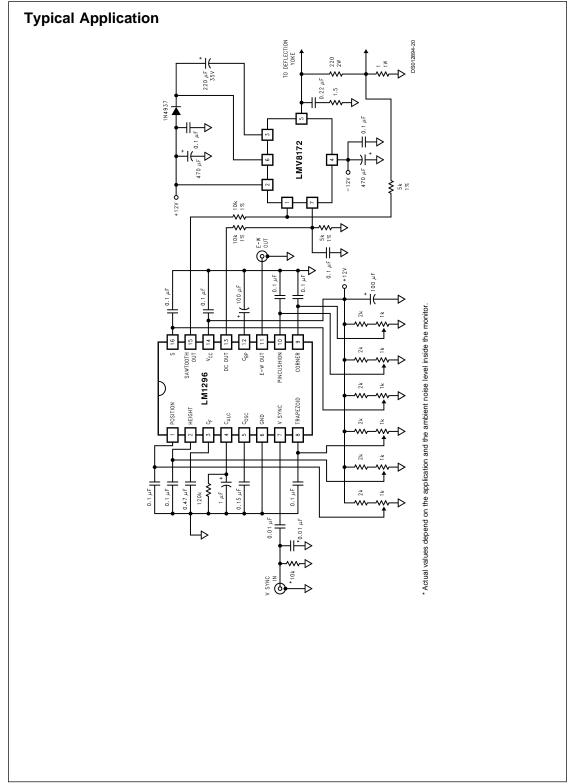

The LM1296 outputs a sawtooth and a variable DC voltage for the vertical deflection amplifier. It also provides the horizontal deflection output circuit with a waveform for Trapezoid, Pincushion and Corner correction.

Referring to Figure 3, pin 7 (V SYNC) goes to the Sync Polarity Correction Block that accepts either positive-going or negative-going sync signals. The polarity-corrected sync is sent to the Injection-Locked Oscillator so that the sawtooth generated is synchronized with the vertical sync. With no sync signal AC-coupled to pin 7, the oscillator free runs at typically 40 Hz.

There are three capacitors and one control pin connected to the Sawtooth Waveform Generation Block.  $C_{\rm OSC}$  is the timing capacitor for the Injection-Locked Oscillator.  $C_{\rm F}$  is the filter capacitor for an internal circuit that detects the existence of vertical sync and prevents the Injection-Locked Oscillator from locking at twice the vertical sync frequency.  $C_{\rm ALC}$  is for the automatic level control (ALC) circuit. The ALC circuit maintains the sawtooth output amplitude, which is set by the DC voltage at pin 2 (HEIGHT), regardless of the vertical sync frequency. Since the output sawtooth goes to the geometry correction circuit as well, the correction waveform generated tracks the sawtooth amplitude, i.e., the height of the CRT raster.

The S Correction block shapes the linear sawtooth into an S-shape sawtooth. Pin 15 (SAWTOOTH OUT) outputs the buffered S-shape sawtooth. The amount of S correction is controlled by the DC voltage at pin 16 (S).

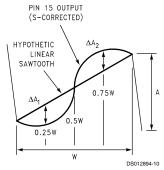

Referring to Figure 4, the extent of S correction is defined by the following equation.

$$k_S = (\Delta A_1 + \Delta A_2)/2A \times 100\%$$

FIGURE 4.

The LM1296 is designed to drive an external vertical deflection amplifier that is operating with positive and negative power supplies. The LM1296 outputs an S-corrected sawtooth with a DC level that is typical 3.85V. Pin 13 (DC OUT) provides a DC voltage of 3.85V  $\pm$  200 mV. By applying a DC control voltage to pin 1 (POSITION), the output voltage at pin 13 can be varied. This sets the output DC current from the vertical deflection amplifier, which in turn sets the raster vertical position.

#### Functional Description (Continued)

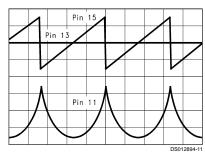

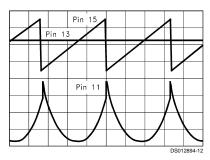

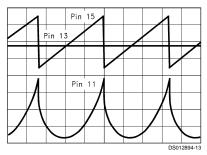

Pin 1 (POSITION) not only controls the pin 13 output, but also the center position of the correction waveform at pin 11 (E-W OUT). As a result, the geometry correction tracks the vertical position of the CRT raster. See *Figure 5* through *Figure 7*

The Pincushion Control Block and the Corner Control Block are non-linear analog circuits. They convert the sawtooth waveform into 2nd order and 4th order parabolic waveforms. These two parabolic waveforms, together with a sawtooth (1st order), are summed and then buffered out at pin 11 (E-W OUT). See waveforms in the Typical Performance Characteristics section. The amplitudes of the 1st, 2nd and 4th order components in the correction waveform are controlled by the DC voltages at pin 8 (TRAPEZOID), pin 9 (CORNER) and pin 10 (PINCUSHION).

FIGURE 5. Raster Position Centered

## **Pin Descriptions**

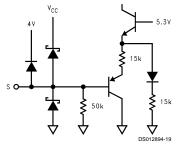

See Figure 8 through Figure 13 for input and output schematics.

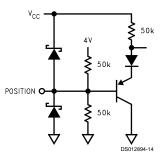

**Pin 1. POSITION:** A 0V to 4V DC voltage applied to this pin sets pin 13 (DC OUT) output voltage from 3.65V to 4.05V. See *Figure 8* for the input schematic.

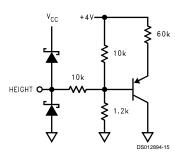

**Pin 2. HEIGHT:** A 0V to 4V DC voltage applied to this pin sets the output amplitude of the sawtooth waveform at pin 15 (SAWTOOTH OUT) as well as the output amplitude of the correction waveform at pin 11 (E-W OUT). See *Figure 9* for the input schematic.

**Pin 3.**  $C_F$ : A 0.47 µF capacitor is connected from this pin to ground. This capacitor prevents the Injection-Locked Oscillator from locking at twice the V sync frequency.

**Pin 4.**  $C_{ALC}$ : A filter capacitor for the automatic level control circuit (ALC) is connected from this pin to ground. The ALC circuit maintains the output amplitudes of SAWTOOTH OUT and E-W OUT regardless of the V sync frequency. The recommended capacitance of  $C_{ALC}$  is between 1  $\mu F$  to 4.7  $\mu F$ .

**Pin 5.** C<sub>OSC</sub>: A timing capacitor for the Injection-Locked Oscillator is connected from this pin to ground. The recommended capacitance is 0.15 µF. Increasing the capacitance will lower the lowest lock frequency.

Pin 6. GND: Ground pin.

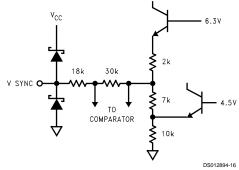

**Pin 7. V SYNC:** This pin accepts AC-coupled V sync of either polarity. See *Figure 10* for the input schematic. The input sensitivity of this pin is about 1 V<sub>PP</sub>. For best noise immunity, a resistor of 10 kΩ in parallel with a filter capacitor of 0.01 μF should be connected from the input side of the coupling capacitor to ground. The values of these components may be

FIGURE 6. Raster Position Up

FIGURE 7. Raster Position Down

varied depending on the application and the ambient noise level inside the monitor. A DC voltage of 0V or 4V on this pin will cause the device to free run at about 40 Hz.

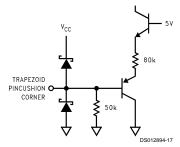

**Pin 8. TRAPEZOID:** A 0V to 4V DC voltage applied to this pin adjusts the polarity and the amount of linear sawtooth component (Trapezoid Correction) in the E-W OUT output. At approximately 2V, the amount is zero. A voltage above 2V sets a negative-sloped sawtooth output, increasing the voltage increases the sawtooth amplitude. A voltage below 2V sets a positive-sloped sawtooth output, decreasing the voltage increases the sawtooth amplitude. See *Figure 11* for the input schematic.

**Pin 9. CORNER:** A 0V to 4V DC voltage applied to this pin adjusts the polarity and the amount of 4th order parabolic component (Corner Correction) in the E-W OUT output. At approximately 2V, the amount is zero. A voltage above 2V sets a concave down 4th order output, increasing the voltage increases the 4th order amplitude. A voltage below 2V sets a concave up 4th order output, decreasing the voltage increases the 4th order amplitude. See *Figure 11* for the input

**Pin 10. PINCUSHION:** A 0V to 4V DC voltage applied to this pin adjusts the polarity and the amount of 2nd order parabolic component (Puncushion Correction) in the E-W OUT output. At approximately 2V, the amount is zero. A voltage above 2V sets a concave down 2nd order output, increasing the voltage increases the 2nd order amplitude. A voltage below 2V sets a concave up 2nd order output, decreasing the voltage increases the 2nd order amplitude. See *Figure 11* for the input schematic.

#### Pin Descriptions (Continued)

**Pin 11. E-W OUT:** The output waveform at this pin consists of the sum of the linear sawtooth, 2nd order parabolic and 4th order parabolic waveform components. The center position of the output waveform tracks the output voltage at pin 13 (DC OUT). See *Figure 12* for the output schematic.

**Pin 12. C**<sub>BP</sub>: A capacitor of at least 100  $\mu F$  is connected from this pin to ground via a short path.

**Pin 13. DC OUT:** This pin outputs a variable DC voltage from 3.65V to 4.05V. The output voltage is controlled by the control voltage at pin 1 (POSITION). See *Figure 12* for the output schematic.

**Pin 14.**  $V_{CC}$ : 12V nominal power supply pin. This pin should be decoupled to pin 6 (GND) via a short path with a capacitor of at least 100 µF.

**Pin 15. SAWTOOTH OUT:** This pin outputs an S-corrected sawtooth waveform with the amplitude controlled by pin 2 (HEIGHT). See *Figure 12* for the output schematic.

**Pin 16: S:** A 0V to 4V DC voltage applied to this pin adjusts the amount of S correction in the sawtooth waveform at pin 15 (SAWTOOTH OUT). 0V sets maximum S correction. See *Figure 13* for the input schematic.

#### **Input/Output Schematics**

FIGURE 8.

FIGURE 9.

FIGURE 10.

FIGURE 11.

FIGURE 12.

FIGURE 13.

#### Physical Dimensions inches (millimeters) unless otherwise noted

\_\_\_\_

16-Lead (0.300" Wide) Molded Dual-In-Line Package Order Number LM1296N NS Package Number N16A

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMI-CONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Corporation Americas

Tel: 1-800-272-9959 Fax: 1-800-737-7018 Email: support@nsc.com

www.national.com

National Semiconductor Europe

Fax: +49 (0) 1 80-530 85 86

Email: europe.support@nsc.com

Deutsch Tel: +49 (0) 1 80-530 85 85

English Tel: +49 (0) 1 80-532 78 32

Français Tel: +49 (0) 1 80-532 93 88

Italiano Tel: +49 (0) 1 80-534 16 80

National Semiconductor Asia Pacific Customer Response Group Tel: 65-2544466 Fax: 65-2504466

Email: sea.support@nsc.com

National Semiconductor Japan Ltd. Tel: 81-3-5620-6175 Fax: 81-3-5620-6179

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications