# Bt860/861

## Multiport YCrCb to NTSC/PAL/SECAM Digital Video Encoder

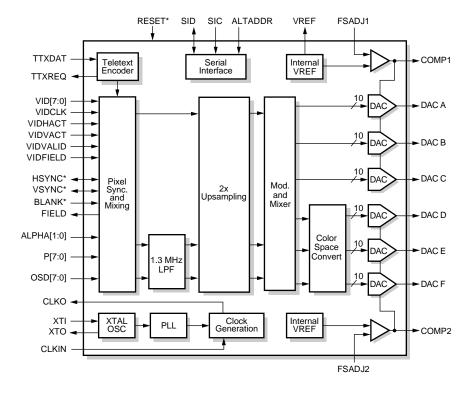

The Bt860/861 is a multiport digital video encoder with pixel synchronization and per-pixel blending capabilities. The three 8-bit YCrCb data ports allow for a variety of video and graphic overlay configurations useful in video set-top box applications.

The Bt860/861 is specifically designed for video systems requiring composite, Y/C (S-Video), and simultaneous component YUV or RGB (SCART) video signals. Worldwide video standards are supported, including NTSC-M (N. America, Taiwan, Japan), PAL-B,D,G,H,I (Europe, Asia), PAL-M (Brazil), PAL-N (Uruguay, Paraguay), PAL-Nc (Argentina), PAL-60, NTSC-443, and SECAM. The Bt860 and Bt861 are functionally identical except that the Bt861 can output the Macrovision 7.x anticopy algorithm.

Multisource video is a key feature of the Bt860/861. Two general purpose ports (P and OSD) allow synchronization with sources that can share clock and frame timing control with the Bt860/861, such as digital video and graphic overlay content generated by an MPEG video decoder. A third port (VID) is specifically configured to interface with video decoders such as those in the Conexant VideoStream decoder family. Any pair of these three ports can be synchronized and blended.

### **Functional Block Diagram**

#### **Distinguishing Features**

- Six 10-bit DACs with individual power management

- Simultaneous output of YUV, S-Video, and CVBS, or RGB (SCART), S-Video, and CVBS

- Current drive output DACs for superior video quality and reduced system cost

- Dynamic video load sensing for reduced power operation

- Three sharpness filter options (1,2,3.5 dB gain) and four reduction filter options

- Programmable adjustment of brightness, contrast, color saturation, and hue

- · Glueless interface with a video decoder

- Three 8-bit YCrCb 4:2:2 inputs for overlay or blending

- ITU-R BT.656, ITU-R BT.601 digital video input options

- NTSC-M, PAL (B,D,G,H,I), PAL-M, PAL-N, NTSC-443, PAL-Nc, PAL-60 and SECAM video output

- 2x upsampling and internal filtering for reduced cost

- Master or slave video timing with programmable HSYNC\* delay

- Interlaced/noninterlaced operation

- Macrovision 7.x copy protection (Bt861)

- Closed Captioning and Extended Data Services encoding

- Teletext encoding (WST system B)

- · 400 kHz serial programming interface

- · On-board voltage reference

- Reduced power modes

- Programmable luma delay (two channels)

- 3.3 V supply, 5 V-tolerant inputs

- Copy Generation Management System (CGMS) support

- VARIS-II and Wide Screen Signalling (WSS) multiple aspect ratio support

- · Internal color bar generation

- · Blue field generation

- · 80-pin MQFP package

#### **Related Products**

- Bt852, Bt868/869, Bt864A/865A, Bt866/867

- Bt835, Bt829A/B

#### **Applications**

- · Digital cable television systems

- · Satellite TV receivers (DBS/DVB/DSS)

- DVD players

- · Video CD players

- · Digital cameras

- PC add-on cards

- Video editing

### **Ordering Information**

| Model Number | Package     | Operating Temperature |

|--------------|-------------|-----------------------|

| Bt860KRF     | 80-Pin MQFP | 0 °C-70 °C            |

| Bt861KRF     | 80-Pin MQFP | 0 °C-70 °C            |

Information provided by Conexant Systems, Inc. (Conexant) is believed to be accurate and reliable. However, no responsibility is assumed by Conexant for its use, nor any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent rights of Conexant other than for circuitry embodied in Conexant products. Conexant reserves the right to change circuitry at any time without notice. This document is subject to change without notice.

Conexant products are not designed or intended for use in life support appliances, devices, or systems where malfunction of a Conexant product can reasonably be expected to result in personal injury or death. Conexant customers using or selling Conexant products for use in such applications do so at their own risk and agree to fully indemnify Conexant for any damages resulting from such improper use or sale.

Conexant and "What's Next in Communications Technologies" are trademarks of Conexant Systems, Inc.

This device is protected by U.S. patent numbers 4,631,603, 4,577,216, and 4,819,098, and other intellectural property rights. The use of Macrovision's copy protection technology in the device must be authorized by Macrovison and is intended for home and other limited pay-per-view uses only, unless otherwise authorized in writing by Macrovision. Reverse engineering or disassembly is prohibited.

Product names or services listed in this publication are for identification purposes only, and may be trademarks or registered trademarks of their respective companies. All other marks mentioned herein are the property of their respective holders.

© 1999 Conexant Systems, Inc. Printed in U.S.A. All Rights Reserved

**Reader Response:** To improve the quality of our publications, we welcome your feedback. Please send comments or suggestions via e-mail to Conexant Reader Response@conexant.com. Sorry, we can't answer your technical questions at this address. Please contact your local Conexant sales office (listed on back page) or applications engineer if you have technical questions.

D860DSA Conexant

# **Table of Contents**

| List 0 | t Figu                 | res vii                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

|--------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| List o | f Table                | esix                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| 1.0    | Functional Description |                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

|        | 1.1                    | Pin Descriptions                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

|        | 1.2                    | Functional Overview                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| 2.0    | Inpu                   | Inputs and Timing2-1                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

|        | 2.1                    | Reset2-12.1.1Initialization and Power-up Configuration2-1                                                                                                                                                                                                                                     |  |  |  |  |  |  |

|        | 2.2                    | Digital Video Ports       2-2         2.2.1 The P Port       2-3         2.2.2 The VID Port       2-3         2.2.3 The OSD Port       2-3         2.2.4 Overlay Modes and Alpha Blending       2-4         2.2.5 Alpha Pin Blending       2-5         2.2.6 Content-based Blending       2-5 |  |  |  |  |  |  |

|        | 2.3                    | Configurations and Timing2-62.3.1ITU-R BT.601 Configurations and Timing.2-72.3.2ITU-R BT.656 Timing2-102.3.3VID Port (Video Decoder Locked) Timing2-12                                                                                                                                        |  |  |  |  |  |  |

|        | 2.4                    | Clock Selection         2-14           2.4.1 Crystal Inputs and the PLL         2-14                                                                                                                                                                                                          |  |  |  |  |  |  |

|        |                        |                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

| Digi | ital Prod | essing and Functionality                        | 3-1  |

|------|-----------|-------------------------------------------------|------|

| 3.1  | Video     |                                                 | 3-1  |

|      | 3.1.1     | Video Standards                                 | 3-1  |

|      | 3.1.2     | Analog Horizontal Sync                          | 3-9  |

|      | 3.1.3     | Analog and Digital Vertical Sync                | 3-9  |

|      | 3.1.4     | Analog Video Blanking                           | 3-10 |

|      | 3.1.5     | Subcarrier and Burst Generation                 | 3-11 |

|      | 3.1.6     | Subcarrier Phasing (SC_H Phase)                 | 3-12 |

|      | 3.1.7     | Noninterlaced Operation                         | 3-12 |

| 3.2  | Effects   |                                                 | 3-13 |

|      | 3.2.1     | Chrominance Disable                             | 3-13 |

|      | 3.2.2     | Internal Filtering                              | 3-13 |

|      | 3.2.3     | Internal Colorbars, Blue Field, and Black Burst | 3-15 |

|      | 3.2.4     | Setup                                           | 3-19 |

|      | 3.2.5     | YUV and RGB Multipliers                         | 3-19 |

|      | 3.2.6     | Programming Values to Comply with YPrPb and RGB | 3-19 |

|      | 3.2.7     | Programmable Video Adjustments Controls         | 3-20 |

|      |           | 3.2.7.1 Hue Adjust                              | 3-20 |

|      |           | 3.2.7.2 Brightness Adjust                       | 3-20 |

|      |           | 3.2.7.3 Contrast Adjust                         | 3-21 |

|      |           | 3.2.7.4 Saturation Adjust                       | 3-21 |

|      |           | 3.2.7.5 Sharpness Adjust                        | 3-21 |

|      | 3.2.8     | Macrovision Encoding (Bt861 Only)               | 3-22 |

|      | 3.2.9     | Outputs                                         | 3-22 |

|      | 3.2.10    | Luminance Delay                                 | 3-22 |

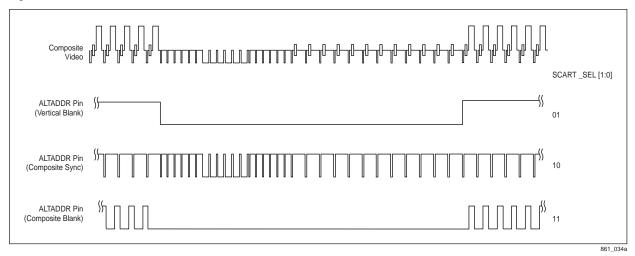

|      | 3.2.11    | Special SCART Signals                           | 3-23 |

|      | 3.2.12    | Output Connection Status                        | 3-23 |

|      | 3.2.13    | Output Filtering and SINX/X Compensation        | 3-24 |

|      | 3.2.14    | Low Power Features                              | 3-24 |

|      | 3.2.15    | Teletext Operation of Bt860/861                 | 3-25 |

|      |           | 3.2.15.1 Teletext Timing Mode 1                 | 3-26 |

|      |           | 3.2.15.2 Teletext Timing Mode 2                 | 3-26 |

|      |           | 3.2.15.3 General Teletext Operation             | 3-27 |

|      | 3.2.16    | Wide Screen Signaling                           | 3-27 |

|      | 3.2.17    | Copy Generation Management System               |      |

|      | 3.2.18    | Closed Captioning and Extended Data Services    |      |

|      |           |                                                 | 3-30 |

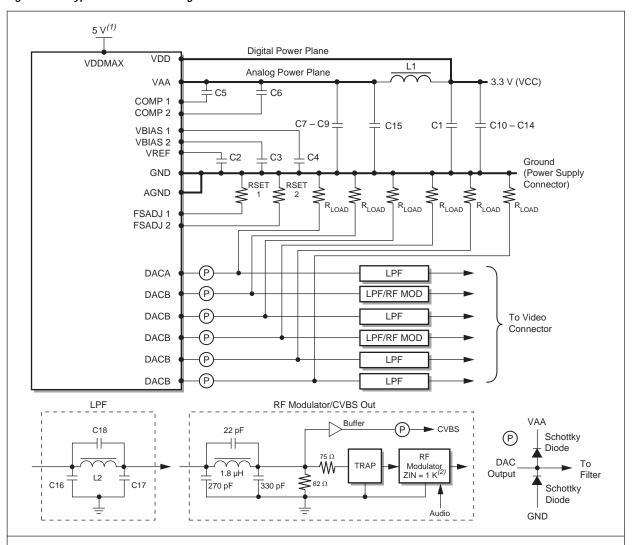

| 4.0 | Applications 4-1                           |                                       |  |  |  |  |

|-----|--------------------------------------------|---------------------------------------|--|--|--|--|

|     | 4.1                                        | PC Board Considerations. 4-1          |  |  |  |  |

|     |                                            | 4.1.1 Component Placement             |  |  |  |  |

|     |                                            | 4.1.2 Power and Ground Planes         |  |  |  |  |

|     |                                            | 4.1.3 Device Decoupling               |  |  |  |  |

|     |                                            | 4.1.4 Power Supply Decoupling         |  |  |  |  |

|     |                                            | 4.1.5 COMP Decoupling                 |  |  |  |  |

|     |                                            | 4.1.6 VREF Decoupling                 |  |  |  |  |

|     |                                            | 4.1.7 VBIAS Decoupling                |  |  |  |  |

|     |                                            | 4.1.8 Digital Signal Interconnect     |  |  |  |  |

|     |                                            | 4.1.9 Analog Signal Interconnect      |  |  |  |  |

|     |                                            | 4.1.10 ESD and Latchup Considerations |  |  |  |  |

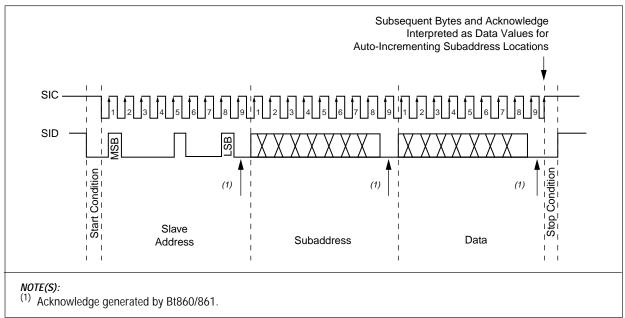

| 5.0 | Serial Programming Interface and Registers |                                       |  |  |  |  |

|     | 5.1                                        | Serial Interface                      |  |  |  |  |

|     |                                            | 5.1.1 Device Address                  |  |  |  |  |

|     |                                            | 5.1.2 Writing Data                    |  |  |  |  |

|     |                                            | 5.1.3 Reading Data                    |  |  |  |  |

|     | 5.2                                        | Internal Registers                    |  |  |  |  |

|     |                                            | 5.2.1 Register Bit Map 5-4            |  |  |  |  |

|     | 5.3                                        | Register Index. 5-8                   |  |  |  |  |

|     | 5.4                                        | Register Detail                       |  |  |  |  |

| 6.0 | Para                                       | metric Data and Specifications        |  |  |  |  |

|     | 6.1                                        | Electrical Specifications             |  |  |  |  |

|     |                                            | 6.1.1 Electrical Parameters           |  |  |  |  |

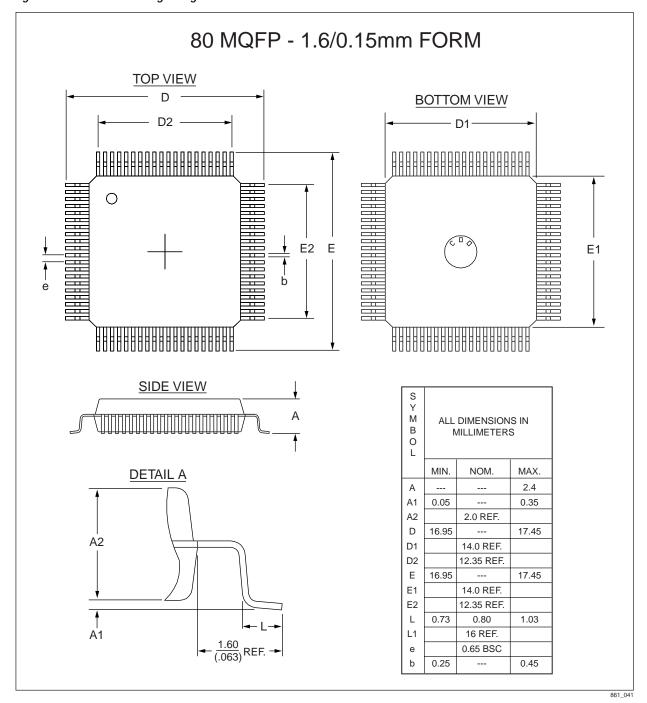

|     | 6.2                                        | Mechanical Drawing                    |  |  |  |  |

Table of Contents Bt860/861

# **List of Figures**

| Figure 1-1.  | Pinout Diagram                                                             | 1-1    |

|--------------|----------------------------------------------------------------------------|--------|

| Figure 1-2.  | Detailed Block Diagram                                                     | 1-6    |

| Figure 2-1.  | Pixel Latching and Blending Mechanism                                      | 2-2    |

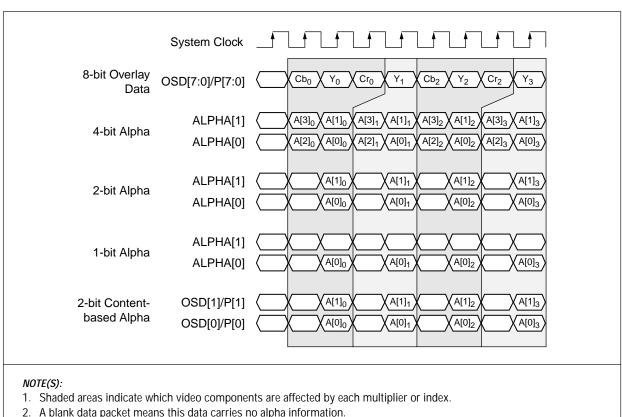

| Figure 2-2.  | Alpha Blending Timing Diagram                                              | 2-5    |

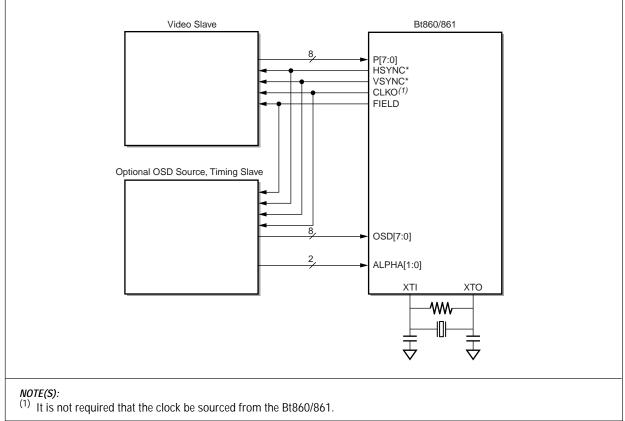

| Figure 2-3.  | Timing Mode 1 Connection Example                                           | 2-7    |

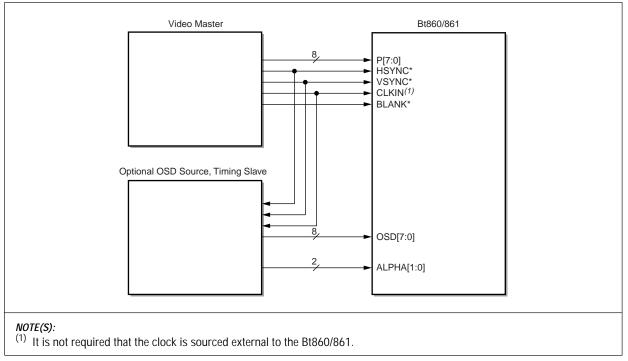

| Figure 2-4.  | Timing Mode 2 Connection Example                                           | 2-8    |

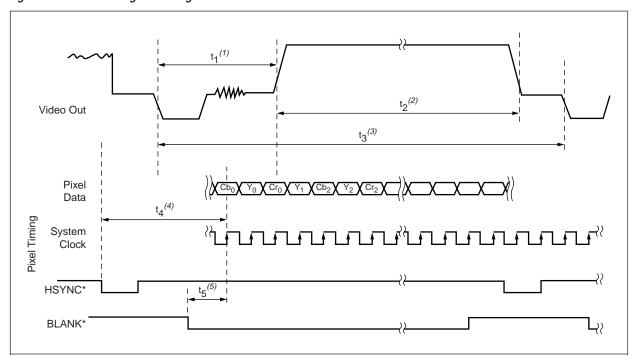

| Figure 2-5.  | Pixel Timing for Timing Modes 1 and 2                                      | 2-9    |

| Figure 2-6.  | Timing Mode 3 and 4 Connection Example                                     | . 2-10 |

| Figure 2-7.  | 625 Line ITU-R BT.656 Timing                                               | . 2-11 |

| Figure 2-8.  | 525 Line ITU-R BT.656 Timing                                               | . 2-11 |

| Figure 2-9.  | Video Decoder Connection Example                                           | . 2-13 |

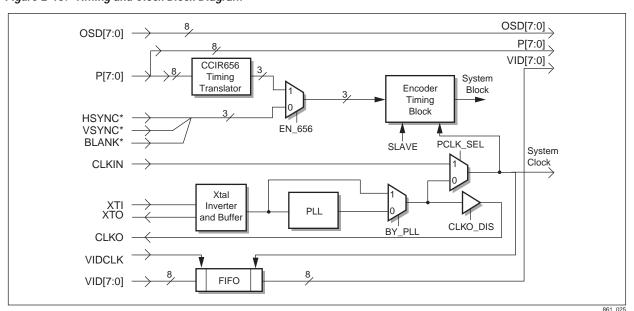

| Figure 2-10. | Timing and Clock Block Diagram                                             | . 2-14 |

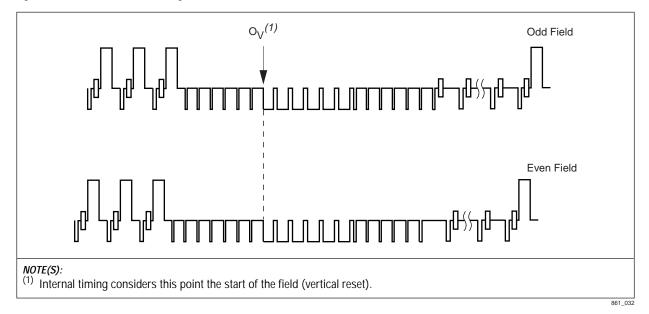

| Figure 3-1.  | NTSC Vertical Timing                                                       | 3-9    |

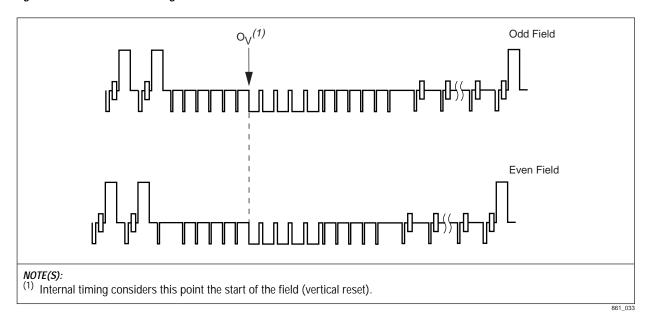

| Figure 3-2.  | PAL Vertical Timing                                                        | . 3-10 |

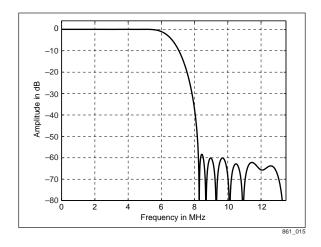

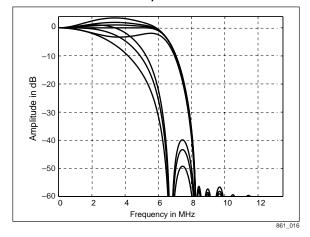

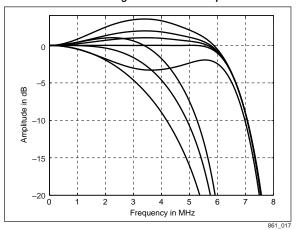

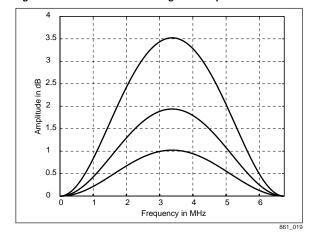

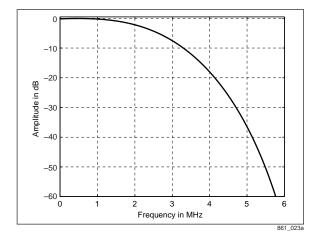

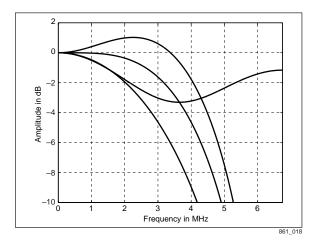

| Figure 3-3.  | Luminance Upsampling Filter                                                | . 3-13 |

| Figure 3-4.  | Luminance Upsampling Filter with Peaking and Reduction Options             | . 3-13 |

| Figure 3-5.  | Close-Up of Luminance Upsampling Filter with Peaking and Reduction Options | . 3-14 |

| Figure 3-6.  | Luminance Reduction Filters Options                                        | . 3-14 |

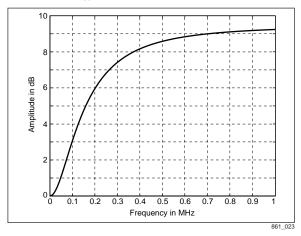

| Figure 3-7.  | Luminance Peaking Filter Options                                           | . 3-14 |

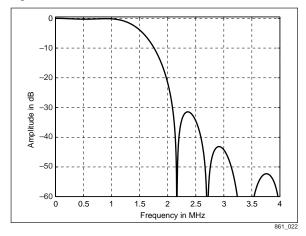

| Figure 3-8.  | Chrominance Filter                                                         | . 3-14 |

| Figure 3-9.  | Chrominance Wide Bandwidth Filter                                          | . 3-14 |

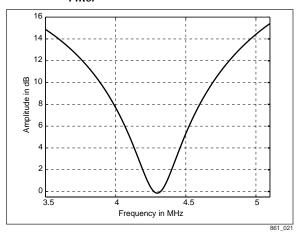

| Figure 3-10. | SECAM High Frequency Pre-emphasis Filter                                   | . 3-14 |

| Figure 3-11. | SECAM Low Frequency Pre-emphasis Filter                                    | . 3-15 |

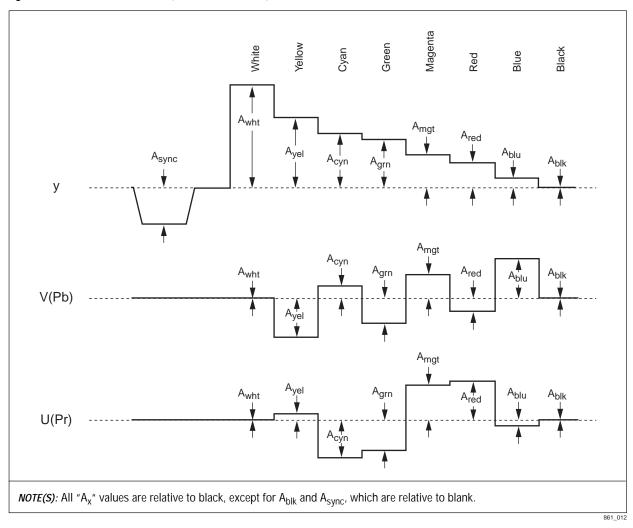

| Figure 3-12. | YUV Video Format (Internal Colorbars)                                      | . 3-16 |

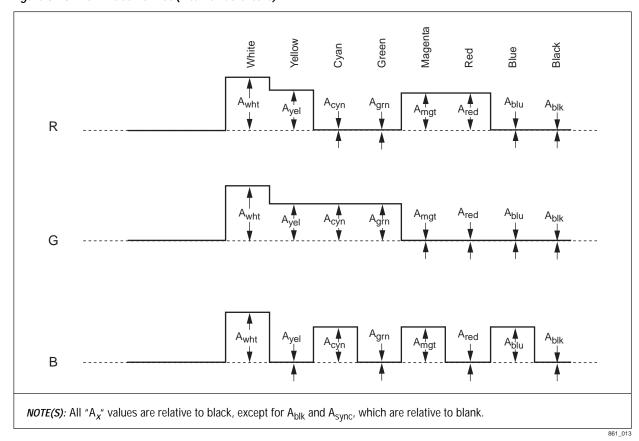

| Figure 3-13. | RGB Video Format (Internal Colorbars)                                      | . 3-17 |

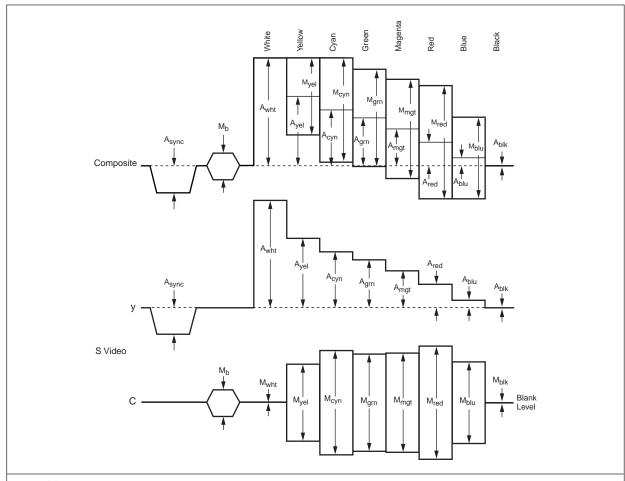

| Figure 3-14. | Composite and S-Video Format (Internal Colorbars)                          | . 3-18 |

| Figure 3-15. | SCART Function on ALTADDR Pin                                              | . 3-23 |

| Figure 3-16. | Teletext Timing                                                            | . 3-25 |

| Figure 3-17. | P:Q Ratio Counter Block Diagram                                            | . 3-26 |

| Figure 3-18. | WSS Waveform                                                               | . 3-28 |

| Figure 3-19. | CGMS Waveform.                                                             |        |

| Figure 3-20. | Closed Captioning or Extended Data Service Waveform (Null Sequence)        | . 3-30 |

| Figure 4-1.  | Typical Connection Diagram                                                 | 4-2    |

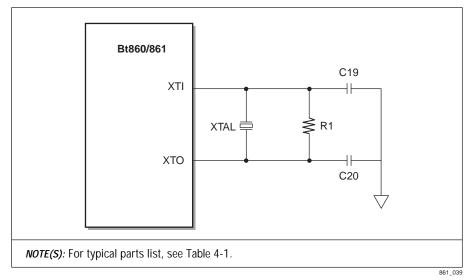

| Figure 4-2.  | Recommended Crystal Circuit                                                | 4-3    |

| Figure 5-1.  | Serial Programming Interface Timing Diagram                                | 5-1    |

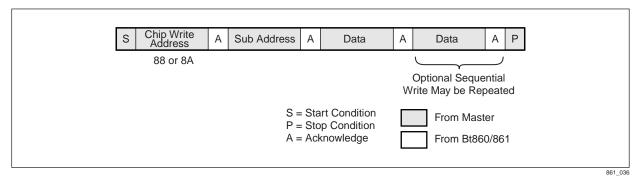

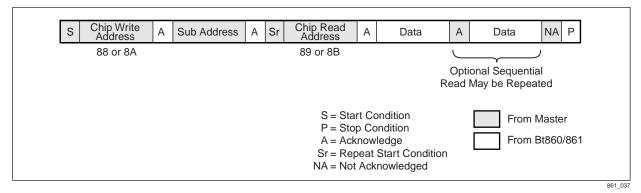

| Figure 5-2.  | Serial Programming Interface Typical Write Sequence                        | 5-3    |

| Figure 5-3.  | Serial Programming Interface Typical Read Sequence                         | 5-3    |

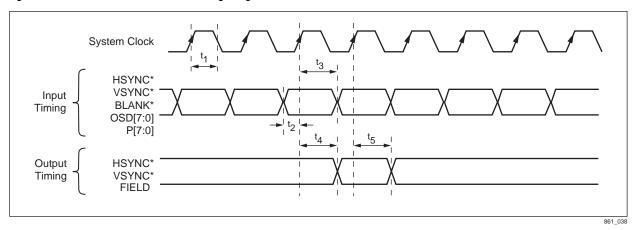

| Figure 6-1.  | Pixel and Control Data Timing Diagram                                      | 6-3    |

| Figure 6-2.  | 80 MQFP Package Diagram                                                    | 6-5    |

List of Figures Bt860/861

# **List of Tables**

| Table 1-1.  | Pin Assignments                                                             | 1-2         |

|-------------|-----------------------------------------------------------------------------|-------------|

| Table 2-1.  | Alpha Blending Configurations                                               | 2-4         |

| Table 2-2.  | Configurable Timing States                                                  | 2- <i>6</i> |

| Table 3-1.  | Target Video Parameters                                                     | 3-2         |

| Table 3-2.  | Register Programming Values for NTSC and PAL Video Standards (ITU-R BT.601) | 3-4         |

| Table 3-3.  | Register Programming Values for NTSC and PAL Video Standards (Square Pixel) | 3- <i>6</i> |

| Table 3-4.  | Register Programming Values for SECAM                                       | 3-8         |

| Table 3-5.  | 100/0/75/0 Colorbars as Described in EIA-770.1. EIA-770.1                   | 3-16        |

| Table 3-6.  | 100/0/75/0 Colorbars for a 625-Line System                                  | 3-17        |

| Table 3-7.  | Composite and Luminance Amplitude                                           | 3-18        |

| Table 3-8.  | Composite and Chrominance Magnitude                                         | 3-19        |

| Table 3-9.  | DAC Format Options                                                          | 3-22        |

| Table 3-10. | P:Q Ratio Counter Values                                                    | 3-26        |

| Table 3-11. | Teletext Line Disable                                                       | 3-27        |

| Table 3-12. | Closed Captioning and Extended Data Services Control Bits                   | 3-29        |

| Table 4-1.  | Typical Parts List                                                          | 4-4         |

| Table 5-1.  | Serial Address Configuration                                                | 5-2         |

| Table 5-2.  | Register Bit Map                                                            | 5-4         |

| Table 5-3.  | Register Index                                                              | 5-8         |

| Table 6-1.  | Absolute Maximum Ratings                                                    | 6-1         |

| Table 6-2.  | DC Characteristics                                                          | 6-2         |

| Table 6-3.  | AC Characteristics                                                          | 6-3         |

| Table 6-4.  | Video Quality Specifications                                                | 6-4         |

|             |                                                                             |             |

List of Tables Bt860/861

# 1.0 Functional Description

## 1.1 Pin Descriptions

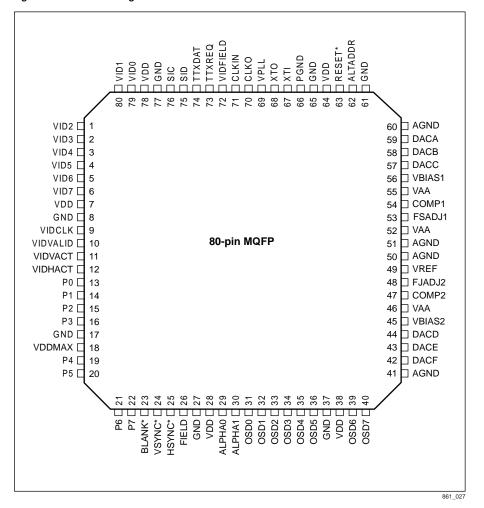

Figure 1-1. Pinout Diagram

### 1.1 Pin Descriptions

Table 1-1. Pin Assignments (1 of 3)

| Pin Name           | 1/0 | Pin #        | Description                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|--------------------|-----|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| PRIMARY VIDEO PORT |     |              |                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| P[7:0]             | I   | 22-19, 16-13 | Primary video input port (TTL compatible) (1). Accepts pixel data in 8-bit YCrCb 4:2:2 format in either ITU-R BT.601 or ITU-R BT.656 control formats. A higher index corresponds to a greater bit significance. By default, data is latched on the rising edge of the system clock (2).                                                                                                                                             |  |  |  |  |

| CLKO               | 0   | 70           | 2x pixel clock output. The clock generated by the PLL is produced at this pin when register bit CLKO_DIS = 0.                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| VSYNC*             | I/O | 24           | Vertical sync input/output (TTL compatible). As an output (master mode operation), VSYNC* follows the rising edge of the system clock. As an input (slave mode operation), VSYNC* is, by default, registered on the rising edge of the system clock <sup>(2)</sup> . The VSYNCI register bit controls the polarity of this signal.                                                                                                  |  |  |  |  |

| HSYNC*             | I/O | 25           | Horizontal sync input/output (TTL compatible). As an output (master mode operation), HSYNC* follows the rising edge of the system clock. As an input (slave mode operation), HSYNC* is, by default, registered on the rising edge of the system clock <sup>(2)</sup> . The HSYNCI register bit controls the polarity of this signal.                                                                                                |  |  |  |  |

| BLANK*             | I   | 23           | Composite blanking control input (TTL compatible). By default, BLANK* is registered on the rising edge of the system clock <sup>(2)</sup> . The video data inputs are ignored while BLANK* is a logical 0. The BLANKI register bit controls the polarity of this signal.                                                                                                                                                            |  |  |  |  |

| FIELD              | 0   | 26           | Field control output (TTL compatible). FIELD transitions after the rising edge of the system clock, two clock cycles following a falling HSYNC*. The FIELDI register bit controls the polarity of this signal. The state of this pin at power-up determines the default state of the PCLK_SEL register bit and the initial clock source. If not externally loaded, this pin will be pulled low with an internal pull-down resistor. |  |  |  |  |

|                    |     |              | SECONDARY VIDEO PORT                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| VID[7:0]           | I   | 6-1, 80-79   | Secondary video input port (TTL compatible). Accepts pixel data in 8-bit YCrCb 4:2:2 format. A higher index corresponds to a greater bit significance. By default, data on the VID port is latched by the rising edge of VIDCLK <sup>(1)</sup> (3).                                                                                                                                                                                 |  |  |  |  |

| VIDCLK             | I   | 9            | Pixel clock for secondary video input port <sup>(1)</sup> .                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| VIDHACT            | I   | 12           | Horizontal active display region. A logical 1 indicates data on VID[7:0] is in the horizontal display region. The VIDHACTI register bit controls the polarity of this signal. By default, data on VIDHACT is latched by the rising edge of VIDCLK <sup>(1)</sup> (3).                                                                                                                                                               |  |  |  |  |

| VIDVACT            | I   | 11           | Vertical active display region. The VIDVACTI register bit controls the polarity of this signal. By default, data on VIDVACT is latched by the rising edge of VIDCLK <sup>(1)</sup> (3).                                                                                                                                                                                                                                             |  |  |  |  |

| VIDFIELD           | I   | 72           | Field indicator for video input port. A logical 1 indicates data is from an even field. The VIDFIELDI register bit controls the polarity of this signal. By default, data on VIDFIELD is latched by the rising edge of VIDCLK <sup>(1)</sup> (3).                                                                                                                                                                                   |  |  |  |  |

| VIDVALID           | I   | 10           | Video data valid qualifier. A logical 1 indicates data on VID[7:0] is valid data. The VIDVALIDI register bit controls the polarity of this signal. By default, data on VIDVALID is latched by the rising edge of VIDCLK <sup>(1)</sup> (3).                                                                                                                                                                                         |  |  |  |  |

Multiport YCrCb to NTSC/PAL/SECAM

1.1 Pin Descriptions

Table 1-1. Pin Assignments (2 of 3)

| Pin Name                  | 1/0 | Pin #        | Description                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|---------------------------|-----|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| GRAPHIC AND BLENDING PINS |     |              |                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| OSD[7:0]                  | I   | 40-39, 36-31 | Dedicated graphic overlay port (TTL compatible.) Accepts pixel data in 8-bit YCrCb 4:2:2 format. Data is latched on the rising edge of the system clock <sup>(1)</sup> ( <sup>2)</sup> .                                                                                                                                                                                                              |  |  |  |

| ALPHA[1:0]                | I   | 30-29        | Alpha blend pins. Provides for 1-, 2-, or 4-bit external blend selection between video and graphic overlay data. Data is latched on the rising edge of the system $\operatorname{clock}^{(1)}(2)$ .                                                                                                                                                                                                   |  |  |  |

|                           |     | TEL          | ETEXT AND SERIAL CONTROL INTERFACE                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| TTXDAT                    | I   | 74           | Teletext data input (TTL compatible) <sup>(1)</sup> .                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| TTXREQ                    | 0   | 73           | Teletext request output (TTL compatible).                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| ALTADDR                   | I/O | 62           | Alternate slave address input (TTL compatible). This pin is sampled immediately following a power-up or pin reset. A logical 1 corresponds to write address of 0x88 and a read address of 0x89, while a logical 0 corresponds to a write address of 0x8A and a read address of 0x8B. See Chapter 5.0, for more detail. This pin also provides special SCART signals when register field SCART_SEL≠00. |  |  |  |

| SID                       | I/O | 75           | Serial programming interface data input/output (TTL compatible). Data is written to and read from the device via this serial bus.                                                                                                                                                                                                                                                                     |  |  |  |

| SIC                       | I   | 76           | Serial programming interface clock input (TTL compatible). The maximum clock rate is 400 kHz.                                                                                                                                                                                                                                                                                                         |  |  |  |

|                           |     |              | ANALOG VIDEO                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| DACA                      | 0   | 59           | DAC A output. See Table 3-9.                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| DACB                      | 0   | 58           | DAC B output. See Table 3-9.                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| DACC                      | 0   | 57           | DAC C output. See Table 3-9.                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| DACD                      | 0   | 44           | DAC D output. See Table 3-9.                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| DACE                      | 0   | 43           | DAC E output. See Table 3-9.                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| DACF                      | 0   | 42           | DAC F output. See Table 3-9.                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| FSADJ1<br>FSADJ2          | I   | 53<br>48     | Full-scale adjust control pin. Resistors RSET1 and RSET2 connected between these pins and AGND control the full-scale output current of the DACs. For standard operation, use the nominal values shown under Recommended Operating Conditions. FSADJ1 controls DACs A/B/C and FSADJ2 controls DACs D/E/F.                                                                                             |  |  |  |

| VREF                      | 0   | 49           | Voltage reference pin. A 1.0 $\mu$ F ceramic capacitor must be used to decouple this pin to AGND. The capacitor must be as close to the device as possible to keep lead lengths to an absolute minimum.                                                                                                                                                                                               |  |  |  |

| COMP1<br>COMP2            | 0   | 54<br>47     | Compensation pin. A 0.1 $\mu$ F ceramic capacitor must be used to decouple this pin to VAA. The capacitor must be as close to the device as possible to keep lead lengths to an absolute minimum.                                                                                                                                                                                                     |  |  |  |

| VBIAS1<br>VBIAS2          | 0   | 56<br>45     | DAC bias voltage. Use a 0.1 $\mu$ F ceramic capacitor to bypass this pin to AGND; the capacitor must be as close to the device as possible to keep lead lengths to an absolute minimum.                                                                                                                                                                                                               |  |  |  |

#### 1.1 Pin Descriptions

Table 1-1. Pin Assignments (3 of 3)

| Pin Name | 1/0         | Pin #                        | Description                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

|----------|-------------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|          | SYSTEM PINS |                              |                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| CLKIN    | I           | 71                           | 2x pixel clock input (TTL compatible).                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| RESET*   | I           | 63                           | Reset control input (TTL compatible). Setting to zero resets video timing (horizontal, vertical, subcarrier counters to the start of VSYNC of first field), the serial control interface, and all registers. RESET* must be a logical 1 for normal operation. Holding this pin low for 50 clocks or more will ensure that all functions are properly reset. |  |  |  |  |

| XTI      | I           | 67                           | Crystal input for PLL.                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| XTO      | 0           | 68                           | Crystal output for PLL.                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|          |             |                              | POWER AND GROUND                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| VAA      | _           | 55, 46, 52                   | Analog power. See Section 4.1 of this document.                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| VDD      | _           | 7, 28, 38, 64, 78            | Digital power. See Section 4.1 of this document.                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| AGND     | _           | 41, 50, 51, 60               | Analog ground. See Section 4.1 of this document.                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| GND      | _           | 8, 17, 27, 37,<br>61, 65, 77 | Digital ground. See Section 4.1 of this document.                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| VPLL     | _           | 69                           | Dedicated power supply for PLL.                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| PGND     | _           | 66                           | Dedicated ground for PLL.                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| VDDMAX   | I           | 18                           | This pin must be tied to the maximum digital input value. Use 3.3 V if only 3.3 V inputs are used, and 5 V if 3.3/5 V inputs are used.                                                                                                                                                                                                                      |  |  |  |  |

#### NOTE(S):

- (1) If these inputs are not used, they should be connected to GND.

- (2) These input are normally sampled on the rising edge of the system clock, but can be sampled on the falling edge by setting register bit PCLK\_EDGE = 1.

- (3) These inputs are normally sampled on the rising edge of VIDCLK, but can be sampled on the falling edge by setting register bit VIDCLK\_EDGE = 1.

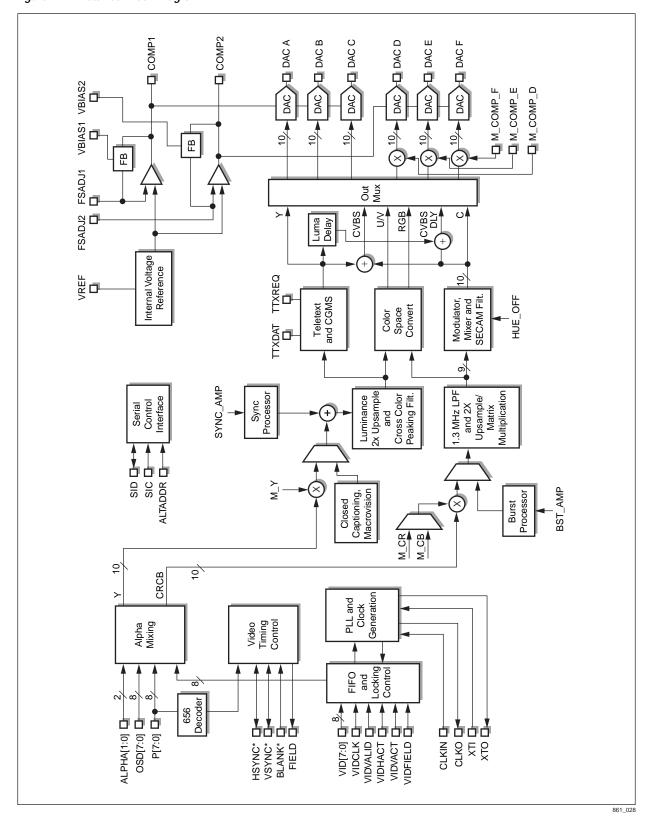

#### 1.2 Functional Overview

The Bt860/861 is a highly programmable 3.3 V multiport digital video encoder with pixel synchronization and per-pixel blending capabilities. It is equipped with three 8-bit YCrCb data ports that allow a variety of video and graphic overlay configurations useful in video set top box applications.

The three 8-bit YCrCb data ports allow two video streams and one alpha-blended overlay stream. For switching between video sources (such as a video decoder and an MPEG source), while providing a common OSD interface using the part's overlay and alpha capabilities.

The Bt860/861's VID port uses a PLL and FIFO to allow direct interfacing with asynchronous video sources, such as the Bt835 video decoder.

In slave mode, the Bt860/861 can be configured to accept either ITU-R BT.656-compliant timing (EAV and SAV codes) or ITU-R BT.601 data timing (HSYNC\* and VSYNC\* signals). The Bt860/861 can also act as timing master, producing ITU-R BT.601 timing.

The Bt860/861 supports worldwide video standards, including:

- NTSC-M (N. America, Taiwan, Japan)

- PAL-B, D, G, H, I (Europe, Asia)

- PAL-M (Brazil)

- PAL-N (Uruguay, Paraguay)

- PAL-Nc (Argentina)

- PAL-60, NTSC-443

- SECAM

The Bt860/861 has six 10-bit current-out video DACs, specifically designed for video systems requiring the generation of high quality composite, Y/C (S-Video), and simultaneous component YUV or RGB (SCART) video signals. Two of the composite output signals can be programmed with a 0–7 clock luminance delay. The connection status of each DAC can be dynamically monitored through the serial programming interface.

The Bt860/861 has several low power options, including sleep mode (only the serial programming interface and PLL are operational), individual DAC disable, PLL disable, and 3.3 V operation. The 3.3 V digital inputs can be configured to be 5 V-tolerant.

The luminance upsampling filter is enhanced to provide a narrow transition region and a low stopband. Programmable luminance sharpness filters provide 0,1, 2, and 3.5 dB peaking options at higher video frequencies, and four reduction filters are added for smoothed step response. To reduce the complexity of the required reconstruction filter, 2x upsampling is implemented.

The Bt860/861 can produce internally generated colorbars and blue field signals.

A 400 kHz serial programming interface (I<sup>2</sup>C-compatible) is provided for fast system programming.

The Bt860/861 provides support for Closed Captioning (CC) and Extended Data Services (XDS), Teletext (WST system B), Copy Generation Management System (CGMS), VARIS-II, and Wide Screen Signaling (WSS).

The Bt860 and Bt861 are functionally identical except that the Bt861 can output the Macrovision 7.x anticopy algorithm.

#### 1.2 Functional Overview

Figure 1-2. Detailed Block Diagram

# 2.0 Inputs and Timing

### 2.1 Reset

The Bt860/Bt861 has the following reset methods:

- · power-up reset

- RESET\* pin reset

- software reset register bit

Power-up reset occurs when the part is powered-up. A pin reset occurs when the RESET\* pin is held low. (It is recommended that the pin be held low for a minimum of 50 system clock cycles.) Both power-up and pin reset cause the initialization of all chip functions, including video timing and serial programming registers.

Writing a 1 to register bit SRESET (1B[7]) resets all serial programing registers to their default states, listed in Section 5.0.

## 2.1.1 Initialization and Power-up Configuration

At power-up all registers reset to their initial values (see Section 5.0).

The state of the FIELD pin at power-up (or pin reset) determines the default state of the PCLK\_SEL register bit and the initial clock source. If the FIELD pin is pulled high, the initial clock source is the CLKIN pin; if the FIELD pin is pulled low, the initial clock source is from the PLL and requires a crystal at the XTI and XTO pins. If not loaded, the FIELD pin is pulled low with the pin's internal pull-down resistor.

The power-up configuration is interlaced NTSC-M, 27 MHz black burst video, as listed in the default values of the register bit map.

**NOTE:** To enable active video, black burst video must be turned off by setting register bit EACTIVE (1D[1]) to 1. Other video configurations must be programmed using the part's serial programming interface registers.

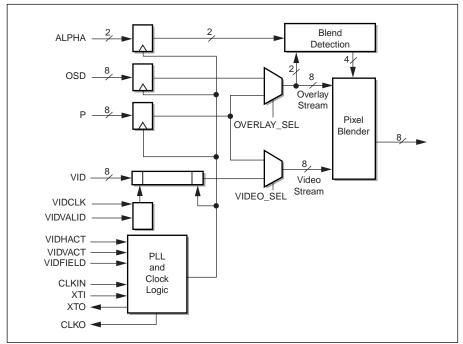

## 2.2 Digital Video Ports

Internally, data to the Bt860/861 is treated as either video, overlay, or alpha data. Video data is the primary visual program content, while overlay data is used for informational or navigational content displayed over the visual program. Alpha data controls the pixel blending of the video and overlay content. Sufficient flexibility exists in the Bt860/861 to allow for a variety of source and blending configurations and interesting visual effects.

Video data is supplied by either the P (Primary Video) port, or the VID (Secondary Video) port. Overlay data can be supplied by either the P port or the OSD (On Screen Display) port. Alpha data can be supplied by the ALPHA port, or embedded in the two LSBs of the overlay luminance data. Figure 2-1 illustrates the pixel latching and blending mechanism.

Figure 2-1. Pixel Latching and Blending Mechanism

861\_042

2.2 Digital Video Ports

#### 2.2.1 The P Port

The P port can accept video data from a variety of digital video sources. It is designed specifically to interface directly with commercial MPEG video decoders and D1 digital video sources. The P port supports both ITU-R BT.601 timing (HSYNC\* and VSYNC\* signals), and ITU-R BT.656 timing (SAV and EAV codes).

Data on the P[7:0] pins can be treated as either video or overlay data, controlled by the VIDEO\_SEL (1A[3]) and OVRLAY\_SEL (1A[4]) register bits (see Figure 2-1). Data on this port must be presented in 8-bit YCrCb 4:2:2 digital video format. The P[7:0] pins are latched using the system clock as configured using register bits PCLK\_SEL (19[7]) and PCLK\_EDGE (19[1]).

#### 2.2.2 The VID Port

The VID port is specially configured for broadcast video sources, such as from a television tuner or local cable system. It can accept a 27 MHz YCrCb 4:2:2 video stream at the same pixel rate as the other ports, or it can accommodate alternate clock rates, such as the 8xF<sub>SC</sub> clock rate used by the Bt835 family of video decoders. Since the time base for these sources is external to the system and therefore asynchronous to the local pixel clock, the Bt860/861 provides a mechanism that synchronizes these two domains. When using the VID port in locking mode, the Bt860/861 immediately synchronizes its vertical timing to the vertical timing presented on the VIDVACT pin, and gradually adjusts its horizontal timing and clock rate to further synchronize with the VID port. VIDCLK latches the incoming data into a FIFO, and data is extracted at the appropriate pixel rate for internal processing.

The average active horizontal pixel count must be equal to the value programmed into the HACTIVE register field. For example, the Bt835 generates pixels at a rate of 14.32 Mpix/s when used for NTSC video capture, but the actual valid pixel count per line is determined by the video mode required. For support of 27 MHz streams, 720 valid pixels will be delivered per line. This configuration is compatible with other video devices connected to the Bt860/861 and running with a continuous pixel rate of 13.5 Mpix/s. The Bt860/861 will generate the necessary video timing and pixel clock to act as master for the other video device.

The VID port can be configured as the video source by setting register bit VIDEO\_SEL (1A[3]) to 1. Data on this port must be presented in 8-bit YCrCb 4:2:2 digital video format.

#### 2.2.3 The OSD Port

The OSD port is functionally very similar to the P port, except that it cannot decode ITU-R BT.656 timing. As the overlay source, this port can be mixed with the video stream using one of the alpha-mixing modes described in Section 2.2.5. While intended as an overlay source, the OSD port can be configured to be the sole image content by using the appropriate blend programming.

The overlay source is selected by setting register bit OVRLAY\_SEL (1A[4]) to 1. Data on this port must be presented in 8-bit YCrCb 4:2:2 digital video format. The OSD[7:0] pins are latched using the system clock as configured by register bits PCLK\_SEL (19[7]) and PCLK\_EDGE (19[1]).

## 2.2.4 Overlay Modes and Alpha Blending

The Bt860/861 can be configured to display only a single video stream, or to mix any combination of two data ports (P, VID, and OSD). Programming register field ALPHAMODE (1A[6:5]) to 00 and register bit BLENDMODE (1A[7]) to 1 selects the internal video bus as the sole source of data, regardless of the alpha source. In this mode, either the VID port or the P port can be used as the video source, which is selected by register bit VIDEO SEL (1A[3]). Other combinations of the ALPHAMODE and BLENDMODE programming will allow blending of the video and overlay buses. Table 2-1 lists all valid input modes.

Table 2-1. Alpha Blending Configurations

| Configuration                  |                |              |                | Programming |           |           |             |                    |

|--------------------------------|----------------|--------------|----------------|-------------|-----------|-----------|-------------|--------------------|

| Video source                   | Overlay source | Alpha Source | Blending depth | BLENDMODE   | ALPHAMODE | VIDEO_SEL | OVERLAY_SEL | Use<br>ALPHA_LUT_X |

| VID                            | None           | None         | None           | 1           | 00        | 1         | Х           | No                 |

| VID                            | Р              | ALPHA[1:0]   | 1 bit          | 1           | 01        | 1         | 0           | Yes                |

| VID                            | Р              | ALPHA[1:0]   | 2 bit          | 1           | 10        | 1         | 0           | Yes                |

| VID                            | Р              | ALPHA[1:0]   | 4 bit          | 1           | 11        | 1         | 0           | No                 |

| VID                            | Р              | P LSBs       | 2 bit          | 0           | XX        | 1         | 0           | Yes                |

| VID                            | OSD            | ALPHA[1:0]   | 1 bit          | 1           | 01        | 1         | 1           | Yes                |

| VID                            | OSD            | ALPHA[1:0]   | 2 bit          | 1           | 10        | 1         | 1           | Yes                |

| VID                            | OSD            | ALPHA[1:0]   | 4 bit          | 1           | 11        | 1         | 1           | No                 |

| VID                            | OSD            | OSD LSBs     | 2 bit          | 0           | XX        | 1         | 1           | Yes                |

| Р                              | None           | None         | None           | 1           | 00        | 0         | Х           | No                 |

| Р                              | OSD            | ALPHA[1:0]   | 1 bit          | 1           | 01        | 0         | 1           | Yes                |

| Р                              | OSD            | ALPHA[1:0]   | 2 bit          | 1           | 10        | 0         | 1           | Yes                |

| Р                              | OSD            | ALPHA[1:0]   | 4 bit          | 1           | 11        | 0         | 1           | No                 |

| Р                              | OSD            | OSD LSBs     | 2 bit          | 0           | XX        | 0         | 1           | Yes                |

| NOTE(S): X or XX = Don't care. |                |              |                |             |           |           |             |                    |

Data from the overlay source may be applied with varying levels of transparency, from fully transparent, no overlay, to fully opaque, full overlay. A 4-bit blend multiplier provides sixteen levels of mixing. The value 1111 is a special case allowing the overlay data to pass completely unmixed. In all other cases the value applied to the video path is (1 - blend / 16), and the value applied to the overlay path is (blend / 16), where blend is the 4-bit multiplier value.

Two methods are used to generate the 4-bit multiplier. The multiplier value can come either from a four-entry by 4-bit lookup table (LUT), or directly from the ALPHA pins. In both cases, the blend multiplier value will be applied to both luma and chroma for the co-sited components (Cb0:Y0:Cr0) and a separate multiplier applied for the (Y1) component.

#### 2.2.5 Alpha Pin Blending

The ALPHA[1:0] pins are used to select the amount of blending per pixel when BLENDMODE = 1. The pins are sampled at the system clock rate and samples during both luma and chroma components may be captured to create 1-, 2-, or 4-bit blend factors. For 1- and 2-bit blend modes, the multiplier LUT (in registers ALPHA\_LUT\_0 through ALPHA\_LUT\_3 is programmed with user-defined multiplier values.

In 1-bit blend mode, the ALPHA[0] pin indexes registers ALPHA\_LUT\_0 and ALPHA\_LUT\_3 to generate the multiplier value. In 2-bit blend mode, the ALPHA[1:0] pins are used as a 2-bit index for registers ALPHA\_LUT\_0 through ALPHA\_LUT\_3.

In 4-bit blend mode, the four bits required are captured in successive load clocks from ALPHA[1:0]. The two LSBs of the 4-bit value are latched during the luma portion of the overlay data load, and the two MSBs are latched during the chroma component load. These four bits provide a direct multiplier for the blending module. Figure 2-2 illustrates the alpha blending timing diagram.

Figure 2-2. Alpha Blending Timing Diagram

861\_026

## 2.2.6 Content-based Blending

Content-based blending uses the two LSBs of the overlay byte associated with the luma pixel to address the multiplier lookup table (registers ALPHA\_LUT\_0 through ALPHA\_LUT\_3). This method is selected by setting BLENDMODE = 0, and is a convenient means of using blending when no alpha pins exist from the overlay device.

## 2.3 Configurations and Timing

The Bt860/861 is capable of various ITU-R BT.601, ITU-R BT.656, and decoder-locked configurations. Table 2-2 lists several ITU-R BT.601 and ITU-R BT.656 configurations, and Section 2.3.3 discusses decoder-locked configurations. In any of these configurations, it is possible to synchronize a primary video source with an alternate video source. These two sources can then be alpha-mixed, or independently selected for external display. Alpha mixing is discussed in detail in Section 2.2.5.

Table 2-2. Configurable Timing States

| Description                                                                                                              | Timing<br>Mode | SLAVE | EN_656 | SYNC_CFG |

|--------------------------------------------------------------------------------------------------------------------------|----------------|-------|--------|----------|

| Bt860/861 is timing master, HSYNC*, VSYNC*, and FIELD <sup>(1)</sup> , are outputs.                                      | 1              | 0     | 0      | 1        |

| Bt860/861 is timing slave, timing derived from HSYNC*, VSYNC*, and BLANK* signals <sup>(2)</sup> .                       | 2              | 1     | 0      | Х        |

| Bt860/861 is timing slave, timing derived from ITU-R BT.656 codes. HSYNC*, and VSYNC* are unused.                        | 3              | 1     | 1      | 0        |

| Bt860/861 is timing slave, timing derived from ITU-R BT.656 codes. HSYNC*, VSYNC*, and FIELD <sup>(1)</sup> are outputs. | 4              | 1     | 1      | 1        |

#### NOTE(S):

- (1) Decoder locking using the VID port requires the part to be in timing mode 1, except SYNC\_CFG = 1 is only required if synchronization with other sources is required.

- (2) Either the BLANK\* pin or the HBLANK, VBLANK, HACTIVE, and VACTIVE register can be used for blanking.

- 3. Configurations not listed are not recommended.

- 4. X = Don't care.

Multiport YCrCb to NTSC/PAL/SECAM

2.3 Configurations and Timing

## 2.3.1 ITU-R BT.601 Configurations and Timing

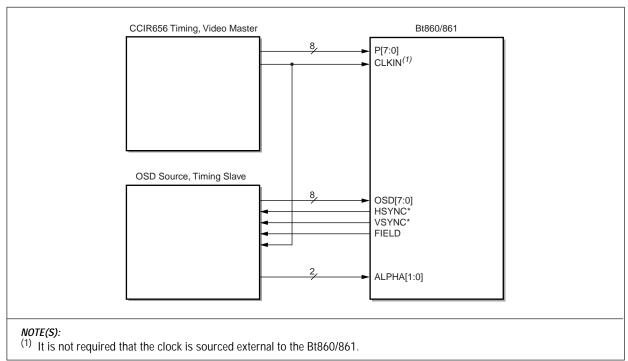

Master and slave ITU-R BT.601 configurations are listed in Table 2-2 as timing modes 1 and 2. Timing mode 1 is the ITU-R BT.601 master mode. An example connection diagram is illustrated in Figure 2-3. In this example, both video sources are slaved to the Bt860/861.

Figure 2-3. Timing Mode 1 Connection Example

861\_009

Timing mode 2 is the ITU-R BT.601 slave mode. An example connection diagram is illustrated in Figure 2-4. In this example, the source feeding the P port is the timing master, and both the optional OSD source and the Bt860/861 are timing slaves. Although additional sources are shown in these diagrams, it is not necessary to have more than one video source.

Figure 2-4. Timing Mode 2 Connection Example

861\_007

When the Bt860/861 is configured for ITU-R BT.601 timing, the HSYNC\*, VSYNC\*, FIELD, and BLANK\* pins synchronize the Bt860/861 to external video sources. In master mode, HSYNC\* field, and VSYNC\* are outputs and the BLANK\* pin is not used. All timing is generated internally and blanking is determined by the HBLANK, VBLANK, HACTIVE, and VACTIVE registers. In slave mode, HSYNC\*, VSYNC\* and BLANK\* are inputs and the encoder's timing is controlled by an external master. Blanking is set either by the internal HBLANK, VBLANK, HACTIVE, and VACTIVE registers (register bit BLK\_IGNORE = 1) or by a blanking signal on the BLANK\* pin (register bit BLK\_IGNORE = 0).

If the registers are used to determine video blanking (register bit BLK\_IGNORE = 1), the first component of the first active pixel of a line should be presented to the encoder at HBLANK + 2 rising system clock edges after the falling edge of HSYNC\* for master mode, and HBLANK + 3 rising system clock edges after the falling edge of HSYNC\* for slave mode. The correct order of the pixel components is  $Cb_0$ ,  $Y_0$ ,  $Cr_0$ ,  $Y_1$ ,  $Cb_2$ ,  $Y_2$ ,  $Cr_2$ .... Figure 2-5 illustrates this timing relationship.

Figure 2-5. Pixel Timing for Timing Modes 1 and 2

#### NOTE(S):

- Blanking times ( $t_1$ ) are listed in Tables 3-1 through 3-4. Desired front porch blanking is set by the HBLANK register. HBLANK =  $t_1 + 14$

- (2) The number of active pixels per line (t<sub>2</sub>) is set by the HACTIVE register.

- (3) The total number of system clocks per line  $(t_3)$  is set by the HCLK register.

- (4) The first component of the first active pixel of the line should be placed HBLANK + 2 (or 3 for slave mode) rising system clock edges after falling HSYNC\*(t<sub>4</sub>) in order to coincide with the end of horizontal blanking.

- When the BLANK\* pin is used, the first component of the first pixel must arrive 3 rising system clock edges after the falling edge of BLANK\* (t<sub>5</sub>).

861\_006

If the BLANK\* signal is used to determine video blanking (in slave mode only), the first component of the first active pixel of a line should be presented to the encoder three rising system clock edges after the falling edge of the BLANK\* signal. Figure 2-5 illustrates this relationship.

2.0 Inputs and Timing Bt860/861

The HBLANK register sets the line blanking time from the midpoint of the falling edge of the analog horizontal sync pulse to the end of blanking. The HACTIVE register sets the number of active pixels after the horizontal blanking period has ended. See Tables 3-1 through 3-4 for appropriate HBLANK and HACTIVE programming values for various NTSC, PAL, and SECAM video standards.

Pixel and data timing (P, OSD, ALPHA, HSYNC\*, VSYNC\*, BLANK\*) are by default, latched into the Bt860/861 on the rising edge of the system clock, but can be latched on the falling edge of the system clock if register bit PCLK\_EDGE (19[1]) is set high. The system clock can be seen on CLKO or CLKIN when appropriate. Legal setup and hold times must be observed.

## 2.3.2 ITU-R BT.656 Timing

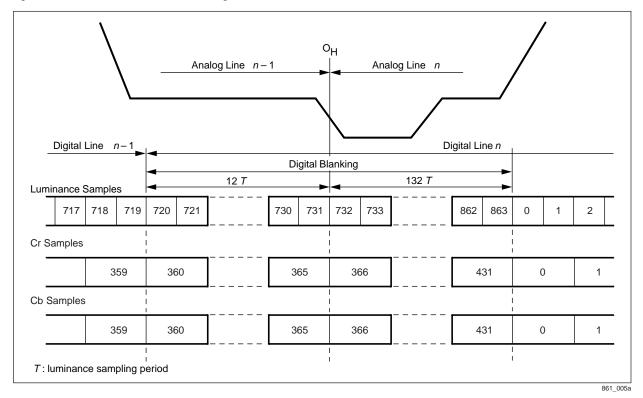

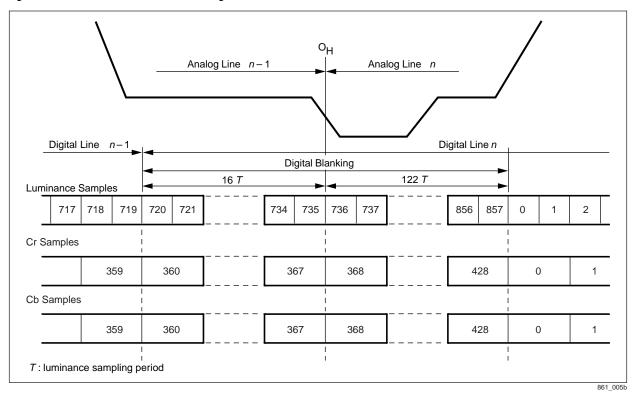

Data on the P port can be routed through the part's ITU-R BT.656 timing translator only when the system clock is 27 MHz, by setting register bit EN\_656 (1A[2]) high. This is accomplished using timing modes 3 or 4 (see Table 2-2). Figure 2-6 illustrates an example connection diagram. ITU-R BT.656 timing derives vertical and horizontal timing information from the video data stream (SAV and EAV codes). These codes are internally converted to HSYNC\* and VSYNC\* signals, which can be then be produced on the Bt860/861's HSYNC\*, VSYNC\*, and FIELD pins. ITU-R BT.656 timing (also known as D1 timing) is illustrated in Figures 2-7 and 2-8. The resultant video is automatically aligned to conform to ITU-R BT.656 video and blanking placement. The contents of the HBLANK, HACTIVE, VACTIVE, and VBLANK registers are ignored, except when register bit BLK\_IGNORE = 1.

Figure 2-6. Timing Mode 3 and 4 Connection Example

861\_010

Figure 2-7. 625 Line ITU-R BT.656 Timing

Figure 2-8. 525 Line ITU-R BT.656 Timing

D860DSA Conexant 2-11

2.0 Inputs and Timing Bt860/861

2.3 Configurations and Timing

Multiport YCrCb to NTSC/PAL/SECAM

In this configuration, the Bt860/861 is a slave to the ITU-R BT.656 data stream. However, the HSYNC\*, VSYNC\* and FIELD pins can be configured as outputs for synchronization with a video slave on the OSD port. While in this configuration, the HSYNC\*, VSYNC\*, and FIELD timing is identical to ITU-R BT.601 master mode timing.

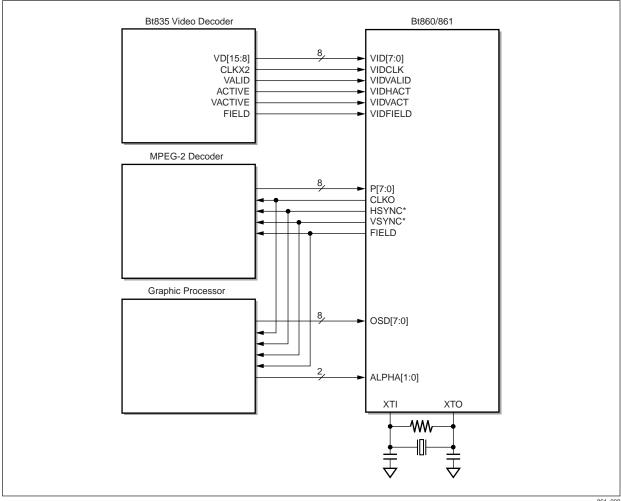

## 2.3.3 VID Port (Video Decoder Locked) Timing

The VID port can accept video signals from a video decoder, such as the Bt835, and is buffered using a FIFO to support asynchronous video streams. The internal logic will automatically pulls data from the FIFO when required. The data lines for the VID port are VID[7:0], and the control lines are VIDCLK, VIDHACT, VIDVACT, VIDFIELD, and VIDVALID. Figure 2-9 illustrates an example configuration using the Bt835 and the Bt860. The PLL and the horizontal and vertical counters are adjusted to track the incoming data on the VID port. The Bt860/861 can be configured to output HSYNC\* and VSYNC\* signals in order to synchronize with the P, OSD, and ALPHA signals. Timing mode 1 must be used when the VID port is selected in conjunction with a source on the P or OSD ports. The PLL (using the XTI and XTO inputs) must be selected as the system clock source.

Multiport YCrCb to NTSC/PAL/SECAM

2.3 Configurations and Timing

Figure 2-9. Video Decoder Connection Example

861\_008

Follow these steps to lock a video decoder to this port:

- 1. Connect to the data and control pins as illustrated in Figure 2-9.

- 2. Select the correct effective clock frequency using the PLL\_FRACT and PLL\_INT registers, and choose the XTAL inputs as the system clock source using register bit PCLK\_SEL (19[7]). See Section 2.4.1, and the PLL\_FRACT and PLL\_INT register descriptions.

- 3. Set these locking registers to the following values:

| FIELD NAME    | VALUE |  |

|---------------|-------|--|

| XL_MDSEL[1:0] | 11    |  |

| XL_SATEN      | 1     |  |

| XL_SAT[3:0]   | 1     |  |

- **4.** Set the part for Timing Mode 1 (see Table 2-2).

- 5. Initiate locking by setting the LOCK (1C[5]) register bit high and the LC\_RST (1C[6]) register bit low.

*NOTE:* When unlocking the Bt861 to a source on the VID port, set the LOCK (1C[5]) register bit low and the LC\_RST (1C[6]) register bit high.

2.4 Clock Selection

## 2.4 Clock Selection

The internal pixel clock (PCLK) can be derived from either the CLKIN input or the crystal inputs. The PCLK\_SEL register bit (19[7]) controls which of these two inputs will become the pixel clock.

## 2.4.1 Crystal Inputs and the PLL

The crystal inputs (XTI and XTO) drive a buffered oscillator to create a clock. This clock is routed through the PLL if register bit BY\_PLL (1D[3]) is 0, and bypasses the PLL untouched if BY\_PLL is 1. Figure 2-10 illustrates the clock block diagram. If PCLK\_SEL is low, this becomes the system clock.

The PLL\_FRACT and the PLL\_INT registers determine the PLL clock frequency multiplier. The default setting generates a 27.0 MHz clock, using a 14.31818 MHz crystal.

If the VID port is enabled using the LOCK (1C[5]) register bit, the PLL is controlled by the tracking servo mechanism.

The frequency programmed through PLL\_FRACT and PLL\_INT is used as a base around which the VID port locking mechanism adjusts the system clock. The PLL\_FRACT and PLL\_INT registers remain unaffected by the locking mechanism, and when locking is disabled (through the LOCK bit), the PLL\_FRACT and PLL\_INT registers once again determine the exact PLL frequency.

Figure 2-10. Timing and Clock Block Diagram

2-14 Conexant D860DSA

## 3.0 Digital Processing and Functionality

## 3.1 Video

#### 3.1.1 Video Standards

The Bt860/861 supports worldwide video standards, including NTSC-M (N. America, Taiwan, Japan), PAL-B, D, G, H, I (Europe, Asia), PAL-M (Brazil), PAL-N (Uruguay, Paraguay), PAL-Nc (Argentina), PAL-60, NTSC-443, and SECAM.

Table 3-1 lists the target video timing and amplitude used to generate the appropriate register programming for various forms of NTSC, PAL, and SECAM as listed in Tables 3-2, 3-3, and 3-4 respectively. These tables provide the programming values of only those registers required to create that particular video standard. Ancillary data, input configuration, and ignored or common value register values are not shown. Video parameter registers which are not relevant to a particular standard are described as such in the register detail section of this document.

Table 3-2 lists the register values required to program the various forms of PAL and NTSC in ITU-R BT.601 resolution, and Table 3-3 lists the register values required to program the various forms of PAL and NTSC in square pixel resolution. Table 3-4 lists register values required to program the encoder for SECAM output, with and without synchronization bottleneck pulses.

Table 3-1. Target Video Parameters (1 of 2)

| )                                         |                     |                     |                     |                    |                     |                     |                     |                    |                             |

|-------------------------------------------|---------------------|---------------------|---------------------|--------------------|---------------------|---------------------|---------------------|--------------------|-----------------------------|

|                                           |                     |                     |                     |                    | Video Standard      | 70                  |                     |                    |                             |

| Parameter Description                     | MTSC-M              | NTSC-J              | NTSC-443            | PAL-M              | PAL-60              | PAL-<br>B,D,G,H,I   | PAL-N               | PAL-Nc             | SECAM                       |

| HSYNC Width (µs)                          | 4.7                 | 4.7                 | 4.7                 | 4.7                | 4.7                 | 4.7                 | 4.7                 | 4.7                | 4.7                         |

| HSYNC and VSYNC Height (V)                | 0.286               | 0.286               | 0.2857              | 0.2857             | 0.3                 | 6.0                 | 0.2857              | 0.3                | 0.3                         |

| HSYNC Rise/Fall Time<br>(10% to 90%) (ns) | 150                 | 150                 | 150                 | 150                | 150                 | 200(1)              | 200                 | 200                | 200                         |

| Burst or Subcarrier Start (µs)            | 5.3                 | 5.3                 | 5.3                 | 5.8                | 5.3                 | 9.6                 | 5.6                 | 5.6                | 5.6                         |

| Burst Width (µs)                          | 2.514<br>(9 cycles) | 2.514<br>(9 cycles) | 2.25<br>(10 cycles) | 2.52<br>(9 cycles) | 2.25<br>(10 cycles) | 2.25<br>(10 cycles) | 2.25<br>(10 cycles) | 2.51<br>(9 cycles) | N/A                         |

| Subcarrier Frequency <sup>(2)</sup> (Hz)  | 3579545             | 3579545             | 4433618.75          | 3579611.49         | 4433618.75          | 4433618.75          | 4433618.75          | 3582056.25         | for=4406250,<br>fob=4250000 |

| Burst or Subcarrier Height (V)            | 0.2857              | 0.2857              | 0.2857              | 0.306              | 0.3                 | 0.3                 | 0.3                 | 0.3                | 0.161                       |

| Phase Alternation                         | ON                  | NO                  | NO                  | YES                | YES                 | YES                 | YES                 | YES                | NO                          |

| Number of Lines per Frame                 | 525                 | 525                 | 525                 | 525                | 525                 | 979                 | 972                 | 625                | 625                         |

| Line Frequency (Hz)                       | 15734.264           | 15734.264           | 15734.264           | 15734.264          | 15734.264           | 15625               | 15625               | 15625              | 15625                       |

| Field Frequency (Hz)                      | 59.94               | 59.94               | 59.94               | 59.94              | 59.94               | 20                  | 20                  | 50                 | 50                          |

| Setup                                     | YES                 | NO                  | YES                 | YES                | NO                  | NO                  | YES                 | NO                 | NO                          |

| First Active Line                         | 22 <sup>(3)</sup>   | 22 <sup>(3)</sup>   | 22 <sup>(3)</sup>   | 22 <sup>(3)</sup>  | 22 <sup>(3)</sup>   | 23 <sup>(4)</sup>   | 23 <sup>(4)</sup>   | 23(4)              | 23(4)                       |

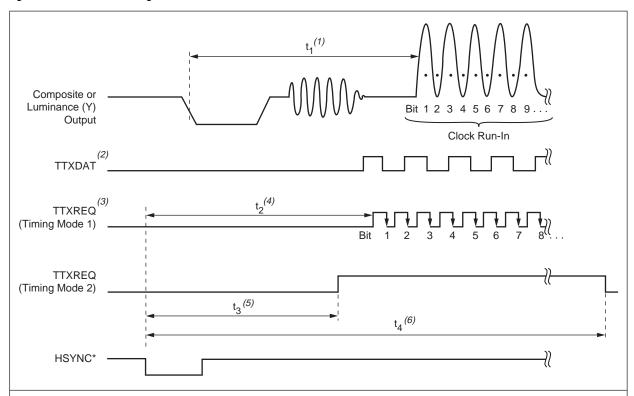

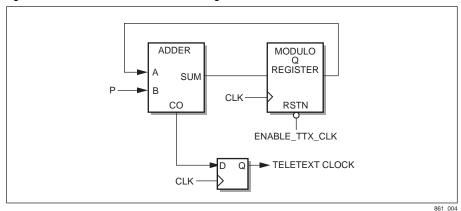

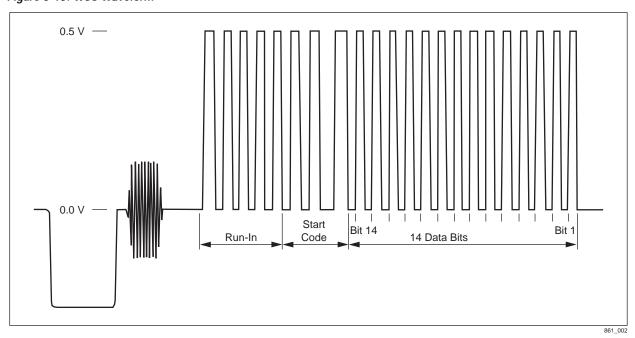

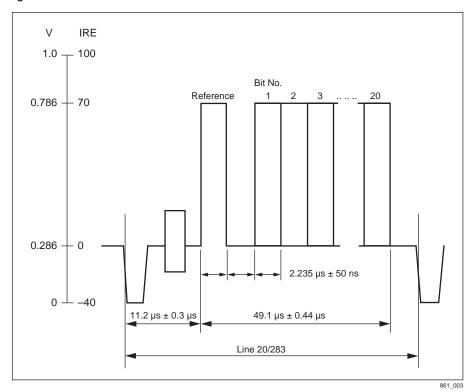

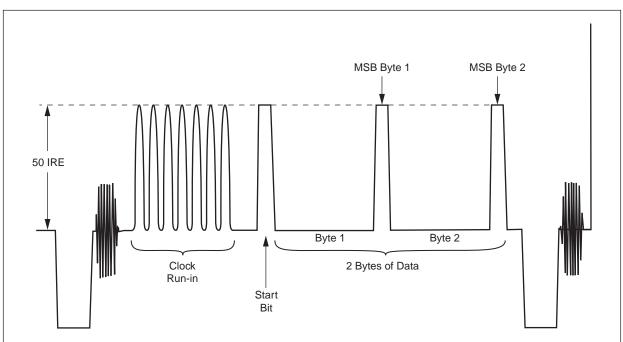

| Last Active Line                          | 262 <sup>(3)</sup>  | 262 <sup>(3)</sup>  | 262 <sup>(3)</sup>  | 262 <sup>(3)</sup> | 262 <sup>(3)</sup>  | 306(4)              | 309(4)              | 309(4)             | 309(4)                      |