# 128Mbit RDRAM® (F-die)

256K x 16 bit x 32s Banks

Direct RDRAM™

Version 1.41 January 2004

# **Change History**

#### Version 1.4 (September 2003)

- First Copy (Version 1.4 is named to unify the version of component and device operation datasheets)

- Based on the 128Mbit E-die RDRAM® for short channel Datasheet Version 1.4

#### **Version 1.41 (January 2004)**

- Add the part number for leaded package.

#### **Overview**

The RDRAM® device is a general purpose high-performance memory device suitable for use in a broad range of applications including communications, graphics, video and any other application where high bandwidth and low latency are required.

The 128Mbit RDRAM devices are extremely high-speed CMOS DRAMs organized as 8M words by 16. The use of Rambus Signaling Level (RSL) technology permits 800MHz transfer rates while using conventional system and board design technologies.

RDRAM devices are capable of sustained data transfers at 1.25 ns per two bytes (10ns per sixteen bytes).

The architecture of RDRAM devices allows the highest sustained bandwidth for multiple, simultaneous randomly addressed memory transactions. The separate control and data buses with independent row and column control yield over 95% bus efficiency. The RDRAM device's 32 banks support up to four simultaneous transactions.

System oriented features for mobile, graphics and communications include power management and byte masking.

#### **Features**

- ♦ Highest sustained bandwidth per DRAM device

- 1.6 GB/s sustained data transfer rate

- Separate control and data buses for maximized efficiency

- Separate row and column control buses for easy scheduling and highest performance

- 32 banks: four transactions can take place simultaneously at full bandwidth data rates

- ◆ Low latency features

- Write buffer to reduce read latency

- 3 precharge mechanisms for controller flexibility

- Interleaved transactions

- Advanced power management:

- Multiple low power states allows flexibility in power consumption versus time to transition to active state

- Power-down self-refresh

- ♦ Organization: 1Kbyte pages and 32 banks

- ◆ Uses Rambus Signaling Level (RSL) interface

- ♦ WBGA package(54 Balls)

Figure 1: Direct RDRAM CSP Package

The 128Mbit RDRAM devices are offered in a horizontal center-bond fanout CSP package.

#### **Key Timing Parameters/Part Numbers**

|                          |      | Spe                 | ed                                             |                               |  |  |

|--------------------------|------|---------------------|------------------------------------------------|-------------------------------|--|--|

| Organization             | Bin  | I/O<br>Freq.<br>MHz | t <sub>RAC</sub><br>(Row<br>Access<br>Time) ns | Part Number                   |  |  |

| 256Kx16x32s <sup>a</sup> | -CS8 | 800                 | 45                                             | K4R271669F-T <sup>b</sup> CS8 |  |  |

| 256Kx16x32s              | -CS8 | 800                 | 45                                             | K4R271669F-R <sup>c</sup> CS8 |  |  |

a. "32s" - 32 banks which use a "split" bank architecture.

b. "T" - Lead free consumer package.

c. "R" - Leaded consumer package.

#### **Pinouts and Definitions**

The following table shows the pin assignments of the center-bonded RDRAM package.

7 DQA7 DQA4 CFM CFMN RQ5 RQ3 DQB0 DQB4 DQB7 6 GND DQA5 DQA2 VDDA RQ6 RQ2 DQB1 DQB5 GND VDD GNDA VDD VDD CMD GND GND VDD SIO0 5 4 VDD GND VDD SIO1 3 SCK GND GND GND GND VREF VCMOS DQB2 VCMOS 2 DQA6 DQA1 RQ7 RQ1 DQB6 1 NC DQA3 DQA0 CTMN CTM RQ4 RQ0 DQB3 NC  $\mathbf{C}$ F  $\mathbf{G}$ **Top View**  $\mathbf{A}$ В D  $\mathbf{E}$ Н J

Table 1: Center-Bonded CSP Device (Top View)

#### b. Top marking example

For consumer package, pin #1(ROW 1, COL A) is located at the A1 position on the top side and the A1 position is marked by the marker "  $\bullet$  ".

**Table 2: Pin Description**

| Signal                | I/O      | Type              | # Pins<br>center | Description                                                                                                                                       |

|-----------------------|----------|-------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| SIO1,SIO0             | I/O      | CMOS <sup>a</sup> | 2                | Serial input/output. Pins for reading from and writing to the control registers using a serial access protocol. Also used for power management.   |

| CMD                   | ı        | CMOS <sup>a</sup> | 1                | Command input. Pins used in conjunction with SIO0 and SIO1 for reading from and writing to the control registers. Also used for power management. |

| SCK                   | I        | CMOS <sup>a</sup> | 1                | Serial clock input. Clock source used for reading from and writing to the control registers                                                       |

| V <sub>DD</sub>       |          |                   | 6                | Supply voltage for the RDRAM core and interface logic.                                                                                            |

| V <sub>DDa</sub>      |          |                   | 1                | Supply voltage for the RDRAM analog circuitry.                                                                                                    |

| V <sub>CMOS</sub>     |          |                   | 2                | Supply voltage for CMOS input/output pins.                                                                                                        |

| GND                   |          |                   | 9                | Ground reference for RDRAM core and interface.                                                                                                    |

| GNDa                  |          |                   | 1                | Ground reference for RDRAM analog circuitry.                                                                                                      |

| DQA7DQA0              | I/O      | RSL <sup>b</sup>  | 8                | Data byte A. Eight pins which carry a byte of read or write data between the Channel and the RDRAM device.                                        |

| CFM                   | I        | RSL <sup>b</sup>  | 1                | Clock from master. Interface clock used for receiving RSL signals from the Channel. Positive polarity.                                            |

| CFMN                  | I        | RSL <sup>b</sup>  | 1                | Clock from master. Interface clock used for receiving RSL signals from the Channel. Negative polarity                                             |

| V <sub>REF</sub>      |          |                   | 1                | Logic threshold reference voltage for RSL signals                                                                                                 |

| CTMN                  | 1        | RSL <sup>b</sup>  | 1                | Clock to master. Interface clock used for transmitting RSL signals to the Channel. Negative polarity.                                             |

| СТМ                   | I        | RSL <sup>b</sup>  | 1                | Clock to master. Interface clock used for transmitting RSL signals to the Channel. Positive polarity.                                             |

| RQ7RQ5 or<br>ROW2ROW0 | 1        | RSL <sup>b</sup>  | 3                | Row access control. Three pins containing control and address information for row accesses.                                                       |

| RQ4RQ0 or<br>COL4COL0 | 1        | RSL <sup>b</sup>  | 5                | Column access control. Five pins containing control and address information for column accesses.                                                  |

| DQB7<br>DQB0          | I/O      | RSL <sup>b</sup>  | 8                | Data byte B.Eight pins which carry a byte of read or write data between the Channel and the RDRAM device.                                         |

| NC                    |          |                   | 2                | No Connection.                                                                                                                                    |

| Total pin count pe    | er packa | ge                | 54               |                                                                                                                                                   |

a. All CMOS signals are high-true; a high voltage is a logic one and a low voltage is logic zero.

b. All RSL signals are low-true; a low voltage is a logic one and a high voltage is logic zero.

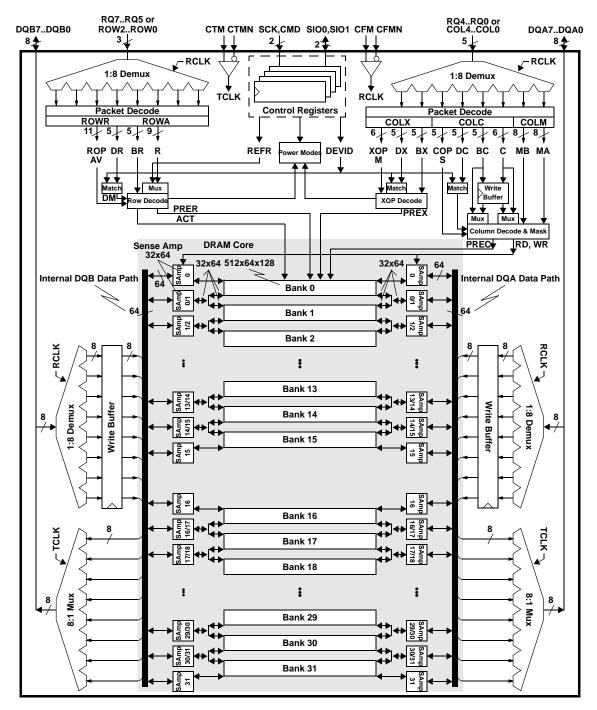

Figure 2: 128Mbit(256Kx16x32s) RDRAM Device Block Diagram

#### **General Description**

Figure 2 is a block diagram of the 128Mbit RDRAM device. It consists of two major blocks: a "core" block built from banks and sense amps similar to those found in other types of DRAM and a Direct Rambus<sup>TM</sup> interface block which permits an external controller to access this core at up to 1.6GB/s.

**Control Registers:** The CMD, SCK, SIO0 and SIO1 pins appear in the upper center of Figure 2. They are used to write and read a block of control registers. These registers supply the RDRAM configuration information to a controller and they select the operating modes of the device. The nine bit REFR value is used for tracking the last refreshed row. Most importantly, the five bit DEVID specifies the device address of the RDRAM device on the Channel

**Clocking:** The CTM and CTMN pins (Clock-To-Master) generate TCLK (Transmit Clock), the internal clock used to transmit read data. The CFM and CFMN pins (Clock-From-Master) generate RCLK (Receive Clock), the internal clock signal used to receive write data and to receive the ROW and COL pins.

**DQA,DQB Pins:** These 16 pins carry read (Q) and write (D) data across the Channel. They are multiplexed/de-multiplexed from/to two 64-bit data paths (running at one-eighth the data frequency) inside the RDRAM device.

**Banks:** The 16Mbyte core of the RDRAM device is divided into thirty two 0.5Mbyte banks, each organized as 512 rows, with each row containing 64 dualocts, and each dualoct containing 16 bytes. A dualoct is the smallest unit of data that can be addressed.

**Sense Amps:** The RDRAM device contains 34 sense amps. Each sense amp consists of 512 bytes of fast storage (256 for DQA and 256 for DQB) and can hold one-half of one row of one bank of the RDRAM device. The sense amp may hold any of the 512 half-rows of an associated bank. However, each sense amp is shared between two adjacent banks of the RDRAM device(except for sense amps 0, 15, 16 and 31). This introduces the restriction that adjacent banks may not be simultaneously accessed.

**RQ Pins:** These pins carry control and address information. They are broken into two groups. RQ7..RQ5 are also called ROW2..ROW0, and are used primarily for controlling row accesses. RQ4..RQ0 are also called COL4..COL0, and are used primarily for controlling column accesses.

**ROW Pins:** The principle use of these three pins is to manage the transfer of data between the banks and the sense

amps of the RDRAM device. These pins are de-multiplexed into a 24-bit ROWA (row-activate) or ROWR (row-operation) packet.

**COL Pins:** The principle use of these five pins is to manage the transfer of data between the DQA/DQB pins and the sense amps of the RDRAM device. These pins are demultiplexed into a 23-bit COLC (column-operation) packet and either a 17-bit COLM (mask) packet or a 17-bit COLX (extended-operation) packet.

**ACT Command:** An ACT (activate) command from an ROWA packet causes one of the 512 rows of the selected bank to be loaded to its associated sense amps (two 256 byte sense amps for DQA and two for DQB).

**PRER Command:** A PRER (precharge) command from an ROWR packet causes the selected bank to release its two associated sense amps, permitting a different row in that bank to be activated, or permitting adjacent banks to be activated.

**RD** Command: The RD (read) command causes one of the 64 dualocts of one of the sense amps to be transmitted on the DQA/DQB pins of the Channel.

WR Command: The WR (write) command causes a dualoct received from the DQA/DQB data pins of the Channel to be loaded into the write buffer. There is also space in the write buffer for the BC bank address and C column address information. The data in the write buffer is automatically retired (written with optional bytemask) to one of the 64 dualocts of one of the sense amps during a subsequent COP command. A retire can take place during a RD, WR, or NOCOP to another device, or during a WR or NOCOP to the same device. The write buffer will not retire during a RD to the same device. The write buffer reduces the delay needed for the internal DQA/DQB data path turnaround

**PREC Precharge:** The PREC, RDA and WRA commands are similar to NOCOP, RD and WR, except that a precharge operation is performed at the end of the column operation. These commands provide a second mechanism for performing precharge.

**PREX Precharge:** After a RD command, or after a WR command with no byte masking (M=0), a COLX packet may be used to specify an extended operation (XOP). The most important XOP command is PREX. This command provides a third mechanism for performing precharge.

#### **Packet Format**

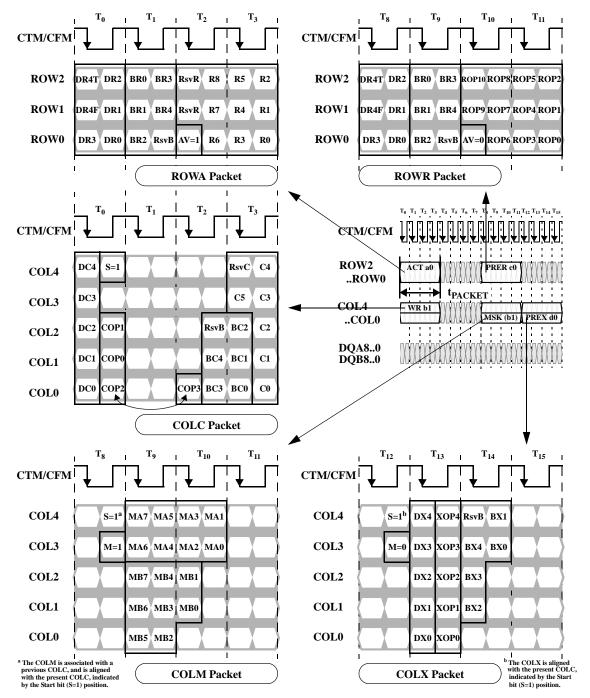

Figure 3 shows the formats of the ROWA and ROWR packets on the ROW pins. Table 3 describes the fields which comprise these packets. DR4T and DR4F bits are encoded to contain both the DR4 device address bit and a framing bit which allows the ROWA or ROWR packet to be recognized by the RDRAM device.

The AV (ROWA/ROWR packet selection) bit distinguishes between the two packet types. Both the ROWA and ROWR packet provide a five bit device address and a five bit bank address. An ROWA packet uses the remaining bits to specify a nine bit row address, and the ROWR packet uses the remaining bits for an eleven bit opcode field. Note the use of the "RsvX" notation to reserve bits for future address field extension.

Table 3: Field Description for ROWA Packet and ROWR Packet

| Field     | Description                                                                                    |

|-----------|------------------------------------------------------------------------------------------------|

| DR4T,DR4F | Bits for framing (recognizing) a ROWA or ROWR packet. Also encodes highest device address bit. |

| DR3DR0    | Device address for ROWA or ROWR packet.                                                        |

| BR4BR0    | Bank address for ROWA or ROWR packet. RsvB denotes bits ignored by the RDRAM device.           |

| AV        | Selects between ROWA packet (AV=1) and ROWR packet (AV=0).                                     |

| R8R0      | Row address for ROWA packet. RsvR denotes bits ignored by the RDRAM device.                    |

| ROP10ROP0 | Opcode field for ROWR packet. Specifies precharge, refresh, and power management functions.    |

Figure 3 also shows the formats of the COLC, COLM, and COLX packets on the COL pins. Table 4 describes the fields which comprise these packets.

The COLC packet uses the S (Start) bit for framing. A COLM or COLX packet is aligned with this COLC packet, and is also framed by the S bit.

The 23 bit COLC packet has a five bit device address, a five bit bank address, a six bit column address, and a four bit opcode. The COLC packet specifies a read or write command, as well as some power management commands.

The remaining 17 bits are interpreted as a COLM (M=1) or COLX (M=0) packet. A COLM packet is used for a COLC write command which needs bytemask control. The COLM packet is associated with the COLC packet from at least t<sub>RTR</sub> earlier. An COLX packet may be used to specify an independent precharge command. It contains a five bit device address, a five bit bank address, and a five bit opcode. The COLX packet may also be used to specify some house-keeping and power management commands. The COLX packet is framed within a COLC packet but is not otherwise associated with any other packet.

Table 4: Field Description for COLC Packet, COLM Packet, and COLX Packet

| Field    | Description                                                                                                 |

|----------|-------------------------------------------------------------------------------------------------------------|

| S        | Bit for framing (recognizing) a COLC packet, and indirectly for framing COLM and COLX packets.              |

| DC4DC0   | Device address for COLC packet.                                                                             |

| BC4BC0   | Bank address for COLC packet. RsvB denotes bits reserved for future extension (controller drives 0's).      |

| C5C0     | Column address for COLC packet. RsvC denotes bits ignored by the RDRAM device.                              |

| COP3COP0 | Opcode field for COLC packet. Specifies read, write, precharge, and power management functions.             |

| M        | Selects between COLM packet (M=1) and COLX packet (M=0).                                                    |

| MA7MA0   | Bytemask write control bits. 1=write, 0=no-write. MA0 controls the earliest byte on DQA70.                  |

| MB7MB0   | Bytemask write control bits. 1=write, 0=no-write. MB0 controls the earliest byte on DQB70.                  |

| DX4DX0   | Device address for COLX packet.                                                                             |

| BX4BX0   | Bank address for COLX packet. RsvB denotes bits reserved for future extension (controller drives 0's).      |

| XOP4XOP0 | Opcode field for COLX packet. Specifies precharge, I <sub>OL</sub> control, and power management functions. |

Direct RDRAM<sup>™</sup>

**Figure 3: Packet Formats**

#### Field Encoding Summary

Table 5 shows how the six device address bits are decoded for the ROWA and ROWR packets. The DR4T and DR4F encoding merges a fifth device bit with a framing bit. When neither bit is asserted, the device is not selected. Note that a broadcast operation is indicated when both bits are set. Broadcast operation would typically be used for refresh and power management commands. If the device is selected, the DM (DeviceMatch) signal is asserted and an ACT or ROP command is performed.

Table 5: Device Field Encodings for ROWA Packet and ROWR Packet

| DR4T | DR4F | Device Selection Device Match signal (DM) |                                                                    |  |  |

|------|------|-------------------------------------------|--------------------------------------------------------------------|--|--|

| 1    | 1    | All devices (broadcast)                   | DM is set to 1                                                     |  |  |

| 0    | 1    | One device selected                       | DM is set to 1 if {DEVID4DEVID0} == {0,DR3DR0} else DM is set to 0 |  |  |

| 1    | 0    | One device selected                       | DM is set to 1 if {DEVID4DEVID0} == {1,DR3DR0} else DM is set to 0 |  |  |

| 0    | 0    | No packet present                         | DM is set to 0                                                     |  |  |

Table 6 shows the encodings of the remaining fields of the ROWA and ROWR packets. An ROWA packet is specified by asserting the AV bit. This causes the specified row of the specified bank of this device to be loaded into the associated sense amps.

An ROWR packet is specified when AV is not asserted. An 11 bit opcode field encodes a command for one of the banks of this device. The PRER command causes a bank and its two associated sense amps to precharge, so another row or an adjacent bank may be activated. The REFA (refresh-activate) command is similar to the ACT command, except the

row address comes from an internal register REFR, and REFR is incremented at the largest bank address. The REFP (refresh-precharge) command is identical to a PRER command.

The NAPR, NAPRC, PDNR, ATTN, and RLXR commands are used for managing the power dissipation of the RDRAM and are described in more detail in "Power State Management" on page 50. The TCEN and TCAL commands are used to adjust the output driver slew rate and they are described in more detail in "Current and Temperature Control" on page 56.

Table 6: ROWA Packet and ROWR Packet Field Encodings

| D 7 79          | 4.77 |     |             | RO | P10 | RC | )P0 ] | Field | i | Nome |                   |                                                                                                                |  |

|-----------------|------|-----|-------------|----|-----|----|-------|-------|---|------|-------------------|----------------------------------------------------------------------------------------------------------------|--|

| DM <sup>a</sup> | AV   | 10  | 9           | 8  | 7   | 6  | 5     | 4     | 3 | 2:0  | Name              | Command Description                                                                                            |  |

| 0               | -    | -   | -           | -  | -   | -  | -     | -     | - |      | -                 | No operation.                                                                                                  |  |

| 1               | 1    | Rov | Row address |    |     |    |       |       |   |      | ACT               | Activate row R8R0 of bank BR4BR0 of device and move device to ATTN <sup>b</sup> .                              |  |

| 1               | 0    | 1   | 1           | 0  | 0   | 0  | xc    | x     | х | 000  | PRER              | Precharge bank BR4BR0 of this device.                                                                          |  |

| 1               | 0    | 0   | 0           | 0  | 1   | 1  | 0     | 0     | х | 000  | REFA              | Refresh (activate) row REFR8REFR0 of bank BR4BR0 of device.  Increment REFR if BR4BR0 = 11111 (see Figure 52). |  |

| 1               | 0    | 1   | 0           | 1  | 0   | 1  | 0     | 0     | х | 000  | REFP              | Precharge bank BR4BR0 of this device after REFA (see Figure 52).                                               |  |

| 1               | 0    | x   | x           | 0  | 0   | 0  | 0     | 1     | х | 000  | PDNR              | Move this device into the powerdown (PDN) power state (see Figure 49).                                         |  |

| 1               | 0    | x   | x           | 0  | 0   | 0  | 1     | 0     | х | 000  | NAPR              | Move this device into the nap (NAP) power state (see Figure 49).                                               |  |

| 1               | 0    | x   | x           | 0  | 0   | 0  | 1     | 1     | х | 000  | NAPRC             | Move this device into the nap (NAP) power state conditionally                                                  |  |

| 1               | 0    | x   | x           | x  | х   | x  | x     | x     | 0 | 000  | ATTN <sup>b</sup> | Move this device into the attention (ATTN) power state (see Figure 47).                                        |  |

| 1               | 0    | x   | x           | x  | х   | x  | x     | x     | 1 | 000  | RLXR              | Move this device into the standby (STBY) power state (see Figure 48).                                          |  |

| 1               | 0    | 0   | 0           | 0  | 0   | 0  | 0     | 0     | х | 001  | TCAL              | Temperature calibrate this device (see Figure 55).                                                             |  |

| 1               | 0    | 0   | 0           | 0  | 0   | 0  | 0     | 0     | х | 010  | TCEN              | Temperature calibrate/enable this device (see Figure 55).                                                      |  |

| 1               | 0    | 0   | 0           | 0  | 0   | 0  | 0     | 0     | 0 | 000  | NOROP             | No operation.                                                                                                  |  |

a. The DM (Device Match signal) value is determined by the DR4T,DR4F, DR3..DR0 field of the ROWA and ROWR packets. See Table 5.

b. The ATTN command does not cause a RLX-to-ATTN transition for a broadcast operation (DR4T/DR4F=1/1).

c. An "x" entry indicates which commands may be combined. For instance, the three commands PRER/NAPRC/RLXR may be specified in one ROP value (011000111000).

Table 7 shows the COP field encoding. The device must be in the ATTN power state in order to receive COLC packets. The COLC packet is used primarily to specify RD (read) and WR (write) commands. Retire operations (moving data from the write buffer to a sense amp) happen automatically. See Figure 18 for a more detailed description.

The COLC packet can also specify a PREC command, which precharges a bank and its associated sense amps. The RDA/WRA commands are equivalent to combining RD/WR with a PREC. RLXC (relax) performs a power mode transition. See "Power State Management" on page 50.

**Table 7: COLC Packet Field Encodings**

| s | DC4 DC0<br>(select device) <sup>a</sup> | COP30             | Name  | Command Description                                                                        |

|---|-----------------------------------------|-------------------|-------|--------------------------------------------------------------------------------------------|

| 0 |                                         |                   | -     | No operation.                                                                              |

| 1 | /= (DEVID40)                            |                   | -     | Retire write buffer of this device.                                                        |

| 1 | == (DEVID40)                            | x000 <sup>b</sup> | NOCOP | Retire write buffer of this device.                                                        |

| 1 | == (DEVID40)                            | x001              | WR    | Retire write buffer of this device, then write column C5C0 of bank BC4BC0 to write buffer. |

| 1 | == (DEVID40)                            | x010              | RSRV  | Reserved, no operation.                                                                    |

| 1 | == (DEVID40)                            | x011              | RD    | Read column C5C0 of bank BC4BC0 of this device.                                            |

| 1 | == (DEVID40)                            | x100              | PREC  | Retire write buffer of this device, then precharge bank BC4BC0 (see Figure 15).            |

| 1 | == (DEVID40)                            | x101              | WRA   | Same as WR, but precharge bank BC4BC0 after write buffer (with new data) is retired.       |

| 1 | == (DEVID40)                            | x110              | RSRV  | Reserved, no operation.                                                                    |

| 1 | == (DEVID40)                            | x111              | RDA   | Same as RD, but precharge bank BC4BC0 afterward.                                           |

| 1 | == (DEVID40)                            | 1xxx              | RLXC  | Move this device into the standby (STBY) power state (see Figure 48).                      |

Table 8 shows the COLM and COLX field encodings. The M bit is asserted to specify a COLM packet with two 8 bit bytemask fields MA and MB. If the M bit is not asserted, an COLX is specified. It has device and bank address fields, and an opcode field. The primary use of the COLX packet is to permit an independent PREX (precharge) command to be

specified without consuming control bandwidth on the ROW pins. It is also used for the CAL(calibrate) and SAM (sample) current control commands (see "Current and Temperature Control" on page 56), and for the RLXX power mode command (see "Power State Management" on page

Table 8: COLM Packet and COLX Packet Field Encodings

| M | DX4 DX0<br>(selects device) | XOP40              | Name    | Command Description                                                                            |

|---|-----------------------------|--------------------|---------|------------------------------------------------------------------------------------------------|

| 1 |                             | -                  | MSK     | MB/MA bytemasks used by WR/WRA.                                                                |

| 0 | /= (DEVID40)                |                    |         | No operation.                                                                                  |

| 0 | == (DEVID40)                | 00000              | NOXOP   | No operation.                                                                                  |

| 0 | == (DEVID40)                | 1xxx0 <sup>a</sup> | PREX    | Precharge bank BX4BX0 of this device (see Figure 15).                                          |

| 0 | == (DEVID40)                | x10x0              | CAL     | Calibrate (drive) I <sub>OL</sub> current for this device (see Figure 54).                     |

| 0 | == (DEVID40)                | x11x0              | CAL/SAM | Calibrate (drive) and Sample (update) I <sub>OL</sub> current for this device (see Figure 54). |

| 0 | == (DEVID40)                | xxx10              | RLXX    | Move this device into the standby (STBY) power state (see Figure 48).                          |

| 0 | == (DEVID40)                | xxxx1              | RSRV    | Reserved, no operation.                                                                        |

a. An "x" entry indicates which commands may be combined. For instance, the two commands PREX/RLXX may be specified in one XOP value (10010).

a. "/=" means not equal, "==" means equal.

b. An "x" entry indicates which commands may be combined. For instance, the two commands WR/RLXC may be specified in one COP value (1001).

#### **Electrical Conditions**

**Table 9: Electrical Conditions**

| Symbol                                  | Parameter and Conditions                                                                           | Min                           | Max                                 | Unit   |

|-----------------------------------------|----------------------------------------------------------------------------------------------------|-------------------------------|-------------------------------------|--------|

| T <sub>J</sub>                          | Junction temperature under bias                                                                    | -                             | 95                                  | °C     |

| V <sub>DD</sub> , V <sub>DDA</sub>      | Supply voltage                                                                                     | 2.50 - 0.13                   | 2.50 + 0.13                         | V      |

| $V_{\mathrm{DD,N,}} V_{\mathrm{DDA,N}}$ | Supply voltage droop (DC) during NAP interval (t <sub>NLIMIT</sub> )                               | -                             | 2.0                                 | %      |

| v <sub>DD,N</sub> , v <sub>DDA,N</sub>  | Supply voltage ripple (AC) during NAP interval (t <sub>NLIMIT</sub> )                              | -2.0                          | 2.0                                 | %      |

| V <sub>CMOS</sub> <sup>a</sup>          | Supply voltage for CMOS pins (2.5V controllers)<br>Supply voltage for CMOS pins (1.8V controllers) | V <sub>DD</sub><br>1.80 - 0.1 | V <sub>DD</sub><br>1.80 + 0.2       | V<br>V |

| V <sub>REF</sub>                        | Reference voltage                                                                                  | 1.40- 0.2                     | 1.40 + 0.2                          | V      |

| V <sub>DIL</sub>                        | RSL data input - low voltage                                                                       | V <sub>REF</sub> - 0.5        | V <sub>REF</sub> - 0.2              | V      |

| $V_{\mathrm{DIH}}$                      | RSL data input - high voltage <sup>b</sup>                                                         | V <sub>REF</sub> + 0.2        | V <sub>REF</sub> + 0.5              | V      |

| R <sub>DA</sub>                         | RSL data asymmetry: $R_{DA} = (V_{DIH} - V_{REF}) / (V_{REF} - V_{DIL})$                           | 0.67                          | 1.00                                | -      |

| V <sub>CM</sub>                         | RSL clock input - common mode $V_{CM} = (V_{CIH} + V_{CIL})/2$                                     | 1.3                           | 1.8                                 | V      |

| V <sub>CIS,CTM</sub>                    | RSL clock input swing: $V_{CIS} = V_{CIH} - V_{CIL}$ (CTM,CTMN pins).                              | 0.35                          | 1.00                                | V      |

| V <sub>CIS,CFM</sub>                    | RSL clock input swing: $V_{CIS} = V_{CIH} - V_{CIL}$ (CFM,CFMN pins).                              | 0.225                         | 1.00                                | V      |

| V <sub>IL,CMOS</sub>                    | CMOS input low voltage                                                                             | - 0.3 <sup>c</sup>            | V <sub>CMOS</sub> /2 - 0.25         | V      |

| V <sub>IH,CMOS</sub>                    | CMOS input high voltage                                                                            | $V_{CMOS}/2 + 0.25$           | V <sub>CMOS</sub> +0.3 <sup>d</sup> | V      |

a.  $V_{CMOS}$  must remain on as long as  $V_{DD}$  is applied and cannot be turned off. b.  $V_{DIH}$  is typically equal to  $V_{TERM}$  (1.8V±0.1V) under DC conditions in a system. c. Voltage undershoot is limited to -0.7V for a duration of less than 5ns.

d. Voltage overshoot is limited to  $V_{\hbox{\scriptsize CMOS}}$  +0.7V for a duration of less than 5ns.

# K4R271669F

#### **Electrical Characteristics**

**Table 10: Electrical Characteristics**

| Symbol               | Parameter and Conditions                                                 | Min                    | Max  | Unit    |

|----------------------|--------------------------------------------------------------------------|------------------------|------|---------|

| $\Theta_{ m JC}$     | Junction-to-Case thermal resistance                                      | -                      | 0.5  | °C/Watt |

| I <sub>REF</sub>     | V <sub>REF</sub> current @ V <sub>REF,MAX</sub>                          | -10                    | 10   | μΑ      |

| I <sub>OH</sub>      | RSL output high current @ (0≤V <sub>OUT</sub> ≤V <sub>DD</sub> )         | -10                    | 10   | μΑ      |

| I <sub>ALL</sub>     | RSL $I_{OL}$ current @ $V_{OL} = 0.9V$ , $V_{DD,MIN}$ , $T_{J,MAX}^{a}$  | 30.0                   | 90.0 | mA      |

| $\Delta I_{OL}$      | RSL I <sub>OL</sub> current resolution step                              | -                      | 2.0  | mA      |

| r <sub>OUT</sub>     | Dynamic output impedance @ V <sub>OL</sub> = 0.9V                        | 150                    | -    | Ω       |

| I <sub>OL,NOM</sub>  | RSL $I_{OL}$ current @ $V_{OL} = 1.0V^{b,c}$                             | 26.6                   | 30.6 | mA      |

| I <sub>I,CMOS</sub>  | CMOS input leakage current @ (0≤V <sub>I,CMOS</sub> ≤V <sub>CMOS</sub> ) | -10.0                  | 10.0 | μΑ      |

| V <sub>OL,CMOS</sub> | CMOS output voltage @ I <sub>OL,CMOS</sub> = 1.0mA                       | -                      | 0.3  | V       |

| V <sub>OH,CMOS</sub> | CMOS output high voltage @ I <sub>OH,CMOS</sub> = -0.25mA                | V <sub>CMOS</sub> -0.3 | -    | V       |

a. This measurement is made in manual current control mode; i.e. with all output device legs sinking current.

b. This measurement is made in automatic current control mode after at least 64 current control calibration operations to a device and after CCA and CCB are initialized to a value of 64. This value applies to all DQA and DQB pins.

c. This measurement is made in automatic current control mode in a  $25\Omega$  test system with  $V_{TERM}$ = 1.714V and  $V_{REF}$ = 1.357V and with the ASYMA and ASYMB register fields set to 0.

# **Timing Conditions**

**Table 11: Timing Conditions**

| Symbol                               | Parameter                                                                                                                  | Min                   | Max        | Unit                  | Figure(s)              |

|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-----------------------|------------|-----------------------|------------------------|

| t <sub>CYCLE</sub>                   | CTM and CFM cycle times (-800)                                                                                             | 2.50                  | 3.83       | ns                    | Figure 56              |

| t <sub>CR</sub> , t <sub>CF</sub>    | CTM and CFM input rise and fall times. Use the minimum value of these parameters during testing.                           | 0.2                   | 0.5        | ns                    | Figure 56              |

| $t_{CH}, t_{CL}$                     | CTM and CFM high and low times                                                                                             | 40%                   | 60%        | t <sub>CYCLE</sub>    | Figure 56              |

| t <sub>TR</sub>                      | CTM-CFM differential (MSE/MS=0/0)<br>CTM-CFM differential (MSE/MS=1/1) <sup>a</sup>                                        | 0.0<br>0.9            | 1.0<br>1.0 | t <sub>CYCLE</sub>    | Figure 43<br>Figure 56 |

| t <sub>DCW</sub>                     | Domain crossing window                                                                                                     | -0.1                  | 0.1        | t <sub>CYCLE</sub>    | Figure 62              |

| $t_{\mathrm{DR}},t_{\mathrm{DF}}$    | DQA/DQB/ROW/COL input rise/fall times (20% to 80%). Use the minimum value of these parameters during testing.              | 0.2                   | 0.65       | ns                    | Figure 57              |

| tS, tH                               | DQA/DQB/ROW/COL-to-CFM setup/hold @ t <sub>CYCLE</sub> =2.50ns                                                             | 0.250 <sup>b</sup>    | -          | ns                    | Figure 57              |

| t <sub>DR1</sub> , t <sub>DF1</sub>  | SIO0, SIO1 input rise and fall times                                                                                       | -                     | 5.0        | ns                    | Figure 59              |

| $t_{\mathrm{DR2}}, t_{\mathrm{DF2}}$ | CMD, SCK input rise and fall times                                                                                         | -                     | 2.0        | ns                    | Figure 59              |

|                                      | SCK cycle time - Serial control register transactions                                                                      | 1000                  | -          | ns                    | Figure 59              |

| t <sub>CYCLE1</sub>                  | SCK cycle time - Power transitions                                                                                         | 10                    | -          | ns                    | Figure 59              |

| $t_{\text{CH1}}, t_{\text{CL1}}$     | SCK high and low times                                                                                                     | 4.25                  | -          | ns                    | Figure 59              |

| t <sub>S1</sub>                      | CMD setup time to SCK rising or falling edge <sup>c</sup>                                                                  | 1.25                  | -          | ns                    | Figure 59              |

| t <sub>H1</sub>                      | CMD hold time to SCK rising or falling edge <sup>c</sup>                                                                   | 1                     | -          | ns                    | Figure 59              |

| $t_{S2}$                             | SIO0 setup time to SCK falling edge                                                                                        | 40                    | -          | ns                    | Figure 59              |

| t <sub>H2</sub>                      | SIO0 hold time to SCK falling edge                                                                                         | 40                    | -          | ns                    | Figure 59              |

| $t_{S3}$                             | PDEV setup time on DQA50 to SCK rising edge.                                                                               | 0                     | -          | ns                    | Figure 50              |

| t <sub>H3</sub>                      | PDEV hold time on DQA50 to SCK rising edge.                                                                                | 5.5                   | -          | ns                    | Figure 60              |

| t <sub>S4</sub>                      | ROW20, COL40 setup time for quiet window                                                                                   | -1                    | -          | t <sub>CYCLE</sub>    | Figure 50              |

| t <sub>H4</sub>                      | ROW20, COL40 hold time for quiet window <sup>d</sup>                                                                       | 5                     | -          | t <sub>CYCLE</sub>    | Figure 50              |

| t <sub>NPQ</sub>                     | Quiet on ROW/COL bits during NAP/PDN entry                                                                                 | 4                     | -          | t <sub>CYCLE</sub>    | Figure 49              |

| t <sub>READTOCC</sub>                | Offset between read data and CC packets (same device)                                                                      | 12                    | -          | t <sub>CYCLE</sub>    | Figure 54              |

| t <sub>CCSAMTOREAD</sub>             | Offset between CC packet and read data (same device)                                                                       | 8                     | -          | t <sub>CYCLE</sub>    | Figure 54              |

| t <sub>CE</sub>                      | CTM/CFM stable before NAP/PDN exit                                                                                         | 2                     | -          | t <sub>CYCLE</sub>    | Figure 50              |

| t <sub>CD</sub>                      | CTM/CFM stable after NAP/PDN entry                                                                                         | 100                   | -          | t <sub>CYCLE</sub>    | Figure 49              |

| t <sub>FRM</sub>                     | ROW packet to COL packet ATTN framing delay                                                                                | 7                     | -          | t <sub>CYCLE</sub>    | Figure 48              |

| t <sub>NLIMIT</sub>                  | Maximum time in NAP mode                                                                                                   |                       | 10.0       | μs                    | Figure 47              |

| t <sub>REF</sub>                     | Refresh interval                                                                                                           |                       | 32         | ms                    | Figure 52              |

| t <sub>BURST</sub>                   | Interval after PDN or NAP (with self-refresh) exit in which all banks of the RDRAM device must be refreshed at least once. |                       | 200        | μs                    | Figure 53              |

| t <sub>CCTRL</sub>                   | Current control interval                                                                                                   | 34 t <sub>CYCLE</sub> | 100ms      | ms/t <sub>CYCLE</sub> | Figure 54              |

**Table 11: Timing Conditions**

| Symbol               | Parameter                                      | Min | Max   | Unit               | Figure(s) |

|----------------------|------------------------------------------------|-----|-------|--------------------|-----------|

| t <sub>TEMP</sub>    | Temperature control interval                   |     | 100   | ms                 | Figure 55 |

| t <sub>TCEN</sub>    | TCE command to TCAL command                    | 150 | -     | t <sub>CYCLE</sub> | Figure 55 |

| t <sub>TCAL</sub>    | TCAL command to quiet window                   | 2   | 2     | t <sub>CYCLE</sub> | Figure 55 |

| t <sub>TCQUIET</sub> | Quiet window (no read data)                    | 140 | -     | t <sub>CYCLE</sub> | Figure 55 |

| t <sub>PAUSE</sub>   | RDRAM device delay (no RSL operations allowed) |     | 200.0 | μs                 | page 38   |

$a.\ MSE/MS\ are\ fields\ of\ the\ SKIP\ register.\ For\ this\ combination\ (skip\ override)\ the\ tDCW\ parameter\ range\ is\ effectively\ 0.0\ to\ 0.0.$

$b. \ t_{S,MIN} \ and \ t_{H,MIN} \ for \ other \ t_{CYCLE} \ values \ can \ be \ interpolated \ between \ or \ extrapolated \ from \ the \ timings \ at \ the \ 3 \ specified \ t_{CYCLE} \ values.$

c. With  $V_{IL,CMOS}$ =0.5 $V_{CMOS}$ -0.4V and  $V_{IH,CMOS}$ =0.5 $V_{CMOS}$ +0.4V d. Effective hold becomes  $t_{H4}$ '= $t_{H4}$ +[PDNXA•64• $t_{SCYCLE}$ + $t_{PDNXB,MAX}$ ]-[PDNX\*256• $t_{SCYCLE}$ ]

$if \ [PDNX \bullet 256 \bullet t_{SCYCLE}] < [PDNXA \bullet 64 \bullet t_{SCYCLE} + t_{PDNXB,MAX}]. \ See \ Figure \ 50.$

# **Timing Characteristics**

**Table 12: Timing Characteristics**

| Symbol             | Parameter                                                                   | Min    | Max    | Unit               | Figure(s) |

|--------------------|-----------------------------------------------------------------------------|--------|--------|--------------------|-----------|

| t <sub>Q</sub>     | CTM-to-DQA/DQB output time @ t <sub>CYCLE</sub> =2.50ns                     | -0.310 | +0.310 | ns                 | Figure 58 |

| $t_{QR}, t_{QF}$   | DQA/DQB output rise and fall times                                          | 0.2    | 0.45   | ns                 | Figure 58 |

| t <sub>Q1</sub>    | SCK(neg)-to-SIO0 delay @ C <sub>LOAD,MAX</sub> = 20pF (SD read data valid). | -      | 10     | ns                 | Figure 61 |

| t <sub>HR</sub>    | SCK(pos)-to-SIO0 delay @ C <sub>LOAD,MAX</sub> = 20pF (SD read data hold).  | 2      | -      | ns                 | Figure 61 |

| $t_{QR1}, t_{QF1}$ | SIO <sub>OUT</sub> rise/fall @ C <sub>LOAD,MAX</sub> = 20pF                 | -      | 12     | ns                 | Figure 61 |

| t <sub>PROP1</sub> | SIO0-to-SIO1 or SIO1-to-SIO0 delay @ C <sub>LOAD,MAX</sub> = 20pF           | -      | 20     | ns                 | Figure 61 |

| t <sub>NAPXA</sub> | NAP exit delay - phase A                                                    | -      | 50     | ns                 | Figure 50 |

| t <sub>NAPXB</sub> | NAP exit delay - phase B                                                    | -      | 40     | ns                 | Figure 50 |

| t <sub>PDNXA</sub> | PDN exit delay - phase A                                                    | -      | 4      | μs                 | Figure 50 |

| t <sub>PDNXB</sub> | PDN exit delay - phase B                                                    | -      | 9000   | t <sub>CYCLE</sub> | Figure 50 |

| t <sub>AS</sub>    | ATTN-to-STBY power state delay                                              | -      | 1      | t <sub>CYCLE</sub> | Figure 48 |

| t <sub>SA</sub>    | STBY-to-ATTN power state delay                                              | -      | 0      | t <sub>CYCLE</sub> | Figure 48 |

| t <sub>ASN</sub>   | ATTN/STBY-to-NAP power state delay                                          | -      | 8      | t <sub>CYCLE</sub> | Figure 49 |

| t <sub>ASP</sub>   | ATTN/STBY-to-PDN power state delay                                          | -      | 8      | t <sub>CYCLE</sub> | Figure 49 |

# **Timing Parameters**

**Table 13: Timing Parameter Summary**

| Parameter           | Description                                                                                                                                                                                                                                                                                                                             | Min<br>-45<br>-800 | Max               | Units              | Figure(s)              |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-------------------|--------------------|------------------------|

| t <sub>RC</sub>     | Row Cycle time of RDRAM banks -the interval between ROWA packets with ACT commands to the same bank.                                                                                                                                                                                                                                    | 28                 | -                 | t <sub>CYCLE</sub> | Figure 16<br>Figure 17 |

| t <sub>RAS</sub>    | RAS-asserted time of RDRAM bank - the interval between ROWA packet with ACT command and next ROWR packet with PRER <sup>a</sup> command to the same bank.                                                                                                                                                                               | 20                 | 64μs <sup>b</sup> | t <sub>CYCLE</sub> | Figure 16<br>Figure 17 |

| t <sub>RP</sub>     | Row Precharge time of RDRAM banks - the interval between ROWR packet with PRER <sup>a</sup> command and next ROWA packet with ACT command to the same bank.                                                                                                                                                                             | 8                  | -                 | t <sub>CYCLE</sub> | Figure 16<br>Figure 17 |

| t <sub>PP</sub>     | Precharge-to-precharge time of RDRAM device - the interval between successive ROWR packets with PRER <sup>a</sup> commands to any banks of the same device.                                                                                                                                                                             | 8                  | -                 | t <sub>CYCLE</sub> | Figure 13              |

| t <sub>RR</sub>     | RAS-to-RAS time of RDRAM device - the interval between successive ROWA packets with ACT commands to any banks of the same device.                                                                                                                                                                                                       | 8                  | -                 | t <sub>CYCLE</sub> | Figure 14              |

| t <sub>RCD</sub>    | RAS-to-CAS Delay - the interval from ROWA packet with ACT command to COLC packet with RD or WR command). Note - the RAS-to-CAS delay seen by the RDRAM core ( $t_{RCD-C}$ ) is equal to $t_{RCD-C} = 1 + t_{RCD}$ because of differences in the row and column paths through the RDRAM interface.                                       | 9                  | -                 | t <sub>CYCLE</sub> | Figure 16<br>Figure 17 |

| t <sub>CAC</sub>    | CAS Access delay - the interval from RD command to Q read data. The equation for $t_{\rm CAC}$ is given in the TPARM register in Figure 40.                                                                                                                                                                                             | 8                  | 12                | t <sub>CYCLE</sub> | Figure 5<br>Figure 40  |

| t <sub>CWD</sub>    | CAS Write Delay (interval from WR command to D write data.                                                                                                                                                                                                                                                                              | 6                  | 6                 | t <sub>CYCLE</sub> | Figure 5               |

| t <sub>CC</sub>     | CAS-to-CAS time of RDRAM bank - the interval between successive COLC commands).                                                                                                                                                                                                                                                         | 4                  | -                 | t <sub>CYCLE</sub> | Figure 16<br>Figure 17 |

| t <sub>PACKET</sub> | Length of ROWA, ROWR, COLC, COLM or COLX packet.                                                                                                                                                                                                                                                                                        | 4                  | 4                 | t <sub>CYCLE</sub> | Figure 3               |

| t <sub>RTR</sub>    | Interval from COLC packet with WR command to COLC packet which causes retire, and to COLM packet with bytemask.                                                                                                                                                                                                                         | 8                  | -                 | t <sub>CYCLE</sub> | Figure 18              |

| t <sub>OFFP</sub>   | The interval (offset) from COLC packet with RDA command, or from COLC packet with retire command (after WRA automatic precharge), or from COLC packet with PREC command, or from COLX packet with PREX command to the equivalent ROWR packet with PRER. The equation for t <sub>OFFP</sub> is given in the TPARM register in Figure 40. | 4                  | 4                 | t <sub>CYCLE</sub> | Figure 15<br>Figure 40 |

| t <sub>RDP</sub>    | Interval from last COLC packet with RD command to ROWR packet with PRER.                                                                                                                                                                                                                                                                | 4                  | -                 | t <sub>CYCLE</sub> | Figure 16              |

| t <sub>RTP</sub>    | Interval from last COLC packet with automatic retire command to ROWR packet with PRER.                                                                                                                                                                                                                                                  | 4                  | -                 | t <sub>CYCLE</sub> | Figure 17              |

a. Or equivalent PREC or PREX command. See Figure 15.

b. This is a constraint imposed by the core, and is therefore in units of  $\mu s$  rather than  $t_{\mbox{CYCLE}}$ .

# **Absolute Maximum Rating**

**Table 14: Absolute Maximum Ratings**

| Symbol                            | Parameter                                                  | Min   | Max                    | Unit |

|-----------------------------------|------------------------------------------------------------|-------|------------------------|------|

| $V_{I,ABS}$                       | Voltage applied to any RSL or CMOS pin with respect to Gnd | - 0.3 | V <sub>DD</sub> +0.3   | V    |

| $V_{\rm DD,ABS}, V_{\rm DDA,ABS}$ | Voltage on VDD and VDDA with respect to Gnd                | - 0.5 | $V_{\mathrm{DD}}$ +1.0 | V    |

| T <sub>STORE</sub>                | Storage temperature                                        | - 50  | 100                    | °C   |

| T <sub>MIN</sub>                  | Minimum operation temperature                              | 0     | Note*                  | °C   |

Note\*) Refer to  $T_{J,}\Theta_{JC}$

# **IDD** - Supply Current Profile

**Table 15: Supply Current Profile**

| I <sub>DD</sub> value   | RDRAM Power State and Steady-State Transaction Rates <sup>a</sup>                                                                                                          | Min | Max<br>-45<br>-800 | Unit |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------------|------|

| I <sub>DD,PDN</sub>     | Device in PDN, self-refresh enabled and INIT.LSR=0.                                                                                                                        | -   | 5000               | μΑ   |

| $I_{\mathrm{DD,NAP}}$   | Device in NAP.                                                                                                                                                             | -   | 4                  | mA   |

| $I_{\mathrm{DD,STBY}}$  | Device in STBY. This is the average for a device in STBY with (1) no packets on the Channel, and (2) with packets sent to other devices.                                   | -   | 75                 | mA   |

| I <sub>DD,REFRESH</sub> | Device in STBY and refreshing rows at the t <sub>REF,MAX</sub> period.                                                                                                     | -   | 75                 | mA   |

| I <sub>DD,ATTN</sub>    | Device in ATTN. This is the average for a device in ATTN with (1) no packets on the Channel, and (2) with packets sent to other devices.                                   | -   | 115                | mA   |

| I <sub>DD,ATTN-W</sub>  | Device in ATTN. ACT command every 8•t <sub>CYCLE</sub> , PRE command every 8•t <sub>CYCLE</sub> , WR command every 4•t <sub>CYCLE</sub> , and data is 11001100             | -   | 500                | mA   |

| I <sub>DD,ATTN-R</sub>  | Device in ATTN. ACT command every 8•t <sub>CYCLE</sub> , PRE command every 8•t <sub>CYCLE</sub> , RD command every 4•t <sub>CYCLE</sub> , and data is 1111111 <sup>b</sup> | -   | 480                | mA   |

a. CMOS interface consumes power in all power states.

**Table 16: Supply Current at Initialization**

| Symbol                  | Parameter                                | Allowed Range of t <sub>CYCLE</sub>  | $V_{DD}$            | Min | Max                     | Unit |

|-------------------------|------------------------------------------|--------------------------------------|---------------------|-----|-------------------------|------|

| I <sub>DD,PWRUP,D</sub> | $I_{\mathrm{DD}}$ from power -on to SETR | 3.33ns to 3.83ns<br>2.50ns to 3.32ns | V <sub>DD,MIN</sub> | -   | 150 <sup>a</sup><br>200 | mA   |

| I <sub>DD,SETR,D</sub>  | I <sub>DD</sub> from SETR to CLRR        | 3.33ns to 3.83ns<br>2.50ns to 3.32ns | V <sub>DD,MIN</sub> | -   | 250<br>332              | mA   |

a. The supply current will be 150mA when  $t_{\mbox{\scriptsize CYCLE}}$  is in the range 15ns to 1000ns.

b. This does not include the  $I_{OL}$  sink current. The RDRAM device dissipates  $I_{OL}$ \* $V_{OL}$  in each output driver when a logic one is driven.

# **Capacitance and Inductance**

**Table 17: RSL Pin Parasitics**

| Symbol            | Parameter and Conditions - RSL pins                                                                              | Min | Max  | Unit | Figure    |

|-------------------|------------------------------------------------------------------------------------------------------------------|-----|------|------|-----------|

| L <sub>I</sub>    | RSL effective input inductance                                                                                   |     | 4.0  | nH   | Figure 63 |

| T                 | Mutual inductance between any DQA or DQB RSL signals                                                             |     | 0.6  |      | Figure 63 |

| L <sub>12</sub>   | Mutual inductance between any ROW or COL RSL signals                                                             |     | 0.6  | nH   |           |

| $\Delta L_{ m I}$ | Difference in L <sub>I</sub> value between any RSL pins of a single device.                                      | -   | 2.0  | nH   | Figure 63 |

| C <sub>I</sub>    | RSL effective input capacitance <sup>a</sup>                                                                     | 2.0 | 2.6  | pF   | Figure 63 |

| C <sub>12</sub>   | Mutual capacitance between any RSL signals.                                                                      | -   | 0.2  | pF   | Figure 63 |

| $\Delta C_{ m I}$ | Difference in C <sub>I</sub> value between average of {CTM, CTMN, CFM, CFMN} and any RSL pins of a single device |     | 0.12 | pF   | Figure 63 |

| R <sub>I</sub>    | RSL effective input resistance                                                                                   | 4   | 18   | Ω    | Figure 63 |

a. This value is a combination of the device IO circuitry and package capacitances measured at VDD=2.5V and f=400MHz with pin biased at 1.4V.

**Table 18: CMOS Pin Parasitics**

| Symbol                  | Parameter and Conditions - CMOS pins                       |     | Max | Unit | Figure    |

|-------------------------|------------------------------------------------------------|-----|-----|------|-----------|

| L <sub>I,CMOS</sub>     | CMOS effective input inductance                            |     | 8.0 | nΗ   |           |

| $C_{I,CMOS}$            | CMOS effective input capacitance (SCK,CMD) <sup>a</sup>    | 1.7 | 2.1 | pF   | Figure 63 |

| C <sub>I,CMOS,SIO</sub> | CMOS effective input capacitance (SIO1, SIO0) <sup>a</sup> | -   | 7.0 | pF   |           |

a. This value is a combination of the device IO circuitry and package capacitances.

# Center-Bonded Fanout Package (54 Balls)

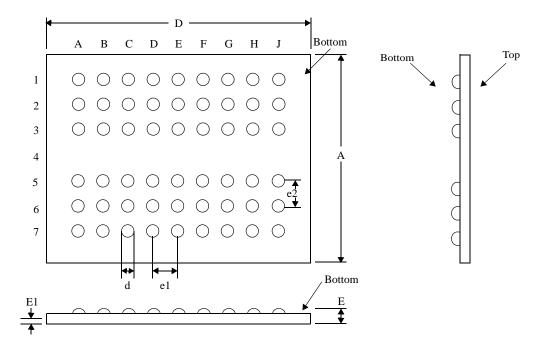

Figure 4 shows the form and dimensions of the recommended package for the center-bonded Fanout CSP device class.

Figure 4: Center-Bonded fanout CSP Package

Table 19 lists the numerical values corresponding to dimensions shown in Figure 4

**Table 19: Center-Bonded Fanout CSP Package Dimension**

| Symbol | Parameter               | Min  | Max  | Unit |

|--------|-------------------------|------|------|------|

| e1     | Ball pitch (x-axis)     | 1.27 | 1.27 | mm   |

| e2     | Ball pitch (y-axis)     | 1.27 | 1.27 | mm   |

| А      | Package body length     | 11.9 | 12.1 | mm   |

| D      | Package body width      | 11.7 | 11.9 | mm   |

| Е      | Package total thickness | -    | 1.25 | mm   |

| E1     | Ball height             | 0.45 | 0.55 | mm   |

| d      | Ball diameter           | 0.55 | 0.65 | mm   |