# SP502

# **Multi–Mode Serial Transceiver**

- Single-Chip Serial Transceiver Supports Industry-Standard

- Software-Selectable Protocols:

- RS-232 (V.28)

- RS-422A (V.11, X.27)

- RS-449

- RS-485

- V.35

- EIA-530

- Programmable Selection of Interface

- +5V-Only Operation

- Six (6) Drivers and Seven (7) Receivers

- Surface Mount Packaging

# **DESCRIPTION...**

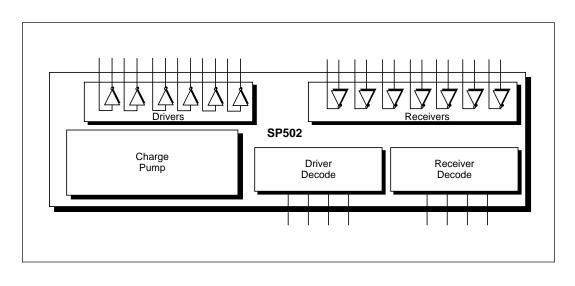

The **SP502** is a highly integrated serial transceiver that allows software control of its interface modes. It offers hardware interface modes for RS-232 (V.28), RS-422A (V.11), RS-449, RS-485, V.35, and EIA-530. The **SP502** is fabricated using low–power BiCMOS process technology, and incorporates a **Sipex** patented (5,306,954) charge pump allowing +5V only operation.

Rev. 7/21/03

SP502 Multi-Mode Serial Transceiver

© Copyright 2003 Sipex Corporation

# **SPECIFICATIONS**

|                                         | MIN.     | TYP. | MAX.      | UNITS          | CONDITIONS                                           |

|-----------------------------------------|----------|------|-----------|----------------|------------------------------------------------------|

| LOGIC INPUTS                            |          |      |           |                |                                                      |

| VIL                                     | 2.0      |      | 0.8       | Volts          |                                                      |

|                                         | 2.0      |      |           | Volts          |                                                      |

|                                         |          |      | 0.4       | Volts          | L _ 2.2mA                                            |

| V <sub>OL</sub><br>V <sub>OH</sub>      | 2.4      |      | 0.4       | Volts          | I <sub>OUT</sub> = 3.2mA<br>I <sub>OUT</sub> = 1.0mA |

| RS-485 DRIVER                           |          |      |           |                | .001                                                 |

| TTL Input Levels                        |          |      |           |                |                                                      |

| V <sub>II</sub>                         |          |      | 0.8       | Volts          |                                                      |

|                                         | 2.0      |      |           | Volts          |                                                      |

| Outputs<br>HIGH Level Output            |          |      | +6.0      | Volts          |                                                      |

| LOW level Output                        |          |      | -0.3      | Volts          |                                                      |

| Differential Output                     | ±1.5     |      | ±5.0      | Volts          | $R_{L}=54\Omega, C_{L}=50pF$                         |

| Balance                                 |          |      | ±0.2      | Volts          |                                                      |

| Open Circuit Voltage                    | 20.0     |      | ±6.0      | Volts          | B 540                                                |

| Output Current<br>Short Circuit Current | 28.0     |      | ±250      | mA<br>mA       | R <sub>L</sub> =54Ω<br>Terminated in -7V to +12V     |

| Transition Time                         |          |      | 120       | ns             | Rise/fall time, 10%-90%                              |

| Maximum Transmission Rate               | 5        |      |           | Mbps           |                                                      |

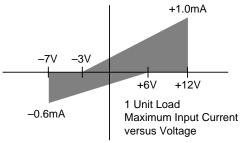

| RS-485 RECEIVER                         |          |      |           |                |                                                      |

| TTL Output Levels                       |          |      |           |                |                                                      |

| V <sub>OL</sub>                         | 0<br>2.4 |      | 0.4       | Volts<br>Volts |                                                      |

| V <sub>OH</sub><br>Input                | 2.4      |      |           | VOIIS          |                                                      |

| HIGH Threshold                          | +0.2     |      | +12.0     | Volts          | (a)-(b)                                              |

| LOW Threshold                           | -7.0     |      | -0.2      | Volts          | (a)-(b)                                              |

| Common Mode Range                       | -7.0     |      | +12.0     | Volts          | Defente menh                                         |

| HIGH Input Current<br>LOW Input Current |          |      |           |                | Refer to graph<br>Refer to graph                     |

| Receiver Sensitivity                    |          |      | ±0.2      | Volts          | Over -7V to +12V common                              |

| ,                                       |          |      |           |                | mode range                                           |

| Input Impedance                         |          |      | 1         | Unit Load      | Refer to graph                                       |

| V.35 DRIVER                             |          |      |           |                |                                                      |

| TTL Input Levels                        | 0        |      | 0.8       | Volts          |                                                      |

| V <sub>IL</sub><br>V <sub>IH</sub>      | 2.0      |      | 0.0       | Volts          |                                                      |

| Outputs                                 | 2.0      |      |           |                |                                                      |

| Differential Output                     | ±0.44    |      | ±0.66     | Volts          | With termination network;                            |

| Output Impedance                        | 50       |      | 150       |                | R <sub>L</sub> =100Ω<br>With termination network     |

| Transition Time                         | 50       |      | 150<br>40 | Ω<br>ns        | with termination network                             |

| Maximum Transmission Rate               | 5        |      | 10        | Mbps           |                                                      |

| V.35 RECEIVER                           |          |      |           |                |                                                      |

| TTL Output Levels                       |          |      |           |                |                                                      |

| Vol                                     | 0        |      | 0.4       | Volts          |                                                      |

| V <sub>OH</sub><br>Receiver Sensitivity | 2.4      |      | ±0.2      | Volts<br>Volts | Over -7V to +12V common                              |

| Receiver Censilivity                    |          |      | ±0.2      | VUIIS          | mode range                                           |

| Input Impedance                         | 90       |      | 110       | Ω              | With termination network                             |

|                                         |          |      |           |                |                                                      |

|                                         |          |      |           |                |                                                      |

|                                         |          |      |           |                |                                                      |

|                                         |          |      |           |                |                                                      |

|                                         |          |      |           |                |                                                      |

|                                         |          |      |           |                |                                                      |

# SPECIFICATIONS (Continued)

|                                               | MIN.        | TYP. | MAX.         | UNITS          | CONDITIONS                                                                               |

|-----------------------------------------------|-------------|------|--------------|----------------|------------------------------------------------------------------------------------------|

| RS-422 DRIVER                                 |             |      |              |                |                                                                                          |

| TTL Input Levels                              |             |      |              |                |                                                                                          |

| V <sub>IL</sub>                               | 0           |      | 0.8          | Volts          |                                                                                          |

|                                               | 2.0         |      |              | Volts          |                                                                                          |

| Outputs                                       |             |      |              |                |                                                                                          |

| Differential Output                           | ±2.0        |      | ±5.0         | Volts          | R <sub>1</sub> =100Ω                                                                     |

| Open Circuit Voltage,Vo                       |             |      | ±6.0         | Volts          |                                                                                          |

| Balance                                       |             |      | ±0.4         | Volts          | $ V_{T}  -  \overline{V_{T}} $                                                           |

| Offset                                        |             |      | +3.0         | Volts          |                                                                                          |

| Short Circuit Current                         |             |      | ±150         | mA             |                                                                                          |

| Power Off Current                             |             |      | ±100         | μΑ             |                                                                                          |

| Transition Time                               |             |      | 60           | ns             | Rise/fall time, 10%-90%                                                                  |

| Maximum Transmission Rate                     | 5           |      |              | Mbps           |                                                                                          |

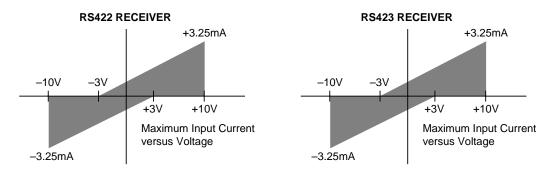

| RS-422 RECEIVER                               |             |      |              |                |                                                                                          |

| TTL Output Levels                             |             |      |              |                |                                                                                          |

| Vol                                           | 0           |      | 0.4          | Volts          |                                                                                          |

| V <sub>OH</sub>                               | 2.4         |      |              | Volts          |                                                                                          |

| Input                                         |             |      |              |                |                                                                                          |

| HIGH Threshold                                | +0.2        |      | +6.0         | Volts          | (a)-(b)                                                                                  |

| LOW Threshold                                 | -6.0        |      | -0.2         | Volts          | (a)-(b)                                                                                  |

| Common Mode Range                             | -10.0       |      | +10.0        | Volts          |                                                                                          |

| HIGH Input Current                            |             |      |              |                | Refer to graph                                                                           |

| LOW Input Current                             |             |      |              | N/ 1/          | Refer to graph                                                                           |

| Receiver Sensitivity                          |             |      | ±0.2         | Volts          |                                                                                          |

| Input Impedance                               | 4           |      |              | kΩ             |                                                                                          |

| RS-232 DRIVER                                 |             |      |              |                |                                                                                          |

| TTL Input Level                               |             |      |              |                |                                                                                          |

| V <sub>IL</sub>                               | 0           |      | 0.8          | Volts          |                                                                                          |

|                                               | 2.0         |      |              | Volts          |                                                                                          |

| Outputs                                       |             |      |              |                |                                                                                          |

| HIGH Level Output                             | +5.0        |      | +15          | Volts          | R <sub>L</sub> =3kΩ, V <sub>IN</sub> =0.8V<br>R <sub>L</sub> =3kΩ, V <sub>IN</sub> =2.0V |

| LOW Level Output                              | -15.0       |      | -5.0         | Volts          | $R_L=3k\Omega, V_{IN}=2.0V$                                                              |

| Open Circuit Voltage                          | -15         |      | +15          | Volts          |                                                                                          |

| Short Circuit Current                         | 000         |      | ±100         | mA             |                                                                                          |

| Power Off Impedance                           | 300         |      | 20           | $\Omega$       |                                                                                          |

| Slew Rate                                     |             |      | 30           | V/µs           | $R_L=3k\Omega$ , $C_L=15pF$                                                              |

| Transition Time                               | 120         |      | 1.56         | μS<br>Kbps     |                                                                                          |

| Maximum Transmission Rate                     | 120         |      |              | Kbps           |                                                                                          |

| RS-232 RECEIVER                               |             |      |              |                |                                                                                          |

| TTL Output Levels                             | 0           |      |              | N / - 1( -     |                                                                                          |

| V <sub>OL</sub>                               | 0           |      | 0.4          | Volts          |                                                                                          |

| V <sub>OH</sub>                               | 2.4         |      |              | Volts          |                                                                                          |

|                                               |             | 17   | 24           | Valte          |                                                                                          |

| HIGH Threshold                                | 0.0         | 1.7  | 2.4          | Volts          |                                                                                          |

| LOW Threshold                                 | 0.8         | 1.2  | 120          | Volts          |                                                                                          |

| Receiver Open Circuit Bias<br>Input Impedance | 0<br>3      | 5    | +2.0<br>7    | Volts<br>kΩ    |                                                                                          |

|                                               | J           | 5    | 1            | K52            |                                                                                          |

| RS-423 DRIVER                                 |             |      |              |                |                                                                                          |

| TTL Input Levels                              | 0           |      |              | Valte          |                                                                                          |

| VIL                                           | 0           |      | 0.8          | Volts          |                                                                                          |

|                                               | 2.0         |      |              | Volts          |                                                                                          |

|                                               | 126         |      | +6.0         | Valta          | P -4500                                                                                  |

| HIGH Level Output<br>LOW Level Output         | +3.6<br>6.0 |      | +6.0<br>-3.6 | Volts<br>Volts | R <sub>L</sub> =450Ω<br>R =450Ω                                                          |

|                                               | -0.0        |      | -3.0         | VUILS          | $R_{L}$ =450 $\Omega$                                                                    |

|                                               |             |      |              |                |                                                                                          |

|                                               |             |      |              |                |                                                                                          |

|                                               |             |      |              |                |                                                                                          |

# SPECIFICATIONS (Continued)

|                              | MIN. | TYP.     | MAX.  | UNITS | CONDITIONS                          |

|------------------------------|------|----------|-------|-------|-------------------------------------|

| RS-423 DRIVER                |      |          |       |       |                                     |

| Open Circuit Voltage         | ±4.0 |          | ±9.0  | Volts |                                     |

| Short Circuit Current        |      |          | ±150  | mA    |                                     |

| Power Off Current            |      |          | ±100  | μΑ    |                                     |

| Transition Time              |      |          | 40    | μS    | Rise/fall time, 10-90%              |

| Maximum Transmission Rate    | 120  |          |       | kbps  |                                     |

| RS-423 RECEIVER              |      |          |       |       |                                     |

| TTL Output Levels            |      |          |       |       |                                     |

| V <sub>OL</sub>              | 0    |          | 0.4   | Volts |                                     |

| VOH                          | 2.4  |          |       | Volts |                                     |

| Input                        |      |          |       |       |                                     |

| HIGH Threshold               | +0.2 |          | +12.0 | Volts |                                     |

| LOW Threshold                | -7.0 |          | -0.2  | Volts |                                     |

| Common Mode Range            | -7.0 |          | +12.0 | Volts |                                     |

| HIGH Input Current           |      |          |       |       | Refer to graph                      |

| LOW Input Current            |      |          | 0.0   | Malta | Refer to graph                      |

| Receiver Sensitivity         | 4    |          | ±0.2  | Volts |                                     |

| Input Impedance              | 4    |          |       | kΩ    |                                     |

| POWER REQUIREMENTS           |      |          |       |       |                                     |

| V <sub>cc</sub>              | 4.75 |          | 5.25  | Volts |                                     |

|                              |      | 20       | 30    | mA    | $V_{CC}$ =5V; no interface selected |

| ENVIRONMENTAL AND MECHANICAL |      |          |       |       |                                     |

| Operating Temperature Range  | 0    |          | +70   | °C    |                                     |

| Storage Temperature Range    | -65  |          | +150  | °C    |                                     |

| Package                      | 8    | 0–pin QF | Р     |       |                                     |

|                              |      |          |       |       |                                     |

Rev. 7/21/03

# AC CHARACTERISTICS

| PARAMETER                                                                                                                                      | MIN. | TYP.       | MAX.              | UNITS          | CONDITIONS                                                                                                                                                 |

|------------------------------------------------------------------------------------------------------------------------------------------------|------|------------|-------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SINGLE-ENDED MODE                                                                                                                              |      |            |                   |                |                                                                                                                                                            |

| RS-232<br>Driver Propagation Delay<br>t <sub>PHL</sub>                                                                                         |      | 1.7        |                   | μs             | Input = 0.8V to 2.0V; 60kHz<br>Unloaded                                                                                                                    |

| t <sub>PLH</sub><br>t <sub>PHL</sub>                                                                                                           |      | 1.1<br>2.0 | 8.0               | μs<br>μs       | Unloaded<br>Loaded with $3k\Omega$ and<br>$2500\pi\Sigma$                                                                                                  |

| t <sub>PLH</sub>                                                                                                                               |      | 2.0        | 8.0               | μS             | 2,500pF<br>Loaded with 3kΩ and<br>2,500pF                                                                                                                  |

| Receiver Propagation Delay                                                                                                                     |      |            |                   |                | Input = 0V to 5.0V; 60kHz;<br>Note 1                                                                                                                       |

| t <sub>PHL</sub><br>t <sub>PLH</sub>                                                                                                           |      |            | 1.0<br>1.0        | μs<br>μs       |                                                                                                                                                            |

| RS-423<br>Driver Propagation Delay<br>t <sub>PHL</sub><br>t <sub>PLH</sub><br>Receiver Propagation Delay                                       |      | 2.0<br>2.0 | 8.0<br>8.0        | μs<br>μs       | Input = $0.8V$ to $2.0V$ ; $60kHz$<br>Loaded with $450\Omega$<br>Loaded with $450\Omega$<br>Input = $-0.2V$ to $2.0V$ ; ;<br>60kHz; Note 2                 |

| t <sub>PHL</sub><br>t <sub>PLH</sub>                                                                                                           |      |            | 1.0<br>1.0        | μS<br>μS       |                                                                                                                                                            |

| DIFFERENTIAL MODE                                                                                                                              |      |            |                   |                |                                                                                                                                                            |

| RS-485<br>Driver Propagation Delay<br>t <sub>PHL</sub><br>t <sub>PI H</sub>                                                                    |      |            | 200<br>200        | ns<br>ns       | Input = 0V to 3.0V; 100kHz<br>Note 3<br>Loaded with $54\Omega$<br>Loaded with $54\Omega$                                                                   |

| Receiver Propagation Delay t <sub>PHL</sub> t <sub>PHL</sub> t <sub>PLH</sub>                                                                  |      |            | 200<br>200        | ns             | Input = a to GND;<br>B = -200mV to +200mV;<br>100kHz, Note 4                                                                                               |

| RS-422<br>Driver Propagation Delay<br>t <sub>PHL</sub><br>t <sub>PLH</sub><br>Receiver Propagation Delay<br>t <sub>PHL</sub>                   |      |            | 200<br>200        | ns<br>ns<br>ns | Input = 0V to 3.0V; 100kHz<br>Note 3<br>Loaded with $100\Omega$<br>Loaded with $100\Omega$<br>Input = a to GND;<br>B = -200mV to +200mV;<br>100kHz, Note 4 |

| t <sub>PLH</sub><br>V.35<br>Driver Propagation Delay<br>t <sub>PHL</sub><br>t <sub>PLH</sub><br>Receiver Propagation Delay<br>t <sub>PHL</sub> |      |            | 200<br>200<br>200 | ns<br>ns       | Input = 0V to 3.0V; 100kHz<br>Note 3<br>Loaded with $100\Omega$<br>Loaded with $100\Omega$<br>Input = a to GND;<br>B = -200mV to +200mV;<br>100kHz, Note 4 |

| трні<br>t <sub>РLH</sub>                                                                                                                       |      |            | 200               | ns             |                                                                                                                                                            |

# **OTHER AC CHARACTERISTICS** (continued)

| PARAMETER                                                                      | MIN.        | TYP.    | MAX.    | UNITS | CONDITIONS                     |

|--------------------------------------------------------------------------------|-------------|---------|---------|-------|--------------------------------|

| DELAY TIME FROM ENA                                                            | BLE MODE TO | D TRI-S | ΓΑΤΕ ΜΟ | DE    |                                |

| RS-232 (SINGLE–ENDED                                                           | MODE)       |         |         |       |                                |

| t <sub>P71</sub> ; Enable to Output L                                          | OW          | 190     |         | ns    | 3kΩ pull–up to output          |

| t <sub>PZH</sub> ; Enable to Output H<br>t <sub>PLZ</sub> ; Disable from Outpu | IIGH        | 130     |         | ns    | 3kΩ pull-down to output        |

| t <sub>PL7</sub> ; Disable from Outpu                                          | ut LOW      | 270     |         | ns    | 5V to input                    |

| t <sub>PHZ</sub> , Disable from Outp                                           | ut HIGH     | 400     |         | ns    | GND to input                   |

| RS-422 (DIFFERENTIAL I                                                         | MODE)       |         |         |       |                                |

| t <sub>P71</sub> ; Enable to Output LO                                         | W           | 100     |         | ns    | $3k\Omega$ pull–up to output   |

| t <sub>nzu</sub> ; Enable to Output HI                                         | GH 🛛        | 100     |         | ns    | $3k\Omega$ pull-down to output |

| t <sub>PL7</sub> ; Disable from Output                                         | LOW         | 130     |         | ns    | 5V to input                    |

| $t_{PLZ}^{PLZ}$ ; Disable from Output $t_{PHZ}$ ; Disable from Output          | HIGH        | 140     |         | ns    | GND to input                   |

|                                                                                |             |         |         |       |                                |

Notes:

- 1.

- . Measured from 2.5V of  $R_{_{\rm IN}}$  to 2.5V of  $R_{_{\rm OUT}}$ . Measured from one–half of  $R_{_{\rm IN}}$  to 2.5V of  $R_{_{\rm OUT}}$ . Measured from 1.5V of  $T_{_{\rm IN}}$  to one–half of  $T_{_{\rm OUT}}$ . Measured from 2.5V of  $R_{_{\rm O}}$  to 0V of A and B. 2. 3.

- 4.

## **POWER MATRIX**

c; ∘r

| Mode                   | Open Input | Input to 5V | Input to GND | AC Signal<br>to Input | 5V to Input<br>with Load | GND to Input<br>with Load | AC Signal with Load | Conditions                                                                                                                                                 |

|------------------------|------------|-------------|--------------|-----------------------|--------------------------|---------------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>V.35</b><br>1110    | 20.71mA    | 21.5mA      | 20.74mA      | 28.32mA               | 58.19mA                  | 55.64mA                   | 73.08mA             | With external driver output<br>termination network;<br>Input = 0.8V to 2V, 60kHz;<br>Load = $3k\Omega$ , 2500pF for<br>RS-232; load = $100\Omega$ for V.35 |

| <b>RS-232</b><br>0010  | 22.53mA    | 22.41mA     | 23.15mA      | 31.54mA               | 43.74mA                  | 40.96mA                   | 62.47mA             | Input = 0.8V to 2V, 60kHz ;<br>Load = 3kΩ, 2500pF                                                                                                          |

| <b>RS-422</b><br>0100  | 17.93mA    | 17.83mA     | 14.13mA      | 32.92mA               | 143.47mA                 | 140.65mA                  | 146.55mA            | Input = 0.8V to 2V, 2.5MHz;<br>Load = 100Ω                                                                                                                 |

| <b>RS-485</b><br>0101  | 17.82mA    | 17.74mA     | 14.07mA      | 32.85mA               | 182.93mA                 | 180.71mA                  | 183.65mA            | Input 0.8V to 2V, 2.5MHz;<br>Load = $54\Omega$                                                                                                             |

| <b>RS-449</b><br>1100  | 19.93mA    | 19.87mA     | 17.84mA      | 23.57mA               | 134.90mA                 | 131.35mA                  | 131.94mA            | Input = 0.8V to 2V, 60kHz;<br>Load = 450Ω for RS-423;<br>Load = 100Ω for RS-422                                                                            |

| <b>EIA-530</b><br>1101 | 19.85mA    | 19.83mA     | 17.82mA      | 23.54mA               | 134.90mA                 | 131.25mA                  | 131.78mA            | Input = $0.8V$ to $2V$ , $60kHz$ ;<br>Load = $450\Omega$ for RS-423;<br>Load = $100\Omega$ for RS-422                                                      |

\*All Driver Input Common V<sub>cc</sub>=5V

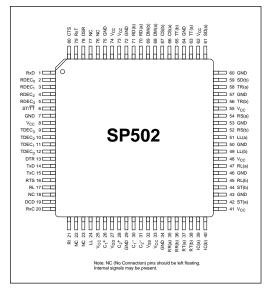

#### PINOUT...

### PIN ASSIGNMENTS... CLOCK AND DATA GROUP

Pin 1 — RxD — Receive Data; TTL output, sourced from RD(a) and RD(b) inputs. Pin 14 — TxD — TTL input ; transmit data source for SD(a) and SD(b) outputs. Pin 15 — TxC — Transmit Clock; common TTL input for both ST and TT driver outputs. Pin 20 — RxC — Receive Clock; TTL output sourced from RT(a) and RT(b) inputs. Pin 37 — RT(a) — Receive Timing: analog

Pin 37 — RT(a) — Receive Timing; analog input, inverted; source for RxC.

Pin 38 — RT(b) — Receive Timing; analog input, non-inverted; source for RxC.

Pin 42—ST(a)—Send Timing; analog output, inverted; sourced from ST.

Pin 44 — ST(b) — Send Timing; analog output, non-inverted; sourced from ST.

Pin 59 — SD(b) — Analog Out — Send data, non-inverted; sourced from TxD.

Pin 61 — SD(a) — Analog Out — Send data, inverted; sourced from TxD.

Pin 63 — TT(a) — Analog In or Out —

Terminal Timing, inverted; sourced to TxC or RxT.

Pin 65 — TT(b) — Analog In or Out — Terminal Timing, non–inverted; sourced to TxC or RxT.

Pin 70 — RD(a) — Receive Data, analog input; inverted; source for RxD. Pin 71 — RD(b) — Receive Data; analog input;

non-inverted; source for RxD.

# **CONTROL LINE GROUP**

Pin 13 — DTR — Data Terminal Ready; TTL input; source for TR(a) and TR(b) outputs.

Pin 16 — RTS — Ready To Send; TTL input; source for RS(a) and RS(b) outputs.

Pin 17 — RL — Remote Loopback; TTL input; source for RL(a) and RL(b) outputs.

Pin 19 — DCD— Data Carrier Detect; TTL output; sourced from RR(a) and RR(b) inputs. Pin 21 — RI — Ring In; TTL output; sourced from IC(a) and IC(b) inputs.

Pin 24 — LL — Local Loopback; TTL input; source for LL(a) and LL(b) outputs.

Pin 35 — RR(a)— Receiver Ready; analog input, inverted; source for DCD.

Pin 36 — RR(b)— Receiver Ready; analog input, non-inverted; source for DCD.

Pin 39 — IC(a)— Incoming Call; analog input, inverted; source for RI.

Pin 40 — IC(b)— Incoming Call; analog input, non-inverted; source for RI.

Pin 45 — RL(b) — Remote Loopback; analog output, non-inverted; sourced from RL.

Pin 47 — RL(a) — Remote Loopback; analog output inverted; sourced from RL.

Pin 49— LL(b) — Local Loopback; analog output, non-inverted; sourced from LL.

Pin 51 — LL(a) — Local Loopback; analog output, inverted; sourced from LL.

Pin 52 — RS(b) — Ready To Send; analog output, non-inverted; sourced from RTS.

Pin 54 — RS(a) — Ready To Send; analog output, inverted; sourced from RTS.

Pin 56 — TR(b) — Terminal Ready; analog

output, non-inverted; sourced from DTR. Pin 58 - TR(a) - Terminal Ready; analog

output, inverted; sourced from DTR.

Pin 66—CS(a)—Clear To Send; analog input, inverted; source for CTS.

Pin 67 — CS(b)— Clear To Send; analog input, non-inverted; source for CTS.

Pin 68 — DM(a)— Data Mode; analog input, inverted; source for DSR.

Pin 69 — DM(b)— Data Mode; analog input, non-inverted; source for DSR.

Pin 78 — DSR— Data Set Ready; TTL output; sourced from DM(a), DM(b) inputs. Pin 80 — CTS— Clear To Send; TTL output; sourced from CS(a) and CS(b) inputs.

#### CONTROL REGISTERS

Pins 2–5 — RDEC0 – RDEC3 — Receiver decode register; configures receiver modes; TTL inputs.

Pin 6 —  $ST/\overline{TT}$  — Enables ST or TT drivers, TTL input.

Pins 12–9 — TDEC0 – TDEC3 — Transmitter decode register; configures transmitter modes; TTL inputs.

#### POWER SUPPLIES

Pins 8, 25, 33, 41, 48, 55, 62, 73, 74 — V<sub>CC</sub> — +5V input.

Pins 7, 29, 34, 43, 46, 50, 53, 57, 60, 64, 72, 75 — GND — Ground.

Pin 27 —  $V_{DD}$  +10V Charge Pump Capacitor — Connects from  $V_{DD}$  to  $V_{CC}$ . Suggested capacitor size is 22 $\mu$ F, 16V.

Pin 32 —  $V_{SS}$  –10V Charge Pump Capacitor — Connects from ground to  $V_{SS}$ . Suggested capacitor size is 22µF, 16V.

Pins 26 and 30 —  $C_1^+$  and  $C_1^-$  — Charge Pump Capacitor — Connects from  $C_1^+$  to  $C_1^-$ . Suggested capacitor size is 22µF, 16V.

Pins 28 and 31 —  $C_2^+$  and  $C_2^-$  — Charge Pump Capacitor — Connects from  $C_2^+$  to  $C_2^-$ . Suggested capacitor size is 22µF, 16V.

NOTE: NC pins should be left floating; internal signals may be present.

#### FEATURES...

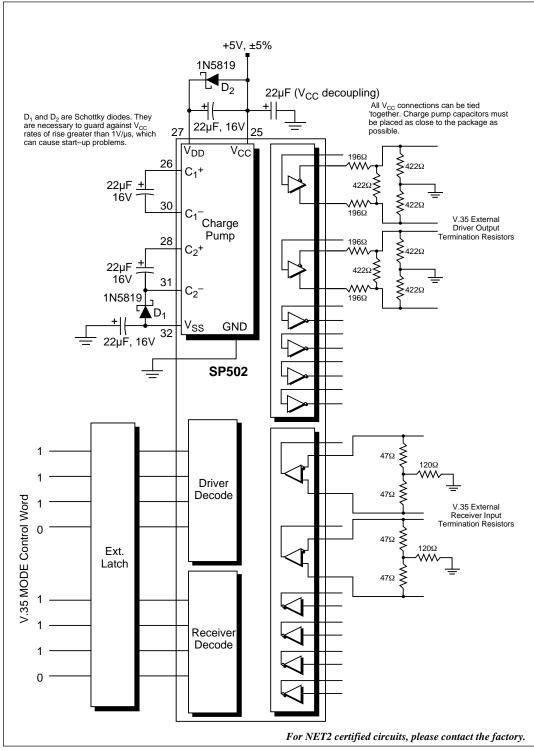

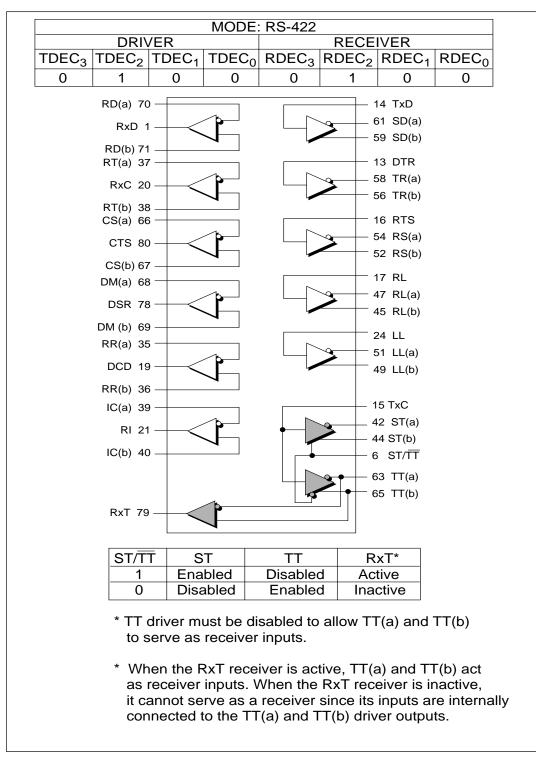

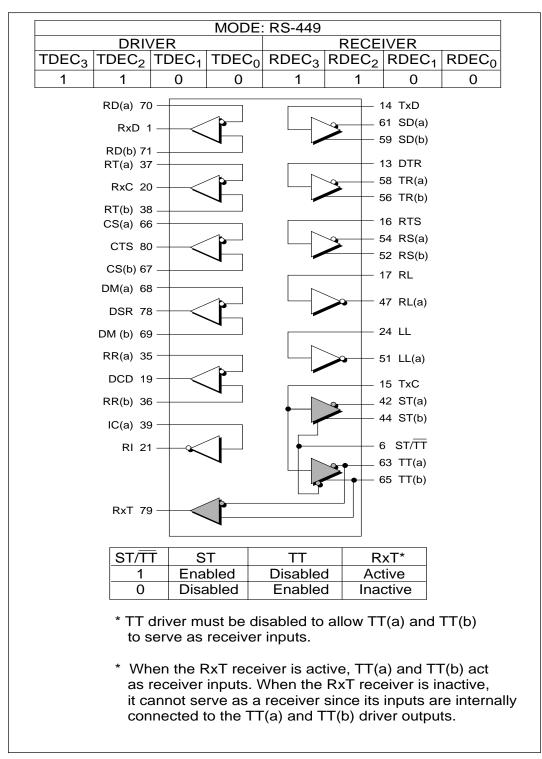

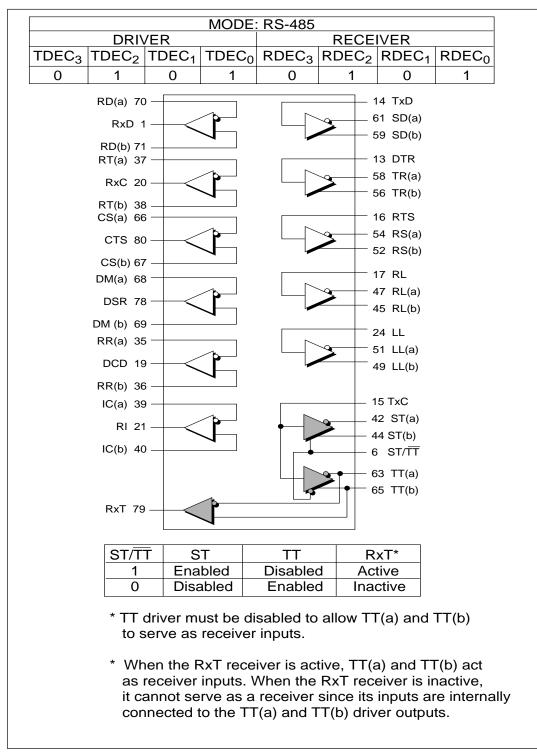

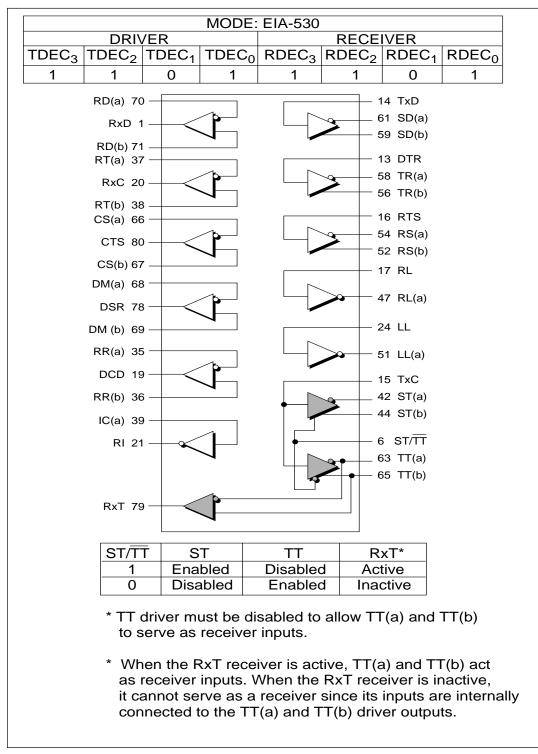

The **SP502** is a highly integrated serial transceiver that allows software control of its interface modes. The **SP502** offers hardware interface modes for RS-232 (V.28), RS-422A (V.11), RS-449, RS-485, V.35, and EIA-530. The interface mode selection is done via an 8–bit switch; four (4) bits control the drivers and four (4) bits control the receivers. The **SP502** is fabricated using low–power BiCMOS process technology, and incorporates a **Sipex** patented (5,306,954) charge pump allowing +5V only operation. Each device is packaged in an 80-pin Quad FlatPack package.

The **SP502** is ideally suited for wide area network connectivity based on the interface modes offered and the driver and receiver configurations. The **SP502** has five (5) independent drivers and six (6) independent receivers and one half-duplex transceiver channel, which allows a maximum of six (6) drivers and seven (7) receivers. The driver and receiver configuration for the **SP502** is ideal for DTE applications. The **SP502** is made up of four separate circuit blocks – the charge pump, drivers, receivers, and decoder. Each of these circuit blocks is described in detail below.

### THEORY OF OPERATION Charge–Pump

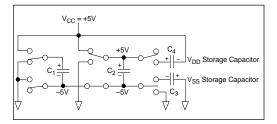

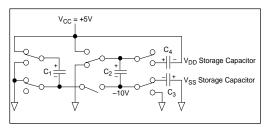

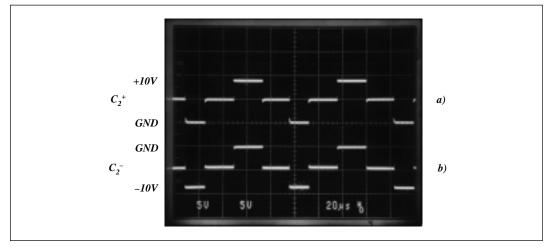

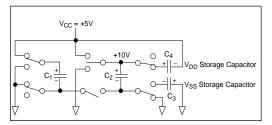

The charge pump is a **Sipex** patented design (5,306,954) and uses a unique approach compared to older less efficient designs. The charge pump still requires four external capacitors, but uses a four-phase voltage shifting technique to attain symmetrical 10V power supplies. *Figure 3a* shows the waveform found on the positive side of capcitor  $C_2$ , and *Figure 3b* shows the negative side of capcitor  $C_2$ . There is a free-running oscillator that controls the four phases of the voltage shifting. A description of each phase follows.

#### Phase 1

—  $V_{SS}$  charge storage —During this phase of the clock cycle, the positive side of capacitors  $C_1$  and  $C_2$  are initially charged to +5V.  $C_1^+$  is then switched to ground and the charge on  $C_1^$ is transferred to  $C_2^-$ . Since  $C_2^+$  is connected to +5V, the voltage potential across capacitor  $C_2$  is now 10V.

#### Phase 2

—  $V_{SS}$  transfer — Phase two of the clock connects the negative terminal of  $C_2$  to the  $V_{SS}$  storage capacitor and the positive terminal of  $C_2$  to ground, and transfers the generated –10V to  $C_3$ . Simultaneously, the positive side of capaci-

Figure 1. Charge Pump Phase 1.

tor C  $_1$  is switched to +5V and the negative side is connected to ground.

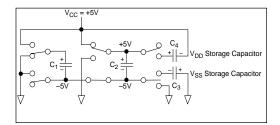

#### Phase 3

$-V_{DD}$  charge storage — The third phase of the clock is identical to the first phase — the charge transferred in C<sub>1</sub> produces -5V in the negative terminal of C<sub>1</sub>, which is applied to the negative side of capacitor C<sub>2</sub>. Since C<sub>2</sub><sup>+</sup> is at +5V, the voltage potential across C<sub>2</sub> is 10V.

#### Phase 4

—  $V_{DD}$  transfer — The fourth phase of the clock connects the negative terminal of  $C_2$  to ground and transfers the generated 10V across  $C_2$  to  $C_4$ , the  $V_{DD}$  storage capacitor. Again, simultaneously with this, the positive side of capacitor  $C_1$  is switched to +5V and the negative side is connected to ground, and the cycle begins again.

Since both V+ and V<sup>-</sup> are separately generated from  $V_{CC}$  in a no-load condition, V+ and V<sup>-</sup> will be symmetrical. Older charge pump ap-

Figure 2. Charge Pump Phase 2.

proaches that generate  $V^-$  from V+ will show a decrease in the magnitude of V<sup>-</sup> compared to V+ due to the inherent inefficiencies in the design.

The clock rate for the charge pump typically operates at 15kHz. The external capacitors must be  $22\mu$ F with a 16V breakdown rating. Two external Schottky diodes connected as in *Figure* 6 are required for high rate of rise power supplies.

#### **External Power Supplies**

For applications that do not require +5V only, external supplies can be applied at the V+ and V<sup>-</sup> pins. The value of the external supply voltages must be no greater than  $\pm 10V$ . The current drain for the  $\pm 10V$  supplies is used for RS-232, and RS-423 drivers. For the RS-232 driver the current requirement will be 3.5mA per driver, and for the RS-423 driver the worst case current drain will be 11mA per driver. The external

Figure 3. Charge Pump Waveforms

Rev. 7/21/03

Figure 4. Charge Pump Phase 3.

power supplies should provide a power supply sequence of: +10V, then +5V, followed by -10V.

#### Drivers

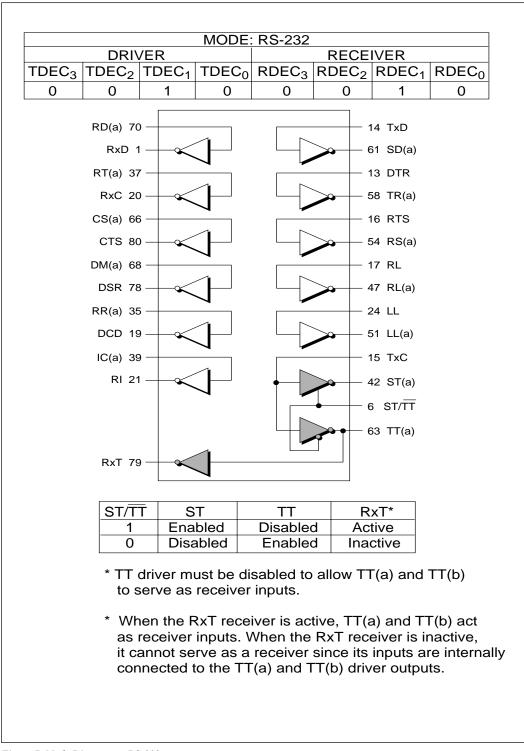

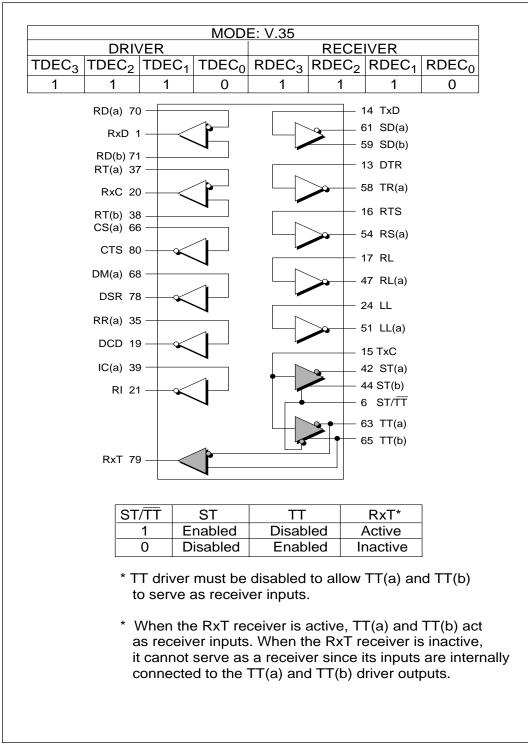

The **SP502** has six (6) drivers which can be programmed in six different modes of operation. One of the drivers for the **SP502** is internally connected to an internal receiver input to make up a half-duplex configuration. As shown in the Mode Diagrams, the driver input of the half-duplex channel is shared with an adjacent driver such that when one is active the other is disabled.

Control for the mode selection is done via a four-bit control word. The **SP502** does not have a latch; the control word must be externally latched either high or low to write the appropriate code into the **SP502**. The drivers are pre-

Figure 5. Charge Pump Phase 4.

arranged such that for each mode of operation the relative position and functionality of the drivers are set up to accommodate the selected interface mode. As the mode of the drivers is changed, the electrical characteristics will change to support the requirements of clock, data, and control line signal levels. *Table 1* shows a summary of the electrical characteristics of the drivers in the different interface modes. Unused driver inputs can be left floating; however, to ensure a desired state with no input signal, pull– up resistors to +5V or pull–down resistors to ground are suggested. Since the driver inputs are both TTL or CMOS compatible, any value resistor less than 100k $\Omega$  will suffice.

There are three basic types of driver circuits — RS-232, RS-423, and RS-485. The RS-232 drivers output a minimum of  $\pm 5V$  level single–ended signals (with  $3k\Omega$  and 2500pF loading), and

| Pin Label                            | Mode:     | RS-232    | V.35      | RS-422  | RS-485  | RS-449    | EIA-530   |

|--------------------------------------|-----------|-----------|-----------|---------|---------|-----------|-----------|

| TDEC <sub>3</sub> -TDEC <sub>0</sub> | 0000      | 0010      | 1110      | 0100    | 0101    | 1100      | 1101      |

| SD(a)                                | tri-state | RS-232    | V.35-     | RS-422- | RS-485– | RS-422-   | RS-422-   |

| SD(b)                                | tri-state | tri-state | V.35+     | RS-422+ | RS-485+ | RS-422+   | RS-422+   |

| TR(a)                                | tri-state | RS-232    | RS-232    | RS-422- | RS-485– | RS-422-   | RS-422-   |

| TR(b)                                | tri-state | tri-state | tri-state | RS-422+ | RS-485+ | RS-422+   | RS-422+   |

| RS(a)                                | tri-state | RS-232    | RS-232    | RS-422– | RS-485– | RS-422–   | RS-422-   |

| RS(b)                                | tri-state | tri-state | tri-state | RS-422+ | RS-485+ | RS-422+   | RS-422+   |

| RL(a)                                | tri-state | RS-232    | RS-232    | RS-422– | RS-485– | RS-423    | RS-423    |

| RL(b)                                | tri-state | tri-state | tri-state | RS-422+ | RS-485+ | tri-state | tri-state |

| LL(a)                                | tri-state | RS-232    | RS-232    | RS-422- | RS-485– | RS-423    | RS-423    |

| LL(b)                                | tri-state | tri-state | tri-state | RS-422+ | RS-485+ | tri-state | tri-state |

| ST(a)                                | tri-state | RS-232    | V.35-     | RS-422- | RS-485– | RS-422–   | RS-422-   |

| ST(b)                                | tri-state | tri-state | V.35+     | RS-422+ | RS-485+ | RS-422+   | RS-422+   |

| TT(a)                                | tri-state | RS-232    | V.35-     | RS-422- | RS-485- | RS-422-   | RS-422-   |

| TT(b)                                | tri-state | tri-state | V.35+     | RS-422+ | RS-485+ | RS-422+   | RS-422+   |

\*The ST and TT driver outputs cannot be enabled simultaneously.

Table 1. SP502 Drivers

Figure 6. Typical Operating Circuit

can operate up to 120kbps. The RS-232 drivers are used in RS-232 mode for all signals, and also in V.35 mode where they are used as the control line signals.

The RS-423 drivers output a minimum of ±3.6V level single–ended signals (with 450 $\Omega$  loading) and can operate up to 120kbps. Open circuit V<sub>OL</sub> and V<sub>OH</sub> measurements may exceed the ±6V limitation of RS-423. The RS-423 drivers are used in RS-449 and EIA-530 modes as RL and LL outputs.

The third type of driver supports RS-485, which is a differential signal that can maintain  $\pm 1.5$ V differential output levels with a worst case load of 54 $\Omega$ . The signal levels and drive capability of the RS-485 drivers allow the drivers to also support RS-422 requirements of  $\pm 2$ V differential output levels with 100 $\Omega$  loads. The RS-422 drivers are used in RS-449 and EIA-530 modes as clock, data, and some control line signals.

The RS-485–type drivers are also used in the V.35 mode. V.35 levels require  $\pm 0.55$ V signals with a load of 100 $\Omega$ . In order to meet the voltage requirements of V.35, external series resistors with source impedance termination resistors must be implemented to voltage divide the driver outputs from 0 to +5V to 0 to +0.55V. *Figure 6* shows the values of the resistor network and how to connect them. The termination network also achieves the 50 $\Omega$  to 150 $\Omega$  source imped-

ance for V.35. For applications that require V.11 signals for clock and data instead of V.35 levels, omit the external termination networks. All of the differential drivers, RS-485, RS-422, and V.35 can operate up to 5Mbps.

#### Receivers

The **SP502** is equipped with seven (7) receivers which can be programmed in six (6) different modes of operation. One of the seven (7) receivers (RxT) is part of a half-duplex channel, which means its inputs are shared with a driver output, as shown in the Mode Diagrams. The RxT receiver has its inputs internally connected to the TT(a) and TT(b) pins. The select pin labeled ST/TT enables either the TT-driver or the ST-driver, but it does not disable the receiver. The RxT receiver is always connected to the TT(a) and TT(b) pins. Any signal that is received or transmitted on TT(a) and TT(b) will trigger a TTL-output at the RxT pin.

Control for the mode selection is done via a 4– bit control word that is independent from the driver control word. The coding for the drivers and receivers is identical. Therefore, if the modes for the drivers and receivers are supposed to be identical in the application, the control lines can be tied together.

Like the drivers, the receivers are pre-arranged for the specific requirements of the interface. As the operating mode of the receivers is changed,

| Pin Label                            | Mode:     | RS-232      | V.35        | RS-422  | RS-485  | RS-449      | EIA-530     |

|--------------------------------------|-----------|-------------|-------------|---------|---------|-------------|-------------|

| RDEC <sub>3</sub> -RDEC <sub>0</sub> | 0000      | 0010        | 1110        | 0100    | 0101    | 1100        | 1101        |

| RD(a)                                | Undefined | RS-232      | V.35-       | RS-422- | RS-485– | RS-422-     | RS-422-     |

| RD(b)                                | Undefined | 15kΩ to GND | V.35+       | RS-422+ | RS-485+ | RS-422+     | RS-422+     |

| RT(a)                                | Undefined | RS-232      | V.35-       | RS-422- | RS-485– | RS-422-     | RS-422-     |

| RT(b)                                | Undefined | 15kΩ to GND | V.35+       | RS-422+ | RS-485+ | RS-422+     | RS-422+     |

| CS(a)                                | Undefined | RS-232      | RS-232      | RS-422- | RS-485– | RS-422-     | RS-422-     |

| CS(b)                                | Undefined | 15kΩ to GND | 15kΩ to GND | RS-422+ | RS-485+ | RS-422+     | RS-422+     |

| DM(a)                                | Undefined | RS-232      | RS-232      | RS-422- | RS-485- | RS-422-     | RS-422-     |

| DM(b)                                | Undefined | 15kΩ to GND | 15kΩ to GND | RS-422+ | RS-485+ | RS-422+     | RS-422+     |

| RR(a)                                | Undefined | RS-232      | RS-232      | RS-422- | RS-485– | RS-422-     | RS-422-     |

| RR(b)                                | Undefined | 15kΩ to GND | 15kΩ to GND | RS-422+ | RS-485+ | RS-422+     | RS-422+     |

| IC(a)                                | Undefined | RS-232      | RS-232      | RS-422- | RS-485– | RS-423      | RS-423      |

| IC(b)                                | Undefined | 15kΩ to GND | 15kΩ to GND | RS-422+ | RS-485+ | 15kΩ to GND | 15kΩ to GND |

| SCT(a)                               | Undefined | RS-232      | V.35-       | RS-422- | RS-485– | RS-422-     | RS-422-     |

| SCT(b)                               | Undefined | 15kΩ to GND | V.35+       | RS-422+ | RS-485+ | RS-422+     | RS-422+     |

\*TT(a) and TT(b) can be programmed as driver outputs or receiver inputs. *Table 2. SP502 Receivers*  the electrical characteristics will change to support the requirements of clock, data, and control line receivers. *Table 2* shows a summary of the electrical characteristics of the receivers in the different interface modes. Unused receiver inputs can be left floating without causing oscillation. To ensure a desired state of the receiver output, a pull–up resistor of  $100k\Omega$  to +5V should be connected to the inverting input for a logic LOW, or the non–inverting input for a logic high. For single-ended receivers, a pull–down resistor to ground of  $5k\Omega$  is internally connected, which will ensure a logic HIGH output.

There are three basic types of receivers — RS-232, RS-423, and RS-485. The RS-232 receiver is a single–ended input with a threshold of 0.8V to 2.4V. The RS-232 receiver has an operating voltage range of  $\pm 15V$  and can receive signals up to 120kbps. RS-232 receivers are used in RS-232 mode for all signal types, and in V.35 mode for control line signals.

The RS-423 receivers are also single–ended but have an input threshold as low as  $\pm 200$ mV. The input impedance is guaranteed to be greater than 4k $\Omega$ , with an operating voltage range of  $\pm 7$ V. The RS-423 receivers can operate up to 120kbps. RS-423 receivers are used for the IC signal in RS-449 and EIA-530 modes, as shown in *Table 2*.

The third type of receiver supports RS-485, which is a differential interface mode. The RS-485 receiver has an input impedance of  $15k\Omega$  and a differential threshold of  $\pm 200$ mV.

Since the characteristics of an RS-422 receiver are actually subsets of RS-485, the receivers for RS-422 requirements are identical to the RS-485 receivers. RS-422 receivers are used in RS-449 and EIA-530 for receiving clock, data, and some control line signals. The RS-485 receivers are also used for the V.35 mode. V.35 levels require the  $\pm 0.55V$  signals with a load of  $100\Omega$ . In order to meet the V.35 input impedance of  $100\Omega$ , the external termination network of *Figure 6* must be applied. The threshold of the V.35 receiver is  $\pm 200$ mV. The V.35 receivers can operate up to 5Mbps. All of the differential receivers can receive data up to 5Mbps.

#### Decoder

The SP502 has the ability to change the interface mode of the drivers or receivers via an 8-bit switch. The decoder for the drivers and receivers is not latched; it is merely a combinational logic switch. The codes shown in Tables 1 and 2 are the only specified, valid modes for the SP502. Undefined codes may represent other interface modes not specified or random outputs (consult the factory for more information). The drivers are controlled with the data bits labeled TDEC<sub>3</sub>-TDEC<sub>0</sub>. The drivers can be put into tri-state mode by writing 0000 to the driver decode switch. The receivers are controlled with data bits  $RDEC_3$ -RDEC<sub>0</sub>; the code 0000 written to the receivers will place the outputs in an undetermined state. All receivers, with the exception of SCT, do not have tri-state capability; the outputs will either be HIGH or LOW depending upon the state of the receiver input.

Figure 7. Mode Diagram — RS-232

Figure 8. Mode Diagram – V.35

Figure 9. Mode Diagram — RS-422

Figure 10. Mode Diagram — RS-449

Figure 11. Mode Diagram — RS-485

Figure 12. Mode Diagram — EIA-530

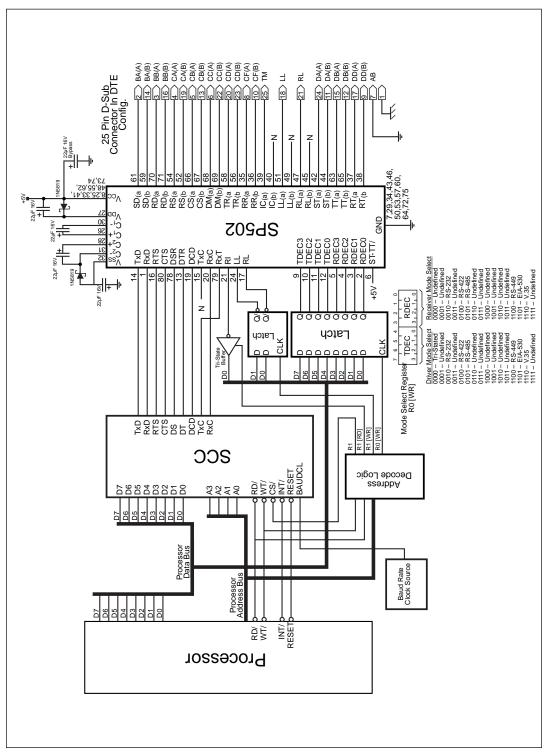

# **APPLICATION EXAMPLE**

The example application that follows is a fully configured serial I/O channel in a DTE configuration. The example is comprised of the following functional elements:

- Processor

- SCC

- SP502

- Mode Select Register (R0[WR])

- RL & LL Control Bit Register (R1[WR])

- RI Status Bit Register (R1[RD])

- Address Decode Logic

- Baud Rate Clock Source

- I/O Connector Interface

Each of the elements of the application example are described below. Please refer to *Figure13*.

#### Processor

The example schematic shows a generic 8-bit processor connected to a generic SCC. The processor is also connected to three registers. The registers are described in further detail below.

#### Address Decode Logic

The address decode logic is connected to the Processor control and address busses and provides the logic necessary to decode the I/O read and write operations for the SCC, Mode Select Register, RL and LL Control Bit Register and the RI Status Bit Register.

#### SCC

The SCC provides the I/O functions for a single serial channel. The SCC is connected to the Processor I/O bus and is programmed by the user software. The SCC's TTL-level serial I/O pins are connected to the corresponding TTL-level serial I/O pins on the **SP502**.

#### SP502

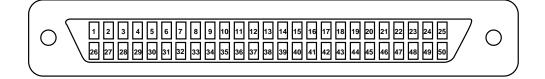

The **SP502** provides buffering and translation from TTL levels to the selected physical level interface standard, such as RS-232, V.35, etc. The physical level interface pins are connected to a standard 25 pin D-subminiature connector wired in a DTE configuration with the pin assignments corresponding to the EIA-530 specification. This choice was purely arbitrary. However, it provides all the necessary signals to support standards other than EIA-530, such as V.35, RS-232, RS-449, etc. with an appropriate cable adapter.

The **SP502** driver and receiver modes are independently configured by programming the **SP502**'s RDEC and TDEC input pins. In the example, the pins are driven by the Mode Select Register with a programmed value stored by the user's software.

Since the **SP502** is shown in a DTE configuration, the example assumes that any synchronous interface clocking will be provided by the attached DCE device. Consequently, the ST/TT pin is tied to +5V, thus causing the **SP502** to receive the transmit clock on the TT(a) and TT(b) input pins and output the transmit clock to the SCC on the RxT output pin. The receive clock is input to the **SP502** on the RT(a) and RT(b) pins and output to the SCC on the RxC pin.

#### **Mode Select Register**

The mode select register is an 8-bit latch attached to the Processor data bus. The Processor, under user-software control, can program the Mode Select Register with the appropriate values to select the **SP502**'s driver and receiver modes.

The table shown on the schematic below the register lists the values for programming the register to drive the RDEC and TDEC pins on the **SP502** for the desired physical level interface. The receivers and drivers can be programmed independently, but in this example the Mode Select Register must be programmed with both the RDEC and TDEC values at the same time. This is because the RDEC and TDEC pins are driven from the same 8-bit latch.

Note that selecting modes for TDEC that are shown in the table as undefined will result in the drivers operating in an undefined mode and should not be used. Likewise, selecting modes for RDEC that are shown in the table as undefined will result in indeterminate logic levels present on the TTL outputs of the **SP502**. Undefined RDEC or TDEC values should never be programmed.

Rev. 7/21/03

Figure 13. DTE Serial Communications Channel

Several other approaches for driving the RDEC and TDEC signals are possible. One approach would use two independent 4-bit latches, one each to drive the RDEC and TDEC pins as separate groups. Another approach would use one 4-bit latch, each output of the latch would drive a corresponding pair of RDEC/TDEC signals. For instance, RDEC<sub>0</sub> and TDEC<sub>0</sub> could be tied together and be driven by the low order bit of the 4-bit latch.

#### **RL & LL Control Bit Registers**

A 2-bit latch is used to allow the Processor to program the states of the RL and LL interface signals. This latch is necessary since most SCCs do not support RL and LL control signals.

#### **RI Status Bit Register**

A 1-bit read register is implemented using a tri-state buffer. This will allow the Processor to read the state of the **RI** (Ring Indicator) interface signal. This is necessary since most SCCs do not support the **RI** interface signal.

The example interface shows the **SP502A**'s IC(a) input tied to the EIA-530 signal TM (Test Mode). EIA530 does not specify an **RI** signal. If EIA-530 operation is required, the **RI** Status Bit Register could be used to monitor the condition of the TM signal or it could be ignored. For other interface standards, the connector pin 25 on the schematic could be tied to the **RI** signal through a cable adapter arrangement. For instance, if RS-232 operation is used, pin 25 of the connector could be tied to pin 22 of the RS-232 adapter (circuit CE) and the **RI** Status Bit Register then used to monitor the RS-232 signal for ring indicator.

#### **Baud Rate Clock Source**

Most SCCs require an external clock source for operation in asynchronous and self-clocking applications.

#### I/O Connector Interface

The I/O connector is wired to the **SP502A** such that the interface represents a DTE device. As shown, the connector is wired in an EIA-530 configuration with EIA-530 signal mnemonics. A 25-pin connector wired to the EIA-530 specification provides pins for all interface signals supported by the **SP502**. If the **SP502** is programmed for other physical interfaces, such as V.35, then an adapter cable will provide the necessary conversion from the EIA-530 pin-outs to those required by the V.35 standard together with its ISO-2593 connector.

#### **Notes Regarding V.35 Operation**

The user will have to provide additional resistor networks if correct V.35 signal levels and termination impedances are required. This is necessary because the SP502 does not provide V.35 signal terminations when programmed for V.35 operation. Two approaches are possible. First, if the SP502 is permanently programmed to operate as V.35 only, with no other interface standard required, then the appropriate resistors can be mounted on the PCB near the SP502. Second, if the SP502 will be programmed for a variety of standards, then a better approach might be to provide the resistors as part of the cable adapter assembly used to convert from the standard EIA-530 connector pin-outs shown in the example to the V.35/ISO-2593 connector and pin-outs.

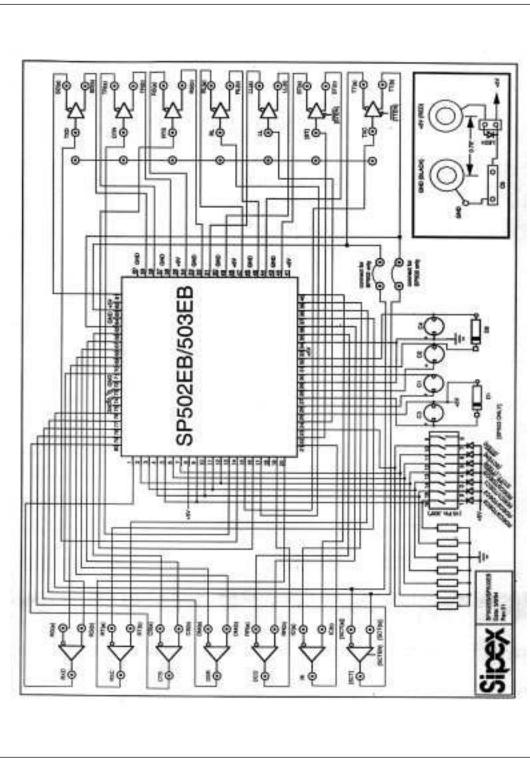

# SP502/SP503 EVALUATION BOARD

The **SP502/SP503 Evaluation Board** (EB) Is designed to offer as much flexibility to the user as possible. Each board comes equipped with an 80-pin QFP Zero-Insertion Force socket to allow for testing of multiple devices. The control lines and inputs and outputs of the device can be controlled either manually or via a data bus under software control. There is a 50-pin connector to allow for easy connection to an existing system via ribbon cable. There are also open areas on the PC board to add additional circuitry to support application-specific requirements.

#### **Manual Control**

The SP502/SP503EB will support both the SP502 or SP503 multi-mode serial transceivers. When used for the SP502, disregard all notation on the board that is in [brackets]. The SP502 has a half-duplex connection between the RxT receiver and the TT driver. Due to this internal connection, the RxT receiver inputs can be accessed via the TT(a) and TT(b) pins. If the user needs separate receiver input test pins, jumpers JP1 and JP2 can be inserted to allow for separate receiver inputs located at SCT(a) and SCT(b). The corresponding TTL output for this receiver is labeled as SCT. This test point is tied to pin 79 of the SP502 or SP503. Pin 7 of the evaluation board is connected to the DIP switch, and is labeled as (SCTEN). When used with the SP502, this pin should be switched to a low state. When the evaluation board is used with the SP503, pin 7 is a tri-state control pin for the SCT receiver.

The transceiver I/O lines are brought out to test pins arranged in the same configuration as shown elsewhere in this data sheet. A top layer silk-screen shows the drivers and receivers to allow direct correlation to the data sheet. The transmitter and receiver decode bits are tied together and are brought out to a DIP switch for manual control of both the driver and receiver interface modes. Since the coding for the drivers and receivers is identical, the bits have been tied together. The DIP switch has 7 positions, four of which are reserved for the TDEC/RDEC control. The other three are used as tri-state control pins. The labels that are in [brackets] apply only to the **SP503**. If a logic one is asserted, the corresponding red LED will be lit. If a zero is asserted, the corresponding red LED will not be lit.

#### Software Control

A 50-pin connector brings all the analog and digital I/O lines,  $V_{cc}$ , and GND to the edge of the card. This can be wired to the user's existing design via ribbon cable. The pinout for the connector is described in the following section. When the evaluation board is operated under software control, the DIP switch should be set up so that all bits are LOW (all LEDs off). This will tie pull-down resistors from the inputs to ground and let the external system control the state of the control inputs.

#### **Power and Ground Requirements**

The evaluation board layout has been optimized for performance by using basic analog circuit techniques, The four charge-pump capacitors must be  $22\mu F(16V)$  and be placed as close to the unit as possible; tantalum capacitors are suggested. The decoupling capacitor must be a minimum of 1µF; depending upon the operating environment, 10µF should be enough for worst case situations. The ground plane for the part must be solid, extending completely under the package. The power supplies for the device should be as accurate as possible; for rated performance ±5% is necessary. The power supply current will vary depending upon the selected mode, the amount of loading and the data rate. As a maximum, the user should reserve 200mA for  $I_{cc}$ . The worst-case operating mode is RS-485 under full load of six (6) drivers supplying 1.6V to 54 $\Omega$  loads. The power and ground inputs can be supplied through either the banana jacks on the evaluation board (Red =  $V_{cc}$  $=+5V\pm5\%$ ; Black = GND) or through the connector.

For reference, the 80-pin QFP Socket is a TESCO part number FPQ-80-65-09A. The 50-pin connector is an AMP part number 749075-5.

Figure 13. SP502/503 Evaluation Board Schematic

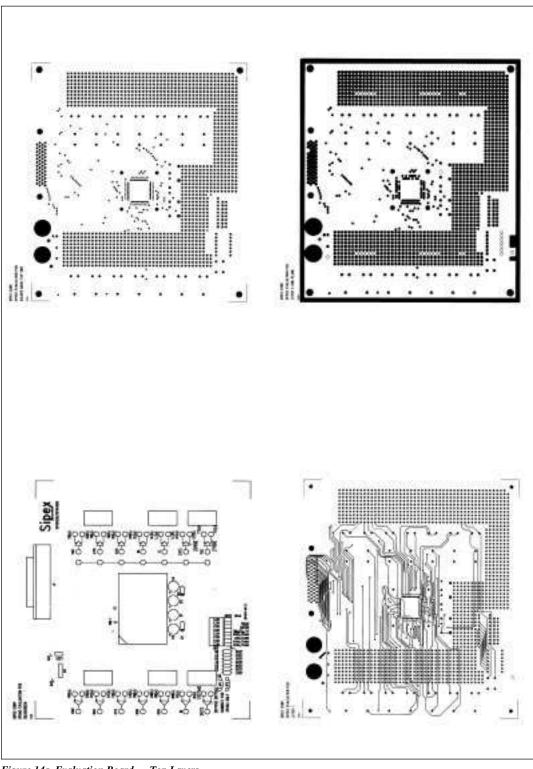

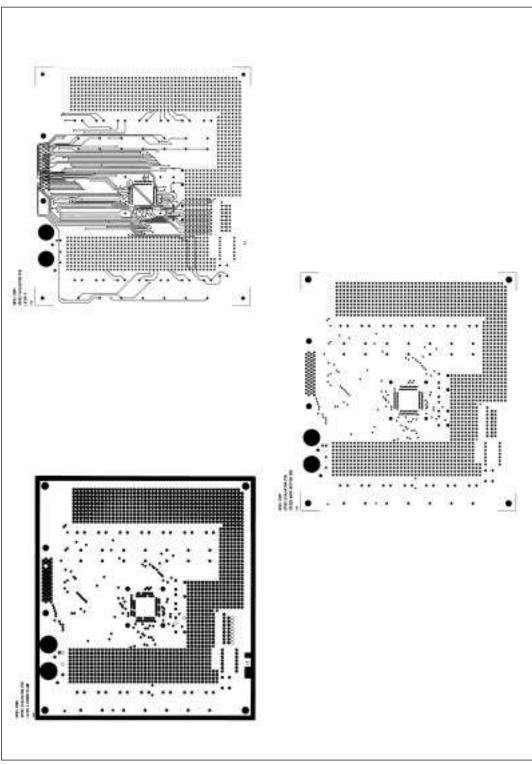

Figure 14a. Evaluation Board — Top Layers

SP502 Multi-Mode Serial Transceiver

© Copyright 2003 Sipex Corporation

Figure 14b. Evaluation Board — Bottom Layers

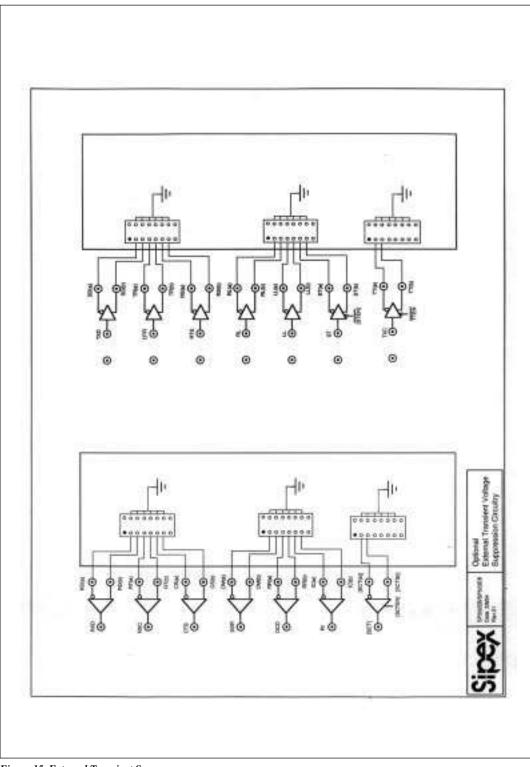

Figure 15. External Transient Suppressors

SP502 Multi-Mode Serial Transceiver

© Copyright 2003 Sipex Corporation

# EDGE DUT PIN CONNECTOR DESCRIPTIONS

- 01 TxD (pin 14) –TTL Input Transmit data; source for SD(a) and SD(b) outputs.

- 02 DTR (pin 13) TTL Input Data terminal ready: source for TR(a) and TR(b) outputs.

- 03 ST/TT (pin 6) –TTL Input ST/TT select pin; enables ST drivers and disables TT drivers when high. Disables ST drivers and enables TT drivers when low.

- 04 DEC<sub>3</sub>/RDEC<sub>3</sub> (pin 5) TTL Input Transmitter/Receiver decode register.

- 05 TDEC<sub>2</sub>/RDEC<sub>2</sub> (pin 4) TTL Input Transmitter/Receiver decode register.

- 06 TDEC<sub>1</sub>/RDEC<sub>1</sub> (pin 3) TTL Input Transmitter/Receiver decode register.

- 07  $TDEC_0/RDEC_0$  (pin 2) TTL Input Transmitter/Receiver decode register.

- 08 RxD (pin 1) TTL Output Receive data; sourced from RD(a) and RD)b) inputs.

- 09 CTS (pin 80) TTL Output Clear to send; sourced from CS(a) and CS(b) inputs.

- 10 RxT (pin 79) TTL Output RxT; sourced from TT(a), TT(b) inputs.

- 11 DSR (pin 78) TTL Output Data set ready; sourced from DM(a) and DM(b) inputs.

- 12 RD(b) (pin 71) Analog In Receive data, non–inverted; source for RxD.

#### EDGE DUT PIN CONNECTOR DESCRIPTIONS

- 13 RD(a) (pin 70) Analog In Receive data, inverted: source for RxD.

- 14 DM(b) (pin 69) Analog In Data mode, non–inverted; source for DSR.

- 15 DM(a) (pin 68) Analog In Data mode, inverted; source for DSR.

- 16 CS(b) (pin 67) Analog In Clear to send; non–inverted; source for CTS.

- 17 CS(a) (pin 66) Analog In Clear to send, inverted; source for CTS.

- 18 TT(b) (pin 65) Analog Out Terminal timing, non–inverted: sourced from TxC input.

- 19 TT(a) (pin 63) Analog Out Terminal timing; inverted: sourced from TxC input.

- 20 TR(a) (pin 58) Analog Out Terminal ready, inverted; sourced from DTR.

- 21 TR(b) (pin 56) Analog Out Terminal ready; non–inverted; sourced from DTR.

- 22 SD(a) (pin 61) Analog Out Send data, inverted; sourced from TxD.

- 23 SD(b) (pin 59) Analog Out Send data; non–inverted; sourced from TxD.

- 24 RS(a) (pin 54) Analog Out Ready to send; inverted; sourced from RTS.

- 25 RS(b) (pin 52) Analog Out Ready to send, non–inverted; sourced from RTS.

Rev. 7/21/03

# EDGE DUT PIN CONNECTOR DESCRIPTIONS

- 26 ST (pin 22) TTL Input Send Timing; source for ST(a) and ST(b) outputs. SP503 only.

- 27 STEN (pin 23) TTL Input Driver enable control pin; active low. SP503 only,

- 28 SCT(a) (pin 76) Analog Input Inverting; input for SCT receiver; SP503 only.

- 29 SCT(b) (pin 77) Analog Input Non– inverting; input for SCT receiver. SP503 only.

- 30  $V_{CC} +5V$  for all circuitry.

- 31 GND signal and power ground.

- 32 LL(a) (pin 51) Analog Out Local loopback, inverted; sourced from LL.

- 33 LL(b) (pin 49) Analog Out Local loopback, non–inverted sourced from LL.

- 34 RL(a) (pin 47) Analog Out Remote loopback; inverted; sourced from RL.

- 35 RL(b) (pin 45) Analog Out Remote loopback; non–inverted; sourced from RL.

- 36 ST(b) (pin 44) Analog Out Send timing, non–inverted; sourced from TxC.

- 37 ST(a) (pin 42) Analog Output –Send timing, inverted; sourced from TxC.

- 38 IC(b) (pin 40) Analog In Incoming call; non–inverted; source for Rl.

### EDGE DUT PIN CONNECTOR DESCRIPTIONS

- 39 IC(a) (pin 39) Analog In Incoming call; inverted; source for Rl.

- 40 RT(b) (pin 38) Analog In Receive timing, non–inverted; source for RxC.

- 41 RT(a) (pin 37) Analog In Receive timing; inverted; source from RxC.

- 42 RR(b) (pin 36) Analog In Receiver ready; non–inverted; source for DCD.

- 43 RR(a) (pin 35) Analog In Receiver ready; inverted; source for DCD.

- 44 LL (pin 24) TTL Input Local loopback; source for LL(a) and LL(b) outputs.

- 45 R1 (pin 21) TTL Output Ring indicator; sourced from IC(a) and IC(b) inputs.

- 46 RxC (pin 20) TTL Output Receive clock; sourced from RT(a) and RT(b) inputs.

- 47 DCD (pin 19) TTL Output Data carrier detect; sourced from RR(a) and RR(b) inputs.

- 48 RL (pin 17) Analog Out Remote loopback; source for RL(a) and RL(b) outputs.

- 49 RTS (pin 16) TTL Input Ready to send; source for RS(a) and RS(b) outputs.

- 50 TxC (pin 15) TTL Input Transmit clock; source for TT(A) and TT(B) outputs.

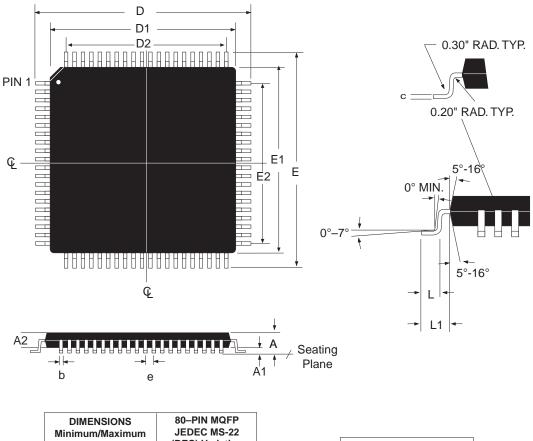

# PACKAGE: 80 PIN MQFP

| DIMENSIONS<br>Minimum/Maximum<br>(mm) | JEDEC MS-22<br>(BEC) Variation |     |      |

|---------------------------------------|--------------------------------|-----|------|

| SYMBOL                                | MIN                            | NOM | MAX  |

| Α                                     |                                |     | 2.45 |

| A1                                    | 0.00                           |     | 0.25 |

| A2                                    | 1.80 2.00 2.                   |     | 2.20 |

| b                                     | 0.22 0.4                       |     | 0.40 |

| D                                     | 17.20 BSC                      |     |      |

| D1                                    | 14.00 BSC                      |     |      |

| D2                                    | 12.35 REF                      |     |      |

| E                                     | 17.20 BSC                      |     |      |

| E1                                    | 14.00 BSC                      |     |      |

| E2                                    | 12.35 REF                      |     |      |

| е                                     | 0.65 BSC                       |     |      |

| Ν                                     | 80                             |     |      |

| COMMON DIMENTIONS |            |      |       |  |  |

|-------------------|------------|------|-------|--|--|

| SYMBL             | MIN        | NOM  | MAX   |  |  |

| С                 | 0.11       |      | 23.00 |  |  |

| L                 | 0.73       | 0.88 | 1.03  |  |  |

| L1                | 1.60 BASIC |      |       |  |  |

80 PIN MQFP (MS-022 BC)

Rev. 7/21/03

SP502 Multi-Mode Serial Transceiver

© Copyright 2003 Sipex Corporation

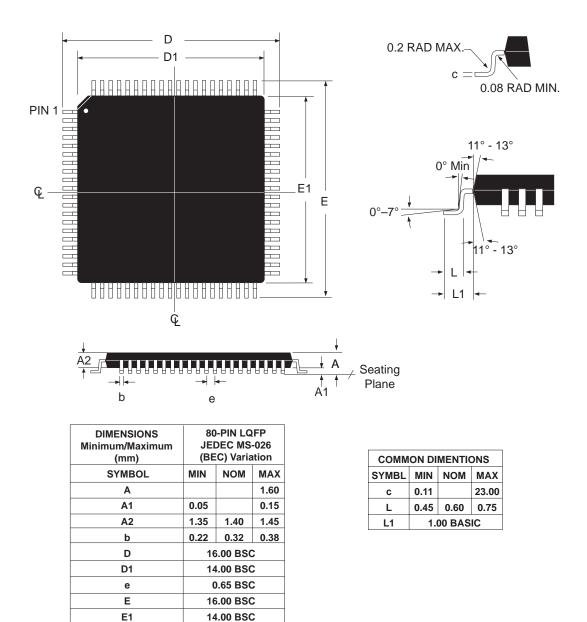

# PACKAGE: 80 PIN LQFP

# **80 PIN LQFP**

SP502 Multi-Mode Serial Transceiver

80

Ν

| ORDERING INFORMATION |                   |               |  |  |  |  |

|----------------------|-------------------|---------------|--|--|--|--|

| Model                | Temperature Range | Package Types |  |  |  |  |

| SP502CF              | 0°C to +70°C      |               |  |  |  |  |

| SP502CM              | 0°C to +70°C      |               |  |  |  |  |

ANALOG EXCELLENCE

Sipex Corporation

Headquarters and Sales Office 233 South Hillview Drive Milpitas, CA 95035 TEL: (408) 934-7500 FAX: (408) 935-7600

Sales Office 22 Linnell Circle Billerica, MA 01821 TEL: (978) 667-8700 FAX: (978) 670-9001 e-mail: sales@sipex.com

Sipex Corporation reserves the right to make changes to any products described herein. Sipex does not assume any liability arising out of the application or use of any product or circuit described hereing; neither does it convey any license under its patent rights nor the rights of others.

Rev. 7/21/03

SP502 Multi-Mode Serial Transceiver

© Copyright 2003 Sipex Corporation