[Channel Lab] 72 10 € 09 .BRUBO 182 :19 HUPB 14 4120 17 17 PB JE PP, SFB 5

# S5H1420 [Channel Decoder for DVB-S/DSS] DATA SHEET

Samsung Electronics Co, Ltd.

10 Jan. 2004 (Version 4.5.1)

Note: This documentation is preliminary and is subject to change. Samsung Electronics Co, Ltd. reserves the right to do any kind of modification in this data sheet regarding hardware or software implementations without notice.

Samsung Electronics Co, Ltd. Proprietary Information

-1-

| TABLE OF CONTENTS                                                                                                         | page |

|---------------------------------------------------------------------------------------------------------------------------|------|

| 1. INTRODUCTION                                                                                                           | 3    |

| 1.1 Overview                                                                                                              |      |

| 1.2 Features                                                                                                              |      |

| 1.3 Applications                                                                                                          |      |

| 1.4 Ordering Information                                                                                                  |      |

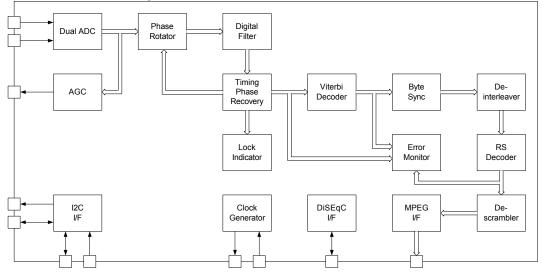

| 1.5 Functional bock diagram                                                                                               |      |

|                                                                                                                           |      |

| 2. IN INFORMATION                                                                                                         | 4    |

| 2.1 Pin assignment<br>2.2 Pin description                                                                                 | 4    |

| 2.2 Pin description                                                                                                       | 5    |

| 3. FUNCTIONAL DESCRIPTION                                                                                                 | 6    |

| 3.1 Signal processing                                                                                                     | 6    |

| 3.1.1 I & Q inputs                                                                                                        | 6    |

| 3.1.2 PRE – AGC                                                                                                           | 6    |

| 3.1.3 Root raised cosine and rate conversion filter                                                                       | 6    |

| 3.1.3 Offset cancellation<br>3.1.4 POST – AGC                                                                             | 6    |

| 3.1.4 POST – AGC                                                                                                          | 6    |

| 3.2 Timing recovery                                                                                                       | 6    |

| 3.2.1 Timing control                                                                                                      | 6    |

| 3.2.2 Loop equation                                                                                                       | 7    |

| <ul><li>3.2.3 Timing lock indicator</li><li>3.3 Carrier recovery and derotator loop</li><li>3.3.1 Loop equation</li></ul> |      |

| 3.3 Carrier recovery and derotator loop                                                                                   |      |

| 3.3.1 Loop equation                                                                                                       | 7    |

| 3.3.2 Carrier lock detector                                                                                               |      |

| 3.3.3 Derotator frequency                                                                                                 | 8    |

| 3.3.4 Automatic frequency detector                                                                                        | 8    |

| 3.3.5 False lock                                                                                                          | 8    |

| 3.4 Forward error correction                                                                                              | 8    |

| 3.4.1 FEC modes                                                                                                           | 8    |

| 3.4.2 Soft decision<br>3.4.3 Viterbi decoder and synchronization                                                          | 8    |

| 3.4.3 Viterbi decoder and synchronization                                                                                 | 8    |

| 3.4.4 Synchronization                                                                                                     | 9    |

| 3.4.5 Error monitoring                                                                                                    | 9    |

| 3.4.6 Convolutional deinterleaver                                                                                         | 9    |

| 3.4.7 Reed-Solomon decoder and descramble<br>3.4.8 Spectrum Inverse of Code Rate 5/6                                      | 9    |

| 3.4.8 Spectrum Inverse of Code Rate 5/6                                                                                   | 10   |

| 3.4.9 MPEG interface                                                                                                      | 10   |

| 3.4.9 MPEG interface<br>3.4.9.1 Parallel output interface                                                                 | 10   |

| 3.4.9.2 Serial output interface.                                                                                          | 10   |

| 3.4.9.2 Serial output interface<br>3.4.9.3 MPEG Clock Control                                                             |      |

| 3.5 Front end interface                                                                                                   | 13   |

| 3.5.1 l <sup>2</sup> C interface                                                                                          | 13   |

| 3.5.2 Write operation (Normal Mode)                                                                                       | 13   |

| 3.5.3 Read operation (Normal Mode)                                                                                        | 13   |

| 3.5.2 Write operation (Normal Mode)<br>3.5.3 Read operation (Normal Mode)<br>3.5.4 Identification register.               | 13   |

| 3.5.5 Sampling frequency.                                                                                                 |      |

| 3.5.6 Clock generation                                                                                                    |      |

| 3.5.7 <sup>12</sup> C Bus reneater                                                                                        | 14   |

| 3.5.7 I <sup>2</sup> C Buš repeater<br>3.5.8 DiSEqC interface                                                             |      |

| 4. REGISTER LIST                                                                                                          |      |

| 5. ELECTRICAL CHARACTERISTICS                                                                                             |      |

| 5. ELECTRICAL CHARACTERISTICS.                                                                                            |      |

| 5.1 Absolute maximum ratings<br>5.2 Recommended operating conditions                                                      |      |

| 5.2 Recommended operating conditions.                                                                                     |      |

| 5.3 DC electrical characteristics                                                                                         |      |

| 5.4 A/D converter                                                                                                         |      |

| 5.5 Timing characteristics                                                                                                |      |

| 5.6 I <sup>2</sup> C Bus characteristics                                                                                  |      |

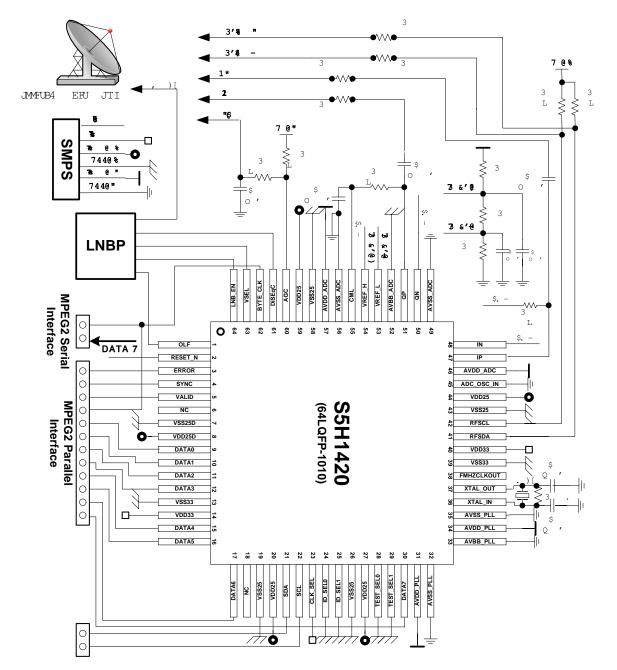

| 6. APPLICATION EXAMPLES                                                                                                   |      |

| 6.1 Application examples with DVB-S Tuner                                                                                 | 29   |

| 7. PACKAGE DIMENSION                                                                                                      | 30   |

| 8. Data Sheet Update History                                                                                              |      |

# 1.1 Overview

The S5H1420 is a single chip channel decoder IC for DBS (Digital Broadcasting System for Satellite) receiver. It consists of a multi-standard QPSK/BPSK demodulator and FEC (Forward Error Correction) decoder compliant with DVB-S and DSS standard. For multi-antenna control it provides DiSEqC1.x and 2.0 standards.

#### 1.2 Features

- Compliant to DVB-S and DSS standard.

- Single chip decoder (ADC/QPSK/FEC).

- Flexible Interface (I<sup>2</sup>C, MPEG2).

- DiSEqC 1.x or 2.0 specification support.

- Satellite dish control.

- DC offset cancellation.

- Automatic gain control

- Nyquist filter: 0.35 for DVB-S, 0.2 for DSS.

- Fully digital synchronization.

Symbol timing recovery range up to ± 50000 ppm.

Carrier recovery range up to ±12.5% of symbol rate.

- Carrier offset cancellation up to ±1/2sampling frequency

- Modulation rate from 1 to 87Mbps(1 ~ 50 Msps)

- QPSK demodulation quality estimation

- Viterbi decoding quality estimation.

Viterbi Input and output BER measurement.

Support depuncturing code rate from 1/2 to 7/8.

- Convolutional deinterleaver and Reed-Solomon decoder

- Automatic byte and frame synchronization

- Automatic spectral inversion ambiguity resolution.

- I<sup>2</sup>C repeater for RF part

- Power down control

- Low power CMOS technology

- 3.3V Single power using diode for 2.5V

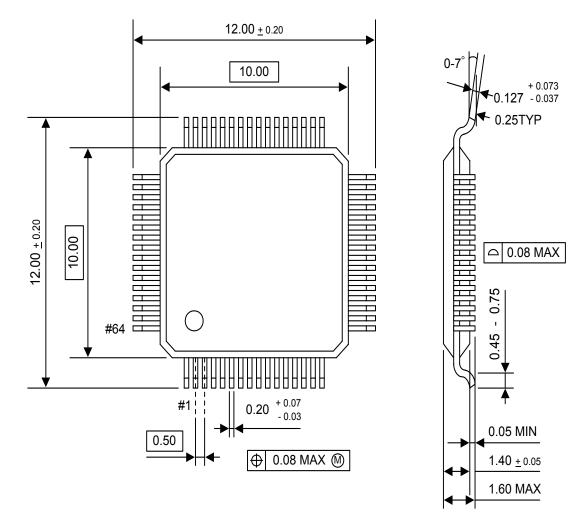

- Compact size package: 64LQFP-1010

## 1.3 Applications

DVB-S Receiver and STB Digital satellite TV PCI satellite Card

#### 1.4 Ordering information

| Type Number   | Package      | Description                                                                                 |

|---------------|--------------|---------------------------------------------------------------------------------------------|

| 1. S5H1420X01 | 64 LQFP-1010 | Plastic Low Profile Quad Flat Package;<br>64 leads (lead length 1.0mm)<br>Body 10x10x1.0 mm |

#### 1.5 Functional bock diagram

# 2. PIN INFORMATION

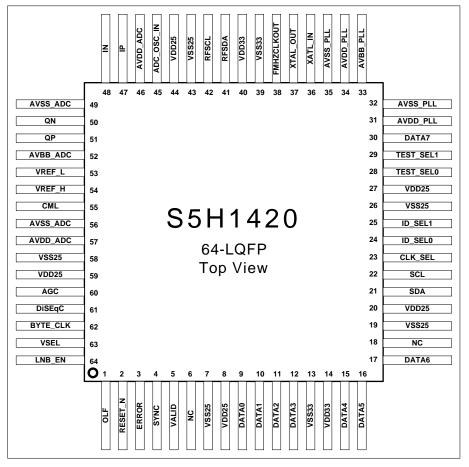

# 2.1 Pin Assignment

Figure1: Pin-out for 64-pin LQFP

Samsung Electronics Co, Ltd. Proprietary Information

#### 2.2 Pin descriptions

| 2.2 Pin descrip      |                      |                   |                              |

|----------------------|----------------------|-------------------|------------------------------|

| Pin Name             | I/O Cell Type        | Pin Number        | Description                  |

| OLF                  | Input                | 1                 | LNB Over Load Flag           |

| RESET_N              | Schmitt Trigger      | 2                 | H/W Reset (Active Low)       |

| ERROR                | Error out            | 3                 | Error indicator output       |

| SYNC                 | Sync_out             | 4                 | Synchronization output       |

| VALID                | Valid out            | 5                 | Valid data period            |

| NC                   | NC                   | 6                 | NC                           |

| DATA                 | Output [7]           | 30                | MPEG2 Stream Serial Data     |

| DATA                 | Output [7:0]         | [:]               | MPEG2 Stream Parallel Data   |

|                      |                      |                   | [Pin 30,17,16,15,12,11,10,9] |

| SDA                  | I/O-open drain(5V)   | 21                | Serial Data from host        |

| SCL                  | Input(5V)            | 22                | Serial Clock from host       |

| CLK_SEL              | Input                | 23                | Master Clock Select          |

| ID_SEL0              | Input                | 24                | I2C Address Select[T0]       |

| ID SEL1              | Input                | 24                | I2C Address Select[T1]       |

| TEST SEL0            | Input                | 28                | Test Mode Select[T2]         |

| TEST_SEL1            | Input                | 29                | Test Mode Select[T3]         |

| NC                   | NC                   | 18                | No connection                |

| XTAL_IN              | Oscillator Input     | 36                | Crystal Oscillator Input     |

| XTAL OUT             | Oscillator Output    | 37                | Crystal Oscillator Output    |

| FMHZCLKOUT           | Output               | 38                | Reference Clock Output       |

| RFSDA                | I/O-open drain (5V)  | 41                | RF Module Control SDA        |

| RFSCL                | n-ch-open drain (5V) | 42                | RF Module Control SCL        |

| ADC_OSC_IN           | Oscillator Input     | 45                | Oscillator Input             |

| AVDD ADC             | Digital Power        | 46                | ADC Total Power              |

| IP                   | Inphase Positive     | 47                | ADC Analog Input             |

| IN                   | Inphase Negative     | 48                | ADC Analog Input             |

| QN                   | Quadrature Negative  | 50                | ADC Analog Input             |

| QP                   | Quadrature Positive  | 51                | ADC Analog Input             |

| VREF L               | Analog Reference     | 53                | ADC Bottom Reference Voltage |

| VREF H               | Analog Reference     | 54                | ADC Top Reference Voltage    |

| CML                  | Analog Reference     | 55                | Common Mode Level Voltage    |

| AGC                  | n-ch Open Drain(5V)  | 60                | Gain Control Output          |

| DISEQC               | Bidirectional (5V)   | 61                | Antenna Select               |

| BYTE CLOCK           | Output (3.3V)        | 62                | Data Transfer clock          |

| VSEL                 | Output               | 63                | LNB Voltage Select Flag      |

| LNB EN               | Output               | 64                | LNB Enable Flag              |

| RF Interface & ADC I |                      | 01                |                              |

|                      |                      |                   |                              |

| ADC                  | AVDD_ADC             | 46, 57            |                              |

|                      | AVSS_ADC             | 56, 49            |                              |

|                      | AVBB_ADC             | 52                |                              |

| PLL                  | AVDD_PLL             | 31                |                              |

|                      | AVSS_PLL             | 32                |                              |

|                      | AVBB_PLL             | 33                |                              |

|                      | AVDD_PLL             | 34                |                              |

|                      | AVSS_PLL             | 35                |                              |

| IO                   | VSS33                | 13, 39            |                              |

|                      | VDD33                | 14, 40            |                              |

| Logic                | VSS25                | 7, 19, 26, 43, 58 |                              |

|                      | VDD25                | 8, 20, 27, 44, 59 |                              |

|                      |                      | -,,,,,,           |                              |

# **3. FUNCTIONAL DESCRIPTION**

## 3.1 Signal processing

#### 3.1.1 I and Q inputs

The dual ADC can get differential (IP/IN, QP/QN) or single inputs (IP, QP), I/Q signals from the tuner are fed to the IP and QP inputs through a DC coupling capacitor and IN and QN must be set DC voltage as CML (typical: 1/2VDD). The reference voltage of high [VREF-H] and low [VREF-L] should be supplied from external generator for application flexibility.

#### 3.1.2 PRE-AGC

The power of I/Q signal is compared to a programmable threshold value, and the difference is integrated. This signal is then converted into a Pulse Width Modulation (PWM) signal to drive the AGC output and it will be low pass filtered by a simple RC analog filter to control the gain command of any amplifier before the A/D converter. The PWM output operates at  $f_{clk}$ / (1, 4, 8 and 16) in order to decrease the radiated noise and to simplify the filter design, and is a 5 V tolerant open drain stage. The PRE-AGC Controls are in Address 0x07 and the PRE-AGC integrator register is in Address 0x15.

#### 3.1.3 Root raised cosine and rate conversion filter

The Root raised cosine (RRC) and rate conversion filter performs anti-aliasing filtering, root raised cosine shaping, rate conversion, timing synchronization and tracking with the timing loop. Two roll-off factors are available: 0.35 (DVB-S) and 0.20 (DSS).

#### 3.1.4 Offset cancellation

This device suppresses the residual I/Q DC component in the QPSK system control register in Addresses 0x05 and 0x06.

#### 3.1.5 POST-AGC

The POST-AGC shall be able to adjust the gain of the incoming I/Q sample from the RRC and rate conversion filter and implement the closed loop that sets the gain adjustment. The reset value (0x8000) of the POST-AGC integrator register can allow an initial settling time of less than 50k master clock periods.

The POST-AGC Controls are in Address 0x08 and the POST-AGC integrator register is in Address 0x16.

## 3.2 Timing recovery

#### 3.2.1 Timing control

The timing loop is programmed with the expected symbol frequency.

We have  $\delta$  parameter, which determine one or two sampling method. It can be expressed as:

$$(1+\alpha)$$

fsym >  $\frac{f_{clk}}{2}$  for  $\delta = 1$ .

In contrast,

$$(1+\alpha)$$

fsym <  $\frac{f_{clk}}{2}$  for  $\delta = 2$ .

Where  $\alpha$  is roll-off factor: 0.35 for DVB-S, 0.2 for DSS.

Thus

Timing NCO frequency word register setting is:

NCO frequency word =

$$\frac{f_{sym}}{f_{clk}} 2^{24} \delta$$

#### 3.2.2 Loop equation

The timing loop may be considered as a second order loop. The loop equation may be calculated using the following formula:

$$\mathcal{E} = 1 << ((P_g + 8) - I_g)$$

$$\mathcal{O} = \Phi_t \quad (1 << I_g)$$

Where,  $P_g$  is propagational gain,  $I_g$  is integral gain and  $\Phi_t$  is timing factor.

$$\Phi_t = 5.0 \times \frac{\frac{1}{2^{24}}}{\frac{1}{f_{sym}}}$$

And we can choose Loop  $f_{clk}$  Bandwidth (*BL*), as follows:

$$BL = \omega \times \frac{1}{2} \times \xi \times (1 + \frac{1}{4\xi^2})$$

Where  $\xi$  is the reference level of the  $\varepsilon$  and  $\omega$ .

$$\xi = \frac{\omega \times \varepsilon}{2}$$

#### 3.2.3 Timing lock indicator

The timing detector need to a lot of symbols for stabilization in order to lock after tuning frequency change of RF and it takes a 1-bit input signal, and uses the presence or absence of locking information to either count up or count down respectively.

The counter operates up to reaches its maximum value when the lock signal goes active. Two cases can cause the lock signal to go to unlocked state; one is assertion of the active-low reset and the other the counter go zero again. User can monitor the MSB 8 bits of TLL (timing lock loop) counter in Address 0x1a and the TLL lock flag in Address 0x14.

#### 3.3 Carrier recovery

The tracking range of the derotator is  $\pm f_{clk}/2$  ( $\pm f_{sampling}/2$ ).

This algorithm is used with QPSK reception, over a small range of capture phases and with a channel noise value over 3.0 dB.

#### 3.3.1 Loop equation

Like the timing loop, the carrier loop is a second-order system where two parameters,  $\varepsilon$  and  $\omega$ .

$$\varepsilon = 1 << ((P_g + 8) - I_g)$$

$$\omega = \Phi_p \quad (1 << I_g)$$

Where,  $P_q$  is propagational gain,  $I_q$  is integral gain and  $\Phi_p$  is phase factor.

$$\Phi_{p} = 75.4 \times \frac{\frac{1}{2^{24}}}{\frac{f_{sym}}{f_{clk}}}$$

Also, we can choose Loop Bandwidth (BL), as follows:

$$BL = \omega \times \frac{1}{2} \times \xi \times (1 + \frac{1}{4\xi^2})$$

Where  $\xi$  is the reference level of the  $\varepsilon$  and  $\omega$ .

$$\xi = \frac{\omega \times \varepsilon}{2}$$

3.3.2 Carrier lock detector

The carrier lock detector operates the same as the timing lock detector in the Phase locked loop (PLL). User can monitor the MSB 8 bits of PLL lock counter in Address 0x19 and the PLL lock flag in Address 0x14.

## 3.3.3 Derotator frequency

The derotator frequency can be either measured (read operation) or forced (write operation).

$$f_{derot} = \frac{f_{sym} \times 2^{24}}{f_{clk}}$$

#### 3.3.4 Automatic frequency detector

The automatic frequency detector (AFD) can evaluate the carrier frequency offset quickly, and may be coupled to the carrier recovery loop.

The digital loop filter of PLL has two paths, proportional and integral, with programmable gain respectively. The integral path contains an accumulator whose contents can be analyzed as a averaged carrier frequency offset.

The phase error signal goes into two paths, the respective gains are applied, the "I" path is integrated, and the two are added together. A Kicker of AFD can help PLL to achieve lock fast. The Kicker finds the phase error signal for large transitions, inserts a large value, into the "I" path. Therefore, PLL can trace the large frequency offset.

#### 3.3.5 False lock

A false lock occurs when phase lock has been detected in the QPSK, but the correct central frequency has not yet been reached. This situation occurs in QPSK for frequency offset points that are multiples of  $f_{sym}/4$ , where  $f_{sym}$  is the QPSK symbol rate, and also at other offsets dictated by the discrete nature of the carrier recovery loop. Therefore, the carrier recovery loop must be handled to take care of a false lock condition.

#### 3.4 Forward Error Correction

## 3.4.1 FEC modes

Since the S5H1420 is a multi-standard decoder, several combinations are possible, at different levels:

the demodulator may accept either QPSK or BPSK signals - the only impact is on the carrier algorithm choice. The algorithm choice also affects the carrier lock detector and the noise evaluation.

there are two primary options concerning the EEC operation, between DVR S. DSS and Reserved.

■ there are two primary options concerning the FEC operation - between DVB-S, DSS and Reserved Mode.

there are two options concerning the FEC feeding. The first is IQ flow, which is the usual case in QPSK modes DVB-S or DSS. The second mode is I-only flow, used for BPSK.

The FEC Mode Register is in Address Hex 22.

In Modes DVB-S and DSS, data is fed to the Soft Decisions.

## 3.4.2 Soft decisions

The adaptive equalizer output is converted into 4-bit sign-magnitude format by the soft decision block, for use by the Viterbi decoder. The MSB corresponds to the sliced bit value. The 3 LSBs of the soft decisions represent the confidence of the sliced bit value, where 111 are high confidence, and 000 is low confidence. A programmable set of thresholds can be used in generating the three LSBs and, consequently, in optimizing the Viterbi decoder performance as a function of code rate.

#### 3.4.3 Viterbi decoder and synchronization

The convolutional codes are generated by the polynomial  $G_x = 171$  octets and  $G_y = 133$  octets in modes DVB-S or DSS. The Viterbi decoder computes for each symbol the metrics of the four possible paths, proportional to the square of the Euclidian distance between the received I and Q and the theoretical symbol value.

The puncture rate and phase are estimated on the error rate basis. Several rates are allowed and may be enabled/disabled through register programming:

# ■1/2, 2/3, 3/4, 5/6, 7/8 for DVB-S

## ∎1/2, 2/3, 6/7 for DSS

For each enabled rate, the current error rate is compared to a programmable threshold.

If it is greater than this threshold, another phase (or another rate) is tried until the right rate is obtained. A programmable hysterics is added to avoid losing the phase during short-term perturbation. The rate may also be imposed by external software, and the phase is incremented only upon request by the microprocessor. The error rate may be read at any time in order to use an algorithm other than that implemented.

The Viterbi decoder produces an absolute decoding. The decoder is controlled via several Viterbi Threshold Registers (Registers 29, 2A, 2B, 2C, 2D and 2E). For each Viterbi Threshold Register, bits 7 to 0 represent a normalization rate threshold – the average number of normalization occurring during sync periods. The sync period is controlled via Viterbi Sync Register (Register 2F). The puncture Rate and Viterbi initial configuration is in Address 30, 31. The automatic rate research is only done through the enabled rates (see the corresponding bit set in the Puncture register). In DSS, it is recommended that you disable puncture rates 3/4, 5/6 and 7/8 in order to save time in the synchronization process. The Viterbi decoder sync search can control using the Puncture register.

#### 3.4.4 Synchronization

In DVB-S, the packet length after inner decoding is 204. The sync word is the first byte of each packet. Its value is Hex 47, but this value is complemented every 8 packets. In DSS, the packet length is 147 and the sync word is Hex 1D.

An Up/Down Sync counter counts whenever a sync word is recognized with the correct timing and counts down during each missing sync word.

This counter is bounded by a programmable maximum - when this value is reached, the SYNC\_FLAG bit ("locked") is set in the SYNC02 register. When the event counter counts down to until 0, this flag is reset.

#### 3.4.5 Error monitoring

A 16-bit counter, ERRCNT, allows the counting of errors at different levels. ERRCNT is fed either by:

- the input QPSK bit errors (that are corrected by the Viterbi decoder), or,

- the bit, or,

- the byte error (it will be corrected by the Reed-Solomon decoder)

- the packet error (It is uncorrectable and lead to a pulse at the ERROR output)

The content of ERRCNT may be transferred to the read only registers ERR\_CNT\_L (LSB) and ERR-CNT\_H (MSB). Two functional modes are proposed, depending on a control register bit:

- 1. ERR\_DISP = 0. The uncorrectable block flag ERROR that error count is not incremented.

- 2. ERR\_DISP = 1. The uncorrectable block flag ERROR that error is counted as 27 erroneous bits (It has nine erroneous bytes with three corrupted bits per byte).

## 3.4.6 Convolutional deinterleaver

In DVB-S, the Convolutional deinterleaver is  $17 \times 12$ . The periodicity of 204 bytes per sync byte is retained. In DSS, the Convolutional deinterleaver is  $146 \times 13$ , and there is also a periodicity of 147 bytes per sync byte. The deinterleaver may be bypassed.

#### 3.4.7 Reed-Solomon decoder and descrambler

The input blocks are 204-byte long with 16 parity bytes in DVB-S. The sync byte is the first byte of the block. Up to 8 byte errors may be fixed.

$$g(\chi) = (\chi - \alpha^{0}) (\chi - \alpha^{1}) (...) (\chi - \alpha^{15})$$

Over the Calois Field generated by:

Over the Galois Field generated by:  $\alpha^{8} + \alpha^{4} + \alpha^{3} + \alpha^{2} + 1=0$

Energy dispersal descrambler and output energy dispersal descrambler generator:

$$\chi^{15} + \chi^{14} +$$

The polynomial is initialized every eight blocks with the sequence 100101010000000. The sync words are unscrambled and the scrambler is reset every 8 packets.

The output interface may be forced into high impedance mode by setting MPEG\_OEN =0 in the Address 39. Doing this affects the DATA [7:0], BYTE\_CLOCK, SYNC, VALID and ERROR pins. The output stream is either parallel (byte stream) or serial (bit stream) depending on bit 1 of Address 39.

## 3.4.8 Spectrum Inverse of Code Rate 5/6

In case of Code Rate 5/6, because of its character, regardless of condition of spectrum it can be locked. Rest of the code rates except 5/6, if Viterbi is locked, byte becomes sync but in case of code rate 5/6, even if Viterbi is locked there are chances byte does not become sync. Therefore, in case of Code Rate 5/6, it should be processed using S/W.

Processing procedure is like below.

- 1. When the rest is locked except byte sync, code rate check 5/6.

- Code rate monitoring : Addr [0x32], Bit position[0-2]

- 2. When Code Rate is 5/6, Check inverse spectrum status.

- Spectrum inverse monitoring : Addr [0x32], Bit poisition[3]

- 3. Inverse inversion spectrum.

- Spectrum inverse setting : Addr [0x31], Bit poisition[3], Set 1

Addr [0x31], Bit poisition[4], Set 1 or 0

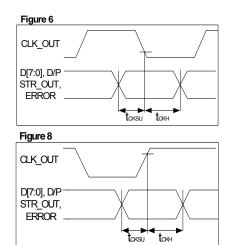

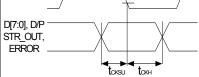

#### 3.4.9.1 Parallel output interface

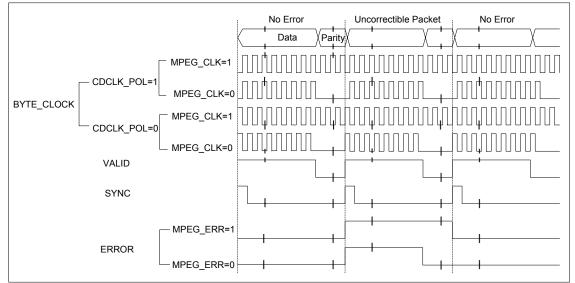

A schematic diagram of the parallel output interface is shown in Figure 4. The parallel output format is compliant with the DVB-S common interface protocol.

When the byte sync is not found (SYNC\_FLAG = 0 in the SYNC02 register), VALID (corresponding to the MiVAL signal of the DVB-S common interface standard) remains at a low level.

BYTE\_CLOCK has a duty cycle between 40 and 60%. The VALID signal is generated depending on bit 2 of Address 39. The BYTE\_CLOCK, SYNC, VALID and ERROR signal polarity is controlled depending on contents in the Register 38.

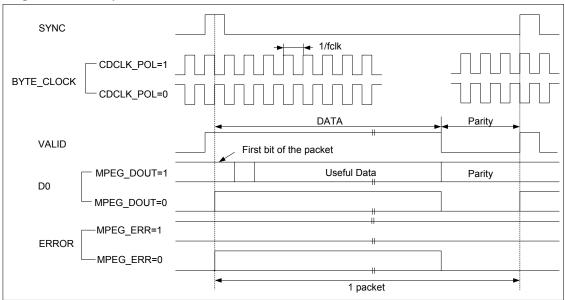

#### 3.4.9.2 Serial output interface

The serial output interface is shown in Figure5. The serial bit stream is available on D7, where MSB is first to reconstruct the original order. If MPEG\_DOUT = 1, then the parity bits are output (Register 39). If MPEG\_DOUT =0, the data is null during the parity time slots.

SYNC is only high during the first bit of each packet, instead of during the first byte in Parallel mode. ERROR has the same function as in parallel mode.

BYTE\_CLOCK is the serial bit clock; it is same the master clock, fclk. All of the outputs are synchronous of the same master clock edge. D7, SYNC, VALID and ERROR may be properly sampled externally by the rising edge of BYTE\_CLOCK.

The first bit detected in a valid packet may be decoded if it is found on the appropriate edge of BYTE\_CLOCK, where SYNC = 1, ERROR = 0, VALID = 1. The following bits only require the assertion of VALID (while VALID = 1,). Outputs D0 to D6 remain at low level in serial mode.

#### Figure4 : Parallel output interface

#### Figure5 : Serial output interface

#### Table 0

|          | Bit1 of 0x39 | Bit4 of 0x02 | MPEG Data   | MPEG Clock |

|----------|--------------|--------------|-------------|------------|

|          | SER_PAR      | SER_SEL_MODE | IVIFEG Dala |            |

| Parallel | 0            | 1            | DATA [7:0]  | BYTE_CLK   |

| Serial   | 1            | 1            | DATA[7]     | BYTE_CLK   |

# 3.4.9.3 MPEG Clock Control

- Through Register Setting, S5H1420 can control MPEG CLOCK to MCU.

| STB MCU                 | 60M                  | Hz                  | 81MHz                |                     |  |

|-------------------------|----------------------|---------------------|----------------------|---------------------|--|

| Symbol Rate             | Symbol Rate<br>>= 25 | Symbol Rate<br>< 25 | Symbol Rate<br>>= 25 | Symbol Rate<br>< 25 |  |

| S5H1420 Master<br>Clock | 59MHz                | 88MHz               | 80MHz                | 88MHz               |  |

| Sampling                | 1                    | 2                   | 1                    | 2                   |  |

- Control register, 3-bit, uses Address 0x22 (MPEG\_CLK\_INTL [2:0])

- If Control registers changes, Some blocks will be reset automatically.

- In case, Auto reset does not work, these blocks' reset can be done manually.

- MPEC IF Clock is made by Control Register and the Rules are as follows

- Tmp = (fMCLK/fSR)\*(1/(2\*CR)), fMCLK : System Clock Frequency,fSR : Symbol Rate, CR : Code Rate

| Control<br>Register | MPEG                   | MPEG Clock            | Pango                                                                   | Divide | -      | 88 MHz<br>ock (MHz) |

|---------------------|------------------------|-----------------------|-------------------------------------------------------------------------|--------|--------|---------------------|

| (0x22)              | Clock(Parallel)        | (Serial)              | Range                                                                   | Divide | Serial | Parallel            |

| 0                   | F <sub>MCLK</sub> /8   | F <sub>MCLK</sub>     | 1 <tmp≤2< td=""><td>1</td><td>88</td><td>11</td></tmp≤2<>               | 1      | 88     | 11                  |

| 1                   | F <sub>MCLK</sub> /16  | F <sub>MCLK</sub> /2  | 2 <tmp≤5< td=""><td>2</td><td>44</td><td>5.5</td></tmp≤5<>              | 2      | 44     | 5.5                 |

| 2                   | F <sub>MCLK</sub> /32  | F <sub>MCLK</sub> /4  | 5 <tmp≤9< td=""><td>3</td><td>22</td><td>2.75</td></tmp≤9<>             | 3      | 22     | 2.75                |

| 3                   | F <sub>MCLK</sub> /64  | F <sub>MCLK</sub> /8  | 9 <tmp≤13< td=""><td>4</td><td>11</td><td>1.375</td></tmp≤13<>          | 4      | 11     | 1.375               |

| 4                   | F <sub>MCLK</sub> /96  | F <sub>MCLK</sub> /12 | 13 <tmp≤17< td=""><td>5</td><td>7.3333</td><td>0.9166625</td></tmp≤17<> | 5      | 7.3333 | 0.9166625           |

| 5                   | F <sub>MCLK</sub> /128 | F <sub>MCLK</sub> /16 | 17 <tmp≤25< td=""><td>6</td><td>5.5</td><td>0.6875</td></tmp≤25<>       | 6      | 5.5    | 0.6875              |

| 6                   | F <sub>MCLK</sub> /192 | F <sub>MCLK</sub> /24 | 25 <tmp≤33< td=""><td>7</td><td>3.6666</td><td>0.458325</td></tmp≤33<>  | 7      | 3.6666 | 0.458325            |

| 7                   | F <sub>MCLK</sub> /256 | F <sub>MCLK</sub> /32 | 33 <tmp< td=""><td>8</td><td>2.75</td><td>0.34375</td></tmp<>           | 8      | 2.75   | 0.34375             |

Example1) System Clock Frequency = 88MHZ, Symbol Rate : 44MSps

| Code Rate | Tmp Value | Setting Control Register Value |

|-----------|-----------|--------------------------------|

| 1/2       | 2         | 1                              |

| 2/3       | 1.5       | 0                              |

| 3/4       | 1.333     | 0                              |

| 5/6       | 1.2       | 0                              |

| 6/7       | 1.166     | 0                              |

| 7/8       | 1.142     | 0                              |

# 3.5 Front end interfaces

# 3.5.1 I<sup>2</sup>C interface

The standard I<sup>2</sup>C protocol is used whereby the first byte is Hex A0 for a write operation, or Hex A1 for a read operation.

## 3.5.2 Write operation

The byte sequence is as follows:

- the first byte gives the device Address plus the direction bit (R/W = 0).

- the second byte contains the internal Address of the first register to be accessed.

- the next byte is written in the internal register. Following bytes (if any) are written in successive internal registers.

- the transfer lasts until stop conditions are encountered.

- the S5H1420 acknowledges every byte transfer.

# 3.5.3 Read operation

The Address of the first register to read is programmed in a write operation without data, and terminated by the stop condition. Then, another start is followed by the device Address and R/W= 1. All following bytes are now data to be read at successive positions starting from the initial Address. Figure 2 shows the  $l^2C$  Normal Mode Write and Read Registers.

## Figure 2: I<sup>2</sup>C Read and Write operations in Mode

Write register 0 to 3 with AA, BB, CC, and DD

| US |    | JB% | E<br>TF | <br>"\$∎≣ | F<br>T | \$<br>8 UB | " Ş | \$BBJ ## | 15 | %BUB\$\$ | \$<br><b>€</b> B B%% | "\$ | 4JQ |

|----|----|-----|---------|-----------|--------|------------|-----|----------|----|----------|----------------------|-----|-----|

|    | EC | 158 | olo     |           |        |            |     |          |    |          |                      |     |     |

Read register 2 and 3

| UA 1        | BSU | ¥JW DF 🏛     | ΤT              | 8 JF % | ĸş, | <b>J</b> F 1 | EUS 'SEE | Ŧ    | ış, | U4 PQ | ] |    |     |      |

|-------------|-----|--------------|-----------------|--------|-----|--------------|----------|------|-----|-------|---|----|-----|------|

| <b>B</b> ⁄4 | IJ  | ¥JW DF<br>⊞8 | <b>۳</b><br>الا | TT     | 57  | BB:          | Œ        | \$\$ | 15  | BB:   | æ | 88 | 157 | U1 Q |

## 3.5.4 Identification register

The Identification Register (at Address Hex 00) gives the release number of the circuit. The content of this register at reset is presently (Hex02)

## 3.5.5 Sampling frequency

The S5H1420 converts the analog inputs into digital 6 bit I and Q flow. The sampling frequency is  $f_{c/k}$  which is derived from an external reference described in Section 3.5.6 'Clock generation'. The maximum value of fclk is 90 MHz.

The sampling causes the repetition of the input spectrum at each integer multiple of  $f_{c/k}$  One has to ensure that no frequency component is folded in the useful signal bandwidth of  $f_{sym}$  (1+  $\alpha$ )/2 where  $f_{sym}$  is the symbol frequency, and  $\alpha$  is the roll-off value.

## 3.5.6 Clock generation

An integrated PLL is the circuit synchronizing an output signal (generated by a VCO with a reference signal in frequency as well as in phase. In this application, it includes the following basic blocks. The phase frequency detector to detect the phase difference between the reference frequency and the output frequency (after division) and to control the charge pumps voltage. Register setting can program the desired frequency.

$f_{out} = (m \times f_{in})/(p \times s)$  $f_{in}$ : input frequency, m=M+8, p=P+2, s=2^S M: Register 03, P: Register 04 [5:0], S: Register 04[7:6]

# 3.5.7 I<sup>2</sup>C bus repeater

In low symbol rate applications, signal pollution generated by the SDA/SCL lines of the  $l^2C$  bus may dramatically worsen tuner phase noise. In order to avoid this problem, the S5H1420 offers an I2C bus repeater so that the RFSDA and RFSCL are active only when necessary. Both RFSDA and RFSCL pins are set high at reset. When the microprocessor writes a 1 into register bit I2C\_RPT, the next  $l^2C$  message on SDA and SCL is repeated on the RFSDA and RFSCL pins respectively, until stop conditions are detected.

To write to the tuner, the external microprocessor must, for each tuner message, perform the following: Program 1 in I2C RPT.

■ Send the message to the tuner.

Any size of byte transfers is allowed, regardless of the Address, until the stop conditions are detected. Transfers are fully bi-directional. The I2C\_RPT bit is automatically reset at the stop condition. The I<sup>2</sup>C repeater register in Address Hex 02 controls configuration.

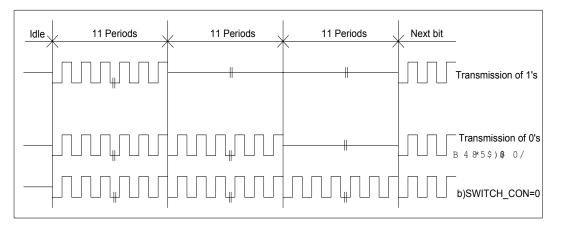

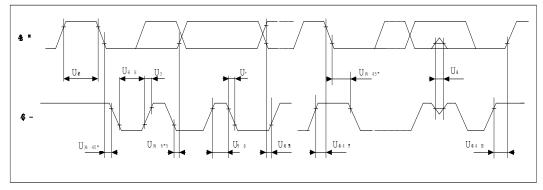

## 3.5.9 DiSEqC interface

This interface allows for the simplification of real time processing of the dialog from microprocessor to LNB. It includes register set (8 bytes) that is filled by the microprocessor via the I<sup>2</sup>C bus, and then transmitted by modulating to 22 kHz clock. The S5H1420 support DiSEqC2.0 for bi-directional interface between microprocessor to LNB and can change the tone frequency by register setting.

## < Transmission >

The S5H1420 have three modes for DiSEqC Interface.

Continuous Mode: The S5H1420 generates continuous tone signal until the mode changes.

■ Tone Burst Mode: For the "Modulated Tone Burst", only one byte (with value Hex FF) and parity bit 1 is sent. As a result, the output signal is 9 bursts of 0.5ms, separated by 8 intervals of 1ms.

For the "Unmodulated Tone Burst" only one byte (with value Hex 00) is sent. The parity bit is still 1, and as a result, the signal is a continuous train of 12.5ms.

■ DiSEqC Mode: DiSEqC is a command-based protocol used to control multiple LNBs in a cascaded network configuration. The S5H1420 complies with DiSEqC2.0. Figure illustrates a typical application of the DiSEqC mode.

## < Receive >

The S5H1420 receives the data from LNBs using DiSEqC pin. In order to receive the data from LNBs should set the register RCV\_EN to 1. The received data is stored to register set.

Two control signals are available on the I<sup>2</sup>C bus:

DiS\_RDY (Transfer Ready/Finish) and DiS\_LENGTH (Message Length).

A typical byte transfer loop, as seen from the microprocessor, may be the following:

While (there is data to transfer)

1 Read the DiS\_RDY signals

2 If DiS\_RDY = $\overline{0}$ , Write byte to transfer in the register set.

3 Set the DiS\_LENGTH.

4 Set the DiS\_RDY =1.

Note, for the above transfer loop, the following:

- At the beginning, the register set is empty (DiS\_RDY =0). This is the idle state.

- As soon as set the DiS\_RDY =1, the transfer will begin.

- After the last transmitted byte, the interface will go into the idle state.

## Figure3: Schematic showing Bit Transmission

Table1

| LNB_CON | SWITCH_CON | Register set | Output                 |

|---------|------------|--------------|------------------------|

| 00      | Х          | Empty        | Continuous tone        |

| 01      | 0          | DATA=00      | Unmodulated tone burst |

| 01      | 1          | DATA=FFor00  | Module tone burst      |

| 10      | Х          | Note 1       | DiSEpC signal          |

| 11      | Х          | XX           | Reserved               |

Note: 1 Byte to transfer in DiSEqC mode.

2 In Mode LNB\_CON (1:0) =10, the DiSEqC pin return to high 2 mode once the transmission is completed.

# **4. REGISTER LIST**

|                        |                              |                                 | -                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |             |                           |                                 |                     |              |                |  |  |  |  |  |  |

|------------------------|------------------------------|---------------------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|---------------------------|---------------------------------|---------------------|--------------|----------------|--|--|--|--|--|--|

| ‡                      | Add                          | Name                            | bit7                 | bit6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | bit5        | bit4                      | bit3                            | bit2                | bit1         | bit0           |  |  |  |  |  |  |

| ID                     | 0x00                         | ID01                            |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |             |                           | 11420_ID                        |                     |              |                |  |  |  |  |  |  |

| SYSTEM                 | 0x01                         | CON_0                           |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |             | 0                         | SOFT_RST                        | 0                   | 0            | DSS_DVB        |  |  |  |  |  |  |

|                        | 0x02                         | CON_1                           |                      | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0           | SER_SEL                   | 0                               | 0                   | PWR_DN       | I2C_RPT        |  |  |  |  |  |  |

| PLL                    | 0x03                         | PLL01                           |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |             |                           | М                               |                     |              |                |  |  |  |  |  |  |

|                        | 0x04                         | PLL02                           |                      | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |             |                           | F                               |                     |              |                |  |  |  |  |  |  |

|                        | 0X05                         | QPSK01                          | KICK_EN              | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1           | DC_EN                     | 1                               | 1                   | MODE         | Q_START        |  |  |  |  |  |  |

|                        | 0X06                         | QPSK02                          | 1                    | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0           | 1                         | DUMP_ACC                        |                     | DC_WIN       |                |  |  |  |  |  |  |

|                        | 0x07                         | Pre01                           | INV_PULSE            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |             |                           |                                 |                     |              |                |  |  |  |  |  |  |

|                        | 0x08                         | Post01                          | 0                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |             |                           |                                 |                     |              |                |  |  |  |  |  |  |

|                        | 0x09                         | Loop01                          |                      | WT_TNCO         WT_PNCO         1         1         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         < |             |                           |                                 |                     |              |                |  |  |  |  |  |  |

|                        | 0x0A<br>0x0B                 | Loop02<br>Loop03                | LOOP_001             | LOOP_OUT KICK_VAL KICK_MUL<br>IGA PLF PGA PLF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |             |                           |                                 |                     |              |                |  |  |  |  |  |  |

|                        | 0x0C                         | Loop03                          |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | T PLF       |                           |                                 | PGA_<br>PGT         |              |                |  |  |  |  |  |  |

|                        | 0x00                         | Loop05                          |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | TLF         |                           |                                 | PG <sup>-</sup>     |              |                |  |  |  |  |  |  |

|                        | 0x0E                         | Pnco01                          |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |             | PNC                       | O0[31:24]                       |                     | ·            |                |  |  |  |  |  |  |

|                        | 0x0F                         | Pnco02                          |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |             |                           | O1[23:16]                       |                     |              |                |  |  |  |  |  |  |

| QPSK                   | 0X10                         | Pnco03                          |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |             |                           | O2[15:08]                       |                     |              |                |  |  |  |  |  |  |

|                        | 0X11                         | Tnco01                          |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |             | TNC                       | O0[31:24]                       |                     |              |                |  |  |  |  |  |  |

|                        | 0X12                         | Tnco02                          |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |             |                           | O1[23:16]                       |                     |              |                |  |  |  |  |  |  |

|                        | 0X13                         | Tnco03                          |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |             | TNC                       | O2[15:08]                       |                     |              |                |  |  |  |  |  |  |

|                        | 0x14                         | Monitor01                       |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |             |                           |                                 | erved               | TLOCK        | PLOCK          |  |  |  |  |  |  |

|                        | 0x15                         | Monitor02                       |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |             |                           |                                 |                     |              |                |  |  |  |  |  |  |

|                        | 0x16                         | Monitor03                       |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |             |                           |                                 |                     |              |                |  |  |  |  |  |  |

|                        | 0x17<br>0x18                 | Monitor04<br>Monitor05          |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |             |                           | <u>I_LEVEL</u><br>Q_LEVEL       |                     |              |                |  |  |  |  |  |  |