ISSUE 8

TRIBUTARY UNIT PAYLOAD PROCESSOR

## **PM5361**

## **TUPP**

# SONET/SDH TRIBUTARY UNIT PAYLOAD PROCESSOR

**DATA SHEET**

**ISSUE 8: JULY 1998**

ISSUE 8

TRIBUTARY UNIT PAYLOAD PROCESSOR

### **PUBLIC REVISION HISTORY**

| Issue No. | Issue Date | Details of Change                                        |

|-----------|------------|----------------------------------------------------------|

| 8         | July 1998  | Data Sheet Reformatted — No Change in Technical Content. |

|           |            | Generated R8 data sheet from PMC-920102, issue R10.      |

Downloaded from **Elcodis.com** electronic components distributor

ISSUE 8

#### TRIBUTARY UNIT PAYLOAD PROCESSOR

#### **CONTENTS**

| 1 | FEATURES   |              |                              | 1  |  |  |  |

|---|------------|--------------|------------------------------|----|--|--|--|

| 2 | APPLICATIO | APPLICATIONS |                              |    |  |  |  |

| 3 | REFERENC   | ES           |                              | 4  |  |  |  |

| 4 | APPLICATIO | ON EXAMPLE.  |                              | 5  |  |  |  |

| 5 | BLOCK DIA  | GRAM         |                              | 6  |  |  |  |

| 6 | DESCRIPTI  | ON           |                              | 8  |  |  |  |

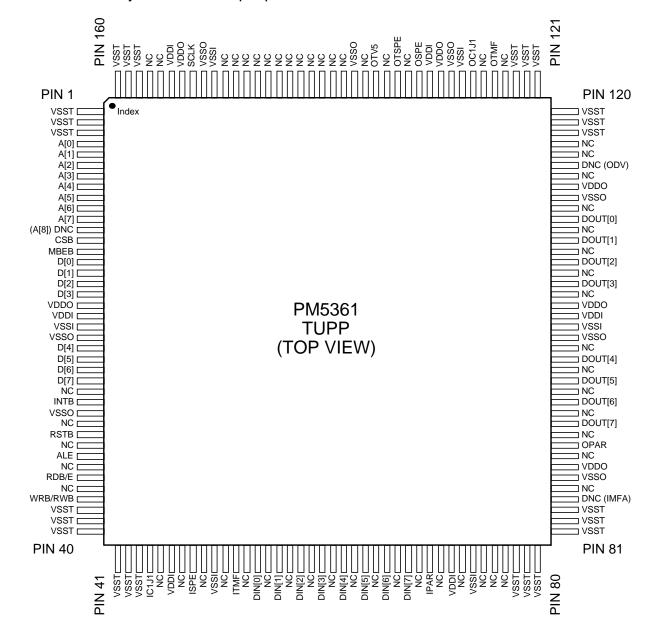

| 7 | PIN DIAGRA | ΑM           |                              | 10 |  |  |  |

| 8 | PIN DESCR  | IPTION       |                              | 11 |  |  |  |

| 9 | FUNCTION   | AL DESCRIPTI | ON                           | 22 |  |  |  |

|   | 9.1        | INPUT        | BUS DEMULTIPLEXER            | 22 |  |  |  |

|   | 9.2        | OUTP         | UT BUS MULTIPLEXER           | 22 |  |  |  |

|   | 9.3        | TRIBU        | TARY PAYLOAD PROCESSOR       | 23 |  |  |  |

|   |            | 9.3.1        | CLOCK GENERATOR              | 23 |  |  |  |

|   |            | 9.3.2        | INCOMING TIMING GENERATOR    | 23 |  |  |  |

|   |            | 9.3.3        | INCOMING MULTIFRAME DETECTOR | 24 |  |  |  |

|   |            | 9.3.4        | POINTER INTERPRETER          | 24 |  |  |  |

|   |            | 9.3.5        | PAYLOAD BUFFER               | 24 |  |  |  |

|   |            | 9.3.6        | OUTGOING TIMING GENERATOR    | 25 |  |  |  |

|   |            | 9.3.7        | POINTER GENERATOR            | 25 |  |  |  |

|   |            | 9.3.8        | COMMON BUS INTERFACE         | 26 |  |  |  |

|   | 9.4        | MICRO        | DPROCESSOR INTERFACE         | 26 |  |  |  |

|   | 9.5        | REGIS        | TER MEMORY MAP               | 26 |  |  |  |

| PMC-920526 |               | ISSUE 8                            | TRIBUTARY UNIT PAYLOAD PROCESSOR |

|------------|---------------|------------------------------------|----------------------------------|

| 10         | NORMAL MODE   | REGISTER DESCRIPTION               | 29                               |

| 11         | TEST FEATURES | S DESCRIPTION                      | 64                               |

|            | 11.1          | I/O TEST MODE                      | 67                               |

| 12         | OPERATION     |                                    | 68                               |

|            | 12.1          | CONFIGURATION OPTIONS              | 68                               |

|            | 12.2          | STS-1 MODE                         | 70                               |

|            | 12.3          | AU3 MODE                           | 70                               |

|            | 12.4          | AU4 MODE                           | 71                               |

| 13         | FUNCTIONAL TI | MING                               | 74                               |

| 14         | ABSOLUTE MAX  | IMUM RATINGS                       | 82                               |

| 15         | D.C. CHARACTE | RISTICS                            | 83                               |

| 16         | MICROPROCES   | SOR INTERFACE TIMING CHARACTERISTI | CS85                             |

| 17         | TUPP TIMING C | HARACTERISTICS                     | 92                               |

| 18         | ORDERING AND  | THERMAL INFORMATION                | 96                               |

| 19         | MECHANICAL IN | IFORMATION                         | 97                               |

ISSUE 8

TRIBUTARY UNIT PAYLOAD PROCESSOR

#### **LIST OF REGISTERS**

| REGISTER 00H: MASTER INCOMING CONFIGURATION                                                  | 30 |

|----------------------------------------------------------------------------------------------|----|

| REGISTER 01H: MASTER OUTGOING CONFIGURATION                                                  | 32 |

| REGISTER 02H: INPUT SIGNAL ACTIVITY MONITOR                                                  | 34 |

| REGISTER 03H: MASTER RESET AND IDENTITY                                                      | 36 |

| REGISTER 04H: TRIBUTARY PAYLOAD PROCESSOR #1 CONFIGURATION                                   | 37 |

| REGISTER 05H: TRIBUTARY PAYLOAD PROCESSOR #2 CONFIGURATION                                   | 39 |

| REGISTER 06H: TRIBUTARY PAYLOAD PROCESSOR #3 CONFIGURATION                                   | 41 |

| REGISTER 07H: TPP AND H4 OOF INTERRUPT ENABLE                                                | 43 |

| REGISTER 08H: TPP INTERRUPT STATUS AND H4 OOF STATUS                                         | 45 |

| REGISTER 09H: PARITY ERROR AND H4 OOF INTERRUPT                                              | 47 |

| REGISTER 20H, 40H, 60H: TU3, OR TU #1 IN TUG2 #1, CONFIGURATION AND STATUS                   | 49 |

| REGISTER 21H-26H, 41H-46H, 61H-66H: TU #1 IN TUG2 #2 TO TUG2 #7, CONFIGURATION AND STATUS 51 |    |

| REGISTER 27H, 47H, 67H: TU3 OR TU #1 IN TUG2 #1 TO TUG2 #7, LOP INTERRUPT                    | 53 |

| REGISTER 28H-2EH, 48H-4EH, 68H-6EH: TU #2 IN TUG2 #1 TO TUG2 #7, CONFIGURATION AND STATUS 55 |    |

| REGISTER 2FH, 4FH, 6FH: TU #2 IN TUG2 #1 TO TUG2 #7                                          | 57 |

| REGISTER 30H-36H, 50H-56H, 70H-76H: TU #3 IN TUG2 #1 TO TUG2 #7, CONFIGURATION AND STATUS 58 |    |

| REGISTER 37H, 57H, 77H: TU #3 IN TUG2 #1 TO TUG2 #7, LOP INTERRUPT                           | 60 |

| REGISTER 38H-3EH, 58H-5EH, 78H-7EH: TU #4 IN TUG2 #2 TO TUG2 #7, CONFIGURATION AND STATUS 61 |    |

| REGISTER 3FH, 5FH, 7FH: TU #4 IN TUG2 #1 TO TUG2 #7, LOP INTERRUPT                           | 63 |

| REGISTER 80H: MASTER TEST                                                                    | 66 |

ISSUE 8

TRIBUTARY UNIT PAYLOAD PROCESSOR

#### **LIST OF FIGURES**

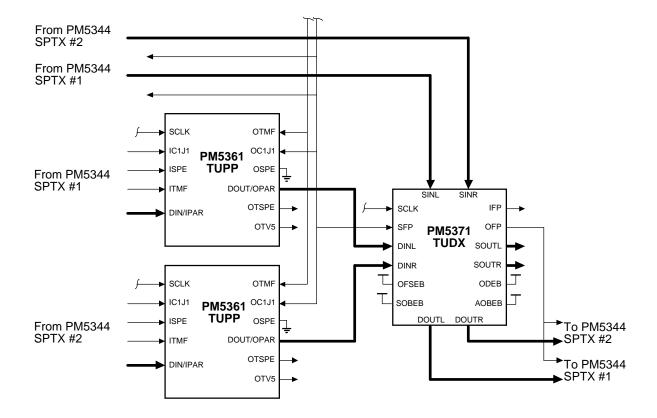

| FIGURE 1  | - SONE I/SDH TRIBUTARY CROSS-CONNECT APPLICATION            | 5  |

|-----------|-------------------------------------------------------------|----|

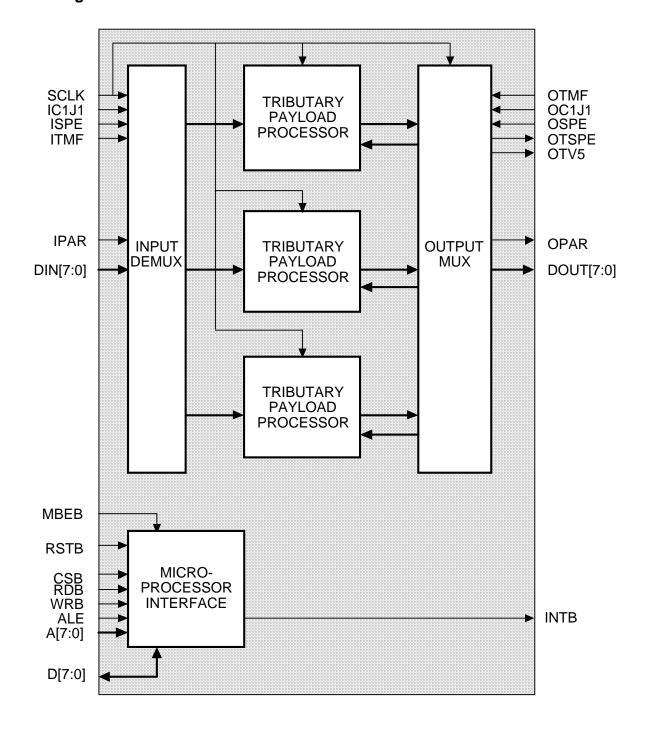

| FIGURE 2  | - OVERALL DEVICE                                            | 6  |

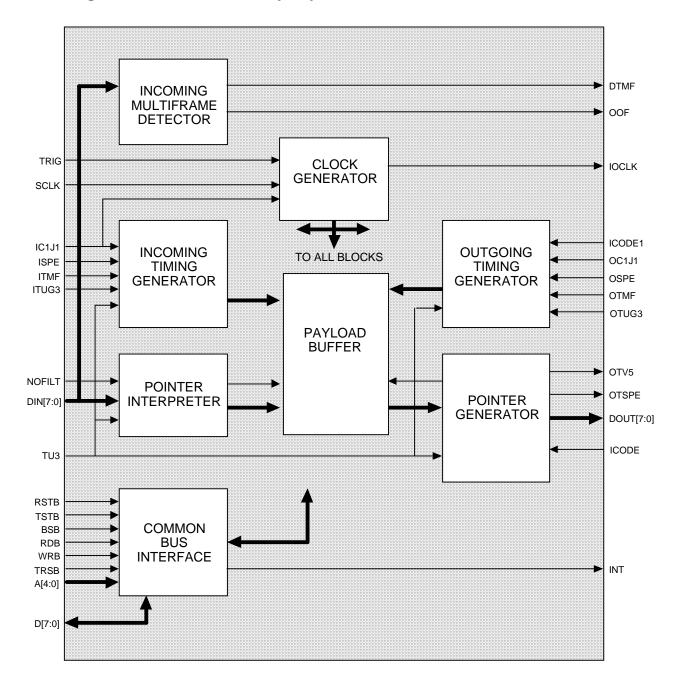

| FIGURE 3  | - EACH TRIBUTARY PAYLOAD PROCESSOR                          | 7  |

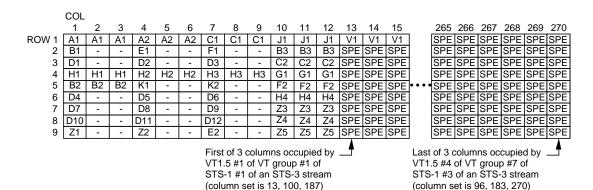

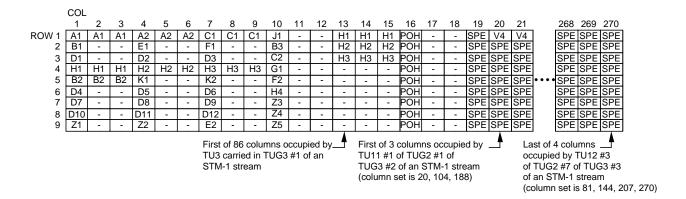

| FIGURE 4  | - SONET STS-3 CARRYING VT1.5 WITHIN STS-1                   | 70 |

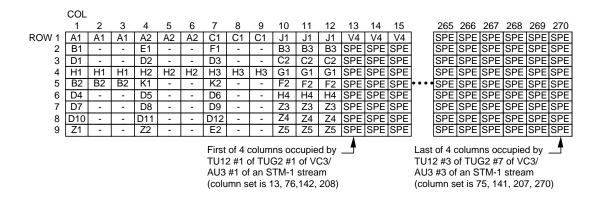

| FIGURE 5  | - SDH STM-1 CARRYING TU12 WITHIN VC3/AU3                    | 71 |

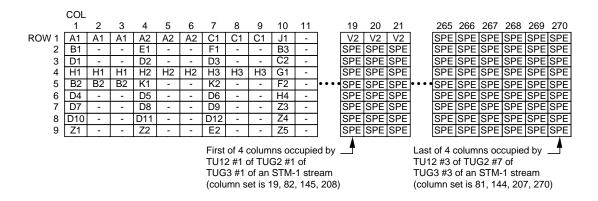

| FIGURE 6  | - SDH STM-1 CARRYING TU12 WITHIN TUG3/AU4                   | 71 |

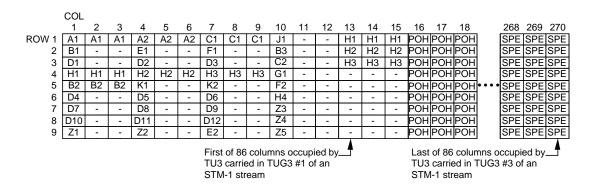

| FIGURE 7  | - SDH STM-1 CARRYING TU3 WITHIN TUG3                        | 72 |

| FIGURE 8  | - SDH STM-1 CARRYING MIX OF TU11, TU12, TU3 WITHIN TUG3/AU4 | 73 |

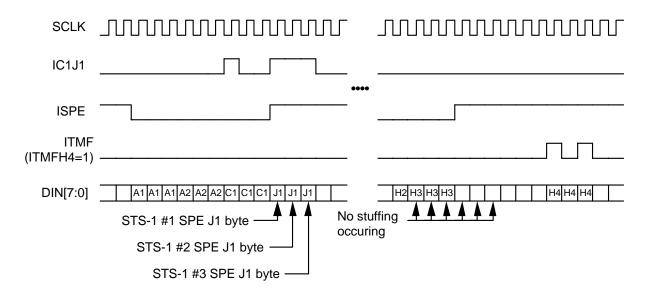

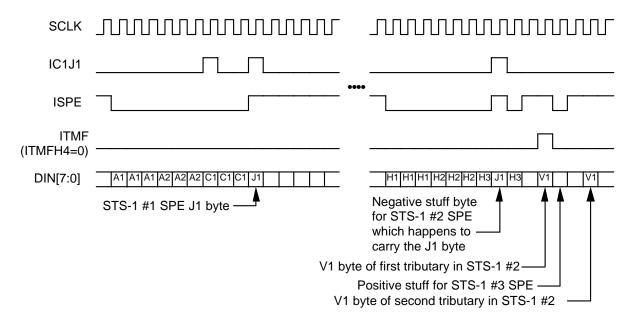

| FIGURE 9  | - INPUT BUS TIMING - SIMPLE STS-1/AU3 CASE                  | 74 |

| FIGURE 10 | - INPUT BUS TIMING - COMPLEX STS-1 / AU3 CASE               | 75 |

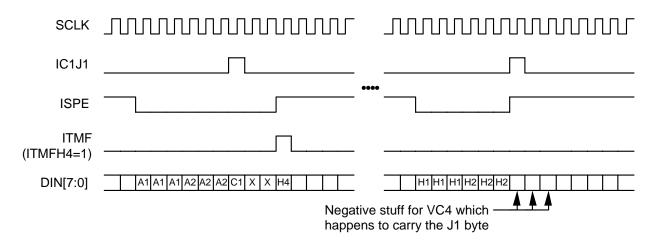

| FIGURE 11 | - INPUT BUS TIMING - AU4 CASE                               | 76 |

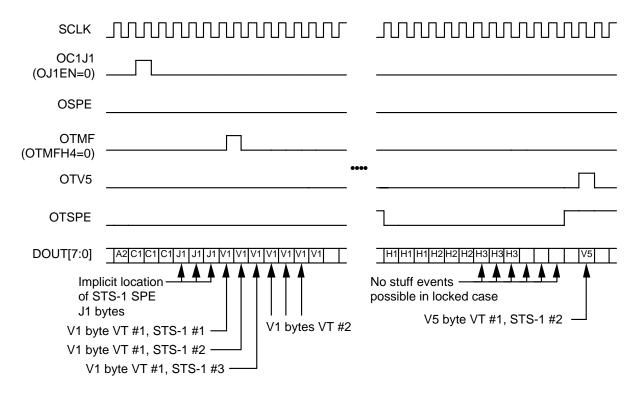

| FIGURE 12 | - OUTPUT BUS TIMING - LOCKED STS-1 SPES / AU3 VCS CASE      | 77 |

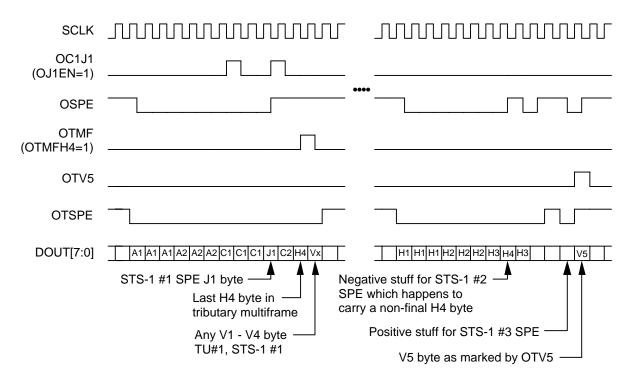

| FIGURE 13 | - OUTPUT BUS TIMING - FLOATING STS-1 SPES / AU3 VCS CASE    | 78 |

| FIGURE 14 | - OUTPUT BUS TIMING - LOCKED AU4 VC CASE                    | 79 |

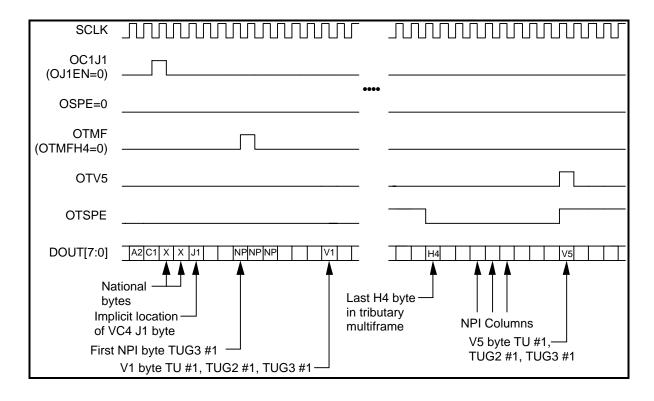

| FIGURE 15 | - OUTPUT BUS TIMING - FLOATING AU4 VC CASE                  | 80 |

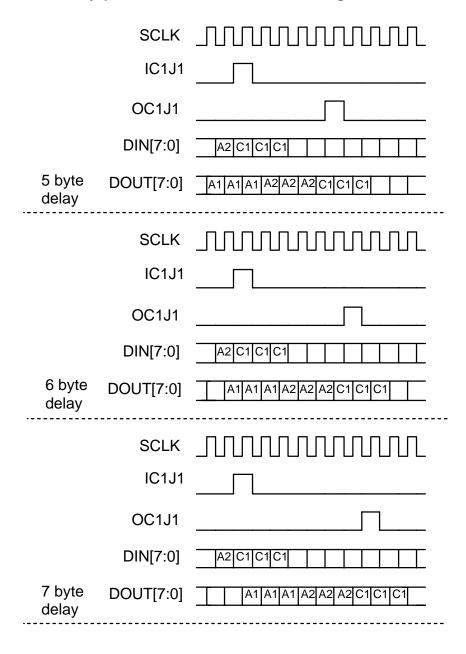

| FIGURE 16 | - BY-PASSED MODE FUNCTIONAL TIMING                          | 81 |

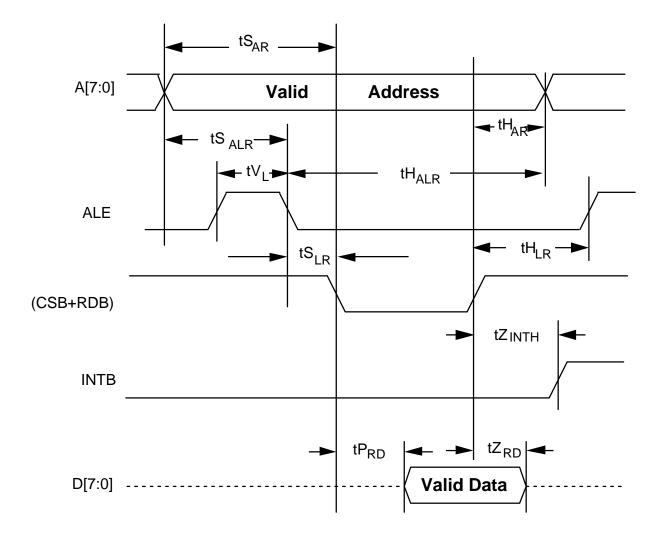

| FIGURE 17 | - MICROPROCESSOR INTERFACE READ TIMING (INTEL MODE)         | 86 |

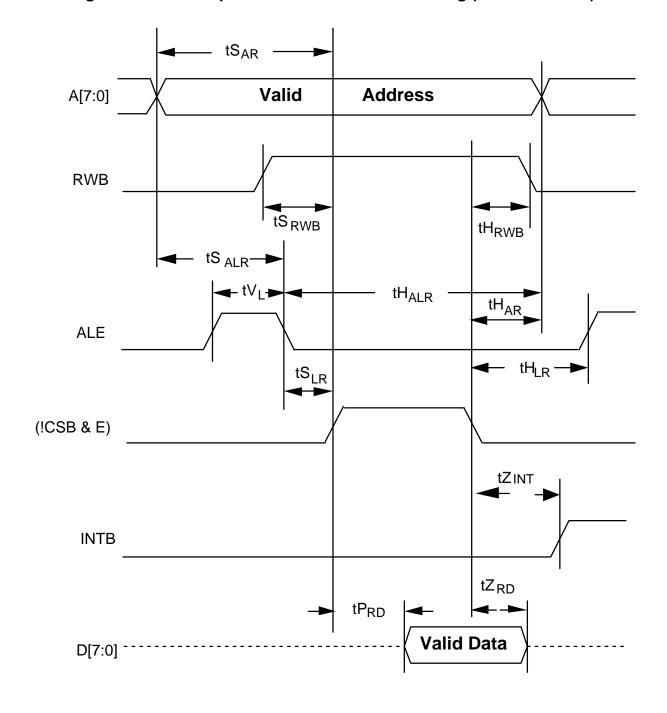

| FIGURE 18 | - MICROPROCESSOR INTERFACE READ TIMING (MOTOROLA MODE)      | 87 |

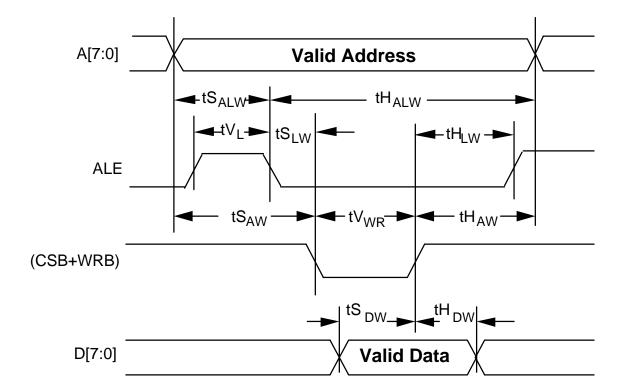

| FIGURE 19 | - MICROPROCESSOR INTERFACE WRITE TIMING (INTEL MODE)        | 89 |

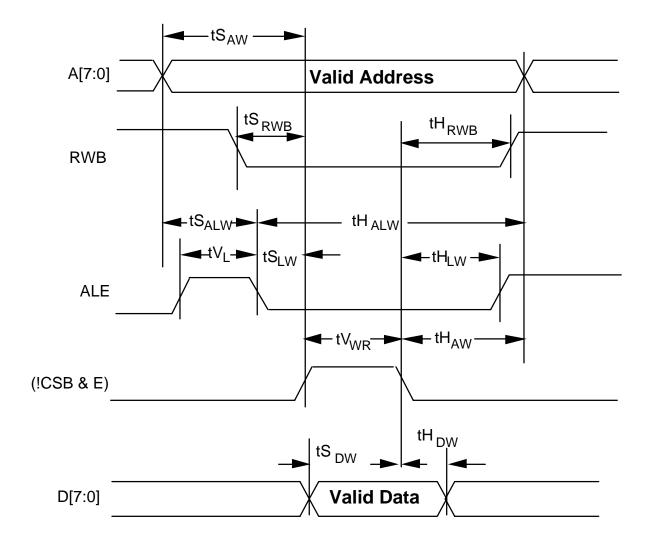

| FIGURE 20 | - MICROPROCESSOR INTERFACE WRITE TIMING (MOTOROLA MODE)     | 90 |

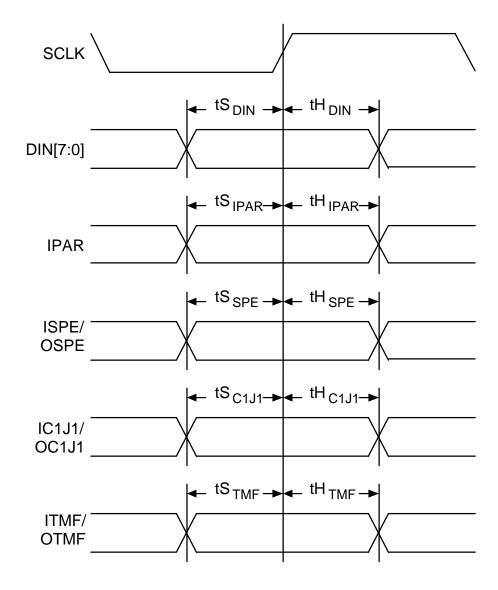

| FIGURE 21 | - INPUT TIMING                                              | 93 |

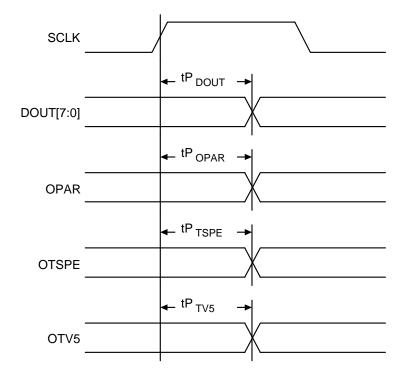

| FIGURE 22 | - OUTPUT TIMING                                             | 94 |

ISSUE 8

TRIBUTARY UNIT PAYLOAD PROCESSOR

#### **LIST OF TABLES**

| IABLE 1  | - TEST MODE REGISTER MEMORY MAP                                | 64 |

|----------|----------------------------------------------------------------|----|

| TABLE 2  | - I/O TEST MODE — INPUT READ REGISTER DESCRIPTION              | 67 |

| TABLE 3  | - I/O TEST MODE — OUTPUT WRITE REGISTER DESCRIPTION            | 67 |

| TABLE 4  | - D.C. CHARACTERISTICS                                         | 83 |

| TABLE 5  | - MICROPROCESSOR INTERFACE READ ACCESS (FIGURE 17, FIGURE 18)  | 85 |

| TABLE 6  | - MICROPROCESSOR INTERFACE WRITE ACCESS (FIGURE 19, FIGURE 20) | 88 |

| TABLE 7  | - TUPP INPUT (FIGURE 21)                                       | 92 |

| TABLE 8  | - TUPP OUTPUT (FIGURE 22)                                      | 94 |

| TABLE 9  | - TUPP ORDERING INFORMATION                                    | 96 |

| TABLE 10 | - TUPP THERMAL INFORMATION                                     | 96 |

ISSUE 8

ISSUE 8

TRIBUTARY UNIT PAYLOAD PROCESSOR

#### 1 FEATURES

- Configurable, multi-channel, payload processor for alignment of SONET virtual tributaries (VTs) or SDH tributary units (TUs). Processes an STS-3 or STM-1 byte serial data stream.

- Transfers all incoming tributaries in the three STS-1 synchronous payload envelopes of an STS-3 byte serial stream to the three STS-1 synchronous payload envelopes of an outgoing STS-3 byte serial stream.

- Transfers all incoming tributaries in the single AU4 or three AU3 administrative units of an STM-1 byte serial stream to the single AU4 or three AU3 administrative units of an outgoing STM-1 byte serial stream.

- Compensates for pleisiochronous relationships between incoming and outgoing higher level (STS-1, AU4, AU3) synchronous payload envelope frame rates through processing of the lower level (VT6, VT3, VT2, VT1.5, TU3, TU2, TU12, or TU11) tributary pointers.

- Provides multiframe synchronization for ring closure at the headend node in a SONET/SDH ring.

- Provides independently configurable AU3/AU4 frame format on incoming and outgoing directions.

- Configurable to process any legal mix of tributaries such as VT1.5, VT2, VT3, VT6, TU11, TU12, TU2, or TU3. Each VT group or TUG2 can be configured to carry one of four tributary types. TUG2s can be multiplexed into VC3s or TUG3s. Each TUG3 can also be configured to carry a TU3.

- Optionally frames to the H4 byte in the path overhead to determine tributary multiframe boundaries. Internally generated H4 bytes with leading logic 1 bits are inserted into the outgoing administrative units.

- Verifies parity on the IC1J1 and ISPE signals and on the incoming data stream and generates parity on the outgoing data stream.

- Detects loss of pointer and re-acquisition for each tributary and optionally generates interrupts. Loss of pointer detection can optionally generate tributary path AIS.

ISSUE 8

- Allows insertion of all zeros or all ones tributary idle code with unequipped indication and valid pointer into any tributary.

- Allows insertion of tributary path AIS into any tributary.

- Operates in conjunction with the PM5323 TSPP Triple SONET/SDH Payload Processor and the PM5344 SONET/SDH Path Terminating Transceiver to align tributaries such that they can be switched by the PM5371 TUDX SONET/SDH Tributary Unit Cross-Connect.

- Operates from a single 19.44 MHz clock.

- Provides a generic 8-bit microprocessor bus interface for configuration, control, and status monitoring.

- Low power, +5 Volt, CMOS technology, TTL compatible inputs and outputs.

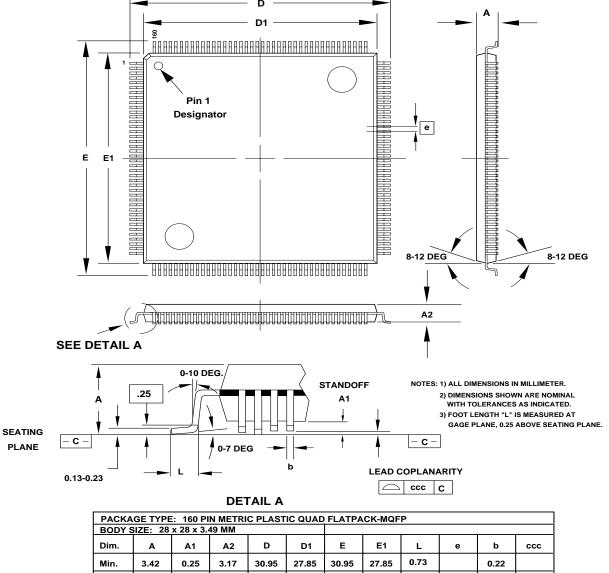

- 160 pin plastic quad flat pack (PQFP) package

ISSUE 8

TRIBUTARY UNIT PAYLOAD PROCESSOR

#### **APPLICATIONS**

- SONET and SDH Wideband Cross-Connects

- SONET and SDH Add-Drop and Terminal Multiplexers

ISSUE 8

TRIBUTARY UNIT PAYLOAD PROCESSOR

#### 3 REFERENCES

- 1. American National Standard for Telecommunications Digital Hierarchy Optical Interface Rates and Formats Specification, ANSI T1.105-1988.

- CCITT Blue Book, Recommendation G.708 "Network Node Interface For The Synchronous Digital Hierarchy", Volume III, Fascicle III.4, 1988.

- 3. CCITT Blue Book, Recommendation G.709 "Synchronous Multiplexing Structure", Volume III, Fascicle III.4, 1988.

- CCITT Study Group XVIII, Report R 33 "Recommendations Drafted By Working Party XVIII/7" (Digital Hierarchies) To Be Approved In 1990 Including Revised Draft Recommendations G.708 and G.709", June 1990.

- 5. Bell Communications Research SONET Transport Systems: Common Generic Criteria, TR-TSY-000253, Issue 2, December 1991.

ISSUE 8

TRIBUTARY UNIT PAYLOAD PROCESSOR

#### 4 APPLICATION EXAMPLE

The PM5361 TUPP is typically used as part of a SONET/SDH tributary cross-connect. TUPPs can be used to transfer the payloads of incoming tributaries into outgoing tributaries that are aligned to facilitate switching. A typical example is shown below.

This example shows the tributaries extracted from an STS-1 or AU3 path terminating device, such as the PM5344 SPTX SONET/SDH Path Terminating Transceiver, being routed through TUPPs so as to be aligned for cross-connection using the PM5371 TUDX SONET/SDH Tributary Unit Cross-Connect.

The TUPP (and SPTX) can be bypassed by switching through whole STS-1s or AU3s that are output by the PM5323 TSPP Triple SONET/SDH Payload Processor. Note that in this application example, the TUPPs are operating in locked output mode (i.e. their OJ1EN bits are low) to allow convenient interfacing to the TUDX chip.

Figure 1 - SONET/SDH Tributary Cross-Connect Application

ISSUE 8

TRIBUTARY UNIT PAYLOAD PROCESSOR

#### 5 BLOCK DIAGRAM

Figure 2 - Overall Device

ISSUE 8

Figure 3 - Each Tributary Payload Processor

ISSUE 8

TRIBUTARY UNIT PAYLOAD PROCESSOR

#### 6 **DESCRIPTION**

The PM5361 TUPP SONET/SDH Tributary Unit Payload Processor is a monolithic integrated circuit that implements a configurable, multi-channel, payload processor for alignment of SONET virtual tributaries (VTs) or SDH tributary units (TUs.)

When configured for SONET compatible operation, the TUPP transfers all tributaries in the three STS-1 synchronous payload envelopes of an incoming STS-3 byte serial stream to the three STS-1 synchronous payload envelopes of an outgoing STS-3 byte serial stream. Similarly, when configured for SDH compatible operation, the TUPP transfers all tributaries in the single AU4 or three AU3 administrative units of an incoming STM-1 byte serial stream to a single AU4 or three AU3 administrative units of an outgoing STM-1 byte serial stream. The TUPP compensates for pleisiochronous relationships between incoming and outgoing higher level (STS-1, AU4, AU3) synchronous payload envelope frame rates through processing of the lower level (VT6, VT3, VT2, VT1.5, TU3, TU2, TU12, TU11) tributary pointers.

The TUPP is configurable to process any legal mix of tributaries. Each VT group can be configured to carry any one of the four tributary types (VT1.5, VT2, VT3, or VT6) and each TUG2 can be configured to carry any one of three tributary types (TU11, TU12, or TU2). TUG2s can be multiplexed into a VC3 or a TUG3. Alternatively, each TUG3 can be configured to carry a TU3.

The TUPP operates in conjunction with the PM5323 TSPP Triple SONET/SDH Payload Processor and the PM5344 SONET/SDH Path Terminating Transceiver to align tributaries such that they can be switched by the PM5371 TUDX SONET/SDH Tributary Unit Cross-Connect.

The TUPP provides useful maintenance functions. They include detection of loss of pointer and pointer re-acquisition for each tributary, and optional generation of interrupts. The TUPP also allows insertion of tributary path AIS or tributary idle (unequipped). The TUPP can also insert inverted new data flag fields that can be used to diagnose downstream pointer processing elements.

No auxiliary high speed clocks are required as the TUPP operates from a single 19.44 MHz line rate clock. The TUPP is configured, controlled and monitored via a generic 8-bit microprocessor bus interface.

ISSUE 8

TRIBUTARY UNIT PAYLOAD PROCESSOR

The TUPP is implemented in low power, +5 Volt, CMOS technology. It has TTL compatible inputs and outputs and is packaged in a 160 pin PQFP package.

ISSUE 8

TRIBUTARY UNIT PAYLOAD PROCESSOR

#### 7 PIN DIAGRAM

The TUPP is packaged in an 160 pin PQFP package having a body size of 28 mm by 28 mm and a pin pitch of 0.65 mm.

ISSUE 8

TRIBUTARY UNIT PAYLOAD PROCESSOR

#### PIN DESCRIPTION

| Pin Name | Туре  | Pin<br>No. | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------|-------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCLK     | Input | 153        | The system clock (SCLK) provides timing for TUPP internal operation. SCLK is a 19.44 MHz, nominally 50% duty cycle clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| VCLK     |       |            | The test vector clock (VCLK) signal is used during TUPP production testing to verify internal functionality.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| IC1J1    | Input | 44         | The input C1/J1 frame pulse (IC1J1) identifies the transport envelope and synchronous payload envelope frame boundaries on the DIN[7:0] bus. IC1J1 is set high while ISPE is low to mark the first C1 byte of the transport envelope frame on the DIN[7:0] bus. IC1J1 is set high while ISPE is high to mark each of the J1 bytes of the synchronous payload envelope(s) on the DIN[7:0] bus. IC1J1 must be present at every occurrence of the first C1 and all J1 bytes. The TUPP will ignore a pulse on IC1J1 at the byte position of the V1 byte of the first tributary of each TUG3 or VC3. IC1J1 is sampled on the rising edge of SCLK. |

ISSUE 8

| Pin Name | Туре  | Pin<br>No. | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------|-------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ITMF     | Input | 52         | The active high incoming tributary multiframe (ITMF) signal identifies the first frame of the tributary multiframe for each STS-1 synchronous payload envelope, AU3, or AU4 administrative unit. ITMF is enabled by the setting the ITMFEN register bit high. When ITMFEN bit is low, the path overhead H4 byte is used to determine tributary multiframe boundaries. ITMF is selectable to pulse high during the V1 byte of the first tributary or during the H4 byte which indicates that the next frame is the first frame of the tributary multiframe. Selection between marking V1 or H4 bytes is controlled by the ITMFH4 register bit. Pulses on ITMF are only effective during the H4 or V1 byte positions, as appropriate. ITMF is ignored at other byte positions. The ITMFEN and ITMFH4 bits are located in the master incoming configuration register. ITMF is sampled on the rising edge of SCLK. |

| ISPE     | Input | 48         | The active high incoming synchronous payload envelope (ISPE) signal identifies the bytes within the transport envelope frame on the DIN[7:0] bus that carry the AU3 or AU4 virtual containers, and STS-1 synchronous payload envelopes. ISPE must be brought high to mark each such byte. ISPE is sampled on the rising edge of SCLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

ISSUE 8

| Pin Name | Туре  | Pin<br>No. | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------|-------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IPAR     | Input | 70         | The incoming stream parity (IPAR) signal carries the parity of the incoming signals. The parity calculation encompasses the IC1J1 signal, the ISPE signal and the DIN[7:0] bus. IC1J1 and ISPE can be included in the parity calculation by setting the INCIC1J1 and INCISPE register bits respectively high. Odd parity is selected by setting the IOP register bit high, and even parity is selected by setting the IOP bit low. The INCIC1J1, INCISPE and IOP bits are located in the master incoming configuration register. IPAR is sampled on the rising edge of SCLK. |

| OC1J1    | Input | 127        | The outgoing C1/J1 frame pulse (OC1J1) marks the transport envelope and synchronous payload envelope frame boundaries on the DOUT[7:0] bus. When the OJ1EN register bit is set low, OC1J1 pulses high to mark the first C1 byte of the transport envelope frame on the DOUT[7:0] bus. The position of the J1 bytes is implicit and fixed to the bytes immediately following the last C1 byte.                                                                                                                                                                                |

|          |       |            | When the OJ1EN register bit is set high, the OC1J1 signal pulses high while ISPE is low to mark the first C1 byte of the transport envelope frame on the DOUT[7:0] bus and pulses high while OSPE is high to mark each of the J1 bytes of the synchronous payload envelope(s) on the DOUT[7:0] bus. OC1J1 must be present at every occurrence of the first C1 byte and all J1 bytes. A V1 pulse added to the OC1J1 input will be ignored by the TUPP.                                                                                                                        |

|          |       |            | The OJ1EN bit is located in the master outgoing configuration register. OC1J1 is sampled on the rising edge of SCLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

ISSUE 8

| Pin Name | Туре  | Pin<br>No. | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------|-------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OTMF     | Input | 125        | The active high outgoing tributary multiframe (OTMF) signal identifies the first frame of the tributary multiframe for each AU3, or AU4 administrative unit, and STS-1 synchronous payload envelope. OTMF is selectable to pulse high during the V1 byte of the first tributary or during the H4 byte of the path overhead which indicates that the next frame is the first frame of the tributary multiframe. Selection between marking V1 or H4 bytes is controlled by the OTMFH4 bit located in the master outgoing configuration register. Pulses on OTMF are only effective during the H4 or V1 byte positions, as appropriate. OTMF is ignored at other byte positions. OTMF is sampled on the rising edge of SCLK.                                                                                                                                    |

| OSPE     | Input | 132        | The active high outgoing synchronous payload envelope (OSPE) signal identifies the bytes within the transport envelope frame on the DOUT[7:0] bus that carry the AU3 or AU4 virtual container(s), and the STS-1 synchronous payload envelopes. When the OJ1EN register bit is set high, OSPE must be set high to mark each such byte. When the OJ1EN bit is set low, the outgoing virtual container (synchronous payload envelope) is locked with the J1 byte immediately following the C1 byte. OSPE is ignored. DOUT[7:0], OTSPE, and OTV5 contain valid data only for bytes in the AU3 or AU4 virtual container(s), or the STS-1 synchronous payload envelopes. Their contents should be ignored for bytes in the transport overhead. The OJ1EN bit is located in the master outgoing configuration register. OSPE is sampled on the rising edge of SCLK. |

ISSUE 8

| Pin Name | Туре   | Pin<br>No. | Function                                                                                                                                                                                                                                                                                         |

|----------|--------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DIN[0]   | Input  | 54         | The data input bus (DIN[7:0]) carries                                                                                                                                                                                                                                                            |

| DIN[1]   |        | 56         | SONET/SDH frame data in byte serial format.  DIN[7] is the most significant bit, corresponding                                                                                                                                                                                                   |

| DIN[2]   |        | 58         | to bit 1 of each serial word, the bit transmitted                                                                                                                                                                                                                                                |

| DIN[3]   |        | 60         | first. DIN[0] is the least significant bit,                                                                                                                                                                                                                                                      |

| DIN[4]   |        | 62         | corresponding to bit 8 of each serial word, the last bit transmitted. The DIN[7:0] bus is sampled                                                                                                                                                                                                |

| DIN[5]   |        | 64         | on the rising edge of SCLK.                                                                                                                                                                                                                                                                      |

| DIN[6]   |        | 66         |                                                                                                                                                                                                                                                                                                  |

| DIN[7]   |        | 68         |                                                                                                                                                                                                                                                                                                  |

| DOUT[0]  | Output | 110        | The data output bus (DOUT[7:0]) carries                                                                                                                                                                                                                                                          |

| DOUT[1]  |        | 108        | SONET/SDH frame data in byte serial format.  DOUT[7] is the most significant bit,                                                                                                                                                                                                                |

| DOUT[2]  |        | 106        | corresponding to bit 1 of each serial word, the bit                                                                                                                                                                                                                                              |

| DOUT[3]  |        | 104        | transmitted first DOUT[0] is the least significant bit, corresponding to bit 8 of each serial word,                                                                                                                                                                                              |

| DOUT[4]  |        | 97         | the last bit transmitted. DOUT[7:0] contains valid                                                                                                                                                                                                                                               |

| DOUT[5]  |        | 95         | data only for bytes in the AU3 or AU4 virtual                                                                                                                                                                                                                                                    |

| DOUT[6]  |        | 93         | container(s), or the STS-1 synchronous payload envelopes. Its contents should be ignored for                                                                                                                                                                                                     |

| DOUT[7]  |        | 91         | bytes in the transport overhead. The DOUT[7:0] bus is updated on the rising edge of SCLK.                                                                                                                                                                                                        |

| OPAR     | Output | 89         | The outgoing stream parity (OPAR) signal carries the parity of the outgoing data stream. Odd parity is selected by setting the OOP register bit in the master parity configuration register high, and even parity is selected by setting the OOP bit low. OPAR is updated on the rising of SCLK. |

ISSUE 8

| Pin Name | Туре   | Pin<br>No. | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------|--------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OTSPE    | Output | 134        | The outgoing tributary synchronous payload envelope (OTSPE) signal marks the bytes carrying the tributary synchronous payload envelope(s). OTSPE is set high to mark each such byte on the DOUT[7:0] bus. OTSPE, contains valid data only for bytes in the AU3 or AU4 virtual container(s), or the STS-1 synchronous payload envelopes. Its contents should be ignored for bytes in the transport overhead. OTSPE is updated on the rising edge of SCLK.                    |

| OTV5     | Output | 136        | The outgoing tributary V5 byte (OTV5) signal marks the various tributary V5 bytes. OTV5 is set high to mark each tributary V5 byte on the DOUT[7:0] bus. When the output tributary is a TU3, OTV5 marks the J1 byte of the TU3. OTV5 contains valid data only for bytes in the AU3 or AU4 virtual container(s), or the STS-1 synchronous payload envelopes. Its contents should be ignored for bytes in the transport overhead. OTV5 is updated on the rising edge of SCLK. |

| MBEB     | Input  | 14         | The active low Motorola bus enable (MBEB) signal configures the TUPP for Motorola bus mode where the RDB/E signal functions as E, and the WRB/RWB signal functions as RWB. When MBEB is high, the TUPP is configured for Intel bus mode where the RDB/E signal functions as RDB. The MBEB input has an integral pull up resistor.                                                                                                                                           |

| CSB      | Input  | 13         | The active low chip select (CSB) signal is low during TUPP register accesses.                                                                                                                                                                                                                                                                                                                                                                                               |

ISSUE 8

| Pin Name | Туре  | Pin<br>No. | Function                                                                                                                                                                                                                                                                                                                                                  |

|----------|-------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RDB/     | Input | 35         | The active low read enable (RDB) signal is low during TUPP register read accesses while in Intel bus mode. The TUPP drives the D[7:0] bus with the contents of the addressed register while RDB and CSB are low.                                                                                                                                          |

| E        |       |            | The active high external access (E) signal is high during TUPP register access while in Motorola bus mode.                                                                                                                                                                                                                                                |

| WRB/     | Input | 37         | The active low write strobe (WRB) signal is low during a TUPP register write accesses while in Intel bus mode. The D[7:0] bus contents are clocked into the addressed register on the rising WRB edge while CSB is low.                                                                                                                                   |

| RWB      |       |            | The read/write select (RWB) signal selects between TUPP register read and write accesses while in Motorola bus mode. The TUPP drives the D[7:0] bus with the contents of the addressed register while CSB is low and RWB and E are high. The D[7:0] bus contents are clocked into the addressed register on the falling E edge while CSB and RWB are low. |

| D[0]     | I/O   | 15         | The bidirectional data bus D[7:0] is used during                                                                                                                                                                                                                                                                                                          |

| D[1]     |       | 16         | TUPP register read and write accesses.                                                                                                                                                                                                                                                                                                                    |

| D[2]     |       | 17         |                                                                                                                                                                                                                                                                                                                                                           |

| D[3]     |       | 18         |                                                                                                                                                                                                                                                                                                                                                           |

| D[4]     |       | 23         |                                                                                                                                                                                                                                                                                                                                                           |

| D[5]     |       | 24         |                                                                                                                                                                                                                                                                                                                                                           |

| D[6]     |       | 25         |                                                                                                                                                                                                                                                                                                                                                           |

| D[7]     |       | 26         |                                                                                                                                                                                                                                                                                                                                                           |

ISSUE 8

| Pin Name | Туре         | Pin<br>No. | Function                                                                                                                                                                                                                                                            |

|----------|--------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A[0]     | Input        | 4          | The address bus A[7:0] selects specific registers                                                                                                                                                                                                                   |

| A[1]     |              | 5          | during TUPP register accesses.                                                                                                                                                                                                                                      |

| A[2]     |              | 6          |                                                                                                                                                                                                                                                                     |

| A[3]     |              | 7          |                                                                                                                                                                                                                                                                     |

| A[4]     |              | 8          |                                                                                                                                                                                                                                                                     |

| A[5]     |              | 9          |                                                                                                                                                                                                                                                                     |

| A[6]     |              | 10         |                                                                                                                                                                                                                                                                     |

| A[7]/TRS |              | 11         | The test register select (TRS) signal selects between normal and test mode register accesses. TRS is high during test mode register accesses, and is low during normal mode register accesses. TRS has an integral pull down resistor.                              |

| RSTB     | Input        | 31         | The active low reset (RSTB) signal provides an asynchronous TUPP reset. RSTB is a Schmitt triggered input with an integral pull up resistor.                                                                                                                        |

| ALE      | Input        | 33         | The address latch enable (ALE) is active high and latches the address bus A[7:0] when low. When ALE is high, the internal address latches are transparent. It allows the TUPP to interface to a multiplexed address/data bus. ALE has an integral pull up resistor. |

| INTB     | OD<br>Output | 28         | The active low interrupt (INTB) signal goes low when a TUPP interrupt source is active. INTB returns high when the interrupt is acknowledged via an appropriate register access. INTB is an open drain output.                                                      |

ISSUE 8

| Pin Name | Туре   | Pin<br>No. | Function                                                                                                 |

|----------|--------|------------|----------------------------------------------------------------------------------------------------------|

| VDDI1    | Power  | 20         | The core power (VDDI1 - VDDI6) pins should be connected to a well decoupled +5 V DC in common with VDDO. |

| VDDI2    |        | 46         |                                                                                                          |

| VDDI3    |        | 72         |                                                                                                          |

| VDDI4    |        | 101        |                                                                                                          |

| VDDI5    |        | 131        |                                                                                                          |

| VDDI6    |        | 155        |                                                                                                          |

| VSSI1    | Ground | 21         | The core ground (VSSI1 - VSSI6) pins should be                                                           |

| VSSI2    |        | 50         | connected to GND in common with VSSO.                                                                    |

| VSSI3    |        | 74         |                                                                                                          |

| VSSI4    |        | 100        |                                                                                                          |

| VSSI5    |        | 128        |                                                                                                          |

| VSSI6    |        | 151        |                                                                                                          |

| VDDO1    | Power  | 19         | The pad ring power (VDDO1 - VDDO6) pins                                                                  |

| VDDO2    |        | 87         | should be connected to a well decoupled +5 V DC in common with VDDI.                                     |

| VDDO3    |        | 102        | Do in common with VDD.                                                                                   |

| VDDO4    |        | 113        |                                                                                                          |

| VDDO5    |        | 130        |                                                                                                          |

| VDDO6    |        | 154        |                                                                                                          |

| VSSO1    | Ground | 22         | The pad ring ground (VSSO1 - VSSO8) pins                                                                 |

| VSSO2    |        | 29         | should be connected to GND in common with VSSI.                                                          |

| VSSO3    |        | 86         | , tool.                                                                                                  |

| VSSO4    |        | 99         |                                                                                                          |

| VSSO5    |        | 112        |                                                                                                          |

| VSSO6    |        | 129        |                                                                                                          |

| VSSO7    |        | 138        |                                                                                                          |

| VSSO8    |        | 152        |                                                                                                          |

ISSUE 8

| Pin Name | Туре   | Pin<br>No. | Function                                                                                 |

|----------|--------|------------|------------------------------------------------------------------------------------------|

| VSST1    | Ground | 1          | The thermal ground (VSST1 - VSST24) pins                                                 |

| VSST2    |        | 2          | should be connected to GND in common with VSSI and VSSO. They may also be left floating. |

| VSST3    |        | 3          | The VSST pins may be electrically connected                                              |

| VSST4    |        | 38         | together (fused) and connected to the back of                                            |

| VSST5    |        | 39         | the die to improve the thermal characteristics of the package.                           |

| VSST6    |        | 40         |                                                                                          |

| VSST7    |        | 41         |                                                                                          |

| VSST8    |        | 42         |                                                                                          |

| VSST9    |        | 43         |                                                                                          |

| VSST10   |        | 78         |                                                                                          |

| VSST11   |        | 79         |                                                                                          |

| VSST12   |        | 80         |                                                                                          |

| VSST13   |        | 81         |                                                                                          |

| VSST14   |        | 82         |                                                                                          |

| VSST15   |        | 83         |                                                                                          |

| VSST16   |        | 118        |                                                                                          |

| VSST17   |        | 119        |                                                                                          |

| VSST18   |        | 120        |                                                                                          |

| VSST19   |        | 121        |                                                                                          |

| VSST20   |        | 122        |                                                                                          |

| VSST21   |        | 123        |                                                                                          |

| VSST22   |        | 158        |                                                                                          |

| VSST23   |        | 159        |                                                                                          |

| VSST24   |        | 160        |                                                                                          |

ISSUE 8

TRIBUTARY UNIT PAYLOAD PROCESSOR

#### **Notes on Pin Description:**

- 1. All TUPP inputs and bidirectionals present minimum capacitive loading and operate at TTL logic levels.

- 2. All TUPP digital outputs and bidirectionals have 4 mA drive capability.

- 3. The VSSO and VSSI ground pins are not internally connected together. Failure to connect these pins externally may cause malfunction or damage the TUPP.

- 4. The VDDO and VDDI power pins are not internally connected together. Failure to connect these pins externally may cause malfunction or damage the TUPP.

ISSUE 8

TRIBUTARY UNIT PAYLOAD PROCESSOR

#### 9 FUNCTIONAL DESCRIPTION

#### 9.1 Input Bus Demultiplexer

The input bus demultiplexer captures data sampled on the DIN bus and distributes this data to the three tributary payload processors within the TUPP.

The input bus demultiplexer also provides timing signals for the other blocks within the TUPP. The system clock, SCLK, is buffered and distributed to the tributary payload processors and the output bus multiplexer. Frame alignment signals for the incoming data stream, IC1J1, ITMF, and ISPE, are sampled, buffered and distributed to the tributary payload processors (TPPs). In order to have synchronous operation of the TPPs with a single clock, the incoming data and control signals may be delayed by up to two system clock cycles before distribution to the TPP. The delay is used to align the incoming data with the outgoing data at each TPP. The amount of delay is adjusted such that the separation of the incoming STS/AU frame and the outgoing frame at each TPP appears to be in multiples of three SCLK periods.

When configured for AU4 mode, the input bus demultiplexer provides the necessary timing coordination between the three tributary payload processors. The single J1 byte marker input on IC1J1 is retimed and distributed to each of the three tributary payload processors. The tributary multiframe detected by TPP #1 is distributed to the two other TPPs, as TPP #1 is the only one receiving a valid H4 byte.

#### 9.2 Output Bus Multiplexer

The output bus multiplexer gathers data from the three tributary payload processors within the TUPP and multiplexes this data onto the DOUT[7:0] bus. It also multiplexes signals from each tributary payload processor that mark tributary SPEs and tributary V5 bytes onto the shared OTSPE and OTV5 signals.

The output bus multiplexer also provides timing signals for other blocks within the TUPP. Frame alignment signals for the outgoing data stream, OC1J1, OSPE and OTMF, are sampled, buffered and distributed to the tributary payload processors (TPPs). The output bus multiplexer contains a four frame counter that will flywheel in the absence of an active OTMF input, internally generating tributary multiframe timing for the outgoing data stream. When configured for locked output mode, i.e. when OJ1EN is low, the output bus multiplexer will internally

**ISSUE 8**

TRIBUTARY UNIT PAYLOAD PROCESSOR

generate J1 and SPE timing for the outgoing data stream that corresponds to the J1 bytes following the C1 bytes and no pointer justifications at the STS-1 (AU3) or AU4 level. This timing drives the outputs of the three tributary payload processors, substituting for the function otherwise provided by the OC1J1 and OSPE inputs.

When configured for AU4 mode, the output bus multiplexer provides the necessary timing coordination between the three tributary payload processors. This consists of deriving VC4 framing from the single J1 byte marker input on OC1J1 and distributing this to each tributary payload processor.

#### 9.3 Tributary Payload Processor

Each tributary payload processor processes the tributaries within an STS-1, AU3, or TUG3. Each TPP can be configured to process any legal mix of VT1.5s, VT2s, VT3s, or VT6s that can be carried in an STS-1 or any legal mix of TU11s, TU12s, TU2s, or TU3s, that can be carried in an AU3 or TUG3. The number of tributaries managed by each TPP ranges from 1 (when configured to process a single TU3) to 28 (when configured to process all VT1.5s or all TU11s).

#### 9.3.1 Clock Generator

The clock generator derives various clocks from the 19.44 MHz system clock and distributes them to other blocks within the tributary payload processor. The overall design is totally synchronous, with processing occurring at a 6.48 MHz rate in each tributary payload processor.

#### 9.3.2 Incoming Timing Generator

The incoming timing generator identifies the incoming tributary being processed at any given point in time. Based on the configuration of the TPP (it can process various mixes of tributary types), the incoming timing generator extracts the STS-1 SPE, VC3, or a single TUG3 from a VC4, and identifies the bytes within these envelopes that correspond to various types of overhead and those that carry specific tributaries to be processed. The H4 byte is identified for the incoming multiframe detector so that it can determine the incoming tributary multiframe boundaries. The identification of specific tributaries allows the pointer interpreter to be time-sliced across the mix of tributaries present in the incoming data stream. The identification of the V1-V3 bytes of VTs, or TUs (or H1-H3 bytes in the case of TU3s) allows the pointer interpreter to function.

ISSUE 8

TRIBUTARY UNIT PAYLOAD PROCESSOR

#### 9.3.3 Incoming Multiframe Detector

The incoming multiframe detector frames to the tributary multiframe encoded into the H4 bytes. It aligns a fly-wheeling multiframe counter to the alignment indicated by the H4 bytes when confidence is achieved in the H4 bytes. A change of incoming tributary multiframe occurs when the H4 bytes cycle error free and in correct sequence for four frames, and the detected alignment is new. The incoming multiframe detector is disabled and the multiframe is indicated by the ITMF input signal, when ITMF is enabled through the ITMFEN register bit.

#### 9.3.4 Pointer Interpreter

The pointer interpreter is a time-sliced state machine that can process up to 28 independent tributaries. The state vector is saved in RAM as directed by the incoming timing generator. The pointer interpreter processes the incoming tributary pointers such that all bytes within the tributary synchronous payload envelope can be identified and written into the unique payload buffer for the tributary in question. A marker that tags the V5 byte (or J1 byte in the case of a TU3) is passed through the payload buffer. The incoming timing generator directs the pointer interpreter to the correct payload buffer for the tributary being processed. Loss of pointer status is captured in microprocessor readable registers for each tributary and interrupts can optionally be generated upon loss of pointer and pointer acquisition. The pointer interpreter detects tributary path AIS and suppresses the loss of pointer indication that would otherwise occur. The pointer interpreter passes this information to the pointer generator triggering path AIS insertion into the corresponding outgoing tributary.

The pointer generator can be configured to insert tributary path AIS into outgoing tributaries if loss of pointer is detected on the associated incoming tributary.

#### 9.3.5 Payload Buffer

The payload buffer is a bank of FIFO buffers. It is synchronous in operation and is based on a time-sliced RAM. The three 19.44 MHz clock cycles in each 6.48 MHz period are shared between the read and write operations. The pointer interpreter writes tributary payload data and the V5 (or TU3 J1) tag into the payload buffer. A 16 byte FIFO buffer is provided for each of the (up to 28) tributaries. Address information is also passed through the payload buffer to allow FIFO fill status to be determined by the pointer generator.

ISSUE 8

TRIBUTARY UNIT PAYLOAD PROCESSOR

#### 9.3.6 Outgoing Timing Generator

The outgoing timing generator identifies the outgoing tributary byte being processed. Based on the configuration of the TPP, the outgoing timing generator effectively constructs the STS-1 SPE, VC3, or VC4, and identifies the bytes within these envelopes that correspond to various types of overhead and bytes that carry specific tributaries. The identification of specific tributaries allows the pointer generator to be time-sliced across the mix of tributaries to be sourced in the outgoing data stream. The identification of the V1-V3 bytes of VTs, or TUs (H1-H3 bytes of TU3s) allows the pointer generator to function.

The sequence H4 bytes is generated by each tributary payload processor and inserted into the outgoing administrative units. The six most significant bits of H4 are set to logic 1. The sequence of the remaining two H4 bits is determined by the OTMF input when enabled or from the incoming multiframe alignment.

#### 9.3.7 Pointer Generator

The pointer generator is a time-sliced state machine that can process up to 28 independent tributaries. The state vector is saved in RAM at the address associated with the current tributary. The pointer generator fills the outgoing tributary synchronous payload envelopes with bytes read from the associated FIFO in the payload buffer for the current tributary. The pointer generator creates pointers in the V1-V3 bytes (or H1-H3 bytes in the case of TU3s) of the outgoing data stream. The marker that tags the V5 byte (or J1 byte in the case of a TU3) that is passed through the payload buffer is used to align the pointer. The outgoing timing generator directs the pointer generator to the FIFO is the payload buffer associated with the tributary being processed. The pointer generator monitors the fill levels of the payload buffers and inserts outgoing pointer justifications as necessary to avoid FIFO spillage. Normally, the pointer generator has a FIFO dead band of 4 bytes. The dead band can be collapse to one so that any incoming pointer justifications will be reflected by a corresponding outgoing justification with no attenuation. Signals are output by the pointer generator that identify outgoing V5 bytes (or J1 bytes in the case of a TU3) and the tributary synchronous payload envelopes. These facilitate tributary performance monitoring external to the TUPP. On a per tributary basis, tributary path AIS and tributary idle (unequipped) can be inserted as controlled by microprocessor accessible registers. The idle code is selectable globally for the entire VC3 or TUG3 to be all zeros or all ones. It is also possible to force an inverted new data flag on individual tributaries for the purpose of diagnosing downstream pointer processors. Tributary path AIS is automatically inserted into

ISSUE 8

TRIBUTARY UNIT PAYLOAD PROCESSOR

outgoing tributaries if the pointer interpreter detects tributary path AIS on the corresponding incoming tributary.

#### 9.3.8 Common Bus Interface

The common bus interface allows microprocessor access to the registers within each tributary payload processor. It is used during normal operation and also during production test. It forms part of the overall microprocessor interface of the TUPP.

#### 9.4 Microprocessor Interface

The microprocessor interface block provides normal and test mode registers, and the logic required to connect to the microprocessor interface. The normal mode registers are required for normal operation, and test mode registers are used to enhance the testability of the TUPP. Tributary based normal mode registers are arranged in order of transmission; TU #1 in TUG2 #1 is the first tributary transmitted, while TU #4 in TUG2 #7 is the last. The register set is accessed as follows:

#### 9.5 Register Memory Map

| Address | Register                                                       |

|---------|----------------------------------------------------------------|

| 00H     | TUPP Master Incoming Configuration                             |

| 01H     | TUPP Master Outgoing Configuration                             |

| 02H     | Input Signal Activity Monitor                                  |

| 03H     | TUPP Master Reset and Identity                                 |

| 04H     | Tributary Payload Processor #1 Configuration                   |

| 05H     | Tributary Payload Processor #2 Configuration                   |

| 06H     | Tributary Payload Processor #3 Configuration                   |

| 07H     | Tributary Payload Processor and H4 OOF Interrupt Enable        |

| 08H     | Tributary Payload Processor Interrupt Status and H4 OOF Status |

| 09H     | Parity Error and H4 OOF Interrupt                              |

| 0AH-1FH | Reserved                                                       |

| 20H     | TPP #1, TU3, or TU #1 in TUG2 #1, Configuration and Status     |

ISSUE 8

| Address | Register                                                  |

|---------|-----------------------------------------------------------|

| 21H     | TPP #1, TU #1 in TUG2 #2, Configuration and Status        |

| 22H     | TPP #1, TU #1 in TUG2 #3, Configuration and Status        |

| 23H     | TPP #1, TU #1 in TUG2 #4, Configuration and Status        |

| 24H     | TPP #1, TU #1 in TUG2 #5, Configuration and Status        |

| 25H     | TPP #1, TU #1 in TUG2 #6, Configuration and Status        |

| 26H     | TPP #1, TU #1 in TUG2 #7, Configuration and Status        |

| 27H     | TPP #1, TU3 or TU #1 in TUG2 #1 to TUG2 #7, LOP Interrupt |

| 28H     | TPP #1, TU #2 in TUG2 #1, Configuration and Status        |

| 29H     | TPP #1, TU #2 in TUG2 #2, Configuration and Status        |

| 2AH     | TPP #1, TU #2 in TUG2 #3, Configuration and Status        |

| 2BH     | TPP #1, TU #2 in TUG2 #4, Configuration and Status        |

| 2CH     | TPP #1, TU #2 in TUG2 #5, Configuration and Status        |

| 2DH     | TPP #1, TU #2 in TUG2 #6, Configuration and Status        |

| 2EH     | TPP #1, TU #2 in TUG2 #7, Configuration and Status        |

| 2FH     | TPP #1, TU #2 in TUG2 #1 to TUG2 #7, LOP Interrupt        |

| 30H     | TPP #1, TU #3 in TUG2 #1, Configuration and Status        |

| 31H     | TPP #1, TU #3 in TUG2 #2, Configuration and Status        |

| 32H     | TPP #1, TU #3 in TUG2 #3, Configuration and Status        |

| 33H     | TPP #1, TU #3 in TUG2 #4, Configuration and Status        |

| 34H     | TPP #1, TU #3 in TUG2 #5, Configuration and Status        |

| 35H     | TPP #1, TU #3 in TUG2 #6, Configuration and Status        |

| 36H     | TPP #1, TU #3 in TUG2 #7, Configuration and Status        |

| 37H     | TPP #1, TU #3 in TUG2 #1 to TUG2 #7, LOP Interrupt        |

| 38H     | TPP #1, TU #4 in TUG2 #1, Configuration and Status        |

| 39H     | TPP #1, TU #4 in TUG2 #2, Configuration and Status        |

| ЗАН     | TPP #1, TU #4 in TUG2 #3, Configuration and Status        |

| 3ВН     | TPP #1, TU #4 in TUG2 #4, Configuration and Status        |

ISSUE 8

TRIBUTARY UNIT PAYLOAD PROCESSOR

| Address | Register                                           |

|---------|----------------------------------------------------|

| 3CH     | TPP #1, TU #4 in TUG2 #5, Configuration and Status |

| 3DH     | TPP #1, TU #4 in TUG2 #6, Configuration and Status |

| 3EH     | TPP #1, TU #4 in TUG2 #7, Configuration and Status |

| 3FH     | TPP #1, TU #4 in TUG2 #1 to TUG2 #7, LOP Interrupt |

| 40H-5FH | Tributary Payload Processor #2 Registers           |

| 60H-7FH | Tributary Payload Processor #3 Registers           |

| 80H     | Master Test                                        |

| 81H-FFH | Reserved for Test                                  |

For all register accesses, CSB must be low.

ISSUE 8

TRIBUTARY UNIT PAYLOAD PROCESSOR

#### 10 NORMAL MODE REGISTER DESCRIPTION

Normal mode registers are used to configure and monitor the operation of the TUPP. Normal mode registers (as opposed to test mode registers) are selected when A[7] is low.

## **Notes on Normal Mode Register Bits:**

- 1. Writing values into unused register bits has no effect. However, to ensure software compatibility with future, feature-enhanced versions of the product, unused register bits must be written with logic 0. Reading back unused bits can produce either a logic 1 or a logic 0; hence unused register bits should be masked off by software when read.

- 2. All configuration bits that can be written into can also be read back. This allows the processor controlling the TUPP to determine the programming state of the block.

- 3. Writable normal mode register bits are cleared to logic 0 upon reset unless otherwise noted.

- 4. Writing into read-only normal mode register bit locations does not affect TUPP operation unless otherwise noted.

ISSUE 8

TRIBUTARY UNIT PAYLOAD PROCESSOR

## Register 00H: Master Incoming Configuration

| Bit   | Туре | Function | Default |

|-------|------|----------|---------|

| Bit 7 | R/W  | IPE      | 0       |

| Bit 6 | R/W  | AUTOAIS  | 0       |

| Bit 5 | R/W  | INCISPE  | 0       |

| Bit 4 | R/W  | INCIC1J1 | 0       |

| Bit 3 | R/W  | IOP      | 0       |

| Bit 2 | R/W  | ITMFH4   | 0       |

| Bit 1 | R/W  | ITMFEN   | 0       |

| Bit 0 | R/W  | ICONCAT  | 0       |

This register configures the TUPP functionality that are related to the incoming data stream.

#### **ICONCAT:**

When set high, the ICONCAT bit configures the incoming section of the TUPP to operate in AU4 mode. When the ICONCAT bit is set low, the incoming section operates in AU3 mode (or equivalently, STS-1 mode).

## **ITMFEN:**

When set high, the ITMFEN bit enables the TUPP to use the ITMF input signal to locate tributary multiframe boundaries. The H4 bytes in the incoming data stream are ignored. When ITMFEN is set low, the H4 bytes are used to locate the boundaries, and the ITMF signal is ignored.

## ITMFH4:

The ITMFH4 bit selects the location of the ITMF in the tributary multiframe. When ITMFH4 is set high, ITMF is pulsed high to mark the H4 byte which indicates that the next AU3/4 or STS-1 frame is the first frame of the tributary multiframe. When ITMFH4 is set low, ITMF marks the V1 byte of the first tributary. ITMFH4 is ignored if ITMF is disabled by setting the ITMFEN bit low.

#### IOP:

The IOP bit controls the expected parity on the incoming parity signal IPAR. When IOP is set high, the parity of the parity signal set, together with IPAR is

**ISSUE 8**

TRIBUTARY UNIT PAYLOAD PROCESSOR

expected to be odd. When IOP is set low, the expected parity is even. Membership of the parity signal set always includes DIN[7:0], and may include input signals IC1J1 and ISPE as controlled by the INCIC1J1 and INCISPE bits, respectively.

## **INCIC1J1:**

The INCIC1J1 bit controls the whether the 1C1J1 input signal participates in the incoming parity calculations. When INCIC1J1 is set high, the parity signal set includes the IC1J1 input. When INCIC1J1 is set low, parity is calculated without regard to the state of IC1J1. Selection of odd or even parity is controlled by the IOP bit.

## INCISPE:

The INCISPE bit controls the whether the ISPE input signal participates in the incoming parity calculations. When INCISPE is set high, the parity signal set includes the ISPE input. When INCISPE is set low, parity is calculated without regard to the state of ISPE. Selection of odd or even parity is controlled by the IOP bit.

## **AUTOAIS:**

The AUTOAIS bit is an active high AIS insertion enable. When AUTOAIS is set high, AIS is automatically generated on the outgoing data stream for all tributaries that exhibit a LOP state. When AUTOAIS is set low, the generation of AIS on the outgoing data stream is inhibited. The negation of AIS occurs at tributary multiframe boundaries.

## IPE:

The IPE bit is an active high interrupt enable. When IPE is set high, the occurrence of a parity error on the incoming parity signal set will cause an interrupt to be asserted on the interrupt (INTB) output. When IPE is set low, incoming parity errors will not cause an interrupt.

ISSUE 8

TRIBUTARY UNIT PAYLOAD PROCESSOR

## **Register 01H: Master Outgoing Configuration**

| Bit   | Туре | Function | Default |

|-------|------|----------|---------|

| Bit 7 |      | Unused   | Х       |

| Bit 6 |      | Unused   | Х       |

| Bit 5 |      | Unused   | Х       |

| Bit 4 |      | Unused   | Х       |

| Bit 3 | R/W  | OOP      | 0       |

| Bit 2 | R/W  | OTMFH4   | 0       |

| Bit 1 | R/W  | OJ1EN    | 0       |

| Bit 0 | R/W  | OCONCAT  | 0       |

This register configures the TUPP functionality that are related to the outgoing data stream.

#### OCONCAT:

When set high, the OCONCAT bit configures the outgoing section of the TUPP to operate in AU4 mode. When the OCONCAT bit is set low, the outgoing section operates in AU3 mode (or equivalently, STS-1 mode).

## OJ1EN: