OBSOLETE PRODUCT

NO RECOMMENDED REPLACEMENT

Sontact our Technical Support Center at contact our Technical Support Com/tsc

1-888-INTERSIL or www.intersil.com/tsc

Decei

December 1995, Rev. F

FN7028

# 120MHz Current Feedback Amplifier

# *élantec*.

The EL2030 is a very fast, wide bandwidth amplifier optimized for gains between -10 and +10. Built using

the Elantec monolithic Complementary Bipolar process, this amplifier uses current mode feedback to achieve more bandwidth at a given gain than a conventional voltage feedback operational amplifier.

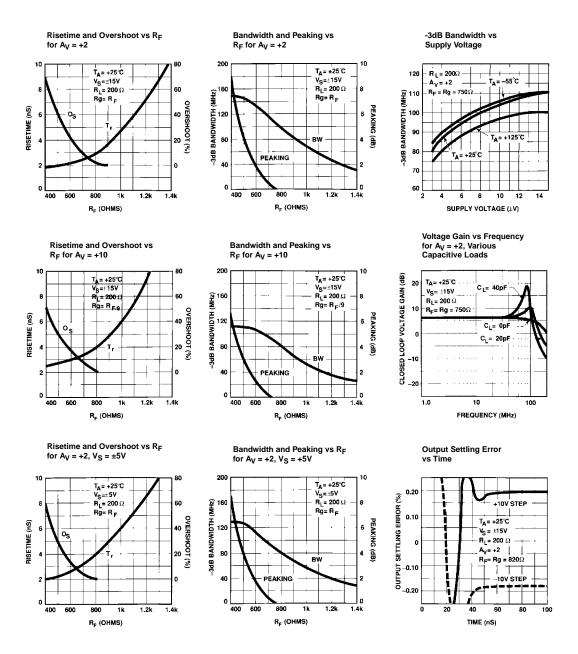

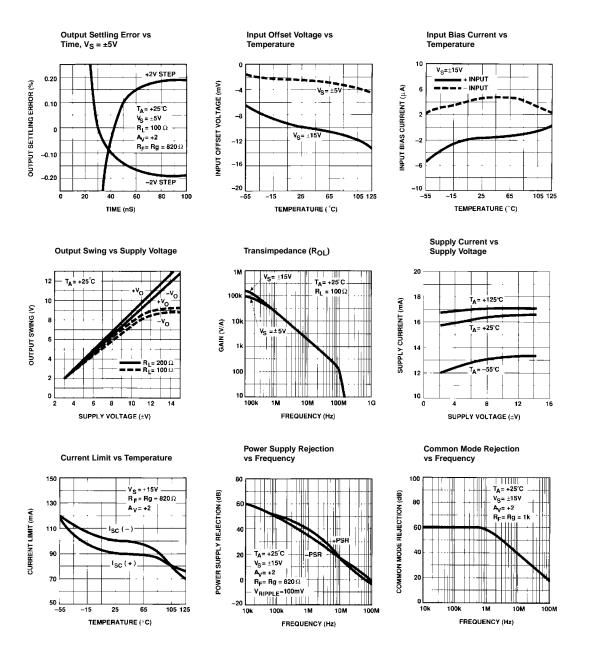

Due to its wide operating supply range ( $\pm 15V$ ) and extremely high slew rate of 2000V/µs, the EL2030 drives  $\pm 10V$  into 200 $\Omega$  at a frequency of 30MHz, while achieving 110MHz of small signal bandwidth at A<sub>V</sub> = +2. This bandwidth is still 95MHz for a gain of +10. On  $\pm 5V$  supplies the amplifier maintains a 90MHz bandwidth for A<sub>V</sub> = +2. When used as a unity gain buffer, the EL2030 has a 120MHz bandwidth with the gain precision and low distortion of closed loop buffers.

The EL2030 features extremely low differential gain and phase, a low noise topology that reduces noise by a factor of 2 over competing amplifiers, and settling time of 40ns to 0.25% for a 10V step. The output is short circuit protected. In addition, datasheet limits are guaranteed for  $\pm 5$ V and  $\pm 15$ V supplies.

Elantec's products and facilities comply with applicable quality specifications. See Elantec document, QRA-1: Processing, Monolithic Integrated Circuits.

# Ordering Information

| PART NUMBER | TEMP. RANGE    | PACKAGE    | PKG. NO. |

|-------------|----------------|------------|----------|

| EL2030CN    | -40°C to +85°C | 8-Pin PDIP | MDP0031  |

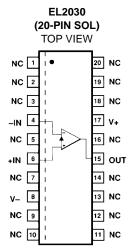

| EL2030CM    | -40°C to +85°C | 20-Pin SOL | MDP0027  |

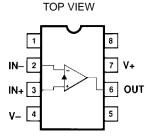

EL2030

(8-PIN PDIP)

#### **Pinouts**

#### **Features**

- -3dB bandwidth = 120MHz, A<sub>V</sub> = 1

- -3dB bandwidth = 110MHz, A<sub>V</sub> = 2

- 0.01% differential gain and 0.01° differential phase (NTSC, PAL)

- 0.05% differential gain and 0.02° differential phase (HDTV)

- Slew rate 2000V/µs

- · 65mA output current

- Drives ±10V into 200Ω load

- Characterized at ±5V and ±15V

- Low voltage noise

- · Current mode feedback

- Settling time of 40ns to 0.25% for a 10V step

- · Output short circuit protected

- · Low cost

### **Applications**

- · Video gain block

- Video distribution amplifier

- HDTV amplifier

- · Residue amplifiers in ADC

- · Current to voltage converter

- · Coax cable driver

NOTE: Non-Designated pins are no connects and are not electrically connected internally. Manufactured under U.S. Patent No. 4,893,091.

### EL2030

Output Short Circuit Duration . . . . . . . . . . . . . . . . . Continuous

### **Absolute Maximum Ratings** (T<sub>A</sub> = 25°C)

| $V_S$           | Supply Voltage         ±18V or 36V           Input Voltage         ±15V or V <sub>S</sub> | A heat sink is required to keep the junction temperature below absolute maximum when the output is shorted. |

|-----------------|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

|                 | Differential Input Voltage                                                                | T <sub>A</sub> Operating Temperature Range                                                                  |

|                 | Maximum Power Dissipation See Curves                                                      | T <sub>J</sub> Operating Junction Temperature                                                               |

| I <sub>IN</sub> | Input Current                                                                             | Plastic Packages150°C                                                                                       |

| IOP             | Peak Output Current Short Circuit Protected                                               | T <sub>ST</sub> Storage Temperature65°C to +150°C                                                           |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

IMPORTANT NOTE: All parameters having Min/Max specifications are guaranteed. Typical values are for information purposes only. Unless otherwise noted, all tests are at the specified temperature and are pulsed tests, therefore:  $T_J = T_C = T_A$

# Open Loop DC Electrical Specifications $V_S = \pm 15V$ , $R_L = 200\Omega$ , unless otherwise specified

| PARAMETER          | DESCRIPTION                                             | CONDITION               | TEMP                                | MIN | TYP | MAX | UNITS |

|--------------------|---------------------------------------------------------|-------------------------|-------------------------------------|-----|-----|-----|-------|

| Vos                | Input Offset Voltage                                    | V <sub>S</sub> = ±15V   | 25°C                                |     | 10  | 20  | mV    |

|                    |                                                         |                         | T <sub>MIN</sub> , T <sub>MAX</sub> |     |     | 30  | mV    |

|                    |                                                         | V <sub>S</sub> = ±5V    | 25°C                                |     | 5   | 10  | mV    |

|                    |                                                         |                         | T <sub>MIN</sub> , T <sub>MAX</sub> |     |     | 15  | mV    |

| V <sub>OS</sub> /T | Offset Voltage Drift                                    |                         |                                     |     | 25  |     | μV/°C |

| +I <sub>IN</sub>   | +Input Current                                          | $V_S = \pm 5V, \pm 15V$ | 25°C                                |     | 5   | 15  | μΑ    |

|                    |                                                         |                         | T <sub>MIN</sub> , T <sub>MAX</sub> |     |     | 25  | μΑ    |

| -I <sub>IN</sub>   | -Input Current                                          | $V_S = \pm 5V, \pm 15V$ | 25°C                                |     | 10  | 40  | μΑ    |

|                    |                                                         |                         | T <sub>MIN</sub> , T <sub>MAX</sub> |     |     | 50  | μΑ    |

| +R <sub>IN</sub>   | +Input Resistance                                       |                         | Full                                | 1.1 | 2.0 |     | MΩ    |

| C <sub>IN</sub>    | Input Capacitance                                       |                         | 25°C                                |     | 1   |     | pF    |

| CMRR               | Common Mode Rejection Ratio (Note 1)                    | $V_S = \pm 5V, \pm 15V$ | Full                                | 50  | 60  |     | dB    |

| -ICMR              | Input Current Common Mode Rejection (Note 1)            |                         | 25°C                                |     | 5   | 10  | μA/V  |

|                    |                                                         |                         | T <sub>MIN</sub> , T <sub>MAX</sub> |     |     | 20  | μA/V  |

| PSRR               | Power Supply Rejection Ratio (Note 2)                   |                         | Full                                | 60  | 70  |     | dB    |

| +IPSR              | +Input Current Power Supply Rejection (Note 2)          |                         | 25°C                                |     | 0.1 | 0.5 | μA/V  |

|                    |                                                         |                         | T <sub>MIN</sub> , T <sub>MAX</sub> |     |     | 1.0 | μA/V  |

| -IPSR              | -Input Current Power Supply Rejection (Note 2)          |                         | 25°C                                |     | 0.5 | 5.0 | μA/V  |

|                    |                                                         |                         | T <sub>MIN</sub> , T <sub>MAX</sub> |     |     | 8.0 | μA/V  |

| R <sub>OL</sub>    | Transimpedance                                          | V <sub>S</sub> = ±15V   | 25°C                                | 88  | 150 |     | V/mA  |

|                    | $(V_{OUT}/(-I_{IN}))$<br>$V_{OUT} = \pm 10V$            |                         | T <sub>MIN</sub> , T <sub>MAX</sub> | 75  |     |     | V/mA  |

|                    | V <sub>OUT</sub> = ±2.5V (Note 3)                       | $V_S = \pm 5V$          | 25°C                                | 80  | 120 |     | V/mA  |

|                    |                                                         |                         | $T_{MIN}, T_{MAX}$                  |     | 70  |     | V/mA  |

| A <sub>VOL</sub>   | Open Loop DC<br>Voltage Gain<br>V <sub>OUT</sub> = ±10V | V <sub>S</sub> = ±15V   | Full                                | 60  | 70  |     | dB    |

|                    | V <sub>OUT</sub> = ±2.5V (Note 3)                       | V <sub>S</sub> = ±5V    | Full                                | 56  | 65  |     | dB    |

| VO                 | Output Voltage Swing (Note 3)                           | V <sub>S</sub> = ±15V   | Full                                | 12  | 13  |     | V     |

|                    |                                                         | V <sub>S</sub> = ±5V    | Full                                | 3   | 3.5 |     | V     |

| lout               | Output Current (Note 4)                                 | V <sub>S</sub> = ±15V   | Full                                | 60  | 65  |     | mA    |

|                    |                                                         | $V_S = \pm 5V$          | Full                                | 30  | 35  |     | mA    |

### Open Loop DC Electrical Specifications $V_S = \pm 15V$ , $R_L = 200\Omega$ , unless otherwise specified (Continued)

| PARAMETER        | DESCRIPTION              | CONDITION | TEMP | MIN | TYP | MAX | UNITS |

|------------------|--------------------------|-----------|------|-----|-----|-----|-------|

| R <sub>OUT</sub> | Output Resistance        |           | 25°C |     | 5   |     | Ω     |

| IS               | Quiescent Supply Current |           | Full |     | 15  | 21  | mA    |

| I <sub>SC</sub>  | Short Circuit Current    |           | 25°C |     | 85  |     | mA    |

#### NOTES:

- 1.  $V_{CM} = \pm 10V$  for  $V_S = \pm 15V$ . For  $V_S = \pm 5V$ ,  $V_{CM} = \pm 2.5V$ .

- 2.  $V_{OS}$  is measured at  $V_S = \pm 4.5 \text{V}$  and at  $V_S = \pm 18 \text{V}$ . Both supplies are changed simultaneously.

- 3.  $R_L = 100\Omega$ .

- 4. For  $V_S = \pm 15V$ ,  $V_{OUT} = \pm 10V$ . For  $V_S \pm 5V$ ,  $V_{OUT} = \pm 2.5V$ .

# Closed Loop AC Electrical Characteristics $V_S = \pm 15 \text{V}, A_V = +2, R_F = 820 \Omega, R_G = 820 \Omega$ and $R_L = 200 \Omega$

| PARAMETER                       | DESCRIPTION                                                         | CONDITION               | TEMP | MIN  | TYP  | MAX | UNITS  |

|---------------------------------|---------------------------------------------------------------------|-------------------------|------|------|------|-----|--------|

| SR                              | Slew Rate (Note 1)                                                  |                         | 25°C | 1200 | 2000 |     | V/µs   |

| FPBW                            | Full Power Bandwidth (Note 2)                                       |                         | 25°C | 19   | 31.8 |     | MHz    |

| t <sub>R</sub> , t <sub>F</sub> | Rise Time. Fall Time                                                | V <sub>PP</sub> = 250mV | 25°C |      | 3    |     | ns     |

| t <sub>S</sub>                  | Settling Time to 0.25% for 10V step (Note 3)                        |                         | 25°C |      | 40   |     | ns     |

| G                               | Differential Gain (Note 4)                                          |                         | 25°C |      | 0.01 |     | % p-p  |

|                                 | Differential Phase (Note 4)                                         |                         | 25°C |      | 0.01 |     | ° p-p  |

| eN                              | Input Spot Noise at 1kHz R <sub>G</sub> = 101; R <sub>F</sub> = 909 |                         | 25°C |      | 4    |     | nV/√Hz |

#### NOTES:

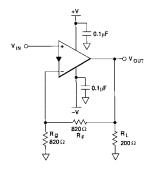

- 1.  $V_O = \pm 10V$ , tested at  $V_O = \pm 5$ . See test circuit.

- 2. Full Power Bandwidth is specified based on Slew Rate measurement FPBW =  $SR/2\pi V_P$ .

- 3. Settling Time measurement techniques are shown in: "Take The Guesswork Out of Settling Time Measurements', EDN, September 19, 1985. Available from the factory upon request.

- 4. NTSC (3.58MHz) and PAL (4.43MHz).

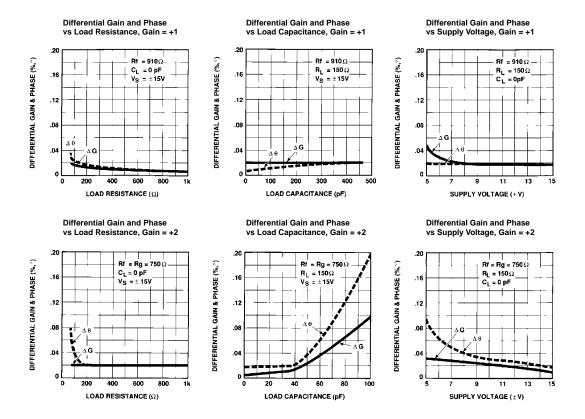

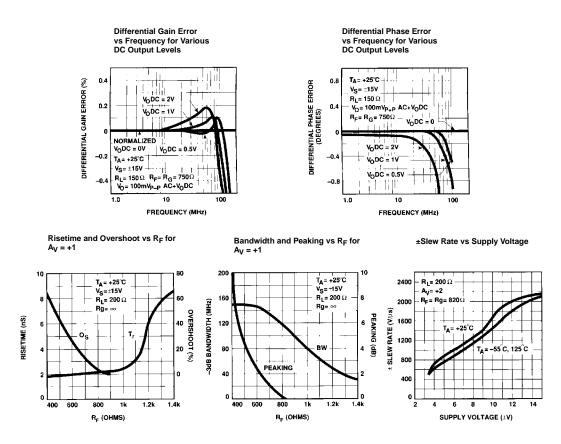

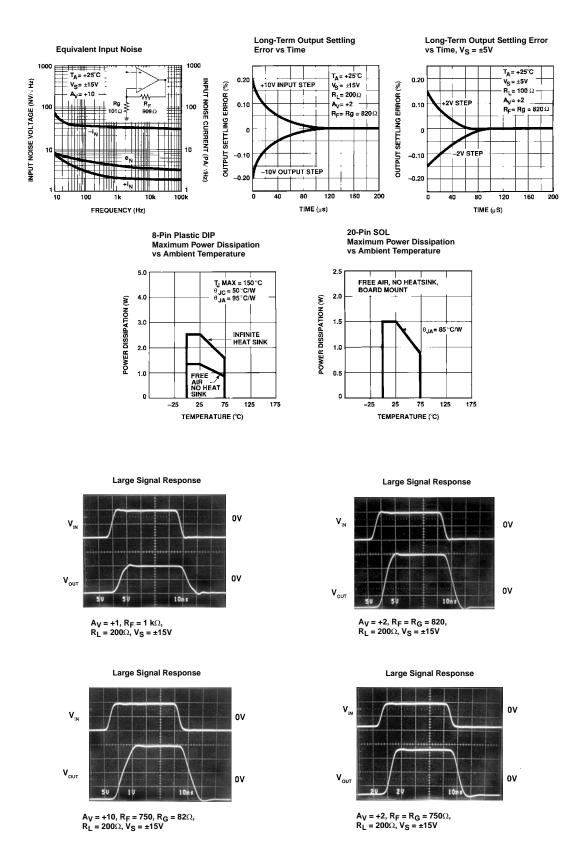

# **Typical Performance Curves**

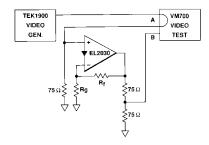

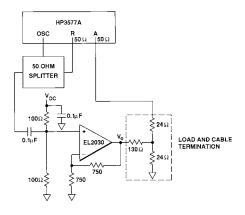

FIGURE 1. NTSC VIDEO DIFFERENTIAL GAIN AND PHASE TEST SET-UP

FIGURE 2. HDTV AND WIDEBAND VIDEO DIFFERENTIAL GAIN AND PHASE TEST SET-UP

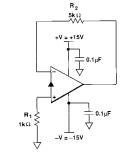

#### **Burn-In Circuit**

ALL PACKAGES USE THE SAME SCHEMATIC

#### **Test Circuit**

### Application Information

### **Product Description**

The EL2030 is a current mode feedback amplifier similar to the industry standard EL2020, but with greatly improved AC characteristics. Most significant among these are the extremely wide bandwidth and very low differential gain and phase. In addition, the EL2030 is fully characterized and tested at ±5V and ±15V supplies.

#### Power Supply Bypassing/Pin Dressing

It is important to bypass the power supplies of the EL2030 with  $0.1\mu F$  ceramic disc capacitors. Although the pin length is not critical, it should not be more the 1/2 inch from the IC pins. Failure to do this will result in oscillation, and possible destruction of the part. Another important detail is the pin length of the inputs. The inputs should be designed with minimum stray capacitance and short pin lengths to avoid ringing and distortion.

#### Latch Mode

The EL2030 can be damaged in certain circumstances resulting in catastrophic failure in which destructive supply currents flow in the device. Specifically, an input signal greater than ±5 volts at currents greater than 5mA is applied to the device when the power supply voltages are zero will result in failure of the device.

In addition, the EL2030 will be destroyed or damaged in the same way for momentary power supply voltage reversals. This could happen, for example, during a power turn on transient, or if the power supply voltages were oscillating and the positive rail were instantaneously negative with respect to the negative rail or vice versa.

#### Differential Gain and Differential Phase

Composite video signals contain intensity, color, hue, timing and audio information in AM, FM, and Phase Modulation. These video signals pass through many stages during their production, processing, archiving and transmission. It is important that each stage not corrupt these signals to provide a "high fidelity" image to the end viewer.

An industry standard way of measuring the distortion of a video component (or system) is to measure the amount of differential gain and phase error it introduces. A 100mV peak to peak sine wave at 3.58MHz for NTSC (4.3MHz for PAL), with 0V DC component serves as the reference. The reference signal is added to a DC offset, shifting the sine wave from 0V to 0.7V which is then applied to the device under test (DUT). The output signal from the DUT is compared to the reference signal. The Differential Gain is a measure of the change in amplitude of the sine wave and is measured in percent. The Differential Phase is a measure of the change in the phase of the sine wave and is measured in degrees. Typically, the maximum positive and negative deviations are summed to give peak differential gain and differential phase errors. The test setup in Figure 1 was used to characterize the EL2030. For higher than NTSC and PAL frequencies, an alternate Differential Gain and Phase measurement can be made using an HP3577A Network Analyzer and the setup shown in Figure 2. The frequency response is normalized to gain or phase with 0V DC at the input. From the normalized value a DC offset voltage is introduced and the Differential Gain or Phase is the deviation from the normalized value.

#### Video Applications

The video signals that must be transmitted for modest distances are usually amplified by a device such as the EL2030 and carried via coax cable. There are at least two ways to drive cables, single terminated and double terminated.

When driving a cable, it is important to terminate it properly to avoid unwanted signal reflections. Single termination (75 $\Omega$  to ground at receive end) may be sufficient for less demanding applications. In general, a double terminated cable (75 $\Omega$  in series at drive end and 75 $\Omega$  to ground at receive end) is preferred since the impedance match at both ends of the line will absorb signal reflections. However, when double termination is used (a total impedance of 150 $\Omega$ ), the received signal is reduced by half; therefore, the amplifier is usually set at a gain of 2 or higher to compensate for attenuation.

Video signals are 1V peak-peak in amplitude, from sync tip to peak white. There are 100 IRE (0.714V) of picture (from black to peak white of the transmitted signal) and 40 IRE (0.286V) of sync in a composite video signal (140 IRE = 1V).

For video applications where a gain of two is used (double termination), the output of the video amplifier will be a maximum of 2V peak-peak. With ±5V power supply, the EL2030 output swing of 3.5V is sufficient to satisfy the video output swing requirements. The EL2030 can drive two double terminated coax cables under these conditions. With ±15V supplies, driving four double terminated cables is feasible.

Although the EL2030's video characteristics (differential gain and phase) are impressive with  $\pm 5$ V supplies at NTSC and PAL frequencies, it can be optimized when the supplies are increased to  $\pm 15$ V, especially at 30MHz HDTV applications. This is primarily due to a reduction in internal parasitic junction capacitance with increased power supply voltage.

The following table summarizes the behavior of the EL2030 at  $\pm 5$ V and  $\pm 15$ V for NTSC. In addition, 30MHz HDTV data is included. Refer to the differential gain and phase typical performance curves for more data.

| ±۷ <sub>S</sub> | RLOAD | Α <sub>V</sub> | GAIN  | PHASE | COMMENTS                |

|-----------------|-------|----------------|-------|-------|-------------------------|

| 15V             | 75Ω   | 1              | 0.02% | 0.03° | Single terminated       |

| 15V             | 150Ω  | 1              | 0.02% | 0.02° | Double terminated       |

| 5V              | 150Ω  | 1              | 0.05% | 0.02° | Double terminated       |

| 15V             | 75Ω   | 2              | 0.02% | 0.08° | Single terminated       |

| 15V             | 150Ω  | 2              | 0.01% | 0.02° | Double terminated       |

| 5V              | 150Ω  | 2              | 0.03% | 0.09° | Double terminated       |

| 15V             | 150Ω  | 2              | 0.05% | 0.02° | HDTV, Double terminated |

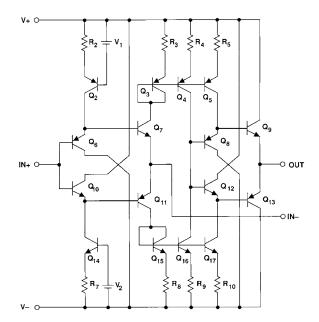

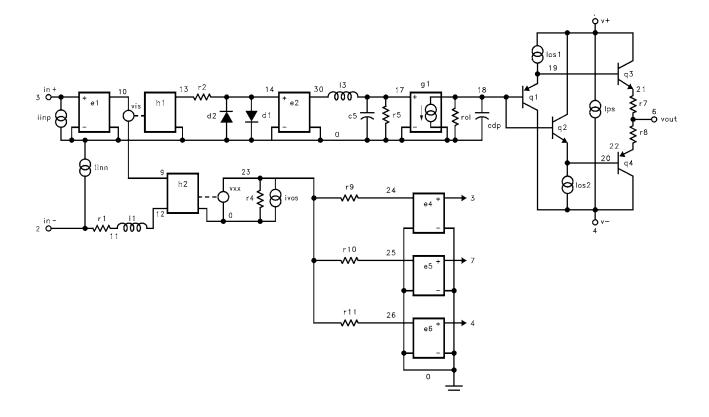

### **Equivalent Circuit**

### EL2030 Macromodel

```

* Revision A. March 1992

* Enhancements include PSRR, CMRR, and Slew Rate Limiting

* Connections:

+input

-input

+Vsupply

-Vsupply

output

.subckt M2030

3

2

7

6

* Input Stage

e1 10 0 3 0 1.0

vis 10 9 0V

h2 9 12 vxx 1.0

r1 2 11 50

I1 11 12 48nH

iinp 3 0 5µA

iinm 2 0 10µA

r12 3 0 2Meg

* Slew Rate Limiting

h1 13 0 vis 600

r2 13 14 1K

d1 14 0 dclamp

d2 0 14 dclamp

* High Frequency Pole

*e2 30 0 14 0 0.00166666666

13 30 17 0.5µH

c5 17 0 1pF

r5 17 0 500

* Transimpedance Stage

g1 0 18 17 0 1.0

rol 18 0 150K

cdp 18 0 2.8pF

* Output Stage

q1 4 18 19 qp

q2 7 18 20 qn

q3 7 19 21 qn

q4 4 20 22 qp

r7 21 6 4

r8 22 6 4

ios1 7 19 2.5mA

ios2 20 4 2.5mA

* Supply Current

ips 7 4 9mA

* Error Terms

ivos 0 23 5mA

```

### EL2030 Macromodel (Continued)

```

vxx 23 0 0V

e4 24 3 1.0

e5 25 0 7 0 1.0

e6 26 0 4 0 1.0

r9 24 23 3K

r10 25 23 1K

r11 26 23 1K

*

* Models

*

.model qn npn (is=5e-15 bf=100 tf=0.1nS)

.model qp pnp (is=5e-15 bf=100 tf=0.1nS)

.model dclamp d(is=1e-30 ibv=0.266 bv=3.7 n=4)

.ends

```

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com