## **LP3986**

# Dual Micropower 150 mA Ultra Low-Dropout CMOS Voltage Regulators in micro SMD Package

# **General Description**

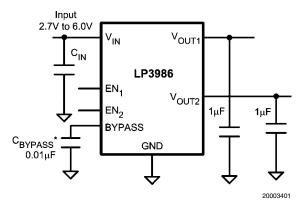

The LP3986 is a 150 mA dual low dropout regulator designed for portable and wireless applications with demanding performance and board space requirements.

The LP3986 is stable with a small 1  $\mu$ F  $\pm 30\%$  ceramic output capacitor requiring smallest possible board space.

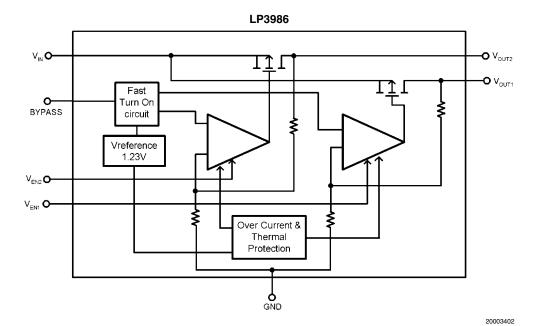

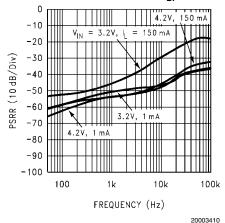

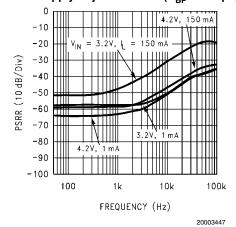

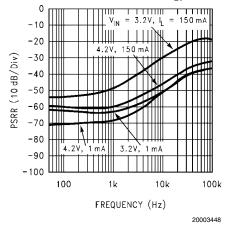

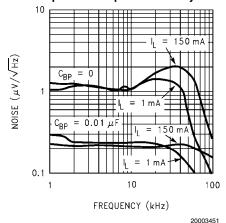

The LP3986's performance is optimized for battery powered systems to deliver ultra low noise, extremely low dropout voltage and low quiescent current independent of load current. Regulator ground current increases very slightly in dropout, further prolonging the battery life. Optional external bypass capacitor reduces the output noise further without slowing down the load transient response. Fast start-up time is achieved by utilizing a speed-up circuit that actively precharges the bypass capacitor. Power supply rejection is better than 60 dB at low frequencies and 55 dB at 10 kHz. High power supply rejection is maintained at low input voltage levels common to battery operated circuits.

The LP3986 is available in a micro SMD package. Performance is specified for a  $-40^{\circ}$ C to  $+125^{\circ}$ C temperature range. For single LDO applications, please refer to the LP3985 datasheet.

## **Features**

- Miniature 8-I/O micro SMD package

- Stable with 1µF ceramic and high quality tantalum output capacitors

- Fast turn-on

- Two independent regulators

- Logic controlled enable

- Over current and thermal protection

## **Key Specifications**

- Guaranteed 150 mA output current per regulator

- 1nA typical quiescent current when both regulators in shutdown mode

- 60 mV typical dropout voltage at 150 mA output current

- 115 µA typical ground current

- 40 µV typical output noise

- 200 µs fast turn-on circuit

- -40°C to +125°C junction temperature

# **Applications**

- CDMA cellular handsets

- GSM cellular handsets

- Portable information appliances

- Portable battery applications

# **Typical Application Circuit**

# **Block Diagram**

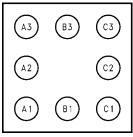

# **Pin Descriptions**

| Name              | *micro SMD Function               |                                  |

|-------------------|-----------------------------------|----------------------------------|

| V <sub>OUT2</sub> | A1                                | Output Voltage of the second LDO |

| EN <sub>2</sub>   | B1 Enable input for the second LD |                                  |

| BYPASS            | C1                                | Bypass capacitor for the bandgap |

| GND               | C2                                | Common ground                    |

| GND               | C3                                | Common ground                    |

| EN <sub>1</sub>   | B3                                | Enable input for the first LDO   |

| V <sub>OUT1</sub> | А3                                | Output Voltage of the first LDO  |

| V <sub>IN</sub>   | A2                                | Common input for both LDOs       |

<sup>\*</sup> Note: The pin numbering scheme for the micro SMD package was revised in April 2002 to conform to JEDEC standard. Only the pin numbers were revised. No changes to the physical location of the inputs/outputs were made. For reference purposes, the obsolete numbering scheme had  $V_{OUT2}$  as pin 1,  $EN_2$  as pin 2, BYPASS as pin 3, GND as pins 4 and 5,  $EN_1$  as pin 6,  $V_{OUT1}$  as pin 7, and  $V_{IN}$  as pin 8.

# **Connection Diagram**

20003404

Top View 8 Bump micro SMD Package See NS Package Number TLA08

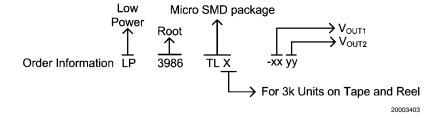

# **Ordering Information**

## For micro SMD Package (TL has thickness of 0.600mm)

| Output Voltage<br>(V) | Grade | Package<br>Marking | LP3986 Supplied as 250 Units, Tape and Reel | LP3986 Supplied as 3000 Units,<br>Tape and Reel |

|-----------------------|-------|--------------------|---------------------------------------------|-------------------------------------------------|

| 2.5 2.5               | STD   | 27                 | LP3986TL-2525                               | LP3986TLX-2525                                  |

| 2.5 2.8               | STD   | 14                 | LP3986TL-2528                               | LP3986TLX-2528                                  |

| 2.5 1.8               | STD   | 30                 | LP3986TL-2518                               | LP3986TLX-2518                                  |

| 2.6 2.6               | STD   | 28                 | LP3986TL-2626                               | LP3986TLX-2626                                  |

| 2.8 1.8               | STD   | 25                 | LP3986TL-2818                               | LP3986TLX-2818                                  |

| 2.8 2.8               | STD   | 10                 | LP3986TL-2828                               | LP3986TLX-2828                                  |

| 2.85 2.85             | STD   | 11                 | LP3986TL-285285                             | LP3986TLX285285                                 |

| 2.9 2.9               | STD   | 15                 | LP3986TL-2929                               | LP3986TLX-2929                                  |

| 3.0 2.8               | STD   | 26                 | LP3986TL-3028                               | LP3986TLX-3028                                  |

| 3.0 3.0               | STD   | 12                 | LP3986TL-3030                               | LP3986TLX-3030                                  |

| 3.1 3.1               | STD   | 13                 | LP3986TL-3131                               | LP3986TLX-3131                                  |

| 3.1 3.3               | STD   | 16                 | LP3986TL-3133                               | LP3986TLX-3133                                  |

| 3.3 3.3               | STD   | 17                 | LP3986TL-3333                               | LP3986TLX-3333                                  |

# **Absolute Maximum Ratings** (Notes 1, 2)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

$\begin{array}{ccc} V_{\text{IN}}, V_{\text{EN}} & -0.3 \text{ to } 6.5 \text{V} \\ V_{\text{OUT}} & -0.3 \text{ to } (V_{\text{IN}} + 0.3 \text{V}) \leq 6.5 \text{V} \\ \text{Junction Temperature} & 150^{\circ}\text{C} \\ \text{Storage Temperature} & -65^{\circ}\text{C to } +150^{\circ}\text{C} \\ \text{Pad Temp. (Note 3)} & 235^{\circ}\text{C} \end{array}$

Maximum Power Dissipation (Note

4) 364mW

ESD Rating (Note 5)

Human Body Model 2kV

Machine Model 200V

# Operating Ratings (Notes 1, 2)

$V_{IN}$  2.7 to 6V  $V_{EN}$  0 to  $(V_{IN} + 0.3V) \le 6V$  Junction Temperature  $-40^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$  Thermal Resistance

$\theta_{JA}$  220°C/W Maximum Power Dissipation (Note 6) 250mW

## **Electrical Characteristics**

Unless otherwise specified:  $V_{IN} = V_{OUT(nom)} + 0.5V$ ,  $C_{IN} = 1~\mu F$ ,  $I_{OUT} = 1 mA$ ,  $C_{OUT} = 1~\mu F$ ,  $C_{BYPASS} = 0.01 \mu F$ . Typical values and limits appearing in standard typeface are for  $T_J = 25^{\circ}C$ . Limits appearing in **boldface type** apply over the entire junction temperature range for operation,  $-40^{\circ}C$  to  $+125^{\circ}C$ . (Notes 7, 8)

| Symbol                       | Parameter                       | Conditions                                                                             | Тур       | Limit               |                       | Units                |

|------------------------------|---------------------------------|----------------------------------------------------------------------------------------|-----------|---------------------|-----------------------|----------------------|

|                              |                                 |                                                                                        |           | Min                 | Max                   | Units                |

|                              | Output Voltage<br>Tolerance     | I <sub>OUT</sub> = 1mA                                                                 |           | -2.5<br><b>-3.0</b> | 2.5<br><b>3.0</b>     | % of V <sub>OL</sub> |

| $\Delta V_{OUT}$             | Line Regulation Error (Note 9)  | $V_{IN} = (V_{OUT(nom)} + 0.5V)$ to 6.0V,<br>$I_{OUT} = 1 \text{ mA}$                  | 0.006     |                     | 0.092<br><b>0.128</b> | %/V                  |

|                              | Load Regulation Error (Note 10) | I <sub>OUT</sub> = 1mA to 150 mA                                                       | 0.003     |                     | 0.006<br><b>0.01</b>  | %/mA                 |

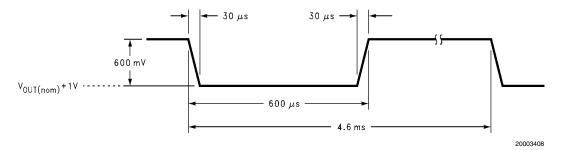

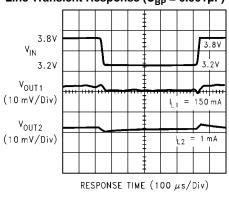

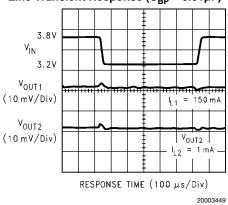

|                              | Output AC Line Regulation       | $V_{IN} = V_{OUT(nom)} + 1V,$<br>$I_{OUT} = 150 \text{ mA } (Figure 1)$                | 1.5       |                     |                       | mV <sub>P-P</sub>    |

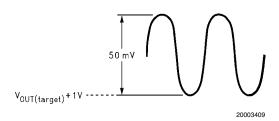

| PSRR I                       | Power Supply Rejection<br>Ratio | V <sub>IN</sub> = 3.1V,<br>f = 1 kHz,<br>I <sub>OUT</sub> = 50 mA ( <i>Figure 2</i> )  | 60        |                     |                       | dB                   |

|                              |                                 | V <sub>IN</sub> = 3.1V,<br>f = 10 kHz,<br>I <sub>OUT</sub> = 50 mA ( <i>Figure 2</i> ) | 50        |                     |                       |                      |

| I <sub>Q</sub> Quiescent Cui | Quiescent Current               | Both Regulators ON<br>V <sub>EN</sub> = 1.4V, I <sub>OUT</sub> = 0 mA                  | 115       |                     | 200                   | μΑ                   |

|                              |                                 | Both Regulators ON<br>V <sub>EN</sub> = 1.4V, I <sub>OUT</sub> = 0 to 150 mA           | 220       |                     | 320                   |                      |

|                              |                                 | One Regulator ON<br>V <sub>EN</sub> = 1.4V I <sub>OUT</sub> = 0 mA                     | 75        |                     | 130                   |                      |

|                              |                                 | One Regulator ON<br>V <sub>EN</sub> = 1.4V I <sub>OUT</sub> = 0 to 150 mA              | 130       |                     | 200                   |                      |

|                              |                                 | V <sub>EN</sub> = 0.4V, Both Regulators OFF (shutdown)                                 | 0.001     |                     | 2<br><b>4</b>         |                      |

|                              | Dropout Voltage<br>(Note 11)    | $I_{OUT} = 1 \text{ mA}$<br>$I_{OUT} = 150 \text{ mA}$                                 | 0.4<br>60 |                     | 2<br>100              | mV                   |

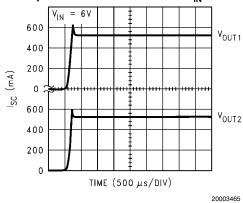

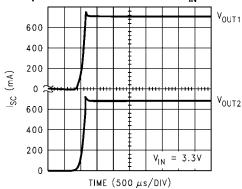

| SC                           | Short Circuit Current Limit     | Output Grounded                                                                        | 600       |                     |                       | mA                   |

| OUT(PK)                      | Peak Output Current(Note 15)    | V <sub>OUT</sub> ≥ V <sub>OUT(nom)</sub> - 5%                                          | 500       | 300                 |                       | mA                   |

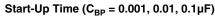

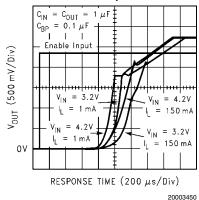

| Γ <sub>ON</sub>              | Turn-On Time<br>(Note 12)       | $C_{\text{BYPASS}} = 0.01 \ \mu\text{F}$                                               | 200       |                     |                       | μs                   |

| P <sub>n</sub>               | Output Noise Voltage            | BW = 10 Hz to 100 kHz,<br>$C_{OUT} = 1\mu F$                                           | 40        |                     |                       | μVrms                |

| Symbol           | Parameter                                 | Conditions                                                                                                                                                                                                | Тур        | Limit |     |        |

|------------------|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------|-----|--------|

|                  |                                           |                                                                                                                                                                                                           |            | Min   | Max | Units  |

| ρn(1/f)          | Output Noise Density                      | $f = 120 \text{ Hz},$ $C_{OUT} = 1\mu\text{F}$                                                                                                                                                            | 1          |       |     | μV/√Hz |

| I <sub>EN</sub>  | Maximum Input Current at EN               | V <sub>EN</sub> = 0.4 and V <sub>IN</sub> = 6V                                                                                                                                                            | ±10        |       |     | nA     |

| V <sub>IL</sub>  | Maximum Low Level Input<br>Voltage at EN  | V <sub>IN</sub> = 2.7 to 6V                                                                                                                                                                               |            |       | 0.4 | V      |

| V <sub>IH</sub>  | Minimum High Level Input<br>Voltage at EN | V <sub>IN</sub> = 2.7 to 6V                                                                                                                                                                               |            | 1.4   |     | V      |

| Xtalk            | Crosstalk Rejection                       | $\Delta I_{Load1} = 150$ mA at 1KHz rate $\Delta I_{Load2} = 1$ mA $\Delta V_{OUT2}/\Delta V_{OUT1}$ $\Delta I_{Load2} = 150$ mA at 1KHz rate $\Delta I_{Load1} = 1$ mA $\Delta V_{OUT2}/\Delta V_{OUT1}$ | -60<br>-60 |       |     | - dB   |

|                  |                                           | All $V_{OUT} > = 2.5V$ ,                                                                                                                                                                                  |            | 1     |     | μF     |

| C <sub>IN</sub>  | Input capacitance(Note 13)                | If $V_{OUT} = 1.8V$ ,<br>$V_{IN\_MIN} = 2.9V$                                                                                                                                                             |            | 4.7   |     | μF     |

| C <sub>OUT</sub> | Capacitance(Note 13)                      | $AII V_{OUT} > = 2.5V,$                                                                                                                                                                                   |            | 1     | 22  | μF     |

|                  |                                           | If $V_{OUT} = 1.8V$ ,<br>$V_{IN\_MIN} >= 2.9V$                                                                                                                                                            |            | 2.2   | 22  | μF     |

|                  | ESR                                       | (Note 14)                                                                                                                                                                                                 |            | 5     | 500 | mΩ     |

**Note 1:** Absolute Maximum Ratings are limits beyond which damage to the device may occur. Operating Ratings are conditions under which operation of the device is guaranteed. Operating Ratings do not imply guaranteed performance limits. For guaranteed performance limits and associated test conditions, see the Electrical Characteristics tables.

Note 2: All voltages are with respect to the potential at the GND pin.

Note 3: Additional information on pad temperature can be found in National Semiconductor Application Note (AN-1112).

Note 4: The Absolute Maximum power dissipation depends on the ambient temperature and can be calculated using the formula:

$$P_{D} = (T_{J} - T_{A})/\theta_{JA},$$

Where  $T_J$  is the junction temperature,  $T_A$  is the ambient temperature, and  $\theta_{JA}$  is the junction-to-ambient thermal resistance. The 364mW rating appearing under Absolute Maximum Ratings results from substituting the Absolute Maximum junction temperature, 150°C, for  $T_J$ , 70°C for  $T_A$ , and 220°C/W for  $\theta_{JA}$ . More power can be dissipated safely at ambient temperatures below 70°C. Less power can be dissipated safely at ambient temperatures above 70°C. The Absolute Maximum power dissipation can be increased by 4.5mW for each degree below 70°C, and it must be derated by 4.5mW for each degree above 70°C.

Note 5: The human body model is 100pF discharged through a 1.5kΩ resistor into each pin. The machine model is a 200pF capacitor discharged directly into each pin.

Note 6: Like the Absolute Maximum power dissipation, the maximum power dissipation for operation depends on the ambient temperature. The 250mW rating appearing under Operating Ratings results from substituting the maximum junction temperature for operation,  $125^{\circ}$ C, for  $T_J$ ,  $70^{\circ}$ C for  $T_A$ , and  $220^{\circ}$ C/W for  $\theta_{JA}$  into (1) above. More power can be dissipated at ambient temperatures below  $70^{\circ}$ C. Less power can be dissipated at ambient temperatures above  $70^{\circ}$ C. The maximum power dissipation for operation can be increased by 4.5mW for each degree below  $70^{\circ}$ C, and it must be derated by 4.5mW for each degree above  $70^{\circ}$ C.

Note 7: All limits are guaranteed. All electrical characteristics having room temperature limits are tested during production with  $T_J = 25^{\circ}$ C or correlated using Statistical Quality Control (SQC) methods. All hot and cold limits are guaranteed by correlating the electrical characteristics to process and temperature variations and applying statistical process control.

Note 8: The target output voltage, which is labeled  $V_{OUT(nom)}$ , is the desired voltage option.

Note 9: The output voltage changes slightly with line voltage. An increase in the line voltage results in a slight increase in the output voltage and vice versa.

Note 10: The output voltage changes slightly with load current. An increase in the load current results in a slight decrease in the output voltage and vice versa. Tested limit applies to Vout 's of 2.5V and greater.

Note 11: Dropout voltage is the input-to-output voltage difference at which the output voltage is 100mV below its nominal value.

Note 12: Turn-on time is that between the enable input just exceeding V<sub>IH</sub> and the output voltage just reaching 95% of its nominal value.

Note 13: Range of capacitor values for which the device will remain stable. This electrical specification is guaranteed by design.

Note 14: Range of capacitor ESR values for which the device will remain stable. This electrical specification is guaranteed by design.

Note 15:  $I_{\mbox{\scriptsize PEAK}}$  guaranteed for Vout 's of 2.5V and greater.

# **Test Signals**

FIGURE 1. Line Regulation Input Test Signal

FIGURE 2. PSRR Input Test Signal

$\begin{tabular}{ll} \textbf{Typical Performance Characteristics} \\ \textbf{F, V}_{IN} = \textbf{V}_{OUT} + 0.5, \textbf{T}_{A} = 25^{\circ}\text{C, both enable pins are tied to V}_{IN} \end{tabular} \label{eq:continuous} \begin{tabular}{ll} \textbf{Unless otherwise specified, C}_{IN} = \textbf{C}_{OUT} \ 1 \mu \textbf{F Ceramic, C}_{BP} = 0.01 \mu \ \textbf{E}_{OUT} + 0.5, \textbf{C}_{A} = 25^{\circ}\text{C, both enable pins are tied to V}_{IN} \end{tabular}$

## Power Supply Rejection Ratio ( $C_{BP} = 0.001 \mu F$ )

## Power Supply Rejection Ratio ( $C_{BP} = 0.01 \mu F$ )

#### Power Supply Rejection Ratio ( $C_{BP} = 0.1 \mu F$ )

#### **Output Noise Spectral Density**

## Line Transient Response ( $C_{BP} = 0.001 \mu F$ )

## Line Transient Response ( $C_{BP} = 0.01 \mu F$ )

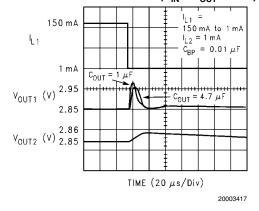

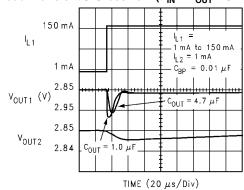

## Load Transient & Cross Talk ( $V_{IN} = V_{OUT} + 0.2V$ )

## Load Transient & Cross Talk ( $V_{IN} = V_{OUT} + 0.2V$ )

20003416

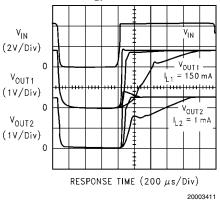

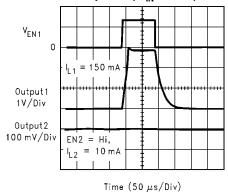

## Enable Response ( $V_{IN} = 4.2V$ )

20003414

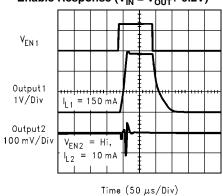

## Enable Response ( $V_{IN} = V_{OUT} + 0.2V$ )

**Enable Response**

Output Short Circuit Current at  $V_{IN} = 6V$

20003415

Output Short Circuit Current at  $V_{\rm IN}$  = 3.3V

20003466

# **Application Hints**

#### **EXTERNAL CAPACITORS**

Like any low-dropout regulator, the LP3986 requires external capacitors for regulator stability. The LP3986 is specifically designed for portable applications requiring minimum board space and smallest components. These capacitors must be correctly selected for good performance.

#### **INPUT CAPACITOR**

An input capacitance of  $\cong 1\mu F$  is required between the LP3986 input pin and ground (the amount of the capacitance may be increased without limit).

This capacitor must be located a distance of not more than 1cm from the input pin and returned to a clean analog ground. Any good quality ceramic, tantalum, or film capacitor may be used at the input.

**Important:** Tantalum capacitors can suffer catastrophic failures due to surge current when connected to a low-impedance source of power (like a battery or a very large capacitor). If a tantalum capacitor is used at the input, it must be guaranteed by the manufacturer to have a surge current rating sufficient for the application.

There are no requirements for the ESR on the input capacitor, but tolerance and temperature coefficient must be considered when selecting the capacitor to ensure the capacitance will be  $\approx 1 \mu F$  over the entire operating temperature range.

#### **OUTPUT CAPACITOR**

The LP3986 is designed specifically to work with very small ceramic output capacitors, any ceramic capacitor (temperature characteristics X7R, X5R, Z5U or Y5V) in 1 to 22  $\mu F$  range with  $5m\Omega$  to  $500m\Omega$  ESR range is suitable in the LP3986 application circuit.

It may also be possible to use tantalum or film capacitors at the output, but these are not as attractive for reasons of size and cost (see next section Capacitor Characteristics).

The output capacitor must meet the requirement for minimum amount of capacitance and also have an ESR (Equivalent Series Resistance) value which is within a stable range.

#### **NO-LOAD STABILITY**

The LP3986 will remain stable and in regulation with no-load (other than the internal voltage divider). This is specially important in CMOS RAM keep-alive applications.

#### **CAPACITOR CHARACTERISTICS**

The LP3986 is designed to work with ceramic capacitors on the output to take advantage of the benefits they offer: for capacitance values in the range of  $1\mu F$  to  $4.7\mu F$  range, ceramic capacitors are the smallest, least expensive and have the lowest ESR values (which makes them best for eliminating high frequency noise). The ESR of a typical  $1\mu F$  ceramic capacitor is in the range of 20 m $\Omega$  to 40 m $\Omega$ , which easily meets the ESR requirement for stability by the LP3986.

The ceramic capacitor's capacitance can vary with temperature. The capacitor type X7R, which operates over a temperature range of -55°C to +125°C, will only vary the capacitance to within  $\pm 15\%$ . Most large value ceramic capacitors ( $\approxeq 2.2\mu\text{F})$  are manufactured with Z5U or Y5V temperature characteristics. Their capacitance can drop by more than 50% as the temperature goes from 25°C to 85°C. Therefore, X7R is recommended over Z5U and Y5 in applications where the ambient temperature will change significantly above or below 25°C.

Tantalum capacitors are less desirable than ceramic for use as output capacitors because they are more expensive when comparing equivalent capacitance and voltage ratings in the  $1\mu F$  to  $4.7\mu F$  range.

Another important consideration is that tantalum capacitors have higher ESR values than equivalent size ceramics. This means that while it may be possible to find a tantalum capacitor with an ESR value within the stable range, it would have to be larger in capacitance (which means bigger and more costly) than a ceramic capacitor with the same ESR value. It should also be noted that the ESR of a typical tantalum will increase about 2:1 as the temperature goes from 25°C down to -40°C, so some guard band must be allowed.

#### **NOISE BYPASS CAPACITOR**

Connecting a 0.01  $\mu$ F capacitor between the  $C_{BYPASS}$  pin and ground significantly reduces noise on the regulator output. This cap is connected directly to a high impedance node in the band gap reference circuit. Any significant loading on this node will cause a change on the regulated output voltage. For this reason, DC leakage current through this pin must be kept as low as possible for best output voltage accuracy. The use of this  $0.01\mu$ F bypass capacitor is strongly recommended to prevent overshoot on the output during start up.

The types of capacitors best suited for the noise bypass capacitor are ceramic and film. High-quality ceramic capacitors with either NPO or COG dielectric typically have very low leakage. Polypropolene and polycarbonate film capacitors are available in small surface-mount packages and typically have extremely low leakage current.

Unlike many other LDO's, addition of a noise reduction capacitor does not effect the transient response of the device.

#### **ON/OFF INPUT OPERATION**

The LP3986 is turned off by pulling the V $_{\rm EN}$  pin low, and turned on by pulling it high. If this feature is not used, the V $_{\rm EN}$  pin should be tied to V $_{\rm IN}$  to keep the regulator output on at all times. To assure proper operation, the signal source used to drive the V $_{\rm EN}$  input must be able to swing above and below the specified turn-on/off voltage thresholds listed in the Electrical Characteristics section under V $_{\rm IL}$  and V $_{\rm IH}$ .

#### **FAST ON-TIME**

The LP3986 outputs are turned on after  $V_{ref}$  voltage reaches its final value (1.23V nominal). To speed up this process, the noise reduction capacitor at the bypass pin is charged with an internal 70 $\mu$ A current source. The current source is turned off when the bandgap voltage reaches approximately 95% of its final value. The turn on time is determined by the time constant of the bypass capacitor. The smaller the capacitor value, the shorter the turn on time, but less noise gets reduced. As a result, turn on time and noise reduction need to be taken into design consideration when choosing the value of the bypass capacitor.

#### MICRO SMD MOUNTING

The micro SMD package requires specific mounting techniques which are detailed in National Semiconductor Application Note (AN-1112). Referring to the section *Surface Mount Technology (SMT) Assembly Considerations*.

For best results during assembly, alignment ordinals on the PC board may be used to facilitate placement of the micro SMD device.

#### MICRO SMD LIGHT SENSITIVITY

Exposing the micro SMD device to direct sunlight will cause misoperation of the device. Light sources such as halogen lamps can effect electrical performance if brought near to the device.

The wavelengths which have most detrimental effect are reds and infra-reds, which means that the fluorescent lighting used

inside most buildings has very little effect on performance. A micro SMD test board was brought to within 1cm of a fluorescent desk lamp and the effect on the regulated output voltage was negligible, showing a deviation of less than 0.1% from nominal.

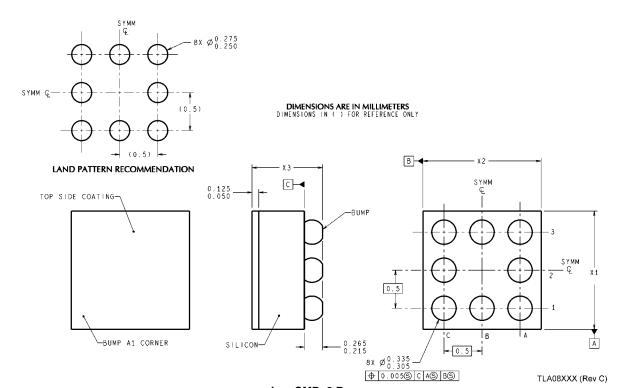

# Physical Dimensions inches (millimeters) unless otherwise noted

micro SMD, 8 Bump

NS Package Number TL08CCA

The dimensions for X11, X2 and X3 are as follows:

X1 = 1.55mm X2 = 1.55mm X3 = 0.600mm

# **Notes**

THE CONTENTS OF THIS DOCUMENT ARE PROVIDED IN CONNECTION WITH NATIONAL SEMICONDUCTOR CORPORATION ("NATIONAL") PRODUCTS. NATIONAL MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE ACCURACY OR COMPLETENESS OF THE CONTENTS OF THIS PUBLICATION AND RESERVES THE RIGHT TO MAKE CHANGES TO SPECIFICATIONS AND PRODUCT DESCRIPTIONS AT ANY TIME WITHOUT NOTICE. NO LICENSE, WHETHER EXPRESS, IMPLIED, ARISING BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT.

TESTING AND OTHER QUALITY CONTROLS ARE USED TO THE EXTENT NATIONAL DEEMS NECESSARY TO SUPPORT NATIONAL'S PRODUCT WARRANTY. EXCEPT WHERE MANDATED BY GOVERNMENT REQUIREMENTS, TESTING OF ALL PARAMETERS OF EACH PRODUCT IS NOT NECESSARILY PERFORMED. NATIONAL ASSUMES NO LIABILITY FOR APPLICATIONS ASSISTANCE OR BUYER PRODUCT DESIGN. BUYERS ARE RESPONSIBLE FOR THEIR PRODUCTS AND APPLICATIONS USING NATIONAL COMPONENTS. PRIOR TO USING OR DISTRIBUTING ANY PRODUCTS THAT INCLUDE NATIONAL COMPONENTS, BUYERS SHOULD PROVIDE ADEQUATE DESIGN, TESTING AND OPERATING SAFEGUARDS.

EXCEPT AS PROVIDED IN NATIONAL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NATIONAL ASSUMES NO LIABILITY WHATSOEVER, AND NATIONAL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE AND/OR USE OF NATIONAL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other brand or product names may be trademarks or registered trademarks of their respective holders.

Copyright© 2007 National Semiconductor Corporation

For the most current product information visit us at www.national.com

National Semiconductor Americas Customer Support Center Email:

new.feedback@nsc.com Tel: 1-800-272-9959

**National Semiconductor Europe Customer Support Center** Fax: +49 (0) 180-530-85-86

Email: europe.support@nsc.com Deutsch Tel: +49 (0) 69 9508 6208 English Tel: +49 (0) 870 24 0 2171 Français Tel: +33 (0) 1 41 91 8790

**National Semiconductor Asia** Pacific Customer Support Center Email: ap.support@nsc.com

National Semiconductor Japan **Customer Support Center** Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560