# MOS INTEGRATED CIRCUIT μ**PD72001-11, 72001-A8**

# MULTI-PROTOCOL SERIAL CONTROLLERS

# DESCRIPTION

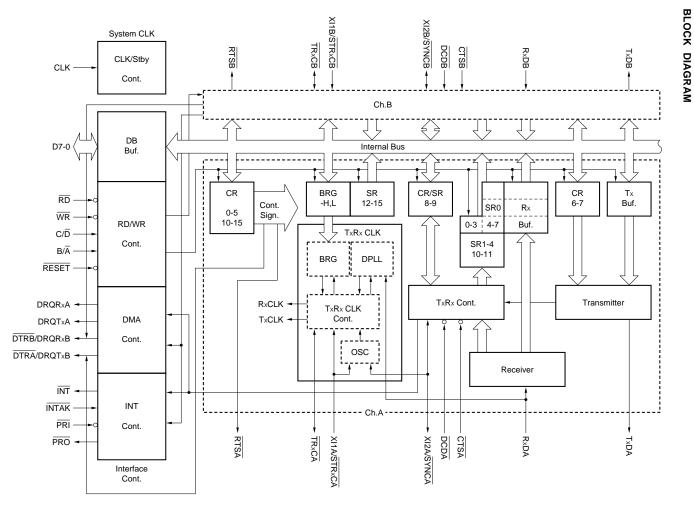

The  $\mu$ PD72001-11 is an MPSC (Multi-Protocol Serial Controller) which is a general-purpose communication LSI equipped with two sets of bidirectional parallel/serial converter circuits for data communication. This controller has a transmitter function to convert the parallel data output by a data terminal into serial data and transmit this data to a data transmission system such as a modem, and a receiver function to convert the serial data output by the data transmission system into parallel data.

The MPSC can be used with data communications equipment with a variety of communication modes such as the generally and widely used start-stop synchronization mode, and the HDLC mode which is used for high-speed communication.

The  $\mu$ PD72001-A8 is a low-voltage model.

For this product, the following documents are separately available. Read these documents as well as this Data Sheet.

- User's Manual (S12472E)

- (I) (S12753E)

- Application Notes

(II) (On preparation) (III) (On preparation)

# FEATURES

- Two sets of parallel/serial circuits supporting three modes: start-stop synchronization, character synchronization, and bit synchronization modes

- → Easy application to a system supporting two or more communication protocols such as a protocol converter or ISDN terminal adapter

- DPLL (Digital Phase Locked Loop), baud rate generator, and crystal oscillation circuit for transmission/reception clock

- ightarrow Helps reduce cost by decreasing the number of external circuits

- Many variations with power-saving features and small package size

- $\rightarrow$  Easy application to portable terminals and high-accuracy portable terminals

The features common to the  $\mu$ PD72001-11 and 72001-A8 are explained as the features of the MPSC in this document.

The information in this document is subject to change without notice.

# ORDERING INFORMATION

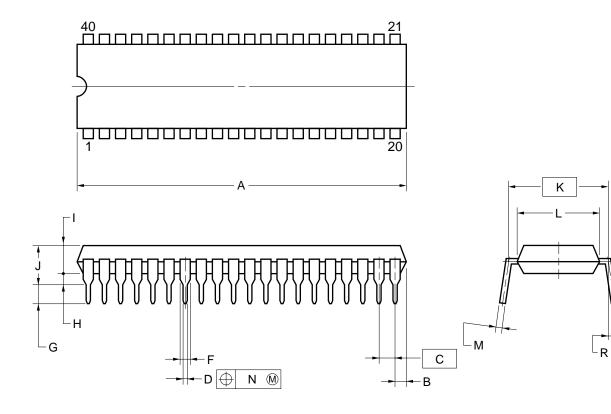

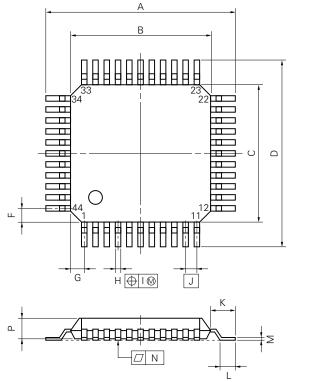

| Part Number       | Package                                                           |

|-------------------|-------------------------------------------------------------------|

| μPD72001C-11      | 40-pin plastic DIP (600 mil)                                      |

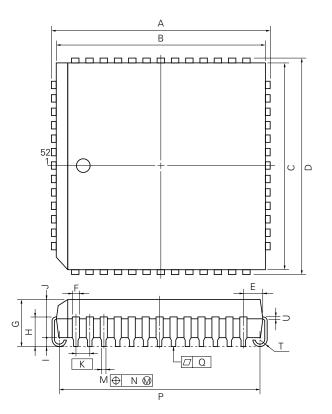

| μPD72001G-11-22   | 44-pin plastic QFP (10 $	imes$ 10 mm) (resin thickness: 1.45 mm)  |

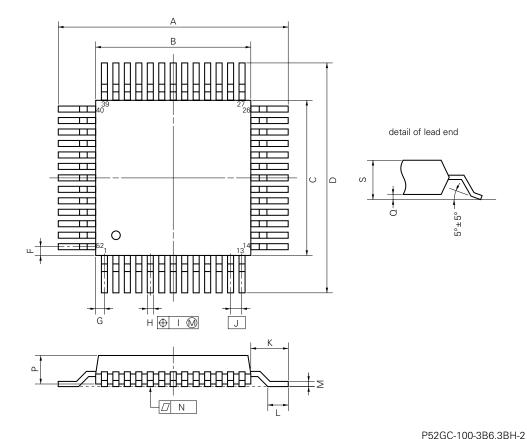

| μPD72001GC-11-3B6 | 52-pin plastic QFP (14 $	imes$ 14 mm) (resin thickness: 2.7 mm)   |

| μPD72001L-11      | 52-pin plastic QFJ (750 $	imes$ 750 mil)                          |

| μPD72001C-A8      | 40-pin plastic DIP (600 mil)                                      |

| μPD72001G-A8-22   | 44-pin plastic QFP (10 $	imes$ 10 mm) (resin thickness: 1.45 mm)  |

| μPD72001GC-A8-3B6 | 52-pin plastic QFP (14 $	imes$ 14 mm) (resin thickness: 2.7 mm)   |

| μPD72001G-A8-22   | 44-pin plastic QFP (10 $\times$ 10 mm) (resin thickness: 1.45 mm) |

# SPECIFICATIONS

| Item                   |                                                                                                                                      | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | cations                                                                                       |  |  |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|--|--|

| Part number            | μΡ[                                                                                                                                  | 072001-11                                                                                                                                                                                                                                                                                                                                                                                                                                                                | μPD72001-A8                                                                                   |  |  |

| Supply voltage         | 5 V ±10 %                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3.3 V ±0.3 V                                                                                  |  |  |

| System clock frequency | 11 MHz MAX.                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 8 MHz MAX. (at $T_A = -10$ to +70 °C)<br>7.14 MHz MAX. (at $T_A = -40$ to +85 °C)             |  |  |

| Maximum transfer rate  | 2.2 Mbps                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1.6 Mbps (at T <sub>A</sub> = -10 to +70 °C)<br>1.43 Mbps (at T <sub>A</sub> = -40 to +85 °C) |  |  |

| Process                | CMOS                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                               |  |  |

| Internal circuit       | Transmit buffer :<br>Receive buffer :<br>Interrupt control fu<br>DMA request sign<br>Overrun error dete<br>DPLL<br>Baud rate generat | Quadruple<br>unction<br>al output: 2 for transmissio<br>ection<br>for<br>circuit for transmission/red<br>function                                                                                                                                                                                                                                                                                                                                                        | on, 2 for reception                                                                           |  |  |

| Communication protocol | Start-stop<br>synchronization                                                                                                        | Character bit length: 5, 6, 7, 8<br>Stop bit length: 1, 1.5, 2<br>Clock rate: ×1, ×16, ×32, ×64<br>Parity generation, check<br>Framing error detection<br>Break generation, detection                                                                                                                                                                                                                                                                                    |                                                                                               |  |  |

|                        | COP<br>(Character<br>Oriented<br>Protocol)                                                                                           | Operation mode: Mono-sync, Bi-sync, External sync<br>Character bit length: 5, 6, 7, 8<br>SYNC character bit length: 6, 8<br>Character synchronization: Internal/external<br>BCS (Block Check Sequence) generation, check:<br>CRC-16<br>CRC-CCITT<br>Parity generation, check<br>SYNC character automatic transmission, detection, rejection                                                                                                                              |                                                                                               |  |  |

|                        | BOP<br>(Bit Oriented<br>Protocol)                                                                                                    | Operation mode:         HDLC (High-level Data Link Control)         SDLC (Synchronous Data Link Control)         SDLC Loop         Flag transmission, detection         Zero insertion, rejection         Address field detection (1 byte)         FCS (Frame Check Sequence) generation, detection         Short frame detection         Abort automatic transmission, detection         Idle detection         Go Ahead detection         Transmit number data control |                                                                                               |  |  |

| Processing data format | Encode/decode of                                                                                                                     | f NRZ (Non-Return to Zero<br>f NRZI (Non-Return to Zero<br>f FM (Frequency Modulatio                                                                                                                                                                                                                                                                                                                                                                                     | o Inverted)                                                                                   |  |  |

★

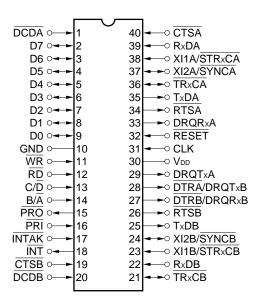

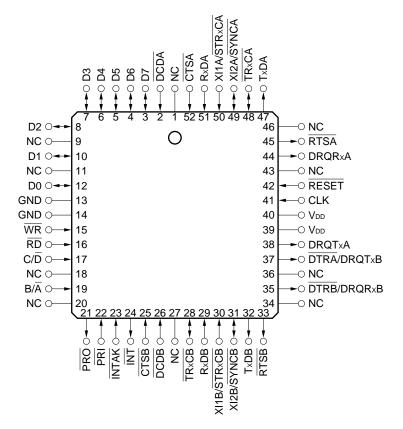

#### **PIN CONFIGURATION (Top View)**

• 40-pin plastic DIP (600 mil) : µPD72001C-11, µPD72001C-A8

• 44-pin plastic QFP (10  $\times$  10 mm) :  $\mu$ PD72001G-11-22,  $\mu$ PD72001G-A8-22

IC: Internally Connected (Leave this pin unconnected)

• 52-pin plastic QFP (14  $\times$  14 mm) :  $\mu$ PD72001GC-11-3B6,  $\mu$ PD72001GC-A8-3B6

- NC: No Connection

- IC : Internally Connected (Leave this pin unconnected.)

- + 52-pin plastic QFJ (750  $\times$  750 mil) :  $\,\mu\text{PD72001L-11}$

6

#### **1. PIN FUNCTIONS**

The functions of the MPSC can be broadly classified into "system interface functions" that control interfacing with the host system, and "transmission/reception functions" to transmit or receive data. This section explains the functions of the pins of the MPSC by classifying the pins into those related to system interfacing and those related to transmission and reception.

Hereafter, "H" (voltage level satisfying V<sub>IH</sub> in the case of an input pin, or voltage level satisfying V<sub>OH</sub> in the case of an output pin) and "L" (voltage level satisfying V<sub>IL</sub> in the case of an input pin, or voltage level satisfying V<sub>OL</sub> in the case of an output pin) are used to indicate the input/output status of a pin.

#### 1.1 Pins Related to System Interface

- (1) VDD Supply voltage pin

- (2) GND GND pin

#### (3) RESET ... Input

This pin inputs a signal from an external device to reset the MPSC. When "L" is input to this pin for the duration of 2 clock cycles ( $2t_{CYK}$ ) or longer, the MPSC is reset (this is called system reset).

As a result of system reset, the transmitter, receiver, and interrupt/DMA functions of the MPSC are disabled, and the TxD pin and general-purpose output pins go high. In this case, because all bits of the control register (CR) are also reset, CR must be set again if a system reset has been executed.

Table 1-1 shows the status of each pin at system reset, in comparison with the pin status at channel reset (CR0: D5, D4, D3 = "0, 1, 1").

The MPSC automatically enters the standby mode at system reset, lowering the power consumption from that in the normal operation mode.

|                                        |     | Pin                  | Status                 |

|----------------------------------------|-----|----------------------|------------------------|

| Pin Name                               | I/O | RESET (system reset) | Channel reset          |

| WR                                     | I   | _                    | -                      |

| RD                                     | I   | _                    | _                      |

| B/Ā                                    | I   | _                    | -                      |

| C/D                                    | I   | _                    | -                      |

| D7 to D0                               | I/O | -                    | -                      |

| INT                                    | 0   | High impedance       | High impedance         |

| INTAK                                  | I   | _                    | -                      |

| PRI                                    | I   | _                    | -                      |

| PRO                                    | 0   | Depends on PRI       | Depends on PRI         |

| DRQTxA                                 | 0   | "L"                  | "L"                    |

| DRQRxA                                 | 0   | "L"                  | "L"                    |

| DTRA/DRQT×B,<br>DTRB/DRQR×B            | 0   | DTR function, "H"    | Retains current status |

| TxDA, TxDB                             | 0   | "Н"                  | "H"                    |

| RxDA, RxDB                             | I   | _                    | -                      |

| TR×CA, TR×CB                           | I/O | Input status         | Retains current status |

| XI1A/STR×CA<br>XI1B/STR×CB             | I   | _                    | -                      |

| XI2A/ <mark>SYNCA</mark><br>XI2B/SYNCB | I/O | Input status         | Retains current status |

| RTSA, RTSB                             | 0   | "Н"                  | "H"                    |

| CTSA, CTSB                             | I   | -                    | -                      |

| DCDA, DCDB                             | I   | _                    | -                      |

#### Table 1-1. Pin Status at Reset

- : Undefined

(4) CLK (System Clock) ... Input

This pin inputs the system clock. The input frequency must be five times that of the data transfer rate or higher.

(5) WR (Write) ... Input

This pin inputs a write control signal for control words and transmit data. This pin is active-low.

(6) RD (Read) ... Input

This pin inputs a read control signal for status and receive data. This pin is active-low.

(7) B/A (Channel B/Channel A) ... Input

This pin inputs a signal to select a channel to be accessed when data is written or read. When this pin is "L", channel A is selected; when it is "H", channel B is selected.

(8) C/D (Control/Data) ... Input

This pin inputs a signal that determines the type of the data on the data bus when the data is written or read.

Table 1-2 shows the selection operations by  $\overline{WR}$ ,  $\overline{RD}$ ,  $B/\overline{A}$ , and  $C/\overline{D}$ .

| WR | RD | B/Ā | C/D |                | Operation                         |

|----|----|-----|-----|----------------|-----------------------------------|

| L  | н  | L   | L   | Channel A      | Writes transmit data to Tx buffer |

|    |    | н   |     | Channel B      |                                   |

| н  | L  | L   | L   | Channel A      | Reads receive data from Rx buffer |

|    |    | н   | ]   | Channel B      |                                   |

| L  | н  | L   | н   | Channel A      | Writes control register           |

|    |    | н   |     | Channel B      |                                   |

| н  | L  | L   | н   | Channel A      | Reads status register             |

|    |    | н   |     | Channel B      |                                   |

| н  | н  | ×   | ×   | High-impedan   | ce state or INTAK sequence        |

| L  | L  | ×   | ×   | Setting prohib | ited                              |

#### Table 1-2. MPSC Control Signals and Operations

×: Don's Care

#### (9) D7 through D0 (Data Bus) ... I/O

These pins constitute a three-state 8-bit bidirectional data bus. This data bus is connected to the data bus of the host processor to transfer control words, status, and transmit/receive data.

#### (10) INT (Interrupt) ... Output (open drain)

This pin outputs an interrupt request signal. If an interrupt occurs in the MPSC, it goes low (active). Because this is an open-drain output pin, it must be pulled up.

#### (11) INTAK (Interrupt Acknowledge) ... Input

This pin inputs a signal to acknowledge interrupt request signals issued by the MPSC. This pin is active-low. This pin is used when the vector mode (CR2A: D7 = "1") is selected, and must be pulled up to "H" when the non-vector mode (CR2A: D7 = "0") is selected.

#### (12) PRI (Priority Input) ... Input

This input pin is used for an interrupt generation request signal and for an output control signal for interrupt vectors. In the normal operation mode, this pin provides an interrupt generation control function. During the INTAK sequence, it provides an output control function for interrupt vectors. How this pin is used differs depending on the interrupt mode.

(a) In vector mode (CR2A: D7 = "1")

In the normal operation mode, the  $\overrightarrow{PRI}$  pin is used to control generation of interrupts. When interrupt vector output mode of Type A-3 or Type B-2 (CR2A: D5, D4, D3 = "0, 1, 0" or "1, 0, 0") is selected, interrupts can be generated regardless of whether the  $\overrightarrow{PRI}$  pin is "L" or "H".

If any other interrupt vector output mode is selected, the PRI pin must be kept "L" to enable generation of interrupts.

During the INTAK sequence, an interrupt vector is output if "L" is input to the  $\overline{PRI}$  pin in any interrupt vector output mode, and output of the interrupt vector is disabled if "H" is input to  $\overline{PRI}$ .

#### (b) Non-vector mode (CR2A: D7 = "0")

In this mode, the  $\overline{PRI}$  pin controls only the generation of interrupts because the INTAK sequence is not used. If an interrupt vector output mode other than Type A-3 and Type B-2 is selected, generation of an interrupt signal is enabled if "L" is input to the  $\overline{PRI}$  pin. The interrupt signal is not generated if "H" is input to  $\overline{PRI}$ . If an interrupt daisy chain is configured, inputting "L" to this pin indicates that a device having a higher priority does not acknowledge interrupt processing or does not have an interrupt request, and only the MPSC with "L" input to its  $\overline{PRI}$  pin can generate an interrupt.

#### (13) PRO (Priority Output) ... Output

This pin is used when an interrupt daisy chain is configured. This output pin is active-low, and controls generation of interrupts requests from a device with a lower priority. Usually, this pin is used along with the  $\overline{PRI}$  pin, and its operation is as follows:

When  $\overrightarrow{PRI} = "H", \overrightarrow{PRO} = "H"$ When  $\overrightarrow{PRI} = "L", \overrightarrow{PRO}$  goes "H" if there is an interrupt request, and goes "L" if there is no interrupt request.

#### (14) DRQTxA (DMA Request TxA) ... Output

This pin outputs a DMA request to a DMA controller. This pin is active-high. It goes "H" if the transmitter of channel A has entered the Tx Buffer Empty status. The condition under which this pin goes "H" differs as follows depending on the setting of the CR1 and D2 bits.

CR1: D2 = "0": The DRQTxA pin goes "H" when the transmitter has entered the Tx Buffer Empty status after the first transmit data has been written. It does not go "H" when the transmitter has entered the Tx Buffer Empty status after reset.

CR1: D2 = "1": The DRQTxA pin goes "H" when the transmitter has entered the Tx Buffer Empty status. This signal is reset when transmit data has been written to channel A.

#### (15) DRQRxA (DMA Request RxA) ... Output

This pin outputs a DMA request to a DMA controller. This pin is active-high and goes "H" if the receiver of channel A has entered the Rx Character Available status. This signal is reset only when receive data has been read from channel A.

#### (16) DTRA/DRQTxB (Data Terminal Ready A/DMA Request TxB) ... Output

The function of this pin is changed as follows depending on the setting of CR2A: D1 and D0.

- (a) When CR2A: D1, D0 = "0, 0" or "0, 1"

- This pin functions as the  $\overline{\text{DTRA}}$  pin. This pin is a general-purpose output pin and can be used to control a modem, etc. The operation of the  $\overline{\text{DTRA}}$  pin is as follows:

When CR5A: D7 = "0",  $\overline{\text{DTRA}}$  = "H" When CR5A: D7 = "1",  $\overline{\text{DTRA}}$  = "L"

(b) When CR2A: D1, D0 = "1, 0"

This pin functions as the DRQTxB output pin. The function of this pin is the same as the DRQTxA pin, except this pin is used with channel B.

(17) DTRB/DRQRxB (Data Terminal Ready B/DMA Request RxB) ... Output The function of this pin changes as follows depending on the setting of CR2A: D1 and D0. (a) When CR2A: D1, D0 = "0, 0" or "0, 1"

This pin functions as the DTRB output pin. The function of this pin is the same as the DTRA pin, except this pin is used with channel B.

(b) When CR2A: D1, D0 = "1, 0"

This pin functions as the DRQR×B output pin. The function of this pin is the same as the DRQR×A pin, except this pin is used with channel B.

#### (18) CTSA (Clear to Send A) and CTSB (Clear to Send B) ... Input

This pin is a general-purpose input pin and can be used to control a modem, etc. Changes in the status of this pin affect the latching operation of the E/S bit. When E/S INT is enabled (CR1: D0 = "1"), the E/S interrupt is generated.

If the Auto Enable mode (CR3: D5 = "1") is set, the transmitter can be controlled by using the Tx Enable bit (CR5: D3) and this pin. This is illustrated in Table 1-3.

| CTS Pin | Tx Enable Bit | Transmitter Status |

|---------|---------------|--------------------|

| L       | 1             | Enabled            |

| н       | 1             | Disabled           |

| H or L  | 0             | Disabled           |

#### Table 1-3. Auto Enable Mode and CTS Pin

(19) DCDA (Data Carrier Detect A) ... Input

DCDB (Data Carrier Detect B) ... Input

These are general-purpose input pins and can be used to control a modem, etc. Changes in the status of this pin affect the latching operation of the E/S bit. When E/S INT is enabled (CR1: D0 = "1"), the E/S interrupt is generated.

If the Auto Enable mode (CR3: D5 = "1") is set, the receiver can be controlled by using the Rx Enable bit (CR3: D0) and this pin. This is illustrated in Table 1-4.

| 1 | Table 1-4. | Auto Enal | ole Mode a | nd DCD Pin |  |

|---|------------|-----------|------------|------------|--|

|   |            |           |            |            |  |

| DCD Pin | Rx Enable Bit | Receiver Status |

|---------|---------------|-----------------|

| L       | 1             | Enabled         |

| н       | 1             | Disabled        |

| H or L  | 0             | Disabled        |

(20) RTSA (Request to Send A) ... Output

RTSB (Request to Send B) ... Output

These are general-purpose output pins and can be used to control a modem, etc. The operations of these pins differ depending on the setting of the operation protocol and the setting of the Auto Enable bit, as shown in Table 1-5.

| Table 1-5. | Auto | Enable | Bit and | <b>RTS Pin</b> |

|------------|------|--------|---------|----------------|

|------------|------|--------|---------|----------------|

| Function<br>Protocol | Auto Enable Bit | RTS Cont. Bit                            | RTS Pin Status                                                            |

|----------------------|-----------------|------------------------------------------|---------------------------------------------------------------------------|

| Start-stop           | 0               | 0                                        | н                                                                         |

| synchronization      |                 | 1                                        | L                                                                         |

|                      | 1               | When "0" from beginning                  | Н                                                                         |

|                      |                 | If set to "1" once and then reset to "0" | If "L" while All Sent <sup>Note</sup> = "0",<br>and "H" if All Sent = "1" |

|                      |                 | 1                                        | L                                                                         |

| COP/BOP              | Don't Care      | 0                                        | Н                                                                         |

|                      |                 | 1                                        | L                                                                         |

Note SR1: D2

#### 1.2 Pins Related to Transmission/Reception

- TxDA (Transmit Data A) and TxDB (Transmit Data B) ... Output These pins output transmit data.

- (2) RxDA (Receive Data A) and RxDB (Receive Data B) ... Input These pins input receive data.

- (3) XI1A/STRxCA (Crystal Input 1A/Source of Transmit Receive Clock A) ... Input XI1B/STRxCB (Crystal Input 1B/Source of Transmit Receive Clock B) ... Input The functions of these pins change depending on the setting of CR15: D7.

- (a) When CR15: D7 = "0"

These pins function as the STRxC pins, and input the transmission and reception clocks, or input source clocks to the internal BRG (Baud Rate Generator) and DPLL (Digital Phase Locked Loop).

- (b) When CR15: D7 = "1" These pins function as XI1 pins and connect one end of the crystal for transmission/reception clock source oscillation.

- (4) XI2A/SYNCA (Crystal Input 2A/Synchronization A) ... I/O

XI2B/SYNCB (Crystal Input 2B/Synchronization B) ... I/O

The functions of these pins change depending on the setting of CR15: D7.

- (a) When CR15: D7 = 0 These pins function as  $\overline{\text{SYNC}}$  pins. The functions of the  $\overline{\text{SYNC}}$  pins differ as shown in Table 1-6, depending on the setting of CR4.

- (b) When CR15: D7 = "1" These pins function as XI2 pins and connect one end of the crystal for transmission/reception clock source oscillation.

| Operation                          | Synchronization                  | SYNC Pin    |    |    | C  | R4     |             |             |                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|------------------------------------|----------------------------------|-------------|----|----|----|--------|-------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Protocol                           | Detection Mode                   | Function    | D7 | D6 | D5 | D4     | D3          | D2          | Function                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| Start-stop<br>synchro-<br>nization |                                  | Input       | >  | <  | ;  | ×      | 0<br>1<br>1 | 1<br>0<br>1 | The $\overline{\text{SYNC}}$ pins function as general-purpose<br>input pins. Changes in the status of these pin<br>("H" $\rightarrow$ "L" or "L" $\rightarrow$ "H") affect the latch<br>operation of the Sync/Hunt bit (SR1: D4), and<br>cause the E/S interrupt.                                                                                                                                                |  |  |

| COP                                | Internal<br>synchro-<br>nization | Output      | >  | <  | 0  | 0<br>1 |             |             | If a SYNC character is detected in the receive character, the SYNC pins go "L" for the duration of 1RxC cycle.                                                                                                                                                                                                                                                                                                   |  |  |

|                                    | External<br>synchro-<br>nization | Input       | 0  | 0  | 1  | 1      | 0           | 0           | The SYNC pins input a signal for establishing<br>character synchronization. When these pins<br>go "L" from "H", execution exits from the Hunt<br>Phase and character synchronization is<br>established. While SYNC input is "L",<br>character synchronization is maintained.<br>Assembling a receive character is started at<br>the rising edge of the receive clock preceding<br>the falling of the SYNC input. |  |  |

| BOP                                |                                  | No function | >  | <  | 1  | 0      |             |             | The SYNC pins do not function.                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

Table 1-6. Functions of SYNC Pins and Setting of CR4 (when CR15: D7 = "0")

- ×: Don't Care

- Caution If a pattern in which 1 bit ("0" or "1") is inserted in between the "Sync character assigned to CR7" and "Sync character assigned to CR6" is received while data is being assembled in the Bi-Sync mode, an "L" pulse of about 1 bit may be generated on the <u>SYNC</u> pin. If the Enter Hunt command is issued while this "L" pulse is present, the command is invalid. However, the recieve operation of the MPSC is not affected at all by the reception of this pattern.

- (5) TRxCA (Transmit Receive Clock A) ... I/O TRxCB (Transmit Receive Clock B) ... I/O

- (a) When CR15: D2 = "0"

These pins input the transmit and receive clocks. They are used to supply external transmit and receive clocks.

[Exception] If either CR15: D6, D5 = "0, 1" or D4, D3 = "0, 1", or both are set, the TRxCA and TRxCB pins function as input pins, even if CR15: D2 = "1".

(b) When CR15: D2 = "1"

These pins function as output pins. The source of the output clock can be selected from a crystal oscillation circuit, BRG, DPLL, or transmit clock, depending on the setting of CR15: D1, D0. Under the conditions explained in [Exception] in (a) above, they unconditionally serve as input pins, and the setting of CR15: D2, D1, D0 is invalid.

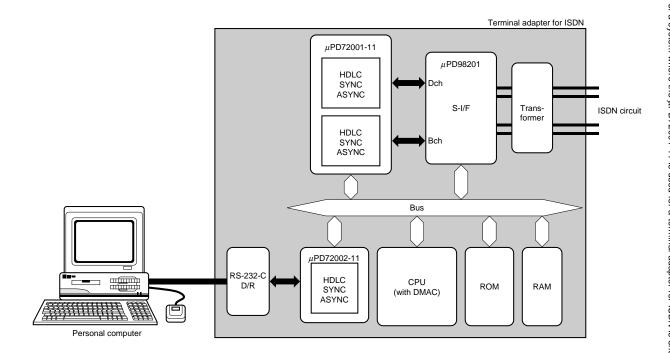

An example of a system where the  $\mu$ PD72001-11 is used for a terminal adapter for ISDN is shown below.

#### 3. ELECTRICAL SPECIFICATIONS

#### (1) µPD72001-11

#### Absolute Maximum Ratings (T<sub>A</sub> = 25 °C)

| Parameter             | Symbol | Condition | Ratings           | Unit |

|-----------------------|--------|-----------|-------------------|------|

| Supply voltage        | Vdd    |           | -0.5 to +7.0      | V    |

| Input voltage         | Vı     |           | –0.5 to Vdd + 0.5 | V    |

| Output voltage        | Vo     |           | –0.5 to Vdd + 0.5 | V    |

| Operating temperature | TA     |           | -40 to +85        | °C   |

| Storage temperature   | Tstg   |           | –65 to +150       | °C   |

Caution If any of the parameters exceeds the absolute maximum ratings, even momentarily, the quality of the product may be impaired. The absolute maximum ratings are values that may physically damage the product(s). Be sure to use the product(s) within the ratings.

#### **DC** Characteristics

#### $\mu$ PD72001-11 (T<sub>A</sub> = -40 to +85 °C, V<sub>DD</sub> = 5 V ± 10 %)

| Parameter                         | Symbol | Condition                       | MIN.    | TYP. | MAX.      | Unit |

|-----------------------------------|--------|---------------------------------|---------|------|-----------|------|

| High-level input voltage          | VIHC   | CLK, STR×C, TR×C                | 3.3     |      | Vdd + 0.5 | V    |

|                                   | VIH    | Other pins                      | 2.2     |      | Vdd + 0.5 | V    |

| Low-level input voltage           | VILC   | CLK, STR×C, TR×C                | -0.5    |      | +0.6      | V    |

|                                   | VIL    | Other pins                      | -0.5    |      | +0.8      | V    |

| High-level output voltage         | Vон    | Іон = -400 μА                   | 0.7 Vdd |      |           | V    |

| Low-level output voltage          | Vol    | IoL = 2.0 mA                    |         |      | 0.45      | V    |

| High-level input leakage current  | Іцн    | Vi = Vdd                        |         |      | 10        | μA   |

| Low-level input leakage current   | Ilil   | Vi = 0 V                        |         |      | -10       | μA   |

| High-level output leakage current | Ігон   | Vo = Vdd                        |         |      | 10        | μA   |

| Low-level output leakage current  | LOL    | Vo = 0 V                        |         |      | -10       | μA   |

| Supply current                    | ldd    | At 11 MHz                       |         | 20   | 40        | mA   |

|                                   |        | In standby mode <sup>Note</sup> |         |      | 1         | mA   |

Note System clock

: 11 MHz

: Inactive

• High-level input voltage :  $(V_{DD} - 0.3 \text{ V})$  to  $(V_{DD} + 0.5 \text{ V})$

• Low-level input voltage : 0 V to 0.3 V

Output pin

Input pin

: Leave unconnected.

# Capacitance (TA = 25 $^{\circ}$ C, VDD = 0 V)

| Parameter         | Symbol | Condition                     | MIN. | MAX. | Unit |

|-------------------|--------|-------------------------------|------|------|------|

| Input capacitance | CIN    | fc = 1 MHz                    |      | 10   | pF   |

| I/O capacitance   | Сю     | Pins other than test pin: 0 V |      | 20   | pF   |

#### **AC Characteristics**

# $\mu$ PD72001-11 (T<sub>A</sub> = -40 to +85 °C, V<sub>DD</sub> = 5 V ± 10 %)

## System interface:

| <b>5</b>                                                                |              |                                                | Rateo | Rated Value |      |  |

|-------------------------------------------------------------------------|--------------|------------------------------------------------|-------|-------------|------|--|

| Parameter                                                               | Symbol       | Condition                                      | MIN.  | MAX.        | Unit |  |

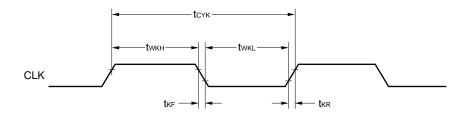

| Clock cycle                                                             | tсүк         |                                                | 90    | 2 000       | ns   |  |

| Clock high-pulse width                                                  | twкн         |                                                | 40    | 1 000       | ns   |  |

| Clock low-pulse width                                                   | <b>t</b> wĸ∟ |                                                | 40    | 1 000       | ns   |  |

| Clock rise time                                                         | <b>t</b> kr  | $1.5 \text{ V} \rightarrow 3.0 \text{ V}$      |       | 10          | ns   |  |

| Clock fall time                                                         | tкғ          | $3.0 \text{ V} \rightarrow 1.5 \text{ V}$      |       | 10          | ns   |  |

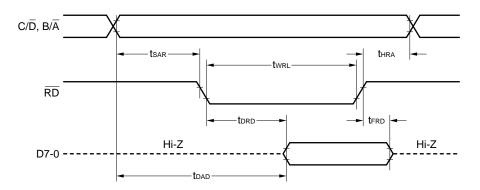

| Address setup time (vs. $\overline{\text{RD}}\downarrow)$               | <b>t</b> sar |                                                | 0     |             | ns   |  |

| Address hold time (vs. $\overline{\text{RD}} \uparrow$ )                | thra         |                                                | 0     |             | ns   |  |

| RD pulse width                                                          | twrl         |                                                | 120   |             | ns   |  |

| $Address \to data \text{ output delay time}$                            | <b>t</b> dad | $T_{A} = -10 \text{ to } +70 ^{\circ}\text{C}$ |       | 100         | ns   |  |

|                                                                         |              | T <sub>A</sub> = -40 to +85 °C                 |       | 110         |      |  |

| $\overline{\text{RD}} \rightarrow \text{data output delay time}$        | <b>t</b> drd | $T_{A} = -10$ to +70 °C                        |       | 100         | ns   |  |

|                                                                         |              | $T_{A} = -40$ to +85 °C                        |       | 110         |      |  |

| $\overline{\text{RD}} \rightarrow \text{data float delay time}$         | <b>t</b> FRD |                                                | 10    | 85          | ns   |  |

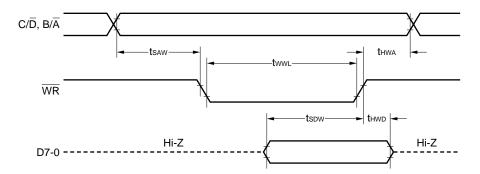

| Address setup time (vs. $\overline{\text{WR}}\downarrow$ )              | tsaw         |                                                | 0     |             | ns   |  |

| Address hold time (vs. $\overline{\text{WR}} \uparrow$ )                | thwa         |                                                | 0     |             | ns   |  |

| WR pulse width                                                          | tww∟         |                                                | 120   |             | ns   |  |

| Data setup time (vs. WR ↑)                                              | tsdw         | $T_{A} = -10 \text{ to } +70 ^{\circ}\text{C}$ | 100   |             | ns   |  |

|                                                                         |              | $T_{A} = -40$ to +85 °C                        | 90    |             |      |  |

| Data hold time (vs. $\overline{WR} \uparrow$ )                          | thwa         |                                                | 0     |             | ns   |  |

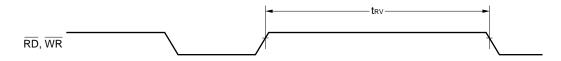

| Recovery time between $\overline{\text{RD}}$ and $\overline{\text{WR}}$ | <b>t</b> RV  |                                                | 140   |             | ns   |  |

#### Serial control:

| Parameter                                                                                                       |                                    | <b>a</b>         | <b>0</b>                       | Rated | Value |      |

|-----------------------------------------------------------------------------------------------------------------|------------------------------------|------------------|--------------------------------|-------|-------|------|

|                                                                                                                 |                                    | Symbol Condition |                                | MIN.  | MAX.  | Unit |

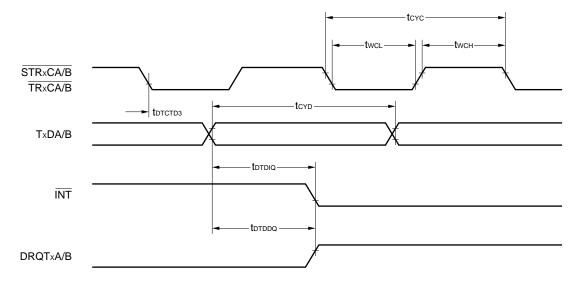

| Transmit/receive data cycl                                                                                      | e                                  | tcyp             |                                | 5     |       | tсүк |

| STRxC, TRxC input clock                                                                                         | cycle                              | tcyc             |                                | 90    |       | ns   |

| STRxC, TRxC input                                                                                               | High                               | twcн             |                                | 40    |       | ns   |

| clock pulse width                                                                                               | Low                                | twc∟             | $T_A = -10$ to +70 °C          | 40    |       | ns   |

|                                                                                                                 |                                    |                  | T <sub>A</sub> = -40 to +85 °C | 45    |       |      |

| $\overline{\text{STRxC}}, \overline{\text{TRxC}} \downarrow \rightarrow \text{TxD} \text{ det}$                 | lay time                           | tDTCTD1          | ×1 mode, COP, BOP              |       | 100   | ns   |

|                                                                                                                 |                                    | tDTCTD2          | ×16, 32, 64 mode               |       | 300   | ns   |

| $\overline{TR {\scriptscriptstyle \times} C} \downarrow \rightarrow T {\scriptscriptstyle \times} D$ delay time |                                    | <b>t</b> DTCTD3  | TRxC is output                 | 0     | 100   | ns   |

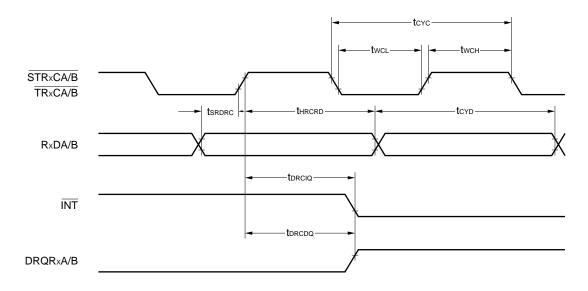

| RxD setup time (vs. STRx                                                                                        | RxD setup time (vs. STRxC, TRxC ↑) |                  | When DPLL is not used          | 0     |       | ns   |

| RxD hold time (vs. STRxC                                                                                        | , TRxC ↑)                          | <b>t</b> HRCRD   | When DPLL is not used          | 120   |       | ns   |

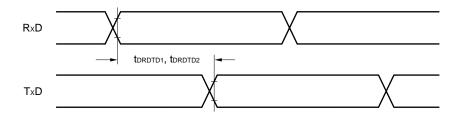

| $RxD \rightarrow TxD$ delay time                                                                                |                                    | tdrdtd1          | ECHO BACK mode                 |       | 100   | ns   |

|                                                                                                                 |                                    | tdrdtd2          | Without SDLC Loop delay        |       | 100   | ns   |

| $TxD \rightarrow \overline{INT}$ delay time                                                                     |                                    | <b>t</b> dtdiq   | Tx INT mode                    | 4     | 6     | tсүк |

| $TxD \rightarrow DRQTx$ delay time                                                                              |                                    | <b>t</b> dtddq   | Tx DMA mode                    | 4     | 6     | tсүк |

| $\overline{\text{RxC}} \uparrow {}^{\text{Note}} \rightarrow \overline{\text{INT}}$ delay time                  |                                    | torciq           | Rx INT mode                    | 7     | 11    | tсүк |

| $\overline{\text{RxC}} \uparrow \text{Note} \rightarrow \text{DRQRx}$ delay time                                |                                    | <b>t</b> drcdq   | Rx DMA mode                    | 7     | 11    | tсүк |

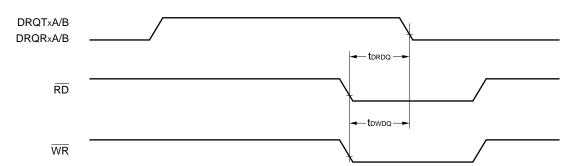

| $\overline{RD} \downarrow \to DRQRx \downarrow delay  time$                                                     |                                    | <b>t</b> drdq    |                                |       | 120   | ns   |

| $\overline{WR} \downarrow \rightarrow DRQTx \downarrow delay  ti$                                               | me                                 | towdq            |                                |       | 120   | ns   |

**Note** Of  $\overline{\text{STRxC}}$  and  $\overline{\text{TRxC}}$ , the one used as the receive clock.

#### Interrupt control:

|                                                                                                       | <b>.</b>       |                                          | Rateo |      |      |

|-------------------------------------------------------------------------------------------------------|----------------|------------------------------------------|-------|------|------|

| Parameter                                                                                             | Symbol         | Condition                                | MIN.  | MAX. | Unit |

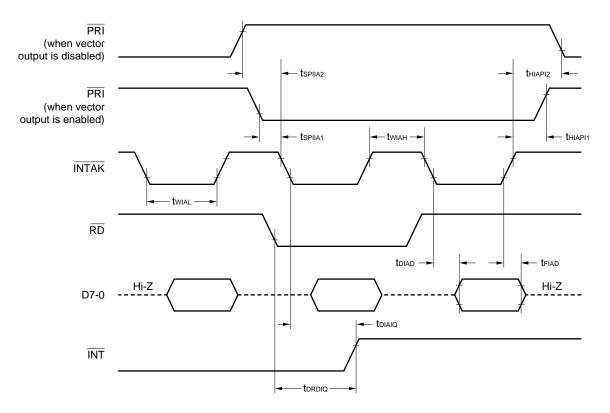

| INTAK low-pulse width                                                                                 | twial          |                                          | 120   |      | ns   |

| INTAK high-pulse width                                                                                | twiah          |                                          | 120   |      | ns   |

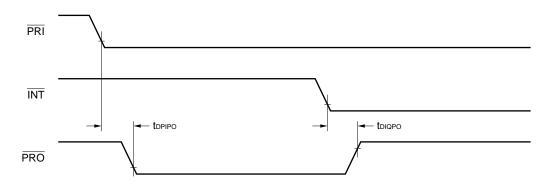

| $\overline{\text{PRI}} \rightarrow \overline{\text{PRO}}$ delay time                                  | <b>t</b> DPIPO |                                          |       | 50   | ns   |

| $\overline{\mathrm{INT}} \downarrow \rightarrow \overline{\mathrm{PRO}} \uparrow \mathrm{delay}$ time | <b>t</b> DIQPO |                                          | -20   | +50  | ns   |

| 2nd $\overline{\text{INTAK}} \downarrow \rightarrow \overline{\text{INT}} \uparrow$ delay time        | <b>t</b> DIAIQ | INT output level = 0.8 V <sup>Note</sup> |       | 120  | ns   |

|                                                                                                       |                | INT output level = 2.2 V <sup>Note</sup> |       | 300  | ns   |

| SR2B read $\overline{RD} \downarrow \rightarrow \overline{INT} \uparrow delay$ time                   | tordiq         | INT output level = 0.8 V <sup>Note</sup> |       | 150  | ns   |

|                                                                                                       |                | INT output level = 2.2 V <sup>Note</sup> |       | 300  | ns   |

| $\overline{PRI}$ setup time (vs. $\overline{INTAK}\downarrow$ )                                       | tspiia1        | When vector output is enabled            | 0     |      | ns   |

| PRI hold time (vs. INTAK ↑)                                                                           | thiapi1        |                                          | 20    |      | ns   |

| $\overline{PRI}$ setup time (vs. $\overline{INTAK}\downarrow$ )                                       | tspiia2        | When vector output is disabled           | 20    |      | ns   |

| PRI hold time (vs. INTAK ↑)                                                                           | thiapi2        |                                          | 20    |      | ns   |

| $\overline{\text{INTAK}} \rightarrow \text{data output delay time}$                                   | <b>t</b> diad  |                                          |       | 120  | ns   |

| $\overline{\text{INTAK}} \rightarrow \text{data float delay time}$                                    | <b>t</b> FIAD  |                                          | 10    | 85   | ns   |

Note Measured value with 2-k $\Omega$  pull-up resistor and 100-pF load capacitance connected

#### Modem control:

| Demonster                                                                                                           |      | Quarterat |                              | Rated | Unit |      |

|---------------------------------------------------------------------------------------------------------------------|------|-----------|------------------------------|-------|------|------|

| Parameter                                                                                                           |      | Symbol    | Condition                    | MIN.  |      | MAX. |

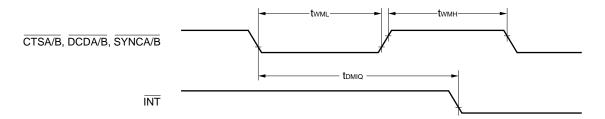

| $\overline{\text{CTS}}, \overline{\text{DCD}}, \overline{\text{SYNC}}$ pulse                                        | High | twмн      |                              | 2     |      | tсүк |

| width                                                                                                               | Low  | twмL      |                              | 2     |      | tсүк |

| $\overline{\text{CTS}}, \overline{\text{DCD}}, \overline{\text{SYNC}} \rightarrow \overline{\text{INT}}$ delay time |      | tdмiq     |                              |       | 2    | tсүк |

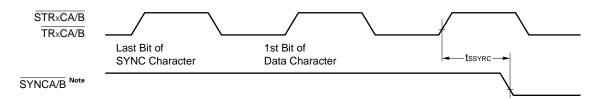

| $\overline{STR_xC},\overline{TR_xC}\hat{\uparrow}\to\overline{SYNC}\text{ setup time}$                              |      | TSSYRC    | COP external synchronization | 0     | 2    | tсүк |

#### **Communication control:**

|                                                                                                                                                                                                                                                     | <b>.</b>        |            | Rated             | Value |      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------------|-------------------|-------|------|

| Parameter                                                                                                                                                                                                                                           | Symbol          | Condition  | MIN.              | MAX.  | Unit |

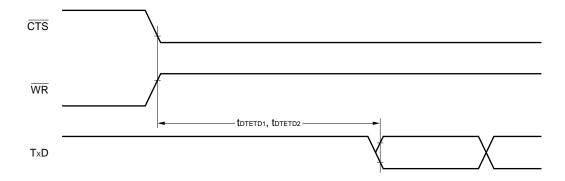

| Transmit enable command                                                                                                                                                                                                                             | <b>t</b> dtetd1 | ASYNC, COP |                   | 3     | tcyc |

| $(\overline{WR} \uparrow, \overline{CTS} \downarrow) \to TxD$ delay time                                                                                                                                                                            | tdtetd2         | ВОР        | 4                 | 7     | tcyc |

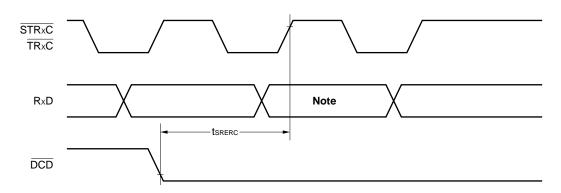

| $\begin{array}{l} \mbox{Receive enable command } (\overline{DCD} \downarrow) \\ \mbox{setup time (vs. start bit, } \overline{STR \times C} \uparrow, \\ \hline \overline{TR \times C} \uparrow \mbox{of sync character})^{\mbox{Note}} \end{array}$ | tsrerc          |            | 1                 |       | tcyc |

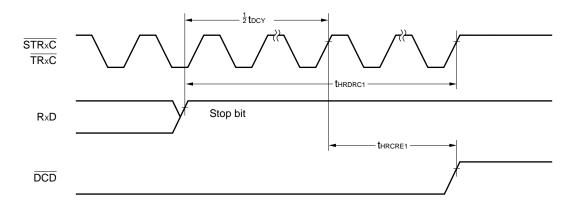

| Receive enable command $(\overline{\text{DCD}}\downarrow)$                                                                                                                                                                                          | thrcre1         | ASYNC      | 7                 |       | tсүк |

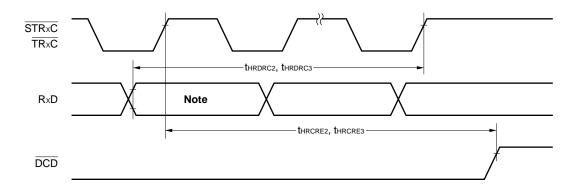

| hold time (vs. STRxC ↑, TRxC ↑) <sup>Note</sup>                                                                                                                                                                                                     | thrcre2         | СОР        | 20tсүс<br>+ 8tсүк |       |      |

|                                                                                                                                                                                                                                                     | thrcre3         | ВОР        | 3tсүс<br>+ 8tсүк  |       |      |

| Receive clock (STRxC, TRxC) <sup>Note</sup>                                                                                                                                                                                                         | tHRDRC1         | ASYNC      | 1                 |       | Bit  |

| hold time (vs. stop bit, MSB of CRC,                                                                                                                                                                                                                | tHRDRC2         | СОР        | 22                |       | tcyc |

| MSB of end flag)                                                                                                                                                                                                                                    | thrdrc3         | BOP        | 5                 |       | tcyc |

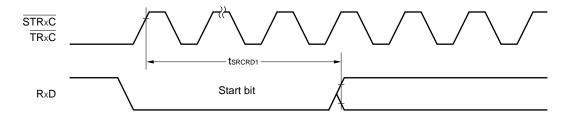

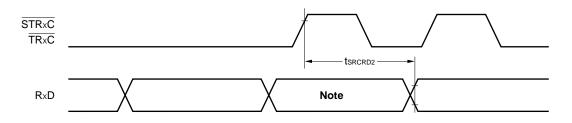

| Receive clock (STRxC, TRxC) <sup>Note</sup>                                                                                                                                                                                                         | tsrcrd1         | ASYNC      | 1                 |       | Bit  |

| setup time (vs. start bit, sync character)                                                                                                                                                                                                          | tsrcrd2         | COP, BOP   | 1                 |       | tcyc |

**Note** Of  $\overline{\text{STRxC}}$  and  $\overline{\text{TRxC}}$ , the one used as the receive clock.

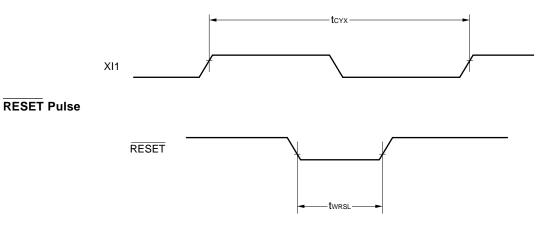

#### Crystal oscillation and reset

| Parameter            | Symbol | Condition | Rated | 11-11 |      |

|----------------------|--------|-----------|-------|-------|------|

|                      |        |           | MIN.  | MAX.  | Unit |

| XI1 input cycle time | tcyx   |           | 90    | 2000  | ns   |

| RESET pulse width    | twrsl  |           | 2     |       | tсүк |

Caution The system clock cycle in all modes must be five times that of the data rate.

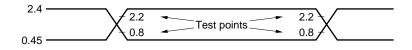

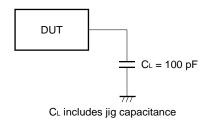

AC Test Input/Output Waveform (except clock)

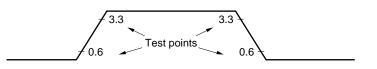

AC Test Clock Input Waveform

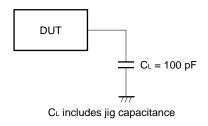

Load Condition

Caution If the load capacitance exceeds 100 pF due to the configuration of the circuit, keep the load capacitance of this device to within 100 pF by inserting a buffer or by some other means.

Remark DUT: Tested device

\*

#### **(2)** μ**PD72001-A8**

#### Absolute Maximum Ratings (T<sub>A</sub> = 25 °C)

| Parameter             | Symbol | Condition | Ratings                       | Unit |

|-----------------------|--------|-----------|-------------------------------|------|

| Supply voltage        | Vdd    |           | -0.5 to +7.0                  | V    |

| Input voltage         | Vi     |           | -0.5 to V <sub>DD</sub> + 0.5 | V    |

| Output voltage        | Vo     |           | -0.5 to V <sub>DD</sub> + 0.5 | V    |

| Operating temperature | TA     |           | -40 to +85                    | °C   |

| Storage temperature   | Tstg   |           | -0 to +150                    | °C   |

Caution If any of the parameters exceeds the absolute maximum ratings, even momentarily, the quality of the product may be impaired. The absolute maximum ratings are values that may physically damage the product(s). Be sure to use the product(s) within the ratings.

| DC Characteristics ( | (T <sub>A</sub> = −40 to +85 °C, V | $DD = 3.3 V \pm 0.3 V$ |

|----------------------|------------------------------------|------------------------|

|----------------------|------------------------------------|------------------------|

| Parameter                         | Symbol | Condition                       | MIN.    | TYP. | MAX.      | Unit |

|-----------------------------------|--------|---------------------------------|---------|------|-----------|------|

| High-level input voltage          | Vінс   | CLK, STR×C, TR×C                | 0.8 Vdd |      | Vdd + 0.5 | V    |

|                                   | Vін    | Other pins                      | 1.8     |      | Vdd + 0.5 | V    |

| Low-level input voltage           | Vilc   | CLK, STRXC, TRXC                | -0.5    |      | 0.15 Vdd  | V    |

|                                   | VIL    | Other pins                      | -0.5    |      | +0.6      | V    |

| High-level output voltage         | Vон    | Іон = -400 μА                   | 2.2     |      |           | V    |

| Low-level output voltage          | Vol    | IoL = 2.0 mA                    |         |      | 0.5       | V    |

| High-level input leakage current  | Іцн    | Vi = Vdd                        |         |      | 10        | μA   |

| Low-level input leakage current   | ILIL   | Vi = 0 V                        |         |      | -10       | μA   |

| High-level output leakage current | Ігон   | Vo = Vdd                        |         |      | 10        | μA   |

| Low-level output leakage current  | Ilol   | Vo = 0 V                        |         |      | -10       | μA   |

| Supply current                    | ldd    | At 8 MHz                        |         | 5    | 20        | mA   |

|                                   |        | In standby mode <sup>Note</sup> |         |      | 1         | mA   |

| Note | System clock                                 | : | 8 MHz (T <sub>A</sub> = -10 to +70 °C)/7.14 MHz (T <sub>A</sub> = -40 to +85 °C) |

|------|----------------------------------------------|---|----------------------------------------------------------------------------------|

|      | Input pin                                    | : | Inactive                                                                         |

|      | <ul> <li>High-level input voltage</li> </ul> | : | (VDD - 0.3 V) to (VDD + 0.5 V)                                                   |

|      | <ul> <li>Low-level input voltage</li> </ul>  | : | 0 V to 0.3 V                                                                     |

|      | Output pin                                   | : | Leave unconnected.                                                               |

#### Capacitance (T<sub>A</sub> = 25 $^{\circ}$ C, V<sub>DD</sub> = 0 V)

| Parameter         | Symbol | Condition                     | MIN. | MAX. | Unit |

|-------------------|--------|-------------------------------|------|------|------|

| Input capacitance | CIN    | fc = 1 MHz                    |      | 10   | pF   |

| I/O capacitance   | Сю     | Pins other than test pin: 0 V |      | 20   | pF   |

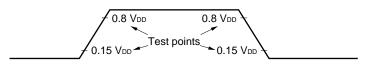

# AC Characteristics (Ta = -40 to +85 °C, V\_{DD} = 3.3 V $\pm$ 0.3 V)

#### ★ System interface:

| -                                                                       | <b>.</b>     |                                           | Ratec | Value | Unit |

|-------------------------------------------------------------------------|--------------|-------------------------------------------|-------|-------|------|

| Parameter                                                               | Symbol       | Condition                                 | MIN.  | MAX.  |      |

| Clock cycle                                                             | tсүк         | T <sub>A</sub> = −10 to +70 °C            | 125   | 2000  | ns   |

|                                                                         |              | T <sub>A</sub> = −40 to +85 °C            | 140   | 2000  | ns   |

| Clock high-pulse width                                                  | twкн         |                                           | 50    | 1000  | ns   |

| Clock low-pulse width                                                   | <b>t</b> wĸ∟ |                                           | 50    | 1000  | ns   |

| Clock rise time                                                         | <b>t</b> kr  | $1.5 \text{ V} \rightarrow 2.2 \text{ V}$ |       | 10    | ns   |

| Clock fall time                                                         | tкғ          | $2.2 \text{ V} \rightarrow 1.5 \text{ V}$ |       | 10    | ns   |

| Address setup time (vs. $\overline{RD} \downarrow$ )                    | <b>t</b> sar | T <sub>A</sub> = −10 to +70 °C            | 0     |       | ns   |

|                                                                         |              | T <sub>A</sub> = −40 to +85 °C            | 5     |       |      |

| Address hold time (vs. $\overline{RD} \uparrow$ )                       | <b>t</b> HRA | T <sub>A</sub> = −10 to +70 °C            | 0     |       | ns   |

|                                                                         |              | T <sub>A</sub> = −40 to +85 °C            | 5     |       |      |

| RD pulse width                                                          | twrl         | T <sub>A</sub> = −10 to +70 °C            | 150   |       | ns   |

|                                                                         |              | T <sub>A</sub> = −40 to +85 °C            | 155   |       |      |

| $Address \to data \text{ output delay time}$                            | <b>t</b> dad | T <sub>A</sub> = −10 to +70 °C            |       | 120   | ns   |

|                                                                         |              | T <sub>A</sub> = −40 to +85 °C            |       | 125   |      |

| $\overline{\text{RD}} \rightarrow \text{data output delay time}$        | <b>t</b> drd | T <sub>A</sub> = −10 to +70 °C            |       | 120   | ns   |

|                                                                         |              | T <sub>A</sub> = −40 to +85 °C            |       | 125   |      |

| $\overline{\text{RD}} \rightarrow \text{data float delay time}$         | <b>t</b> FRD |                                           | 10    | 120   | ns   |

| Address setup time (vs. $\overline{\rm WR}\downarrow$ )                 | tsaw         |                                           | 0     |       | ns   |

| Address hold time (vs. $\overline{\text{WR}} \uparrow$ )                | thwa         | T <sub>A</sub> = −10 to +70 °C            | 0     |       | ns   |

|                                                                         |              | T <sub>A</sub> = −40 to +85 °C            | 5     |       |      |

| WR pulse width                                                          | tww∟         | T <sub>A</sub> = −10 to +70 °C            | 150   |       | ns   |

|                                                                         |              | T <sub>A</sub> = −40 to +85 °C            | 155   |       |      |

| Data setup time (vs. $\overline{\text{WR}} \uparrow$ )                  | tsdw         | T <sub>A</sub> = −10 to +70 °C            | 120   |       | ns   |

|                                                                         |              | T <sub>A</sub> = −40 to +85 °C            | 125   |       |      |

| Data hold time (vs. $\overline{\text{WR}} \uparrow$ )                   | thwd         | T <sub>A</sub> = −10 to +70 °C            | 0     |       | ns   |

|                                                                         |              | T <sub>A</sub> = −40 to +85 °C            | 5     |       |      |

| Recovery time between $\overline{\text{RD}}$ and $\overline{\text{WR}}$ | trv          | T <sub>A</sub> = −10 to +70 °C            | 180   |       | ns   |

|                                                                         |              | T <sub>A</sub> = −40 to +85 °C            | 190   |       |      |

#### Serial control:

|   | Descender                                                                                  | Quarterat       |                         |                                | Rated | l Value | 11-21 |

|---|--------------------------------------------------------------------------------------------|-----------------|-------------------------|--------------------------------|-------|---------|-------|

|   | Parameter                                                                                  | Symbol          |                         | ondition                       | MIN.  | MAX.    | Unit  |

|   | Transmit/receive data cycle                                                                | tcyp            |                         |                                | 5     |         | tсүк  |

| * | STRxC, TRxC input clock cycle                                                              | tcyc            | $T_A = -10$ to +70 °C   |                                | 125   | DC      | ns    |

|   |                                                                                            |                 | $T_{A} = -40$ to +85 °C |                                | 140   | DC      | ns    |

| * | STRxC, TRxC input                                                                          | twcн            | High level              | T <sub>A</sub> = −10 to +70 °C | 50    | DC      | ns    |

|   | clock pulse width                                                                          |                 |                         | T <sub>A</sub> = -40 to +85 °C | 55    | DC      | ns    |

|   |                                                                                            | twc∟            | Low level               | T <sub>A</sub> = −10 to +70 °C | 60    | DC      | ns    |

|   |                                                                                            |                 |                         | T <sub>A</sub> = −40 to +85 °C | 65    | DC      | ns    |

|   | $\overline{\text{STRxC}}, \overline{\text{TRxC}} \downarrow \rightarrow \text{delay time}$ | tDTCTD1         | ×1 mode, COP,           | T <sub>A</sub> = −10 to +70 °C |       | 140     | ns    |

|   |                                                                                            |                 | BOP                     | T <sub>A</sub> = −40 to +85 °C |       | 145     | ns    |

|   |                                                                                            | tDTCTD2         | ×16, 32, 64 mode        | T <sub>A</sub> = -10 to +70 °C |       | 300     | ns    |

|   |                                                                                            |                 |                         | T <sub>A</sub> = -40 to +85 °C |       | 305     | ns    |

| * | $\overline{TRxC} \downarrow \to TxD$ delay time                                            | <b>t</b> отстоз | TRxC is output          |                                | 0     | 100     | ns    |

| * | RxD setup time (vs. STRxC, TRxC ↑)                                                         | <b>t</b> SRDRC  | When DPLL is            | T <sub>A</sub> = −10 to +70 °C | 0     |         | ns    |

|   |                                                                                            |                 | not used                | T <sub>A</sub> = -40 to +85 °C | 5     |         | ns    |

| * | RxD hold time (vs. STRxC, TRxC ↑)                                                          | <b>t</b> HRCRD  | When DPLL is            | T <sub>A</sub> = −10 to +70 °C | 140   |         | ns    |

|   |                                                                                            |                 | not used                | T <sub>A</sub> = -40 to +85 °C | 145   |         | ns    |

|   | $RxD \rightarrow TxD$ delay time                                                           | tdrdtd1         | ECHO BACK mode          | )                              |       | 100     | ns    |

|   |                                                                                            | tdrdtd2         | Without SDLC Loop       | o delay                        |       | 100     | ns    |

|   | $TxD \rightarrow \overline{INT}$ delay time                                                | tdtdiq          | Tx INT mode             |                                | 4     | 6       | tсүк  |

|   | $TxD \rightarrow DRQTx$ delay time                                                         | <b>t</b> dtddq  | Tx DMA mode             |                                | 4     | 6       | tсүк  |

|   | $\overline{RxC} \uparrow {}^{Note} \to \overline{INT} \text{ delay time}$                  | torciq          | Rx INT mode             |                                | 7     | 11      | tсүк  |

|   | $\overline{\text{RxC}} \uparrow \text{Note} \rightarrow \text{DRQRx} \text{ delay time}$   | <b>t</b> DRCDQ  | Rx DMA mode             |                                | 7     | 11      | tсүк  |

|   | $\overline{RD} \downarrow \to DRQRx \downarrow delay  time$                                | <b>t</b> DRDQ   |                         |                                |       | 140     | ns    |

|   | $\overline{WR} \downarrow \to DRQTx \downarrow delay  time$                                | towdq           |                         |                                |       | 140     | ns    |

**Note** Of  $\overline{\text{STRxC}}$  and  $\overline{\text{TRxC}}$ , the one used as the receive clock.

#### Interrupt control:

| _                                                                                |                |                                          |                                |      | l Value |      |

|----------------------------------------------------------------------------------|----------------|------------------------------------------|--------------------------------|------|---------|------|

| Parameter                                                                        | Symbol         | Co                                       | ndition                        | MIN. | MAX.    | Unit |

| INTAK low-pulse width                                                            | twial          |                                          |                                | 150  |         | ns   |

| INTAK high-pulse width                                                           | twiaн          |                                          |                                | 150  |         | ns   |

| $\overline{\text{PRI}} \rightarrow \overline{\text{PRO}}$ delay time             | <b>t</b> DPIPO |                                          |                                |      | 50      | ns   |

| $\overline{INT} \downarrow \rightarrow \overline{PRO} \uparrow delay  time$      | <b>t</b> DIQPO |                                          |                                | -20  | +50     | ns   |

| 2nd $\overline{INTAK} \downarrow \rightarrow \overline{INT} \uparrow$ delay time |                | $\overline{INT}$ output level = 0        | 0.8 V <sup>Note</sup>          |      | 120     | ns   |

|                                                                                  |                | INT output level = 1.8 V <sup>Note</sup> |                                |      | 300     | ns   |

| SR2B read $\overline{RD} \downarrow \to \overline{INT} \uparrow delay$ time      |                | INT output level                         | T <sub>A</sub> = −10 to +70 °C |      | 170     | ns   |

|                                                                                  |                | = 0.8 V <sup>Note</sup>                  | T <sub>A</sub> = −40 to +85 °C |      | 180     | ns   |

|                                                                                  |                | $\overline{INT}$ output level = 1        | .8 V <sup>Note</sup>           |      | 350     | ns   |

| $\overline{PRI}$ setup time (vs. $\overline{INTAK}\downarrow$ )                  | tspiia1        | When vector output                       | is enabled                     | 0    |         | ns   |

| PRI hold time (vs. INTAK ↑)                                                      | thiapi1        |                                          |                                | 20   |         | ns   |

| $\overline{PRI}$ setup time (vs. $\overline{INTAK}\downarrow$ )                  | tspiia2        | When vector output                       |                                | 20   |         | ns   |

| PRI hold time (vs. INTAK ↑)                                                      | thiapi2        | is disabled                              | T <sub>A</sub> = −10 to +70 °C | 20   |         | ns   |

|                                                                                  |                |                                          | T <sub>A</sub> = −40 to +85 °C | 25   |         | ns   |

| $\overline{\text{INTAK}} \rightarrow \text{data output delay time}$              | tdiad          |                                          |                                |      | 120     | ns   |

| $\overline{\text{INTAK}} \rightarrow \text{data float delay time}$               | triad          |                                          |                                | 10   | 130     | ns   |

\*

★

Note Measured value with 2-k $\Omega$  pull-up resistor and 100-pF load capacitance connected

# Modem control:

| Parameter                                                                                                |            | Symbol        | Condition                    | Rated Value |      | 11.24 |

|----------------------------------------------------------------------------------------------------------|------------|---------------|------------------------------|-------------|------|-------|

|                                                                                                          |            |               |                              | MIN.        | MAX. | Unit  |

| CTS, DCD, SYNC                                                                                           | High       | twмн          |                              | 2           |      | tсүк  |

| pulse width                                                                                              | Low        | twm∟          |                              | 2           |      | tсүк  |

| $\boxed{\overline{CTS},  \overline{DCD},  \overline{SYNC} \to \overline{INT}}$                           | delay time | <b>t</b> dмiq |                              |             | 2    | tсүк  |

| $\overline{\text{STRxC}}, \overline{\text{TRxC}} \uparrow \rightarrow \overline{\text{SYNC}}$ setup time |            | tssyrc        | COP external synchronization | 0           | 2    | tсүк  |

#### Communication control:

| _                                                                                                                                                                                                                                        |         |            | Rated              | Value | Unit |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|--------------------|-------|------|

| Parameter                                                                                                                                                                                                                                | Symbol  | Condition  | MIN.               | MAX.  |      |

| Transmit enable command $\overline{(WR} \uparrow$ ,                                                                                                                                                                                      | tdtetd1 | ASYNC, COP |                    | 3     | tcyc |