**OBSOLETE**

December 5, 2008

# **LP2980LV**

# Micropower SOT, 50 mA Low-Voltage Low-Dropout **Regulator For Applications With Output Voltages < 2V**

# **General Description**

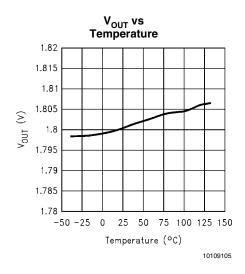

The LP2980LV is a 50 mA, fixed-output voltage regulator designed for high performance in applications requiring output voltages below 2V.

Using an optimized VIP® (Vertically Integrated PNP) process, the LP2980LV delivers unequalled performance in all specifications critical to battery-powered designs:

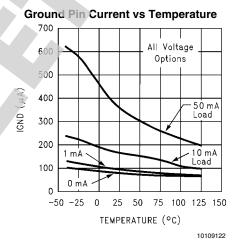

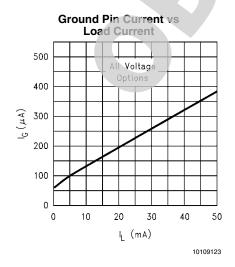

Low Ground Pin Current. Typically 280 µA @ 50 mA load, and 75  $\mu$ A @ 1 mA load.

Sleep Mode. Less than 1 µA quiescent current when ON/ OFF pin is pulled low.

Smallest Possible Size. SOT-23 package uses absolute minimum board space.

Precision Output. 0.5% tolerance output voltages available (A grade).

#### **Features**

- Guaranteed 50 mA output current

- Smallest possible size (SOT-23 Package)

- Requires few external components

- < 1 µA quiescent current when shutdown

- Low ground pin current at all load currents

- Output voltage accuracy 0.5% (A Grade)

- High peak current capability (150 mA typical)

- Wide supply voltage range (16V max)

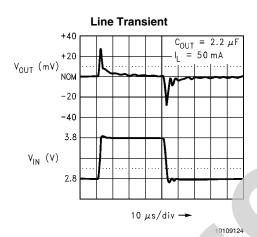

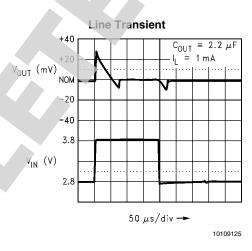

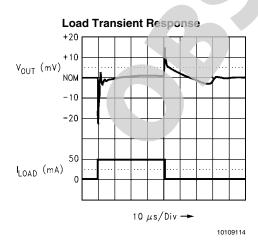

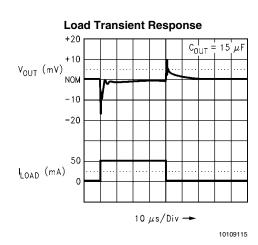

- Fast dynamic response to line and load

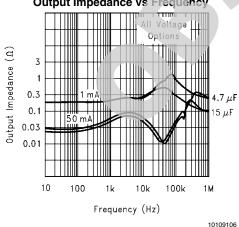

- Low  $Z_{OUT}$  0.1 $\Omega$  typical (10 Hz to 1 MHz)

- Overtemperature/overcurrent protection

- -40°C to +125°C junction temperature range

## **Applications**

- Cellular Phone

- Palmtop/Laptop Computer

- Personal Digital Assistant (PDA)

- Camcorder, Personal Stereo, Camera

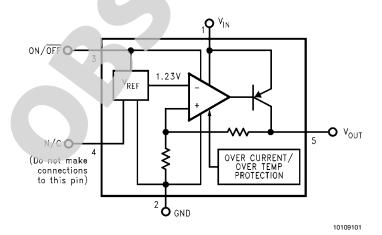

# **Block Diagram**

VIP® is a registered trademark of National Semiconductor Corporation.

© 2008 National Semiconductor Corporation

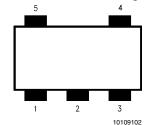

# **Connection Diagrams**

5-Lead Small Outline Package (M5)

Top View

See NS Package Number MF05A

For ordering information see *Table 1*

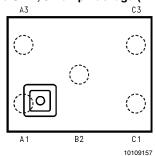

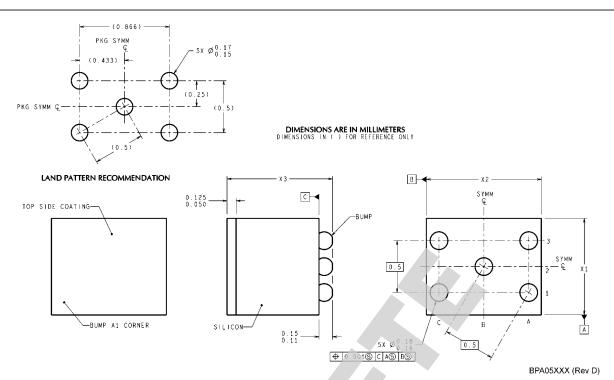

micro SMD, 5 Bump Package (BPA05)

**Note:** The actual physical placement of the package marking will vary from part to part. The package marking will designate the date code and will vary considerably. Package marking does not correlate to device type in any way.

Toρ View See NS Package Number BPA05

# **Pin Descriptions**

| Name             | Pin I  | Number    | Function                                       |  |  |

|------------------|--------|-----------|------------------------------------------------|--|--|

|                  | SOT-23 | micro SMD |                                                |  |  |

| V <sub>IN</sub>  | 1      | C3        | Input Voltage                                  |  |  |

| GND              | 2      | A1        | Common Ground (device substrate)               |  |  |

| ON/OFF           | 3      | A3        | Logic high enable input                        |  |  |

| N/C              | 4      | B2        | Post package trim - do not connect to this pin |  |  |

| V <sub>OUT</sub> | 5      | C1        | Regulated output voltage                       |  |  |

# **Ordering Information**

**TABLE 1. Package Marking and Ordering Information**

| Output Voltage<br>(V) | Grade | Order Information | Package Marking | Supplied as:                |

|-----------------------|-------|-------------------|-----------------|-----------------------------|

| 1.5V                  | Α     | LP2980AIM5X-1.5   | LANA            | 3000 Units on Tape and Reel |

| 1.5V                  | Α     | LP2980AIM5-1.5    | LANA            | 1000 Units on Tape and Reel |

| 1.5V                  | STD   | LP2980IM5X-1.5    | LANB            | 3000 Units on Tape and Reel |

| 1.5V                  | STD   | LP2980IM5-1.5     | LANB            | 1000 Units on Tape and Reel |

| 1.8V                  | Α     | LP2980AIM5X-1.8   | LAGA            | 3000 Units on Tape and Reel |

| 1.8V                  | А     | LP2980AIM5-1.8    | LAGA            | 1000 Units on Tape and Reel |

| 1.8V                  | STD   | LP2980IM5X-1.8    | LAGB            | 3000 Units on Tape and Reel |

| 1.8V                  | STD   | LP2980IM5-1.8     | LAGB            | 1000 Units on Tape and Reel |

For output voltages > 2V, refer to LP2980 datasheet. If a non-standard voltage is required, see LP2980-ADJ.

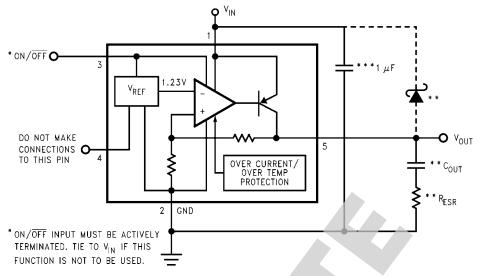

# **Basic Application Circuit**

- \*\* SEE APPLICATION HINTS.

- \*\*\* MINIMUM VALUE REQUIRED FOR STABILITY (MAY BE INCREASED WITHOUT LIMIT).

10109103

## **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

Storage Temperature Range -65°C to +150°C

**Operating Junction Temperature**

Range  $-40^{\circ}\text{C to } +125^{\circ}\text{C}$

Lead Temperature

(Soldering, 5 sec.)

ESD Rating (Note 2) 2 k\

Power Dissipation (Note 3)

Internally Limited

Input Supply Voltage (Survival)

Input Supply Voltage (Operating)

ON/OFF Input Voltage (Survival)

Output Voltage (Survival), (Note 4)

IOUT (Survival)

Input-Output Voltage (Survival)

Input-Output Voltage (Survival)

Input-Output Voltage (Survival)

Input-Output Voltage (Survival),

(Note 5) -0.3V to +16V

### **Electrical Characteristics**

Limits in standard typeface are for  $T_J = 25^{\circ}$ C, and limits in **boldface type** apply over the full operating temperature range. Unless otherwise specified:  $V_{IN} = V_{O(NOM)} + 1V$ ,  $I_L = 1$  mA,  $C_{IN} = 1$  µF,  $C_{OUT} = 4.7$  µF,  $V_{ON/OFF} = 2V$ .

260°C

| Symbol                                 | Parameter                                                    | Conditions                                       | Тур   | Гур LP2980LVAI-XX     |                       | LP2980LVI-XX          |                       | Units             |

|----------------------------------------|--------------------------------------------------------------|--------------------------------------------------|-------|-----------------------|-----------------------|-----------------------|-----------------------|-------------------|

|                                        |                                                              |                                                  |       | (Note 6)              |                       | (Note 6)              |                       |                   |

|                                        |                                                              |                                                  |       | Min                   | Max                   | Min                   | Max                   |                   |

|                                        |                                                              | I <sub>L</sub> = 1 mA                            |       | -0.50                 | 0.50                  | -1.00                 | 1.00                  |                   |

| $\Delta V_{O}$                         | Output Voltage Tolerance                                     | 1 mA < I <sub>L</sub> < 50 mA                    |       | -0.75<br><b>-2.50</b> | 0.75<br>2.50          | -1.50<br><b>-3.50</b> | 1.50<br><b>-3.50</b>  | %V <sub>NOM</sub> |

| $\frac{\Delta V_0}{\Delta V_{1N}}$     | Output Voltage Line<br>Regulation                            | $V_{O(NOM)} + 1V \le V_{IN} \le 16V$             | 0.007 |                       | 0.014<br><b>0.032</b> |                       | 0.014<br><b>0.032</b> | %/V               |

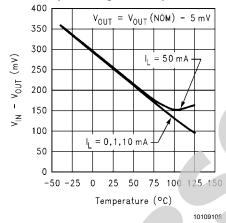

|                                        |                                                              | I <sub>L</sub> = 0                               | 65    |                       | 85<br><b>110</b>      |                       | 85<br><b>110</b>      |                   |

|                                        |                                                              | I <sub>L</sub> = 1 mA                            | 75    |                       | 95<br><b>160</b>      |                       | 95<br><b>160</b>      |                   |

| $I_{GND}$                              | Ground Pin Current                                           | I <sub>L</sub> = 10 mA                           | 120   |                       | 175<br><b>325</b>     |                       | 175<br><b>325</b>     | μΑ                |

|                                        |                                                              | I <sub>L</sub> = 50 mA                           | 280   |                       | 475<br><b>850</b>     |                       | 475<br><b>850</b>     |                   |

|                                        |                                                              | V <sub>ON/OFF</sub> < 0.18∨                      | 0     |                       | 1                     |                       | 1                     |                   |

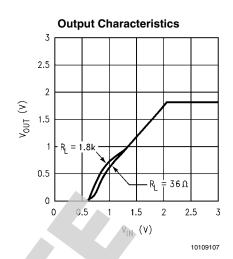

| V <sub>IN</sub> (min)                  | Minimum input voltage required to maintain output regulation | I <sub>L</sub> = 50 mA                           | 2.05  |                       | 2.20                  |                       | 2.20                  | V                 |

| V <sub>ON/OFF</sub>                    | ON/OFF Input Voltage                                         | High = O/P ON                                    | 1.4   | 1.6                   |                       | 1.6                   |                       | V                 |

|                                        | (Note 7)                                                     | Low = O/P OFF                                    | 0.55  |                       | 0.18                  |                       | 0.18                  | V                 |

| I <sub>ON/OFF</sub>                    | ON/OFF Input Current                                         | $V_{ON/OFF} = 0$                                 | 0     |                       | -1                    |                       | -1                    |                   |

|                                        |                                                              | $V_{ON/OFF} = 5V$                                | 5     |                       | 15                    |                       | 15                    | μΑ                |

| I <sub>O(PK)</sub>                     | Peak Output Current                                          | $V_{OUT} \ge V_{O(NOM)} - 5\%$                   | 150   | 100                   |                       | 100                   |                       | mA                |

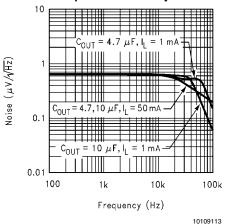

| e <sub>n</sub>                         | Output Noise Voltage (RMS)                                   | BW = 300 Hz to 50 kHz,<br>$C_{OUT}$ = 10 $\mu$ F | 125   |                       |                       |                       |                       | μV                |

| $\frac{\Delta V_{OUT}}{\Delta V_{IN}}$ | Ripple Rejection                                             | $f = 1 \text{kHz C}_{OUT} = 10 \mu\text{F}$      | 63    |                       |                       |                       |                       | dB                |

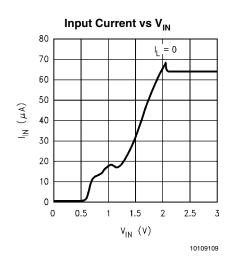

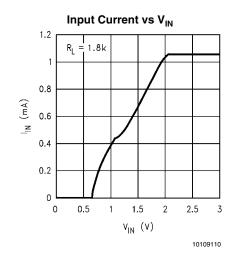

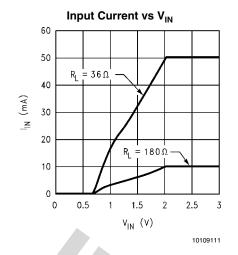

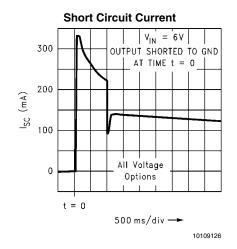

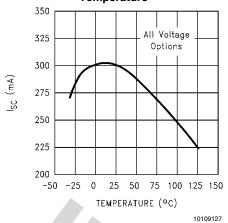

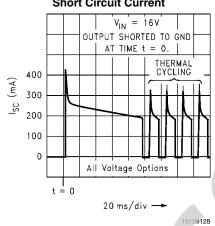

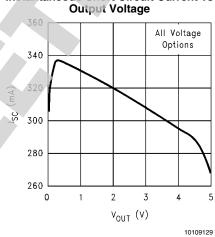

| I <sub>O(MAX)</sub>                    | Short Circuit Current                                        | R <sub>L</sub> = 0 (Steady State) (Note 8)       | 150   |                       |                       |                       |                       | mA                |

Note 1: Absolute maximum ratings indicate limits beyond which damage to the component may occur. Electrical specifications do not apply when operating the device outside of its rated operating conditions.

Note 2: The ESD rating of pins 3 and 4 is 1 kV.

Note 3: The maximum allowable power dissipation is a function of the maximum junction temperature,  $T_{J(MAX)}$ , the junction-to-ambient thermal resistance,  $\theta_{JA}$ , and the ambient temperature,  $T_A$ . The maximum allowable power dissipation at any ambient temperature is calculated using:

$$P(MAX) = \frac{T_J(MAX) - T_A}{\theta_{J-A}}$$

The value of  $\theta_{JA}$  for the SOT-23 package is 220°C/W. Exceeding the maximum allowable power dissipation will cause excessive die temperature, and the regulator will go into thermal shutdown.

Note 4: If used in a dual-supply system where the regulator load is returned to a negative supply, the LP2980LV output must be diode-clamped to ground.

Note 5: The output PNP structure contains a diode between the  $V_{IN}$  and  $V_{OUT}$  terminals that is normally reverse-biased. Reversing the polarity from  $V_{IN}$  to  $V_{OUT}$  will turn on this diode and possibly damage the device (see Application Hints).

Note 6: Limits are 100% production tested at 25°C. Limits over the operating temperature range are guaranteed through correlation using Statistical Quality Control (SQC) methods. The limits are used to calculate National's Average Outgoing Quality Level (AOQL).

Note 7: The ON/OFF input must be properly driven to prevent misoperation. For details, refer to Application Hints.

Note 8: See Typical Performance Characteristics curves.

#

#### Min Input Voltage vs Temperature

#### **Instantaneous Short Circuit Current vs** Temperature

**Short Circuit Current**

**Instantaneous Short Circuit Current vs**

**Output Impedance vs Frequency**

**Output Noise Density**

#### **Ripple Rejection** 100 $C_{OUT} = 10 \mu F, I_L = 50 \text{ mA}$ 90 $C_{OUT} = 10 \mu F, I_{L} = 1 mA$ 80 Ripple Rejection (dB) 70 60 50 40 All Voltage 30 Options 20 10 10k 10 100 1k 100k Frequency (Hz) 10109112

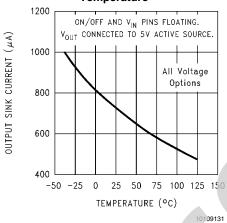

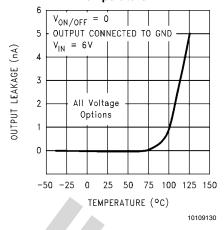

#### Output Reverse Leakage vs Temperature

# **Application Hints**

#### **INPUT CAPACITOR**

An input capacitor whose capacitance is  $\geq$  1  $\mu$ F is required between the LP2980 input pin and ground (the amount of capacitance may be increased without limit).

The input capacitor must be located a distance of not more than 1 cm away from the input pin and returned to a clean analog ground. Any good quality ceramic, Tantalum, or film capacitor may be used at the input.

#### Input to Output Leakage vs Temperature

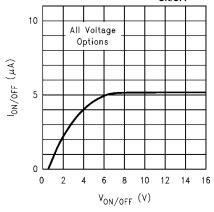

#### ON/OFF Pin current vs V<sub>ON/OFF</sub>

10109132

**IMPORTANT:** Tantalum capacitors may suffer catastrophic failure due to surge current when connected to a low-impedance source of power (like a battery or very large capacitor). If a Tantalum input capacitor is used, it must be guaranteed by the manufacturer to have a surge current rating sufficient for the application.

There are no requirements for ESR on the input capacitor, but tolerance and temperature coefficient must be considered when selecting the capacitor to ensure the capacitance will be  $\geq 1~\mu\text{F}$  over the entire operating range.

#### **OUTPUT CAPACITOR**

The LP2980 requires an output capacitor to maintain loop stability. The capacitor must be selected to meet the requirements of capacitance and ESR (equivalent series resistance) over the full operating temperature range of the application (see SELECTING THE OUTPUT CAPACITOR).

The minimum amount of capacitance which can be used on the output is 2.2  $\mu F$ , but this value may be increased without limit.

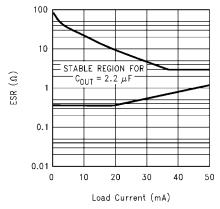

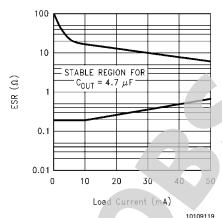

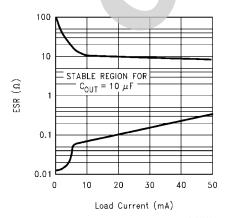

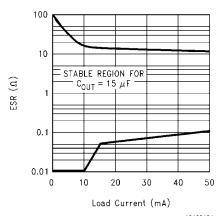

Four curves are provided which show the stable ESR range of the LP2980-1.8V operated with output capacitances of 2.2, 4.7, 10, and 15  $\mu$ F:

2.2 µF ESR Curves For 1.8V Output

4.7 μF ESR Curves For 1.8V Output

10 μF ESR Curves For 1.8V Output

15 μF ESR Curves For 1.8V Output

It should be noted that for the lower values of the output capacitance (< 10  $\mu$ F), it may be necessary to use a capacitor and series resistance to provide sufficient ESR. To understand why this is true, the basic characteristics of capacitance types must be explained:

#### **CAPACITOR CHARACTERISTICS**

**Ceramic Capacitors** have an extremely low ESR (in the range of 5-15 m $\Omega$ ), and can only be used on the output of the LP2980 if an external resistor is placed in series to supply the needed ESR (a resistance value of about  $2\Omega$  +/- 30% is recommended).

Be careful of the temperature coefficient of ceramics: select X7R or X5R if possible, because those types typically vary less than +/– 25% over the range of –40 to +125°C. Z5U types are worse, and will typically lose half (or more) of their capacitance over the same temperature range.

A source for large-value ceramics with good performance is Taiyo-Yuden. Their web address is :

http://www.t-yuden.com/hicap.html

**Tantalum capacitors** have ESR values that are more difficult to determine: the manufacturers specify only a maximum limit, which is typically 10X or 20X the typical value. ESR values can vary considerably from lot to lot and from manufacturer to manufacturer. For example, some 4.7  $\mu$ F/10V devices tested showed typical values in the range of 0.5 - 1 $\Omega$ , but values as high as 6 $\Omega$  have been seen.

It should also be noted that the ESR typically increases about 2X - 3X when going from +125°C down to -40°C.

Another factor to consider is that Tantalum manufacturers are presently designing their products toward the goal of getting the lowest possible ESR, in an attempt to compete with the new high-value ceramic capacitors. This means that the typical values will probably continue to decline in the future.

#### **SELECTING THE OUTPUT CAPACITOR**

This section contains guidelines for selecting an output capacitor which will maintain good regulator stability over the entire operating temperature range (refer to **ESR CURVES**).

#### 2.2 µF Output Capacitor

The smallest output capacitor which can be used with the LP2980-1.8 is  $2.2\,\mu\text{F}$ . However, care must be exercised if this value is used because of the ESR requirement.

At load currents  $\leq$  25mA, the stable ESR range is approximately 0.5 $\Omega$  to 6 $\Omega$ . This range is probably sufficiently wide that most 2.2  $\mu$ F Tantalum capacitors would fall within it.

At higher values of load currents (using a 2.2  $\mu$ F output capacitor), the stable ESR window gets very narrow. It is likely that a Tantalum capacitor would not be a good choice for a design that must be robust enough for mass production. Instead, a 2.2  $\mu$ F capacitor with very low ESR (either ceramic or film) should be used with a  $2\Omega$  external resistor placed in series to provide the ESR.

#### 4.7 µF Output Capacitor

If a 4.7  $\mu F$  capacitor is used, the stable range of ESR values for 50 mA operation is approximately  $0.6\Omega$  to  $6\Omega$ . Because of the reduced ESR values of the new Tantalum, it is possible to find 4.7  $\mu F$  Tantalum capacitors with ESR values at or below  $0.6\Omega$ . To ensure a stable design, it is recommended that an external resistor (value about  $0.5\Omega$ ) be added in series with the 4.7  $\mu F$  Tantalum to provide adequate minimum ESR.

At values of load current ≤ 20 mA, the ESR range is wide enough that Tantalum can be used without external resistance for added ESR.

Another acceptable configuration for 50 mA operation is to use a ceramic or film 4.7  $\mu$ F capacitor (which has very low ESR) with an external  $2\Omega$  resistor in series.

#### 10 μF Output Capacitor

50 mA operation using a 10  $\mu$ F output capacitor requires an ESR in the range of approximately  $0.4\Omega$  to  $7\Omega$ . As stated previously, it is possible that solid Tantalum capacitors can be found with ESR values near to or below  $0.4\Omega$ . An external resistor in series with the Tantalum (value of about  $0.5\Omega$ ) is recommended to assure unconditional stability.

At values of load current ≤ 20 mA, the ESR range is wide enough that Tantalum can be used without external resistance for added ESR.

Another acceptable configuration for 50 mA operation is to use a ceramic or film 10  $\mu$ F capacitor (which has very low ESR) with an external  $2\Omega$  resistor in series.

#### 15 µF Output Capacitor

The stable ESR range (for 50 mA load current) using a 15  $\mu$ F output capacitor is approximately 0.1 $\Omega$  to 10 $\Omega$ . It is extremely unlikely that a 15  $\mu$ F Tantalum capacitor would be found with

an ESR below  $0.1\Omega$ , so no external resistance is required with a Tantalum

As before, another acceptable configuration for 50 mA operation is to use a ceramic or film 15  $\mu F$  capacitor with an external  $2\Omega$  resistor in series.

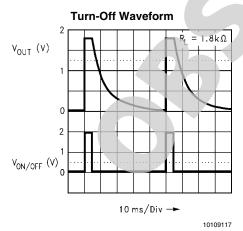

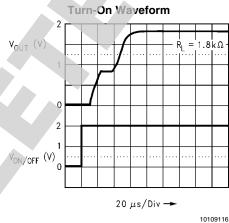

#### **ON/OFF INPUT OPERATION**

The LP2980 is shut off by pulling the ON/OFF input low, and turned on by pulling it high. If this feature is not to be used, this pin should be tied to  $V_{\rm IN}$  to keep the regulator on at all times.

To ensure proper operation, the signal source used to drive the ON/OFF input must be able to swing above and below the specified turn-on/turn-off voltage thresholds (see Electrical Characteristics).

It is also important that the turn-on (and turn-off) voltage signals applied to the ON/OFF input have a slew rate which is not less than 40 mV/µs.

**CAUTION:** The regulator output state can not be guaranteed if a slow-moving AC (or DC) signal is applied that it is in the range between the turn-on/turn-off voltage thresholds specified in the Electrical Characteristics section.

#### REVERSE INPUT/OUTPUT VOLTAGE

The PNP power transistor used as the pass element in the LP2980 has an inherent diode connected between the regulator output and input. During normal operation (where the input voltage is higher than the output) this diode is reverse-biased.

However, if the output is pulled above the input, this diode will turn ON and current will flow into the regulator output. In such cases, a parasitic SCR can latch which will allow a high current to flow into  $V_{\text{IN}}$  (and out the ground pin), which can damage the part.

In any application where the output may be pulled above the input, an external Schottky diode must be connected from  $V_{\text{IN}}$  to  $V_{\text{OUT}}$  (cathode on  $V_{\text{IN}}$ , anode on  $V_{\text{OUT}}$ ), to limit the reverse voltage across the LP2980 to 0.3V (see Basic Application Circuit).

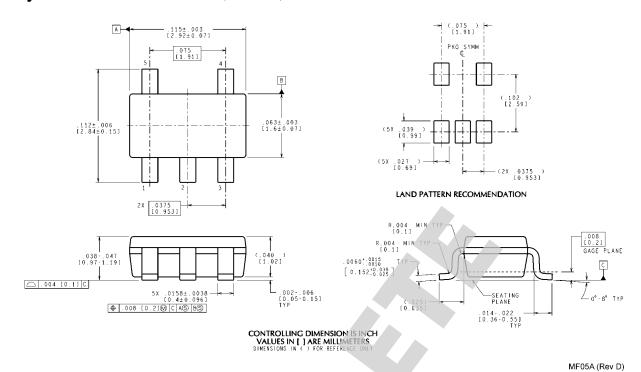

# Physical Dimensions inches (millimeters) unless otherwise noted

5-Lead Small Outline Package (M5)

NS Package Number MF05A

For Order Numbers, refer to *Table 1* in the "Order Information" section of this document.

NOTES: UNLESS OTHERWISE SPECIFIED

- 1. EPOXY COATING

- 2. 63Sn/37Pb EUTECTIC BUMP

- 3. RECOMMEND NON-SOLDER MASK DEFINED LANDING PAD.

- 4. PIN 1 IS ESTABLISHED BY LOWER LEFT CORNER WITH RESPECT TO TEXT ORIENTATION. REMAINING PINS ARE NUMBERED COUNTER CLOCK-

- 5. XXX IN DRAWING NUMBER REPRESENTS PACKAGE SIZE VARIATION WHERE X1 IS PACKAGE WIDTH, X2 IS PACKAGE LENGTH AND X3 IS PACK-AGE HEIGHT.

- 6.NO JEDEC REGISTRATION AS OF AUG.1999.

micro SMD, 5 Bump, Package (BPA05)

NS Package Number BPA05A

For Order Numbers, refer to Table 1in the "Ordering Information" section of this document.

The dimensions for X1, X2 and X3 are as given: X1 = 0.930 + -0.030 mm

X2 = 1.107 +/- 0.030mm

X3 = 0.850 + - 0.050mm

## **Notes**

For more National Semiconductor product information and proven design tools, visit the following Web sites at:

| Pr                             | oducts                       | Design Support          |                                |  |  |

|--------------------------------|------------------------------|-------------------------|--------------------------------|--|--|

| Amplifiers                     | www.national.com/amplifiers  | WEBENCH® Tools          | www.national.com/webench       |  |  |

| Audio                          | www.national.com/audio       | App Notes               | www.national.com/appnotes      |  |  |

| Clock and Timing               | www.national.com/timing      | Reference Designs       | www.national.com/refdesigns    |  |  |

| Data Converters                | www.national.com/adc         | Samples                 | www.national.com/samples       |  |  |

| Interface                      | www.national.com/interface   | Eval Boards             | www.national.com/evalboards    |  |  |

| LVDS                           | www.national.com/lvds        | Packaging               | www.national.com/packaging     |  |  |

| Power Management               | www.national.com/power       | Green Compliance        | www.national.com/quality/green |  |  |

| Switching Regulators           | www.national.com/switchers   | Distributors            | www.national.com/contacts      |  |  |

| LDOs                           | www.national.com/ldo         | Quality and Reliability | www.national.com/quality       |  |  |

| LED Lighting                   | www.national.com/led         | Feedback/Support        | www.national.com/feedback      |  |  |

| Voltage Reference              | www.national.com/vref        | Design Made Easy        | www.national.com/easy          |  |  |

| PowerWise® Solutions           | www.national.com/powerwise   | Solutions               | www.national.com/solutions     |  |  |

| Serial Digital Interface (SDI) | www.national.com/sdi         | Mil/Aero                | www.national.com/milaero       |  |  |

| Temperature Sensors            | www.national.com/tempsensors | Solar Magic®            | www.national.com/solarmagic    |  |  |

| Wireless (PLL/VCO)             | www.national.com/wireless    | Analog University®      | www.national.com/AU            |  |  |

THE CONTENTS OF THIS DOCUMENT ARE PROVIDED IN CONNECTION WITH NATIONAL SEMICONDUCTOR CORPORATION ("NATIONAL") PRODUCTS. NATIONAL MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE ACCURACY OR COMPLETENESS OF THE CONTENTS OF THIS PUBLICATION AND RESERVES THE RIGHT TO MAKE CHANGES TO SPECIFICATIONS AND PRODUCT DESCRIPTIONS AT ANY TIME WITHOUT NOTICE. NO LICENSE, WHETHER EXPRESS, IMPLIED, ARISING BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS

TESTING AND OTHER QUALITY CONTROLS ARE USED TO THE EXTENT NATIONAL DEEMS NECESSARY TO SUPPORT NATIONAL'S PRODUCT WARRANTY. EXCEPT WHERE MANDATED BY GOVERNMENT REQUIREMENTS, TESTING OF ALL PARAMETERS OF EACH PRODUCT IS NOT NECESSARILY PERFORMED. NATIONAL ASSUMES NO LIABILITY FOR APPLICATIONS ASSISTANCE OR BUYER PRODUCT DESIGN. BUYERS ARE RESPONSIBLE FOR THEIR PRODUCTS AND APPLICATIONS USING NATIONAL COMPONENTS. PRIOR TO USING OR DISTRIBUTING ANY PRODUCTS THAT INCLUDE NATIONAL COMPONENTS, BUYERS SHOULD PROVIDE ADEQUATE DESIGN, TESTING AND OPERATING SAFEGUARDS.

EXCEPT AS PROVIDED IN NATIONAL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NATIONAL ASSUMES NO LIABILITY WHATSOEVER, AND NATIONAL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE AND/OR USE OF NATIONAL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other brand or product names may be trademarks or registered trademarks of their respective holders.

Copyright© 2008 National Semiconductor Corporation

For the most current product information visit us at www.national.com

National Semiconductor Americas Technical Support Center Email: support@nsc.com ww.national.com Tel: 1-800-272-9959

National Semiconductor Europe **Technical Support Center** Email: europe.support@nsc.com German Tel: +49 (0) 180 5010 771 English Tel: +44 (0) 870 850 4288

National Semiconductor Asia Pacific Technical Support Center Email: ap.support@nsc.com

National Semiconductor Japan **Technical Support Center** Email: ipn.feedback@nsc.com

101091 Version 6 Revision 1 Print Date/Time: 2008/12/05 10:23:42