# M30245 Group User's Manual

RENESAS 16-BIT SINGLE-CHIP MICROCOMPUTER

M16C FAMILY / M16C/20 SERIES

All information contained in these materials, including products and product specifications, represents information on the product at the time of publication and is subject to change by Renesas Technology Corp. without notice. Please review the latest information published by Renesas Technology Corp. through various means, including the Renesas Technology Corp. website (http://www.renesas.com).

Rev. 2.00

Revision date: Oct 16, 2006

Renesas Technology www.renesas.com

#### Notes regarding these materials

- This document is provided for reference purposes only so that Renesas customers may select the appropriate Renesas products for their use. Renesas neither makes warranties or representations with respect to the accuracy or completeness of the information contained in this document nor grants any license to any intellectual property rights or any other rights of Renesas or any third party with respect to the information in this document.

- 2. Renesas shall have no liability for damages or infringement of any intellectual property or other rights arising out of the use of any information in this document, including, but not limited to, product data, diagrams, charts, programs, algorithms, and application circuit examples.

- 3. You should not use the products or the technology described in this document for the purpose of military applications such as the development of weapons of mass destruction or for the purpose of any other military use. When exporting the products or technology described herein, you should follow the applicable export control laws and regulations, and procedures required by such laws and regulations.

- 4. All information included in this document such as product data, diagrams, charts, programs, algorithms, and application circuit examples, is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas products listed in this document, please confirm the latest product information with a Renesas sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas such as that disclosed through our website. (http://www.renesas.com)

- 5. Renesas has used reasonable care in compiling the information included in this document, but Renesas assumes no liability whatsoever for any damages incurred as a result of errors or omissions in the information included in this document.

- 6. When using or otherwise relying on the information in this document, you should evaluate the information in light of the total system before deciding about the applicability of such information to the intended application. Renesas makes no representations, warranties or guaranties regarding the suitability of its products for any particular application and specifically disclaims any liability arising out of the application and use of the information in this document or Renesas products.

- 7. With the exception of products specified by Renesas as suitable for automobile applications, Renesas products are not designed, manufactured or tested for applications or otherwise in systems the failure or malfunction of which may cause a direct threat to human life or create a risk of human injury or which require especially high quality and reliability such as safety systems, or equipment or systems for transportation and traffic, healthcare, combustion control, aerospace and aeronautics, nuclear power, or undersea communication transmission. If you are considering the use of our products for such purposes, please contact a Renesas sales office beforehand. Renesas shall have no liability for damages arising out of the uses set forth above.

- 8. Notwithstanding the preceding paragraph, you should not use Renesas products for the purposes listed below:

- (1) artificial life support devices or systems

- (2) surgical implantations

- (3) healthcare intervention (e.g., excision, administration of medication, etc.)

- (4) any other purposes that pose a direct threat to human life

- Renesas shall have no liability for damages arising out of the uses set forth in the above and purchasers who elect to use Renesas products in any of the foregoing applications shall indemnify and hold harmless Renesas Technology Corp., its affiliated companies and their officers, directors, and employees against any and all damages arising out of such applications.

- 9. You should use the products described herein within the range specified by Renesas, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas shall have no liability for malfunctions or damages arising out of the use of Renesas products beyond such specified ranges.

- 10. Although Renesas endeavors to improve the quality and reliability of its products, IC products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Please be sure to implement safety measures to guard against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other applicable measures. Among others, since the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 11. In case Renesas products listed in this document are detached from the products to which the Renesas products are attached or affixed, the risk of accident such as swallowing by infants and small children is very high. You should implement safety measures so that Renesas products may not be easily detached from your products. Renesas shall have no liability for damages arising out of such detachment.

- 12. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written approval from Renesas.

- 13. Please contact a Renesas sales office if you have any questions regarding the information contained in this document. Renesas semiconductor products, or if you have any other inquiries.

#### General Precautions in the Handling of MPU/MCU Products

The following usage notes are applicable to all MPU/MCU products from Renesas. For detailed usage notes on the products covered by this manual, refer to the relevant sections of the manual. If the descriptions under General Precautions in the Handling of MPU/MCU Products and in the body of the manual differ from each other, the description in the body of the manual takes precedence.

#### 1. Handling of Unused Pins

Handle unused pins in accord with the directions given under Handling of Unused Pins in the manual.

— The input pins of CMOS products are generally in the high-impedance state. In operation with an unused pin in the open-circuit state, extra electromagnetic noise is induced in the vicinity of LSI, an associated shoot-through current flows internally, and malfunctions occur due to the false recognition of the pin state as an input signal become possible. Unused pins should be handled as described under Handling of Unused Pins in the manual.

#### 2. Processing at Power-on

The state of the product is undefined at the moment when power is supplied.

- The states of internal circuits in the LSI are indeterminate and the states of register settings and pins are undefined at the moment when power is supplied.

In a finished product where the reset signal is applied to the external reset pin, the states of pins are not guaranteed from the moment when power is supplied until the reset process is completed.

In a similar way, the states of pins in a product that is reset by an on-chip power-on reset function are not guaranteed from the moment when power is supplied until the power reaches the level at which resetting has been specified.

- 3. Prohibition of Access to Reserved Addresses

Access to reserved addresses is prohibited.

— The reserved addresses are provided for the possible future expansion of functions. Do not access these addresses; the correct operation of LSI is not guaranteed if they are accessed.

#### 4. Clock Signals

After applying a reset, only release the reset line after the operating clock signal has become stable. When switching the clock signal during program execution, wait until the target clock signal has stabilized.

- When the clock signal is generated with an external resonator (or from an external oscillator) during a reset, ensure that the reset line is only released after full stabilization of the clock signal. Moreover, when switching to a clock signal produced with an external resonator (or by an external oscillator) while program execution is in progress, wait until the target clock signal is stable.

- 5. Differences between Products

Before changing from one product to another, i.e. to one with a different type number, confirm that the change will not lead to problems.

— The characteristics of MPU/MCU in the same group but having different type numbers may differ because of the differences in internal memory capacity and layout pattern. When changing to products of different type numbers, implement a system-evaluation test for each of the products.

### How to Use This Manual

This user's manual is written for the M30245 group.

The reader of this manual is expected to have the basic knowledge of electric and logic circuits and microcomputers.

This manual explains a function of the following kind.

- M30245M8-XXXGP

- M30245MC-XXXGP

- M30245FCGP

These products have similar features except for the memories, which differ from one product to another. Be careful when writing a program, as the memories have different capacities.

| RAM Size<br>(Byte) | 1                               |                                                                    |                    |

|--------------------|---------------------------------|--------------------------------------------------------------------|--------------------|

| 10K                |                                 | Flash memory version:M30245FCGP<br>Mask ROM version:M30245MC-XXXGP |                    |

| 5K                 | Mask ROM version:M30245M8-XXXGP |                                                                    |                    |

|                    | 64K                             | 128K                                                               | ROM Size<br>(Byte) |

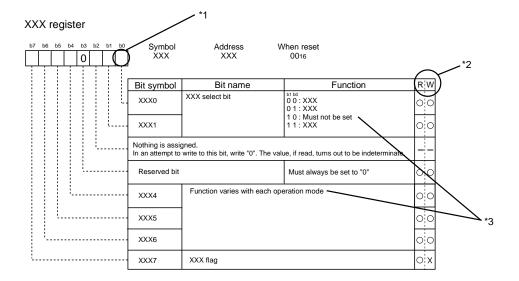

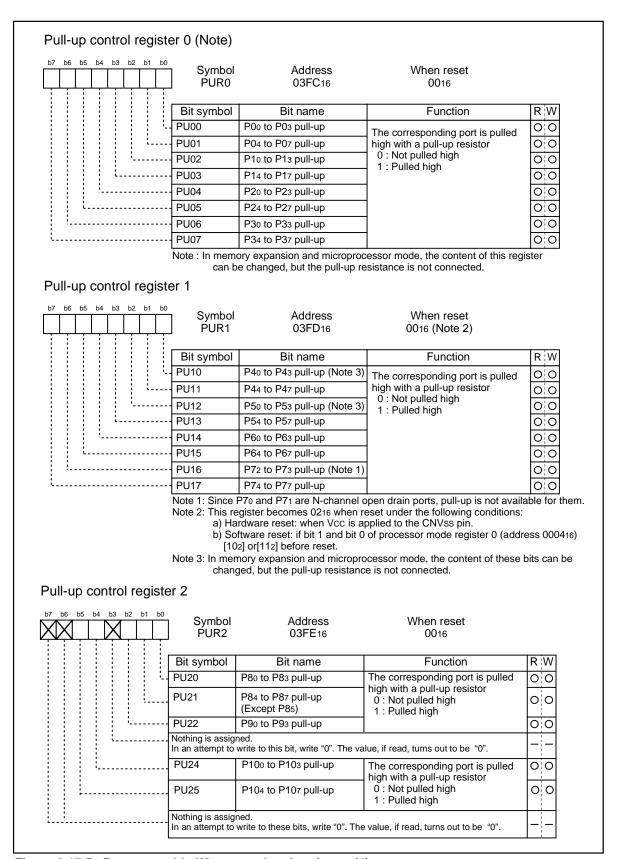

The figure of each register configuration describes its functions and attributes as follows:

\*1

Blank: Set to "0" or "1" according to intended use

0: Set to "0"

1: Set to "1"

X: Nothing is assigned

\*2

R: Read

O.....Possible to read

X.....Impossible to read

-....Nothing is assigned

W: Write

O.....Possible to write

X.....Written value is invalid

When write, value can be "0" or "1"

-....Nothing is assigned

\*3

Terms to use here are explained as follows.

Nothing is assigned

Nothing is assigned to the bit concerned. When write, set "0" for new function in future plan.

• Must not be set

Not select. The operation at having selected is not guaranteed.

• Reserved bit

Reserved bit. Set the specified value.

• Function varies with each operation mode

Bit function changes according to the mode of peripheral functions.

• Always set to "0" in A mode.

Set the corresponding bit to "0" in A mode.

• Invalid in A mode

The bit concerned has no function in A mode. Set the specified value.

Valid when bit A="0"

When bit A is "1", the bit concerned has no function. When bit A is "0", the bit concerned has function.

### **Table of Contents**

| Chapter 1. Hardware                                                                 | 1  |

|-------------------------------------------------------------------------------------|----|

| Chapter 2. Peripheral Functions Usage                                               | 3  |

| 2.1 Protect                                                                         |    |

|                                                                                     |    |

| 2.1.1 Overview                                                                      |    |

| 2.1.2 Protect Operation                                                             |    |

| 2.2 Timer A                                                                         |    |

| 2.2.1 Overview                                                                      |    |

| 2.2.2 Operation of Timer A (timer mode)                                             |    |

| 2.2.3 Operation of Timer A (timer mode, gate function selected)                     |    |

| 2.2.4 Operation of Timer A (timer mode, pulse output function selected)             |    |

| 2.2.5 Operation of Timer A (event counter mode, reload type selected)               |    |

| 2.2.6 Operation of Timer A (event counter mode, free run type selected)             | 20 |

| 2.2.7 Operation of timer A (two-phase pulse signal process in event counter mode,   |    |

| normal mode selected)                                                               | 22 |

| 2.2.8 Operation of timer A (two-phase pulse signal process in event counter mode,   |    |

| multiply-by-4 mode selected)                                                        |    |

| 2.2.9 Operation of Timer A (one-shot timer mode)                                    |    |

| 2.2.10 Operation of Timer A (pulse width modulation mode, 16-bit PWM mode selected) |    |

| 2.2.11 Operation of Timer A (pulse width modulation mode, 8-bit PWM mode selected)  |    |

| 2.2.12 Precautions for Timer A (timer mode)                                         |    |

| 2.2.13 Precautions for Timer A (event counter mode)                                 |    |

| 2.2.14 Precautions for Timer A (one-shot timer mode)                                |    |

| 2.2.15 Precautions for Timer A (pulse width modulation mode)                        |    |

| 2.3 Clock-Synchronous Serial I/O                                                    | 39 |

| 2.3.1 Overview                                                                      | 39 |

| 2.3.2 Operation of Serial I/O (transmission in clock-synchronous serial I/O mode)   | 45 |

| 2.3.3 Operation of Serial I/O (reception in clock-synchronous serial I/O mode)      | 49 |

| 2.3.4 Precautions for Serial I/O (in clock-synchronous serial I/O mode)             | 53 |

| 2.4 Clock-Asynchronous Serial I/O (UART)                                            | 55 |

| 2.4.1 Overview                                                                      |    |

| 2.4.2 Operation of Serial I/O (transmission in UART mode)                           |    |

| 2.4.3 Operation of Serial I/O (reception in UART mode)                              |    |

| 2.4.4 Serial I/O Precautions (UART Mode)                                            |    |

| 2.4.5 Operation of Serial I/O (transmission used for SIM interface)                 |    |

| 2.4.6 Operation of Serial I/O (reception used for SIM interface)                    |    |

| 2.4.7 Clock Signals in used for the SIM Interface                                   |    |

| 2.5 Serial Interface Special Function                                               |    |

| 2.5.1 Overview                                                                      |    |

| 2.5.2 Operation of Serial Interface Special Function (transmission in master mode   |    |

| without delay)                                                                      | 94 |

|                                                                                     |    |

| 2.5.3 Operation of Serial Interface Special Function (reception in master mode with |     |

|-------------------------------------------------------------------------------------|-----|

| clock delay)                                                                        |     |

| 2.5.4 Operation of Serial Interface Special Function (transmission in slave mode    |     |

| without delay)                                                                      |     |

| clock delay)                                                                        |     |

| 2.6 Serial sound interface                                                          |     |

| 2.6.1 Overview                                                                      |     |

| 2.6.2 Example of Serial Sound Interface operation                                   | _   |

| 2.6.3 Precautions for Serial Sound Interface operation                              |     |

| 2.7 Frequency synthesizer (PLL)                                                     |     |

| 2.7.1 Overview                                                                      |     |

| 2.7.2 Operation of frequency synthesizer                                            |     |

| 2.7.3 Precautions for Frequency synthesizer                                         |     |

| 2.8 USB function                                                                    |     |

| 2.8.1 Overview                                                                      |     |

| 2.8.2 USB function control                                                          |     |

| 2.8.3 USB Interrupt                                                                 |     |

| 2.8.4 USB Operation (Suspend/Resume Function)                                       |     |

| 2.8.5 USB Operation (Endpoint 0)                                                    |     |

| 2.8.6 USB Operation (Endpoints 1 to 4 Receive)                                      |     |

| 2.8.7 USB Operation (Endpoints 1 to 4 Transmit)                                     |     |

| 2.8.8 USB Operation (Interface with DMAC Transfer)                                  |     |

| 2.8.9 Precautions for USB                                                           |     |

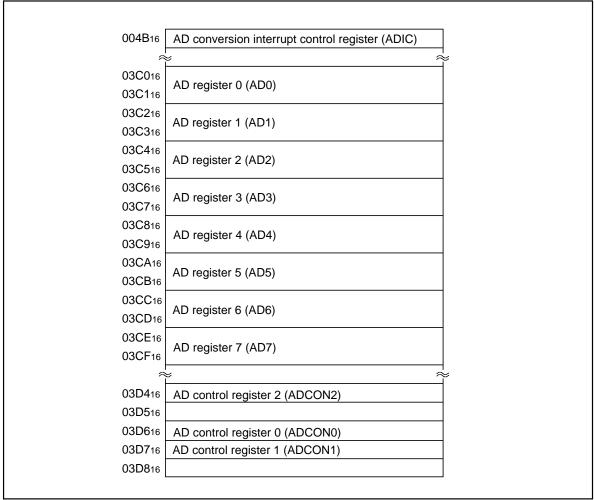

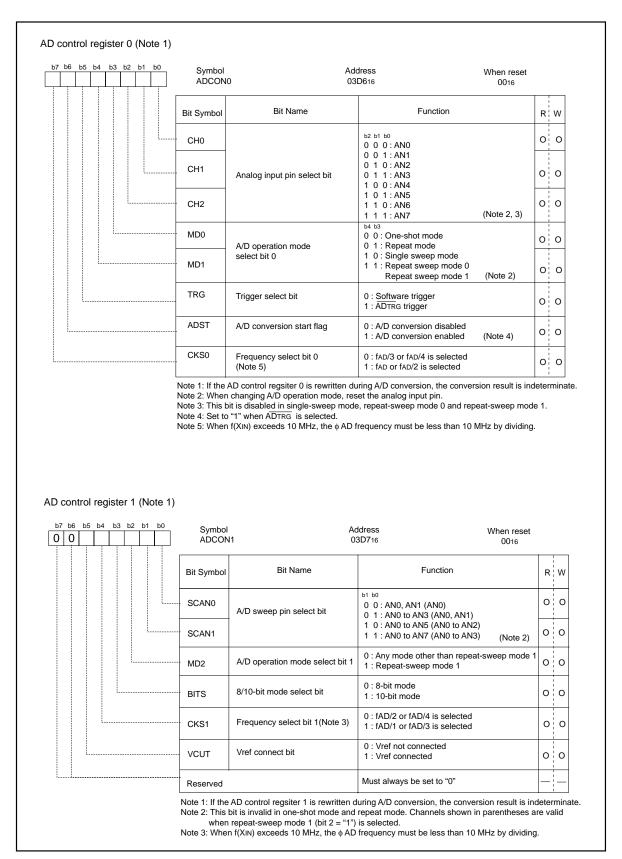

| 2.9 A/D Converter                                                                   | 213 |

| 2.9.1 Overview                                                                      | 213 |

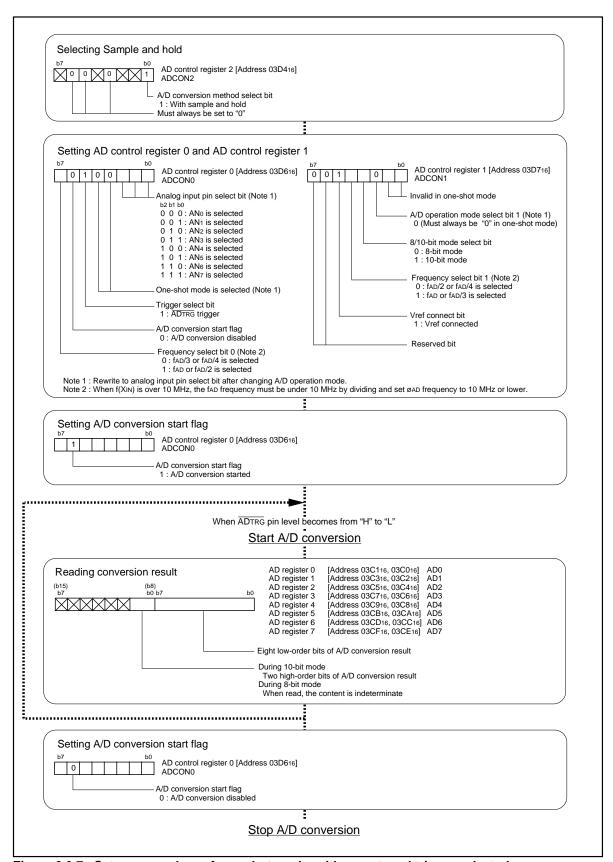

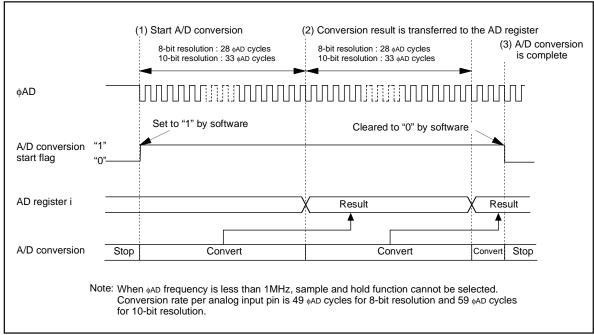

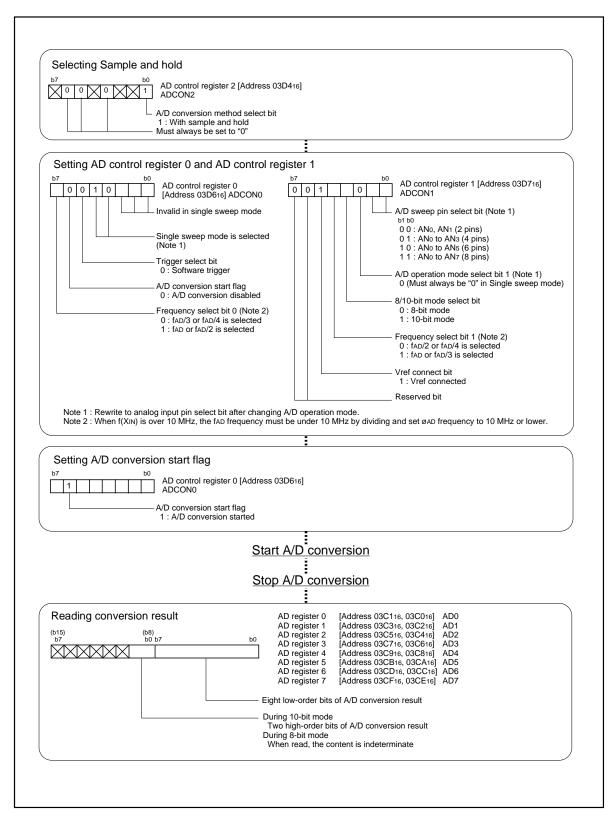

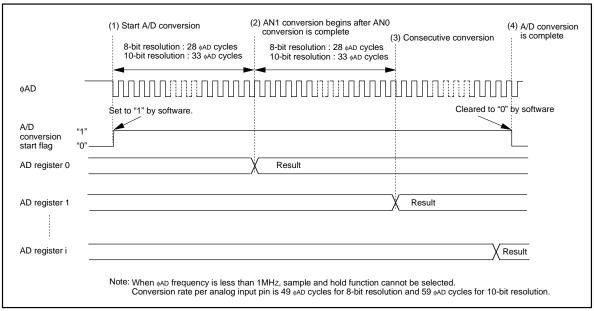

| 2.9.2 Operation of A/D converter (one-shot mode)                                    | 218 |

| 2.9.3 Operation of A/D Converter (in one-shot mode, an external trigger selected)   | 220 |

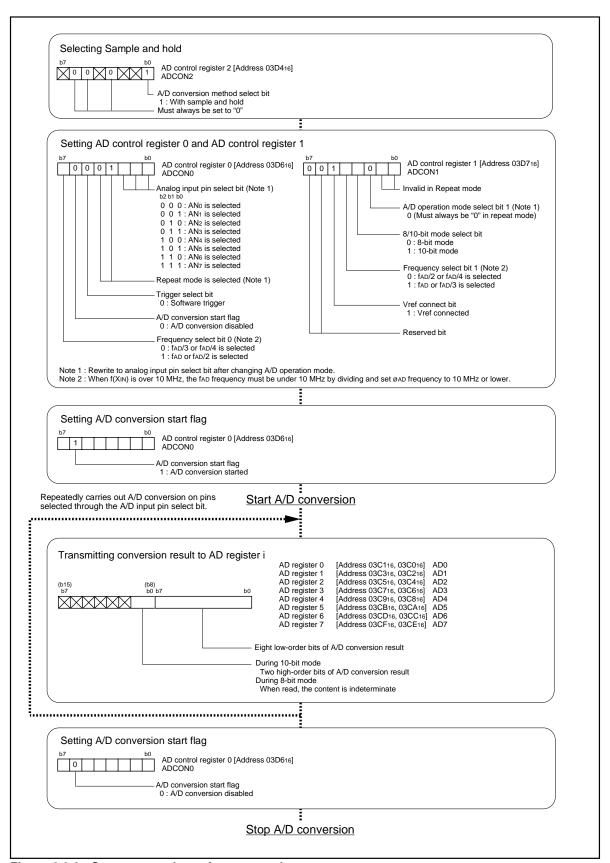

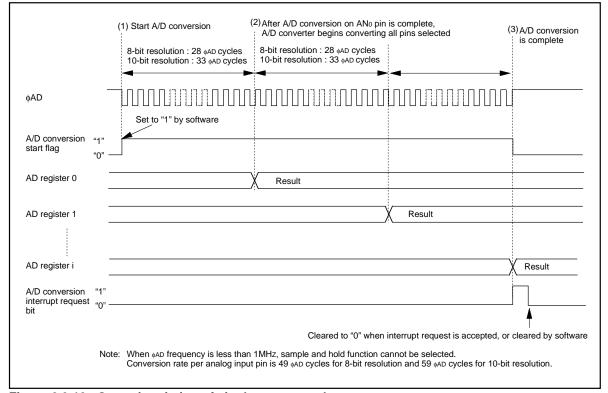

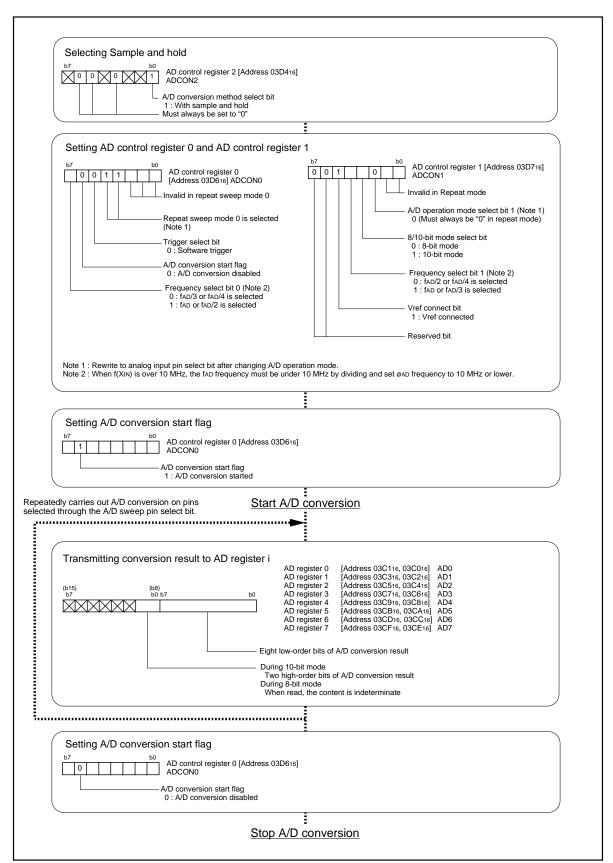

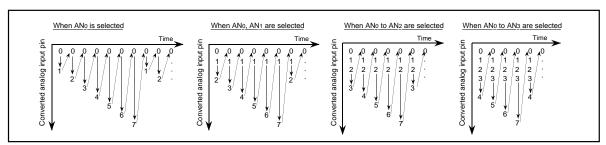

| 2.9.4 Operation of A/D Converter (in repeat mode)                                   | 222 |

| 2.9.5 Operation of A/D Converter (in single sweep mode)                             | 224 |

| 2.9.6 Operation of A/D Converter (in repeat sweep mode 0)                           | 226 |

| 2.9.7 Operation of A/D Converter (in repeat sweep mode 1)                           |     |

| 2.9.8 Precautions for A/D Converter                                                 | 230 |

| 2.9.9 Method of A/D Conversion (10-bit mode)                                        |     |

| 2.9.10 Method of A/D Conversion (8-bit mode)                                        |     |

| 2.9.11 Absolute Accuracy and Differential Non-Linearity Error                       |     |

| 2.9.12 Internal Equivalent Circuit of Analog Input                                  |     |

| 2.9.13 Sensor's Output Impedance under A/D Conversion (reference value)             |     |

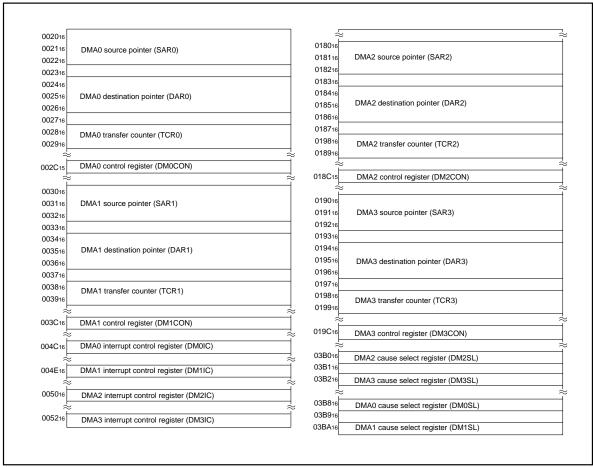

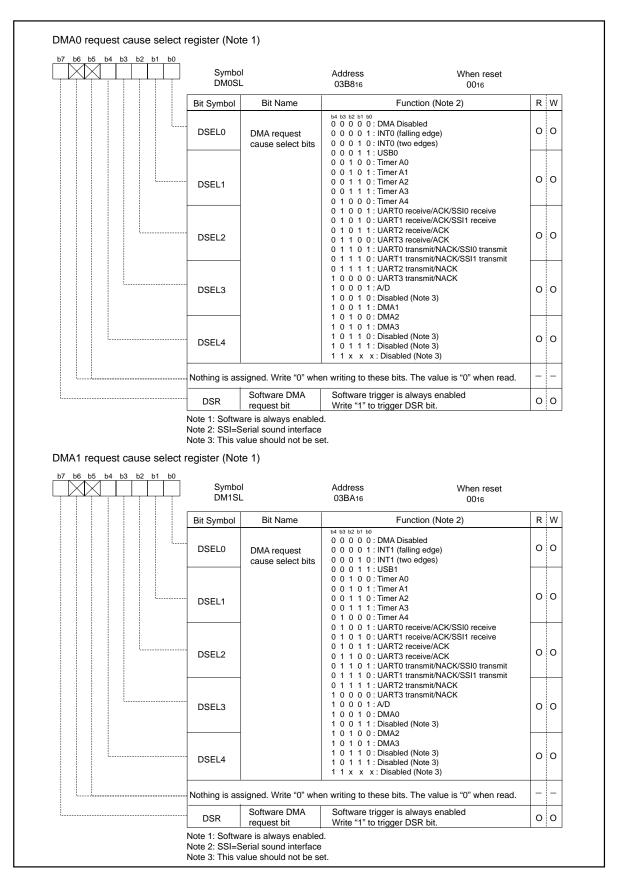

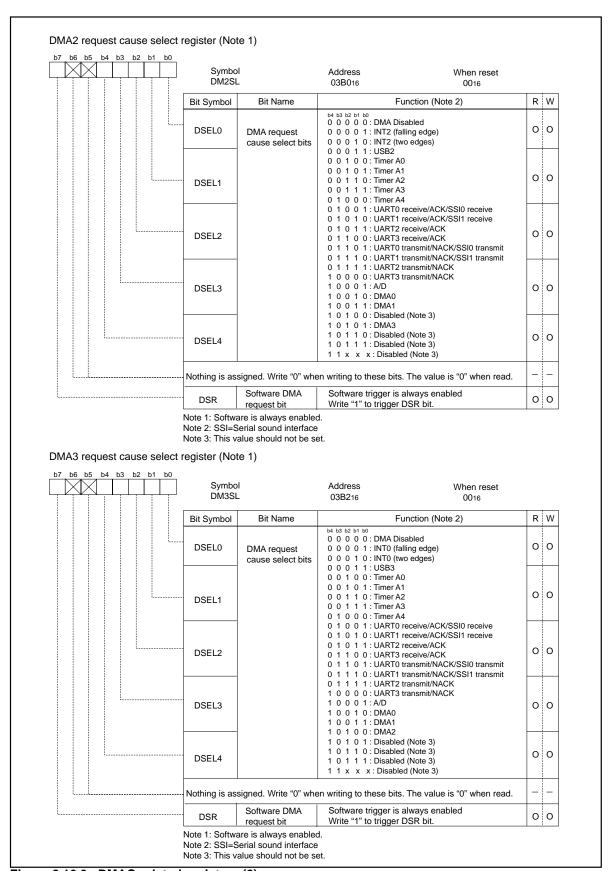

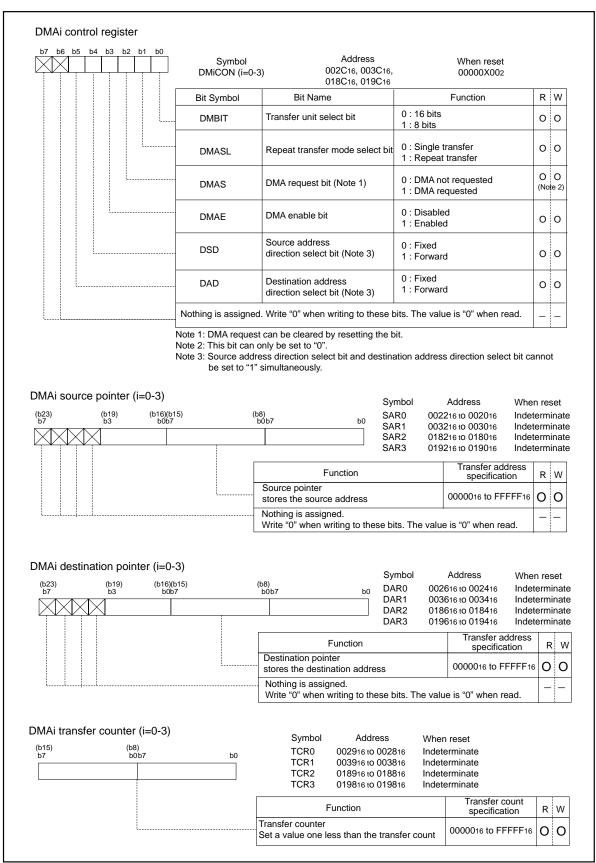

| 2.10 DMAC Usage                                                                     |     |

| 2.10.1 Overview of the DMAC usage                                                   |     |

| 2.10.2 Operation of DMAC (one-shot transfer mode)                                   |     |

| 2.10.3 Operation of DMAC (repeated transfer mode)                                   |     |

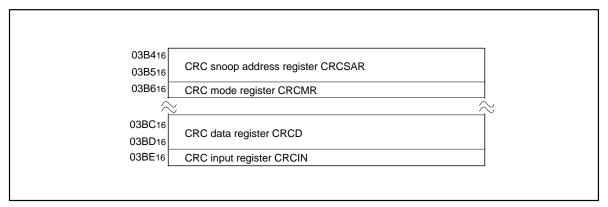

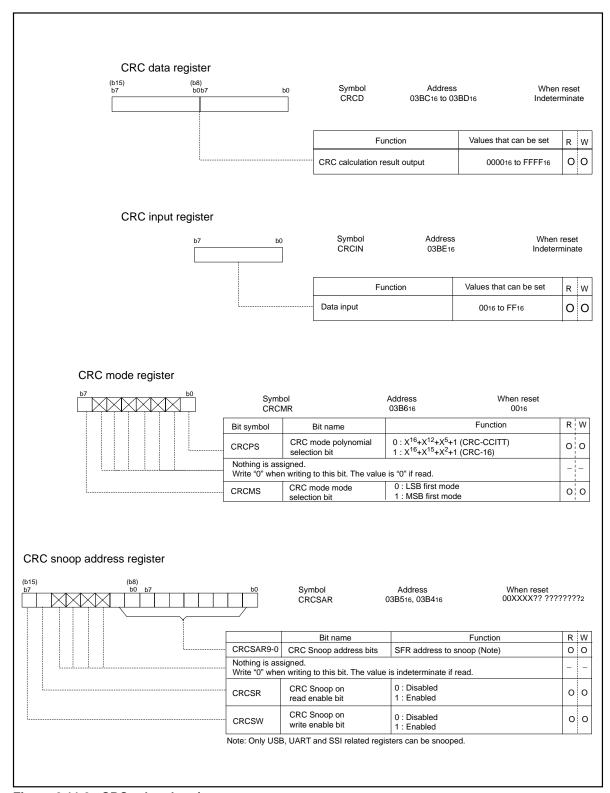

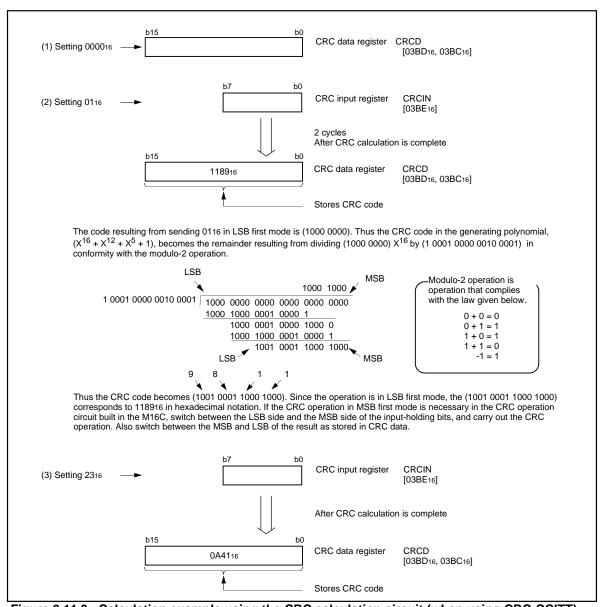

| 2.11 CRC Calculation Circuit                                                        |     |

| 2.11.1 Overview                                                                     |     |

| 2.11.2 Operation of CRC Calculation Circuit                                         |     |

| 2.11.3 SFR Access Snoop Function                                                    |     |

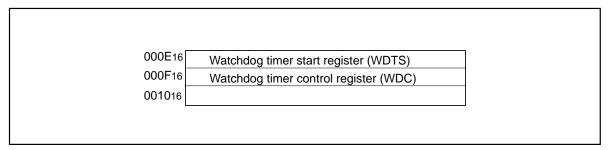

| 2.12 Watchdog Timer                                                                 | 253 |

| 2.12.1 Overview                                                    | 253 |

|--------------------------------------------------------------------|-----|

| 2.12.2 Operation of Watchdog Timer (Watchdog timer interrupt)      | 256 |

| 2.13 Address Match Interrupt Usage                                 | 258 |

| 2.13.1 Overview of the address match interrupt usage               | 258 |

| 2.13.2 Operation of Address Match Interrupt                        | 260 |

| 2.14 Key-Input Interrupt Usage                                     | 262 |

| 2.14.1 Overview of the key-input interrupt usage                   | 262 |

| 2.14.2 Operation of Key-Input Interrupt                            | 265 |

| 2.15 Multiple interrupts Usage                                     | 267 |

| 2.15.1 Overview of the Multiple interrupts usage                   | 267 |

| 2.15.2 Multiple Interrupts Operation                               | 272 |

| 2.16 Power Control Usage                                           | 274 |

| 2.16.1 Overview of the power control usage                         |     |

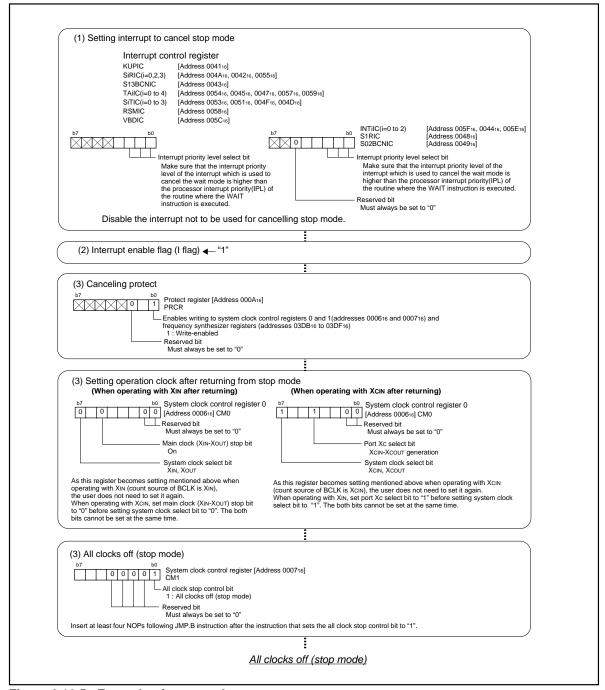

| 2.16.2 Stop Mode Set-Up                                            |     |

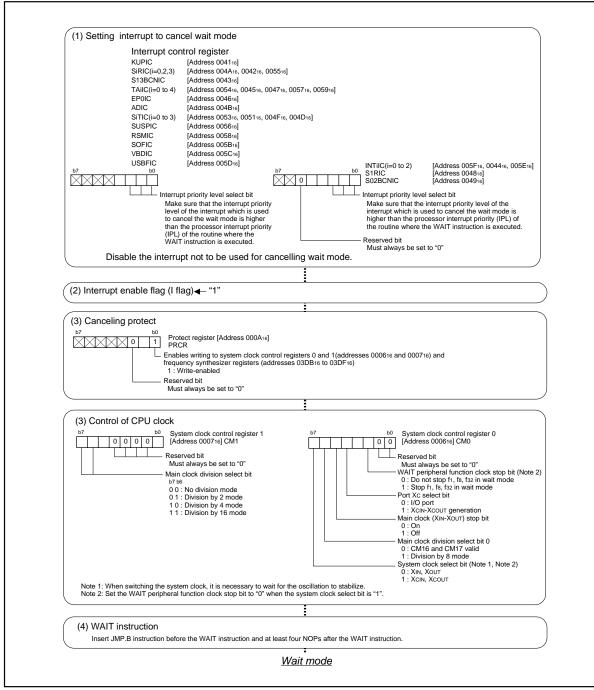

| 2.16.3 Wait Mode Set-Up                                            |     |

| 2.16.4 Precautions in Power Control                                |     |

| 2.17 Programmable I/O Ports Usage                                  |     |

| 2.17.1 Overview of the programmable I/O ports usage                | 284 |

| Chapter 3. Examples of Peripheral Functions                        |     |

|                                                                    |     |

| Applications                                                       |     |

| 3.1 Long-Period Timers                                             | 295 |

| 3.2 Variable-Period Variable-Duty PWM Output                       | 299 |

| 3.3 Buzzer Output                                                  | 303 |

| 3.4 Solution for External Interrupt Pins Shortage                  | 305 |

| 3.5 Memory to Memory DMA Transfer                                  |     |

| 3.7 Buzzer Output                                                  |     |

| 3.6 CRC Calculation SFR Access Snoop Function in Clock Synchronous |     |

| Serial Data Transmit                                               | 244 |

|                                                                    |     |

| 3.7 Transfer from USB FIFO to Serial Sound Interface               |     |

| 3.8 Controlling Power Using Stop Mode                              |     |

| 3.9 Controlling Power Using Wait Mode                              | 325 |

| Chapter 4. External Buses                                          | 320 |

| •                                                                  |     |

| 4.1 Overview of External Buses                                     |     |

| 4.2 Data Access                                                    |     |

| 4.2.1 Data Bus Width                                               |     |

| 4.2.2 Chip Selects and Address Bus                                 |     |

| 4.2.3 R/W Modes                                                    |     |

| 4.3 Connection Examples                                            |     |

| 4.3.1 16-bit Memory to 16-bit Width Data Bus Connection Example    |     |

| 4.3.2 8-bit Memory to 16-bit Width Data Bus Connection Example     | 335 |

| 4.3.3 8-bit Memory to 8-bit Width Data Bus Connection Example                 | 337 |

|-------------------------------------------------------------------------------|-----|

| 4.3.4 Two 8-bit and 16-Bit Memory to 16-Bit Width Data Bus Connection Example | 338 |

| 4.3.5 Chip Selects and Address Bus                                            | 339 |

| 4.4 Connectable Memories                                                      | 340 |

| 4.4.1 Operation Frequency and Access Time                                     | 340 |

| 4.4.2 Connecting Low-Speed Memory                                             | 343 |

| 4.4.3 Connectable Memories                                                    | 346 |

| 4.5 Releasing an External Bus (HOLD input and HLDA output)                    | 347 |

| 4.6 Precautions for External Bus                                              | 349 |

| Chapter 5. Standard Characteristics                                           | 351 |

| 5.1 DC Standard Characteristics                                               | 352 |

| 5.1.1 Port Standard Characteristics                                           | 352 |

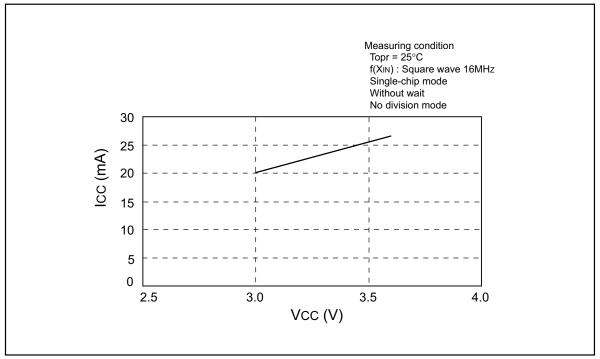

| 5.1.2 VCC-ICC Characteristics                                                 | 354 |

## Chapter 1

Hardware

### Chapter 2

Peripheral Functions Usage

M30245 Group 2. Protect

#### 2.1 Protect

#### 2.1.1 Overview

'Protect' is a function that causes a value held in a register to be unchanged even when a program runs away. The following is an overview of the protect function:

#### (1) Registers affected by the protect function

The registers affected by the protect function are:

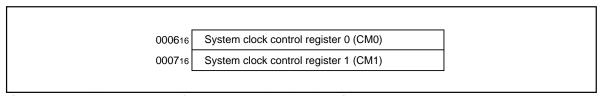

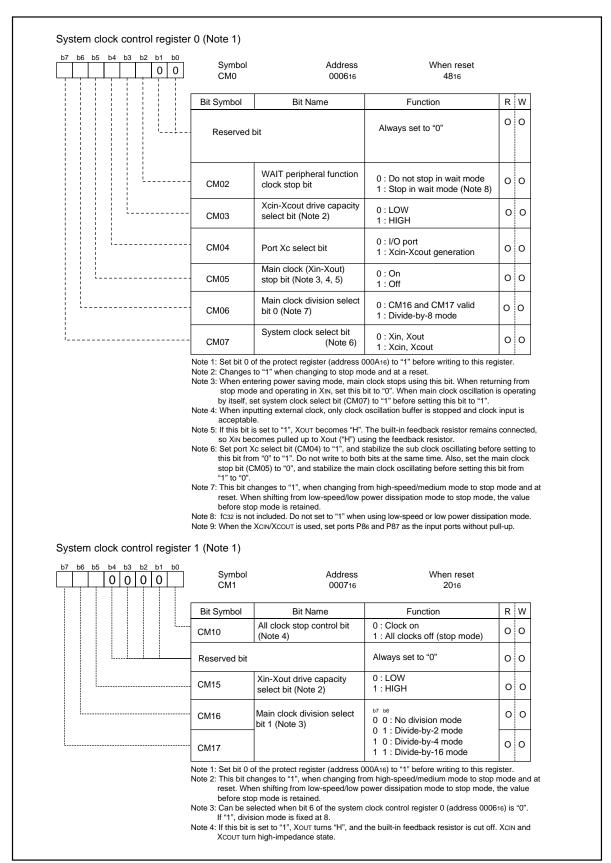

- (a) System clock control registers 0, 1 (addresses 000616 and 000716)

- (b) Processor mode registers 0, 1 (addresses 000416 and 000516)

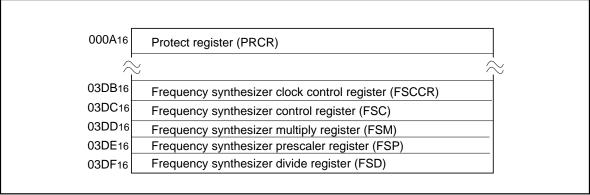

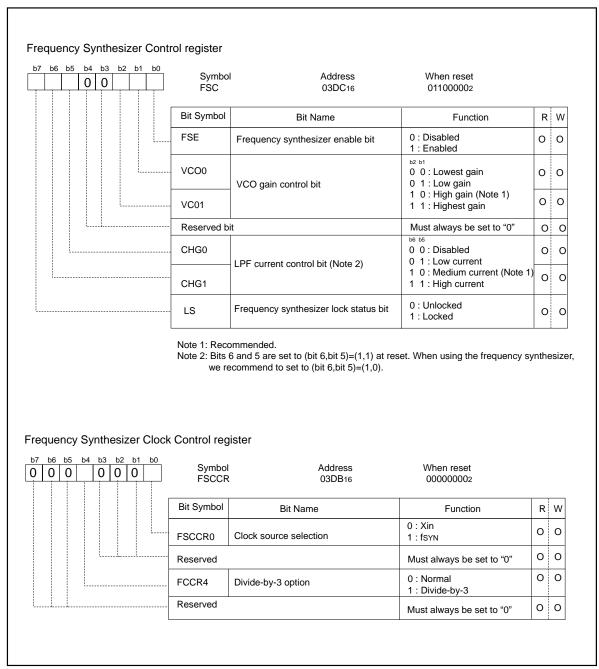

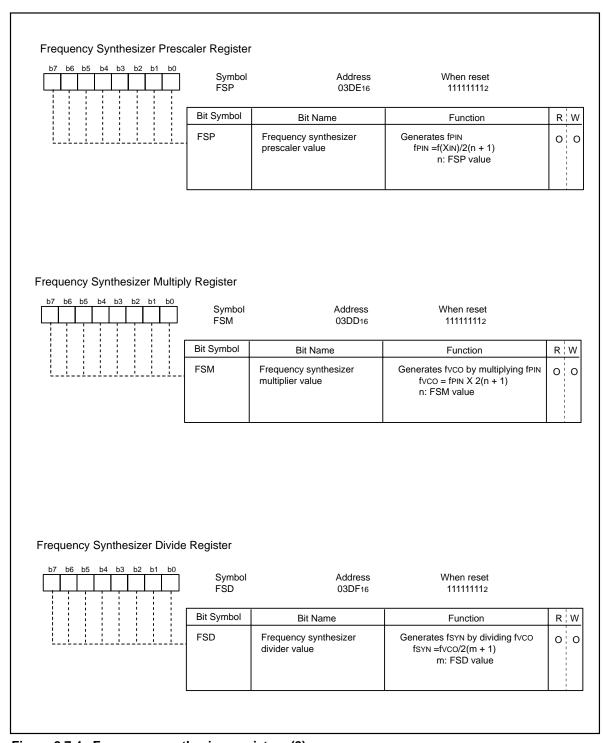

- (c) Frequency synthesizer-related registers (address 03DB16 to 03DF16)

The values in registers (a) through (c) cannot be changed in write-protect state. To change values in the registers, put the individual registers in write-enabled state.

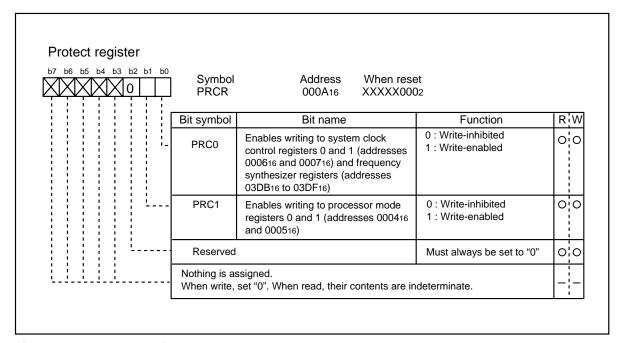

#### (2) Protect register

Figure 2.1.1 shows protect register.

Figure 2.1.1. Protect register

M30245 Group 2. Protect

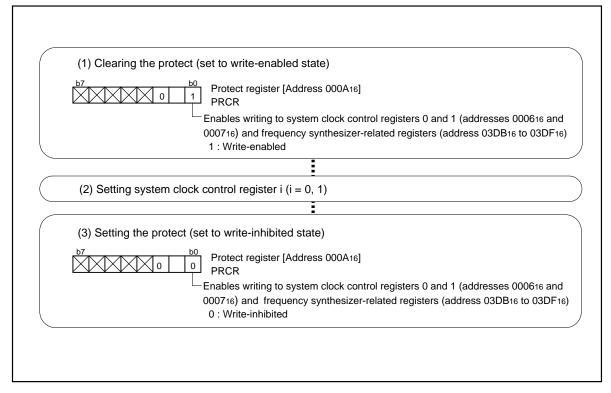

#### 2.1.2 Protect Operation

The following explains the protect operation. Figure 2.1.2 shows the set-up procedure.

Operation (1) Setting "1" in the write-enable bit of system clock control registers 0 and 1 and frequency synthesizer-related registers causes system clock control register 0 and 1 and frequency synthesizer-related registers to be in write-enabled state.

- (2) The contents of system clock control register 0 and 1 and these of frequency synthesizer-related registers are changed.

- (3) Setting "0" in PRC0 causes system clock control register 0 and 1 and frequency synthesizer-related registers to be in write-inhibited state.

- (4) To change the contents of processor mode register 0 and that of processor mode register 1, follow the same steps as in dealing with system clock control registers and frequency synthesizer-related registers.

Figure 2.1.2. Set-up procedure for protect function

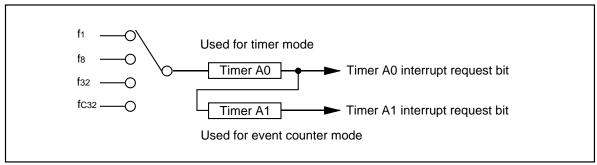

#### 2.2 Timer A

#### 2.2.1 Overview

The following is an overview for timer A, a 16-bit timer.

#### (1) Mode

Timer A operates in one of the four modes:

#### (a) Timer mode

In this mode, the internal count source is counted. Two functions can be selected: the pulse output function that reverses output from a port every time an overflow occurs, or the gate function which controls the count start/stop according to the input signal from a port.

#### (b) Event counter mode

This mode counts the pulses from the outside and the number of overflows in other timers. The freerun type, in which nothing is reloaded from the reload register, can be selected when an underflow occurs. The pulse output function can also be selected. Please refer to the timer mode explanation for details, as the operation is identical.

Furthermore, Timer A has a two-phase pulse signal processing function which generates an up count or down count in the event counter mode, depending on the phase of the two input signals. The normal mode or 4-multiplication mode can be selected depending on the phase detective method.

#### (c) One-shot timer mode

In this mode, the timer is started by the trigger and stops when the timer goes to "0". The trigger can be selected from the following 2 types: an overflow of the timer, or a software trigger. The pulse output function can also be selected. Please refer to the timer mode explanation for details, as the operation is identical.

#### (d) Pulse width modulation (PWM) mode

In this mode, the arbitrary pulses are successively output. Either a 16-bit fixed-period PWM mode or 8-bit variable-period mode can be selected. The trigger for initiating output can also be selected. Please refer to the one-shot timer mode explanation for details, as the operation is identical.

#### (2) Count source

The internal count source can be selected from f1, f8, f32, and fC32. Clocks f1, f8, and f32 are derived by dividing the CPU's main clock by 1, 8, and 32 respectively. Clock fC32 is derived by dividing the CPU's secondary clock by 32.

#### (3) Frequency division ratio

In timer mode or pulse width modulation mode, [the value set in the timer register + 1] becomes the frequency division ratio. In event counter mode, [the set value + 1] becomes the frequency division ratio when a down count is performed, or [FFFF16 - the set value + 1] becomes the frequency division ratio when an up count is performed. In one-shot timer mode, the value set in the timer register becomes the frequency division ratio.

The counter overflows (or underflows) when a count source equal to a frequency division ratio is input, and an interrupt occurs. For the pulse output function, the output from the port varies (the value in the port register does not vary).

#### (4) Reading the timer

Either in timer mode or in event counter mode, reading the timer register takes out the count at that moment. Read it in 16-bit units. The data either in one-shot timer mode or in pulse width modulation mode is indeterminate.

#### (5) Writing to the timer

To write to the timer register when a count is in progress, the value is written only to the reload register. When writing to the timer register when a count is stopped, the value is written both to the reload register and to the counter. Write a value in 16-bit units.

#### (6) Relation between the input/output to/from the timer and the direction register

With the output function of the timer, pulses are output regardless of the contents of the port direction register. To input an external signal to the timer, set the port direction register to input.

#### (7) Pins related to timer A

(a) TA0IN, TA1IN, TA2IN, TA3IN, TA4IN Input pins to timer A.

(b) TA00UT, TA10UT, TA20UT, TA30UT, TA40UT Output pins from timer A. They become input pins to

timer A when event counter mode is active.

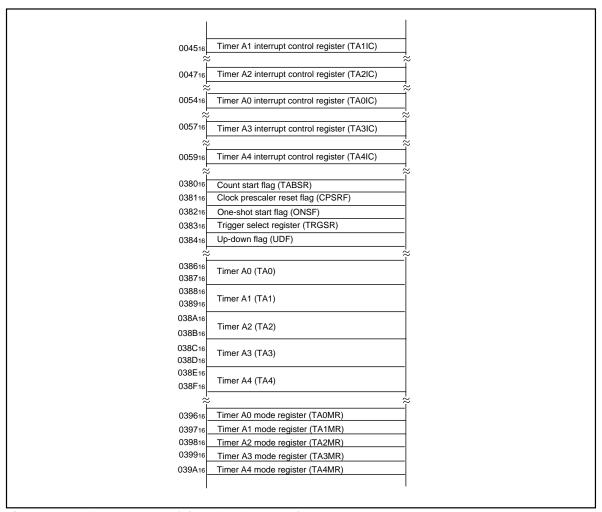

#### (8) Registers related to timer A

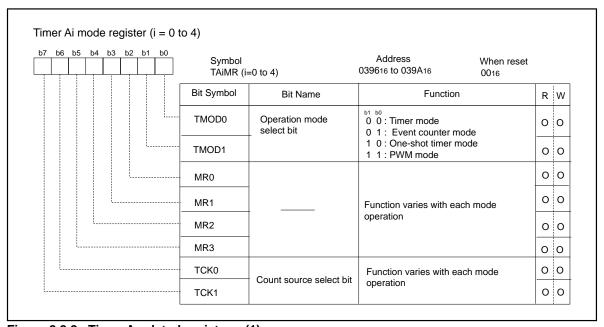

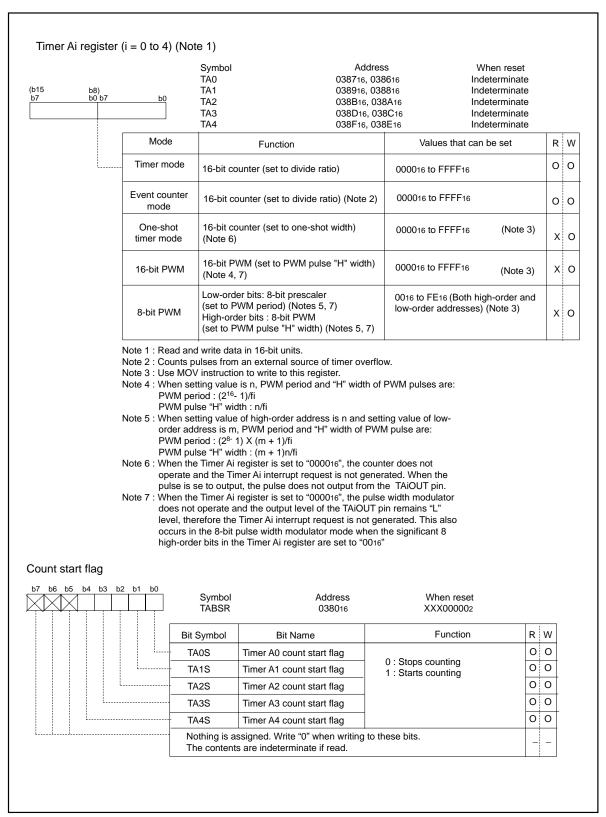

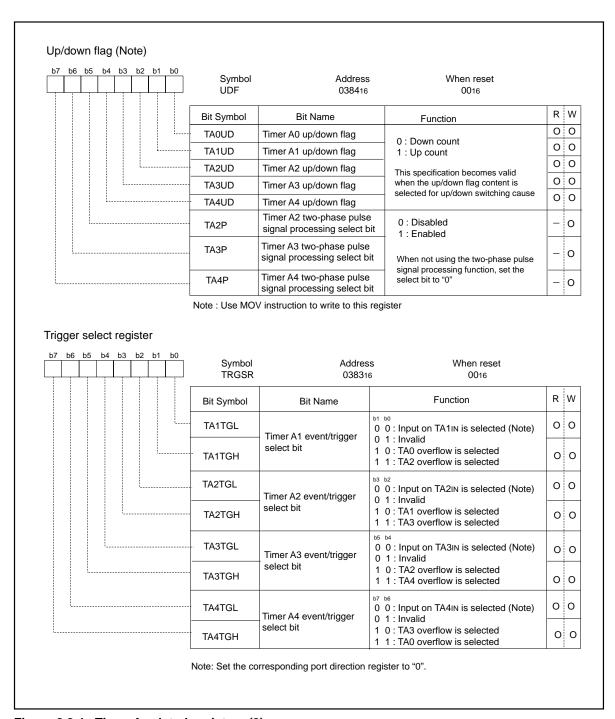

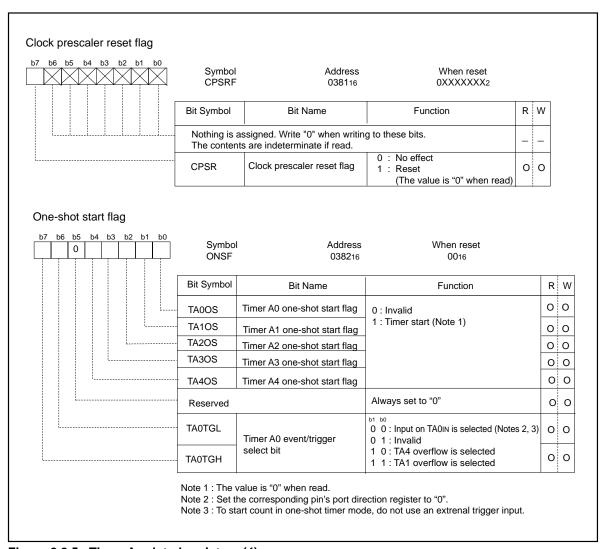

Figure 2.2.1 shows the memory map of timer A-related registers. Figures 2.2.2 through 2.2.5 show timer A-related registers.

Figure 2.2.1. Memory map of timer A-related registers

Figure 2.2.2. Timer A-related registers (1)

Figure 2.2.3. Timer A-related registers (2)

Figure 2.2.4. Timer A-related registers (3)

Figure 2.2.5. Timer A-related registers (4)

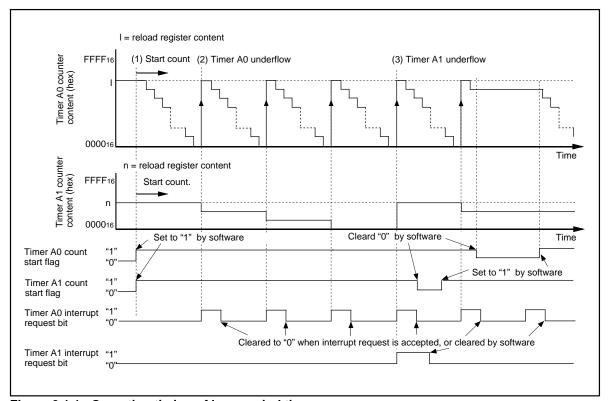

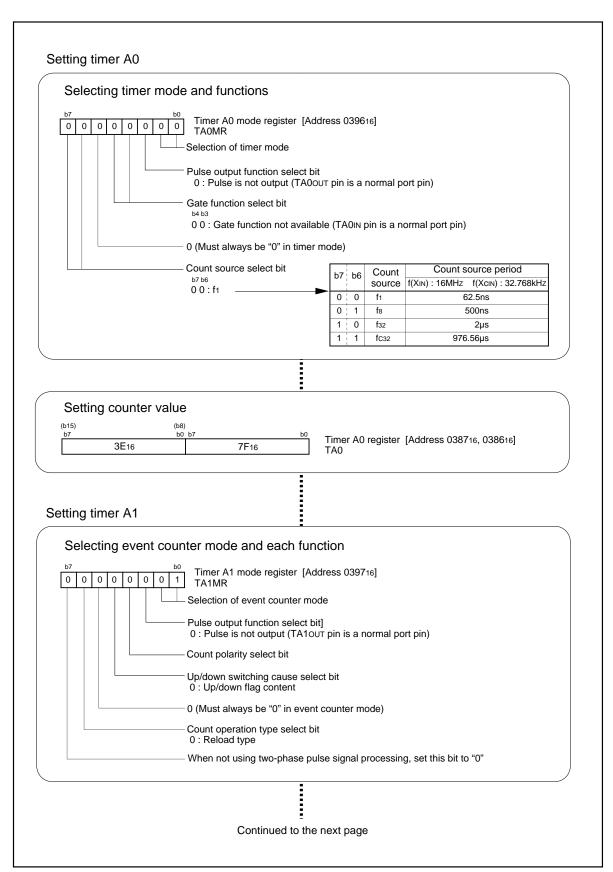

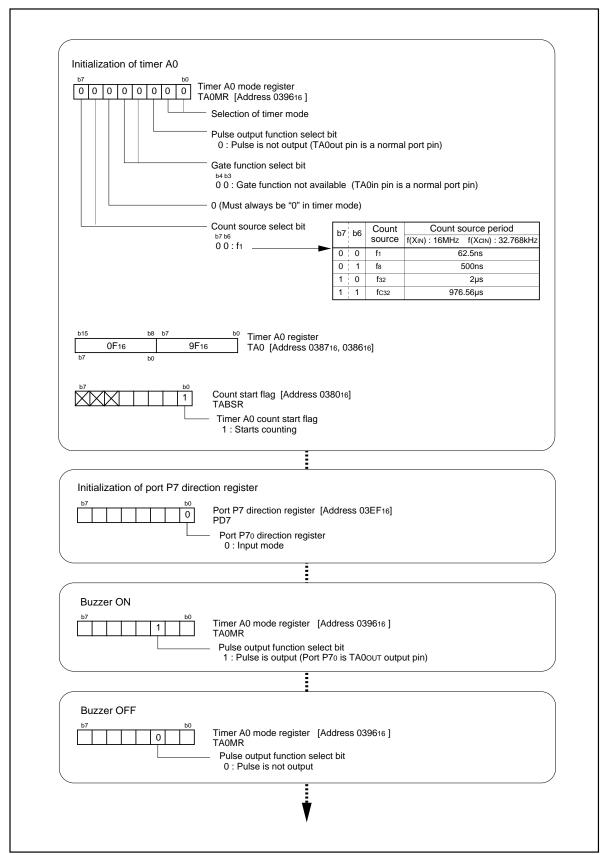

#### 2.2.2 Operation of Timer A (timer mode)

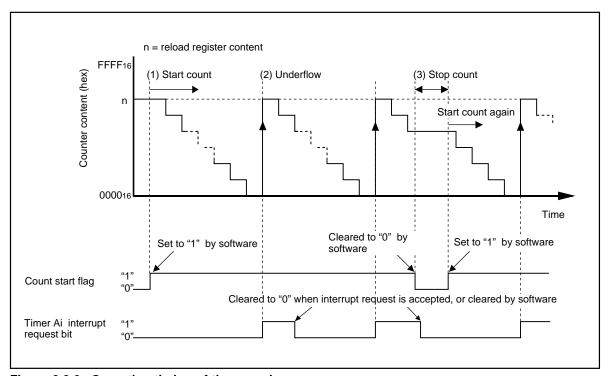

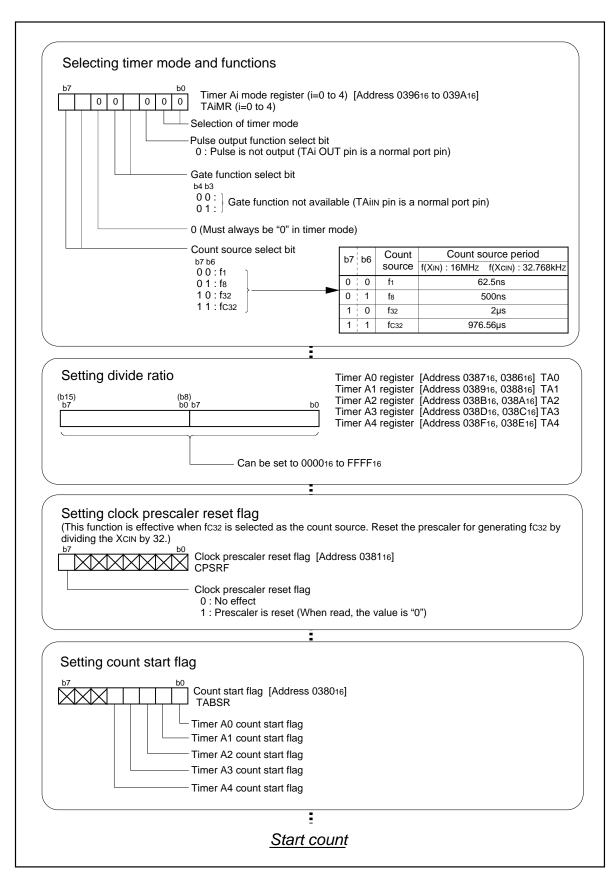

In timer mode, choose functions from those listed in Table 2.2.1. Operations of the circled items are described below. Figure 2.2.6 shows the operation timing, and Figure 2.2.7 shows the set-up procedure.

Table 2.2.1. Choosed functions

| Item                  |   | Set-up                                                                    |  |

|-----------------------|---|---------------------------------------------------------------------------|--|

| Count source          | 0 | Internal count source (f1 / f8 / f32 / fc32)                              |  |

| Pulse output function | 0 | No pulses output                                                          |  |

|                       |   | Pulses output                                                             |  |

| Gate function         | 0 | No gate function                                                          |  |

|                       |   | Performs count only for the period in which the TAilN pin is at "L" level |  |

|                       |   | Performs count only for the period in which the TAin pin is at "H" level  |  |

Operation (1) Setting the count start flag to "1" causes the counter to perform a down count on the count source.

- (2) If an underflow occurs, the content of the reload register is reloaded, and the count continues. At this time, the timer Ai interrupt request bit goes to "1".

- (3) Setting the count start flag to "0" causes the counter to hold its value and to stop.

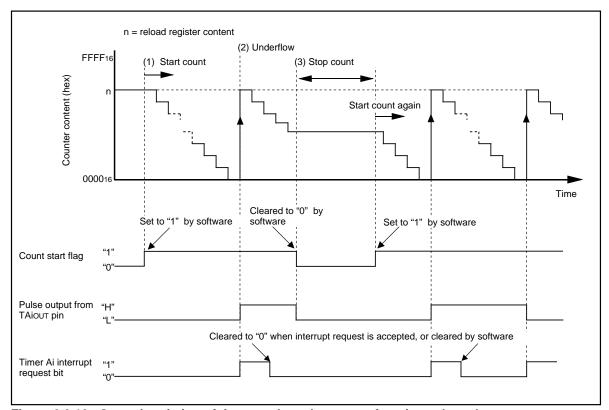

Figure 2.2.6. Operation timing of timer mode

Figure 2.2.7. Set-up procedure of timer mode

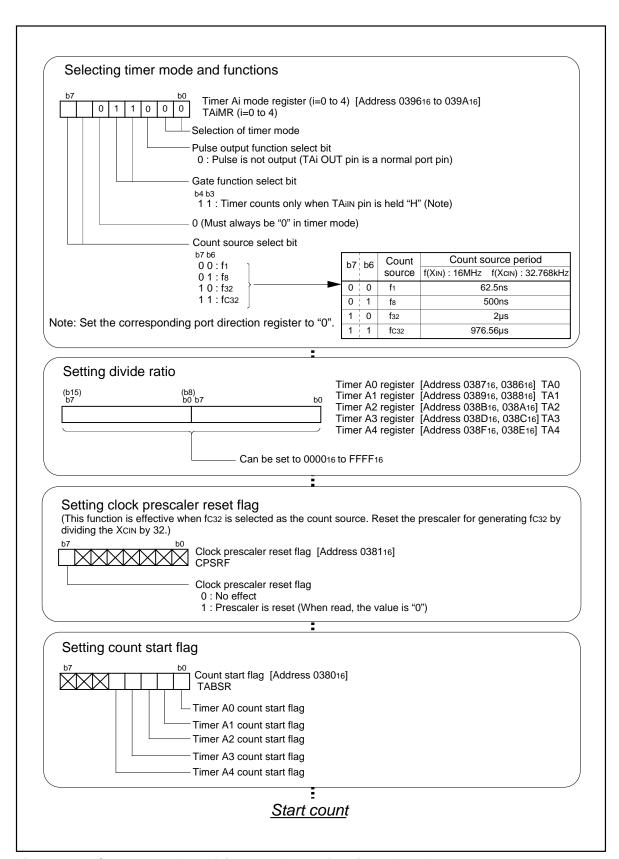

#### 2.2.3 Operation of Timer A (timer mode, gate function selected)

In timer mode, choose functions from those listed in Table 2.2.2. Operations of the circled items are described below. Figure 2.2.8 shows the operation timing, and Figure 2.2.9 shows the set-up procedure.

Table 2.2.2. Choosed functions

| Item                  | Set-up |                                                                           |  |

|-----------------------|--------|---------------------------------------------------------------------------|--|

| Count source          | 0      | O Internal count source(f1 / f8 / f32 / fc32)                             |  |

| Pulse output function | 0      | No pulses output                                                          |  |

|                       |        | Pulses output                                                             |  |

| Gate function         |        | No gate function                                                          |  |

|                       |        | Performs count only for the period in which the TAin pin is at "L" level  |  |

|                       | 0      | Performs count only for the period in which the TAiın pin is at "H" level |  |

Operation (1) When the count start flag is set to "1" and the TAilN pin inputs at "H" level, the counter performs a down count on the count source.

- (2) When the TAin pin inputs at "L" level, the counter holds its value and stops.

- (3) If an underflow occurs, the content of the reload register is reloaded and the count continues. At this time, the timer Ai interrupt request bit goes to "1".

- (4) Setting the count start flag to "0" causes the counter to hold its value and to stop.

Note • Make the pulse width of the signal input to the TAilN pin not less than two cycles of the count source.

Figure 2.2.8. Operation timing of timer mode, gate function selected

Figure 2.2.9. Set-up procedure of timer mode, gate function selected

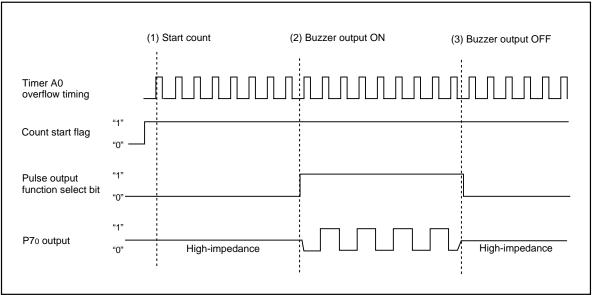

#### 2.2.4 Operation of Timer A (timer mode, pulse output function selected)

In timer mode, choose functions from those listed in Table 2.2.3. Operations of the circled items are described below. Figure 2.2.10 shows the operation timing, and Figures 2.2.11 shows the set-up procedure

| Table | 2.2.3. | Choosed | l functions |

|-------|--------|---------|-------------|

|-------|--------|---------|-------------|

| Item                  |   | Set-up                                                                    |  |

|-----------------------|---|---------------------------------------------------------------------------|--|

| Count source          | 0 | Internal count source(f1 / f8 / f32 / fc32)                               |  |

| Pulse output function |   | No pulses output                                                          |  |

|                       | 0 | Pulses output                                                             |  |

| Gate function         | 0 | No gate function                                                          |  |

|                       |   | Performs count only for the period in which the TAin pin is at "L" level  |  |

|                       |   | Performs count only for the period in which the TAiın pin is at "H" level |  |

Operation (1) Setting the count start flag to "1" causes the counter to perform a down count on the count source.

- (2) If an underflow occurs, the content of the reload register is reloaded and the count continues. At this time, the timer Ai interrupt request bit goes to "1". Also, the output polarity of the TAiout pin reverses.

- (3) Setting the count start flag to "0" causes the counter to hold its value and to stop. Also, the TAiout pin outputs an "L" level.

Figure 2.2.10. Operation timing of timer mode, pulse output function selected

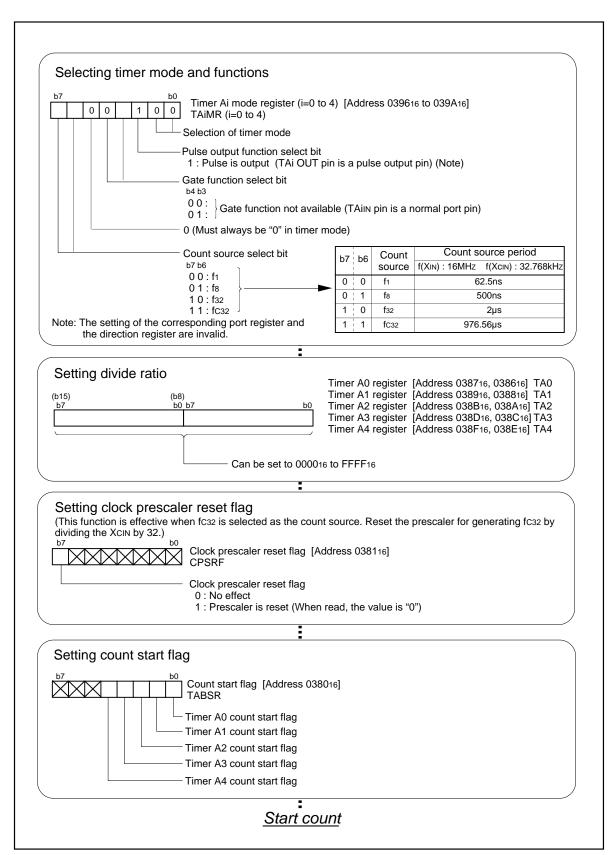

Figure 2.2.11. Set-up procedure of timer mode, pulse output function selected

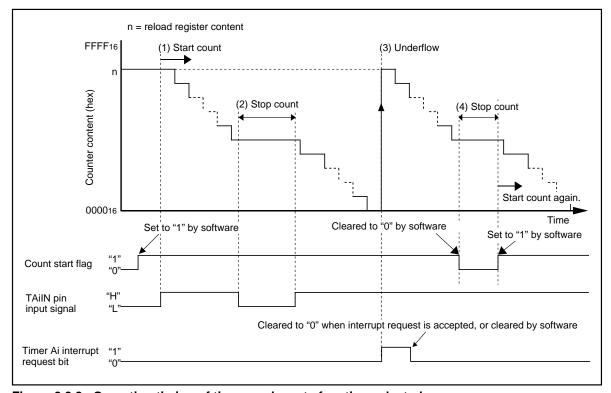

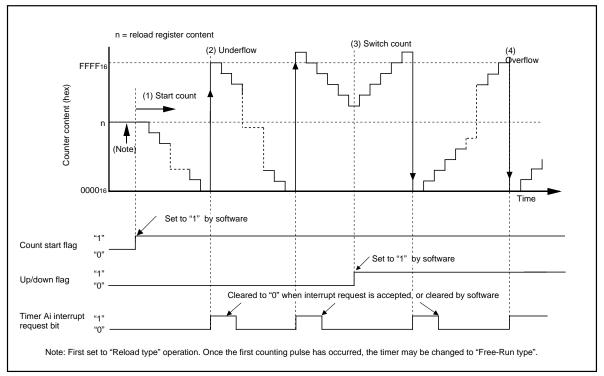

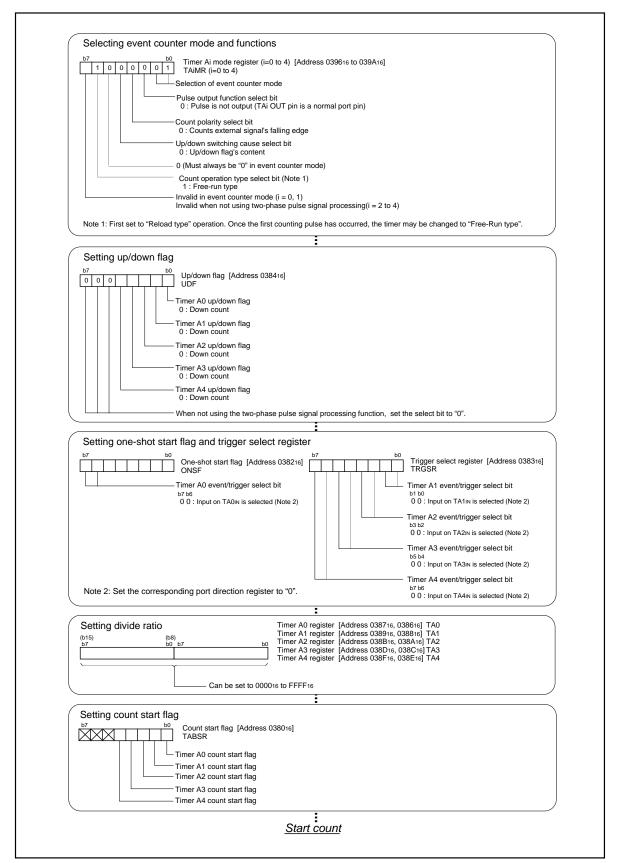

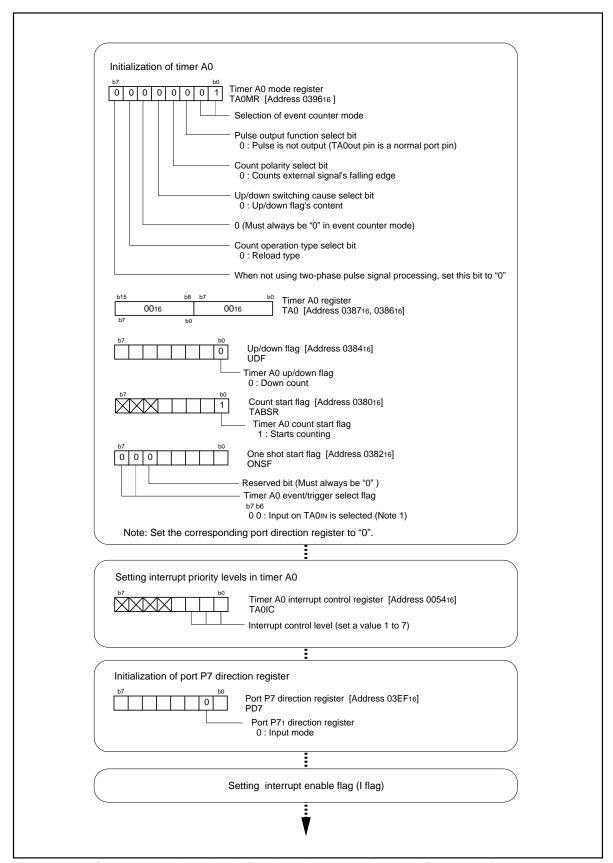

#### 2.2.5 Operation of Timer A (event counter mode, reload type selected)

In event counter mode, choose functions from those listed in Table 2.2.4. Operations of the circled items are described below. Figure 2.2.12 shows the operation timing, and Figure 2.2.13 shows the set-up procedure.

Table 2.2.4. Choosed functions

| Item         | Set-up       |                                                  | ltem                                     |   | Set-up                  |

|--------------|--------------|--------------------------------------------------|------------------------------------------|---|-------------------------|

| Count source | 0            | Input signal to TAilN                            | Pulse output function                    | 0 | No pulses output        |

|              |              | (counting falling edges)                         |                                          |   | Pulses output           |

|              |              | Input signal to TAilN<br>(counting rising edges) | Count operation type                     | 0 | Reload type             |

|              |              |                                                  |                                          |   | Free-run type           |

|              | TAj overflow | TAj overflow                                     | Factor for switching between up and down | 0 | Content of up/down flag |

|              |              |                                                  |                                          |   | Input signal to TAiout  |

|              |              |                                                  |                                          |   |                         |

Note: j = i - 1, but j = 4 when i = 0.

Operation (1) Setting the count start flag to "1" causes the counter to count the falling edges of the count source.

- (2) If an underflow occurs, the content of the reload register is reloaded, and the count continues. At this time, the timer Ai interrupt request bit goes to "1".

- (3) If switching from an up count to a down count or vice versa while a count is in progress, the switch takes effect from the next effective edge of the count source.

- (4) Setting the count start flag to "0" causes the counter to hold its value and to stop.

- (5) If an overflow occurs, the content of the reload register is reloaded, and the count continues. At this time, the timer Ai interrupt request bit goes to "1".

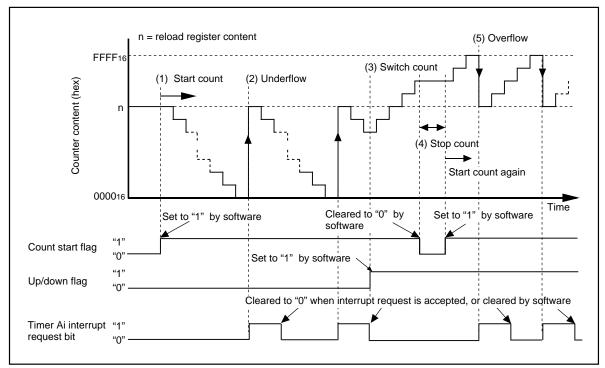

Figure 2.2.12. Operation timing of event counter mode, reload type selected

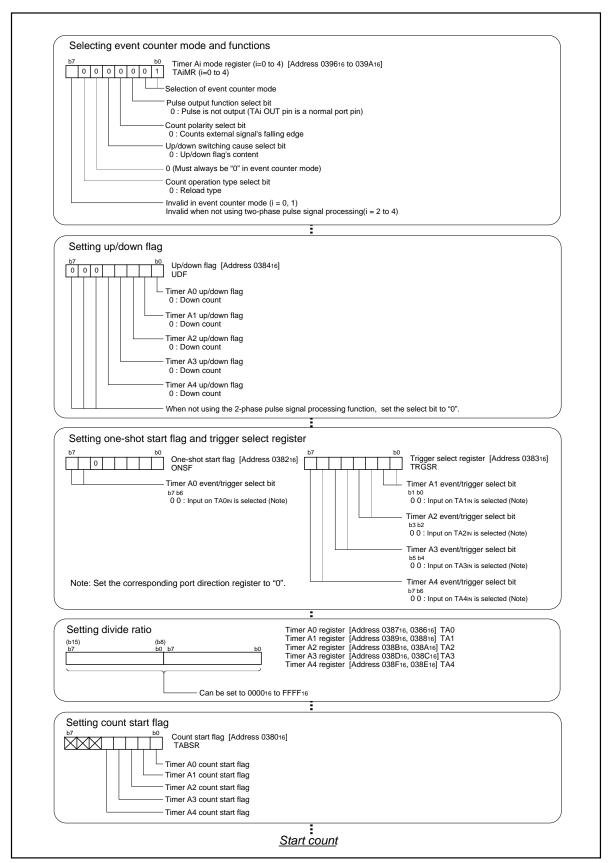

Figure 2.2.13. Set-up procedure of event counter mode, reload type selected

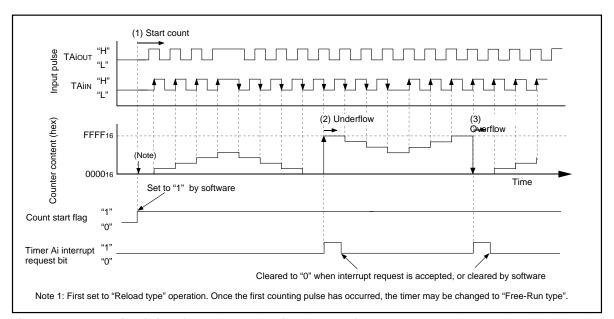

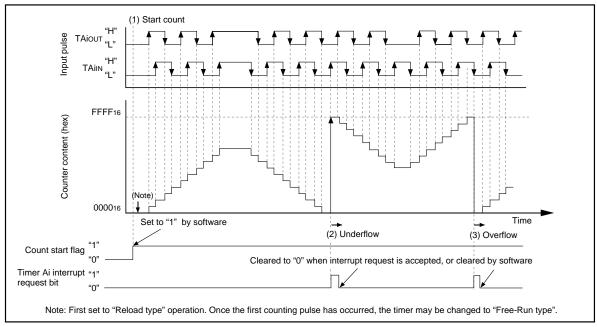

#### 2.2.6 Operation of Timer A (event counter mode, free run type selected)

In event counter mode, choose functions from those listed in Table 2.2.5. Operations of the circled items are described below. Figure 2.2.14 shows the operation timing, and Figure 2.2.15 shows the set-up procedure.

Table 2.2.5. Choosed functions

| Item         | Set-up |                                                  | Item                  |                      | Set-up                 |                         |

|--------------|--------|--------------------------------------------------|-----------------------|----------------------|------------------------|-------------------------|

| Count source |        | o Input signal to TAilN (counting falling edges) | Pulse output function | 0                    | No pulses output       |                         |

|              |        |                                                  |                       |                      | Pulses output          |                         |

|              |        | Input signal to TAiin (counting rising edges)    | Count operation type  |                      | Reload type            |                         |

|              |        |                                                  |                       | 0                    | Free-run type          |                         |

|              |        | 1                                                | TAj overflow          | Factor for switching | 0                      | Content of up/down flag |

|              |        |                                                  | between up and down   |                      | Input signal to TAiout |                         |

|              |        |                                                  |                       |                      |                        |                         |

Note: j = i - 1, but j = 4 when i = 0

Operation (1) Setting the count start flag to "1" causes the counter to count the falling edges of the count source.

- (2) Even if an underflow occurs, the content of the reload register is not reloaded, but the count continues. At this time, the timer Ai interrupt request bit goes to "1".

- (3) If switching from an up count to a down count or vice versa while a count is in progress, the switch takes effect from the next effective edge of the count source.

- (4) Even if an overflow occurs, the content of the reload register is not reloaded, but the count continues. At this time, the timer Ai interrupt request bit goes to "1".

Figure 2.2.14. Operation timing of event counter mode, free run type selected

Figure 2.2.15. Set-up procedure of event counter mode, free run type selected

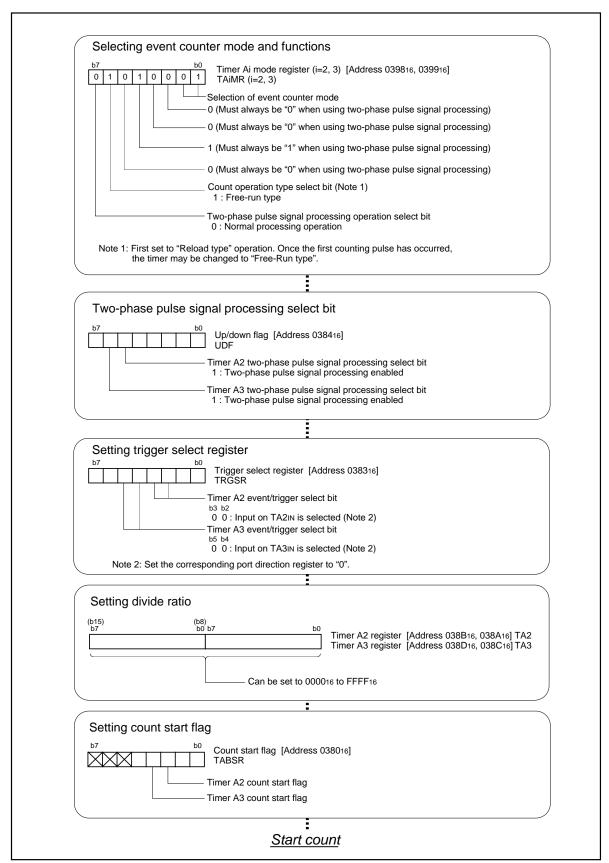

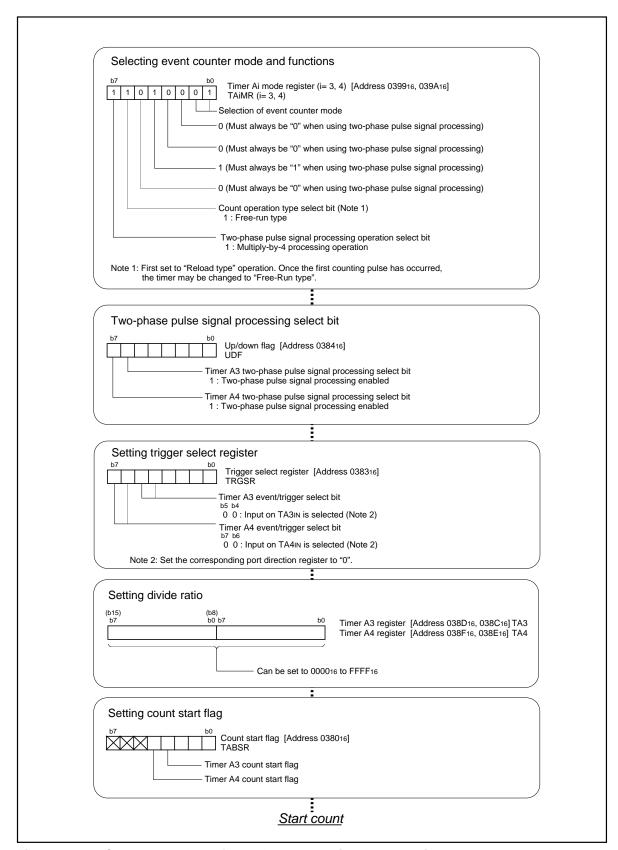

### 2.2.7 Operation of timer A (two-phase pulse signal process in event counter mode, normal mode selected)

In processing two-phase pulse signals in event counter mode, choose functions from those listed in Table 2.2.6. Operations of the circled items are described below. Figure 2.2.16 shows the operation timing, and Figure 2.2.17 shows the set-up procedure.

Table 2.2.6. Choosed functions

| Item                 |   | Set-up                      |

|----------------------|---|-----------------------------|

| Count operation type |   | Reload type                 |

|                      | 0 | Free run type               |

| Two-phase pulses     | 0 | Normal processing           |

| process (Note)       |   | 4-multiplication processing |

Note: Timer A3 alone can be selected. Timer A2 is solely used for normal processes, and timer A4 is solely used for 4 multiplication processes.

Operation (1) Setting the count start flag to "1" causes the counter to count effective edges of the count source.

- (2) Even if an underflow occurs, the content of the reload register is not reloaded, but the count continues. At this time, the timer Ai interrupt request bit goes to "1".

- (3) Even if an overflow occurs, the content of the reload register is not reloaded, but the count continues. At this time, the timer Ai interrupt request bit goes to "1".

• The up count or down count conditions are as follows:

If a rising edge is present at the TAilN pin when the input signal level to the TAioUT pin is "H", an up count is performed.

If a falling edge is present at the TAin pin when the input signal level to the TAiout pin is "H", a down count is performed.

• Set TAilN pin and TAiOUT pin's port direction register to "0".

Figure 2.2.16. Operation timing of two-phase pulse signal process in event counter mode, normal mode selected

Figure 2.2.17. Set-up procedure of two-phase pulse signal process in event counter mode, normal mode selected

#### 2.2.8 Operation of timer A (two-phase pulse signal process in event counter mode, multiply-by-4 mode selected)

In processing two-phase pulse signals in event counter mode, choose functions from those listed in Table 2.2.7. Operations of the circled items are described below. Figure 2.2.18 shows the operation timing, and Figure 2.2.19 shows the set-up procedure.

Table 2.2.7. Choosed functions

| Item                 | Set-up |               | Item                  |   | Set-up                      |  |

|----------------------|--------|---------------|-----------------------|---|-----------------------------|--|

| Count operation type |        | Reload type   | Processing two- phase |   | Normal processing           |  |

|                      | 0      | Free run type | pulses (Note)         | 0 | 4-multiplication processing |  |

Note: Timer A3 alone can be selected. Timer A2 is solely used for normal processes, and timer A4 is solely used for 4multiplication processes.

- Operation (1) Setting the count start flag to "1" causes the counter to count effective edges of the count source.

- (2) Even if an underflow occurs, the content of the reload register is not reloaded, but the count continues. At this time, the interrupt request bit goes to "1".

- (3) Even if an overflow occurs, the content of the reload register is not reloaded, but the count continues. At this time, the interrupt request bit goes to "1".

Note

• The up count or down count conditions are as follows:

Table 2.2.8. The up count or down count conditions

|          | Input signal to the<br>TAio∪⊤ pin | Input signal to the TAilN pin |       | Input signal to the<br>TAiou⊤ pin | Input signal to the TAim pin |  |  |  |

|----------|-----------------------------------|-------------------------------|-------|-----------------------------------|------------------------------|--|--|--|

| Up count | "H" level                         | Rising                        | Down  | "H" level                         | Falling                      |  |  |  |

|          | "L" level                         | Falling                       | count | "L" level                         | Rising                       |  |  |  |

|          | Rising                            | "L" level                     |       | Rising                            | "H" level                    |  |  |  |

|          | Falling                           | "H" level                     |       | Falling                           | "L" level                    |  |  |  |

• Set TAilN pin and TAiOUT pin's port direction register to "0".

Figure 2.2.18. Operation timing of two-phase pulse signal process in event counter mode, multiply-by-4 mode selected

Figure 2.2.19. Set-up procedure of two-phase pulse signal process in event counter mode, multiply-by-4 mode selected

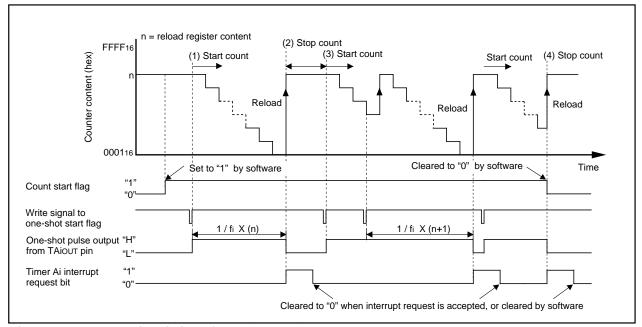

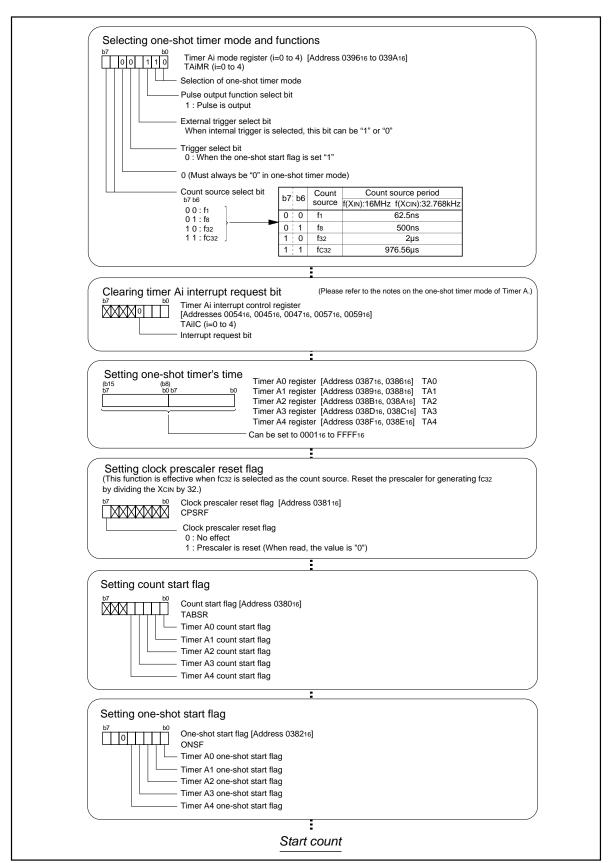

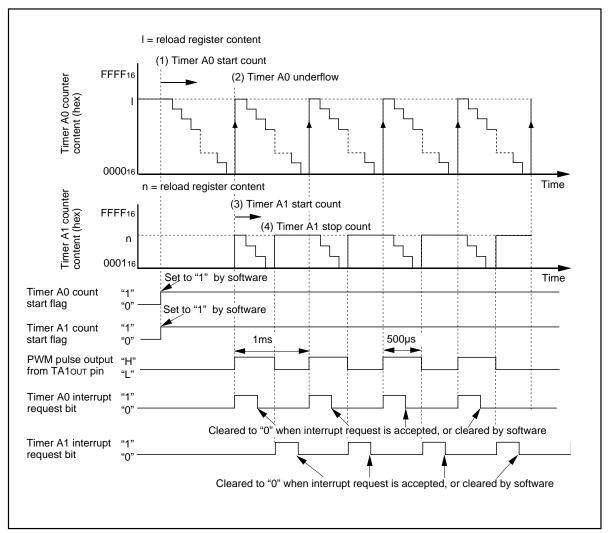

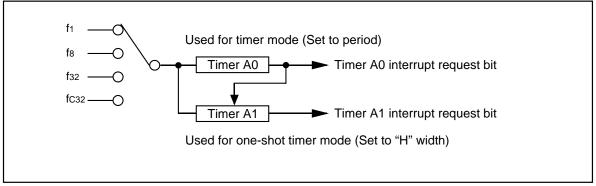

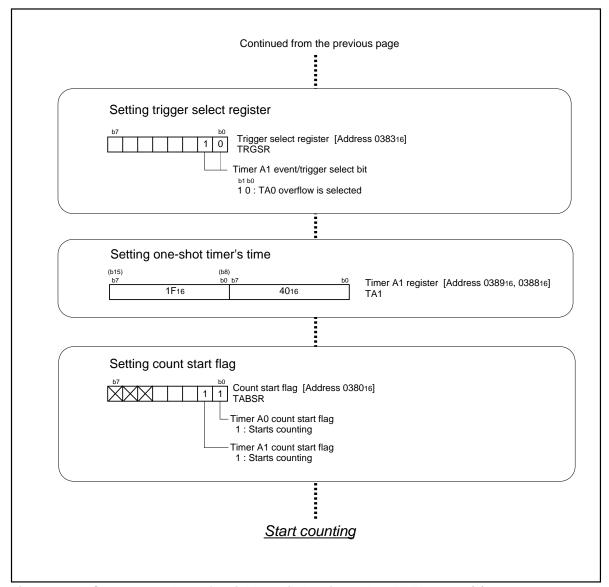

#### 2.2.9 Operation of Timer A (one-shot timer mode)

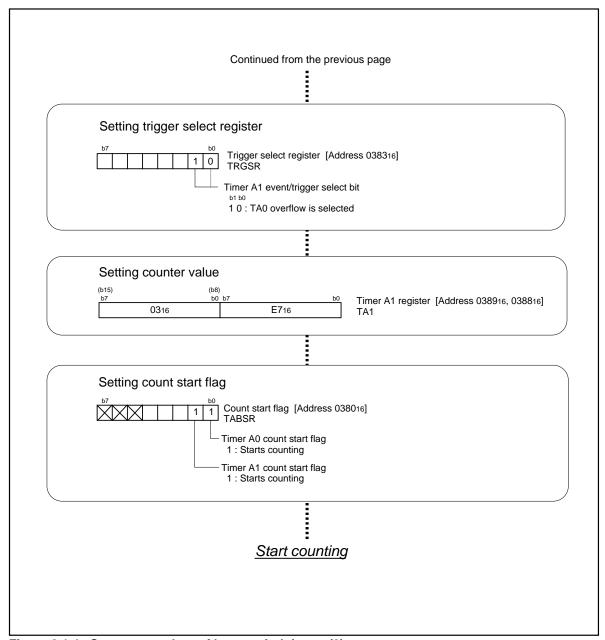

In one-shot timer mode, choose functions from those listed in Table 2.2.9. Operations of the circled items are described below. Figure 2.2.20 shows the operation timing, and Figures 2.2.21 shows the set-up procedure.

Table 2.2.9. Choosed functions

| Item                  | Set-up |                                                                       |  |

|-----------------------|--------|-----------------------------------------------------------------------|--|

| Count source          | 0      | Internal count source (f1 / f8 / f32 / fc32)                          |  |

| Pulse output function |        | No pulses output                                                      |  |

|                       | 0      | Pulses output                                                         |  |

| Count start condition |        | External trigger input (falling edge of input signal to the TAin pin) |  |

|                       |        | External trigger input (rising edge of input signal to the TAiın pin) |  |

|                       |        | Timer overflow (TAj/TAk overflow)                                     |  |

|                       | 0      | Writing "1" to the one-shot start flag                                |  |

Note: j = i - 1, but j = 4 when i = 0; k = i + 1, but k = 0 when i = 4.

- Operation (1) Setting the one-shot start flag to "1" with the count start flag set to "1" causes the counter to perform a down count on the count source. At this time, the TAioUT pin outputs an "H" level.

- (2) The instant the value of the counter becomes "000016", the TAiout pin outputs an "L" level, and the counter reloads the content of the reload register and stops counting. At this time, the timer Ai interrupt request bit goes to "1".

- (3) If a trigger occurs while a count is in progress, the counter reloads the value in the reload register again and continues counting. The reload timing is in step with the next count source input after the trigger.

- (4) Setting the count start flag to "0" causes the counter to stop and to reload the content of the reload register. Also, the TAiout pin outputs an "L" level. At this time, the timer Ai interrupt request bit goes to "1".

Figure 2.2.20. Operation timing of one-shot mode

Figure 2.2.21. Set-up procedure of one-shot mode

2. Timer A M30245 Group

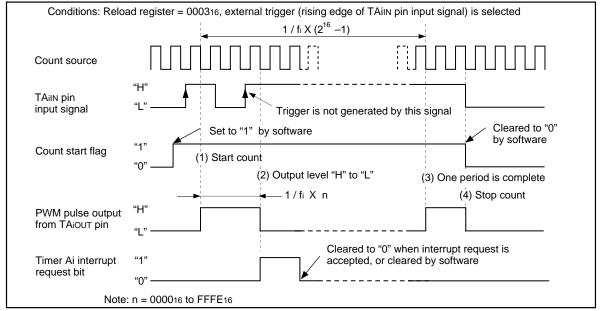

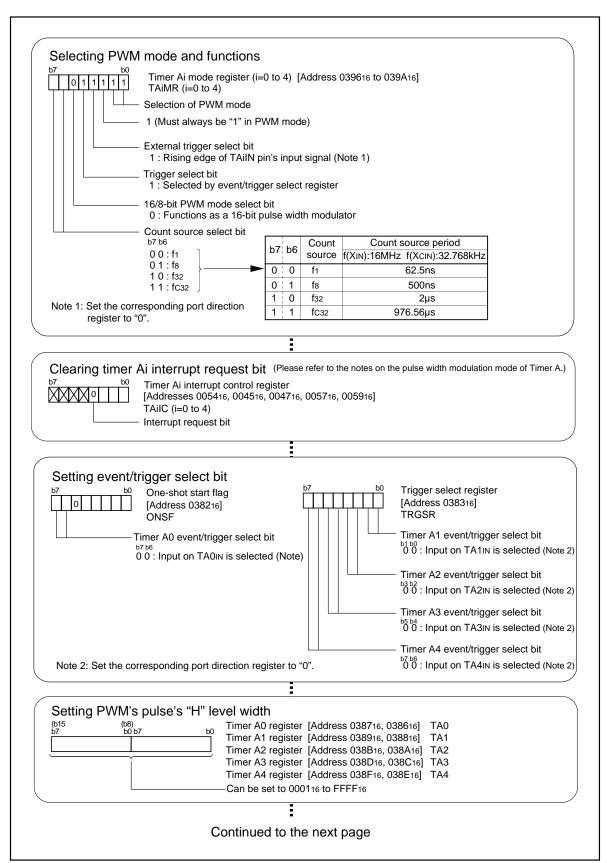

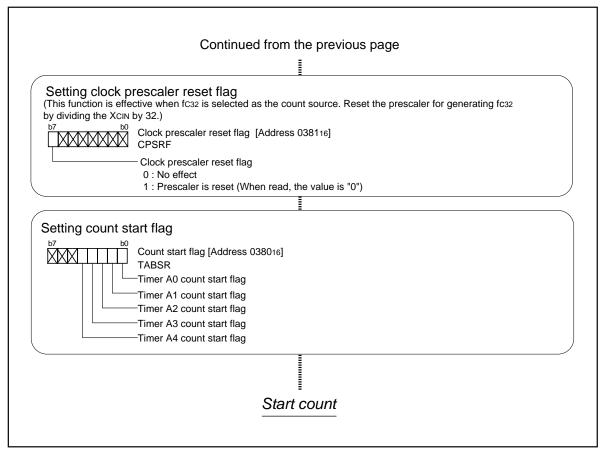

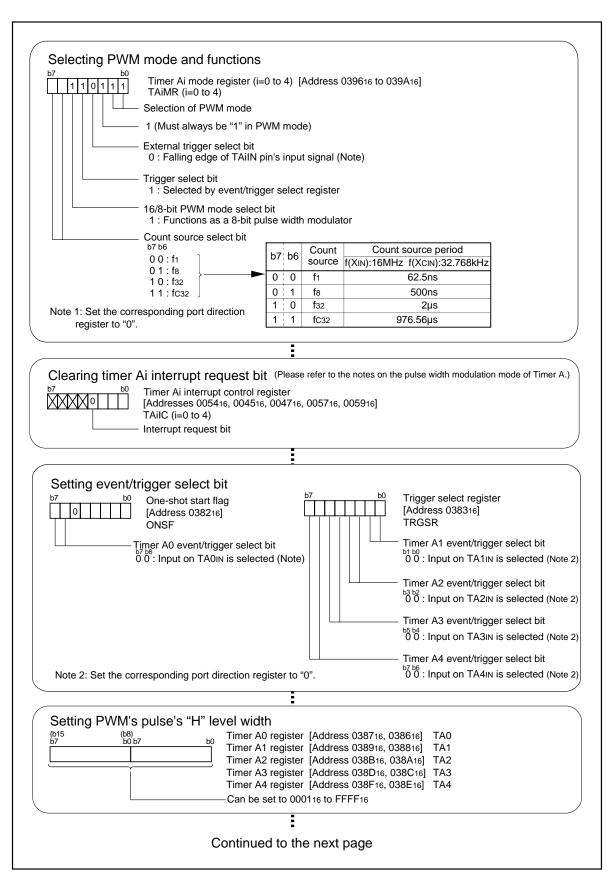

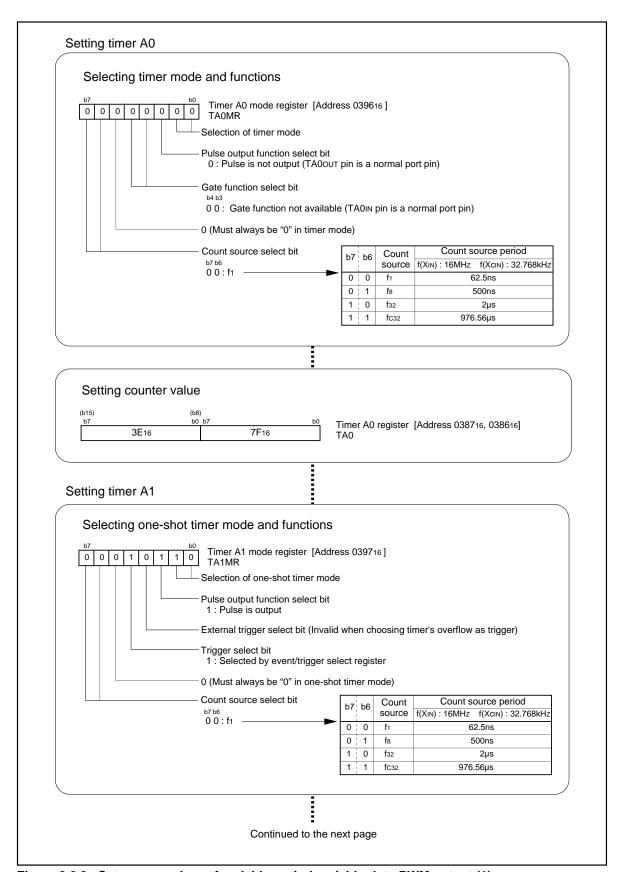

## 2.2.10 Operation of Timer A (pulse width modulation mode, 16-bit PWM mode selected)

In pulse width modulation mode, choose functions from those listed in Table 2.2.10. Operations of the circled items are described below. Figure 2.2.22 shows the operation timing, and Figures 2.2.23 and 2.2.24 show the set-up procedure.

Table 2.2.10. Choosed functions

| Item                  | Set-up |                                                                        |  |  |  |

|-----------------------|--------|------------------------------------------------------------------------|--|--|--|

| Count source          | 0      | Internal count source (f1 / f8 / f32 / fc32)                           |  |  |  |

| PWM mode              | 0      | 16-bit PWM                                                             |  |  |  |

|                       |        | 8-bit PWM                                                              |  |  |  |

| Count start condition |        | External trigger input (falling edge of input signal to the TAilN pin) |  |  |  |

|                       | 0      | External trigger input (rising edge of input signal to the TAin pin)   |  |  |  |

|                       |        | Timer overflow (TAj/TAk overflow)                                      |  |  |  |

Note: j = i - 1, but j = 4 when i = 0; k = i + 1, but k = 0 when i = 4.

- Operation (1) If the TAin pin input level changes from "L" to "H" with the count start flag set to "1", the counter performs a down count on the count source. Also, the TAiout pin outputs an "H" level.

- (2) The TAiout pin output level changes from "H" to "L" when a set time period elapses. At this time, the timer Ai interrupt request bit goes to "1".

- (3) The counter reloads the content of the reload register every time PWM pulses are output for one cycle, and continues counting.

- (4) Setting the count start flag to "0" causes the counter to hold its value and to stop. Also, the TAiout outputs an "L" level.

Note

- The period of PWM pulses becomes  $(2^{16} 1)/fi$ , and the "H" level pulse width becomes n/fi. If the timer Ai register is set to "000016", the pulse width modulator does not work, and the the TAIOUT pin output level remains at "L".

- (fi: frequency of the count source f1, f8, f32, fC32; n: value of the timer)

- Set TAilN pin's port direction register to "0".

Figure 2.2.22. Operation timing of pulse width modulation mode, 16-bit PWM mode selected

Figure 2.2.23. Set-up procedure of pulse width modulation mode, 16-bit PWM mode selected (1)

Figure 2.2.24. Set-up procedure of pulse width modulation mode, 16-bit PWM mode selected (2)

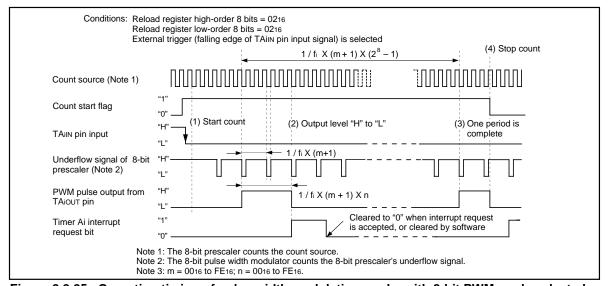

## 2.2.11 Operation of Timer A (pulse width modulation mode, 8-bit PWM mode selected)

In pulse width modulation mode, choose functions from those listed in Table 2.2.11. Operations of the circled items are described below. Figure 2.2.25 shows the operation timing, and Figures 2.2.26 and 2.2.27 show the set-up procedure.

Table 2.2.11. Choosed functions

| Item                  | Set-up |                                                                        |  |

|-----------------------|--------|------------------------------------------------------------------------|--|

| Count source          | 0      | Internal count source (f1 / f8 / f32 / fc32)                           |  |

| PWM mode              |        | 16-bit PWM                                                             |  |

|                       | 0      | 8-bit PWM                                                              |  |

| Count start condition | 0      | External trigger input (falling edge of input signal to the TAiın pin) |  |

|                       |        | External trigger input (rising edge of input signal to the TAiın pin)  |  |

|                       |        | Timer overflow (TAj/TAk overflow)                                      |  |

Note: j = i - 1, but j = 4 when i = 0; k = i + 1, but k = 0 when i = 4.

Operation (1) If the TAilN pin input level changes from "H" to "L" with the count start flag set to "1", the counter performs a down count on the count source. Also, the TAiOUT pin outputs an "H" level.

- (2) The TAiout pin output level changes from "H" to "L" when a set time period elapses. At this time, the timer Ai interrupt request bit goes to "1".

- (3) The counter reloads the content of the reload register every time PWM pulses are output for one cycle, and continues counting.

- (4) Setting the count start flag to "0" causes the counter to hold its value and to stop. Also, the TAiout pin outputs an "L" level.

Note

- The period of PWM pulses becomes  $(m + 1) \times (2^8 1) / fi$ , and the "H" level pulse width becomes  $n \times (m + 1) / fi$ . If "0016" is set in the eight higher-order bits of the timer Ai register, the pulse width modulator does not work, and the TAioUT pin output level remains at "L".

- (fi: frequency of the count source f1, f8, f32, fc32; n: value of the timer)

- When a trigger is generated, the TAiout pin outputs "L" level of same amplitude as "H" level of the set PWM pulse, after which it starts PWM pulse output.

- Set TAin pin's port direction register to "0".

Figure 2.2.25. Operation timing of pulse width modulation mode, with 8-bit PWM mode selected

Figure 2.2.26. Set-up procedure of pulse width modulation mode, 8-bit PWM mode selected (1)

Figure 2.2.27. Set-up procedure of pulse width modulation mode, 8-bit PWM mode selected (2)

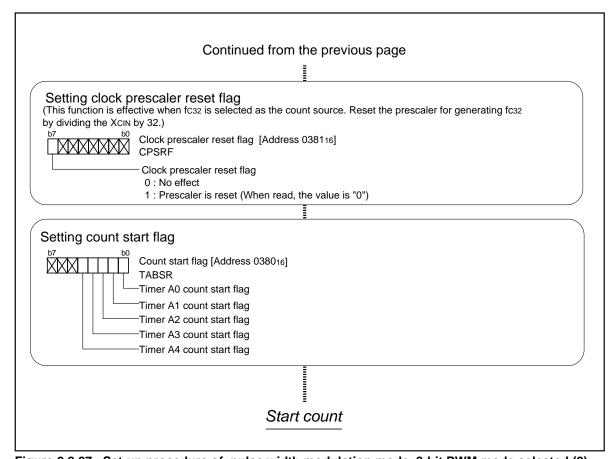

# 2.2.12 Precautions for Timer A (timer mode)

(1) To clear reset, the count start flag is set to "0". Set a value in the timer Ai register, then set the flag to "1".

(2) Reading the timer Ai register while a count is in progress allows reading, with arbitrary timing, the value of the counter. Reading the timer Ai register with the reload timing shown in Figure 2.2.28 gets "FFFF16". Reading the timer Ai register after setting a value in the timer Ai register with a count halted but before the counter starts counting gets a proper value.

Figure 2.2.28. Reading timer Ai register

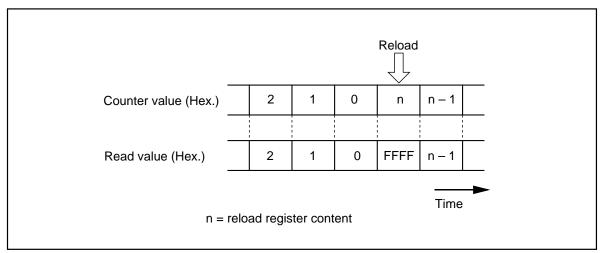

## 2.2.13 Precautions for Timer A (event counter mode)

(1) To clear reset, the count start flag is set to "0". Set a value in the timer Ai register, then set the flag to "1".

- (2) Reading the timer Ai register while a count is in progress allows reading, with arbitrary timing, the value of the counter. Reading the timer Ai register with the reload timing shown in Figure 2.2.29 gets "FFFF16" by underflow or "000016" by overflow. Reading the timer Ai register after setting a value in the timer Ai register with a count halted but before the counter starts counting gets a proper value.

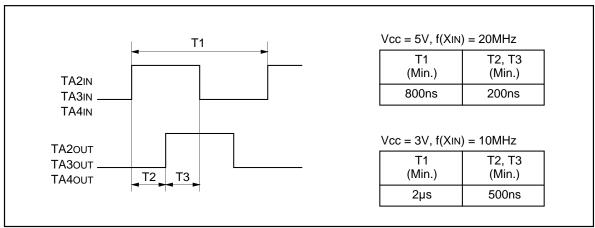

- (3) Please note the standards for the differences between the 2 pulses used in the two-phase pulse signals input signals to the TAiIN pin and TAiOUT pin (i = 2, 3, 4), as shown in Figure 2.2.30.

- (4) When free run type is selected, if count is stopped, set a value in the timer Ai register again.

Figure 2.2.29. Reading timer Ai register

Figure 2.2.30. Standard of 2-phase pulses

(5) In the case of using as "Free-Run type", the timer register contents may be unknown when counting begins. If the timer register is set before counting has started, then the starting value will be unknown.

- In the case where the up/down count will not be changed.

- Enable the "Reload" function and write to the timer register before counting begins. Rewrite the value to the timer register immediately after counting has started. If counting up, rewrite "000016" to the timer register. If counting down, rewrite "FFFF16" to the timer register. This will cause the same operation as "Free-Run type" mode.

- In the case where the up/down count has changed.

- First set to "Reload type" operation. Once the first counting pulse has occurred, the timer may be changed to "Free-Run type".

## 2.2.14 Precautions for Timer A (one-shot timer mode)

- (1) At reset, the count start flag is set to "0". Set a value in the timer Ai register, then set the flag to "1".

- (2) Setting the count start flag to "0" while a count is in progress causes as follows:

- The counter stops counting and a content of reload register is reloaded.

- The TAiout pin outputs "L" level.

- The interrupt request generated and the timer Ai interrupt request bit goes to "1".

- (3) The timer Ai interrupt request bit goes to "1" if the timer's operation mode is set using any of the following procedures:

- Selecting one-shot timer mode after reset.

- Changing operation mode from timer mode to one-shot timer mode.

- Changing operation mode from event counter mode to one-shot timer mode.

Therefore, to use timer Ai interrupt (interrupt request bit), set timer Ai interrupt request bit to "0" after the above listed changes have been made.

(4) If a trigger occurs while a count is in progress, after the counter performs one down count following the reoccurrence of a trigger, the reload register contents are reloaded, and the count continues. To generate a trigger while a count is in progress, generate the second trigger after an elapse longer than one cycle of the timer's count source after the previous trigger occurred.

## 2.2.15 Precautions for Timer A (pulse width modulation mode)

(1) To clear reset, the count start flag is set to "0". Set a value in the timer Ai register, then set the flag to "1".

- (2) The timer Ai interrupt request bit becomes "1" if setting operation mode of the timer in compliance with any of the following procedures:

- Selecting PWM mode after reset.

- Changing operation mode from timer mode to PWM mode.

- Changing operation mode from event counter mode to PWM mode.

Therefore, to use timer Ai interrupt (interrupt request bit), set timer Ai interrupt request bit to "0" after the above listed changes have been made.

(3) Setting the count start flag to "0" while PWM pulses are being output causes the counter to stop counting. If the TAioUT pin is outputting an "H" level in this instance, the output level goes to "L", and the timer Ai interrupt request bit goes to "1". If the TAioUT pin is outputting an "L" level in this instance, the level does not change, and the timer Ai interrupt request is not generated.

## 2.3 Clock-Synchronous Serial I/O

### 2.3.1 Overview

Clock-synchronous serial I/O carries out 8-bit data communications in synchronization with the clock. The following is an overview of the clock-synchronous serial I/O.

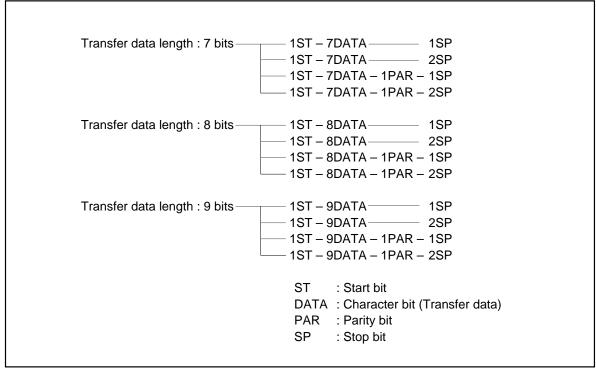

## (1) Transmission/reception format

8-bit data

### (2) Transfer rate

If the internal clock is selected as the transfer clock, the divide-by-2 frequency, resulting from the bit rate generator division, becomes the transfer rate. The bit rate generator count source can be selected from the following: f1, f8, and f32. Clocks f1, f8, and f32 are derived by dividing the CPU's main clock by 1, 8, and 32 respectively.

Furthermore, if an external clock is selected as the transfer clock, the clock frequency input to the CLK pin becomes the transfer rate.

### (3) Error detection

Only overrun errors can be detected. Overrun error is an error that occurs if the serial interface starts receiving the next data item before reading the contents of the UARTi receive buffer register and receives the 7th bit of the next data.

### (4) How to deal with an error

When receiving data, read an error flag and reception data simultaneously to determine which error

has occurred. If the data read is erroneous, initialize the error flag and the UARTi receive buffer

register, then receive the data again.

## To initialize the UARTi receive buffer register

- 1. Set the receive enable bit to "0" (disable reception).

- 2. Set the serial I/O mode select bit to "0002" (invalid serial I/O).

- 3. Set the serial I/O mode select bit.

- 4. Set the receive enable bit to "1" again (enable reception).

- To transmit data again due to an error such as staggered serial clock caused by noise, set the UARTi transmit buffer register again, then transmit the data again.

## To set the UARTi transmit buffer register again

- 1. Set the serial I/O mode select bits to "0002" (invalidate serial I/O).

- 2. Set the serial I/O mode select bits again.

- 3. Set the transmit enable bit to "1" (enable transmission), then set transmission data in the UARTi transmit buffer register.

## (5) Function selection

For clock-synchronous serial I/O, the following functions can be selected:

## (a) CTS/RTS function

In the CTS function, an external IC can start transmission/reception by inputting an "L" level to the  $\overline{\text{CTS}}$  pin. The  $\overline{\text{CTS}}$  pin input level is detected when transmission/reception starts. Therefore, if the level is set to "H" during transmission/reception, it will stop from the next data.

The RTS function informs an external IC that RTS is reception-ready and has changed to "L". RTS goes back to "H" at the first falling edge of the transfer clock.

The clock-synchronous serial I/O has three types of CTS/RTS functions to choose from:

CTS/RTS functions disabled

CTS/RTS pin is a programmable I/O port.

CTS function only enabled

RTS function only enabled

CTS/RTS pin performs the CTS function.

CTS/RTS pin performs the RTS function.

## (b) Function for choosing CLK polarity

This function switches the polarity of the transfer clock. The following operations are available:

- Data is input at the falling edge of the transfer clock, and is output at the rising edge.

- Data is input at the rising edge of the transfer clock, and is output at the falling edge.

## (c) Function for choosing which bit to transmit/receive first

This function is to choose whether to transmit/receive data from bit 0 or from bit 7. Choose either of the following:

LSB first Data is transmitted/received from bit 0.

MSB first Data is transmitted/received from bit 7.

## (d) Function for choosing continuous receive mode

Continuous receive mode is a mode in which reading the receive buffer register makes the receptionenabled status ready. In this mode, there is no need to write dummy data to the transmit buffer register so as to make the reception-enabled status ready. But at the time of starting reception, read the receive buffer register into a dummy manner.

Normal mode Writing dummy data to the transmit buffer register makes the

reception enabled status ready.

• Continuous receive mode Reading the reception buffer register makes the reception-enabled

status ready.

## (e) Data logic select function

This function is to reverse data when writing to transmit buffer register or reading from receive buffer register.

## (f) Function for choosing a transmission interrupt factor

The timing to generate a transmission interrupt can be selected from the following: the instant the transmission buffer is emptied or the instant the transmission register is emptied. When transmission buffer empty timing is selected, an interrupt occurs when transmitted data is moved from the transmission buffer to the transmission register. Therefore, data can be transmitted in succession. When transmission register empty timing is selected, an interrupt occurs when data transmission is complete.

## (g) TxD, RxD I/O polarity reverse function

This function is to reverse a polarity of TxD port output level and a polarity of RxD port input level.

Following are some examples in which various functions (a) through (g) are selected:

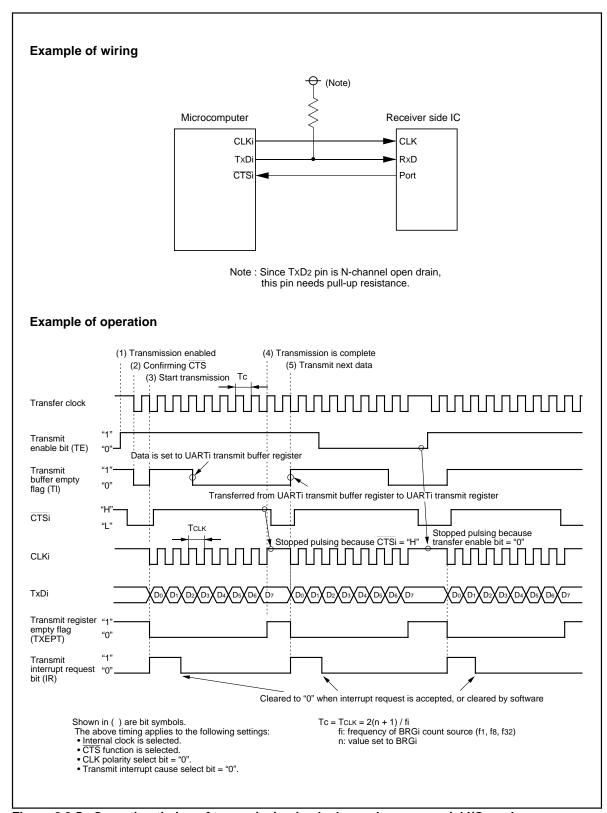

- Transmission Operation WITH: CTS function, transmission at falling edge of transfer clock, LSB First, interrupt at instant transmission buffer is emptied

- Transmission Operation WITH: CTS/RTS function disabled, transmission at falling edge of transfer clock, LSB First, interrupt at instant transmission is completed

- Reception Operation WITH: RTS function, reception at falling edge of transfer clock, LSB First, suc-

cessive reception mode disabled

### (6) Input to the serial I/O and the direction register

To input an external signal to the serial I/O, slect the function select register A to I/O port and set the direction register to input.

### (7) Pins related to the serial I/O

CTS0, CTS1, CTS2, CTS3 pins Input pins for the CTS function

RTS0, RTS1, RTS2, RTS3 pins Output pins for the RTS function

CLK0, CLK1, CLK2, CLK3 pins Input/output pins for the transfer clock

• RxD0, RxD1, RxD2, RxD3 pins Input pins for data

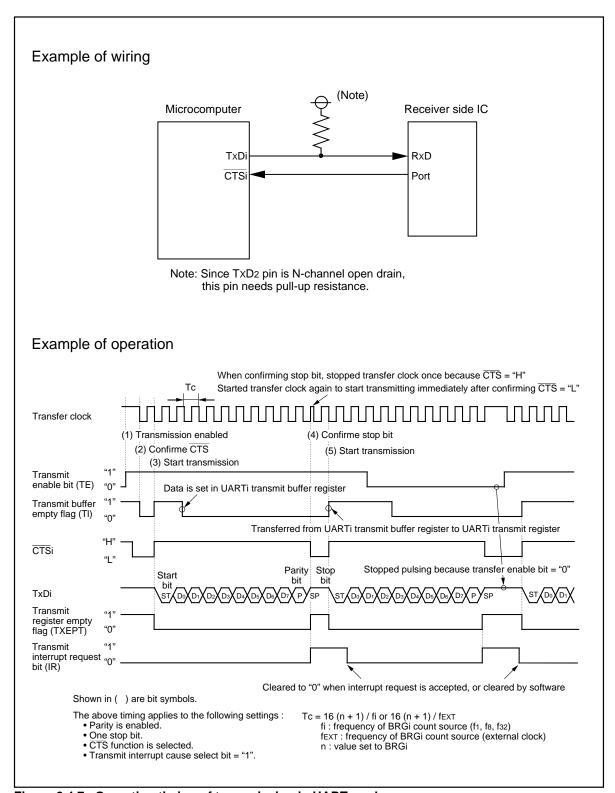

• TxD0, TxD1, TxD2, TxD3 pins Output pins for data (Note)

Note: Since TxD2 pin is N-channel open drain, this pin needs pull-up resistor.

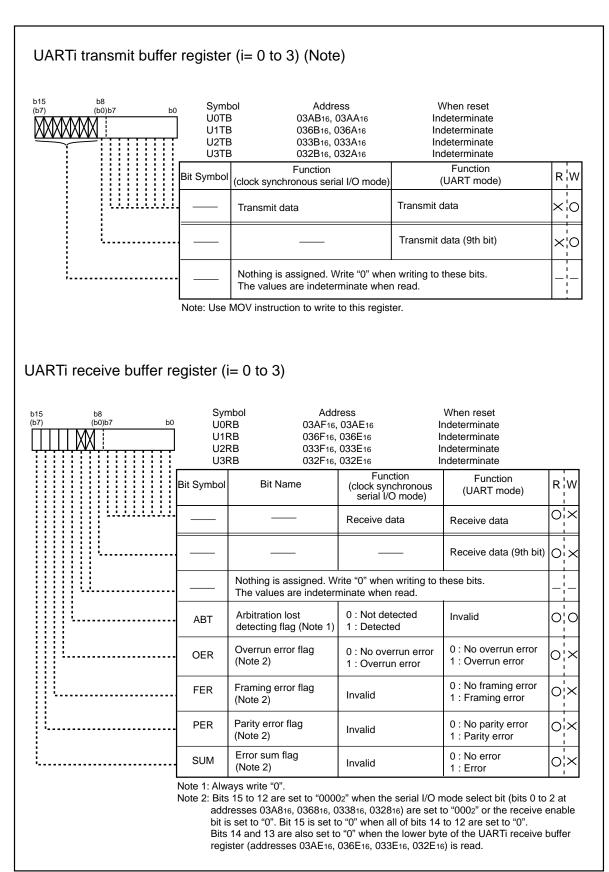

## (8) Registers related to the serial I/O

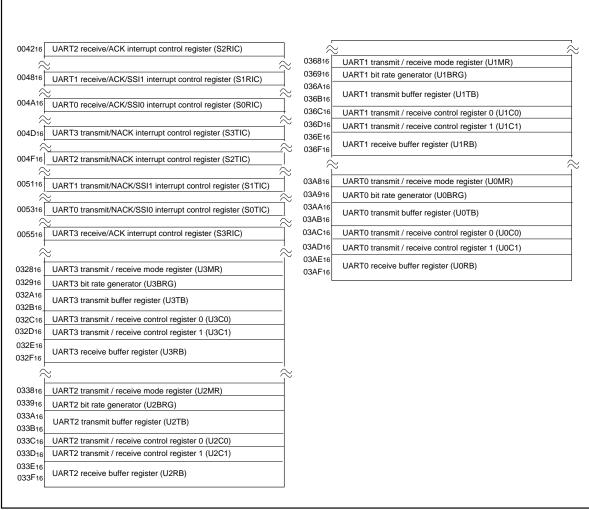

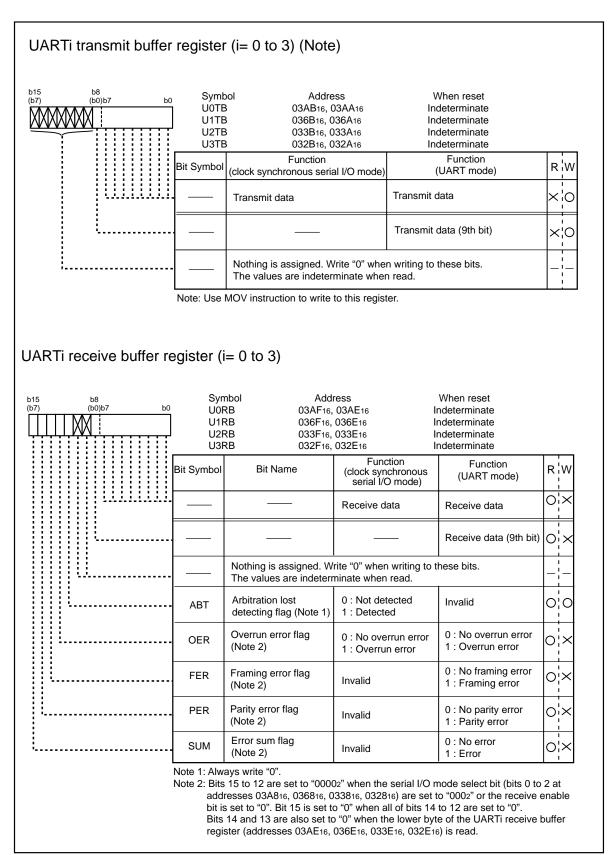

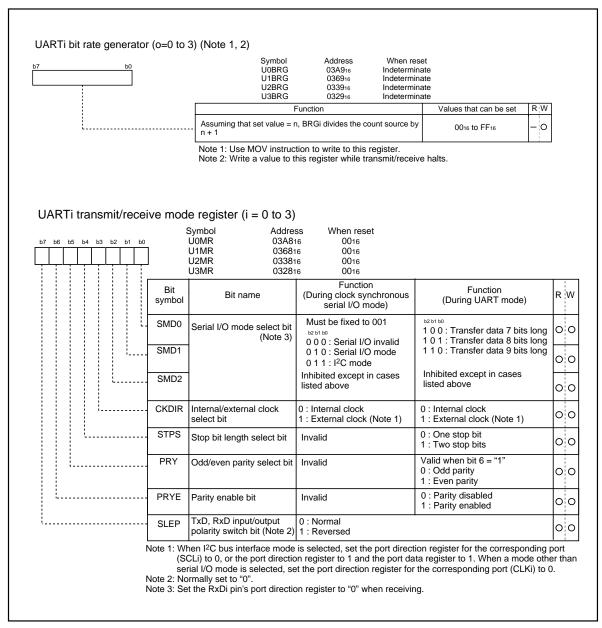

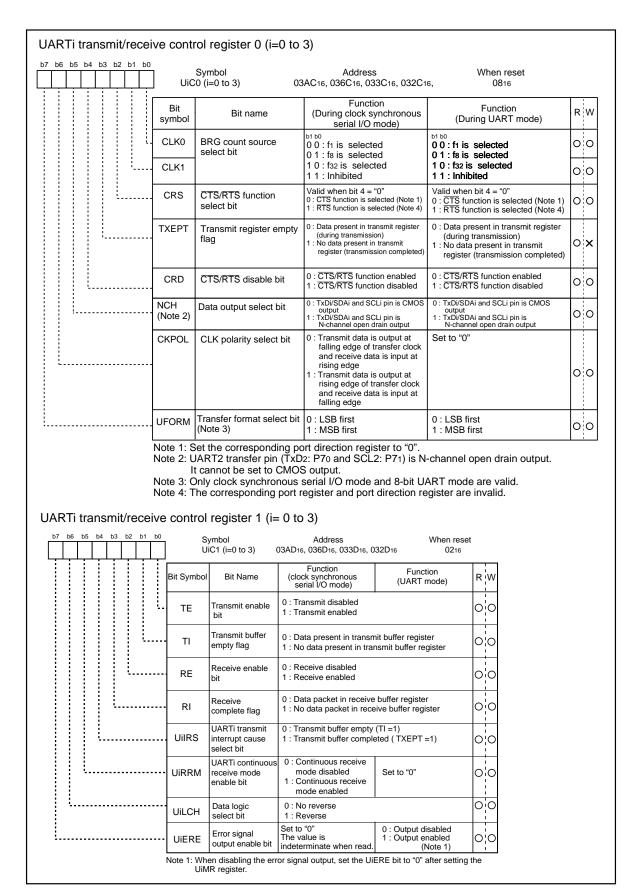

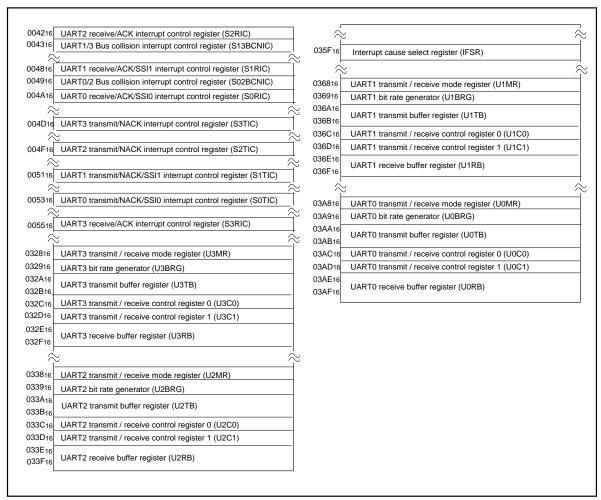

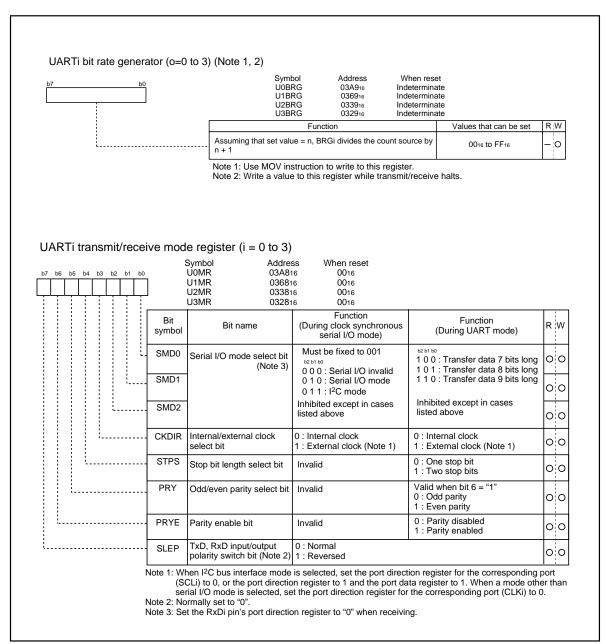

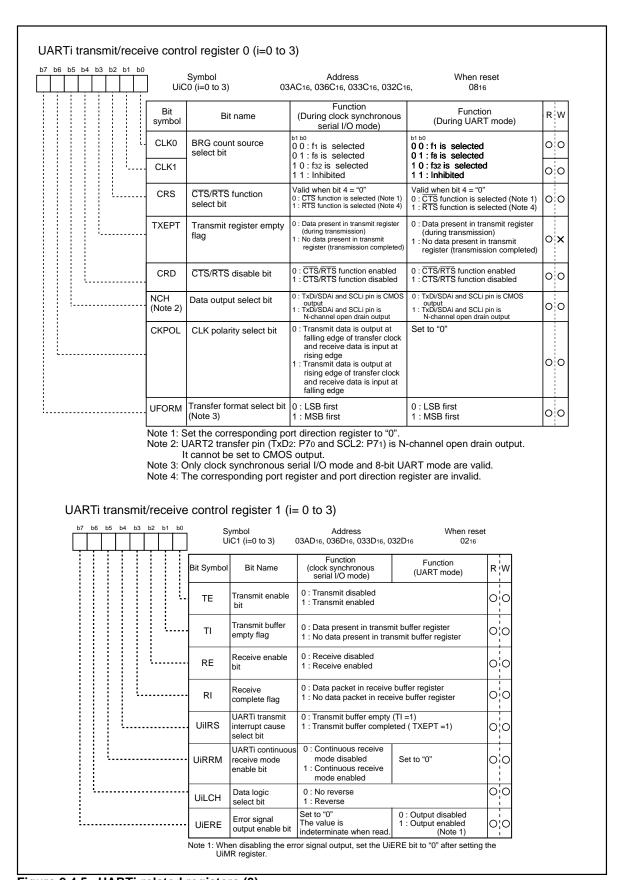

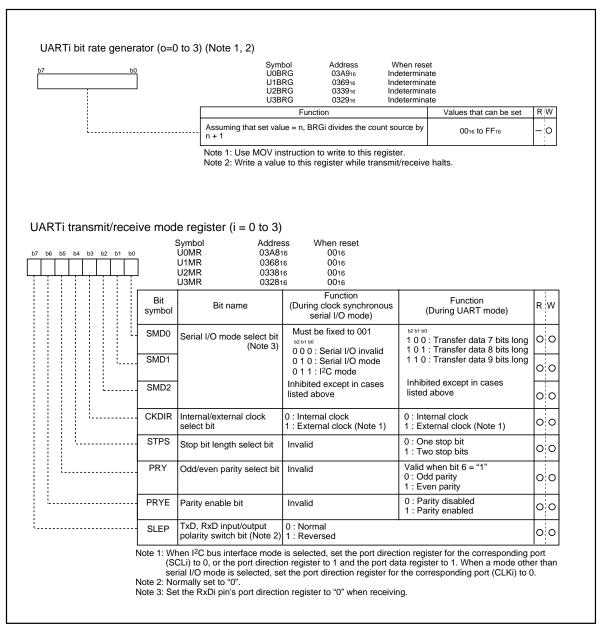

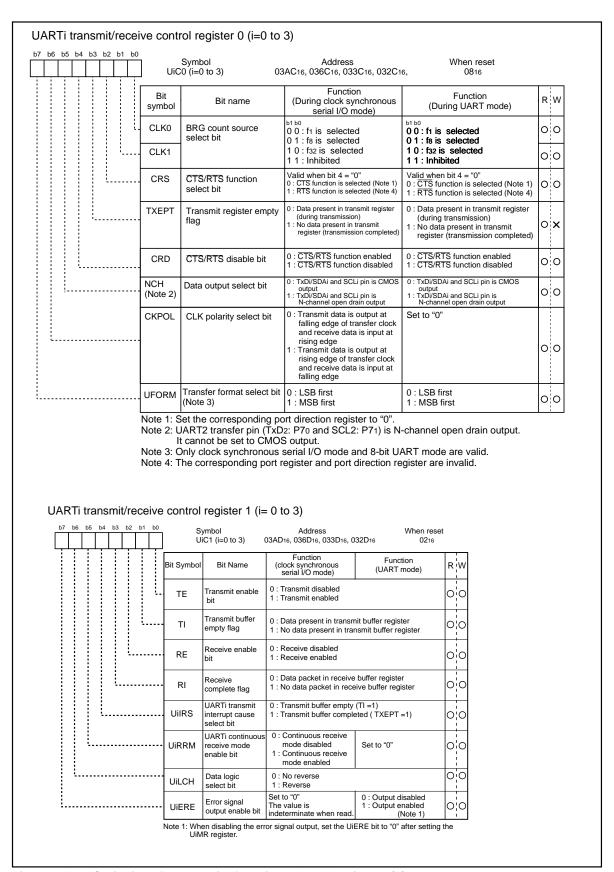

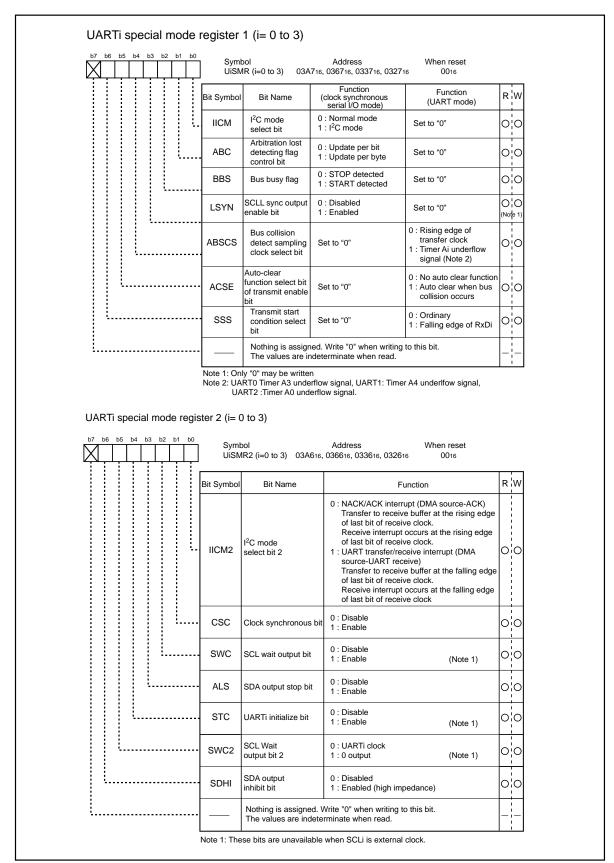

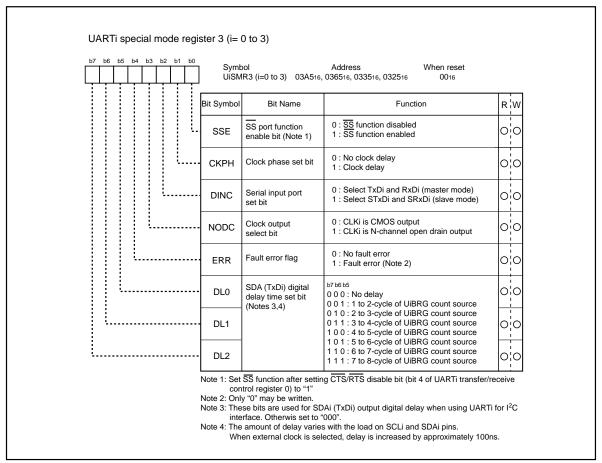

Figure 2.3.1 shows the memory map of serial I/O-related registers, and Figures 2.3.2 to 2.3.4 show serial I/O-related registers.

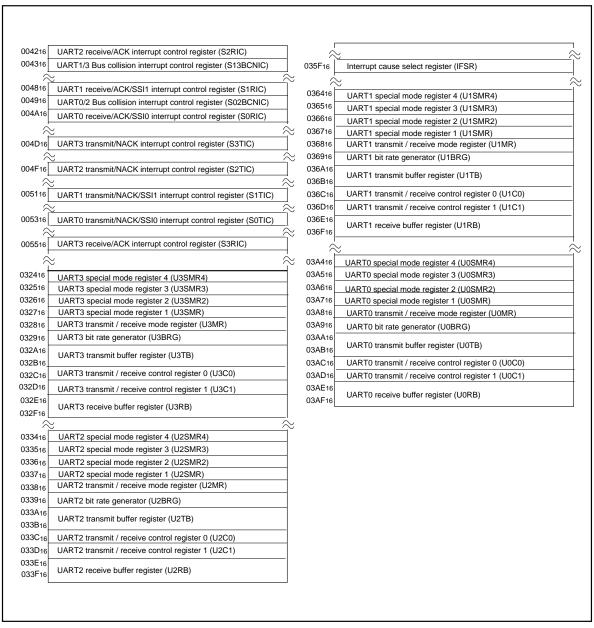

Figure 2.3.1. Memory map of serial I/O-related registers

Figure 2.3.2. Serial I/O-related registers (1)

Figure 2.3.3. Serial I/O-related registers (2)

Figure 2.3.4. Serial I/O-related registers (3)

RENESAS

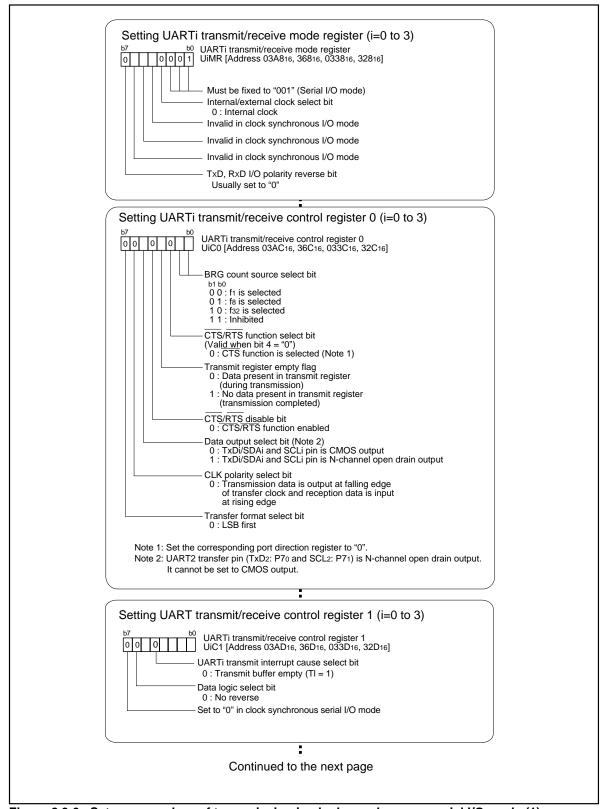

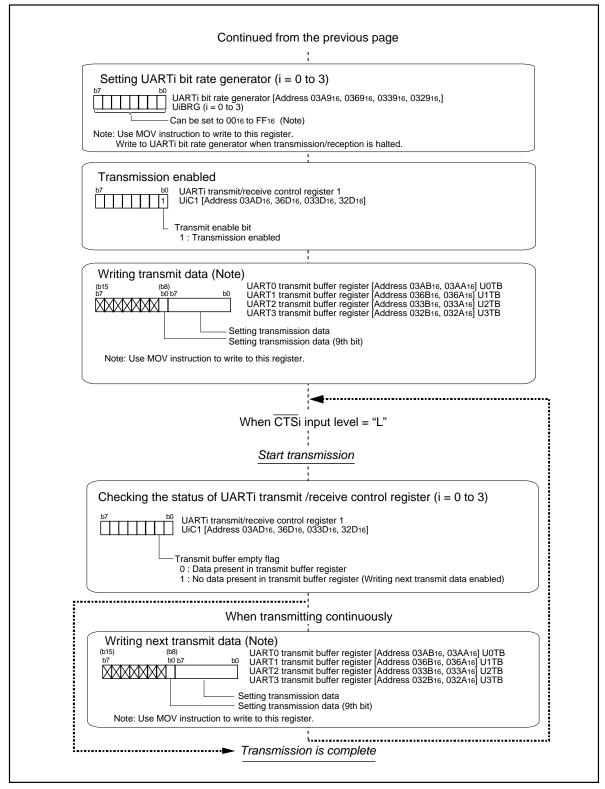

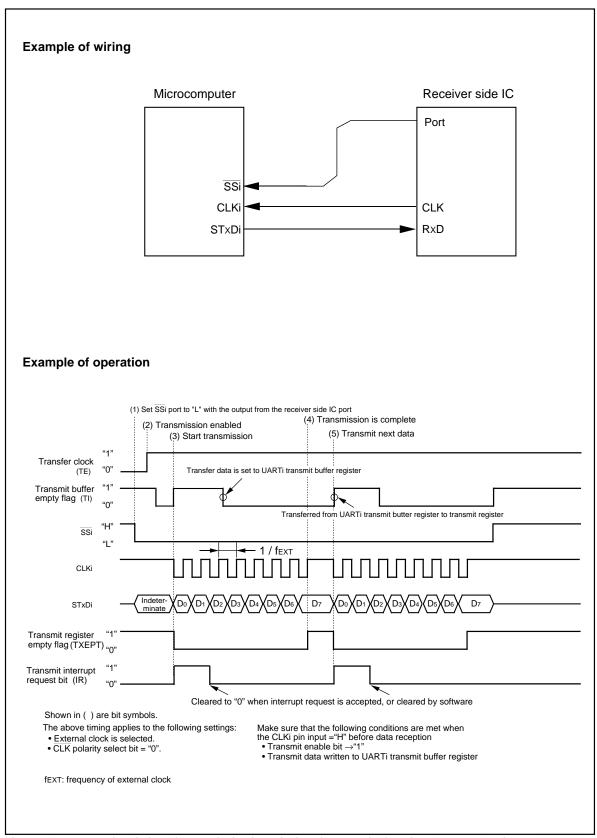

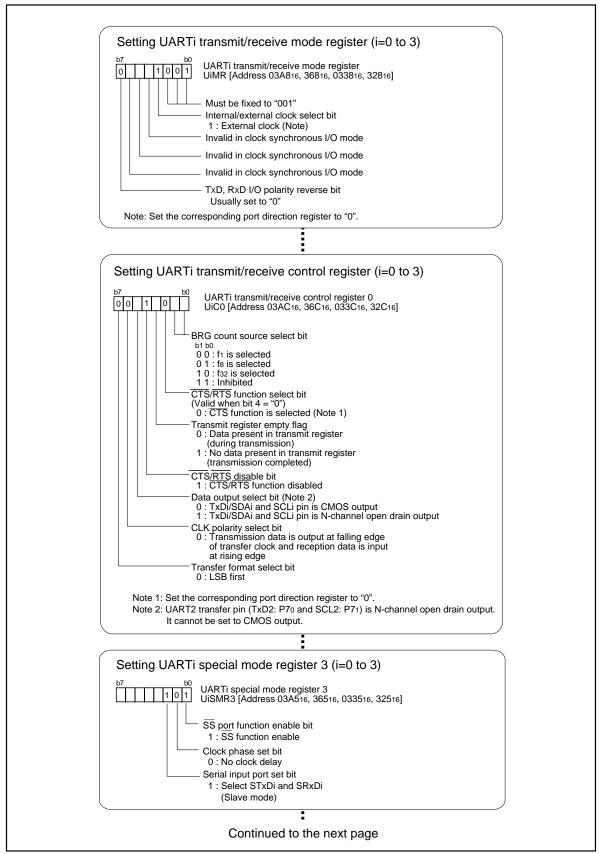

## 2.3.2 Operation of Serial I/O (transmission in clock-synchronous serial I/O mode)

In transmitting data in clock-synchronous serial I/O mode, choose functions from those listed in Table 2.3.1. Operations of the circled items are described below. Figure 2.3.5 shows the operation timing, and Figures 2.3.6 and 2.3.7 show the set-up procedures.

Table 2.3.1. Choosed functions

| Item           | Set-up                                                |                                                                       | Item                 | Set-up    |                           |

|----------------|-------------------------------------------------------|-----------------------------------------------------------------------|----------------------|-----------|---------------------------|

| Transfer clock | clock O Internal clock (f1 / f8 / f32) Transfer clock |                                                                       | 0                    | LSB first |                           |

| source         |                                                       | External clock (CLKi pin)                                             |                      |           | MSB first                 |

| CTS function   | 0                                                     | CTS function enabled                                                  | Transmission         | 0         | Transmission buffer empty |

|                |                                                       | CTS function disabled                                                 | interrupt factor     |           | Transmission complete     |

| CLK polarity   | 0                                                     | Output transmission data at the falling edge of the Data logic select | Data logic select    | 0         | No reverse                |

|                |                                                       | transfer clock                                                        | function             |           | Reverse                   |

|                | Output transmission data at the rising edge of the    | 0                                                                     | No reverse           |           |                           |

|                |                                                       | transfer clock                                                        | polarity reverse bit |           | Reverse                   |

- Operation (1) Setting the transmit enable bit to "1" and writing transmission data to the UARTi transmit buffer register makes data transmissible status ready.

- (2) When input to the CTSi pin goes to "L" level, transmission starts (the CTSi pin must be controlled on the reception side).

- (3) In synchronization with the first falling edge of the transfer clock, transmission data held in the UARTi transmit buffer register is transmitted to the UARTi transmit register. At this time, the UARTi transmit interrupt request bit goes to "1". Also, the first bit of the transmission data is transmitted from the TxDi pin. Then the data is transmitted bit by bit from the lower order in synchronization with the falling edges.

- (4) When transmission of 1-byte data is completed, the transmit register empty flag goes to "1", which indicates that transmission is completed. The transfer clock stops at "H" level.

- (5) If the next transmission data is set in the UARTi transmit buffer register while transmission is in progress (before the eighth bit has been transmitted), the data is transmitted in succession.

Figure 2.3.5. Operation timing of transmission in clock-synchronous serial I/O mode

Figure 2.3.6. Set-up procedure of transmission in clock-synchronous serial I/O mode (1)

Figure 2.3.7. Set-up procedure of transmission in clock-synchronous serial I/O mode (2)

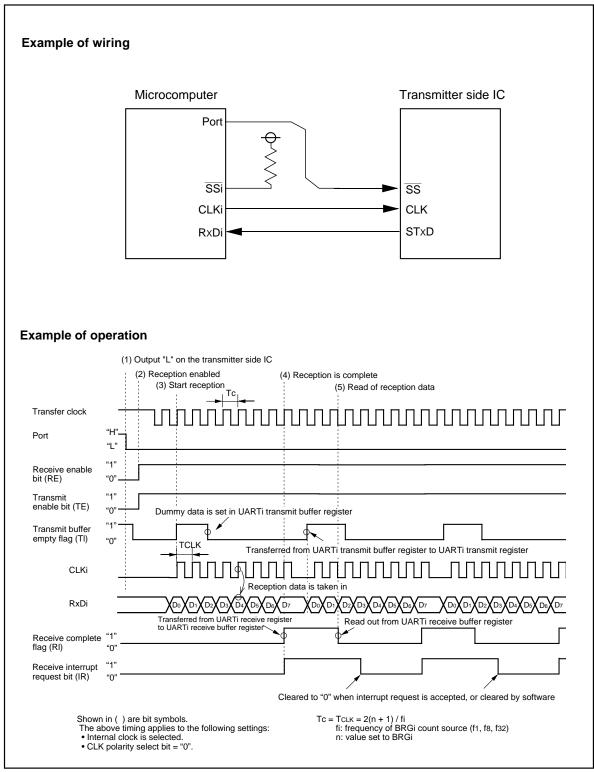

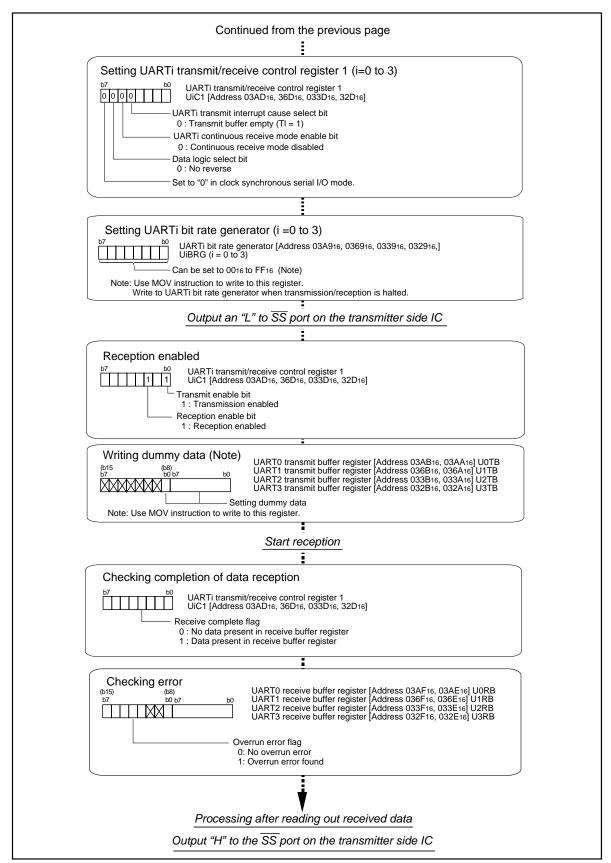

## 2.3.3 Operation of Serial I/O (reception in clock-synchronous serial I/O mode)

In receiving data in clock-synchronous serial I/O mode, choose functions from those listed in Table 2.3.2. Operations of the circled items are described below. Figure 2.3.8 shows the operation timing, and Figures 2.3.9 and 2.3.10 show the set-up procedures.

Table 2.3.2. Choosed functions

| Item           | Set-up                                             |                                                     | Item                   | Set-up |            |

|----------------|----------------------------------------------------|-----------------------------------------------------|------------------------|--------|------------|

| Transfer clock | 0                                                  | Internal clock (f1 / f8 / f32)                      | Transfer clock         | 0      | LSB first  |

| source         |                                                    | External clock (CLKi pin)                           |                        |        | MSB first  |

| RTS function   | 0                                                  | RTS function enabled                                | Continuous receive     | 0      | Disabled   |

|                |                                                    | RTS function disabled                               | abled                  |        | Enabled    |

| CLK polarity   | 0                                                  | Output transmission data at the falling edge of the | a at Data logic select | 0      | No reverse |

|                |                                                    | transfer clock                                      | function               |        | Reverse    |

|                | Output transmission data at the rising edge of the | 0                                                   | No reverse             |        |            |

|                |                                                    | transfer clock                                      | polarity reverse bit   |        | Reverse    |

- Operation (1) Writing dummy data to the UARTi transmit buffer register, setting the receive enable bit to "1", and the transmit enable bit to "1", makes the data receivable status ready. At this time, the output from the RTSi pin goes to "L" level, which informs the transmission side that the data receivable status is ready (output the transfer clock from the IC on the transmission side after

- checking that the RTS output has gone to "L" level).

- (2) In synchronization with the first rising edge of the transfer clock, the input signal to the RxDi pin is stored in the highest bit of the UARTi receive register. Then, data is taken in by shifting right the content of the UARTi reception data in synchronization with the rising edges of the transfer clock.

- (3) When 1-byte data lines up in the UARTi receive register, the content of the UARTi receive register is transmitted to the UARTi receive buffer register. The transfer clock stops at "H" level. At this time, the receive complete flag and the UARTi receive interrupt request bit goes to "1"

- (4) The receive complete flag goes to "0" when the lower-order byte of the UARTi buffer register is read.

Note • Set CLKi and RxDi pins' port direction register to "0".

Figure 2.3.8. Operation timing of reception in clock-synchronous serial I/O mode

Figure 2.3.9. Set-up procedure of reception in clock-synchronous serial I/O mode (1)

Figure 2.3.10. Set-up procedure of reception in clock-synchronous serial I/O mode (2)

## 2.3.4 Precautions for Serial I/O (in clock-synchronous serial I/O mode)

Transmission/reception

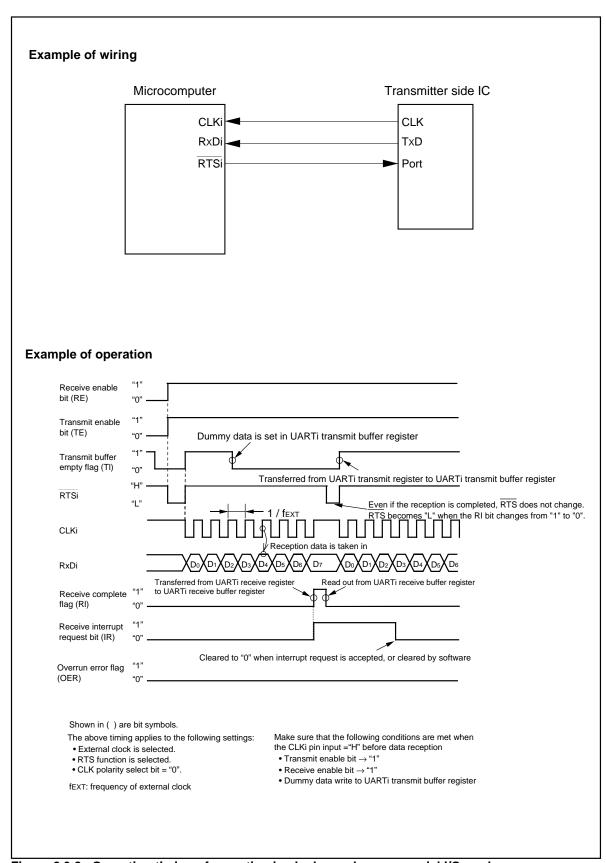

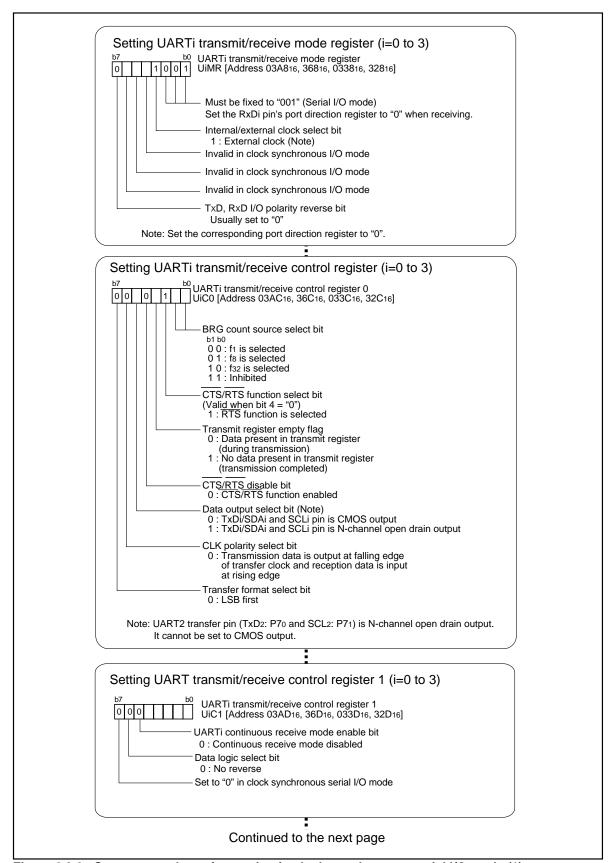

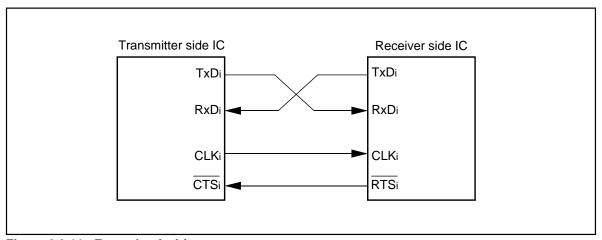

(1) With an external clock selected, and choosing the RTS function, the output level of the RTSi pin goes to "L" when the data-receivable status becomes ready, which informs the transmission side that the reception has become ready. The output level of the RTSi pin goes to "H" when reception starts. So if the RTSi pin is connected to the CTSi pin on the transmission side, the circuit can transmission and reception data with consistent timing. With the internal clock, the RTS function has no effect. Figure 2.3.11 shows an example of wiring.

Figure 2.3.11. Example of wiring

### Transmission

- (1) With an external clock selected, perform the following set-up procedure with the CLKi pin input level = "H" if the CLK polarity select bit = "0" or with the CLKi pin input level = "L" if the CLK polarity select bit = "1":

- 1. Set the transmit enable bit (to "1")

- 2. Write transmission data to the UARTi transmit buffer register

- 3. "L" level input to the CTSi pin (when the CTS function is selected)

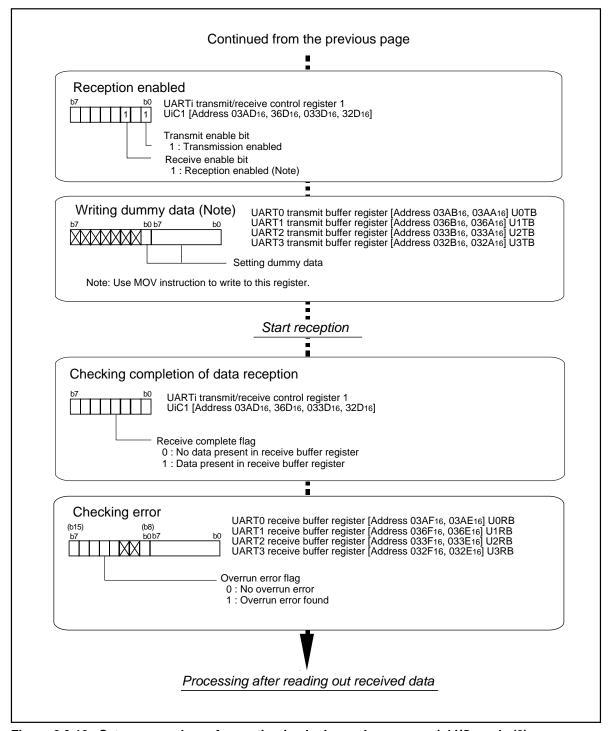

- Reception (1) In operating the clock-synchronous serial I/O, operating a transmitter generates a shift clock.

Fix settings for transmission even when using the device only for reception. Dummy data is output to the outside from the TxDi pin (transmission pin) when receiving data.

- (2) With the internal clock selected, setting the transmit enable bit to "1" (transmission-enabled status) and setting dummy data in the UARTi transmission buffer register generates a shift clock.

- With the external clock selected, a shift clock is generated when the transmit enable bit is set to "1", dummy data is set in the UARTi transmit buffer register, and the external clock is input to the CLKi pin.

- (3) When receiving data in succession, an overrun error occurs if the serial interface starts receiving the next data item while the receive complete flag is 1 (before reading the contents of the UARTi receive buffer register) and receives the 7th bit of the next data item, and then the overrun error flag is set to "1". In this instance, the next data is written to the UARTi receive buffer register, so handle with this problem by writing programs on transmission side and reception side so that the previous data is transmitted again.

- If an overrun error occurs, the UARTi receive interrupt request bit does not go to "1".

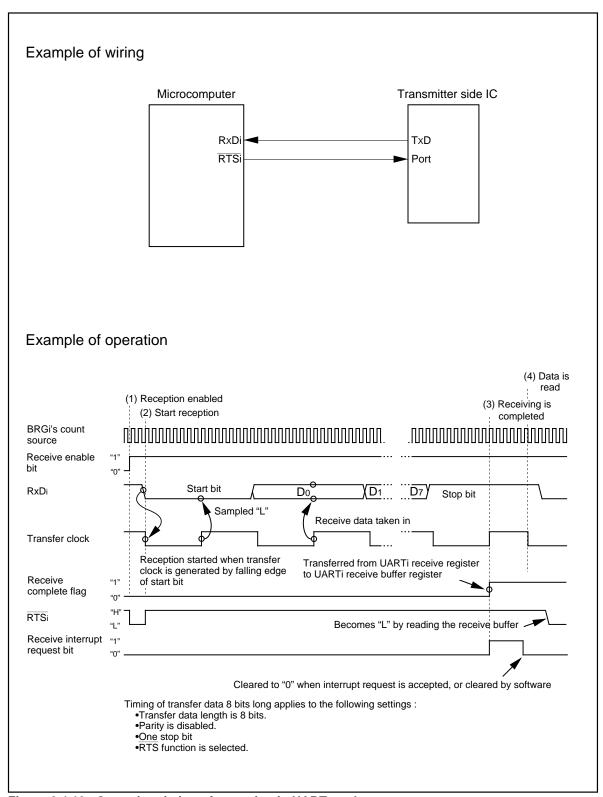

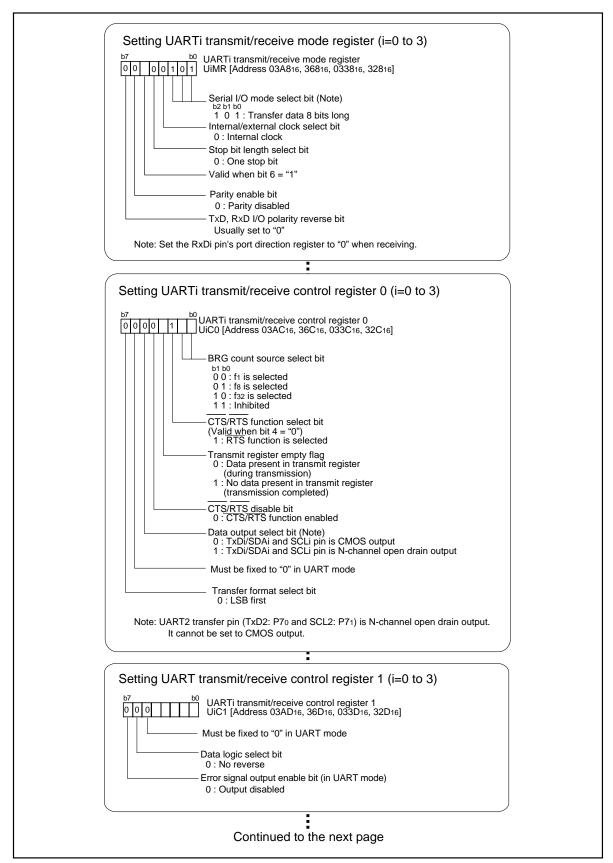

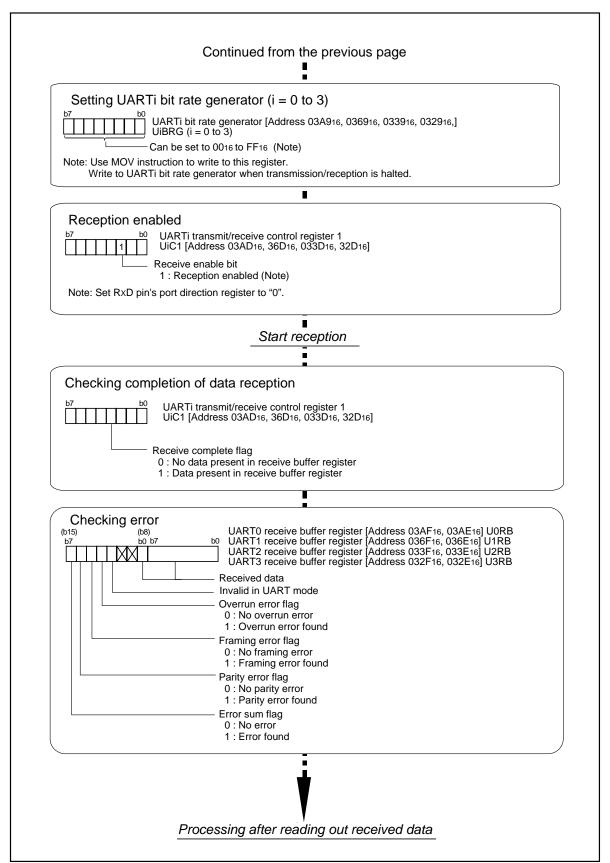

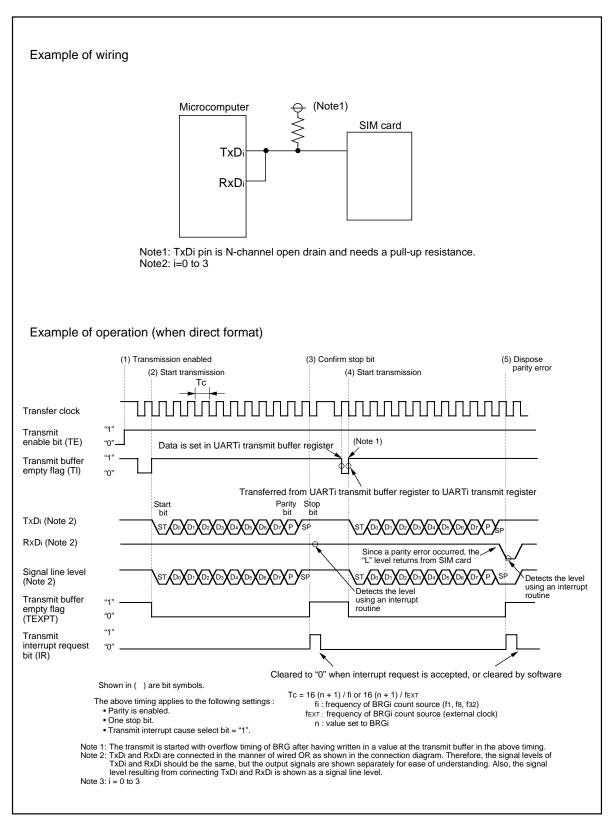

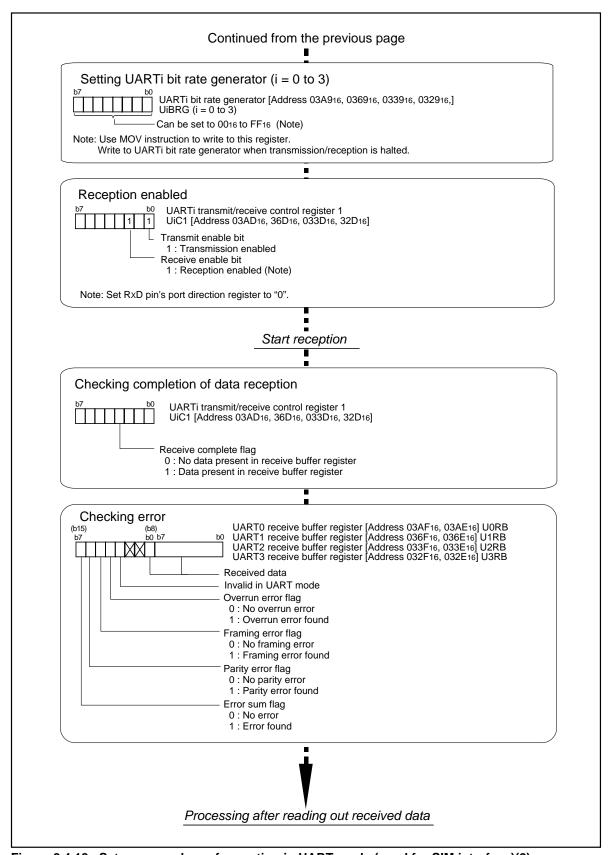

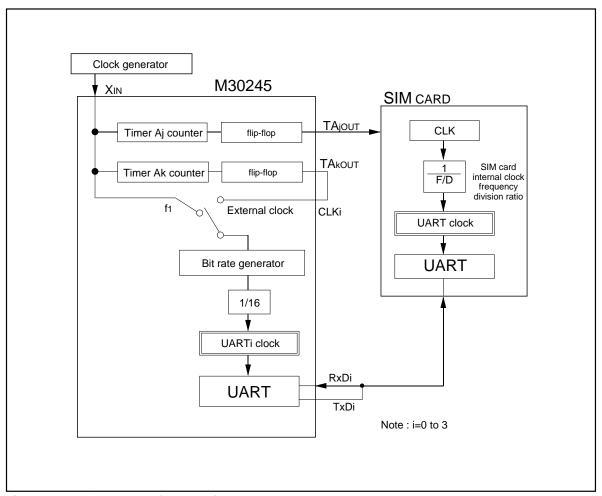

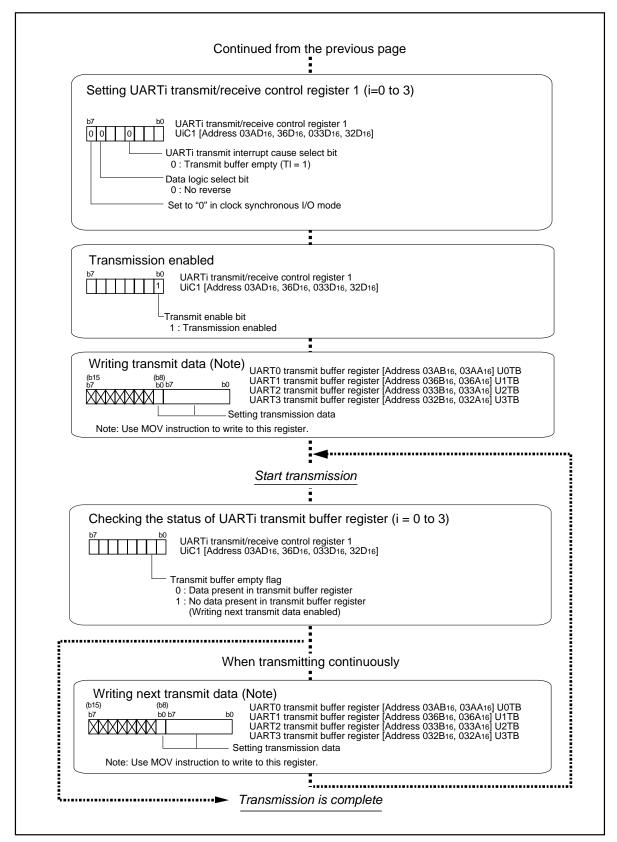

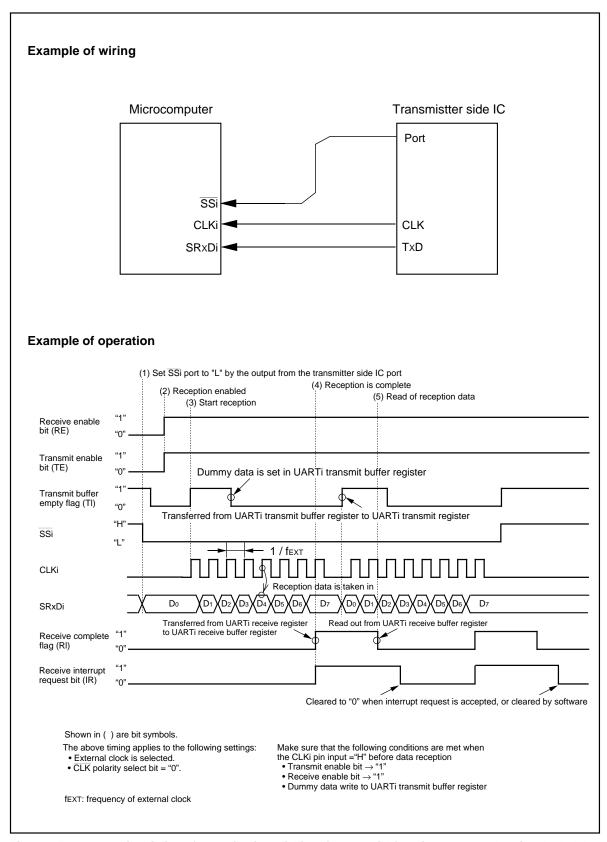

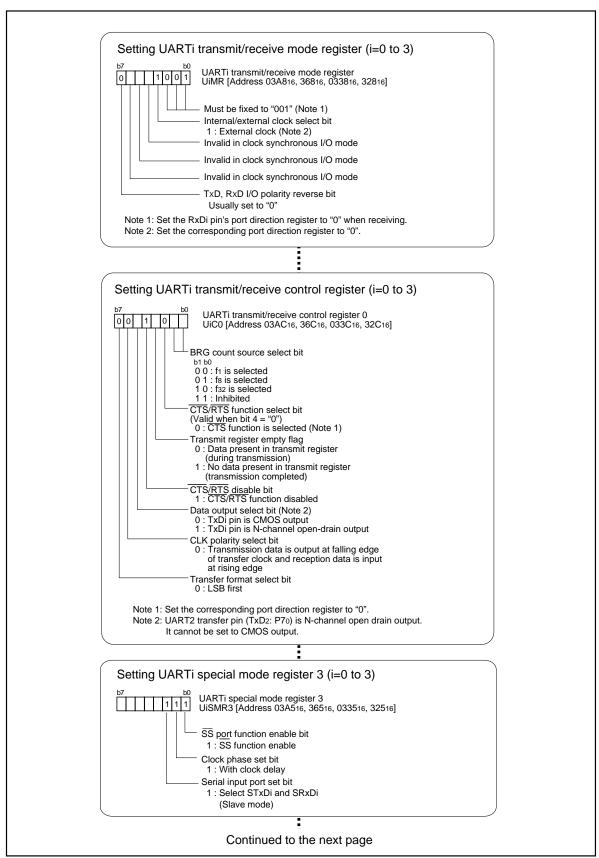

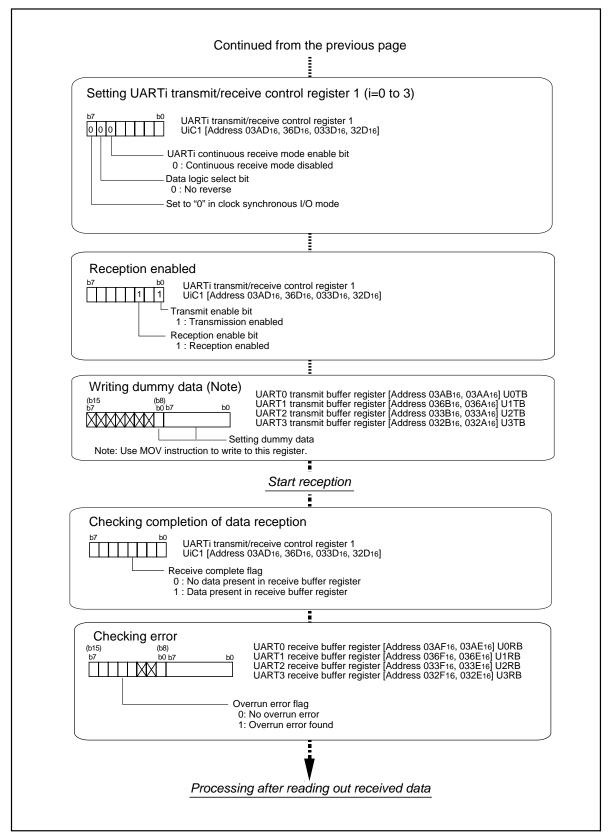

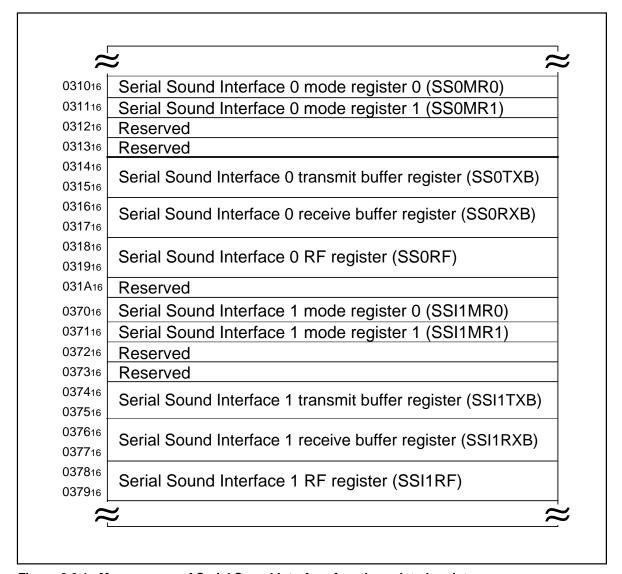

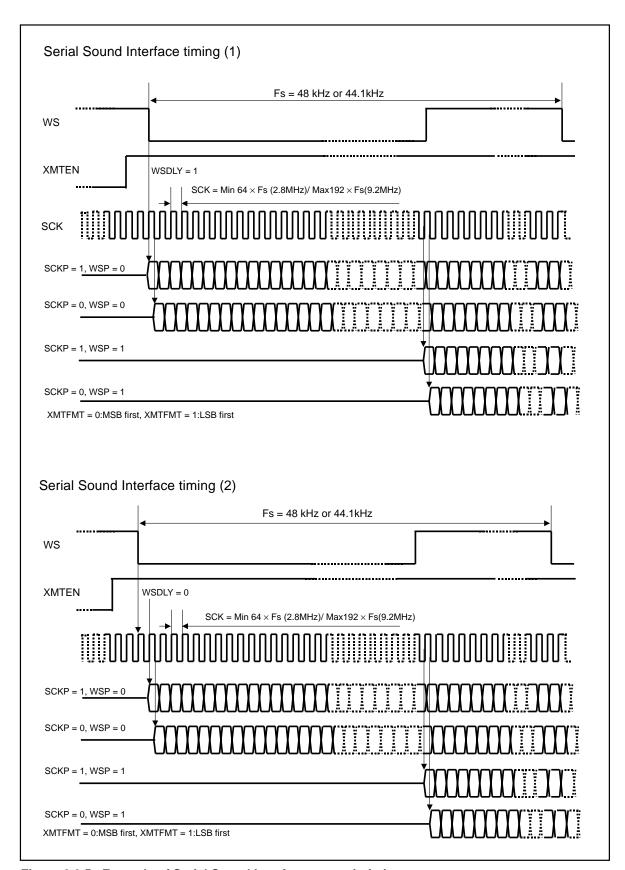

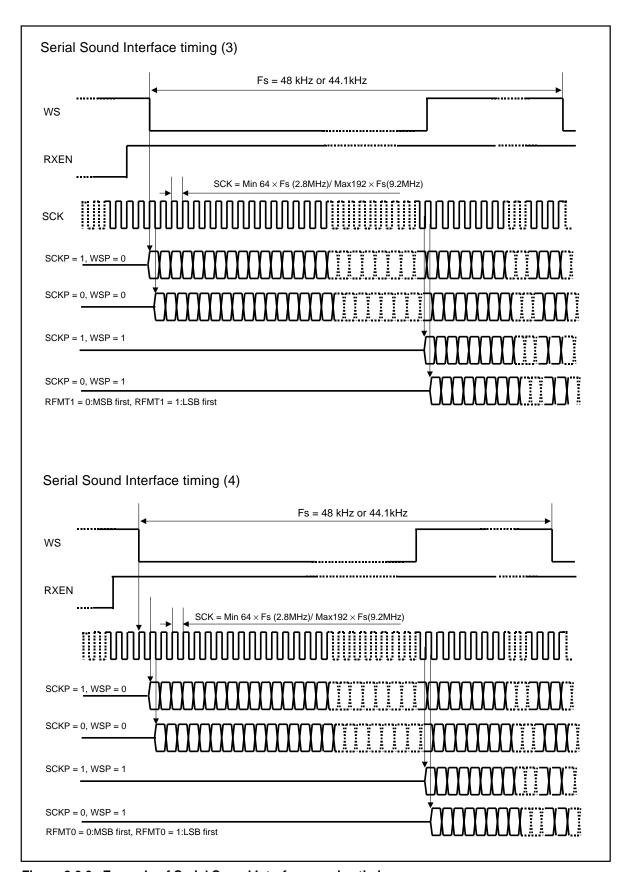

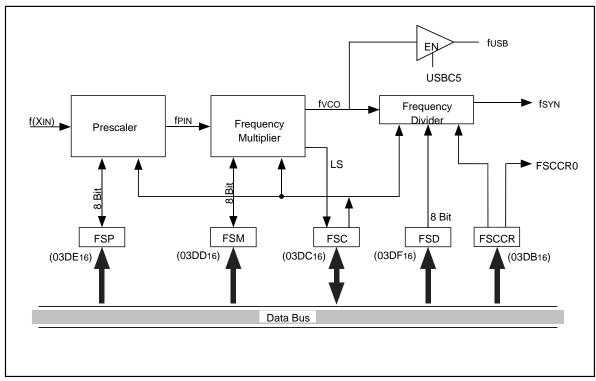

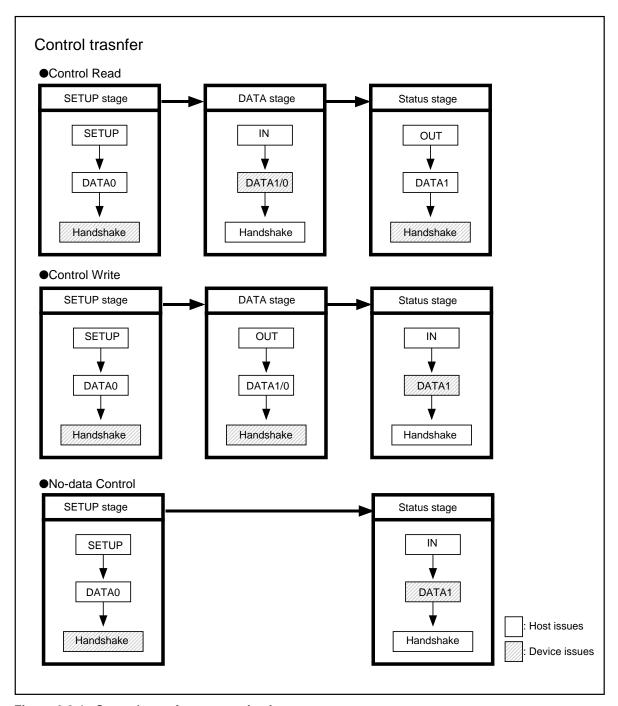

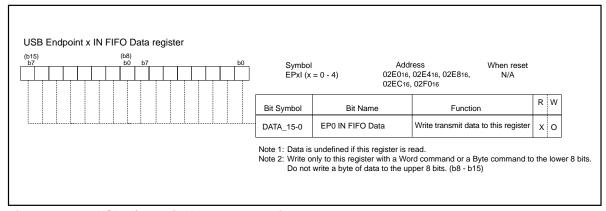

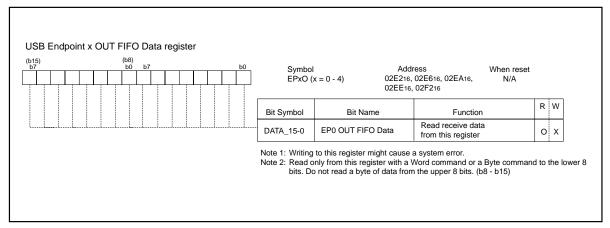

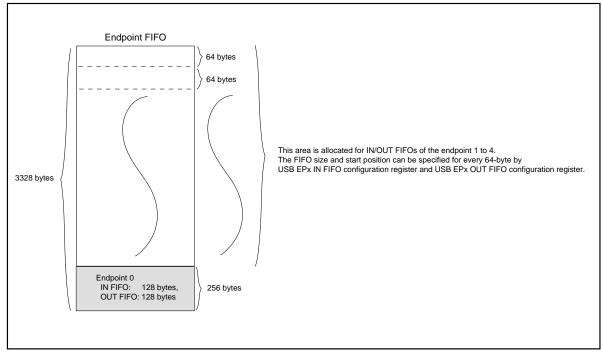

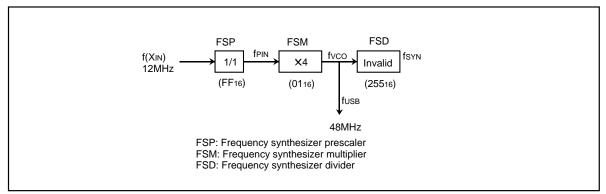

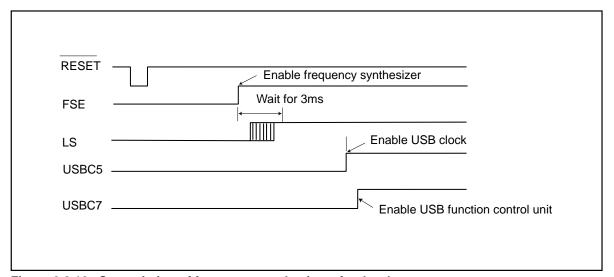

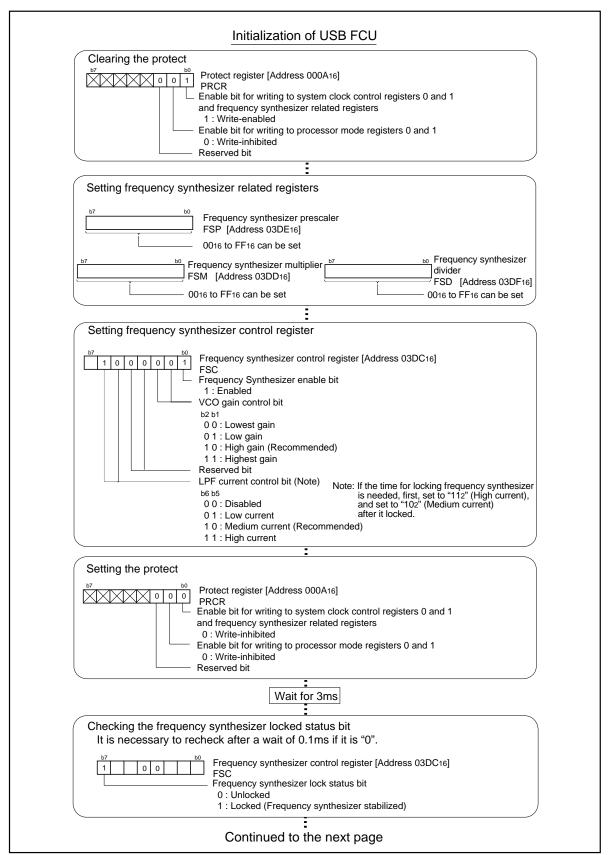

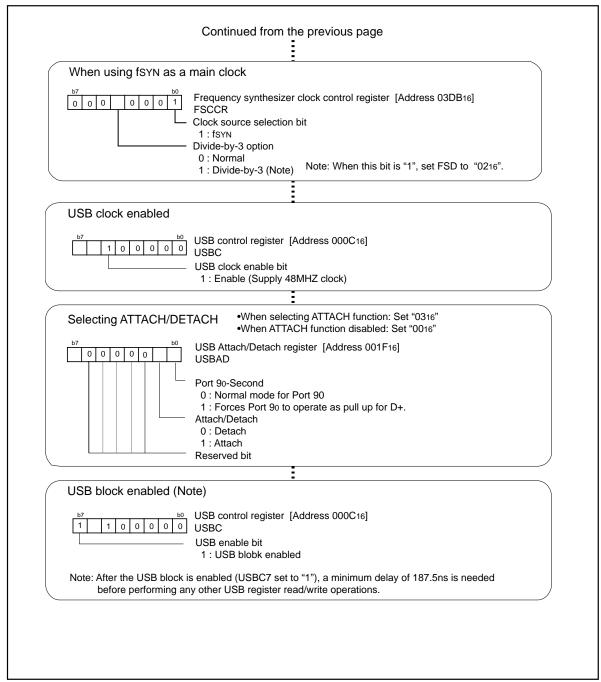

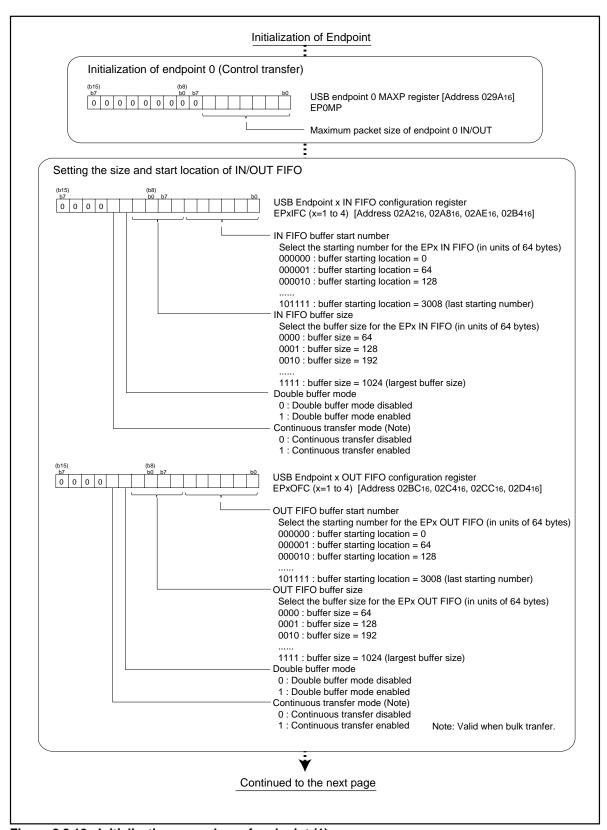

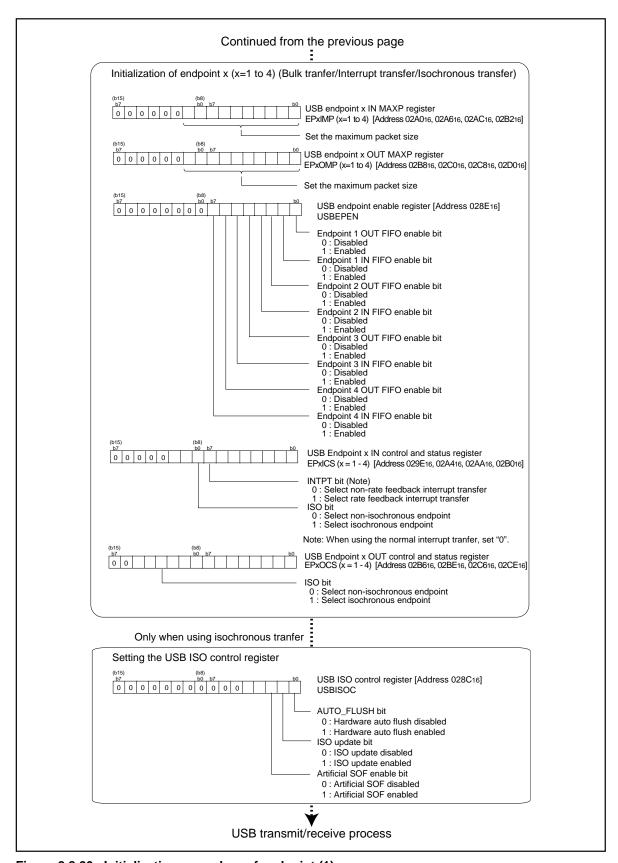

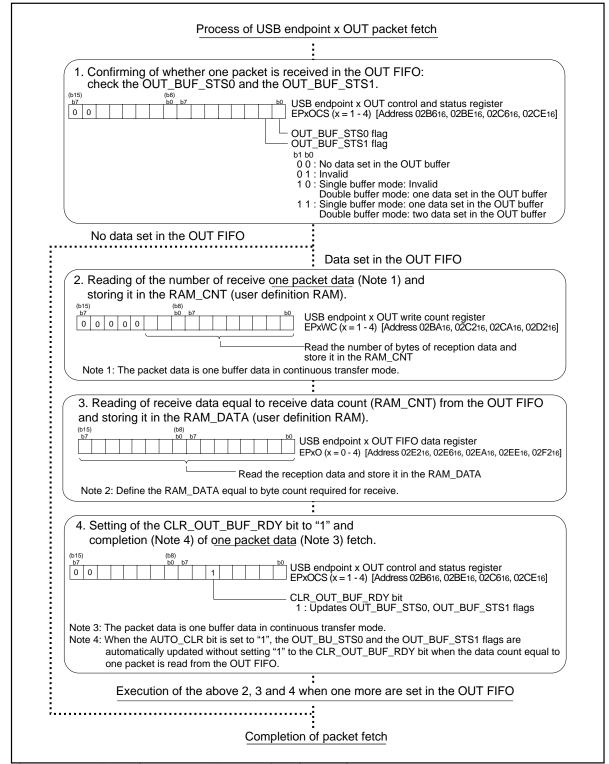

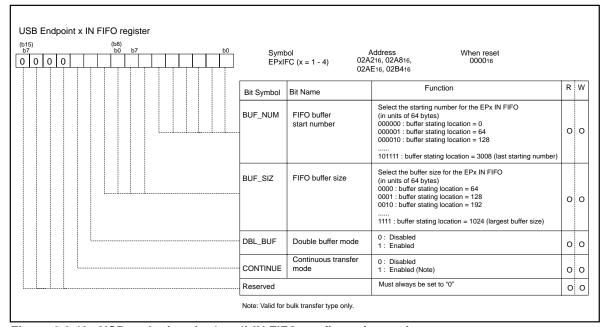

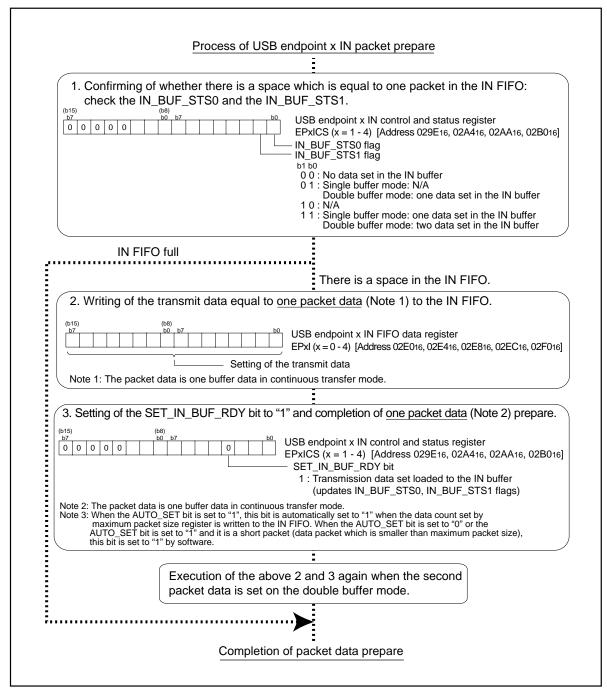

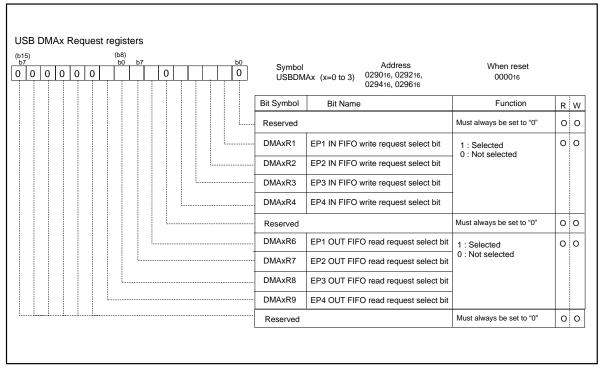

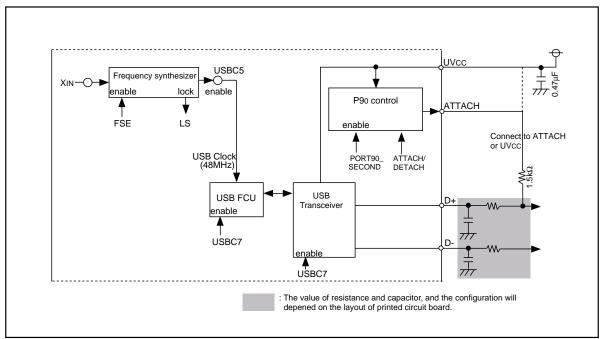

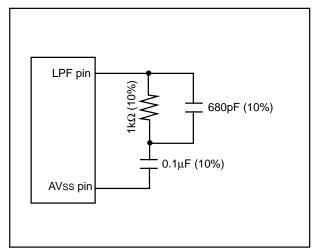

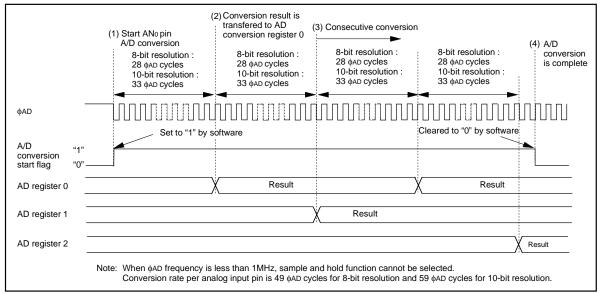

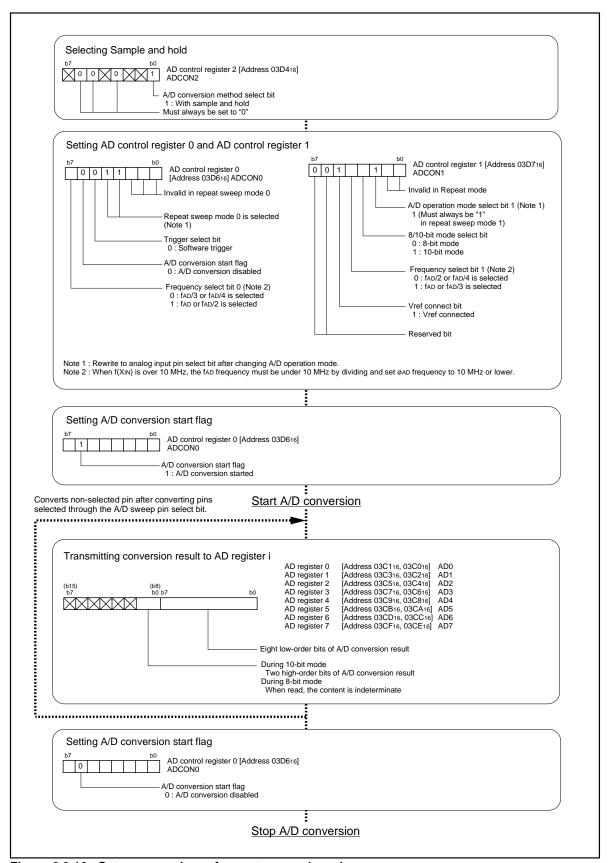

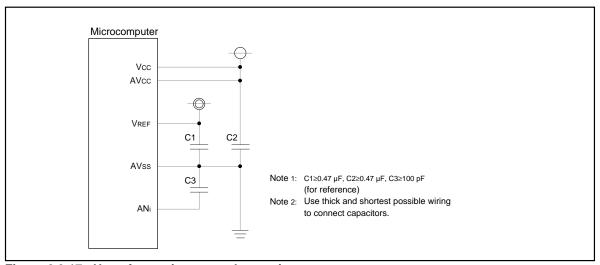

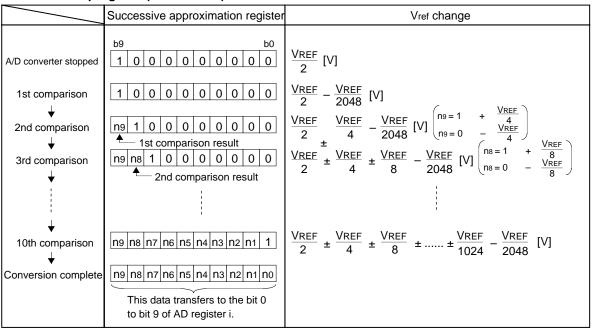

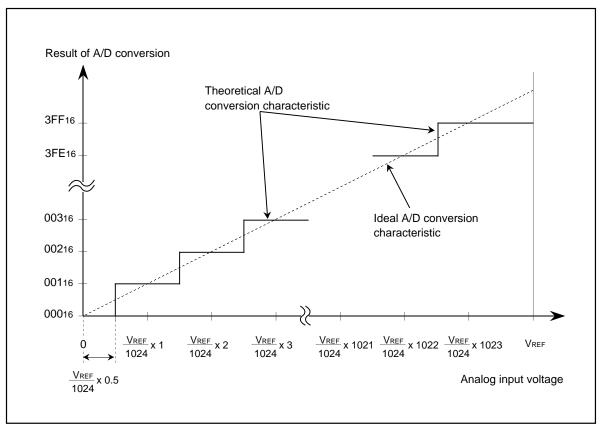

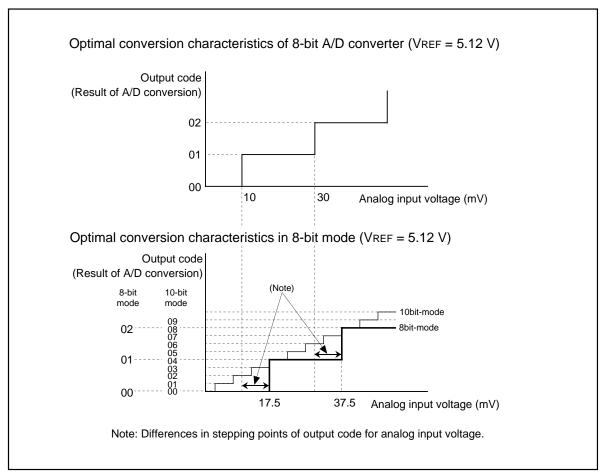

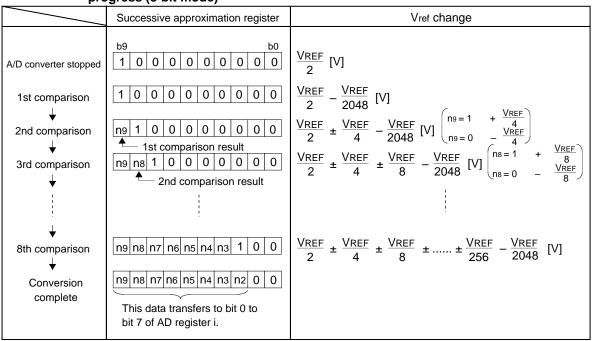

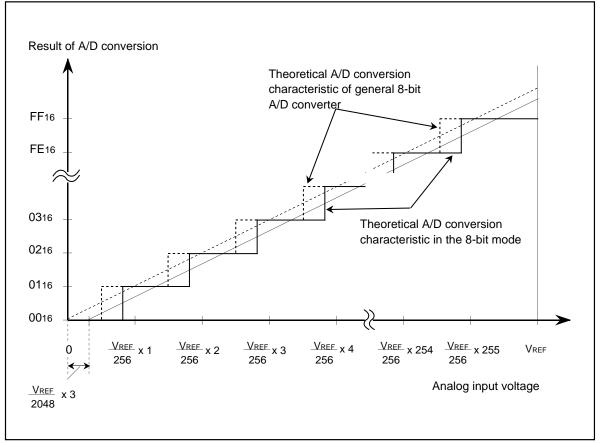

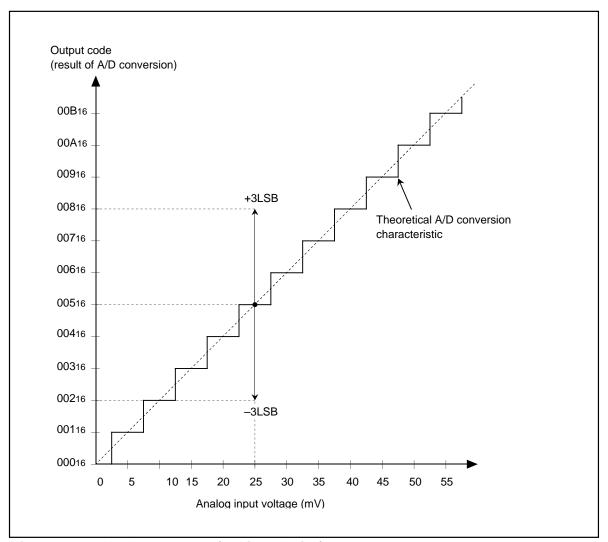

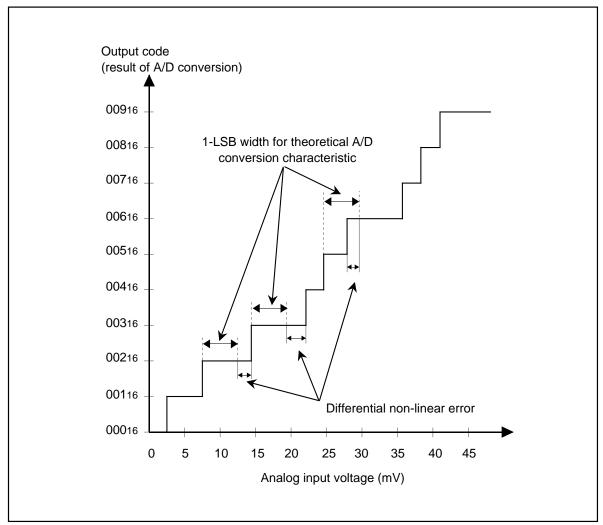

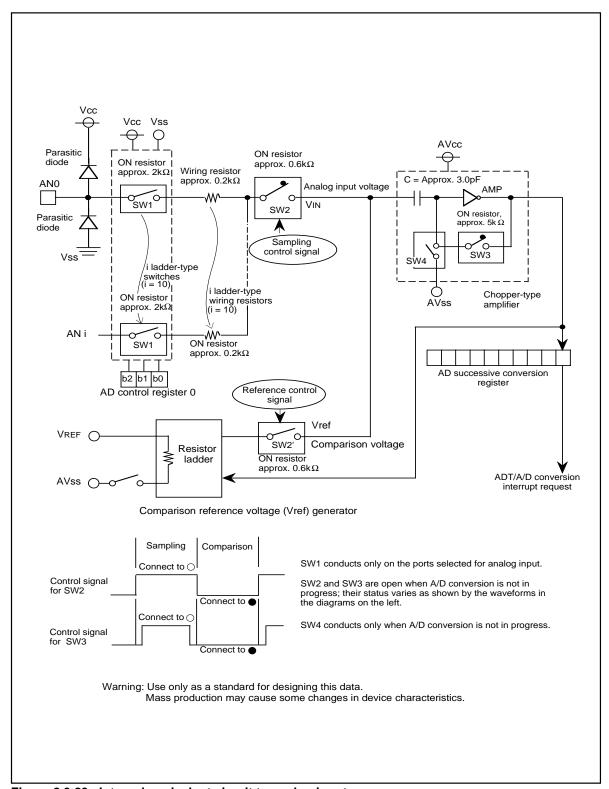

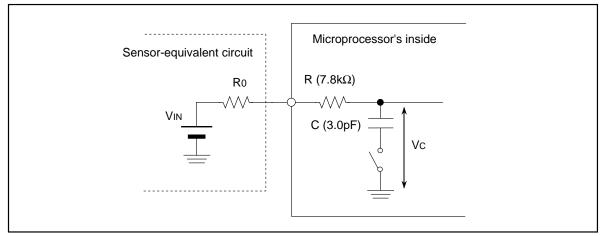

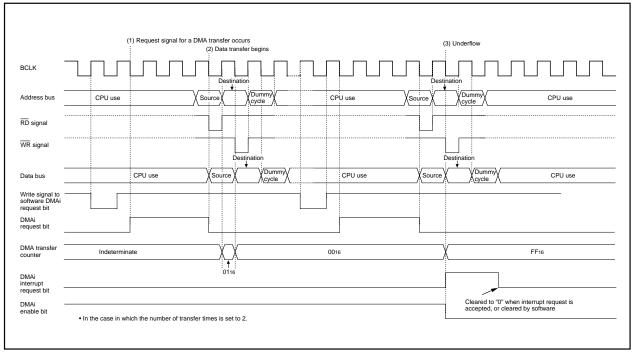

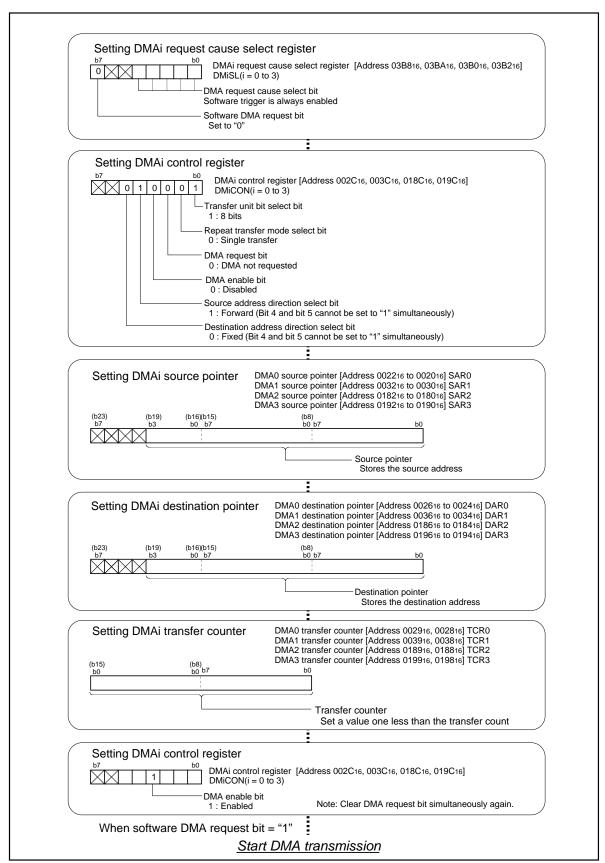

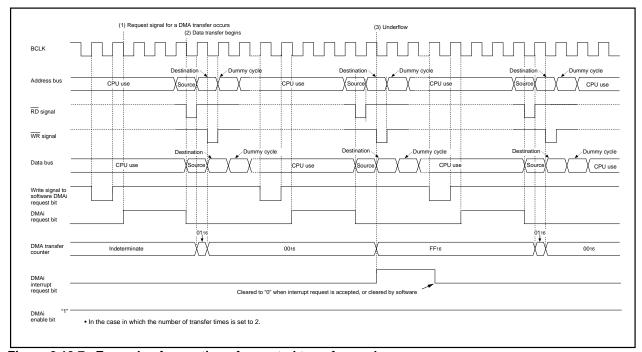

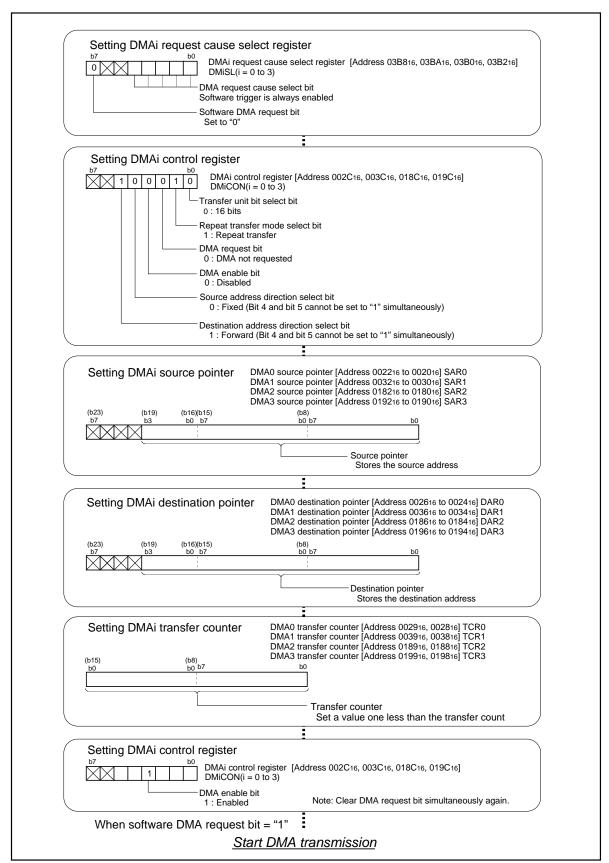

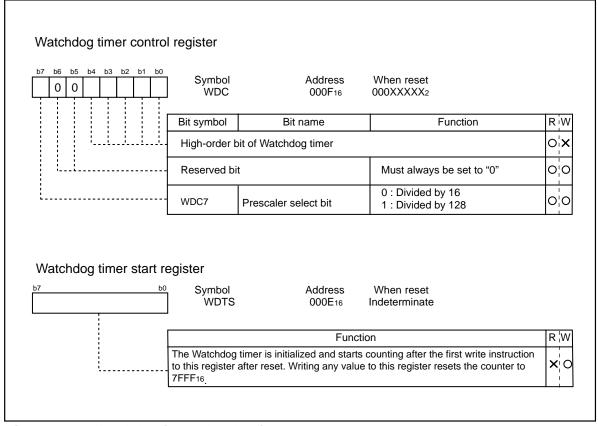

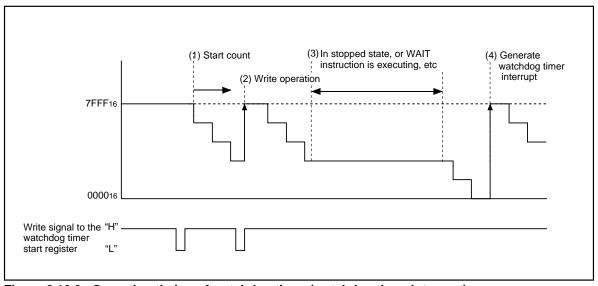

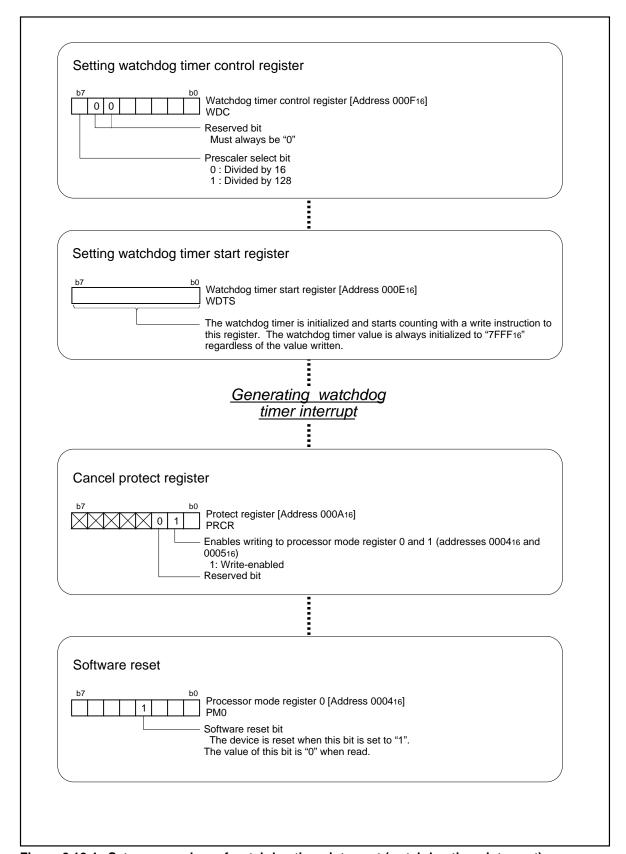

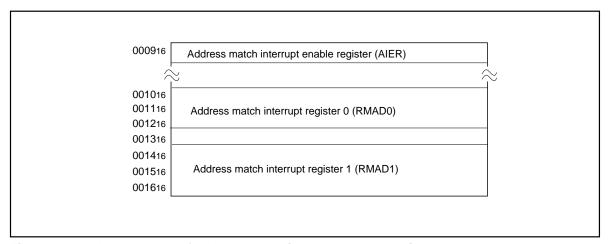

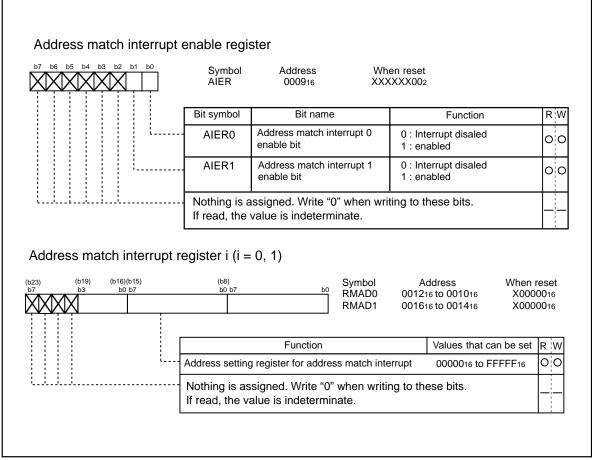

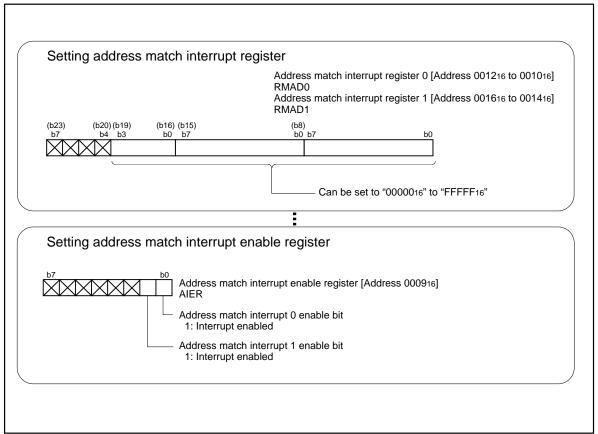

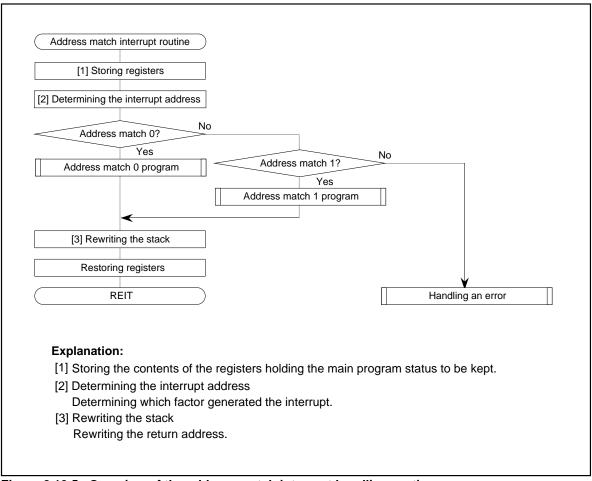

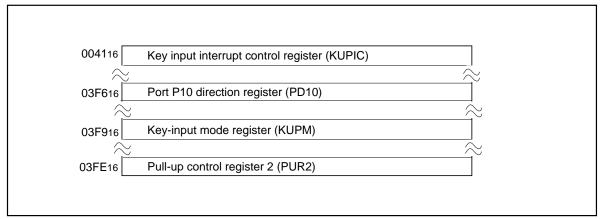

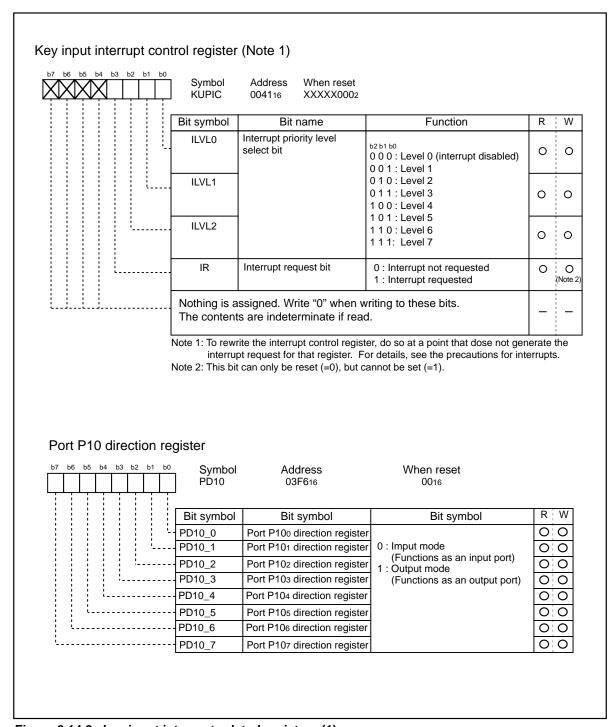

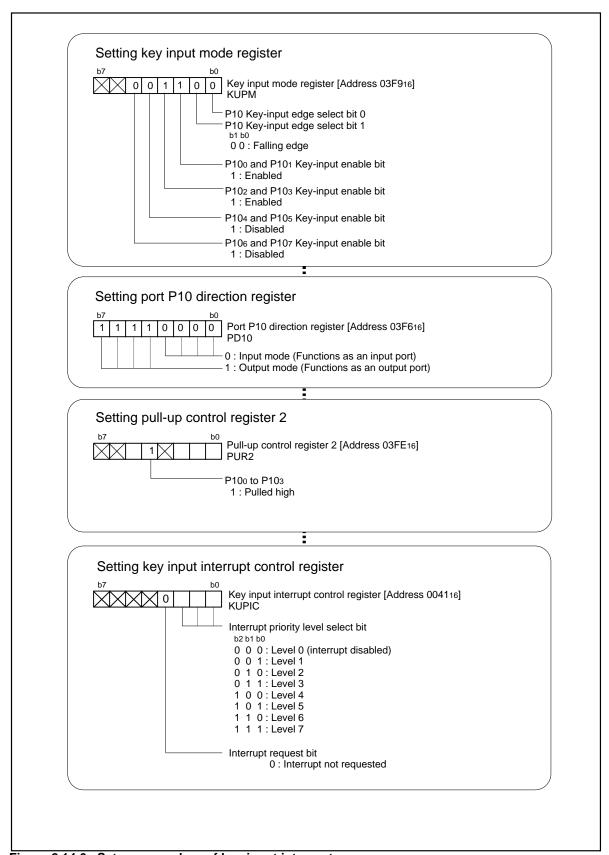

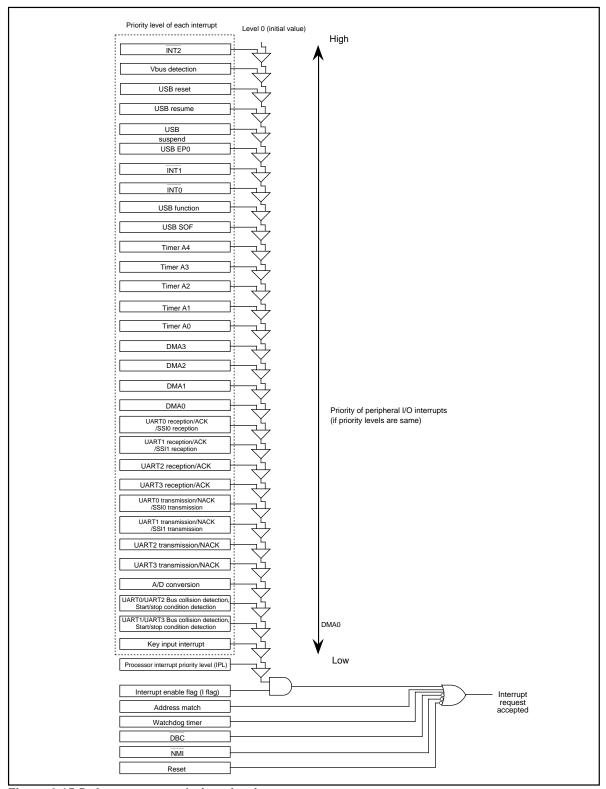

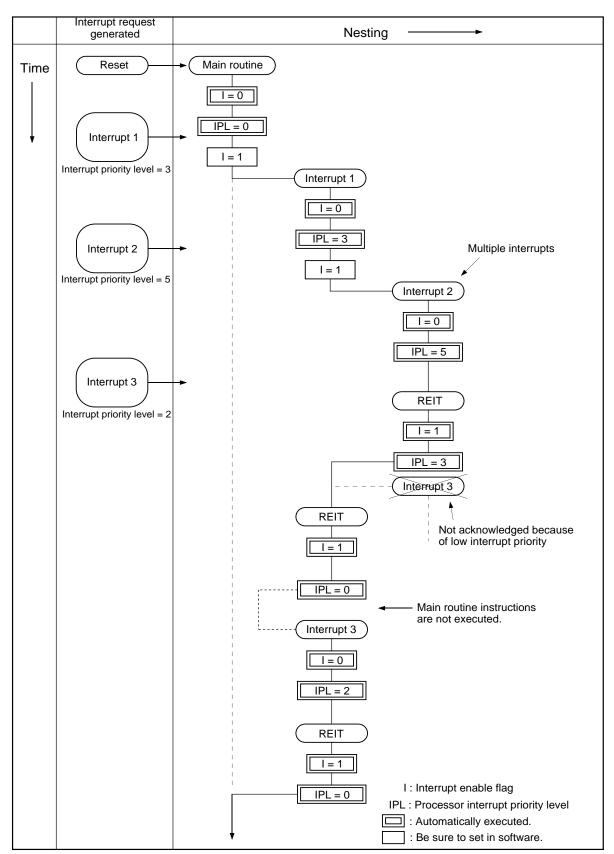

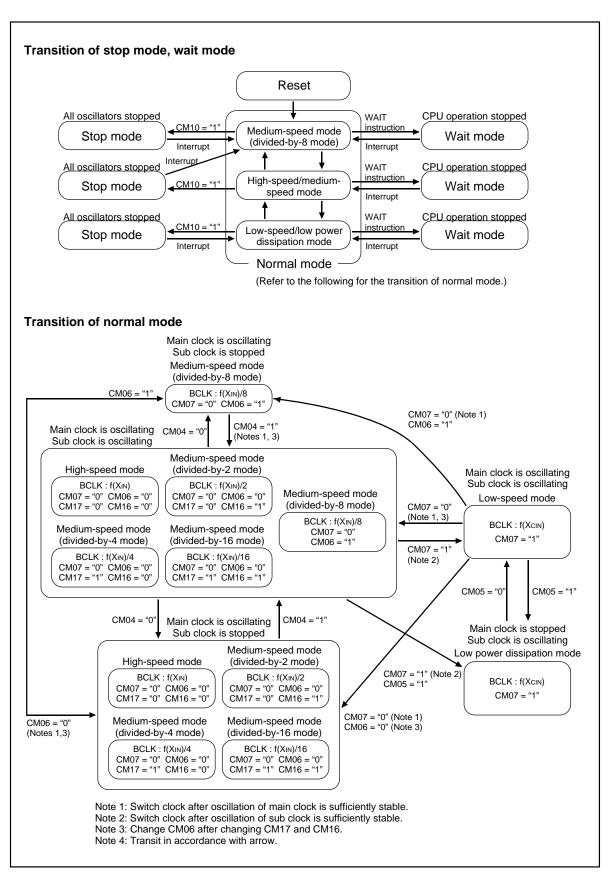

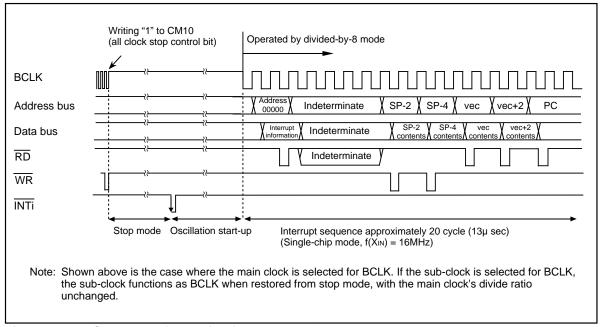

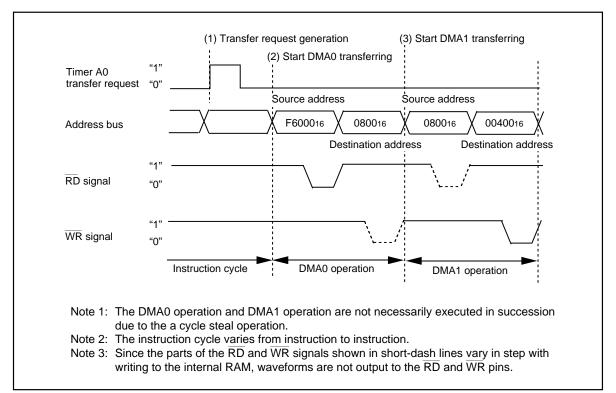

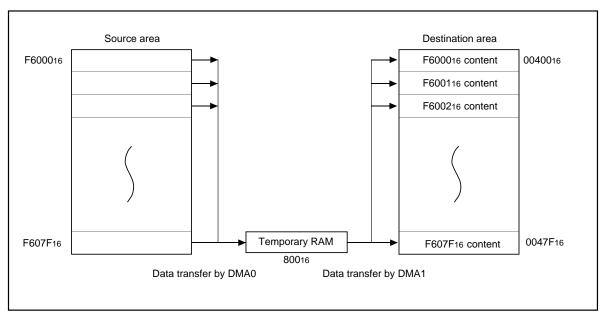

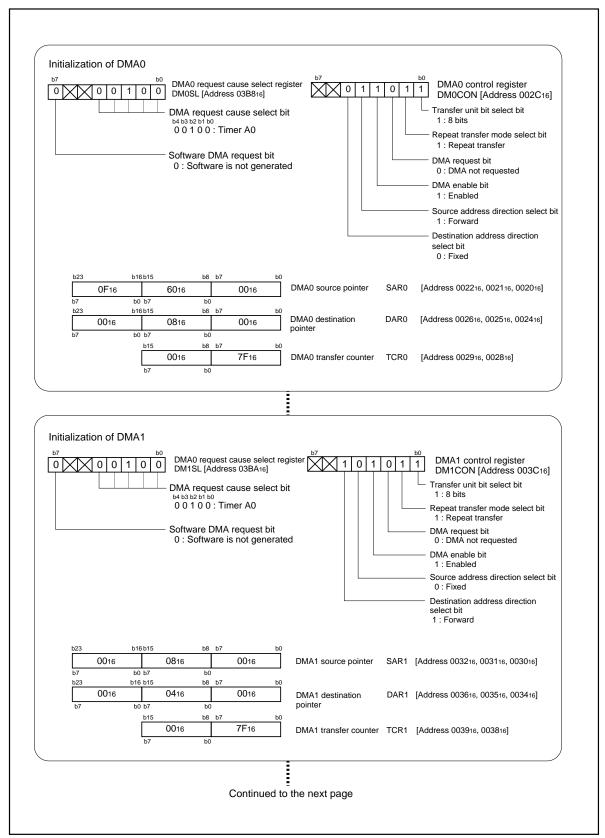

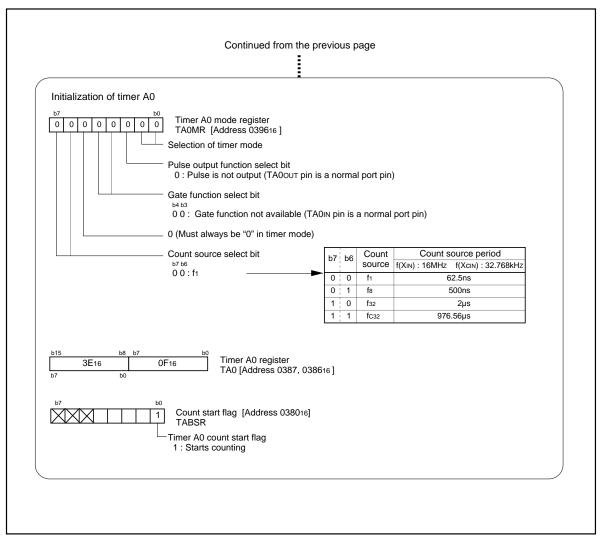

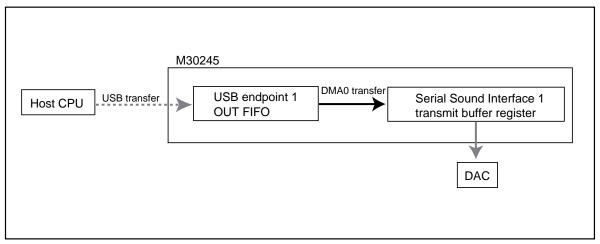

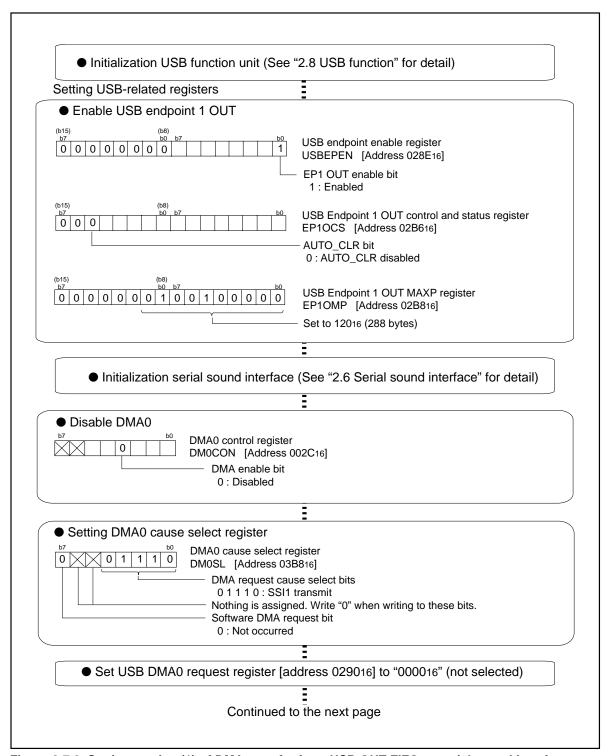

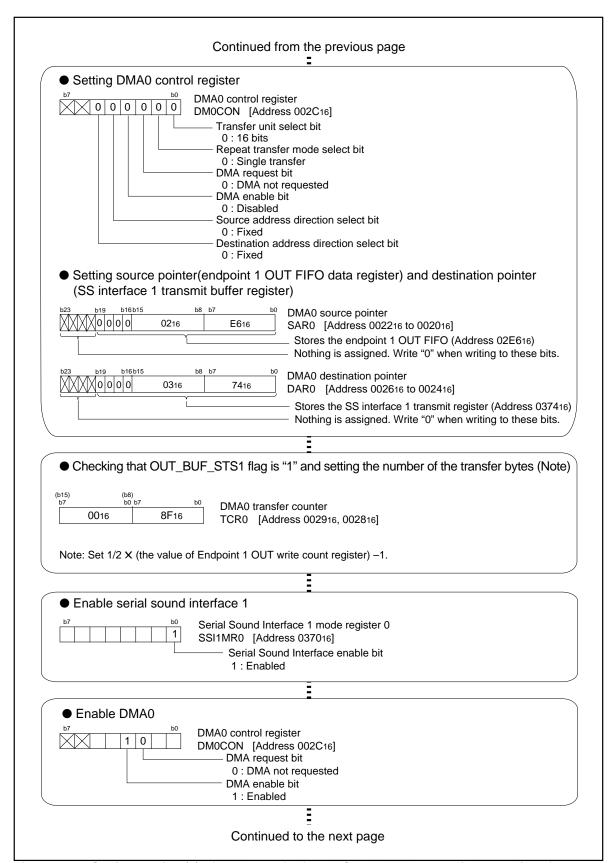

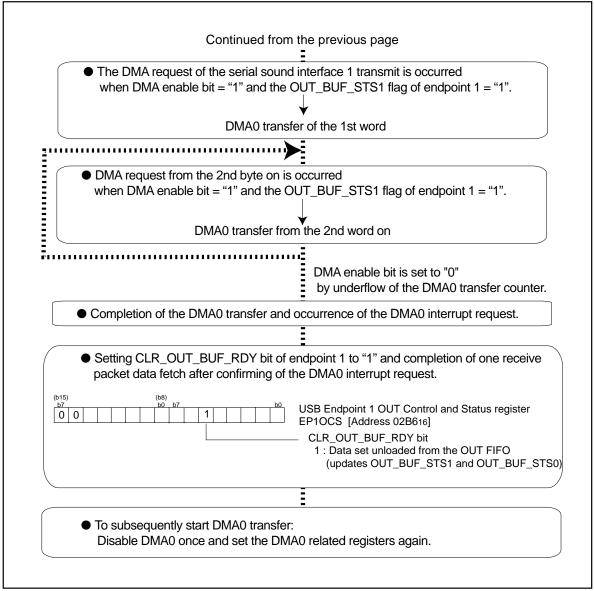

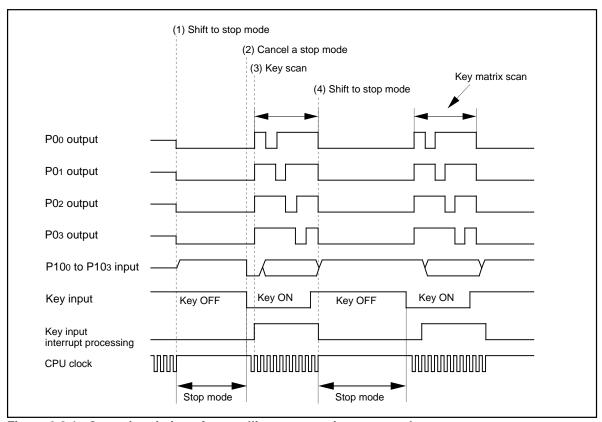

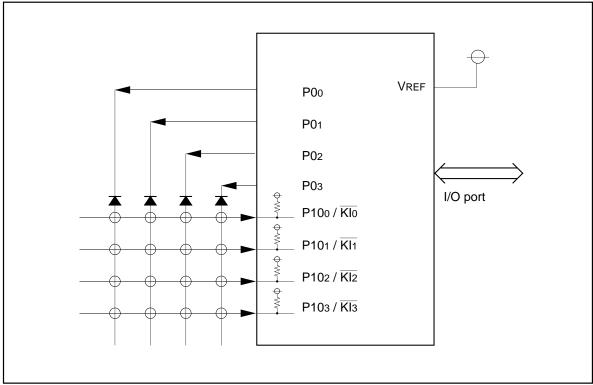

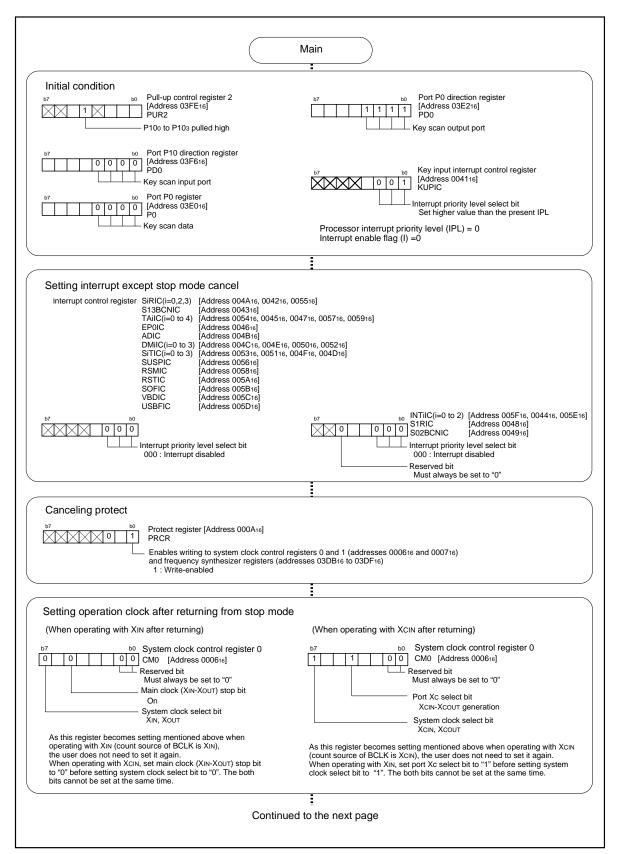

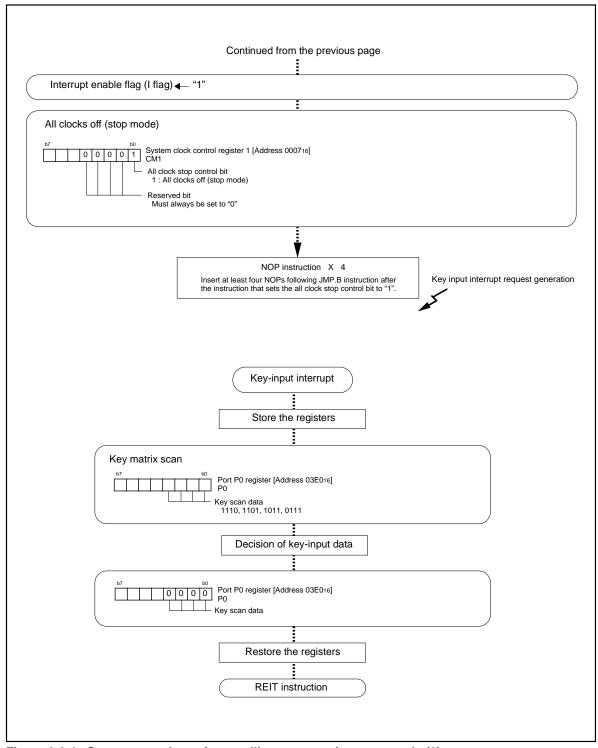

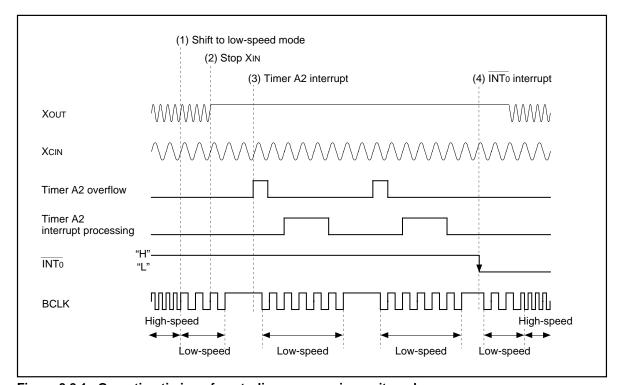

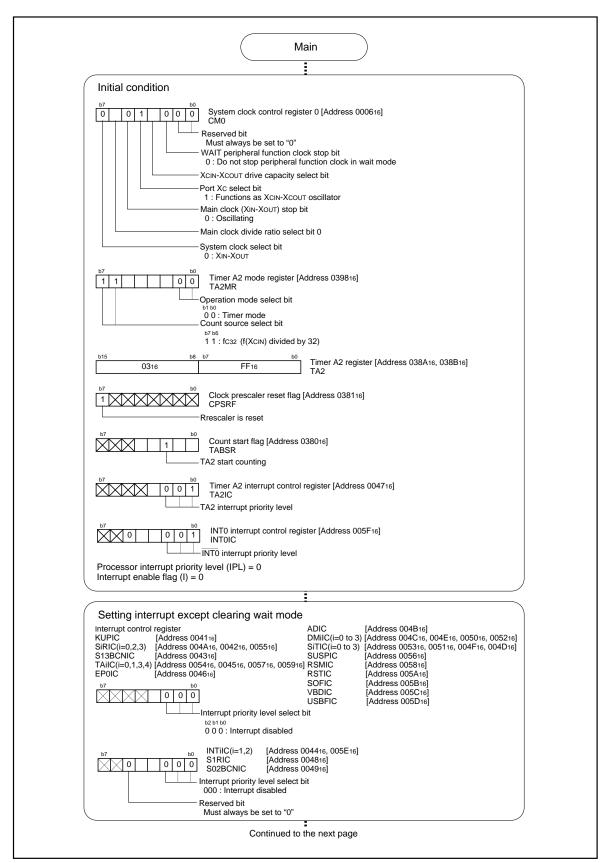

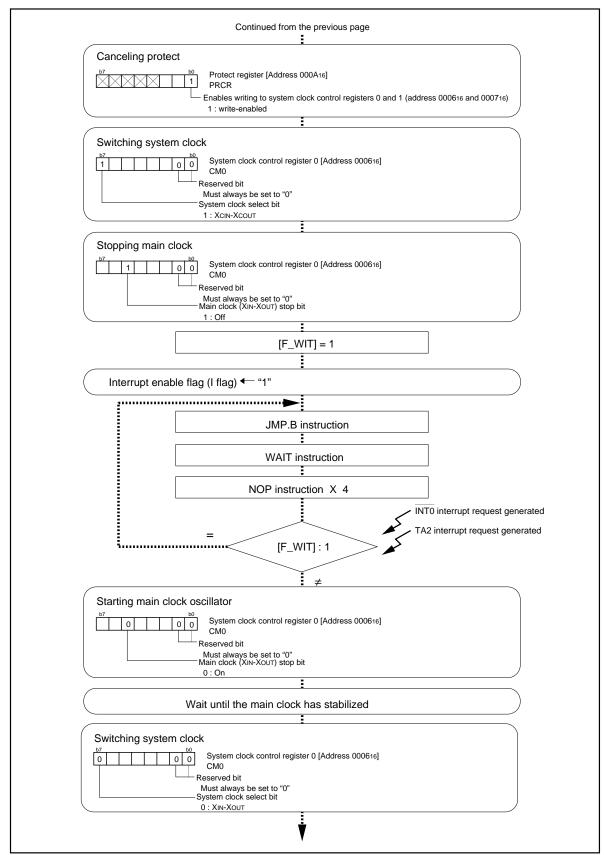

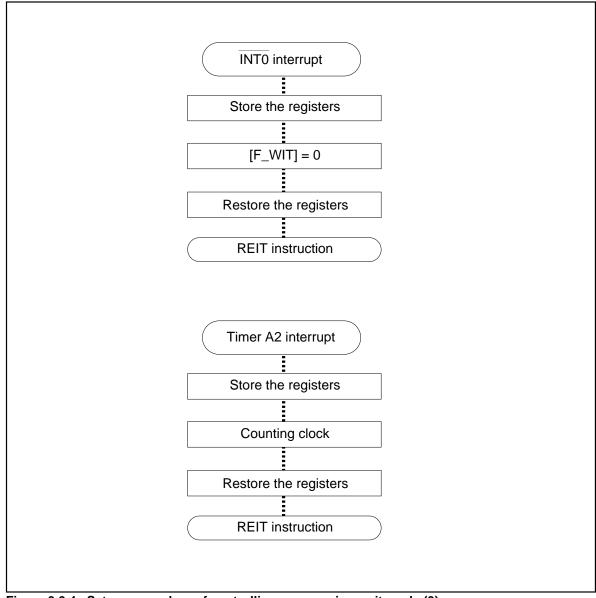

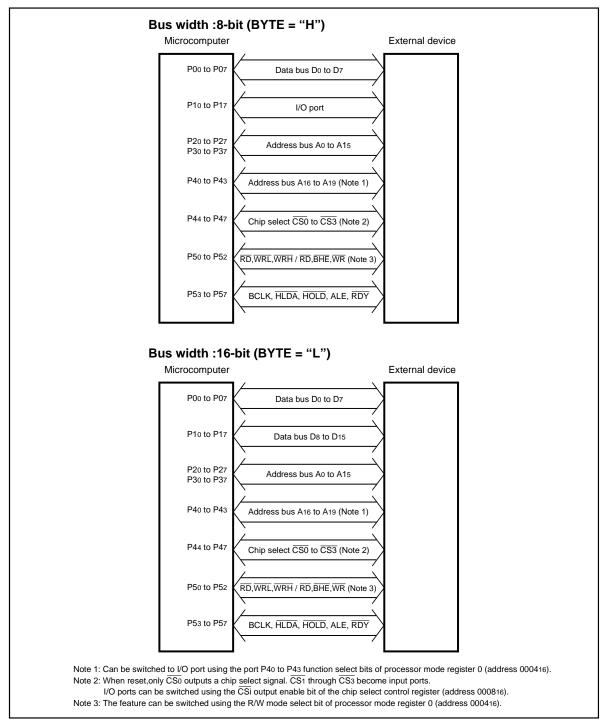

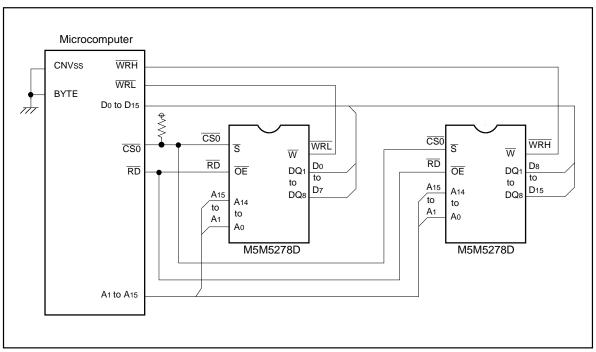

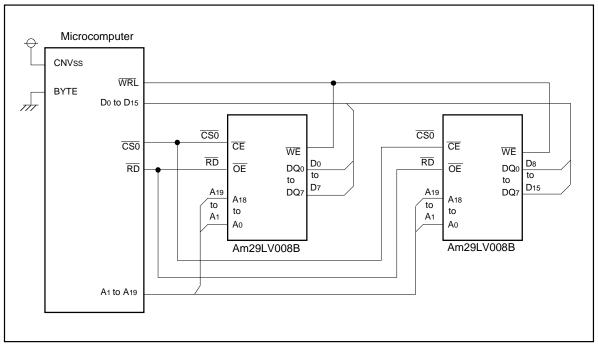

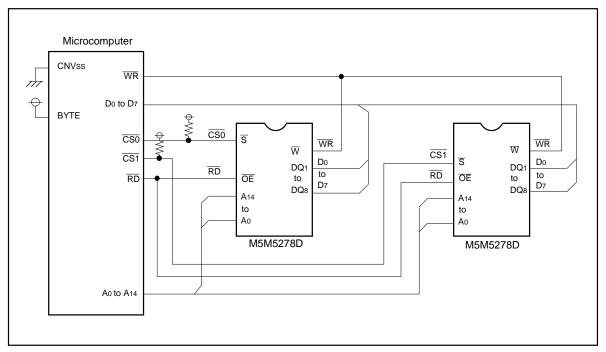

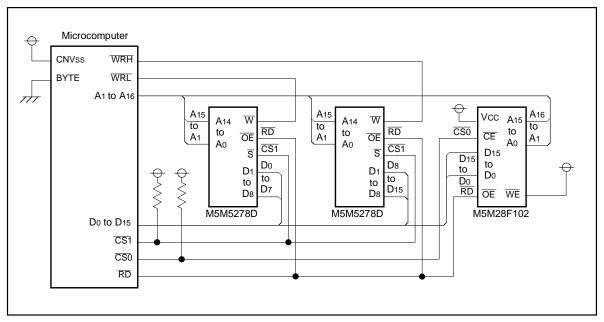

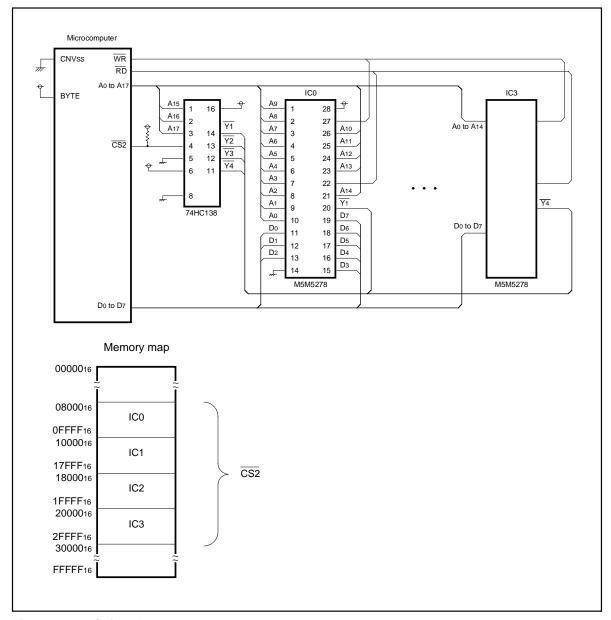

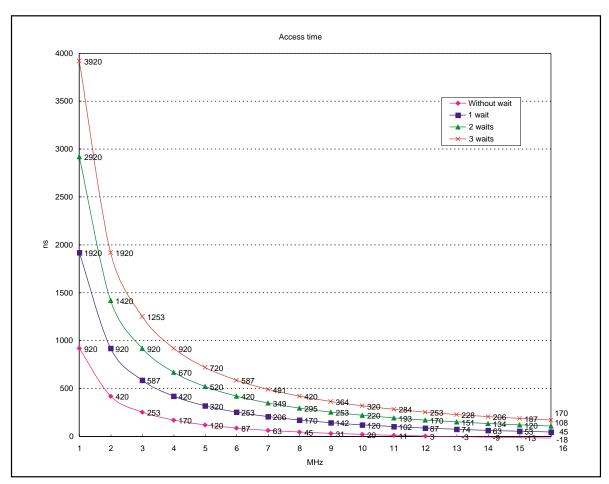

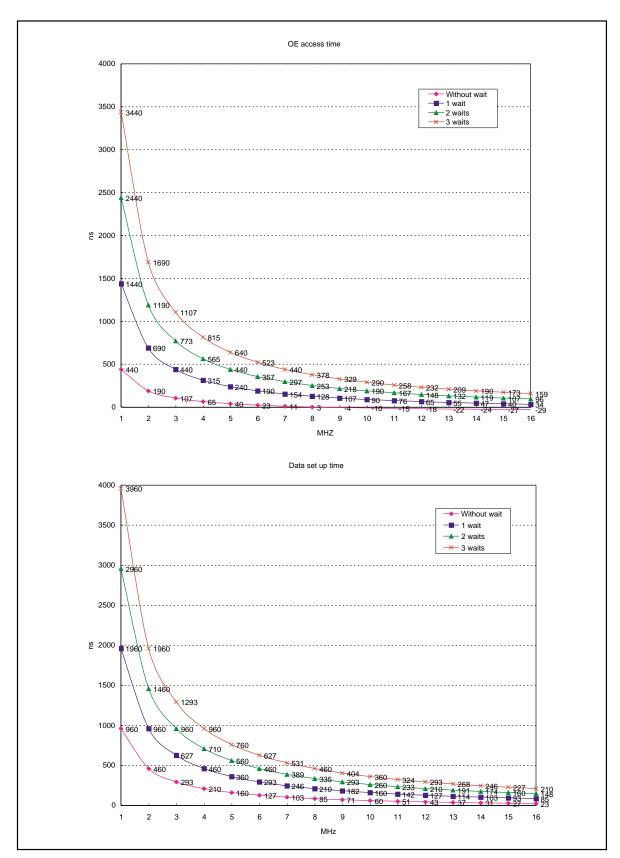

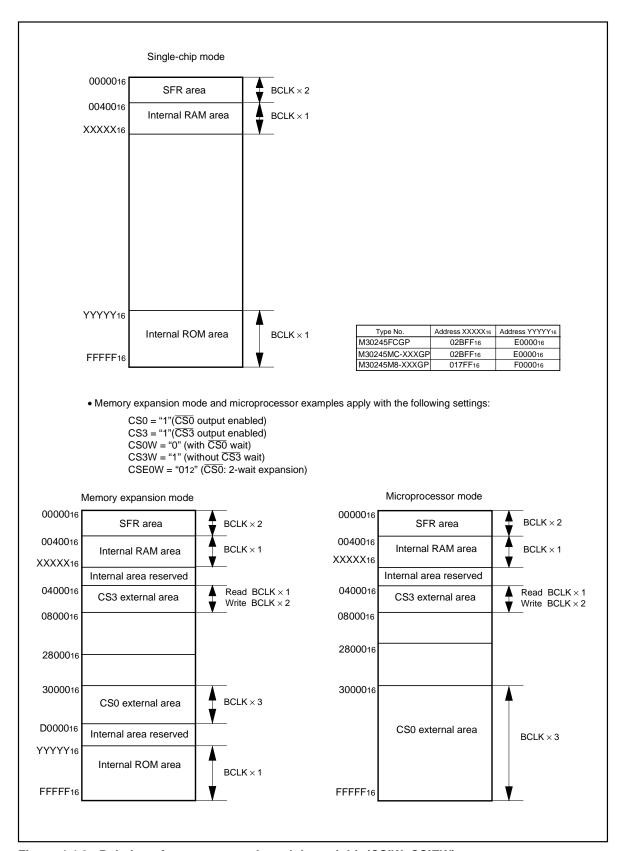

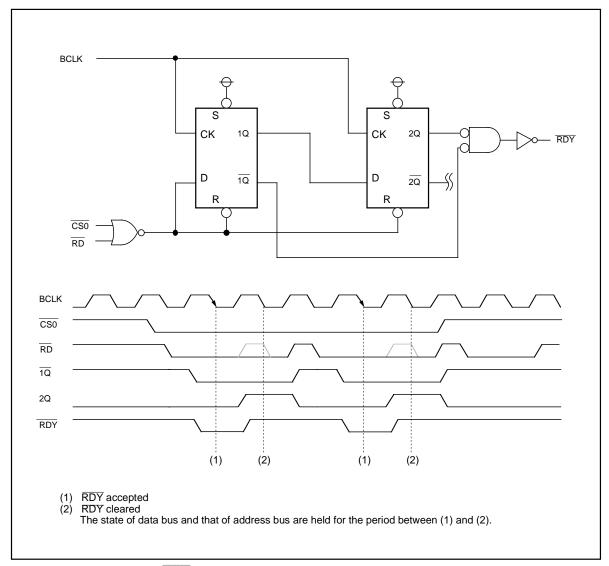

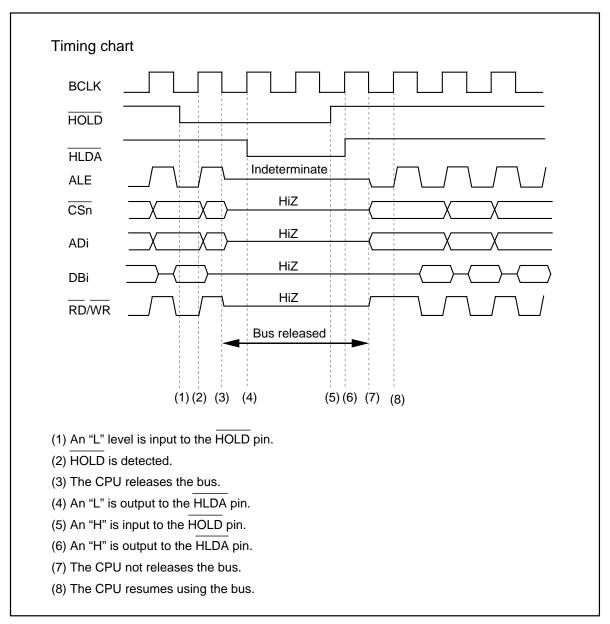

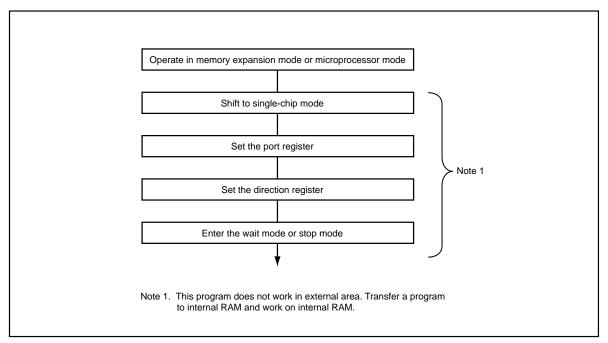

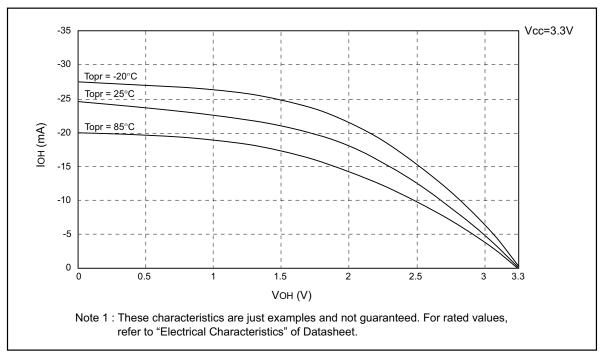

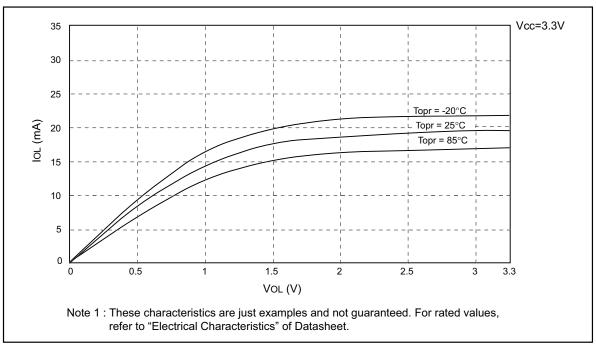

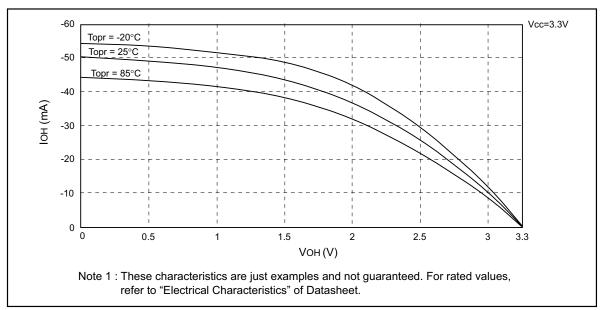

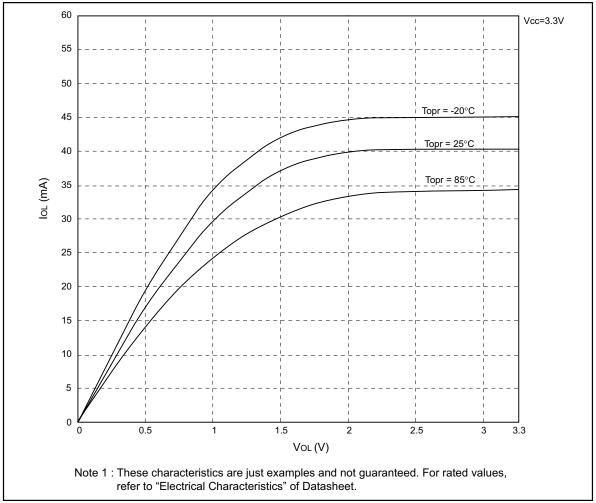

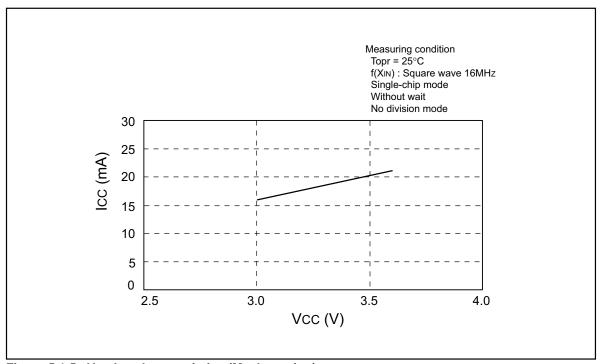

- (4) To receive data in succession, set dummy data in the lower-order byte of the UARTi transmit buffer register every time reception is made. In continuous receive mode, when the receive buffer is read out, the unit simultaneously goes to a receive enable state without having to set dummy data back to the transmit buffer register again.