**MSM6376**

O K I SEMICONDUCTOR GROUP

T-77-13

## ADPCM SPEECH SYNTHESIZER WITH EXTERNAL ROM

## **GENERAL DESCRIPTION**

MSM6376 is a two-channel mixing ADPCM speech synthesizer LSI using up to 16 M-bit external speech data storage, such as ROM, and EPROM. Since it has a built-in 12-bit DA converter and low pass filter, a speech data output system can easily be configured by connecting an external power amplifier and

speaker. MSM6376 is best suited to the evaluation of MSM6372, MSM6373, MSM6374, and MSM6375, which are used as speech synthesizer LSIs with built in ROM, because the MSM6376 has the same circuit configuration as those LSIs.

#### **FEATURES**

- External memory capacity 16 Mbits ROM

- · 4-bit straight ADPCM method

- Echo reproduction and simultaneous output of two audible tones (sound volume variation for one tone in three stages)

- Output of either of two built-in BEEP tones (1 Hz and 2 Hz) by designation code (when oscillation is 64 kHz)

- Sampling frequency 4.0, 6.4 and 8.0 kHz (at oscillation of 64 kHz) up to 32 kHz is possible.

- Maximum speech period of 10.9 minutes (at sampling frequency of 6.4 kHz) with 16 Mbits ROM

Maximum number of words:

111 words

- Built-in 12-bit D/A converter of class A voltage type (with built-in pop noise suppression circuit)

- Built-in LPF with attenuation factor of –

24 dB/oct (fcut to 3 x fcut)

Note) fcut=cutoff frequency

- Standby function to stop oscillation and all functions during the standby state

- Oscillation selectable between CR oscillation and crystal oscillation

- Master oscillation frequency:

64 to 128 kHz (LPF output)

64 to 256 kHz (DAC output)

- Supply voltage: 4.5 to 5.5V

- 64 pin-V1 plastic QFP (QFP64-P-1420-V1K)

ww.DataSheet4U.com

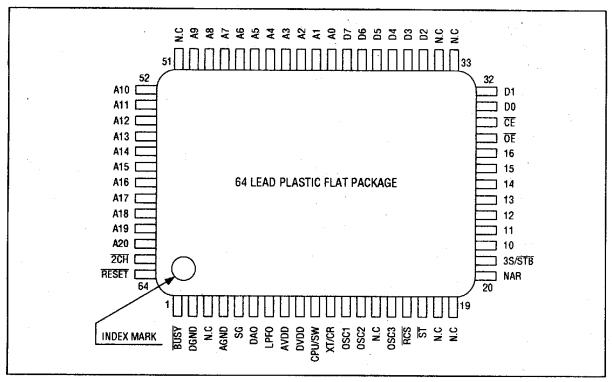

#### PIN CONFIGURATION (Top View)

#### O K I SEMICONDUCTOR GROUP

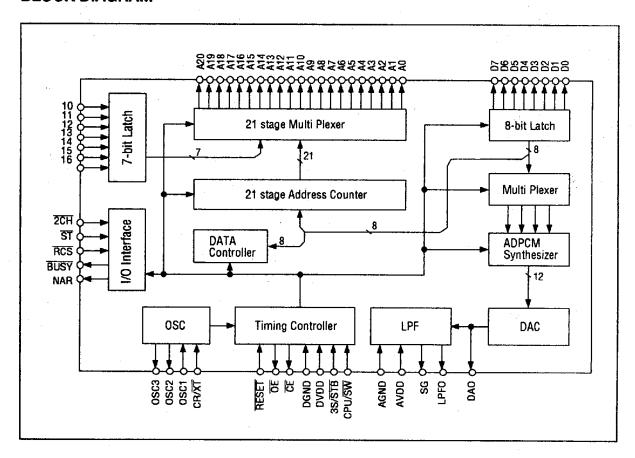

#### **BLOCK DIAGRAM**

## Absolute Maximum Ratings

## O K I SEMICONDUCTOR GROUP

(DGND = AGND = 0V)

| Parameter            | Symbol Conditions |           | Rating                      | Unit |  |

|----------------------|-------------------|-----------|-----------------------------|------|--|

| Power supply voltage | V <sub>DD</sub>   | T. 05°0   | -0.3 ~ +7.0                 | ٧    |  |

| Input voltage        | Vı                | Ta = 25°C | -0.3 ~ V <sub>DD</sub> +0.3 | ٧    |  |

| Storage temperature  | T <sub>stg</sub>  | <u> </u>  | <b>−55 ~ +150</b>           | °C   |  |

## • Operating Ranges

(DGND = AGND = 0V)

| Parameter             | Symbol          | Conditions | Range               | Unit |

|-----------------------|-----------------|------------|---------------------|------|

| Power supply voltage  | V <sub>DD</sub> | -          | 4.5 ~ +5.5          | . V  |

| Operating temperature | Topr            | _          | -40 ~ +85           | °C   |

| DAO output level      | V <sub>DD</sub> | No load    | 0 ~ V <sub>DD</sub> | ٧    |

## • DC Characteristics

$(DV_{DD} = AV_{DD} = 5V, DGND = AGND = 0V, Ta=-40-85^{\circ}C)$

| (- 55                           |                  |                                        |      |      |      |           |  |

|---------------------------------|------------------|----------------------------------------|------|------|------|-----------|--|

| Item                            | Symbol           | Conditions                             | Min. | Тур. | Max. | Unit<br>V |  |

| "H" input voltage               | ViH              | <del>-</del>                           | 4.2  |      | _    |           |  |

| "L" input voltage               | V <sub>IL</sub>  |                                        |      |      | 0.8  | ٧         |  |

| "H" output voltage              | VoH              | I <sub>OH</sub> = -40 μA               | 4.6  | _    |      | ٧         |  |

| "L" output voltage              | V <sub>OL</sub>  | l <sub>OL</sub> = 40 μA                | _    |      | 0.4  | V         |  |

| "H" input current               | lin              | V <sub>IH</sub> = V <sub>DD</sub>      |      | _    | 10   | μA        |  |

| "L" input current               | ելը              | V <sub>IL</sub> = 0V                   | -10  | _    | _    | μА        |  |

| Operating current consumption   | I <sub>DD1</sub> |                                        | _    | 4    | 10   | mΑ        |  |

| Output leak current             | ILO              | 0 ≤ V <sub>OUT</sub> ≤ V <sub>DD</sub> | -10  |      | 10   | μA        |  |

| Standby current consumption     | I <sub>DD2</sub> |                                        | _    | _    | 10   | μA        |  |

| Relative precision of DA output | VDAE             | no load                                | I —  | _    | 40   | m۷        |  |

| DA output impedance             | Ror              | <u> </u>                               | 15   | 25   | 35   | kΩ        |  |

| LPF load impedance              | RAOUT            | <del></del>                            | 50   |      |      | kΩ        |  |

O K I SEMICONDUCTOR GROUP

MSM6376

## • AC Characteristics ( $V_{DD} = 5V$ , $Ta = -40 \sim 85$ °C, $f_{OSC1} = 64$ kHz)

| Item                                                       | Symbol                              | Conditions                    | Min. | Тур. | Max.         | Unit |

|------------------------------------------------------------|-------------------------------------|-------------------------------|------|------|--------------|------|

| Master oscillation frequency                               | f <sub>(osc1)</sub>                 | . <u>—</u>                    | 40   | ·    | 256          | kHz  |

| Master oscillation duty cycle                              | f <sub>duty</sub>                   | ·                             | 40   | 50   | 60           | %    |

| RESET input pulse width                                    | tw(RST)                             |                               | 10   | -    | -            | μS   |

| ST input pulse width (Note 1)                              | tw(ST)                              | * CPU interface               | 0.35 | -    | 350          | μS   |

| 2CH input pulse width                                      | tw(2CH)                             |                               | 0.35 | _    | _            | μS   |

| ST-ST pulse interval                                       | tss                                 | <del></del> .                 | 0.35 | _    | -            | μS   |

| 2CH setup time                                             | tchs                                | _                             | 0.35 | _    | -            | μS   |

| 2CH hold time                                              | tscн                                |                               | 0.35 | -    |              | μS   |

| Data set time                                              | tow                                 |                               | 10   | -    | -            | μS   |

| Data hold time                                             | two                                 | <del>-</del>                  | 10   | +    | -            | μS   |

| RCS setup time                                             | tcs                                 |                               | 10   | -    |              | μS   |

| RCS hold time                                              | tac                                 |                               | 10   | _    | _            | μS   |

|                                                            | fs1                                 | f <sub>(osc1)</sub> /8        | -    | 8.0  |              | kHz  |

| Selectable sampling frequency                              | f <sub>S2</sub>                     | f <sub>(osc1)</sub> /10       | -    | 6.4  | _            | kHz  |

|                                                            | f <sub>S3</sub>                     | f <sub>(osc1)</sub> /16       | _    | 4.0  | -            | kHz  |

| BUSY output time (1)                                       | tsas                                | <del>-</del> :                | _    |      | 10           | μS   |

| BUSY output time (2) (Note 2)                              | t <sub>BN</sub>                     | At f <sub>s</sub> = 8 kHz     | 350  | 375  | 400          | μS   |

| BUSY output time (3) (Note 5)                              | tBF                                 | At master<br>frequency=64 kHz |      | -    | 64           | mS   |

| NAR output time (1)                                        | tsns                                |                               | -    | _    | 10           | μS   |

| NAR output time (2) (Note 2)                               | tnaa                                | At f <sub>s</sub> =8 kHz      | 350  | 375  | 400          | μS   |

| NAR output time (3) (Note 2)                               | tnab                                | At f <sub>s</sub> =8 kHz      | 350  | 375  | 400          | μS   |

| NAR output time (4) (Note 2)                               | tnac                                | At f <sub>s</sub> =8 kHz      | 350  | -    | 550          | . μS |

| D/A converter transition time (Note 3)                     | t <sub>DAR</sub> , t <sub>DAF</sub> | At master<br>frequency=64 kHz | 60   | 64   | 68           | , mS |

| LPF stabilizing time (Note 4)                              | , t <sub>L</sub>                    | At master<br>frequency=64 kHz | 12   | 16   | 20           | mS   |

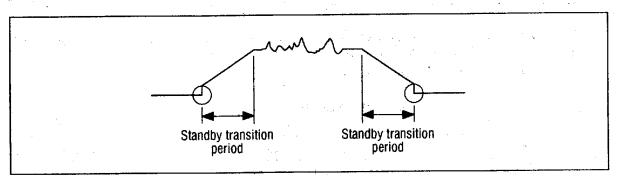

| Standby transition time (Note 3) (at end of speech output) | t <sub>STB</sub>                    | At master<br>frequency=64 kHz | 2.9  | 3.0  | 3.1          | mS   |

| ST - 2CH pulse interval                                    | ts2CH                               | At master<br>frequency=64 kHz | 1.0  | _    | -            | mS   |

| ST input wait time                                         | tns                                 | <del>_</del>                  | 10   | -    | <del>-</del> | μS   |

|                                                            |                                     |                               |      |      | L            |      |

**Note 1:** The MAX value is proportional to fs.

Note 2: The duration is proportional to fs.

Note 3: The duration is proportional to fosc.

$\textbf{Note 4:} \ \, \textbf{Applicable at the start of oscillation}.$

Note 5: When playback occurs during the standby transition period (tDAF).

## O K I SEMICONDUCTOR GROUP

## AC Characteristics (V<sub>DD</sub> = 5V, Ta = -40 ~ 85°C, f<sub>OSC1</sub> = 40 - 256 kHz)

| Item                           | Symbol                              | Conditions    | Min.         | Тур.                   | Max.  | Unit |

|--------------------------------|-------------------------------------|---------------|--------------|------------------------|-------|------|

| Master oscillation frequency   | f <sub>(osc1)</sub>                 | <u> </u>      | 40           |                        | 256   | kHz  |

| Master oscillation duty cycle  | f <sub>duty</sub>                   | <del></del>   | 40           | 50                     | 60    | %    |

| RESET input pulse width        | tw(RST)                             | -             | 10           |                        |       | μS   |

| ST input pulse width           | tw(s⊤)                              | CPU interface | 0.35         | <u>-</u>               | a     | μS   |

| 2CH input pulse width          | tw( <del>2CH</del> )                |               | 0.35         | _                      |       | μS   |

| ST-ST pulse interval           | t <sub>SS</sub>                     | · — `         | 0.35         | _                      | . –   | μS   |

| 2CH setup time                 | tchs                                |               | 0.35         | _                      |       | μS   |

| 2CH hold time                  | tscн                                | -             | 0.35         | _                      |       | μS   |

| Data set time                  | tow                                 |               | 10           | 1                      |       | μS   |

| Data hold time                 | t <sub>WD</sub>                     | <del>-</del>  | 10           | -                      | _     | μS   |

| RCS setup time                 | tcs                                 |               | 10           | <del>-</del> .         | _     | μS   |

| RCS hold time                  | t <sub>BC</sub>                     | _             | - 10         | <u>-</u>               |       | μS   |

|                                | f <sub>S1</sub>                     |               | -            | f <sub>(osc)</sub> /8  | _     | kHz  |

| Selectable sampling frequency  | f <sub>S2</sub>                     |               | _            | f <sub>(osc)</sub> /10 |       | kHz  |

|                                | f <sub>S3</sub>                     |               | -            | f <sub>(osc)</sub> /16 |       | kHz  |

| BUSY output time (1)           | tsas                                | <u>—</u>      | -            | _                      | 10    | μS   |

| BUSY output time (2)           | t <sub>BN</sub>                     |               | a            | b                      | С     | μS   |

| BUSY output time (3) (Notes 2) | t <sub>BF</sub>                     |               |              |                        | e     | mS   |

| NAR output time (1)            | tsns                                | <del></del>   | <del>-</del> | -                      | 10    | μŞ   |

| NAR output time (2)            | tnaa                                |               | a            | b                      | С     | μS   |

| NAR output time (3)            | t <sub>NAB</sub>                    | <u></u>       | a            | b                      | С     | μS   |

| NAR output time (4)            | tnac                                |               | a            | -                      | d     | μS   |

| D/A converter transition time  | t <sub>dar</sub> , t <sub>daf</sub> |               | e-4          | е                      | e+4   | mS   |

| LPF stabilizing time (Note 1)  | tլ                                  |               | f-4          | f                      | f+4   | mS   |

| Standby transition time        |                                     |               | 0.01         |                        | g+0.1 | mS   |

| (at end of speech output)      | tsta                                |               | g-0.1        | g                      | y+v.1 | 1113 |

| ST-2CH pulse interval          | t <sub>S2CH</sub>                   | _             | h            | _                      | _     | mS   |

| ST input wait time             | t <sub>NS</sub>                     | _             | 10           | _                      | _     | μS   |

$$a = 350 \times \frac{8 \text{ (kHz)}}{f_S \text{ (kHz)}} \qquad b = 375 \times \frac{8 \text{ (kHz)}}{f_S \text{ (kHz)}} \qquad c = 400 \times \frac{8 \text{ (kHz)}}{f_S \text{ (kHz)}} \qquad d = 550 \times \frac{8 \text{ (kHz)}}{f_S \text{ (kHz)}}$$

$$e = 64 \times \frac{64 \text{ (kHz)}}{f_{OSC} \text{ (kHz)}} \qquad f = 16 \times \frac{64 \text{ (kHz)}}{f_{OSC} \text{ (kHz)}} \qquad g = 3.0 \times \frac{64 \text{ (kHz)}}{f_{OSC} \text{ (kHz)}} \qquad h = 1.0 \times \frac{64 \text{ (kHz)}}{f_{OSC} \text{ (kHz)}}$$

Note 1: Applicable at the start of oscillation.

Note 2: When playback occurs during the standby transition period (tDAF).

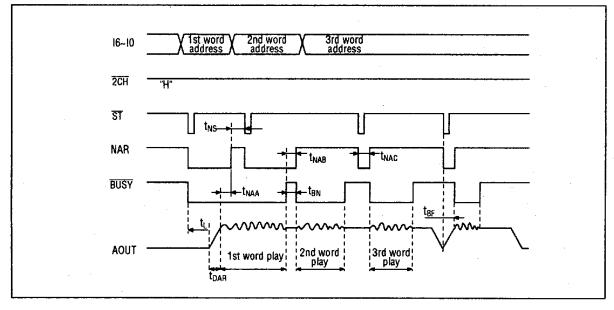

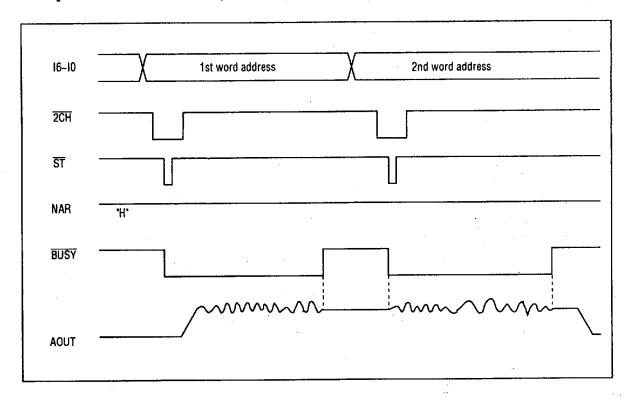

### **TIMING DIAGRAMS**

# O K I SEMICONDUCTOR GROUP

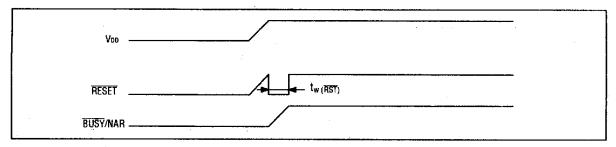

## 1. At power-on

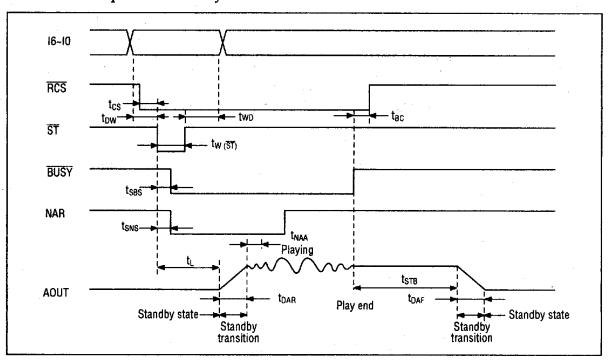

## 2. At LSI startup and in standby state

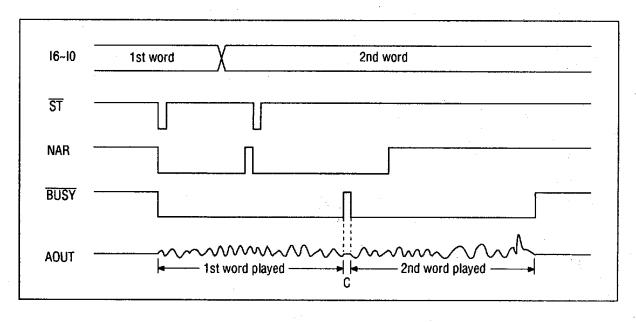

## 3. Operation in channel 1 only (CPU input interface)

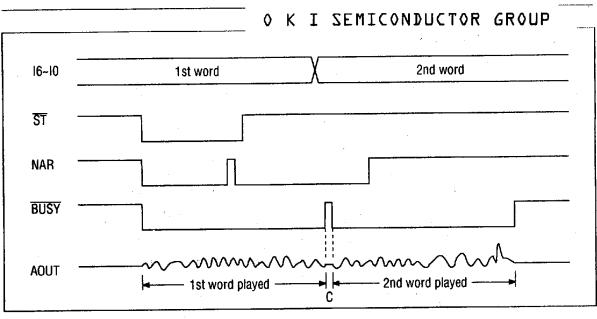

## 4. Operation in channel 2 only (CPU input interface)

#### O K I SEMICONDUCTOR GROUP

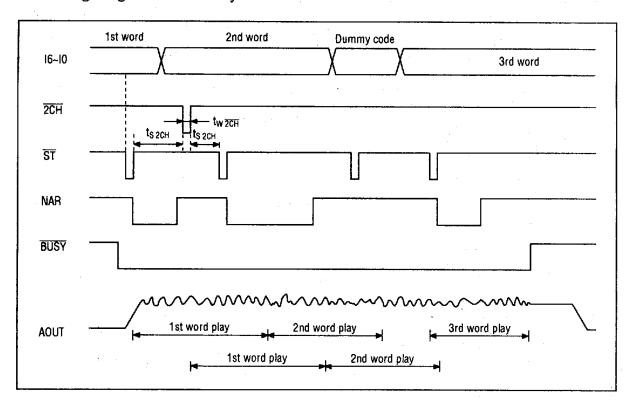

#### 5. Timing Diagram of Echo Playback in Channel 1

- 1. Input of the 2CH pulse without lowering ST starts echo playback. Echo playback is canceled unless play is continuous.

- At echo playback, the waveform is a combination of the playback of channel 1 by the ST pulse and a-6 DB playback of channel 2 by the 2CH pulse.

- 3. In continuous play, the echo is applied to the next word (continuous play means playback of another word during a single word vocalization.)

- 4. Input unused code as a dummy code from the user selectable code at the end of echo playback. Without this input, the LSI may enter the standby mode without waiting for the 3 seconds after the end of playback when the standby option is selected.

## O K I SEMICONDUCTOR GROUP

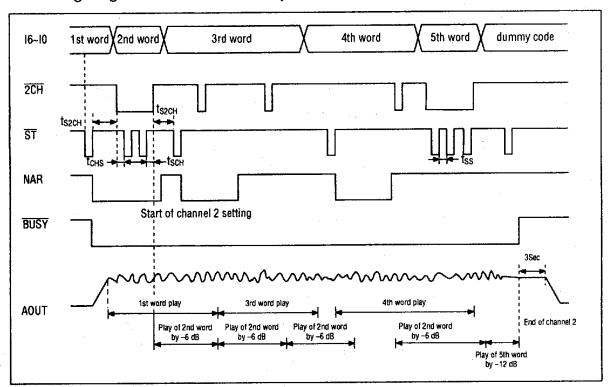

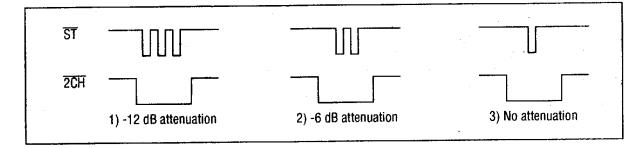

## 6. Timing Diagram of Simultaneous Playback in Channel 1 and Channel 2

- 1. Channel 2 starts playing when the ST pulse is input and 2CH="L". The sounds volume can be changed by the number of the ST pulses using the table below.

- 2 Channel 2 plays a pre-set word each time the 2CH pulse is input with the same sound volume until the LSI goes to the standby state or until channel 2 is reset.

- 3 Please input an unused code as a dummy code from the user selectable codes at the end of playback of channel 2. Without this input, the LSI may enter the standby mode without waiting for the 3 seconds after the end of play when the standby option is selected.

**OKI** Semiconductor

| Number of ST pulses | Attenuation       |

|---------------------|-------------------|

| 1                   | No attenuation    |

| 2                   | -6dB attenuation  |

| 3                   | -12dB attenuation |

## **PIN FUNCTIONS**

## O K I SEMICONDUCTOR GROUP

| Pin name | Input/output | Function                                                                                                      |

|----------|--------------|---------------------------------------------------------------------------------------------------------------|

| 16-10    | Input        | Selects and enters a user-specified word corresponding to the                                                 |

|          | ·            | vocalized word.                                                                                               |

|          |              | The code when the level of the ST pulse goes low is read, and                                                 |

|          |              | latched as the level rises.                                                                                   |

| A0-A20   | Output       | These are the address terminals for the external connection of memory                                         |

|          |              | The data is output when $\overline{RCS}$ is "L".                                                              |

| D0-D7    | Input        | These are the terminals to input the data from external memory.                                               |

|          |              | The data is input when RCS is "L".                                                                            |

| 2CH      | Input        | Reproduces echo, or reproduces two different tones simultaneously.                                            |

|          | 1            | If $\overline{2CH}$ pulse is entered during operation in channel 1, echo is                                   |

| •        |              | reproduced. Delay time for the echo can be changed according to                                               |

|          |              | the time of input of <del>2CH</del> pulse.                                                                    |

|          |              | If ST pulse is entered when the level for CH2 is low, reproduction                                            |

|          |              | is performed in channel 2.                                                                                    |

| ST       | Input        | Activated at the fall of ST. Data on 16 through 10 is read when their                                         |

|          |              | level is "L", and latched at the rise of $\overline{ST}$ .                                                    |

|          |              | Enter an address for channel 1 when the level of NAR is "H". For                                              |

|          |              | reproduction in channel 2, sound volume can be changed according to                                           |

|          |              | the number of ST pulses when the level of 2CH is "L".                                                         |

|          |              | In the case of SW input interface, synthesis is repeated while the level                                      |

|          |              | of ST is set to "L".                                                                                          |

| RCS      | Input        | When the level is "L", this terminal enables ST pulse to be input and                                         |

|          |              | the address from A0-A20, $\overline{\text{OE}}$ and $\overline{\text{CE}}$ are output.                        |

|          | 1            | When the level is "H", the address terminals of A0-A20, and $\overline{\text{CE}}$ and $\overline{\text{OE}}$ |

|          |              | become high impedance.                                                                                        |

| BUSY     | Output       | During playback, "L" level is output.                                                                         |

| NAR      | Output       | When the level is "H", the next channel address can be input.                                                 |

| CR/XT    | Input        | Selects CR oscillation or crystal oscillation. If the level of CR/XT is                                       |

|          |              | set to "H", OSC1, OSC2, and OSC3 work as CR oscillation terminals;                                            |

|          |              | if the level of CR/XT is set to "L", OSC1 and OSC2 work as crystal                                            |

|          |              | oscillation terminals, and a resistor with a resistance of about                                              |

|          |              | 2 M-ohms is inserted between OSC1 and OSC2.                                                                   |

## O K I SEMICONDUCTOR GROUP

| Pin name | Input/output                          | Function                                                                       |

|----------|---------------------------------------|--------------------------------------------------------------------------------|

| OSC1     | Input                                 | Crystal oscillation and CR oscillaito terminals.                               |

| OSC2     | Output                                | To use them for crystal oscillation, leave the OSC3 terminal open.             |

| OSC3     | Output                                | If an external clock signal is to be used, it should be connected to           |

|          |                                       | the OSC1 terminal with OSC2 and OSC3 left open.                                |

| CPU/SW   | Input                                 | Terminal for selection between CPU interface and SW input interface.           |

|          | ļ                                     | "H" level = CPU interface.                                                     |

|          |                                       | "L" level = switch interface                                                   |

|          |                                       | Note: If SW input interface is selected, echo reproduction, and                |

|          |                                       | 2-channel mixing reproduction cannot be performed.                             |

| 3S/STB   | Input                                 | If the level of the 3S terminals is "H", standby state is invoked three        |

| ·        |                                       | seconds after completion of speech synthesis.                                  |

| * .e.    |                                       | If the level of the 3S terminals is "L", the output from the DA converter      |

|          | ÷                                     | remains at 1/2 VDD after completion of speech synthesis.                       |

| RESET    | Input                                 | If the level of this terminals is set to "L", the LSI is put in standby state. |

|          | ·                                     | Upon RESET, oscillation is stopped, the output from the DA converter           |

|          |                                       | is grounded, and put to the initial state.                                     |

|          |                                       | The M6376 has a built-in power-on reset circuit. To make the power-            |

|          |                                       | on resetting function reliably, raise the power supply within 1msec. If        |

|          | 1                                     | this is impossible to do, enter the RESET pulse when the power                 |

|          |                                       | is turned on.                                                                  |

| CE       | Output                                | A timing output terminal that controls chip enable of external memory          |

|          |                                       | The signal is output when the level of RCS is "L".                             |

| ŌĒ       | Output                                | A timing output terminal that controls reading from external memory.           |

|          |                                       | The signal is output when the level of RCS is "L".                             |

| DAO      | Output                                | A terminal that outputs analog voice sent from the DA converter.               |

| AOUT     | Output                                | A terminal for output of analog voice sent from the LPF.                       |

| SG       | Output                                | A terminal that improves SN ratio of LPF.                                      |

|          | ·                                     | To utilize the outpur from the LPF, connect a capacitor of about 1µF.          |

| AVDD     |                                       | An analog power supply terminal.                                               |

| AGND     |                                       | An analog grounding terminal.                                                  |

| DVDD     |                                       | A digital power supply terminal.                                               |

|          | · · · · · · · · · · · · · · · · · · · | A digital grounding terminal.                                                  |

#### **FUNCTION DESCRIPTION**

## O K I SEMICONDUCTOR GROUP

#### 1. Voice Code Selection

mum 111 words/phrases. The setting of I0-I6 is as follows:

User selectable words (phrases) are maxi-

Table 1 List of User Selected Words

| 10-16      | Code explanation                 |

|------------|----------------------------------|

| 000000     | STOP code                        |

| 0000001    |                                  |

| 2          | User selectable code (111 words) |

| 1101111    |                                  |

| 1110000    |                                  |

| <b>t</b> . | BEEP code                        |

| 1110111    |                                  |

| 1111000    |                                  |

| 1          | Test codes (do not use)          |

| 1111111    |                                  |

## 2. CPU Interface and Switch Input Interface

The CPU interface and the switch input interface can be selected by the  $CPU/\overline{SW}$  pin. When the CPU pin is high, the CPU interface is on. When the CPU pin is low, the switch input interface is on.

#### 2-1 CPU interface

If the CPU interface is selected, the ST pulse becomes valid when the NAR pin is "H". User selected words are then fetched internally and vocalized. This interface is effective for playback of several words continuously. Please note that when the ST pulse is

Figure 1 Timing of CPU Interface ( $\overline{ST} \le 350 \mu S$ )

Figure 2 Timing of CPU Interface ( $\overline{ST} > 800 \mu S$ )

kept at the "L" level for longer than  $800 \,\mu\text{S}$ , one word is played twice (at 8 kHz sampling).

When the  $\overline{ST}$  pulse width is between 350  $\mu S$  and 800  $\mu S$ , a single word is played once or twice. However, when the  $\overline{ST}$  pulse is input from the standby state, a single word is played only once if within 80 $\mu S$ .

When a  $\overline{ST}$  pulse width of longer than 350µS (master frequency is 64 kHz) is input and the  $\overline{BUSY}$  option has been selected, make sure

the  $\overline{ST}$  pulse is within 800  $\mu$ S after the rise of  $\overline{BUSY}$  pin.

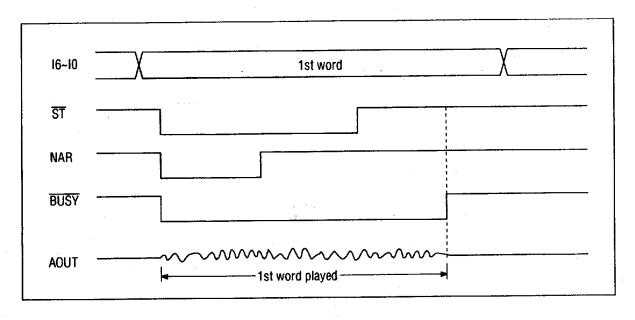

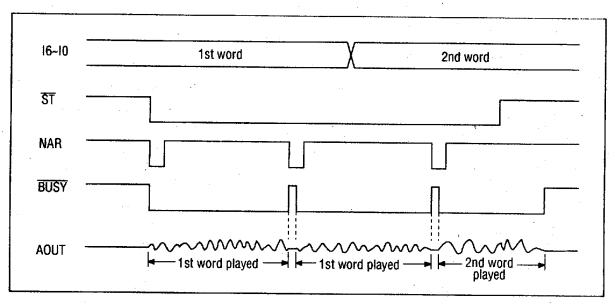

#### 2-2 SW input interface

If the SW input interface is selected, the specified word is played repeatedly when ST is "L" at the end of play of the specified word and is finished when it is "H".

For example, when this LSI is operated using a push switch, the same word is played repeatedly as long as the switch is pressed

Figure 3 Timing of SW Input Interface (playing one word)

and when the switch is released, playback stops when the currently playing word is finished.

When playing different words continuously, change the code of I0-I6 and maintain  $\overline{ST}$  at

O K I SEMICONDUCTOR GROUP the "L" level before the play back is completed.

However, note that the playing interrupted if the input level of I6-I0 becomes "L" instantly when switching the address.

Figure 4 Timing of SW Input Interface (repeated play)

In SW input interface, playback of the 1st and 2nd channels simultaneously is not pos-

sible. Neither 2 channel mixing nor echo playback is possible in this interface.

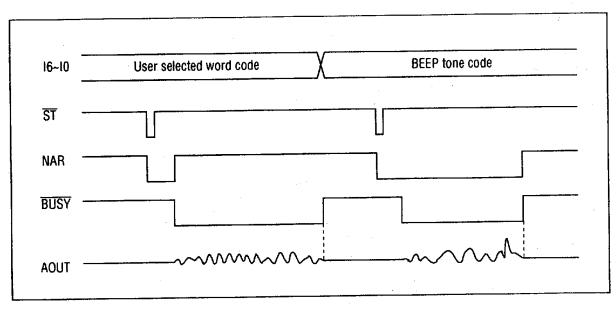

#### 3. BEEP Tone Generation

Since this LSI has an on-chip circuit to generate BEEP tones, the BEEP tones are selected using I6-I0. Depending on the word code, the frequency and duration can be changed. The amplitude is approximately  $1/4\ V_{DD}$ .

The NAR/BUSY pin outputs a "L" level

## O K I SEMICONDUCTOR GROUP

during BEEP tone play regardless of either NAR or /BUSY is selected as the option. Figure 5 shows such timing.

Neither the STOP code (explained later) nor 2 channel playback is valid during the playback of BEEP tone, The following table shows the relationship between the BEEP tones and addresses when the oscillation frequency is 64 kHz.

| Table 2 F | Relationship be | etween BEEP | I ones and Au | dresses |

|-----------|-----------------|-------------|---------------|---------|

| 1. 1      | T.T.            |             | 0             |         |

| 16 | 15 | 14 | 13 | 12 | 11 | 10 | BEEP tone | Generating duration |

|----|----|----|----|----|----|----|-----------|---------------------|

|    |    |    |    |    |    |    | frequency | (sec)               |

|    |    |    | •  |    | 0  | 0  |           | 0.064               |

|    |    |    |    |    | 0  | 1  |           | 0.125               |

|    |    |    |    | 0  | 1  | 0  | 2.0       | 0.250               |

|    |    |    |    |    | 1  | 1  |           | 0.500               |

| 1  | 1  | 1  | 0  |    | 0  | 0  |           | 0.064               |

|    |    |    |    |    | 0  | 1  |           | 0.125               |

|    | '  |    |    | 1  | 1  | 0  | 1.0       | 0.250               |

|    |    |    |    |    | 1  |    | · <b></b> | 0.500               |

When the code for BEEP tone is input while playing either the 1st channel or the 2nd channel, the BEEP tone is generated after the

completion of play. The reverse case also holds true.

Figure 5 Timing at BEEP Tone Generation

## OK I SEMICONDUCTOR GROUP

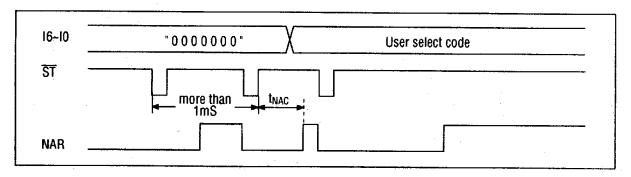

#### 4. Stop Code

Speech playing is finished when the  $\overline{ST}$  pulse is input by setting I6-I7 to "0000000" during play. The DA converter becomes 1/2  $V_{DD}$ .

The input method of the ST pulse is subject to the AC characteristics when the NAR output is "H". When the NAR output is at the "L" level, the STOP code is valid by

setting the  $\overline{ST}$  pulse to the "L" level longer than 1 msec ( $f_{osc}$ =64 kHz) or by the timing shown in Figure 6.

The STOP code is not valid during the generation of BEEP tone. When the STOP code is input, only playback is stopped while the oscillation and the analog circuitry are still operating. When the RESET pulse is input, all operations are halted.

Figure 6 Example of STOP Code Input Timing

### 5. Sampling Frequencies

Sampling frequencies can be specified for each word in the speech data of the built-in ROM. When the 1st and the 2nd channels are simultaneously played back, the sampling frequency of the 1st channel has priority.

Three types of sampling frequencies can be selected during speech data analysis. The relationship between the master frequency,  $f_{OSC}$ , and the sampling frequency,  $f_{S}$ , is as follows:

| Selection 1 | $f_{s1} = fose/8$      |

|-------------|------------------------|

| Selection 2 | $f_{s2}^{n}$ =fose/10  |

| Selection 3 | $f_{cs}^{32}$ =fose/16 |

## 6. Echo Playback and Channel 2 Playback

By using the  $\overline{2CH}$  input, echo or 2 channel playback is possible. Because both echo and 2 channel playback use the  $\overline{2CH}$  pin, switch between modes by returning the LSI to the standby state.

This function is not available in the SW input interface or during generation of BEEP tones.

#### 6-1 Echo Playback

Echo playback is performed by combining a speech waveform of the 1st channel with a delayed speech waveform with -6 dB attenuation (half the amplitude of the channel 1 speech waveform).

The echo delay time is the time until the 2CH pulse is input from the start of play of channel 1.

However, when starting this operation from the standby state, pop noise suppression time is not counted as delay time.

In echo playback, echo is applied to all the words during continuous play of channel 1 (continuous play means playback of the next word during playback.)

## 6-2 Channel Mixing Playback

Using 2 channel mixing playback, a different word can be played during the play of channel 1. This has a wide range of application such as BGM (back ground music) and combinations of instruments. Speech data on channel 2 can remain the same while the sound volume may be changed to 1, 1/2 and 1/4 according to channel 1. The change in

of ST pulses when starting the 2nd channel.

**OKI** Semiconductor

sound volume is determined by the number

Table 3 Number of ST Pulses and Attenuation

| Number of ST pulses | Attenuation                            |  |

|---------------------|----------------------------------------|--|

| . 1                 | No attenuation (100% of speech data)   |  |

| 2                   | -6dB attenuation (1/2 of speech data)  |  |

| 3                   | -12dB attenuation (1/4 of speech data) |  |

Figure 7 Input Timing of 2 Channel Mixing

Once 2 channel mixing is set, it is maintained until the standby state or until channel 2 is reset. Because of this, restart can be accomplished by the input of the 2CH pulse only.

### 7. Standby Transition

When standby transition is enabled as an option, the LSI changes to the standby state and halts all operations unless another word is played within 3 seconds of the completion of playback of a single word. For this reason, it takes approximately 100 mS before the next playback is started as the LSI needs to activate the pop noise suppression circuitry.

When standby transition is disabled as an option, the LSI does not go into the standby mode even when playback is completed. At this time, the output from AOUT is approximately  $1/2~V_{DD}$  and the LSI still draws current as oscillation is continued. When restarted, the next playback begins after approximately 350  $\mu$ s.

If disabling standby transition as an option, the RESET pulse must be input to set to the

standby state. Pop noise may be generated at the input of the RESET pulse as the output level from AOUT becomes GND level instantly.

### 8. Voice Input

The voice output pin can be selected by the output of the DA converter either directly or through the built-in low-pass filter.

## 8-1 Output Waveform of DA Converter

The output amplitude from the DA converter is maximum  $4095/4096 \times V_{DD}$  of a square wave that synchronizes with a sampling frequency. When selecting the DA output, addition of an external low-pass filter is highly recommended.

Because the output impedance of DAO varies between  $15 \mathrm{K}\Omega$  and  $35 \mathrm{K}\Omega$ , determine the filter constant so that the resistance variation does not influence the cut-off frequency of the low-pass filter.

Table 4 shows the output level from the AOUT pin when selecting an optional DA output.

## O K I SEMICONDUCTOR GROUP

## **Table 4 Output Level from DA Converter**

| Condition          | Minimum level       | Center level           | Maximum level       | Unit |

|--------------------|---------------------|------------------------|---------------------|------|

| 1 channel playback | 1/4 V <sub>DD</sub> | $\frac{1}{2}V_{DD}$    | 3 V <sub>DD</sub>   | v    |

| 2 channel mixing   | 0.0                 | 1/2 V <sub>DD</sub>    | V <sub>DD</sub>     | V    |

| BEEP tone playback | 3 V <sub>DD</sub>   | $\frac{1}{2}$ $V_{DD}$ | $\frac{3}{8}V_{DD}$ | V.   |

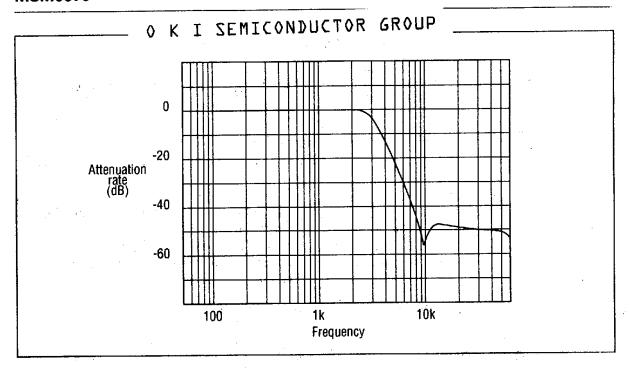

#### 8-2 Low-pass filter output

Since the low-pass filter is composed of switch capacitors, the cut-off frequency varies proportional to the master clock frequency. When the sampling frequency ( $f_s$ ) is 1/8 and 1/10 of the master clock frequency, the cutoff frequency,  $f_{cut}$ , is  $f_{cut}$ =3/64  $f_{osc}$  and is  $f_{cut}$ =3/128 when  $f_s$  is 1/16. Table 5 shows the relationship between the sampling frequencies and the cut-off frequencies.

Table 5 Cut-off Frequency of Low-pass Filter

| Sampling frequency | Master clock frequency | Cut-off frequency<br>(f <sub>cut</sub> ) |  |

|--------------------|------------------------|------------------------------------------|--|

| (f <sub>s</sub> )  | (fosc)                 |                                          |  |

| 4.0 kHz            | 64 kHz                 | 1.5 kHz                                  |  |

| 6.4 kHz            | 64 kHz                 | 3.0 kHz                                  |  |

| 8.0 kHz            | 64 kHz                 | 3.0 kHz                                  |  |

| 12.8 kHz           | 128 kHz                | 6.0 kHz                                  |  |

| 16.0 kHz           | 128 kHz                | 6.0 kHz                                  |  |

The low-pass filter characteristics when the sampling frequency is 8 kHz are shown in figure 8. Table 6 shows the output level

from AOUT when selecting the low-pass filter option.

Table 6 Output Level of Low-pass Filter

| Condition          | Minimum level       | Center level        | Maximum level                 | Unit |

|--------------------|---------------------|---------------------|-------------------------------|------|

| 1 channel playback | $\frac{1}{4}V_{DD}$ | $\frac{1}{2}V_{DD}$ | $\frac{3}{4}$ V <sub>DD</sub> | ٧    |

| 2 channel mixing   | 0.7                 | $\frac{1}{2}V_{DD}$ | V <sub>DD</sub> -0.7          | ٧    |

| BEEP tone playback | 3/8 V <sub>DD</sub> | ½ V <sub>DD</sub>   | 3 V <sub>DD</sub>             | ٧    |

Figure 8 Low-pass Filter Characteristics (f<sub>s</sub>=8 kHz)

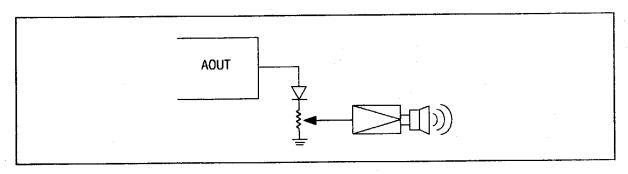

## 8-3 Pop Noise of Low-Pass Filter Output

Although this LSI has a built-in pop noise suppression circuit, the voltage of the circled portion in the figure below may be changed

abruptly by approximately 0.7V when selecting the low-pass filter output and may generate a "pop" sound.

Figure 9 Pop Noise of Low-pass Filter Output

When connecting a diode at the output from AOUT, the "pop" sound can be reduced.

Figure 10 shows the circuit.

Figure 10 Pop Noise Suppression Circuit

## O K I SEMICONDUCTOR GROUP

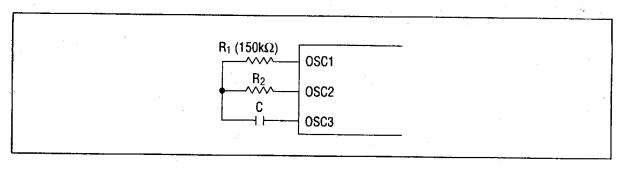

9. RC Oscillation

The external circuit diagram for RC oscillation is shown below:

Figure 11 RC Oscillation Connection Circuit

#### 9-1 Determination of RC Constant

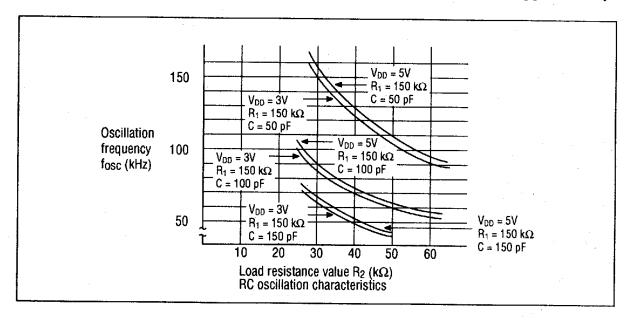

The RC oscillation frequency characteristics are shown in Figure 12. If  $f_{\rm osc}$  is set to 64 kHz, choose the appropriate values for C and  $R_2$  using the following as a reference:

C=100 pF,  $R_1$ =150k $\Omega$ ,  $R_2$ =50k $\Omega$ .

9-2 Fluctuation of RC oscillation frequencies

When choosing RC oscillation, the RC oscillation frequencies are varied according to the fluctuation of the external C and R<sub>2</sub> as well as the process variations of LSI.

When using a  $50k\Omega$  R2, the error due to process variations of the LSI is maximum  $\pm 4\%$  so that the fluctuation of the RC oscillation frequency when using a capacitance (C) of  $\pm 1\%$  accuracy and a resistance (R<sub>2</sub>) of  $\pm 2\%$  accuracy is maximum  $\pm 7\%$  approximately.

Figure 12 RC Oscillation Frequency

## O K I SEMICONDUCTOR GROUP

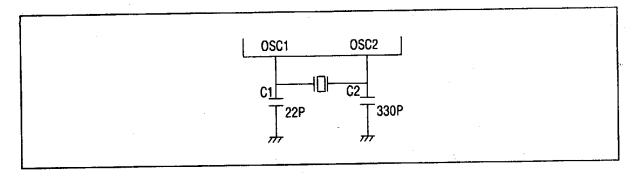

10. Crystal Oscillation

crystal oscillator, KF-38S4-13PO102 (64 kHz), made by Kyocera.

Figure 13 shows an external circuit using a

Figure 13 Circuit Diagram of Crystal Oscillator Connection

11. Connection with MSC 1191/1192

When using an MSC1191 and an MSC1192, connect the STBY pin to the OSC3/ $\overline{\text{CS}}$  pin an

the OSC2 pin, respectively. When connecting with an MSC1191/1192, set C and R after mounting it to the board as the oscillation characteristics may change.

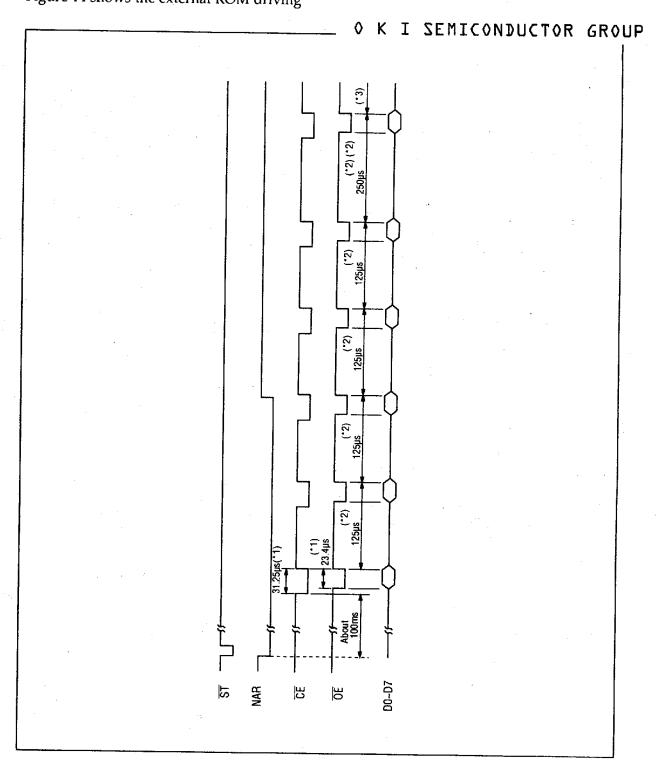

12. External ROM Timing

Figure 14 shows the external ROM driving

timing under voice playback at  $f_{\rm osc}$  = 64kHz and  $f_{\rm s}$  = 8.0kHz.

Note \*1) This is proportional to  $f_{osc}$

\*2) This is proportional to fs

\*3) CE,OE and D0~D7 are input and output at the frequency of 250µs or 125µs hereafter.

Figure 14 External ROM Timing

Note: Use a CMOS type 27C256 as an EPROM if possible. If an NMOS type 27256 is used, there are some cases where the power voltage variation of the EPROM becomes a source to generate noise.

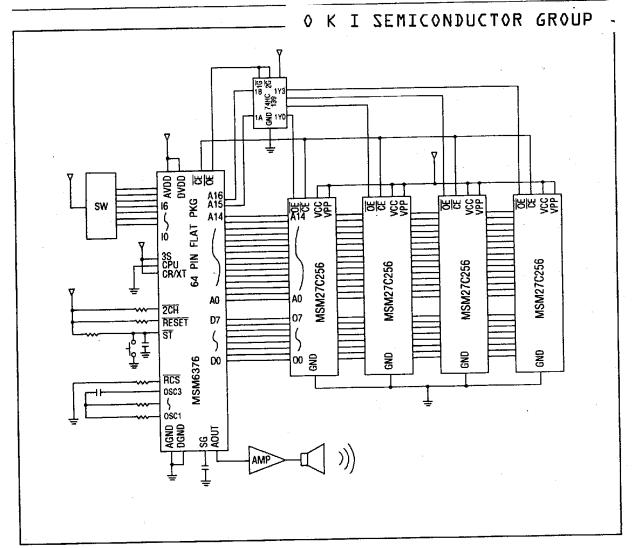

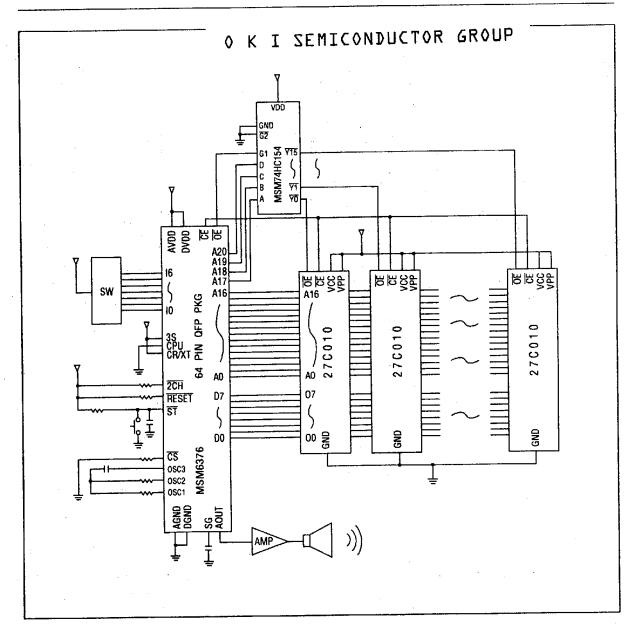

Figure 15 Example of Interface Using Four 256K EPROMs

Note: Use a CMOS type 27C256 as an EPROM if possible. If an NMOS type 27256 is used, there are some cases where the power voltage variation of the EPROM becomes a source to generate noise.

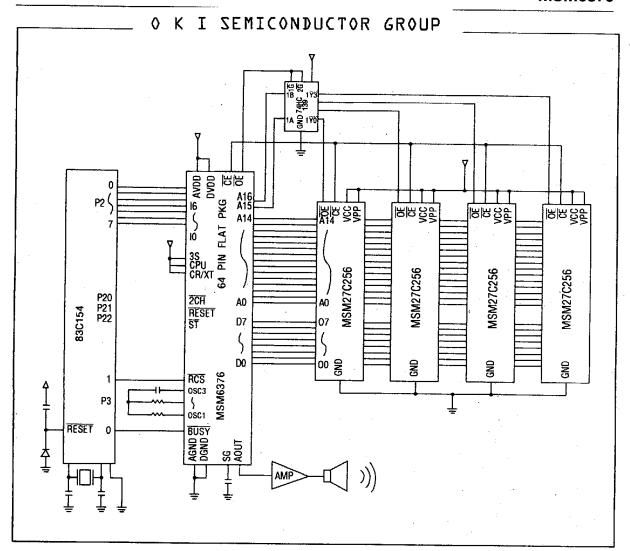

Figure 16 Example of Applied CPU Interface Circuit

Note: Use a CMOS type 27C010 as an EPROM if possible. If an NMOS type EPPROM is used the power voltage variation of the EPROM becomes a source to generate noise.

Figure 17 Example of Interface Using 16-1Mbit EPROMs