National Semiconductor

## LM1291 Video PLL System for Continuous-Sync Monitors

## **General Description**

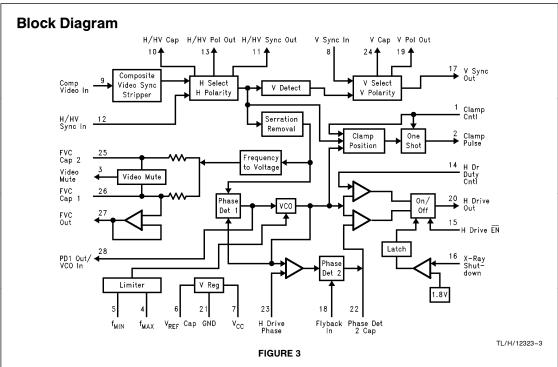

The LM1291 is an integrated horizontal time base solution specifically designed to operate in continuous-sync video monitors. It automatically synchronizes to any H frequency from 22 kHz to 125 kHz and provides the drive pulse to the high power deflection circuit.

Available sync processing includes a vertical sync separator and a composite video sync stripper. An internal sync selection scheme gives highest priority to separate H and V sync, then composite sync, and finally sync on video; no external switching between sync sources is necessary. The LM1291 provides polarity-normalized H/HV and V sync outputs, along with logic flags which show the respective input polarities

The design uses an on-chip FVC (Frequency-to-Voltage Converter) to set the center frequency of the VCO (Voltage-Controlled Oscillator). This technique allows autosync operation over the entire frequency range using just one optimized set of external components.

The system includes a second phase detector which compensates for storage time variation in the horizontal output transistor; the picture's horizontal position is thus independent of temperature and component variance.

The LM1291 provides DC control pins for H Drive duty cycle and flyback phase.

**Connection Diagram**

**Features**

- Wide continuous autosync range-22 kHz to 125 kHz (1:5.7) with no component switching or external adjustments

- No manufacturing trims required—internal VCO capacitor trimmed on chip

- No costly high-precision components needed

- Low phase jitter (1.3 ns at 100 kHz)

- DC controlled H phase and duty cycle

- Video mute pulse for blanking during H frequency transitions

- Input sync prioritization

- Clamp pulse position and width control

- Continuous clamp pulse output, even with no sync input ■ Resistor-programmable minimum and maximum VCO frequency

- X-ray input disables H drive and mutes video until V<sub>CC</sub> powered down

- H drive disabled for V<sub>CC</sub> < 9.5V</p>

- Horizontal output transistor protected against accidental turn-on during flyback

- Capacitor-programmable frequency ramping, df<sub>VCO</sub>/dt, protects H output transistor during scanning mode changes

VIDEO MUTE f<sub>мах</sub> fMIN V<sub>REF</sub> CAP V<sub>CC</sub> V SYNC IN 21 COMP VIDEO IN H/HV CAP 10 19

CLAMP CNTL 28 PD1 OUT/VCO IN CLAMP PULSE 27 FVC OUT 26 FVC CAP1 25 FVC CAP2 24 V CAP 23 H DRIVE PHASE 22 PHASE DET 2 CAP GND 20 H DRIVE OUT - V POL OUT H/HV SYNC OUT -FLYBACK IN 18 H/HV SYNC IN--V SYNC OUT 12 17 H/HV POL OUT-13 16 -X-RAY SHUTDOWN H DR DUTY CNTL 14 15 -H DRIVE EN TL/H/12323-1 **FIGURE 1** Order Number LM1291N See NS Package Number N28B

© 1995 National Semiconductor Corporation TL/H/12323 RRD-B30M115/Printed in U. S. A.

June 1995

Absolute Maximum Ratings (Notes 1 & 3) If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

| Supply Voltage                                                 | 14V             |

|----------------------------------------------------------------|-----------------|

| Input Voltage, V <sub>DC</sub>                                 |                 |

| Pins 15, 23                                                    | 5V              |

| Pins 4, 5                                                      | 8V              |

| Pins 8, 28                                                     | 10V             |

| Pins 1, 9, 12, 14, 16, 18                                      | V <sub>CC</sub> |

| Power Dissipation (P <sub>D</sub> )                            | 2.5W            |

| (Above 25°C Derate Based on $\theta_{JA}$ and T <sub>J</sub> ) |                 |

| Thermal Resistance ( $\theta_{JA}$ )                           | 50°C/W          |

**Operating Ratings** (Note 2)

Operating Temperature RangeSupply Voltage (VCC)10.8V

$-20^{\circ}\text{C to} + 80^{\circ}\text{C}$   $10.8\text{V} \leq \text{V}_{CC} \leq 13.2\text{V}$

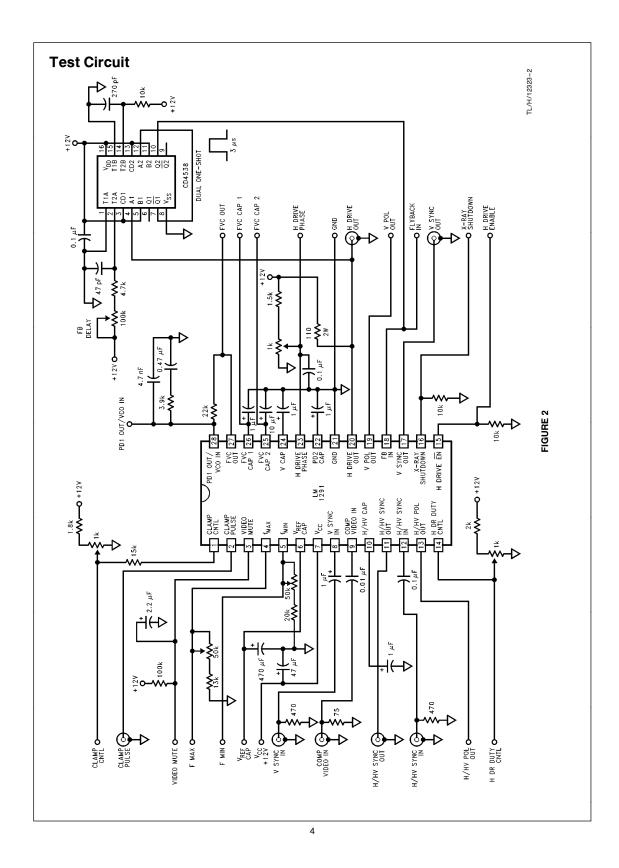

## **Electrical Characteristics** See Test Circuit (*Figure 2*); $T_A = 25^{\circ}C$ ; $V_{CC} = 12V$

| Parameter                                                               | Conditions                                                          | Typical<br>(Note 6) | Limit<br>(Note 7) | Units                 |

|-------------------------------------------------------------------------|---------------------------------------------------------------------|---------------------|-------------------|-----------------------|

| Supply Current                                                          |                                                                     | 30                  | 40                | mA (max)              |

| Jitter                                                                  | H Sync frequency = 100 kHz<br>(Note 8)                              | 1.3                 |                   | ns p-p                |

| Minimum composite video<br>input voltage                                | Pin 9, cap coupled (0.01 $\mu$ F), sync tip to black level          |                     | 0.14              | V <sub>PP</sub> (min) |

| DC clamp level, composite<br>video input                                |                                                                     | 2.0                 |                   | V <sub>DC</sub>       |

| Clamp charging current,<br>composite video input                        |                                                                     | 1                   |                   | mA                    |

| H/HV sync input amplitude (Pin 12)                                      | Cap coupled, 10% duty cycle                                         |                     | 1.0               | V <sub>PP</sub> (min) |

| V sync input amplitude (Pin 8)                                          | Cap coupled, 1% duty cycle                                          |                     | 1.0               | V <sub>PP</sub> (min) |

| High level output voltage V <sub>OH</sub> ,<br>(Pins 2, 11, 13, 17, 19) | $I_{OH} = -100 \ \mu A$                                             | 4.3                 | 4.0               | V <sub>DC</sub> (min) |

| Low level output voltage V <sub>OL</sub> ,<br>(Pins 2, 11, 13, 17, 19)  | $I_{OL} = 1.6 \text{ mA}$                                           | 0.25                | 0.4               | V <sub>DC</sub> (max  |

| Video Mute low level output<br>voltage (Pin 3)                          | $I_{OL} = 2 \text{ mA}$                                             |                     | 0.4               | V <sub>DC</sub> (max  |

| Mute detection voltage<br>threshold                                     | $\Delta V$ , $ FVC Cap 1 - FVC Cap 2 $ for Mute Output low          | 100                 |                   | mV                    |

| Flyback input threshold (Pin 18)                                        | Positive-going flyback pulse                                        | 1.4                 |                   | V                     |

| Under-voltage lockout (Pin 7)                                           | V <sub>CC</sub> below threshold:<br>H Drive Output open (unlatched) | 9.5                 |                   | V                     |

| Frequency to voltage gain                                               | 22 kHz $\leq f_{H} \leq$ 125 kHz                                    | 0.047               |                   | V/kHz                 |

| VCO gain constant                                                       | $f_{VCO} = 100 \text{ kHz}$                                         | $1.34	imes10^5$     |                   | Rad/s/V               |

| PD1 Phase Detector gain constant                                        | $f_{VCO} = 100 \text{ kHz}$                                         | 130                 |                   |                       |

|                                                                         | $f_{VCO} = 60 \text{ kHz}$                                          | 78.1                |                   | μA/Radian             |

|                                                                         | $f_{VCO} = 22 \text{ kHz}$                                          | 28.6                |                   |                       |

| Frequency to voltage linearity                                          | 22 kHz $\leq$ f <sub>H</sub> $\leq$ 125 kHz                         | 1.0                 |                   | %                     |

| VCO linearity                                                           | 22 kHz $\leq$ f <sub>VCO</sub> $\leq$ 125 kHz                       | 1.0                 |                   | %                     |

| Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Conditions                                                                                                                                                                                                                                                                                                                                                                              | Typical<br>(Note 6)                                                                                                                    | Limit<br>(Note 7)                                                                       | Units                                                                     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| H Drive duty cycle control<br>gain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | DC input 0V-4V; 30%-70%<br>allowed                                                                                                                                                                                                                                                                                                                                                      | 0.1                                                                                                                                    |                                                                                         | T <sub>H</sub> /V                                                         |

| H Drive Phase control gain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | (Note 9)                                                                                                                                                                                                                                                                                                                                                                                | 47                                                                                                                                     |                                                                                         | °/V                                                                       |

| PD1 Phase detector leakage current<br>+ VCO input bias current (Pin 28)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                        | 1                                                                                       | μA (max                                                                   |

| H Drive low level output voltage<br>(Pin 20)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | I <sub>OL</sub> = 100 mA                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                        | 0.8                                                                                     | V (max)                                                                   |

| H Drive EN low level input voltage<br>(Pin 15)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | H Drive output active                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                        | 0.8                                                                                     | V (max)                                                                   |

| H Drive EN high level input voltage<br>(Pin 15)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | H Drive output open (unlatched)                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                        | 2.0                                                                                     | V (min)                                                                   |

| X-ray Shutdown threshold voltage<br>(Pin 16)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Above threshold<br>H Drive Output Open (Latched)                                                                                                                                                                                                                                                                                                                                        | 1.72                                                                                                                                   | 1.65<br>1.8                                                                             | V (min)<br>V(max)                                                         |

| H/HV Sync out<br>propagation delay change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | H/HV in vs. Comp Video in                                                                                                                                                                                                                                                                                                                                                               | 32                                                                                                                                     |                                                                                         | ns                                                                        |

| Clamp Pulse width                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | (back porch) $R_{SET} = 15k$ ; $V_{SET} = 0V$                                                                                                                                                                                                                                                                                                                                           | 0.4                                                                                                                                    |                                                                                         | μs                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | (back porch) $R_{SET} = 15k$ ; $V_{SET} = 1.5V$                                                                                                                                                                                                                                                                                                                                         | 1.4                                                                                                                                    |                                                                                         | μs                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | (sync tip) R <sub>SET</sub> = 15k; V <sub>SET</sub> = 4V                                                                                                                                                                                                                                                                                                                                | 0.6                                                                                                                                    |                                                                                         | μs                                                                        |

| Clamp Pulse Delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | (back porch) Trailing edge H/HV Sync In to leading edge clamp pulse                                                                                                                                                                                                                                                                                                                     | 0.1                                                                                                                                    |                                                                                         | μs                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | (sync tip) Leading edge H/HV Sync In<br>to leading edge clamp pulse                                                                                                                                                                                                                                                                                                                     | 0.025 T <sub>H</sub>                                                                                                                   |                                                                                         | s                                                                         |

| Internal Ref voltage at pin 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | No load                                                                                                                                                                                                                                                                                                                                                                                 | 8.2                                                                                                                                    |                                                                                         | V                                                                         |

| Note 2: Operating Ratings indicate conditions for<br>and test conditions, see the Electrical Characteri<br>may degrade when the device is not operated ur<br>Note 3: All voltages are measured with respect 1<br>Note 4: The maximum power dissipation must be<br>allowable power dissipation at any elevated temp<br>this device, $T_{Jmax} = 150^{\circ}$ C. The typical thermal<br>Note 5: Human Body model, 100 pF capacitor d<br>Note 6: Typicals are at $T_A = T_J = 25^{\circ}$ C and rep<br>Note 7: Tested limits are guaranteed to National<br>Note 8: Measured with HP 53310A Modulation D<br>Note 9: Phase limits: $-0.15 < \phi < \left(0.35 - \frac{10}{2}\right)$ | o GND, unless otherwise specified.<br>derated at elevated temperatures and is dictated by $T_{Jmax}$<br>erature is $P_D = (T_{Jmax} - T_A)/\theta_{JA}$ or the number given in th<br>resistance ( $\theta_{JA}$ ) of these parts when board mounted follow<br>ischarged through a 1.5 kΩ resistor.<br>present most likely parametric norm.<br>'s AOQL (Average Outgoing Quality Level). | t conditions listed.<br>, θ <sub>JA</sub> and the ambie<br>the Absolute Maximu<br>w: LM1291N 50°C/V<br>where t <sub>DFB</sub> is the f | Some performance<br>int temperature, T <sub>A</sub><br>im Ratings, whiche<br><i>N</i> . | e characteristic<br>,. The maximur<br>ver is lower. Fo<br>ansistor turn-o |

## **Pin Descriptions**

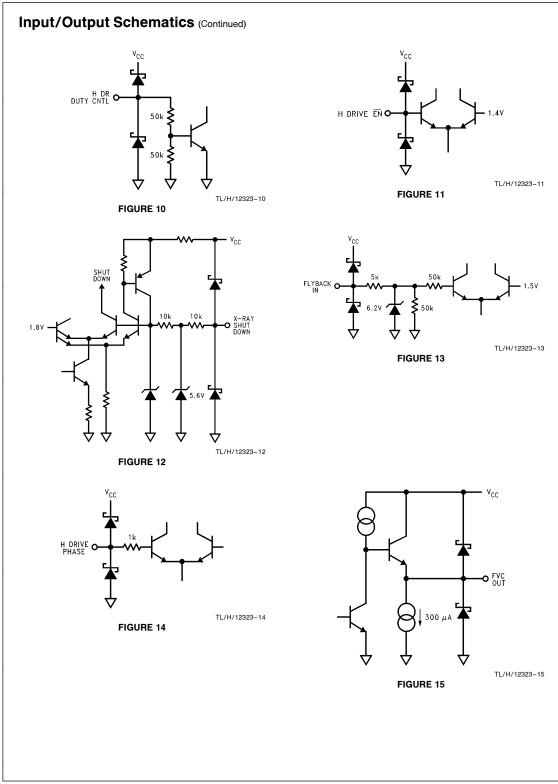

See Figures 4 through 15 for input and output schematics.

**Pin 1 - CLAMP CNTL:** This low-impedance current-mode input pin is internally biased to 2V. The direction of current sets the pulse position (back porch or sync-tip), while the current magnitude sets the pulse width. In a typical application, a control voltage of 0V-4V is applied to this pin through a 15 kΩ resistor. A voltage below 2V positions the pulse on the back porch of the horizontal sync pulse and decreasing voltage narrows the pulse. A voltage above 2V sets the pulse on the H sync-tip (slightly delayed from the leading edge) and increasing voltage narrows the pulse. At the boundary of the switchover between the two modes, there is a narrow region of uncertainty resulting in oscillation, which should be no problem in most applications.

When there is no H sync in sync-tip mode, the clamp pulse is generated by the VCO at the frequency preset by pin 5 (f<sub>MIN</sub>). This feature is intended for use in On Screen Display systems.

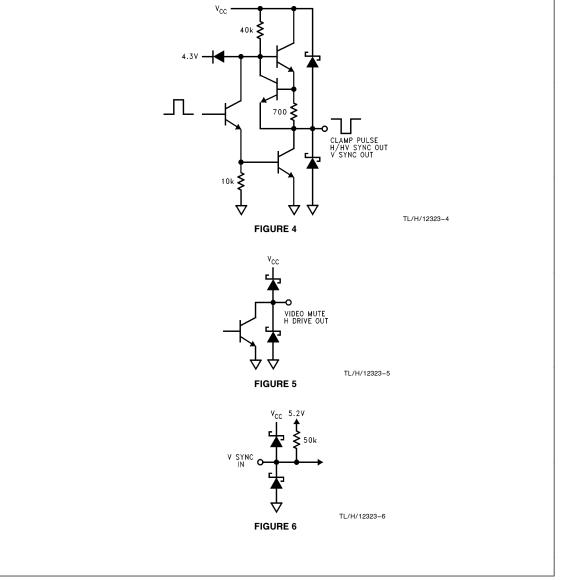

**Pin 2 - CLAMP PULSE:** Active-low clamp pulse output. See *Figure 4* for the output schematic.

**Pin 3 - VIDEO MUTE:** This NPN open-collector output produces an active-low pulse when triggered by a step change of H sync frequency. See *Figure 5* for the output schematic.

**Pin 4 - f\_{MAX}:** A resistor from this pin to ground sets the upper frequency limit of the VCO.  $f_{MAX}$  is approximately:

$\frac{1.8\times10^9}{(\mathsf{R}_{\mathsf{MAX}}+500)}\,\mathsf{Hz}$

**Pin 5 - f**MIN: A resistor from this pin to ground sets the lower frequency limit of the VCO. f<sub>MIN</sub> is approximately:

$$7.5 imes 10^3 + rac{5.6 imes 10^8}{(R_{MIN} + 500)} \, Hz$$

**Pin 6 - V<sub>REF</sub> CAP:** This is the decoupling pin for the internal 8.2V reference. It should be decoupled to pin 21 (GND) via a short path with a cap of at least 470  $\mu$ F.

**Pin 7 - V<sub>CC</sub>:** 12V nominal power supply pin. This pin should be decoupled to pin 21 (GND) via a short path with a cap of at least 47 μF.

**Pin 8 - V SYNC IN:** This pin accepts AC-coupled V sync of either polarity. The pin is internally biased at 5.2V; its input resistance is approximately 50 k $\Omega$ . For best noise immunity, a resistor of 2 k $\Omega$  or less should be connected from the input side of the coupling cap to ground. See *Figure 6* for the input schematic.

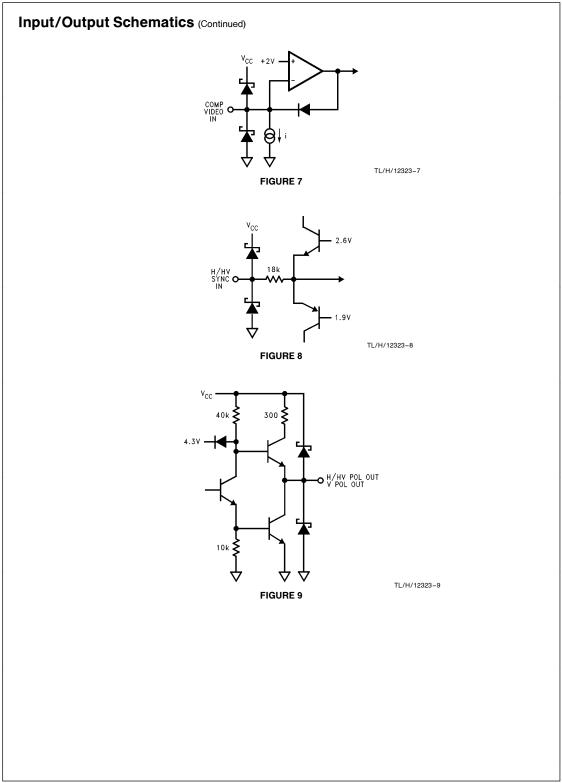

**Pin 9 - COMP VIDEO IN:** The composite video sync stripper is active only when no signal is present at pin 12 (H/HV IN). The signal to pin 9 must have negative-going sync tips which are at least 0.14V below black level. For best noise immunity, a resistor of 2 k $\Omega$  or less should be connected from the input side of the coupling cap to ground. See *Figure 7* for the input schematic.

**Pin 10 - H/HV CAP:** A capacitor is connected from this pin to ground for detecting the polarity and existence of H/HV sync at pin 12.

### Pin Descriptions (Continued)

**Pin 11 - H/HV SYNC OUT:** The sync processor outputs active-low H/HV sync derived from the active sync input (pin 9 or pin 12). Pin 11 stays low in the absence of sync input. See *Figure 4* for the output schematic.

**Pin 12 - H/HV SYNC IN:** This pin accepts AC-coupled H or composite sync of either polarity. For best noise immunity, a resistor of 2 k $\Omega$  or less should be connected from the input side of the coupling cap to ground. See *Figure 8* for the input schematic.

**Pin 13 - H/HV POL OUT:** A low logic level indicates activehigh H/HV sync to pin 12, a high level indicates active-low. Pin 13 stays low in the absence of H/HV sync. See *Figure 9* for the output schematic.

**Pin 14 - H DR DUTY CNTL:** A DC voltage applied to this pin sets the duty cycle of the horizontal drive output (pin 20), with a range of approximately 30%–70%. 2V sets the duty cycle to 50%. See *Figure 10* for the input schematic.

**Pin 15 - H DRIVE EN:** A low logic level input enables H DRIVE OUT (pin 20). See *Figure 11* for the input schematic.

**Pin 16 - X-RAY SHUTDOWN:** This pin is for monitoring CRT anode voltage. If the input voltage exceeds an internal threshold, H DRIVE OUT (pin 20) is latched high and VIDEO MUTE (pin 3) is latched low.  $V_{CC}$  has to be reduced to below approximately 2V to clear the latched condition, i.e., power must be turned off. See *Figure 12* for the input schematic.

**Pin 17 - V SYNC OUT:** The sync processor outputs activelow V sync derived from the active sync input (pin 8, pin 9 or pin 12). Pin 17 stays low in the absence of sync input. See *Figure 4* for the output schematic.

**Pin 18 - FLYBACK IN:** Input pin for phase detector 2. For best operation, the flyback peak should be at least 5V but not greater than V<sub>CC</sub>. Any pulse width greater than 1.5  $\mu$ s is acceptable. See *Figure 13* for the input schematic.

**Pin 19 - V POL OUT:** A low logic level indicates active-high V sync to pin 8, a high level indicates active-low. Pin 19 stays low in the absence of V sync. See *Figure 9* for the output schematic.

**Pin 20 - H DRIVE OUT:** This is an open-collector output which provides the drive pulse for the high power deflection circuit. The pulse duty cycle is controlled by pin 14. Polarity convention: Horizontal deflection output transistor is on when H DRIVE OUT is low. See *Figure 5* for the output schematic.

**Pin 21 - GND:** System ground. For best jitter performance, all LM1291 filter components and bypass capacitors should be connected to this pin via short paths.

**Pin 22 - PHASE DET 2 CAP:** The low-pass filter cap for the output of phase detector 2 is connected from this pin to pin 21 (GND) via a short path.

**Pin 23 - H DRIVE PHASE:** A DC control voltage applied to this pin sets the phase of the flyback pulse with respect to the leading edge of H sync. See *Figure 14* for the input schematic.

**Pin 24 - V CAP:** A capacitor is connected from this pin to ground for detecting the polarity and existence of V sync at pin 8.

**Pin 25 - FVC CAP 2:** Secondary FVC filter pin.  $C_{FVC2}$  is connected from this pin to ground. The width of the VIDEO MUTE (pin 3) pulse is controlled by the time constant difference between the filters at pins 25 and 26.

**Pin 26 - FVC CAP 1:** Primary FVC filter pin.  $C_{FVC1}$  is connected from this pin to pin 21 (GND) via a short path. The voltage at this pin is buffered to pin 27 (FVC OUT).

**Pin 27 - FVC OUT:** Buffered output of the Frequency-to-Voltage Converter, which sets the VCO center frequency through an external resistor to pin 28. Care should be taken when further loading this pin, since during the vertical interval it presents a high output impedance. Excessive loading can cause top-of-screen phase recovery problems.

**Pin 28 - PD1 OUT/VCO IN:** Phase detector 1 has a gated charge pump output which requires an external low-pass filter. For best jitter performance, the filter should be grounded to pin 21 (GND) via a short path. If a voltage source is applied to this pin, the phase detector is disabled and the VCO can be controlled directly.

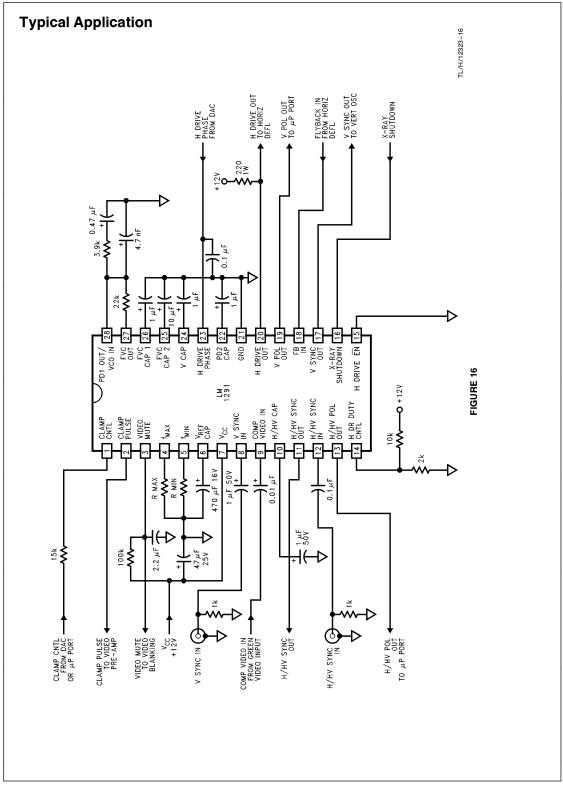

## **Application Hints**

#### 1. Phase control for geometry correction:

Pin 23 (H DRIVE PHASE) is designed to control static phase (picture horizontal position), while pin 22 (PHASE DET 2 CAP) controls dynamic phase for geometry correction. With the use of both pins 22 and 23, complete control of static and dynamic phase can be achieved. To accomplish this, the low-pass filter cap at pin 22 is not grounded, but is connected instead to a modulating AC voltage source. The cap then functions both as a low-pass filter (for phase detector 2) and as an input coupling cap (for the AC source).

#### 2. Programmable frequency ramping:

H frequency transitions from high to low present a special problem for deflection output stages without current limiting. If, during such a transition, the output transistor on-time increases excessively before the B+ voltage has decreased to its final level, then the deflection inductor current ramps too high and the induced flyback pulse can exceed the breakdown voltage, BV<sub>CEX</sub>, of the output transistor. To prevent this, the rate of change of the VCO frequency must be limited.

Consider a scanning mode transition at t=0 from  $f_1$  to  $f_2.$  The VCO frequency as a function of time,  $f_{VCO}(t),$  is described by the equation,

$$f_{VCO}(t) \cong f_1 + (f_2 - f_1)(1 - \exp(-t/\tau))$$

#### where $au = 40 imes 10^3 imes C_{FVC1}$ .

The above equation can be used to predict VCO behavior during frequency transitions, but in practice the value of  $C_{FVC1}$  is most easily determined empirically. In general, large values minimize the chance of exceeding  $BV_{CEX}$ , but generate long PLL capture times.

# Application Hints (Continued)

## 3. Video mute:

Numerous designs require video blanking during scanning mode transitions. The LM1291 provides an active-low pulse at pin 3 when triggered by a step change of H sync frequency from f<sub>1</sub> to f<sub>2</sub>. The pulse width is controlled by the time constants set up through capacitors C<sub>FVC2</sub> and C<sub>FVC1</sub>, at pins 25 and 26 respectively. For C<sub>FVC2</sub>  $\geq$  3  $\times$  C<sub>FVC1</sub>, the pulse width is approximately:

Many sync sources fail to exhibit a clean step change of H sync frequency during scanning mode transitions. For this reason, in most applications a pulse smoothing circuit is needed at pin 3. Typically a 2.2  $\mu$ F cap to ground is used in conjunction with a 100 k $\Omega$  pull-up resistor. See *Figure 16*. The resulting pulse has a slow rise time at the trailing edge, which extends the effective mute duration slightly.

$$40 imes 10^3 imes C_{FVC2} imes In\left(rac{|f_2 - f_1|}{2.13 imes 10^3}

ight)$$

seconds

## **Input/Output Schematics**

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications