# 16-Bit Stereo Audio Codec

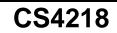

# Complete CMOS Stereo Audio Input<br/>and Output System featuring:General DescriptionThe CS4218 Stereo Audio Codec

- Delta-Sigma A/D and D/A Converters using 64x Oversampling.

- Input Anti-Aliasing and Output Smoothing Filters.

- Programmable Input Gain (0 dB to 22.5 dB).

- Programmable Output Attenuation (0 dB to 46.5 dB).

- Sample frequencies from 4 kHz to 50 kHz.

- Low Distortion, THD < 0.02% for DAC. THD < 0.02% for ADC.

- Low Power Dissipation: 80 mA typical.

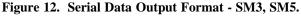

- Power-Down Mode : 1 mA typical.

- Pin Compatible with CS4216 when used in Serial Modes 3 and 4 (See Appendix A).

- I<sup>2</sup>S(TM) Compatible Serial Mode (SM5).

- Operates from 5V or 3.3V Digital Power Supply. Requires 5V Analog Power Supply.

The CS4218 Stereo Audio Codec is a monolithic CMOS device for computer multimedia, automotive, and portable audio applications. It performs A/D and D/A conversion, filtering, and level setting, creating 4 audio inputs and 2 audio outputs for a digital computer system. The digital interfaces of left and right channels are multiplexed into a single serial data bus with word rates up to 50 kHz per channel.

ADCs and the DACs use delta-sigma modulation with 64X oversampling. The ADCs and DACs include digital decimation filters and output smoothing filters on-chip which eliminate the need for external anti-aliasing filters.

The CS4218 is pin and function compatible with the CS4216 when used in Serial modes 3 and 4. See the Appendix A at the end of this data sheet for details.

I<sup>2</sup>S is a trademark of Philips.

Ordering Information:

CS4218-KL

0° to 70°C

CS4218-KQ

0° to 70°C

44-pin PLCC 44-pin TQFP

Crystal Semiconductor Corporation P.O. Box 17847, Austin, TX 78760 (512) 445 7222 FAX: (512) 445 7581 http://www.crystal.com

Copyright © Crystal Semiconductor Corporation 1996 (All Rights Reserved) SEP '96 DS135F1 **1**

## Contents

| Description                                    |       |        |       |       |      |     |     |     |   |  |      |

|------------------------------------------------|-------|--------|-------|-------|------|-----|-----|-----|---|--|------|

| Cover                                          |       |        |       | •     |      |     |     |     |   |  | . 1  |

| Contents                                       |       |        |       |       |      |     |     |     |   |  | . 2  |

| Recommended Operating Conditi                  | ons   |        |       |       |      |     |     |     |   |  | . 3  |

| Analog Input Characteristics .                 |       |        |       |       |      |     |     |     |   |  | . 3  |

| Analog Output Characteristics                  |       |        |       |       |      |     |     |     |   |  | . 4  |

| Switching Characteristics                      |       |        |       |       |      |     |     |     |   |  | . 5  |

| Digital Characteristics                        |       |        |       |       |      |     |     |     |   |  | . 7  |

| A/D Decimation Filter Characteris              | tics  |        |       |       |      |     |     |     |   |  | . 8  |

| D/A Interpolation Characteristics              |       |        |       |       |      |     |     |     |   |  | . 8  |

| Absolute Maximum Ratings .                     |       |        |       |       |      |     |     |     |   |  | . 8  |

| Filter Response Plots                          |       |        |       |       |      |     |     |     |   |  | . 9  |

| Typical Connection Diagram .                   |       |        |       |       |      |     |     |     |   |  | . 1  |

| Overview                                       |       |        |       |       |      |     |     |     |   |  | . 12 |

| Functional Description                         |       |        |       |       |      |     |     |     |   |  | . 12 |

| <ul> <li>Analog Inputs and Outputs</li> </ul>  |       |        |       |       |      |     |     |     |   |  | . 12 |

| - Offset Calibration                           |       |        |       |       |      |     |     |     |   |  | . 1: |

| - Input Gain and Output Leve                   | I Set | tting  |       |       |      |     |     |     |   |  | . 1: |

| <ul> <li>Muting and the ADC Valid C</li> </ul> | Coun  | ter    |       |       |      |     |     |     |   |  | . 1: |

| - Parallel Digital I/O Pins .                  |       |        |       |       |      |     |     |     |   |  | . 1  |

| - Reset and Power Down Mo                      | des   |        |       |       |      |     |     |     |   |  | . 1: |

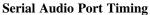

| - Audio Serial Interface .                     |       |        |       |       |      |     |     |     |   |  | . 14 |

| Serial Interface Modes                         |       |        |       |       |      |     |     |     |   |  | . 1  |

| - Serial Mode 3                                |       |        |       |       |      |     |     |     |   |  | . 1  |

| - Serial Mode 4                                |       |        |       |       |      |     |     |     |   |  | . 22 |

| - Serial Mode 5                                |       |        |       |       |      |     |     |     |   |  | . 2  |

| Power Supply and Grounding .                   |       |        |       |       |      |     |     |     |   |  | . 20 |

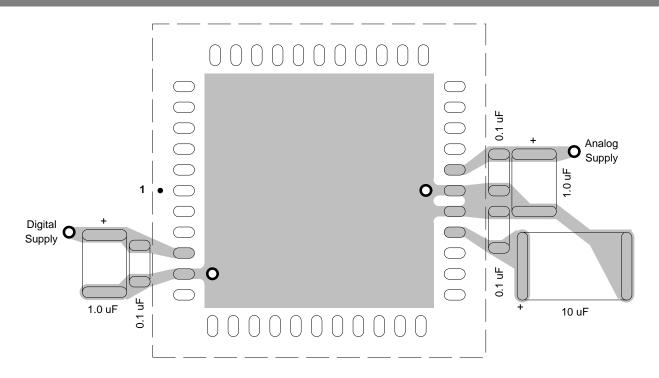

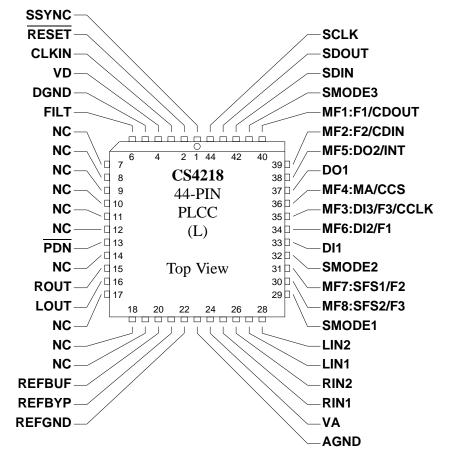

| Pin Diagrams and Descriptions                  |       |        |       |       |      |     |     |     |   |  | . 29 |

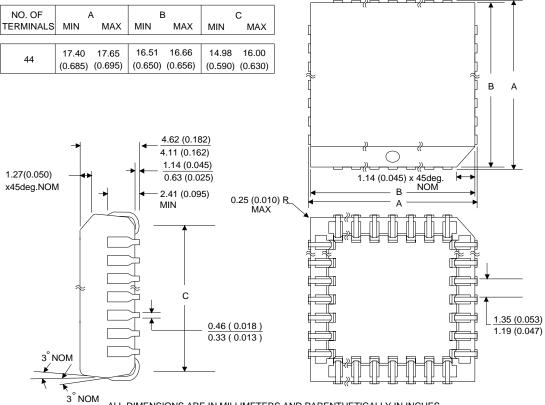

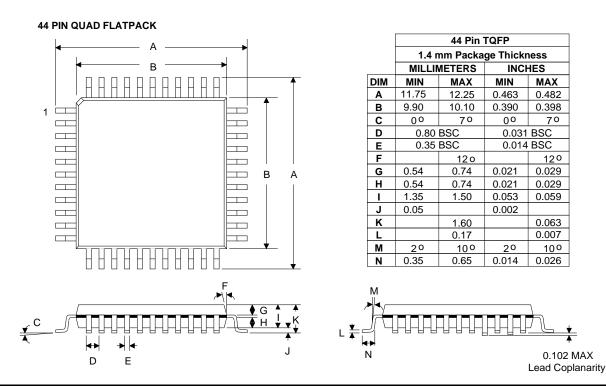

| Package Information                            |       |        |       |       |      |     |     |     |   |  | . 3  |

| Parameter Definitions                          |       |        |       |       |      |     |     |     |   |  | . 30 |

| Appendix A: CS4218 Compatibilit                | y wi  | th th  | e C   | S42   | 16   |     |     |     |   |  | . 3  |

| Appendix B: Applications of Seria              | I Mo  | de 4   | 1 (SI | M4)   |      |     |     |     |   |  | . 40 |

| Appendix C: Setting CLKIN/SCLK                 | Rat   | tio fo | or D  | esire | ed S | Sam | ple | Rat | е |  | . 43 |

# **RECOMMENDED OPERATING CONDITIONS** (AGND, DGND = 0V, all voltages with respect to 0V.)

| Parameter                     |                       | Symbol | Min  | Тур | Max  | Units |

|-------------------------------|-----------------------|--------|------|-----|------|-------|

| Power Supplies:               | Digital               | VD     | 4.75 | 5.0 | 5.25 | V     |

|                               | Digital (Low Voltage) | VD     | 3.0  | 3.3 | 3.6  | V     |

|                               | Analog                | VA     | 4.75 | 5.0 | 5.25 | V     |

| Operating Ambient Temperature |                       | Тд     | 0    | 25  | 70   | °C    |

**ANALOG CHARACTERISTICS**(T<sub>A</sub> = 25°C; VA, VD = +5V; Input Levels: Logic 0 = 0V,

Logic 1 = VD; 1kHz Input Sine Wave; CLKIN = 12.288 MHz; SM3 Slave sub-mode, 256 BPF; 0dB gain/attenuation;Conversion Rate = 48 kHz; SCLK = 12.288 MHz; Measurement Bandwidth is 10 Hz to 20 kHz; Unless otherwise specified.)

| Parameter *                                               | Symbol         | Min         | Тур      | Max         | Units      |

|-----------------------------------------------------------|----------------|-------------|----------|-------------|------------|

| Analog Input Characteristics - Minimum gain setting (0 dl | B); unless oth | nerwise spe | ecified. | •           | -          |

| ADC Resolution                                            |                | 16          | -        | -           | Bits       |

| ADC Differential Nonlinearity (Note                       | 1)             | -           | -        | ±0.9        | LSB        |

| Instantaneous Dynamic Range (Note                         | 3) IDR         | 80          | 84       | -           | dB         |

| Total Harmonic Distortion                                 | THD            | -           | -        | 0.02        | %          |

| Interchannel Isolation                                    |                | -           | 80       | -           | dB         |

| Interchannel Gain Mismatch                                |                | -           | -        | ±0.5        | dB         |

| Frequency Response (Note                                  | 1)             | -0.5        | -        | +0.2        | dB         |

| Programmable Input Gain                                   |                | -           | 22.5     | -           | dB         |

| Gain Step Size                                            |                | -           | 1.5      | -           | dB         |

| Absolute Gain Step Error                                  |                | -           | -        | 0.75        | dB         |

| Gain Drift (Note                                          | 1)             | -           | 100      | -           | ppm/°C     |

| Offset Error 0dB G<br>22.5dB G                            |                |             |          | ±50<br>±500 | LSB<br>LSB |

| Full Scale Input Voltage                                  |                | 2.5         | 2.8      | 3.1         | Vpp        |

| Input Resistance (Notes 1                                 | ,2)            | 20          | -        | -           | kΩ         |

| Input Capacitance (Note                                   | 1)             | -           | -        | 15          | pF         |

Notes: 1. This specification is guaranteed by characterization, not production testing.

2. Input resistance is for the input selected. Non-selected inputs have a very high (>1M $\Omega$ ) input resistance.

3. Operation in Slave sub-modes may yield results lower than the 80 dB minimum.

\* Parameter definitions are given at the end of this data sheet.

#### Specifications are subject to change without notice.

## ANALOG CHARACTERISTICS (Continued)

| Parameter *                         |                                                              | Symbol      | Min        | Тур           | Max            | Units          |

|-------------------------------------|--------------------------------------------------------------|-------------|------------|---------------|----------------|----------------|

| Analog Output Characteristics - Min | imum Attenuation; Unless                                     | s Otherwise | e Specifie | d.            |                |                |

| DAC Resolution                      |                                                              |             | 16         | -             | -              | Bits           |

| DAC Differential Nonlinearity       | (Note 1)                                                     |             | -          | -             | ±0.9           | LSB            |

| Total Dynamic Range                 |                                                              | TDR         | -          | 93            | -              | dB             |

| Instantaneous Dynamic Range         |                                                              | IDR         | 80         | 83            | -              | dB             |

| Total Harmonic Distortion           | (Note 4)                                                     | THD         | -          | -             | 0.02           | %              |

| Interchannel Isolation              | (Note 4)                                                     |             | -          | 80            | -              | dB             |

| Interchannel Gain Mismatch          |                                                              |             | -          | -             | ±0.5           | dB             |

| Frequency Response                  | (Note 1)                                                     |             | -0.5       | -             | +0.2           | dB             |

| Programmable Attenuation            | (Note 5)                                                     |             | -          | -46.5         | -              | dB             |

| Attenuation Step Size               | (Note 5)                                                     |             | -          | 1.5           | -              | dB             |

| Absolute Attenuation Step Error     | (Note 5)                                                     |             | -          | -             | 0.75           | dB             |

| Gain Drift                          | (Note 1)                                                     |             | -          | 100           | -              | ppm/°C         |

| REFBUF Output Voltage<br>Maximum    | (Note 6)<br>n output current= 400 μA                         |             | 1.9        | 2.1           | 2.3            | V              |

| Offset Voltage                      | (Note 7)                                                     |             | -          | 10            | -              | mV             |

| Full Scale Output Voltage           | (Note 4)                                                     |             | 2.4        | 2.7           | 3.1            | Vpp            |

| External Load Impedance             |                                                              |             | 10k        | -             | -              | Ω              |

| Internal Resistor Value for LOUT ar | nd ROUT                                                      |             | 400        | 600           | 800            | Ω              |

| Deviation from Linear Phase         | (Note 1)                                                     |             | -          | -             | 1              | Degree         |

| Out of Band Energy                  | (22 kHz to 100 kHz)                                          |             | -          | -60           | -              | dB             |

| Power Supply                        |                                                              | · · · · ·   |            |               |                |                |

| Power Supply Current (Note 8)       | Operating (VD = 5.0V)<br>Operating (VD = 3.3V)<br>Power Down |             | -<br>-     | 80<br>65<br>- | 100<br>85<br>1 | mA<br>mA<br>mA |

| Power Supply Rejection              | (1 kHz)                                                      |             | -          | 40            | _              | dB             |

Notes: 4. 10 k $\Omega$ , 100 pF load.

5. Tested in SM3, Slave sub-mode, 256 BPF.

6. REFBUF load current must be DC. To drive dynamic loads, REFBUF must be buffered.

AC variations in REFBUF current may degrade ADC and DAC performance.

7. No DC load.

8. Typical current: VA = 30mA, VD = 50mA with VD = 5.0V. VA = 30mA, VD = 35mA with VD = 3.3V. Power supply current does not include output loading.

\* Parameter definitions are given at the end of this data sheet.

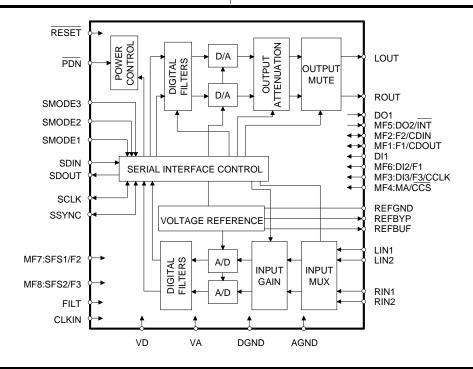

## **SWITCHING CHARACTERISTICS** (T<sub>A</sub> = 25°C; VA, VD = +5V, outputs loaded with 30 pF; Input

Levels: Logic 0 = 0V, Logic 1 = VD)

| Parameter                                                     |                                  | Symbol             | Min         | Тур             | Max         | Units      |

|---------------------------------------------------------------|----------------------------------|--------------------|-------------|-----------------|-------------|------------|

| Input clock (CLKIN) frequency SM3<br>SM3 Master and Slave Mod | Multiplier Mode<br>des, SM4, SM5 | CLKIN<br>CLKIN     | 64<br>1.024 | 768<br>12.288   | 800<br>12.8 | KHz<br>MHz |

| CLKIN low time                                                |                                  | <sup>t</sup> ckl   | 15          | -               | -           | ns         |

| CLKIN high time                                               |                                  | <sup>t</sup> ckh   | 15          | -               | -           | ns         |

| Sample Rate                                                   | (Note 1)                         | Fs                 | 4           | -               | 50          | kHz        |

| DI pins setup time to SCLK edge                               | (Note 1)                         | ts2                | 10          | -               | -           | ns         |

| DI pins hold time from SCLK edge                              | (Note 1)                         | <sup>t</sup> h2    | 8           | -               | -           | ns         |

| DO pins delay from SCLK edge                                  |                                  | <sup>t</sup> pd2   | -           | -               | 30          | ns         |

| SCLK and SSYNC output delay from CLKIN rising                 | Modes (Note 1)                   | <sup>t</sup> pd3   | -           | -               | 50          | ns         |

| SCLK period All master Mod                                    | des (Notes 1,7)<br>Slave Mode    | <sup>t</sup> sckw  | -<br>75     | 1/(Fs*bpf)<br>- | -           | s<br>ns    |

| SCLK high time                                                | Slave Mode                       | <sup>t</sup> sckh  | 30          | -               | -           | ns         |

| SCLK low time                                                 | Slave Mode                       | <sup>t</sup> sckl  | 30          | -               | -           | ns         |

| SDIN, SSYNC setup time to SCLK edge                           | Slave Mode                       | <sup>t</sup> s1    | 15          | -               | -           | ns         |

| SDIN, SSYNC hold time from SCLK edge                          | Slave Mode                       | <sup>t</sup> h1    | 10          | -               | -           | ns         |

| SDOUT delay from SCLK edge                                    |                                  | <sup>t</sup> pd1   | -           | -               | 28          | ns         |

| Output to Hi-Z state                                          | bit 64 (Note 1)                  | thz                | -           | -               | 12          | ns         |

| Output to non-Hi-Z                                            | bit 1 (Note 1)                   | t <sub>nz</sub>    | 15          | -               | -           | ns         |

| RESET pulse width low                                         |                                  |                    | 500         | -               | -           | ns         |

| CCS low to CCLK rising                                        | SM4 (Note 1)                     | t <sub>cslcc</sub> | 25          | -               | -           | ns         |

| CDIN setup to CCLK falling                                    | SM4 (Note 1)                     | <sup>t</sup> discc | 15          | -               | -           | ns         |

| CCLK low to CDIN invalid (hold time)                          | SM4 (Note 1)                     | <sup>t</sup> ccdih | 10          | -               | -           | ns         |

| CCLK high time                                                | SM4 (Note 1)                     | <sup>t</sup> cclhh | 25          | -               | -           | ns         |

| CCLK low time                                                 | SM4 (Note 1)                     | <sup>t</sup> cclhl | 25          | -               | -           | ns         |

| CCLK Period                                                   | SM4 (Note 1)                     | <sup>t</sup> cclkw | 75          | -               | -           | ns         |

| CCLK rising to CDOUT data valid                               | SM4 (Note 1)                     | tccdov             | -           | -               | 30          | ns         |

| CCLK rising to CDOUT Hi-Z                                     | SM4 (Note 1)                     | tccdot             | -           | -               | 30          | ns         |

| CCLK falling to CCS high                                      | SM4 (Note 1)                     | tcccsh             | 0           | -               | -           | ns         |

| RESET low time prior to PDN rising                            |                                  | trph               | 100         | -               | -           | ns         |

| RESET low hold time after PDN rising                          |                                  | trhold             | 50          | -               | -           | ms         |

Notes: 7. When the CS4218 is in master modes (SSYNC and SCLK outputs), the SCLK duty cycle is 50%. The equation is based on the selected sample frequency (Fs) and the number of bits per frame (bpf).

Power Down Mode Timing

# **DIGITAL CHARACTERISTICS** ( $T_A = 25^{\circ}C$ ; VA = 5V, VD = 5V or 3.3V)

| Parameter                                            | Symbol | Min    | Тур | Max    | Units |

|------------------------------------------------------|--------|--------|-----|--------|-------|

| High-level Input Voltage                             | VIH    | 2.0    | -   | VD+0.3 | V     |

| Low-level Input Voltage                              | VIL    | -0.3   | -   | 0.8    | V     |

| High-level Output Voltage at $I_0 = -2.0 \text{ mA}$ | VOH    | VD-0.3 | -   | -      | V     |

| Low-level Output Voltage at I0 = +2.0 mA             | VOL    | -      | -   | 0.2    | V     |

| Input Leakage Current (Digital Inputs)               |        | -      | -   | 10     | μΑ    |

| Output Leakage Current (High-Z Digital Outputs)      |        | -      | -   | 10     | μΑ    |

| Output Capacitance (Note 1)                          | COUT   | -      | -   | 15     | pF    |

| Input Capacitance (Note 1)                           | CIN    | -      | -   | 15     | pF    |

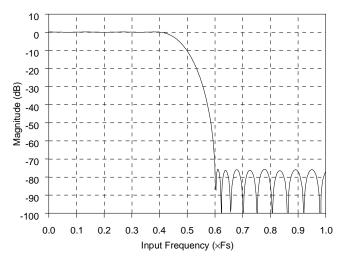

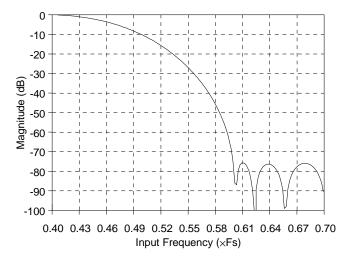

# **A/D Decimation Filter Characteristics**

| Parameter                           | Symbol | Min    | Тур | Max    | Units |

|-------------------------------------|--------|--------|-----|--------|-------|

| Passband                            |        | 0      | -   | 0.40Fs | Hz    |

| Frequency Response                  |        | -0.5   | -   | +0.2   | dB    |

| Passband Ripple (0-0.4Fs)           |        | -      | -   | ±0.1   | dB    |

| Transition Band                     |        | 0.40Fs | -   | 0.60Fs | Hz    |

| Stop Band                           |        | 0.60Fs | -   | -      | Hz    |

| Stop Band Rejection                 |        | 74     | -   | -      | dB    |

| Group Delay                         |        | -      |     | 8/Fs   | S     |

| Group Delay Variation vs. Frequency |        | -      |     | 0.0    | μs    |

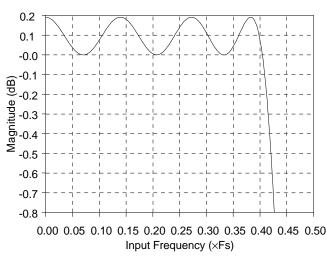

## **D/A Interpolation Filter Characteristics**

| Parameter                           | Symbol | Min    | Тур | Max    | Units |

|-------------------------------------|--------|--------|-----|--------|-------|

| Passband                            |        | 0      | -   | 0.40Fs | Hz    |

| Frequency Response                  |        | -0.5   | -   | +0.2   | dB    |

| Passband Ripple (0-0.4Fs)           |        | -      | -   | ±0.1   | dB    |

| Transition Band                     |        | 0.40Fs | -   | 0.60Fs | Hz    |

| Stop Band                           |        | 0.60Fs | -   | -      | Hz    |

| Stop Band Rejection                 |        | 74     | -   | -      | dB    |

| Group Delay                         |        | -      | -   | 8/Fs   | s     |

| Group Delay Variation vs. Frequency |        | -      | -   | 0.1/Fs | μs    |

## **ABSOLUTE MAXIMUM RATINGS** (AGND, DGND = 0V, all voltages with respect to 0V.)

| Ра                    | rameter              | Symbol | Min  | Тур | Max    | Units |

|-----------------------|----------------------|--------|------|-----|--------|-------|

| Power Supplies:       | Digital              | VD     | -0.3 | -   | 6.0    | V     |

|                       | Analog               | VA     | -0.3 | -   | 6.0    | V     |

| Input Current         | (Except Supply Pins) |        | -    | -   | ±10.0  | mA    |

| Analog Input Voltage  |                      |        | -0.3 | -   | VA+0.3 | V     |

| Digital Input Voltage |                      |        | -0.3 | -   | VD+0.3 | V     |

| Ambient Temperature   | (Power Applied)      |        | -55  | -   | +125   | °C    |

| Storage Temperature   |                      |        | -65  | -   | +150   | °C    |

Warning: Operation beyond these limits may result in permanent damage to the device. Normal operation is not guaranteed at these extremes.

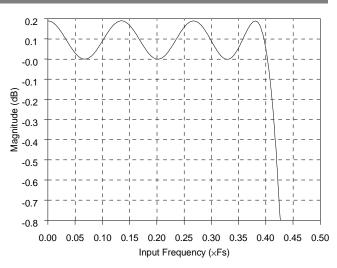

Figure 1. CS4218 ADC Frequency Response

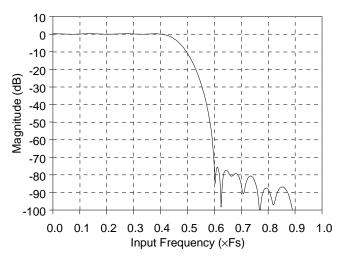

Figure 3. CS4218 ADC Transition Band

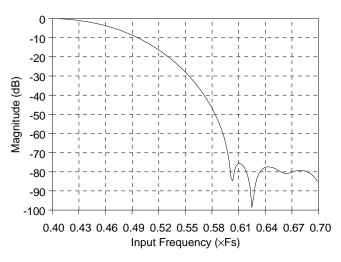

Figure 5. CS4218 DAC Passband Ripple

Figure 2. CS4218 ADC Passband Ripple

Figure 4. CS4218 DAC Frequency Response

Figure 6. CS4218 DAC Transition Band

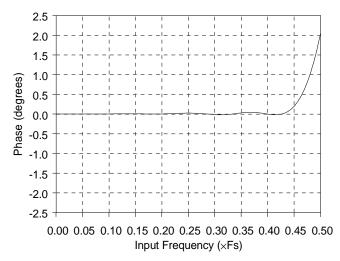

Figure 7. CS4218 DAC Deviation from Linear Phase

# CRYSTAL

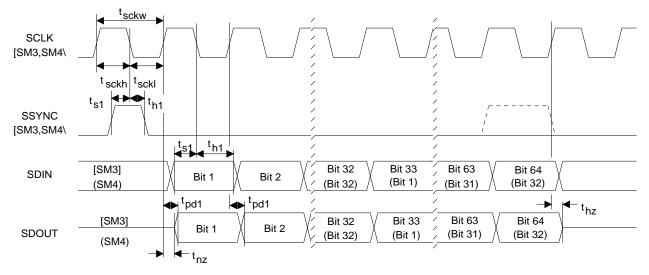

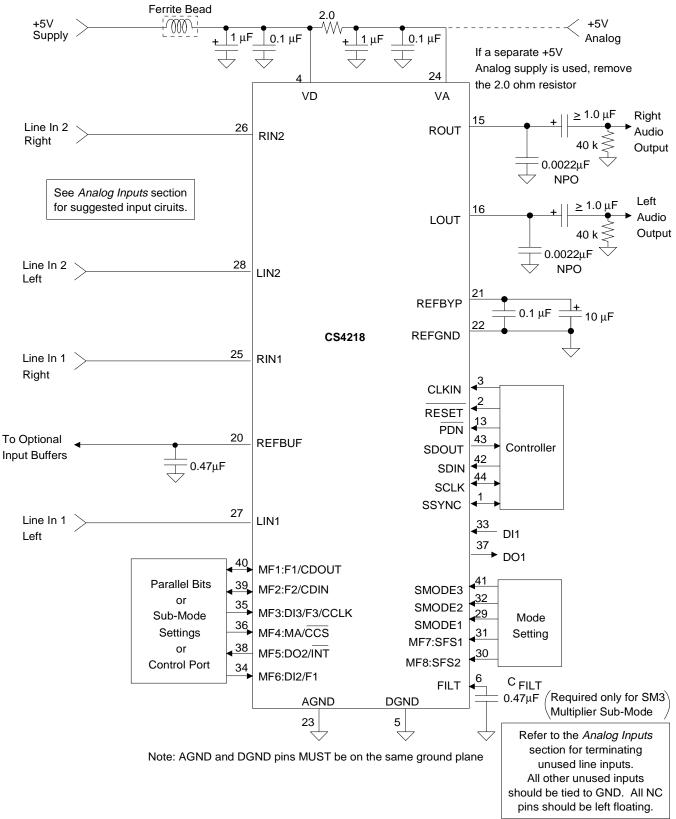

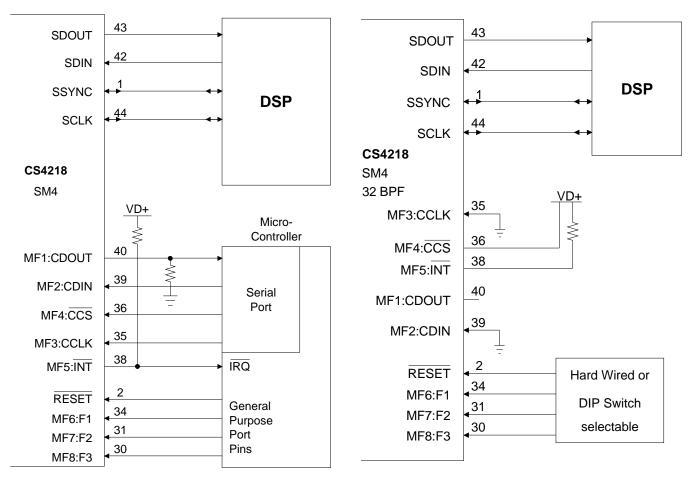

Figure 8. Typical Connection Diagram

DS135F1

The CS4218 contains two analog-to-digital converters, two digital-to-analog converters, adjustable input gain, and adjustable output level control. Since the converters contain all the required filters in digital or sampled analog form, the filters' frequency responses track the sample rate of the CS4218. Only a single-pole RC filter is required for the analog inputs and outputs. Communication with the CS4218 is via a serial port, with separate pins for data input and output. The filters and converters operate over a sample rate range of 4 kHz to 50 kHz.

### FUNCTIONAL DESCRIPTION

### Analog Inputs and Outputs

Figure 8 illustrates the suggested connection diagram for the CS4218. The line level inputs, LIN1 or LIN2 and RIN1 or RIN2, are selected by an internal input multiplexer. This multiplexer is a source selector and is not designed for realtime switching between inputs at the sample rate.

When using the CS4218 as a drop-in replacement for the CS4216, existing recommended circuits (shown in the CS4216 data sheet) may be used as is without any noticeable degradation in performance. Performance may vary with user-specific input circuits and should be checked when contemplating the use of CS4218 in existing CS4216 designs.

Unused analog inputs that are not selected have a very high input impedance, so they may be tied to AGND directly. Unused analog inputs that are selected should be tied to AGND through a 0.1  $\mu$ F capacitor. This prevents any DC current flow.

The analog inputs are single-ended and internally biased to the REFBUF voltage (nominally

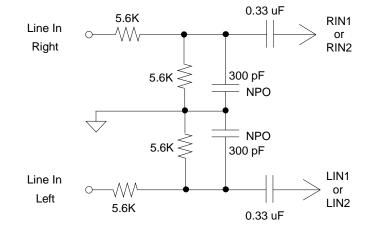

Figure 9. Line Inputs.

2.1 V). The REFBUF output should be buffered if it is to be used for microphone phantom power.

The use of a single-pole RC filter is recommended for use as an external anti-alias filter for the CS4218. The maximum cutoff frequency (lowpass) should not exceed 200 kHz. A lower value for cuttoff frequency may be used, and is dependent upon the application's input bandwidth.

The CS4218 inputs will accept a 1Vrms signal, so a divide by two resistor network will serve as a front-end interface to 2 Vrms line level systems. Figure 9 shows a simple input circuit that includes a gain of 0.5 and the required RC filter. The gain of 0.5 yields a full scale input sensitivity of 2 V<sub>rms</sub> with the CS4218 programmable gain set to 0.

The analog outputs are also single-ended and centered around the REFBUF voltage. AC coupling capacitors of >1  $\mu$ F are recommended. Refer to Figure 8 for the recommended analog output circuit.

When using the CS4218 as a drop-in replacement for the CS4216, the external 600 ohm series resistors on LOUT and ROUT are not required, since they are part of the CS4218 internal circuitry.

In applications where both CS4218 and CS4216 are to be used, a board stuff option should be included in the bill of materials which will allow either a 600-ohm or a 0-ohm resistor to be used externally on both LOUT and ROUT.

## **Offset Calibration**

Both input and output offset voltages are minimized by internal calibration. Offset calibration occurs after exiting a reset or power down condition. During calibration, which takes 194 frames, output data from the ADCs will be all zeros, and will be flagged as invalid. Also, the DAC outputs will be <u>muted</u>. After power down mode or power up, <u>RESET</u> should be held low for a minimum of 50 ms to allow the voltage reference to settle. Changing sample rates in master and slave modes automatically initiates a calibration.

## Input Gain and Output Level Setting

Input gain is adjustable from 0 dB to +22.5 dB in 1.5 dB steps. Output level attenuation is adjustable from 0 dB to -46.5 dB in 1.5 dB steps. Both input and output gain adjustments are internally made on zero-crossings of the analog signal, to minimize "zipper" noise. The gain change automatically takes effect if a zero crossing does not occur within 512 frames.

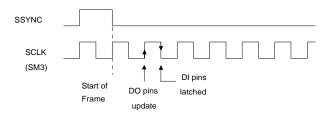

Figure 10. Digital Input/Output Timing

### Muting and the ADC Valid Counter

The mute function allows the the user to turn off the output channels (LOUT and ROUT). Prior to muting, the attenuation should be gradually ramped to maximum (46.5 dB), taking 1.5dB steps. This significantly reduces any audible artifacts that may be heard once muting is enabled. It is the users responsibility to program the serial host to perform the ramping.

The serial data stream contains a "Valid Data" indicator, the ADV bit, for the A/D converters which is low until enough clocks have passed since reset, or low-power (power down mode) operation to have valid A/D data from the filters (i.e., until calibration time plus the full latency of the digital filters has passed.)

## Parallel Digital Input/Output Pins

Parallel digital inputs are general purpose pins whose values are reflected in the serial data output stream to the processor. Parallel digital outputs provide a way to control external devices using bits in the serial data input stream. All parallel digital pins, with the exception of DI1 and DO1, are multifunction and are defined by the serial mode selected. In Serial Mode 3 master modes and Serial Mode 5, two digital inputs and two digital outputs are available. In Serial Mode 3 slave modes, three digital inputs and two digital outputs are available. In Serial Mode 4 only one digital input and digital output exists. Figure 10 shows when the DI pins are latched, and when the DO pins are updated.

## **Reset and Power Down Modes**

Reset places the CS4218 into a known state and must be held low for at least 50 ms after powerup or a hard power down. In reset, the digital outputs are driven low. Reset sets all control data register bits to zero. Changing sample rates in

master and slave modes automatically initiates a calibration.

An RC filter with a time constant greater than 50 ms may be used on the  $\overrightarrow{\text{RESET}}$  pin. The CS4218  $\overrightarrow{\text{RESET}}$  pin has hysterisis to ensure proper resets when using an RC filter.

Hard power down mode may be initiated by bringing the  $\overrightarrow{PDN}$  pin low. All analog outputs will be driven to the REFBUF voltage which will then decay to zero. All digital outputs will be driven low and then will go to a high impedance state. Minimum power consumption will occur if CLKIN is held low. After leaving the power down state,  $\overrightarrow{RESET}$  should be held low for 50 ms to allow the analog voltage reference to settle before calibration is started.

Alternatively, soft power down may be initiated in slave modes by reducing the SCLK frequency below the minimum values shown in Table 1. In soft power down the analog outputs are muted and the serial data from the codec will indicate invalid data and the appropriate error code. The parallel bit I/O is still functional in soft power down mode. This is, in effect, a low power mode with only the parallel bit I/O unit functioning.

| Bits Per Frame         | Minimum SCLK<br>Frequency |

|------------------------|---------------------------|

| For All Modes Except S | M3 Multiplier Sub Mode    |

| 32                     | CLKIN / 96                |

| 64                     | CLKIN / 48                |

| 128                    | CLKIN / 24                |

| 256                    | CLKIN / 12                |

| SM3 Multiplier Sub Mod | e                         |

| 64                     | (16 * CLKIN) / 48         |

| 128                    | (16 * CLKIN) / 24         |

| 256                    | (16 * CLKIN) / 12         |

# Table 1. Soft Power Down Conditions (Slave Modes only)

## **Audio Serial Interface**

In Serial Mode 3 (SM3), the audio serial port uses 4 pins: SDOUT, SDIN, SCLK and SSYNC. SDIN carries the D/A converters' input data and control bits. Input data is ignored for frames not allocated to the selected CS4218. SDOUT carries the A/D converters' output data and status bits. SDOUT goes to a high-impedance state during frames not allocated to the selected CS4218. SCLK clocks data in to and out of the CS4218. SSYNC indicates the start of a frame and/or sub-frame. SCLK and SSYNC must be synchronous to the master clock.

Serial Mode 4 (SM4) is similar to SM3 with the exception of the control information. In Serial Mode 4, the control information is entered through a separate asynchronous control port. Therefore, the audio serial port only contains audio data, which reduces the number of bits on the audio port from 64 to 32 per codec. This is useful for lower bit rate serial hosts.

Serial Mode 5 (SM5) is compatible with the  $I^2S^{TM}$  serial data protocol. SM5 is a Master mode only. As in SM3, 4 pins are used: SDOUT, SDIN, SCLK, and SSYNC.

The serial port protocol is based on frames consisting of 1, 2, or 4 sub-frames. The frame rate is the system sample rate. Each sub-frame is used by one CS4218 device. Up to 4 CS4218s may be attached to the same serial control lines. SFS1 and SFS2 are tied low or high to indicate to each CS4218 which sub-frame is allocated for it to use.

## Serial Data Format

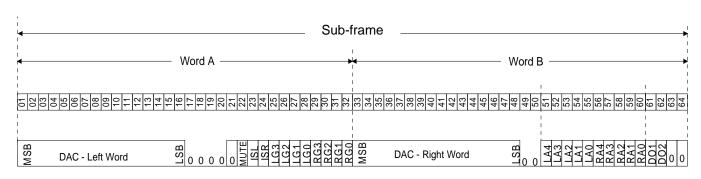

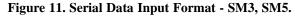

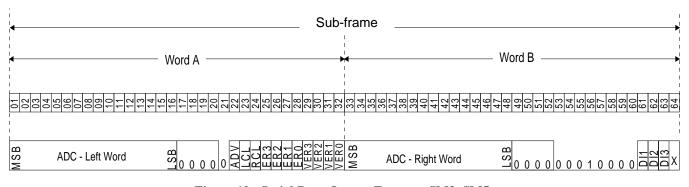

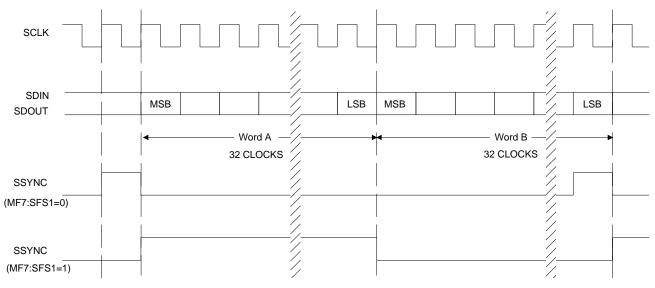

In SM3 and SM5, a sub-frame is 64 bits in length and consists of two 16-bit audio values and two 16-bit control fields. In SM4 a subframe is 32 bits in length and only contains the two 16-bit audio fields; the control data is loaded through a separate port. The audio data is MSB

first, 2's complement format. Sub-frame bit assignments are shown in Figure 13. Control data bits all reset to zero.

### **CS4218 SERIAL INTERFACE MODES**

The CS4218 has three serial port modes, selected by the SMODE1, SMODE2 and SMODE3 pins. In all modes, CLKIN, SCLK and SSYNC must be derived from the same clock source. SM3 was designed as an easy interface to general purpose DSPs and provides features such as master and slave sub-modes and variable frame sizes. SM4 is similar to SM3 but splits the audio data from the control data thereby reducing the audio serial bus bandwidth by half. The control data is transmitted through a control serial port in SM4. SM5 is compatible with the  $I^2S$  serial data protocol.

Table 2 lists the three serial port modes available, along with some of the differences between modes. The first three columns in Table 2 select the serial mode. The "SCLK Bit Center" column indicates whether SCLK is rising or falling in the center of a bit period. The "Sub-frame Width" column indicates how many bits are in an individual codec's sub-frame. In SM3 and SM4, the number of bits per frame is programmable. In all modes, SCLK and SSYNC must be synchronous to the master clock. The last column in Table 2 lists the master frequencies used by the codec. In the SM3 Multiplier sub-modes, the master CLKIN is multiplied internally by 16, so a 16xFs input clock must be provided.

#### SERIAL MODE 3, (SM3)

Serial Mode 3, Master and Slave sub-modes are enabled by setting SMODE3 = 0, SMODE2 = 1and SMODE1 = 0. SM3 Multiplier Sub-Modes are enabled by setting SMODE 3 = 0, SMODE 2 = 0, and SMODE 1 = 0. Serial Mode 3 is designed to interface easily to DSPs.

Figure 11 illustrates the serial data in, SDIN, sub-frame for all SM3 sub-modes. Figure 12 also illustrates the serial data out, SDOUT, subframe for all SM3 sub-modes. Figure 13 shows sub-frame bit definitions.

In SM3 master sub-modes, MF5:DO2 is a general purpose output and MF6:DI2 is a general purpose input. The other six multifunction pins are used to select sub-modes under SM3. In SM3 slave sub-modes, MF3:F3 is configured as an additional general purpose input.

SM3 is divided into four sub-modes, Master (SM3-M), Slave (SM3-S), Multiplier Master (SM3-MM), and Multiplier Slave (SM3-MS). SM3-M and SM3-S are identical to the CS4216 SM3 Master and Slave sub-modes, respectively. In SM3-M and SM3-MM sub-modes, the CS4218 generates SSYNC and SCLK, while in SM3-S and SM3-MS sub-modes SSYNC and

| SMC | DDE F | PINS | Serial | SCLK Bit     | Sub-frame            | Bits per               | SCLK &       | Master                 |

|-----|-------|------|--------|--------------|----------------------|------------------------|--------------|------------------------|

| 3   | 2     | 1    | Mode   | Center       | Width                | Frame (BPF)            | SSYNC        | Frequency              |

| 0   | 0     | 0    | SM3*   | Falling      | 64 bits              | 64/128/256             | Master/Slave | CLKIN = 16xFs          |

| 0   | 0     | 1    | SM5    | Rising       | 64 bits              | 64                     | Master       | CLKIN = 256xFs         |

| 0   | 1     | 0    | SM3    | Falling      | 64 bits              | 64/128/256             | Master/Slave | CLKIN or SCLK = 256×Fs |

| 0   | 1     | 1    | I      | Factory Test | mode                 |                        |              |                        |

| 1   | х     | х    | SM4    | Falling      | 32 bits <sup>†</sup> | 32/64/128 <sup>†</sup> | Master/Slave | CLKIN = 256×Fs         |

<sup>†</sup>Contains audio data only. Control information is entered through a separate serial port. \* SM3 Multiplier sub-modes.

#### **Table 2. Serial Port Modes**

SCLK must be generated externally. When the codec is the serial port master, the serial port signal transitions are controlled with respect to the internal analog sampling clock to minimize the amount of digital noise coupled into the analog section. Since SSYNC and SCLK are externally derived when the codec slaves to the serial port, optimum noise management cannot be obtained; therefore, master modes should be used whenever possible. Multiplier sub-modes are identical to the SM3 modes except the master clock, CLKIN, is internally multiplied by 16. A 0.47  $\mu$ F capacitor must be tied to the FILT pin when using the Multiplier sub-modes.

#### Master Clock Frequency

In SM3-M and SM3-S sub-modes, the master clock, CLKIN, must be  $256 \times Fs_{max}$ . For example, given a 48 kHz maximum sample frequency, the master clock frequency must be 12.288 MHz. In SM3-MM and SM3-MS sub-modes, CLKIN must be  $16xFs_{max}$ . For example, given a 48 kHz maximum sample frequency, the master clock frequency must be 768 kHz. SCLK and SSYNC must be synchronous to the master clock.

| 13 and SM5                |                                    |                                                                                                                                                                                                                                                            |                                       |                                           |                                                                                                                                                                                                                                                                    |

|---------------------------|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit(s)                    | Symbol                             | Description                                                                                                                                                                                                                                                | Bit(s)                                | Symbol                                    | Description                                                                                                                                                                                                                                                        |

| 1-16                      | DAC-LEFT                           | Audio Data, DAC Left<br>2's Complement data,<br>MSB first (Bit 1 = MSB)                                                                                                                                                                                    | 33-48                                 | DAC-RIGHT                                 | Audio Data, DAC Right<br>2's Complement data,<br>MSB first (Bit 33 = MSB)                                                                                                                                                                                          |

| 17-21                     | unused                             | Unused, write with 0's                                                                                                                                                                                                                                     | 49,50                                 | unused                                    | Unused, write with 0's                                                                                                                                                                                                                                             |

| 22                        | MUTE                               | Mute DAC Outputs<br>0 = Outputs ON<br>1 = Outputs MUTED                                                                                                                                                                                                    | 51 - 55                               | LA4 - LA0                                 | Left Output Attenuation<br>1.5dB Increments.<br>00000 = no atten. (0dB)<br>11111 = 46.5dB atten.                                                                                                                                                                   |

| 23                        | ISL                                | Input Mux, Left Select<br>0 = LIN1<br>1 = LIN2                                                                                                                                                                                                             | 56 - 60                               | RA4 - RA0                                 | Right Output Attenuation<br>1.5dB Increments.<br>00000 = no atten. (0dB)<br>11111 = 46.5dB atten.                                                                                                                                                                  |

| 24                        | ISR                                | Input Mux, Right Select<br>0 = RIN1<br>1 = RIN2                                                                                                                                                                                                            | 61                                    | DO1                                       | Digital Output 1<br>0 = Output LOW<br>1 = Output HIGH                                                                                                                                                                                                              |

| 25-28                     | LG3 - LG0                          | Left Input Gain<br>1.5dB Increments.<br>0000 = No gain (0dB)<br>1111 = 22.5 dB gain                                                                                                                                                                        | 62                                    | DO2                                       | Digital Output 2<br>0 = Output LOW<br>1 = Output HIGH                                                                                                                                                                                                              |

| 29-32                     | RG3 - RG0                          | Right Input Gain<br>1.5dB Increments.<br>0000 = No gain (0dB)<br>1111 = 22.5 dB gain                                                                                                                                                                       | 63,64                                 | unused                                    | Unused, write with 0's                                                                                                                                                                                                                                             |

| 13 and SM5                | Subframe Bit D                     | efinitions for SDOUT                                                                                                                                                                                                                                       |                                       | T                                         | 1                                                                                                                                                                                                                                                                  |

| D(t/c)                    | <b>•</b> • •                       | Description                                                                                                                                                                                                                                                | $\mathbf{D}_{\mathbf{H}}(\mathbf{a})$ | 0                                         | Description                                                                                                                                                                                                                                                        |

| Bit(s)                    | Symbol                             | Description                                                                                                                                                                                                                                                | Bit(s)                                | Symbol                                    | Description                                                                                                                                                                                                                                                        |

| <b>Вії(s)</b><br>1-16     | ADC-LEFT                           | Audio Data, ADC Left<br>2's Complement data,<br>MSB first (Bit 1 = MSB)                                                                                                                                                                                    | 29-32                                 | VER3-VER0                                 |                                                                                                                                                                                                                                                                    |

|                           |                                    | Audio Data, ADC Left<br>2's Complement data,                                                                                                                                                                                                               |                                       |                                           | CS4218 Version Number<br>0000 = Rev A<br>1000 = Rev B and later<br>Audio Data, ADC Right<br>2's Complement data,                                                                                                                                                   |

| 1-16                      | ADC-LEFT                           | Audio Data, ADC Left<br>2's Complement data,<br>MSB first (Bit 1 = MSB)<br>These bits can be 0 or 1<br>ADC Valid Data<br>0 = Invalid ADC data                                                                                                              | 29-32                                 | VER3-VER0                                 | CS4218 Version Number<br>0000 = Rev A<br>1000 = Rev B and later<br>Audio Data, ADC Right<br>2's Complement data,<br>MSB first (Bit 33 = MSB)                                                                                                                       |

| 1-16<br>17-21             | ADC-LEFT<br>reserved               | Audio Data, ADC Left<br>2's Complement data,<br>MSB first (Bit 1 = MSB)<br>These bits can be 0 or 1<br>ADC Valid Data                                                                                                                                      | 29-32<br>33-48                        | VER3-VER0<br>ADC-RIGHT                    | CS4218 Version Number<br>0000 = Rev A<br>1000 = Rev B and later<br>Audio Data, ADC Right<br>2's Complement data,<br>MSB first (Bit 33 = MSB)                                                                                                                       |

| 1-16<br>17-21<br>22       | ADC-LEFT<br>reserved<br>ADV        | Audio Data, ADC Left<br>2's Complement data,<br>MSB first (Bit 1 = MSB)<br>These bits can be 0 or 1<br>ADC Valid Data<br>0 = Invalid ADC data<br>1 = Valid ADC data<br>ADC Left Clipping<br>0 = Normal                                                     | 29-32<br>33-48<br>49-60               | VER3-VER0<br>ADC-RIGHT<br>reserved        | CS4218 Version Number<br>0000 = Rev A<br>1000 = Rev B and later<br>Audio Data, ADC Right<br>2's Complement data,<br>MSB first (Bit 33 = MSB)<br>These bits can be 0 or 1<br>Digital Input 1<br>0 = Input LOW                                                       |

| 1-16<br>17-21<br>22<br>23 | ADC-LEFT<br>reserved<br>ADV<br>LCL | Audio Data, ADC Left<br>2's Complement data,<br>MSB first (Bit 1 = MSB)<br>These bits can be 0 or 1<br>ADC Valid Data<br>0 = Invalid ADC data<br>1 = Valid ADC data<br>ADC Left Clipping<br>0 = Normal<br>1 = Clipping<br>ADC Right Clipping<br>0 = Normal | 29-32<br>33-48<br>49-60<br>61         | VER3-VER0<br>ADC-RIGHT<br>reserved<br>DI1 | CS4218 Version Number<br>0000 = Rev A<br>1000 = Rev B and later<br>Audio Data, ADC Right<br>2's Complement data,<br>MSB first (Bit 33 = MSB)<br>These bits can be 0 or 1<br>Digital Input 1<br>0 = Input LOW<br>1 = Input HIGH<br>Digital Input 2<br>0 = Input LOW |

## Figure 13. SM3 / SM5 Subframe, Bit definitions

## Master Sub-Mode (SM3-M)

Master sub-mode is selected by setting MF4:MA = 1, which configures SSYNC and SCLK as outputs from the CS4218. During power down, SSYNC and SCLK are driven high impedance, and during reset they both are driven low. In Master sub-mode the number of bits per frame determines how many codecs can occupy the serial bus and is illustrated in Figure 14.

## Bits Per Frame (Master Sub-Modes)

MF8:SFS2 selects the number of bits per frame. The two options are MF8:SFS2 = 1 which selects 128 bits per frame, and MF8:SFS2 = 0 which selects 64 bits per frame.

Selecting 128 bits per frame (MF8:SFS2 = 1) allows two CS4218s to operate from the same serial bus since each codec requires 64 bit periods. The sub-frame used by an individual codec is selected using MF7:SFS1. MF7:SFS1 = 0 selects sub-frame 1 which is the first 64 bits following the SSYNC pulse. MF7:SFS1 = 1 selects sub-frame 2 which is the last 64 bits of the frame.

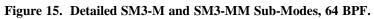

Selecting 64 bits per frame (MF8:SFS2 = 0) allows only one CS4218 to occupy the serial port. Since there is only one sub-frame (which is equal to one frame), MF7:SFS1 is defined differently in this mode. MF7:SFS1 selects the format of SSYNC. MF7:SFS1 = 0 selects an SSYNC pulse one SCLK period high, directly preceding the data as shown in the center portion of Figure 14. This format is used for all other master and slave sub-modes in SM3. If MF7:SFS1 = 1, an alternate SSYNC format is chosen in which SSYNC is high during the entire Word A (32 bits), which includes the left sample, and low for the entire Word B (32 bits), which includes the right sample. This alternate format for SSYNC is illustrated in the bottom portion of Figure 14 and is only available in SM3-M and SM3-MM sub-modes with 64 bits per frame. A more detailed timing diagram for the 64 bits-perframe master sub-modes is shown in Figure 15.

# Sample Frequency Selection (Master Sub-Modes)

In SM3-M and SM3-MM sub-modes, the multifunction pins MF1:F1, MF2:F2, and MF3:F3 are used to select the sample frequency divider. Table 3 lists the decoding for the sample frequency select pins where the sample frequency selected is CLKIN/N. Also shown are the sample frequencies obtained by using one of two example master clocks: either 12.288 MHz or 11.2896 MHz. Changing sample frequency automatically initiates a calibration cycle.

| MF1: | MF2: | MF3: | Ν    | Fs (kHz)<br>with CLKIN<br>or 16xCLKIN |                |

|------|------|------|------|---------------------------------------|----------------|

| F1   | F2   | F3   |      | 12.288<br>MHz                         | 11.2896<br>MHz |

| 0    | 0    | 0    | 256  | 48.00                                 | 44.10          |

| 0    | 0    | 1    | 384  | 32.00                                 | 29.40          |

| 0    | 1    | 0    | 512  | 24.00                                 | 22.05          |

| 0    | 1    | 1    | 640  | 19.20                                 | 17.64          |

| 1    | 0    | 0    | 768  | 16.00                                 | 14.70          |

| 1    | 0    | 1    | 1024 | 12.00                                 | 11.025         |

| 1    | 1    | 0    | 1280 | 9.60                                  | 8.82           |

| 1    | 1    | 1    | 1536 | 8.00                                  | 7.35           |

|       | •             |                            | ME n<br>K Periods |             | 4       | — FRAME    | (n+2) — |                   | FRAME (n+3) |          |                                                       |

|-------|---------------|----------------------------|-------------------|-------------|---------|------------|---------|-------------------|-------------|----------|-------------------------------------------------------|

|       | Sub-fra       | ame 1                      | Sub-fra           | me 2        | Sub-fra | ame 1      | Sub-fra | ame 2             |             |          | MF8: MF7: Sub-                                        |

| DATA  | Word A        | Word B                     | Word A            | Word B      | Word A  | Word B     | Word A  | Word B            | Word A      | Word B   | SFS2 SFS1 frame                                       |

|       |               |                            |                   | י<br>י<br>ד |         |            |         |                   |             |          | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ |

| SSYNC |               |                            |                   |             |         |            |         |                   | 1           |          |                                                       |

|       | I             |                            | I                 | 1           |         | 1          |         | I                 |             |          |                                                       |

|       |               | AME n →<br>K Periods       | FRAM              | E (n+1)     | ← FRAM  | IE (n+2) → | ← FRAM  | 1E (n+3) <b>→</b> | FRA         | ME (n+4) |                                                       |

|       | Sub-fra       | ame 1                      | Sub-fra           | me 1        | Sub-fra | ame 1      | Sub-fra | ime 1             | Sub-fra     | ame 1    | MF8: MF7: Sub-                                        |

| DATA  | Word A        | Word B                     | Word A            | Word B      | Word A  | Word B     | Word A  | Word B            | Word A      | Word B   | SFS2 SFS1 frame                                       |

| _     |               | _                          | 1                 | <br> <br> - |         | <br> <br>  |         |                   | 1           |          | 0 0 1                                                 |

| SSYNC |               |                            | -                 |             |         |            |         |                   | -           |          |                                                       |

|       | FRA<br>64 SCL | ME n <b>→</b><br>K Periods | FRAM              | E (n+1) —   | ← FRAM  | IE (n+2)   | ← FRAM  | E (n+3) →         | FRAI        | ME (n+4) |                                                       |

|       | Sub-fra       | me 1                       | Sub-fra           | me 1        | Sub-fra | ame 1      | Sub-fra | ime 1             | Sub-fra     | ame 1    | MF8: MF7: Sub-                                        |

| DATA  | Word A        | Word B                     | Word A            | Word B      | Word A  | Word B     | Word A  | Word B            | Word A      | Word B   | SFS2 SFS1 frame                                       |

| SSYNC |               |                            | <br>              | <br> <br>   |         |            |         |                   | <br>        | ]        |                                                       |

Figure 14. SM3-M and SM3-MM Sub-Modes.

### Slave Sub-Mode (SM3-S)

In SM3, Slave sub-mode is selected by setting MF4:MA = 0 which configures SSYNC and SCLK as inputs to the CS4218. These two signals must be externally derived from CLKIN. In SM3-S and SM3-MS sub-modes, the phase relationship between SCLK/SSYNC and CLKIN cannot be controlled since SCLK and SSYNC are externally derived. Therefore, the noise performance may be slightly worse than when using the master sub-modes.

The number of sub-frames on the serial port is selected using MF1:F1 and MF2:F2. In SM3-S and SM3-MS sub-modes, MF3:F3 works as an additional general purpose input DI3. Figures 16 through 18 illustrate the SM3-S and SM3-MS sub-mode formats.

### Bits per Frame (Slave Sub-Modes)

In slave sub-modes, MF1:F1 and MF2:F2 select the number of bits per frame, which determines how many CS4218s can occupy one serial port. Table 4 lists the decoding for MF1:F1 and MF2:F2.

When set for 64 SCLKs per frame, one device occupies the entire frame; therefore, a sub-frame is equivalent to a frame. MF7:SFS1 and MF8:SFS2 must be set to zero.

When set for 128 SCLKs per frame, two devices can occupy the serial port, with MF7:SFS1 se-

| MF1:<br>F1 | MF2:<br>F2 | Bits per<br>Frame | Sample Frequency/<br>SCLK     |

|------------|------------|-------------------|-------------------------------|

| 0          | 0          | 64                | ratio to CLKIN sensed         |

| 0          | 1          | 128               | ratio to CLKIN sensed         |

| 1          | 0          | 256               | ratio to CLKIN sensed         |

| 1          | 1          | 256               | fixed <sup>†</sup> . = 256×Fs |

<sup>†</sup> SCLK is master clock. CLKIN is not used. Not available in Multiplier Slave sub-mode.

Table 4. SM3-S/SM3-MS, Bits per Frame.

lecting the particular sub-frame. MF8:SFS2 must be set to zero. See Figure 17.

When set for 256 SCLKs per frame (MF1:F1, MF2:F2 = 10), four devices can occupy the serial port. In this format both MF8:SFS2 and MF7:SFS1 are used to select the particular sub-frame.

In all three of the above slave sub-mode formats. the frequency of the incoming SCLK signal, in relation to the master clock provided on the CLKIN pin, determines the sample frequency. The CS4218 determines the ratio of SCLK to CLKIN and sets the internal operating frequency accordingly. Table 5 lists the SCLK to CLKIN frequency ratio used to determine the codec's sample frequency. To obtain a given sample frequency, SCLK must equal CLKIN divided by the number in the table, based on the number of bits per frame. As an example for SM3-S, assuming 64 BPF (bits per frame) and CLKIN = 12.288 MHz, if a sample frequency of 24 kHz is desired, SCLK must equal CLKIN divided by 8 or 1.536 MHz. A change in sample rate automatically initiates a calibration cycle.

When MF1:F1 = MF2:F2 = 1, SCLK is used as the master clock and is assumed to be 256 times the sample frequency. In this mode, CLKIN is

| SCLK 1 |     | N Ratio | Fs (kHz)   | Fs (kHz)    |

|--------|-----|---------|------------|-------------|

| BPF    | BPF | BPF     | with CLKIN | with CLKIN  |

| 050    | 400 | 64      |            | or 16xCLKIN |

| 256    | 128 | 64      | 12.288 MHZ | 11.2896 MHz |

| 1      | 2   | 4       | 48.00      | 44.10       |

| 1.5    | 3   | 6       | 32.00      | 29.40       |

| 2      | 4   | 8       | 24.00      | 22.05       |

| 2.5    | 5   | 10      | 19.20      | 17.64       |

| 3      | 6   | 12      | 16.00      | 14.70       |

| 4      | 8   | 16      | 12.00      | 11.025      |

| 5      | 10  | 20      | 9.60       | 8.82        |

| 6      | 12  | 24      | 8.00       | 7.35        |

Table 5.SM3-S/SM3-MS, Fs Select.

# CRYSTAL

ignored and the sample frequency is linearly scaled with SCLK. (The CLKIN pin must be tied low.) This mode also fixes SCLK at 256 bits per frame with MF7:SFS1 and MF8:SFS2 selecting the particular sub-frame. This master clocking option is not available in the multiplier (SM3-MS) sub-mode.

# Multiplier Sub-Modes (SM3-MM and SM3-MS)

The SM3 Multiplier sub-modes are identical to the SM3-M and SM3-S sub-modes with the following exceptions:

- Set SMODE1 = SMODE2 = SMODE3 = 0. This selects SM3 Multiplier mode.

- CLKIN must be 16\*Fs, as opposed to 256\*Fs used for SM3-M and SM3-S.

- A 0.47uF capacitor must be connected to the FILT pin as shown in Figure 8.

Master / Slave setup, frame formats, and sample rate selection are identical to SM3-M and SM3-S. Please note that the MF1:F1 = MF2:F2 = 1 slave configuration supported by the SM3-S submode it not available in SM3-MS sub-mode.

#### Figure 16. SM3-S and SM3-MS - 64 BPF; MF1:F1, MF2:F2 = 00

|         |         |        |          | ← FRAME (n+1) → |         |        |          | FRAM   | IE (n+2) |        |                  |      |            |

|---------|---------|--------|----------|-----------------|---------|--------|----------|--------|----------|--------|------------------|------|------------|

|         | Sub-fra | me 1   | Sub-frar | me 2            | Sub-fra | ime 1  | Sub-frai | me 2   | Sub-fra  | me 1   | MF8:             | MF7: |            |

| DATA    | Word A  | Word B | Word A   | Word B          | Word A  | Word B | Word A   | Word B | Word A   | Word B | <u>SFS2</u><br>0 | SFS1 | frame<br>1 |

|         |         |        |          |                 |         |        |          |        |          |        | 0                | 1    | 2          |

| SSYNC _ |         |        |          |                 |         |        |          |        |          |        |                  |      |            |

#### Figure 17. SM3-S and SM3-MS - 128 BPF; MF1:F1, MF2:F2 = 01

|       | FRAME n FRAME n 256 SCLK Periods |                                                 |        |        |        |        |        |        |        | -      |        | MF7:<br>SFS1 |   |

|-------|----------------------------------|-------------------------------------------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------------|---|

|       | Sub-fra                          | Sub-frame 1 Sub-frame 2 Sub-frame 3 Sub-frame 4 |        |        |        |        |        |        |        | me 1   | 0      | 0            | 1 |

| DATA  | Word A                           | Word B                                          | Word A | Word B | Word A | Word B | Word A | Word B | Word A | Word B | 0      | 1            | 2 |

| DATA  |                                  |                                                 |        |        |        |        |        |        |        | J      | 1<br>1 | 0            | 3 |

| SSYNC |                                  |                                                 |        |        |        |        |        |        |        |        |        |              |   |

#### Figure 18. SM3-S and SM3-MS - 256 BPF; MF1:F1, MF2:F2 = 10

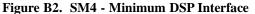

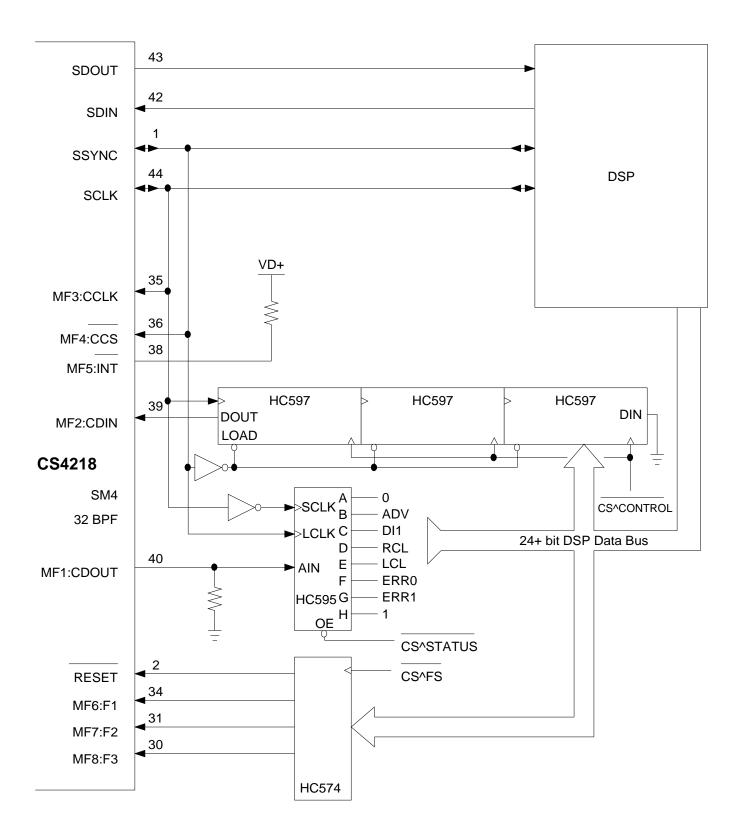

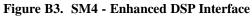

#### SERIAL MODE 4, (SM4)

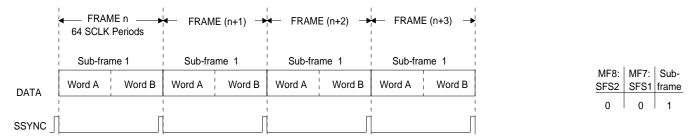

Serial Mode 4 is enabled by setting SMODE3 = 1. Both Master and Slave submodes are available and are selected by setting the SMODE2 and SMODE1 pins as shown in Table 6. In Master sub-mode, the phase relationship between SCLK/SSYNC and CLKIN is controlled to minimize digital noise coupling into the analog section. Therefore, Master submode may yield slightly better noise performance than Slave sub-mode. In Slave sub-mode, SCLK and SSYNC must be synchronous to CLKIN.

In serial mode 4, the CLKIN frequency must be 256 times the highest sample frequency needed. SM4 differs from SM3 and SM5 in that SM4 splits the audio data from the control data, with the control data on an independent serial port. This reduces the audio serial bus bandwidth by half, providing an easier interface to low-cost DSPs. The audio serial port sub-frame is illustrated in Figure 19 for SM4.

| SMODE1 | SMODE2               | SM4, Sub-Mode        |  |  |

|--------|----------------------|----------------------|--|--|

| 0      | 0                    | Master, 32 BPF       |  |  |

| 0      | 1                    | Slave, 128/64/32 BPF |  |  |

| 1      | 0 Master, 64 BPF, TS |                      |  |  |

| 1      | 1                    | Master, 64 BPF, TS2  |  |  |

| I | Slave, 120/04/32 DFF |

|---|----------------------|

| 0 | Master, 64 BPF, TS1  |

| 1 | Master, 64 BPF, TS2  |

|   |                      |

#### Master Sub-Mode (SM4)

Master sub-mode configures SSYNC and SCLK as outputs from the CS4218. During power down, SSYNC and SCLK are driven high impedance, and during reset they both are driven low. There are two SM4 Master sub-modes. One allows 32 bits per frame and the other allows 64 bits per frame. As shown in Table 6, the SMODE1 and SMODE2 pins select the particular Master sub-mode (as well as the Slave sub-mode). When SMODE1 is set to zero. SMODE2 selects either Master sub-mode with 32-bit frames, or Slave sub-mode.

SMODE1.SMODE2 = 00 selects Master submode where a frame = sub-frame = 32 bits. This sub-mode allows only one codec on the audio serial bus, with the first 16 bits being the left channel and the second 16 bits being the right channel. The Appendix B section contains more information on low-cost implementations of this sub-mode.

SMODE1 = 1 selects Master sub-mode with a frame width of 64 bits. This sub-mode allows up to two codecs to occupy the same bus. SMODE2 is now used to select the particular time slot. If SMODE2 = 0 the codec selects time slot 1. which is the first 32 bits. If SMODE2 = 1 the codec selects time slot 2, which is the second 32 bits.

Figure 19. SM4-Audio Serial Port, 32 BPF

In Master sub-mode, multifunction pins MF6:F1, MF7:F2, and MF8:F3 select the sample frequency as shown in Table 7. This table indicates how to obtain standard audio sample frequencies given one of two CLKIN frequencies: 12.288 MHz or 11.2896 MHz. Other CLKIN frequencies may be used with the corresponding sample frequencies being CLKIN/N. A change in sample rate automatically initiates a calibration cycle.

| MF6: | MF7: | MF8: | N    | Fs (kHz)<br>with CLKIN |                |

|------|------|------|------|------------------------|----------------|

| F1   | F2   | F3   |      | 12.288<br>MHz          | 11.2896<br>MHz |

| 0    | 0    | 0    | 256  | 48.00                  | 44.10          |

| 0    | 0    | 1    | 384  | 32.00                  | 29.40          |

| 0    | 1    | 0    | 512  | 24.00                  | 22.05          |

| 0    | 1    | 1    | 640  | 19.20                  | 17.64          |

| 1    | 0    | 0    | 768  | 16.00                  | 14.70          |

| 1    | 0    | 1    | 1024 | 12.00                  | 11.025         |

| 1    | 1    | 0    | 1280 | 9.60                   | 8.82           |

| 1    | 1    | 1    | 1536 | 8.00                   | 7.35           |

#### Table 7. SM4-Master, Fs Select

#### Slave Sub-Mode (SM4)

In SM4, Slave sub-mode is selected by setting SMODE1, SMODE2 = 01. This mode configures SSYNC and SCLK as inputs to the CS4218. These two signals must be externally derived from CLKIN. Since the CS4218 has no control over the phase relationship of SSYNC and SCLK to CLKIN, the noise performance in Slave sub-mode may be slightly worse than when using Master sub-mode. The CS4218 internally sets the sample frequency by sensing the ratio of SCLK to CLKIN; therefore, for a given CLKIN frequency, the sample frequency is selected by changing the SCLK frequency. A change in sample rate automatically initiates a calibration cycle. Table 9 shows the sample rates generated with two example clocks.

SM4-Slave allows up to four codecs to occupy the same audio serial port. Table 8 lists the pin configurations required to set the serial audio port up for 32, 64, or 128 bits-per-frame (BPF). Since each codec requires one sub-frame of 32 bits, 64 bits-per-frame allows up to two codecs to occupy the same audio serial port, and 128 bits-per-frame allows up to four codecs to occupy the same audio serial port. When set up for more than one codec on the bus, other pins are needed to select the particular time slot (TS) associated with each codec. MF8:SFS2 selects the time slot when in 64 BPF mode, and MF8:SFS2 and MF7:SFS1 select one of four time slots when in 128 bits-per-frame mode. Table 8 lists the decoding for time slot selection.

| MF6:<br>F1 | MF7:<br>SFS1 | MF8:<br>SFS2 | Bits Per<br>Frame<br>(BPF) | Time<br>Slot<br>(TS) |

|------------|--------------|--------------|----------------------------|----------------------|

| 0          | 0            | 0            | 32                         | 1                    |

| 0          | 0            | 1            | Rese                       | erved                |

| 0          | 1            | 0            | 64                         | 1                    |

| 0          | 1            | 1            | 64                         | 2                    |

| 1          | 0            | 0            | 128                        | 1                    |

| 1          | 1            | 0            | 128                        | 2                    |

| 1          | 0            | 1            | 128                        | 3                    |

| 1          | 1            | 1            | 128                        | 4                    |

Table 8. SM4-Slave, Audio Port BPF & TS Select

| SCLK 1     | to CLKII  | N Ratio   | Fs (kHz)                 | Fs (kHz)                  |

|------------|-----------|-----------|--------------------------|---------------------------|

| BPF<br>128 | BPF<br>64 | BPF<br>32 | with CLKIN<br>12.288 MHz | with CLKIN<br>11.2896 MHz |

| 2          | 4         | 8         | 48.00                    | 44.10                     |

| 3          | 6         | 12        | 32.00                    | 29.40                     |

| 4          | 8         | 16        | 24.00                    | 22.05                     |

| 5          | 10        | 20        | 19.20                    | 17.64                     |

| 6          | 12        | 24        | 16.00                    | 14.70                     |

| 8          | 16        | 32        | 12.00                    | 11.025                    |

| 10         | 20        | 40        | 9.60                     | 8.82                      |

| 12         | 24        | 48        | 8.00                     | 7.35                      |

Table 9. SM4-Slave, Fs Select.

## Serial Control Port (SM4)

Serial Mode 4 separates the audio data from the control data. Since control data such as gain and attenuation do not change often, this mode reduces the bandwidth needed to support the audio serial port.

The control information is entered through a separate port that can be asynchronous to the audio port and only needs to be updated when changes in the control data are needed. After a reset or power down, the control port must be written once to initialize it if the port will be accessed to read or write control bits. This initial write is considered a "dummy" write since the data is ignored by the codec. A second write is needed to configure the codec as desired. Then, the control port only needs to be written to when a change is desired, or to obtain the status information. The control port does not function if the master clock is not operating. When the control port is used asynchronously to the audio port, the noise performance may be slightly degraded due to the asynchronous digital noise.

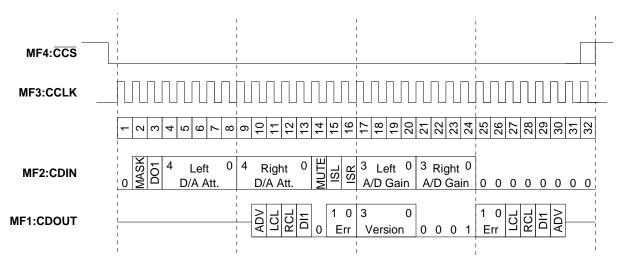

Since control data does not need to be accessed each audio frame, an interrupt pin, MF5: INT, is included in this mode and will go low when status has changed. The control port serial data format is illustrated in Figure 20. The control port uses one of the multifunction pins as a chip select line, MF4:CCS, that must be low for entering control data. Although only 23 bits contain useful data on MF2:CDIN, a minimum of 31 bits must be written. If more than 31 bits are written without toggling MF4:CCS, only the first 31 are recognized. MF1:CDOUT contains status information that is output on the rising edge of MF3:CCLK. Status information is repeated at the end of the frame, bits 25 through 30, to allow a simple 8-bit shift and latch register to store the most important status information using the rising edge of MF4:CCS at the latch control (see Appendix B).

## Interrupt Pin - MF5: INT

Serial Mode 4 defines the multifunction pin MF5: $\overline{INT}$  as an open-collector interrupt pin. In SM4, this pin requires a pullup resistor and will go low when the ADV bit or DI1 pin change, or a rising edge on the LCL or RCL bits occurs, or by exiting an SCLK out of range condition (Error = 3). The interrupt may be masked by setting the MASK bit in the control serial data port. MF5: $\overline{INT}$  is reset by reading the control serial port.

Figure 20. SM4 - Control Serial Port

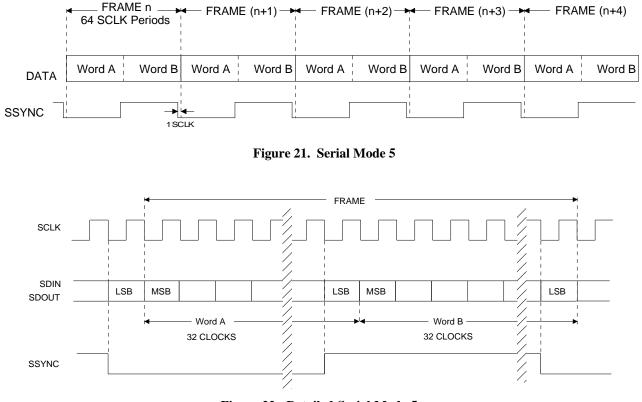

The Serial Mode 5 is compatible with the Phillips  $I^2S$  serial protocol. SM5 is enabled by setting SMODE3 = 0, SMODE2 = 0, and SMODE1 = 1. This is a master mode fixed at 64 BPF.

Figure 21 shows the frame format of the SM5. Figure 22 shows the detailed frame format.

The multi-function pins MF4, MF7, and MF8 are not used in this mode. MF4 should be tied to VD, and MF7 and MF8 should be tied to ground.

Figures 11 & 12 illustrate the serial data in, SDIN, and serial data out, SDOUT, sub-frames for SM5.

The multifunction pins MF1:F1, MF2:F2, and MF3:F3 are used to select the sample frequency divider. Table 3 lists the decoding for the sample frequency select pins where the sample frequency selected is CLKIN/N. Also shown are the sample frequencies obtained by using one of two example master clocks. A change in sample rate will automatically initiate a calibration cycle.

Figure 22. Detailed Serial Mode 5.

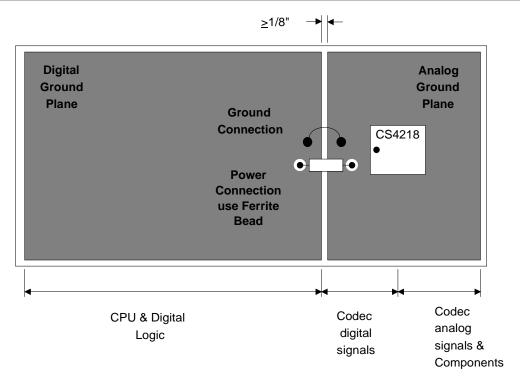

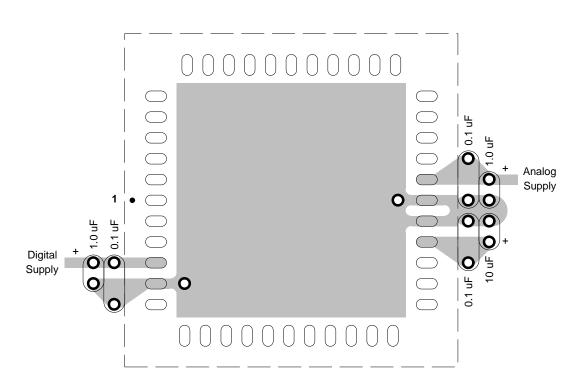

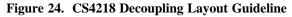

## **Power Supply and Grounding**

The CS4218, along with associated analog circuitry, should be positioned in an isolated section of the circuit board, and have its own, separate, ground plane. On the CS4218, the analog and digital grounds are internally connected; therefore, the AGND and DGND pins must be externally connected with no impedance between them. The best solution is to place the entire chip on a solid ground plane as shown in Figure 23. Preferably, it should also have its own power plane. The +5V (or +3.3V) supply must be connected to the CS4218 via a ferrite bead, positioned closer than 1" to the device. If using +5V for VD, the VA supply can be derived from VD, as shown in Figure 8. Alternatively, a separate +5V analog supply may be used for VA, in which case, the 2.0  $\Omega$  resistor between VA and VD should be removed. A single connection between the CS4218 ground (analog ground) and the board digital ground should be positioned as shown in Figure 23.