### **HCTL-1100 Series**

# General Purpose Motion Control ICs

# AVAGO

# **Data Sheet**

### Description

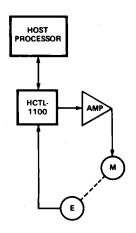

The HCTL-1100 series is a high performance, general purpose motion control IC, fabricated in Avago CMOS technology. It frees the host processor for other tasks by performing all the time-intensive functions of digital motion control. The programmability of all control parameters provides maximum flexibility and quick design of control systems with a minimum number of components. In addition to the HCTL-1100, the complete control system consists of a host processor to specify commands, an amplifier, and a motor with an incremental encoder (such as the HP HEDS-5XXX, -6XXX, -9XXX series). No analog compensation or velocity feedback is necessary.

### **Features**

- · Low power CMOS

- · PDIP and PLCC versions available

- Enhanced version of the HCTL-1000

- DC, DC brushless, and step motor control

- · Position and velocity control

- Programmable digital filter and commutator

- · 8-Bit parallel, and PWM motor command ports

- TTL compatible

- · SYNC pin for coordinating multiple HCTL-1100 ICs

- 100 kHz to 2 MHz operation

- · Encoder input port

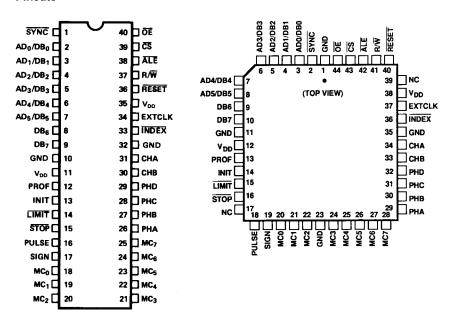

### **Pinouts**

ESD WARNING: NORMAL HANDLING PRECAUTIONS SHOULD BE TAKEN TO AVOID STATIC DISCHARGE.

### **Applications**

Typical applications for the HCTL-1100 include printers, medical instruments, material handling machines, and industrial automation.

**Note:** Avago Technologies encoders are not recommended for use in safety critical applications. Eg. ABS braking systems, power steering, life support systems and critical care medical equipment. Please contact sales representative if more clarification is needed.

HCTL-1100 vs. HCTL-1000 The HCTL-1100 is designed to replace the HCTL-1000. Some differences exist, and some enhancements have been added.

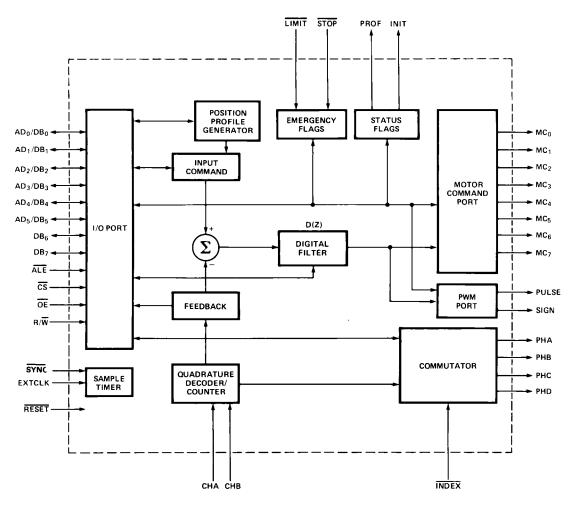

**System Block Diagram**

### Comparison of HCTL-1100 and HCTL-1000

| Description                              | HCTL-1100                                  | HCTL-1000                         |

|------------------------------------------|--------------------------------------------|-----------------------------------|

| Max. Supply Current                      | 30 mA                                      | 180 mA                            |

| Max. Power Dissipation                   | 165 mW                                     | 950 mW                            |

| Max. Tri-State Output<br>Leakage Current | 150 nA                                     | 10 μΑ                             |

| Operating Frequency                      | 100 kHz-2 MHz                              | 1 MHz-2 MHz                       |

| Operating Temperature<br>Range           | -20°C to +85°C                             | 0°C to 70°C                       |

| Storage Temperature Range                | -55°C to +125°C                            | -40°C to +125°C                   |

| Synchronize 2 or More ICs                | Yes                                        | _                                 |

| Preset Actual Position<br>Registers      | Yes                                        | _                                 |

| Read Flag Register                       | Yes                                        | -                                 |

| Limit and Stop Pins                      | Must be pulled up to $V_{DD}$ if not used. | Can be left floating if not used. |

| Hard Reset                               | Required                                   | Recommended                       |

| PLCC Package Available                   | Yes                                        | _                                 |

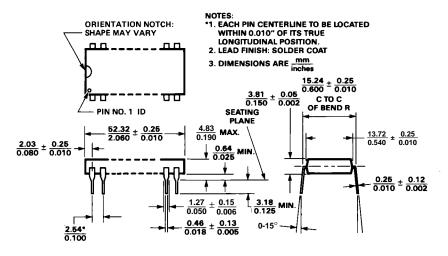

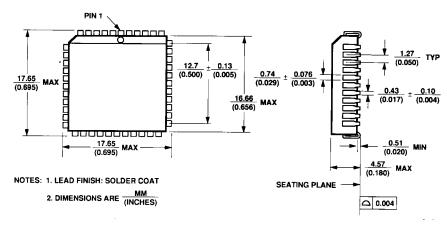

### **Package Dimensions**

40-PIN PLASTIC DUAL INLINE PACKAGE

44 PIN PLASTIC LEADED CHIP CARRIER PACKAGE

### Theory of Operation

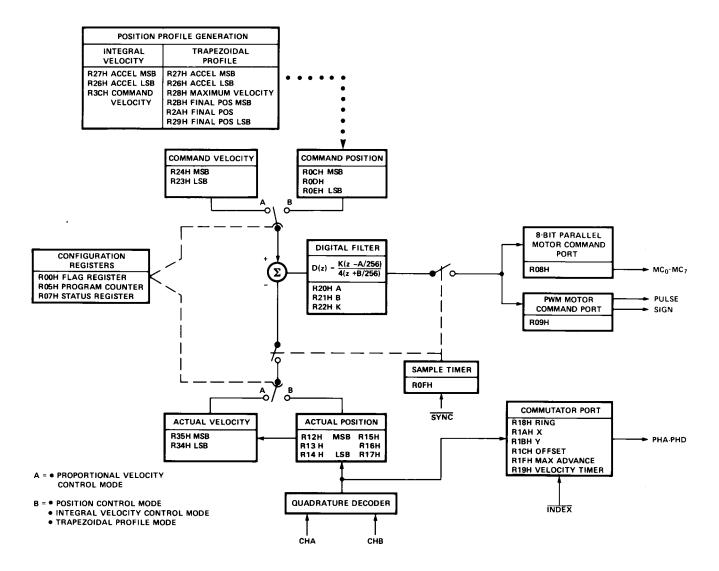

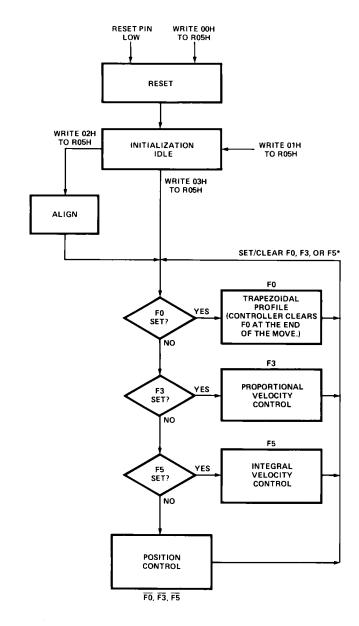

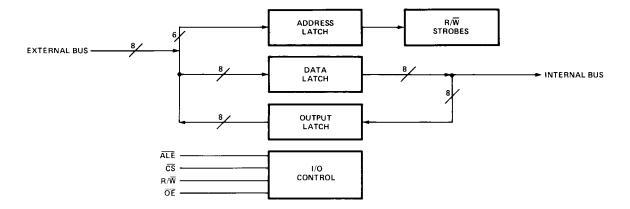

The HCTL-1100 is a general purpose motor controller which provides position and velocity control for DC, DC brushless and stepper motors. The internal block diagram of the HCTL-1100 is shown in Figure 1. The HCTL-1100 receives its input commands from a host processor and position feedback from an incremental encoder with quadrature output. An 8-bit bi-directional multiplexed address/data bus interfaces the HCTL-1100 to the host processor. The encoder

feedback is decoded into quadrature counts and a 24-bit counter keeps track of position. The HCTL-1100 executes any one of four control algorithms selected by the user. The four control modes are:

- Position Control

- Proportional Velocity Control

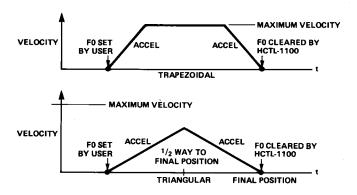

- Trapezoidal Profile Control for point to point moves

- Integral Velocity Control with continuous velocity profiling using linear acceleration

The resident Position Profile Generator calculates the necessary profiles for Trapezoidal Profile Control and Integral Velocity Control. The HCTL-1100 compares the desired position (or velocity) to the actual position (or velocity) to compute compensated motor commands using a programmable digital filter D(z). The motor command is externally available at the Motor Command port as an 8-bit byte and at the PWM port as a Pulse Width Modulated (PWM) signal.

The HCTL-1100 has the capability of providing electronic commutation for DC brushless and stepper motors. Using the encoder position information, the motor phases are enabled in the correct sequence. The commutator is fully programmable to encompass most motor/encoder combinations. In addition, phase overlap and phase advance can be programmed to improve torque ripple and high speed performance. The HCTL-1100 contains a number of flags including two externally available flags, Profile and Initialization, which allow the user to see or check the status of the controller. It also has two emergency inputs, Limit and Stop, which allow operation of the HCTL-1100 to be interrupted under emergency conditions.

The HCTL-1100 controller is a digitally sampled data system. While information from the host processor is accepted asynchronously with respect to the control functions, the motor command is computed on a discrete sample time basis. The sample timer is programmable.

Figure 1. Internal Block Diagram.

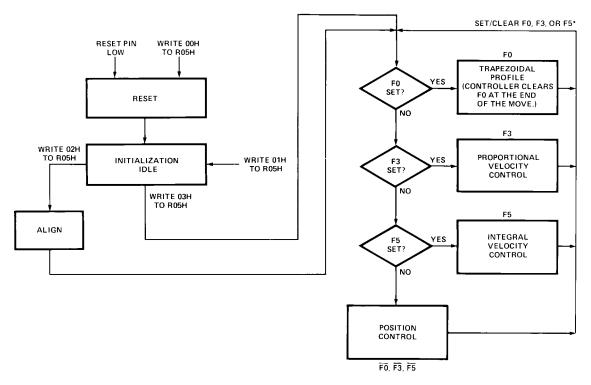

Figure 2. Operating Mode Flowchart.

### **Electrical Specifications**

### **Absolute Maximum Ratings**

| Operating Temperature, T <sub>A</sub>                 | 20°C to 85°C                      |

|-------------------------------------------------------|-----------------------------------|

| Storage Temperature, T <sub>S</sub>                   | 55°C to 125°C                     |

| Supply Voltage, V <sub>DD</sub>                       | 0.3 V to 7 V                      |

| Input Voltage, V <sub>IN</sub>                        | 0.3 V to $V_{DD} + 0.3 \text{ V}$ |

| Maximum Operating Clock Frequency, f <sub>CLK</sub> . | 2 MHz                             |

DC Electrical Characteristics  $V_{DD} = \ 5 \ V \pm \ 5\%; \ T_A = \ -20 ^{\circ}C \ to \ +85 ^{\circ}C$

| Parameter                          | Symbol           | Min. | Typ. | Max.              | Units | Test Conditions                                                                            |

|------------------------------------|------------------|------|------|-------------------|-------|--------------------------------------------------------------------------------------------|

| Supply Voltage                     | V <sub>DD</sub>  | 4.75 | 5.00 | 5.25              | V     |                                                                                            |

| Supply Current                     | I <sub>DD</sub>  |      | 15   | 30                | mA    |                                                                                            |

| Input Leakage Current              | I <sub>IN</sub>  |      | 10   | 100               | nA    | $V_{IN} = 0.00 \text{ and } 5.25 \text{ V}$                                                |

| Input Pull-Up Current              |                  |      |      |                   |       |                                                                                            |

| SYNC PIN                           | I <sub>PU</sub>  |      | - 40 | ± 150             | μΑ    | $V_{IN} = 0.00 \text{ V}$                                                                  |

| Tristate Output Leakage<br>Current | I <sub>OZ</sub>  |      | 10   | -150              | nA    | Sync, LIMIT, STOP<br>pin #35 (PDIP)<br>V <sub>OUT</sub> = -0.3 to 5.25 V<br>pin #38 (PLCC) |

| Input Low Voltage                  | V <sub>IL</sub>  | -0.3 |      | 0.8               | V     |                                                                                            |

| Input High Voltage                 | V <sub>IH</sub>  | 2.0  |      | $V_{\mathrm{DD}}$ | V     |                                                                                            |

| Output Low Voltage                 | V <sub>OL</sub>  | -0.3 |      | 0.4               | V     | $I_{OL} = 2.2 \text{ mA}$                                                                  |

| Output High Voltage                | V <sub>OH</sub>  | 2.4  |      | $V_{\mathrm{DD}}$ | V     | $I_{OH} = -200 \mu\text{A}$                                                                |

| Power Dissipation                  | P <sub>D</sub>   |      | 75   | 165               | mW    |                                                                                            |

| Input Capacitance                  | C <sub>IN</sub>  |      |      | 20                | pF    |                                                                                            |

| Output Capacitance                 | C <sub>OUT</sub> |      | 100  |                   | pF    |                                                                                            |

### **AC Electrical Characteristics**

$V_{DD} = 5 \text{ V} \pm 5\%$ ;  $T_A = -20^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$ ; Units = nsec

|    |                                                                    |                   | C    | Clock Fi | requenc | y    | - Formula*        |                      |

|----|--------------------------------------------------------------------|-------------------|------|----------|---------|------|-------------------|----------------------|

| ID |                                                                    |                   | 2 N  | ИHz      | 1 M     | IHz  | FOIT              | IIUIA *              |

| #  | Signal                                                             | Symbol            | Min. | Max.     | Min.    | Max. | Min.              | Max.                 |

| 1  | Clock Period (clk)                                                 | t <sub>CPER</sub> | 500  |          | 1000    |      |                   |                      |

| 2  | Pulse Width, Clock High                                            | t <sub>CPWH</sub> | 230  |          | 300     |      |                   |                      |

| 3  | Pulse Width, Clock Low                                             | $t_{CPWL}$        | 200  |          | 200     |      | 200               |                      |

| 4  | Clock Rise and Fall Time                                           | t <sub>CR</sub>   |      | 50       |         | 50   |                   | 50                   |

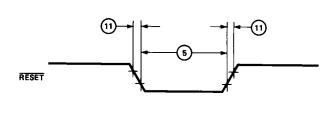

| 5  | Input Pulse Width Reset                                            | t <sub>IRST</sub> | 2500 |          | 5000    |      | 5 clk             |                      |

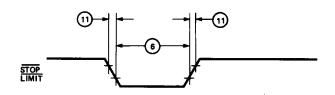

| 6  | Input Pulse Width Stop, Limit                                      | t <sub>IP</sub>   | 600  |          | 1100    |      | 1 clk<br>+ 100 ns |                      |

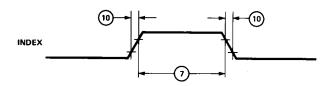

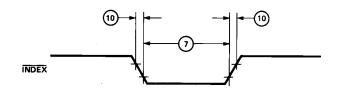

| 7  | Input Pulse Width Index, Index                                     | t <sub>IX</sub>   | 1600 |          | 3100    |      | 3 clk<br>+ 100 ns |                      |

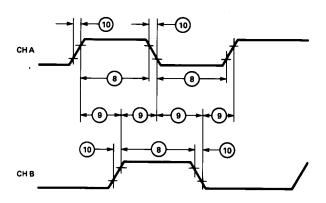

| 8  | Input Pulse Width CHA, CHB                                         | $t_{IAB}$         | 1600 |          | 3100    |      | 3 clk<br>+ 100 ns |                      |

| 9  | Delay CHA to CHB Transition                                        | t <sub>AB</sub>   | 600  |          | 1100    |      | 1 clk<br>+ 100 ns |                      |

| 10 | Input Rise/Fall Time CHA, CHB,<br>Index                            | t <sub>IABR</sub> |      | 450      |         | 900  |                   | 900 (clk<br>< 1 MHz) |

| 11 | Input Rise/Fall Time Reset, ALE, CS, OE, Stop, Limit               | $t_{IR}$          |      | 50       |         | 50   |                   | 50                   |

| 12 | Input Pulse Width $\overline{\text{ALE}}$ , $\overline{\text{CS}}$ | t <sub>IPW</sub>  | 80   |          | 80      |      | 80                |                      |

| 13 | Delay Time, ALE Fall to CS Fall                                    | t <sub>AC</sub>   | 50   |          | 50      |      | 50                |                      |

| 14 | Delay Time, ALE Rise to CS Rise                                    | t <sub>CA</sub>   | 50   |          | 50      |      | 50                |                      |

| 15 | Address Setup Time Before ALE Fall                                 | t <sub>ASR1</sub> | 20   |          | 20      |      | 20                |                      |

| 16 | Address Setup Time Before CS Fall                                  | t <sub>ASR</sub>  | 20   |          | 20      |      | 20                |                      |

| 17 | Write Data Setup Time Before CS Rise                               | $t_{ m DSR}$      | 20   |          | 20      |      | 20                |                      |

| 18 | Address/Data Hold Time                                             | t <sub>H</sub>    | 20   |          | 20      |      | 20                |                      |

| 19 | Setup Time, R/W Before CS Rise                                     | t <sub>WCS</sub>  | 20   |          | 20      |      | 20                |                      |

| 20 | Hold Time, R/W After CS Rise                                       | t <sub>WH</sub>   | 20   |          | 20      |      | 20                |                      |

| 21 | Delay Time, Write Cycle, CS<br>Rise to ALE Fall                    | $t_{CSAL}$        | 1700 |          | 3400    |      | 3.4 clk           |                      |

| 22 | Delay Time, Read/Write, CS<br>Rise to CS Fall                      | t <sub>CSCS</sub> | 1500 |          | 3000    |      | 3 clk             |                      |

| 23 | Write Cycle, ALE Fall to ALE<br>Fall For Next Write                | t <sub>WC</sub>   | 1830 |          | 3530    |      | 3.7 clk           |                      |

### AC Electrical Characteristics (continued).

|    |                                                                                        |                    | (    | Clock F | requenc | y    | - Formula*        |         |

|----|----------------------------------------------------------------------------------------|--------------------|------|---------|---------|------|-------------------|---------|

| ID |                                                                                        |                    | 2 N  | ИНz     | 1 M     | IHz  | F orm             | ula*    |

| #  | Signal                                                                                 | Symbol             | Min. | Max.    | Min.    | Max. | Min.              | Max.    |

| 24 | Delay Time, $\overline{\text{CS}}$ Rise to $\overline{\text{OE}}$ Fall                 | t <sub>CSOE</sub>  | 1700 |         | 3200    |      | 3 clk<br>+ 200 ns |         |

| 25 | Delay Time, OE Fall to Data<br>Bus Valid                                               | t <sub>OEDB</sub>  | 100  |         | 100     |      | 100               |         |

| 26 | Delay Time, CS Rise to Data<br>Bus Valid                                               | t <sub>CSDB</sub>  | 1800 |         | 3300    |      | 3 clk<br>+ 300 ns |         |

| 27 | Input Pulse Width OE                                                                   | t <sub>IPWOE</sub> | 100  |         | 100     |      | 100               |         |

| 28 | $\frac{\text{Hold Time, Data Held After}}{\text{OE Rise}}$                             | t <sub>DOEH</sub>  | 20   |         | 20      |      | 20                |         |

| 29 | Delay Time, Read Cycle, CS<br>Rise to ALE Fall                                         | t <sub>CSALR</sub> | 1820 |         | 3320    |      | 3 clk<br>+ 320 ns |         |

| 30 | Read Cycle, $\overline{\text{ALE}}$ Fall to $\overline{\text{ALE}}$ Fall For Next Read | $t_{RC}$           | 1950 |         | 3450    |      | 3 clk<br>+ 450 ns |         |

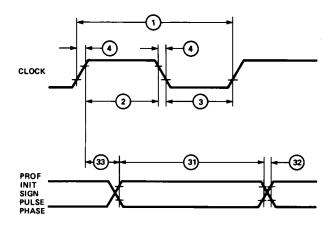

| 31 | Output Pulse Width, PROF,<br>INIT, Pulse, Sign, PHA-PHD,<br>MC Port                    | t <sub>OF</sub>    | 500  |         | 1000    |      | 1 clk             |         |

| 32 | Output Rise/Fall Time, PROF,<br>INIT, Pulse, Sign, PHA-PHD,<br>MC Port                 | $t_{OR}$           | 20   | 150     | 20      | 150  | 20                | 150     |

| 33 | Delay Time, Clock Rise to<br>Output Rise                                               | $t_{\mathrm{EP}}$  | 20   | 300     | 20      | 300  | 20                | 300     |

| 34 | Delay Time, CS Rising to MC<br>Port Valid                                              | $t_{CSMC}$         |      | 1600    |         | 3200 |                   | 3.2 clk |

| 35 | Hold Time, ALE High After CS Rise                                                      | t <sub>ALH</sub>   | 100  |         | 100     |      | 100               |         |

| 36 | Pulse Width, ALE High                                                                  | t <sub>ALPWH</sub> | 100  |         | 100     |      | 100               |         |

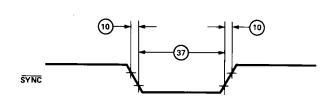

| 37 | Pulse Width, SYNC Low                                                                  | t <sub>SYNC</sub>  | 9000 |         | 18000   |      | 18 clk            |         |

<sup>\*</sup>General formula for determining AC characteristics for other clock frequencies (clk), between 100 kHz and 2 MHz.

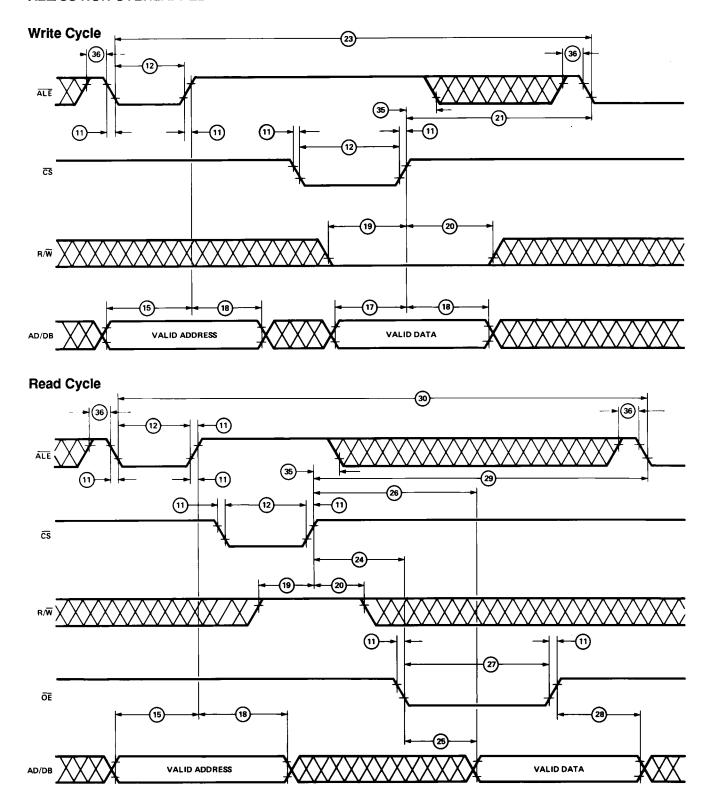

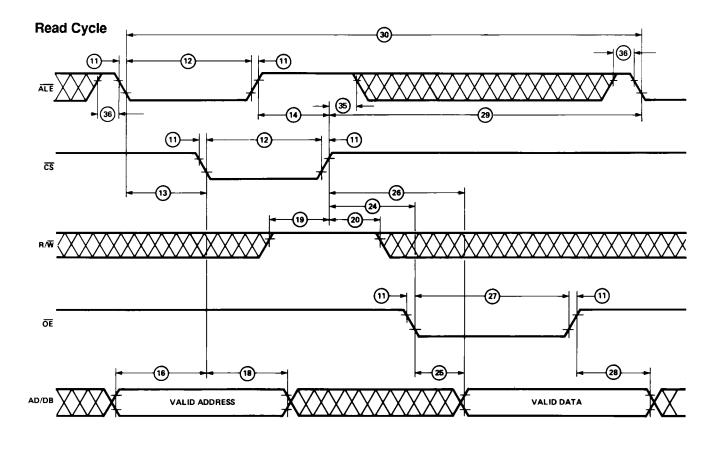

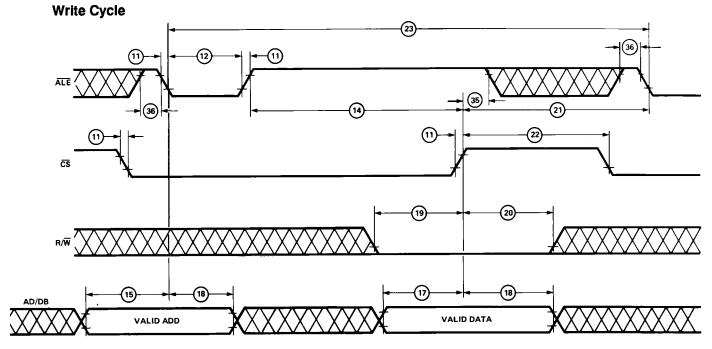

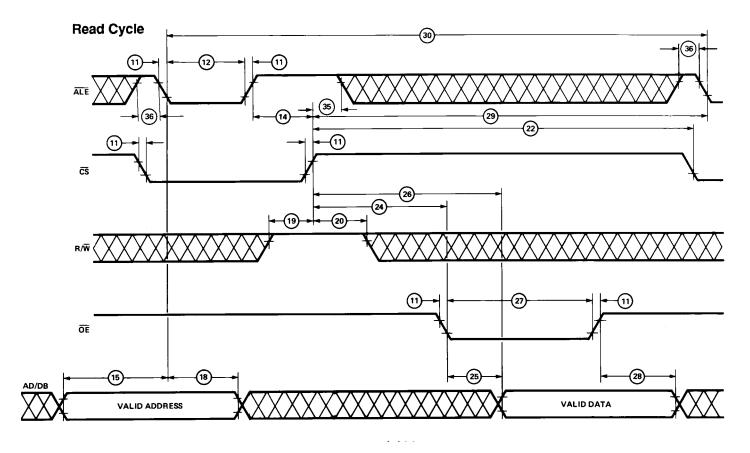

### HCTL-1100 I/O Timing Diagrams

Input logic level values are the TTL Logic levels  $V_{IL}=0.8\ V$  and  $V_{IH}=2.0\ V$ . Output logic levels are  $V_{OL}=0.4\ V$  and  $V_{OH}=2.4\ V$ .

### **HCTL-1100 I/O Timing Diagrams**

There are three different timing configurations which can be used to give the user flexibility to interface the HCTL-1100 to most microprocessors. See the I/O interface section for more details.

### **ALE/CS NON OVERLAPPED**

### ALE/CS OVERLAPPED

# Write Cycle ALE AD/DB VALID ADDRESS VALID DATA

### HCTL-1100 I/O Timing Diagrams

### **ALE WITHIN CS**

### ....

# Pin Descriptions and Functions Input/Output Pins

|                     | Pin N         | umber |                                                                                                   |  |             |

|---------------------|---------------|-------|---------------------------------------------------------------------------------------------------|--|-------------|

| Symbol              | ool PDIP PLCC |       | Symbol PDIP PLCC                                                                                  |  | Description |

| AD0/DB0-<br>AD5/DB5 | 2-7           | 3-8   | Address/Data Bus – Lower 6 bits of 8-bit I/O port which are multiplexed between address and data. |  |             |

| DB6, DB7            | 8, 9          | 9, 10 | Data bus – Upper 2 bits of 8-bit I/O port used for data only.                                     |  |             |

# Input Signals

|                   | Pin N  | umber            |                                                                                                                                                                                                                                                                            |  |

|-------------------|--------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Symbol            | PDIP   | PLCC             | Description                                                                                                                                                                                                                                                                |  |

| СНА/СНВ           | 31, 30 | 34, 33           | Channel A, B – Input pins for position feedback from an incremental shaft encoder. Two channels, A and B, 90 degrees out of phase are required.                                                                                                                            |  |

| Index             | 33     | 36               | Index Pulse – Input from the reference or index pulse of an incremental encoder. <u>Used only in conjunction with the Commutator</u> . Either a low or high true signal can be used with the Index pin. See Timing Diagrams and Encoder Interface section for more detail. |  |

| R/W               | 37     | 41               | Read/Write - Determines direction of data exchange for the I/O port.                                                                                                                                                                                                       |  |

| ALE               | 38     | 42               | Address Latch Enable – Enables lower 6 bits of external data bus into internal address latch.                                                                                                                                                                              |  |

| CS                | 39     | 43               | Chip Select – Performs I/O operation dependent on status of R/W line. For a Write, the external bus data is written into the internal addressed location. For Read, data is read from an internal location into an internal output latch.                                  |  |

| OE                | 40     | 44               | Output Enable – Enables the data in the internal output latch onto the external data bus to complete a Read operation.                                                                                                                                                     |  |

| Limit             | 14     | 15               | Limit Switch – An internal flag which when externally set, triggers an unconditional branch to the Initialization/Idle mode before the next control sample is executed. Motor Command is set to zero. Status of the Limit flag is monitored in the Status register.        |  |

| Stop              | 15     | 16               | Stop Flag – An internal flag that is externally set. When flag is set during Integral Velocity Control mode, the Motor Command is decelerated to a stop.                                                                                                                   |  |

| Reset             | 36     | 40               | Reset - A hard reset of internal circuitry and a branch to Reset mode.                                                                                                                                                                                                     |  |

| ExtClk            | 34     | 37               | External Clock                                                                                                                                                                                                                                                             |  |

| $V_{\mathrm{DD}}$ | 11, 35 | 12, 38           | Voltage Supply – Both $V_{\text{DD}}$ pins must be connected to a 5.0 volt supply.                                                                                                                                                                                         |  |

| GND               | 10, 32 | 1, 11,<br>23, 35 | Circuit Ground                                                                                                                                                                                                                                                             |  |

| SYNC              | 1      | 2                | Used to synchronize multiple HCTL-1100 sample timers.                                                                                                                                                                                                                      |  |

| NC                | -      | 17, 39           | Not connected. These pins should be left floating.                                                                                                                                                                                                                         |  |

### **Output Pins**

|         | Pin Number |                 |                                                                                                                                                                                                               |

|---------|------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol  | PDIP       | PLCC            | Description                                                                                                                                                                                                   |

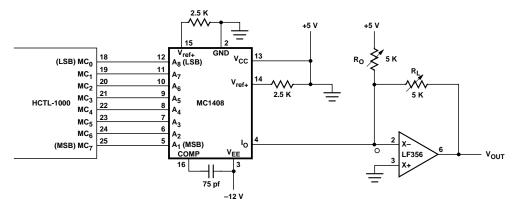

| MC0-MC7 | 18-25      | 20-22,<br>24-28 | Motor Command Port – 8-bit output port which contains the digital motor command adjusted for easy bipolar DAC interfacing. MC7 is the most significant bit (MSB).                                             |

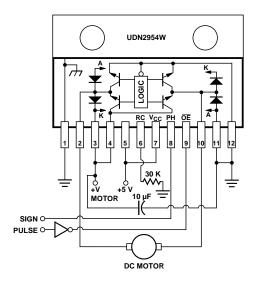

| Pulse   | 16         | 18              | Pulse – Pulse width modulated signal whose duty cycle is proportional to the Motor Command magnitude. The frequency of the signal is External Clock/100 and pulse width is resolved into 100 external clocks. |

| Sign    | 17         | 19              | Sign – Gives the sign/direction of the pulse signal.                                                                                                                                                          |

| PHA-PHD | 26-29      | 29-32           | Phase A, B, C, D – Phase Enable outputs of the Commutator.                                                                                                                                                    |

| Prof    | 12         | 13              | Profile Flag – Status flag which indicates that the controller is executing a profiled position move in the Trapezoidal Profile Control mode.                                                                 |

| Init    | 13         | 14              | Initialization/Idle Flag – Status flag which indicates that the controller is in the Initialization/Idle mode.                                                                                                |

### Pin Functionality

### **SYNC Pin**

The SYNC pin is used to synchronize two or more ICs. It is only valid in the INIT/IDLE mode (see Operating the HCTL-1100). When this pin is pulled low, the internal sample timer is cleared and held to zero. When the level on the pin is returned to high, the internal sample timer instantly starts counting down from the programmed value.

Connecting all SYNC pins together in the system and pulsing the SYNC signal from the host processor will synchronize all controllers.

### Limit Pin

This emergency-flag input is used to disable the control modes of the HCTL-1100. A low level on this input pin causes the internal Limit flag to be set. If this pin is NOT used, it must be pulled up to  $V_{DD}$ . If it is not connected, the pin could float low, and possibly trigger a false emergency condition.

The Limit flag, when set in any control mode, causes the HCTL-1100 to go into the Initialization/ Idle mode, clearing the Motor Command and causing an immediate motor shutdown. When the Limit flag is set, none of the three control mode flags (F0, F3, or F5) are cleared as the HCTL-1100 enters the Initialization/Idle mode. The user should be aware that these flags are still set before commanding the HCTL-1100 to re-enter one of the four control modes from Initialization/Idle mode.

In general, the user should clear all control mode flags after the limit pin has been pulled low, then proceed.

### Stop Pin

The Stop flag affects the HCTL-1100 only in the Integral Velocity Mode.

When a low level is present on this emergency-flag input, the internal stop flag is set. If this pin is NOT used, it must be pulled up to  $V_{DD}$ . If it is not connected, the pin could float low, and possibly trigger a false emergency condition.

When the STOP flag is set, the system will come to a decelerated stop and stay in this mode with a command velocity of zero until the Stop flag is cleared and a new command velocity is specified.

Notes on Limit and Stop Flags Stop and Limit flags are set by a low level input at their respective pins. The flags can only be cleared when the input to the corresponding pin goes high, signifying that the emergency condition has been corrected, AND a write to the Status register (R07H) is executed. That is, after the emergency pin has been set and cleared, the flag also must be cleared by writing to R07H. Any word that is written to R07H after the emergency pin is set and cleared will clear the emergency flag. The lower four bits of that word will also reconfigure the Status register.

# Encoder Input Pins (CHA, CHB, INDEX)

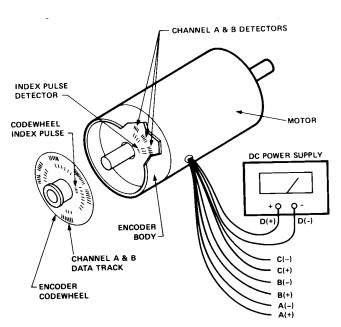

The HCTL-1100 accepts TTL compatible outputs from 2 and 3 channel incremental encoders such as the HEDS-5XXX, 6XXX, and 9XXX series encoders. Channels A and B are internally decoded into quadrature counts which increment or decrement the 24-bit position counter. For example, a 500-count encoder is decoded into 2000 quadrature counts per revolution. The position counter will be incremented when Channel B leads Channel A. The Index channel is used only for the Commutator and its function is to serve as a reference point for the internal Ring Counter.

The HCTL-1100 employs an internal 3-bit state delay filter to remove any noise spikes from the encoder inputs to the HCTL-1100. This 3-bit state delay filter requires the encoder inputs to remain stable for three consecutive clock rising edges for an encoder pulse to be considered valid by the HCTL-1100's actual position counter (i.e., an encoder pulse must remain at a logic level high or low for three consecutive clock rising edges for the HCTL-1100's actual position counter to be incremented or decremented.) The designer should therefore generally avoid creating the encoder pulses of less than 3 clock cycles.

The index signal of an encoder is used in conjunction with the Commutator. It resets the internal ring counter which keeps track of the rotor position so that no cumulative errors are generated.

The Index pin of the HCTL-1100 also has a 3-bit filter on its input. The Index pin is active low and level transition sensitive. It detects a valid high-to-low transition and qualifies the low input level through the 3-bit filter. At this point, the Index signal is internally detected by the commutator logic. This type of configuration allows an Index or Index signal to be used to generate the reference mark for commutator operation as long as the AC specifications for the Index signal are met.

### Motor Command Port (MC0-MC7)

The 8-bit Motor Command port consists of register R08H whose data goes directly to external pins MC0-MC7. MC7 is the most significant bit. R08H can be read and written to, however, it should be written to only during the Initialization/Idle mode. During any of the four Control modes, the controller writes the motor command into R08H.

This topic is further discussed in the "Register Section" under "Motor Command Register R08H".

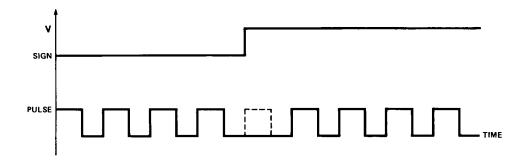

# Pulse Width Modulation (PWM) Output Port (Pulse, Sign)

The PWM port consists of the Pulse and Sign pins. The PWM port outputs the motor command as a pulse width modulated signal with the correct polarity. This topic is further discussed in the "Register Section" under "PWM Motor Command Register R09H".

Trapezoid Profile Pin (Prof)

The Trapezoid Profile Pin is

internally connected to software flag bit 4 in the Status Register. This flag is also represented by bit 0 in the Flag Register (R00H). See the "Register Section" for more information. Both the Pin and the Flag indicate the status of a trapezoid profile move. When the HCTL-1100 begins a trapezoid move, this flag is set by the controller (a high level appears on the pin), indicating the move is in progress. When the HCTL-1100 finishes the move, this flag is cleared by the controller.

Note that the instant the flag is cleared may not be the same instant the motor stops. The flag indicates the completion of the command profile, not the actual profile. If the motor is stalled during the move, or cannot physically keep up with the move, the flag will be cleared before the move is finished.

### INIT/IDLE Pin (INIT)

This pin indicates that the HCTL-1100 is in the INIT/IDLE mode, waiting to begin control. This pin is internally connected to the software flag bit 5 in the Status Register R07H. This flag is also represented by bit 1 in the Flag Register (R00H) (See the "Register Section" for more information).

### **Commutator Pins (PHA-PHD)**

These pins are connected only when using the commutator of the HCTL-1100 to drive a brushless motor or step motor. The four pins can be programmed to energize each winding on a multiphase motor.

### Operation of the HCTL-1100

### Registers

The HCTL-1100 operation is controlled by a bank of 64 8-bit registers, 35 of which are user accessible. These registers contain command and configura-

tion information necessary to properly run the controller chip. The 35 user-accessible registers are listed in Tables 1 and 2. The register number is also the address. A functional block diagram of the HCTL-1100 which shows the role of the user-

accessible registers is also included in Figure 3. The other 29 registers are used by the internal CPU as scratch registers and should not be accessed by the user.

Figure 3. Register Block Diagram.

Table 1. Register Reference By Mode

| Register  |              |                            |                          | User               |

|-----------|--------------|----------------------------|--------------------------|--------------------|

| Hex       | Dec.         | Function                   | Data Type <sup>[1]</sup> | Access             |

| General   | Control      |                            |                          |                    |

| R00H      | R00D         | Flag Register              |                          | r/w                |

| R05H      | R05D         | Program Counter            | scalar                   | r/w                |

| R07H      | R07D         | Status Register            | -                        | r/w <sup>[2]</sup> |

| R0FH      | R15D         | Sample Timer               | scalar                   | r/w                |

| R12H      | R18D         | Read Actual Position MSB   | 2's Complement           | $\mathbf{r}^{[4]}$ |

| R13H      | R19D         | Read Actual Position       | 2's Complement           | $r^{[4]}/w^{[5]}$  |

| R14H      | R20D         | Read Actual Position LSB   | 2's Complement           | $\mathbf{r}^{[4]}$ |

| R15H      | R21D         | Preset Actual Position MSB | 2's Complement           | $W^{[8]}$          |

| R16H      | R22D         | Preset Actual Position     | 2's Complement           | $W^{[8]}$          |

| R17H      | R23D         | Preset Actual Position LSB | 2's Complement           | $\mathbf{W}^{[8]}$ |

| Output l  | Registers    |                            |                          |                    |

| R07H      | R07D         | Sign Reversal Inhibit      | -                        | r/w <sup>[2]</sup> |

| R08H      | R08D         | 8 bit Motor Command        | 2's Complement+80H       | r/w                |

| R09H      | R09D         | PWM Motor Command          | 2's Complement           | r/w                |

| Filter Re | egisters     |                            |                          |                    |

| R20H      | R32D         | Filter Zero, A             | scalar                   | r/w                |

| R21H      | R33D         | Filter Pole, B             | scalar                   | r/w                |

| R22H      | R34D         | Gain, K                    | scalar                   | r/w                |

| Commut    | tator Regist | ters                       |                          |                    |

| R07H      | R07D         | Status Register            | -                        | r/w <sup>[2]</sup> |

| R18H      | R24D         | Commutator Ring            | scalar <sup>[6,7]</sup>  | r/w                |

| R19H      | R25D         | Velocity Timer             | scalar                   | W                  |

| R1AH      | R26D         | X                          | scalar <sup>[6,7]</sup>  | r/w                |

| R1BH      | R27D         | Y Phase Overlap            | scalar <sup>[6,7]</sup>  | r/w                |

| R1CH      | R28D         | Offset                     | 2's Complement[7]        | r/w                |

| R1FH      | R31D         | Max. Phase Advance         | scalar <sup>[6,7]</sup>  | r/w                |

|           | Control M    | ode                        |                          |                    |

| R00H      | R00D         | Flag Register              | -                        | r/w                |

| R12H      | R18D         | Read Actual Position MSB   | 2's Complement           | $\mathbf{r}^{[4]}$ |

| R13H      | R19D         | Read Actual Position       | 2's Complement           | $r^{[4]}/w^{[5]}$  |

| R14H      | R20D         | Read Actual Position LSB   | 2's Complement           | $\mathbf{r}^{[4]}$ |

| R0CH      | R12D         | Command Position MSB       | 2's Complement           | r/w <sup>[3]</sup> |

| R0DH      | R13D         | Command Position           | 2's Complement           | r/w <sup>[3]</sup> |

| R0EH      | R14D         | Command Position LSB       | 2's Complement           | r/w <sup>[3]</sup> |

Table 1. (continued).

| Register |              |                          |                       | <b>T</b> I         |

|----------|--------------|--------------------------|-----------------------|--------------------|

| Hex      | Dec.         | Function                 | Data Type             | User<br>Access     |

| Trapezo  | id Profile ( | Control Mode             |                       |                    |

| R00H     | R00D         | Flag Register            | -                     | r/w                |

| R07H     | R07D         | Status Register          | -                     | $r/w^{[2]}$        |

| R12H     | R18D         | Read Actual Position MSB | 2's Complement        | $\mathbf{r}^{[4]}$ |

| R13H     | R19D         | Read Actual Position     | 2's Complement        | $r^{[4]}/w^{[5]}$  |

| R14H     | R20D         | Read Actual Position LSB | 2's Complement        | $\mathbf{r}^{[4]}$ |

| R29H     | R41D         | Final Position LSB       | 2's Complement        | r/w                |

| R2AH     | R42D         | Final Position           | 2's Complement        | r/w                |

| R2BH     | R43D         | Final Position MSB       | 2's Complement        | r/w                |

| R26H     | R38D         | Acceleration LSB         | scalar                | r/w                |

| R27H     | R39D         | Acceleration MSB         | scalar <sup>[6]</sup> | r/w                |

| R28H     | R40D         | Maximum Velocity         | scalar <sup>[6]</sup> | r/w                |

| Integral | Velocity M   | ode                      |                       |                    |

| R00H     | R00D         | Flag Register            | -                     | r/w                |

| R12H     | R18D         | Read Actual Position MSB | 2's Complement        | $\mathbf{r}^{[4]}$ |

| R13H     | R19D         | Read Actual Position     | 2's Complement        | $r^{[4]}/w^{[5]}$  |

| R14H     | R20D         | Read Actual Position LSB | 2's Complement        | $\mathbf{r}^{[4]}$ |

| R26H     | R38D         | Acceleration LSB         | scalar                | r/w                |

| R27H     | R39D         | Acceleration MSB         | scalar <sup>[6]</sup> | r/w                |

| R3CH     | R60D         | Command Velocity         | 2's Complement        | r/w                |

| Proport  | ional Veloc  | ity Mode                 |                       |                    |

| R00H     | R00D         | Flag Register            | -                     | r/w                |

| R12H     | R18D         | Read Actual Position MSB | 2's Complement        | $\mathbf{r}^{[4]}$ |

| R13H     | R19D         | Read Actual Position     | 2's Complement        | $r^{[4]}/w^{[5]}$  |

| R14H     | R20D         | Read Actual Position LSB | 2's Complement        | $\mathbf{r}^{[4]}$ |

| R23H     | R35D         | Command Velocity LSB     | 2's Complement        | r/w                |

| R24H     | R36D         | Command Velocity MSB     | 2's Complement        | r/w                |

| R34H     | R52D         | Actual Velocity LSB      | 2's Complement        | r                  |

| R35H     | R53D         | Actual Velocity MSB      | 2's Complement        | r                  |

- Notes:

1. Consult appropriate section for data format and use.

2. Upper 4 bits are read only.

3. Writing to R0EH (LSB) latches all 24 bits.

4. Reading R14H (LSB) latches data in R12H and R13H.

5. Writing to R13H clears Actual Position Counter to zero.

6. The scalar data is limited to positive numbers (00H to 7FH).

7. The commutator registers (R18H, R1CH, R1FH) have further limits which are discussed in the Commutator section of this data sheet.

8. Writing to R17H (R23D) latches all 24 bits (only in INIT/IDLE mode).

Table 2. Register Reference Table by Register Number

| Register |      |                              |                                              |                               | •••                                |

|----------|------|------------------------------|----------------------------------------------|-------------------------------|------------------------------------|

| Hex      | Dec. | Function                     | Mode Used                                    | Data Type                     | User<br>Access                     |

| R00H     | R00D | Flag Register                | All                                          | _                             | r/w                                |

| R05H     | R05D | Program Counter              | All                                          | scalar                        | w                                  |

| R07H     | R07D | Status Register              | All                                          | _                             | $r/w^{[2]}$                        |

| R08H     | R08D | 8 bit Motor Command Port     | All                                          | 2's complement<br>+ 80H       | r/w                                |

| R09H     | R09D | PWM Motor Command Port       | All                                          | 2's complement                | r/w                                |

| ROCH     | R12D | Command Position (MSB)       | All except Proportional Velocity             | 2's complement                | r/w <sup>[3]</sup>                 |

| R0DH     | R13D | Command Position             | All except Proportional Velocity             | 2's complement                | r/w <sup>[3]</sup>                 |

| R0EH     | R14D | Command Position (LSB)       | All except Proportional Velocity             | 2's complement                | r/w <sup>[3]</sup>                 |

| R0FH     | R15D | Sample Timer                 | All                                          | scalar                        | r/w                                |

| R12H     | R18D | Read Actual Position (MSB)   | All                                          | 2's complement                | $\mathbf{r}^{[4]}$                 |

| R13H     | R19D | Read Actual Position         | All                                          | 2's complement                | r <sup>[4]</sup> /w <sup>[5]</sup> |

| R14H     | R20D | Read Actual Position (LSB)   | All                                          | 2's complement                | $\mathbf{r}^{[4]}$                 |

| R15H     | R21D | Preset Actual Position (MSB) | INIT/IDLE                                    | 2's complement                | w <sup>[8]</sup>                   |

| R16H     | R22D | Preset Actual Position       | INIT/IDLE                                    | 2's complement                | w <sup>[8]</sup>                   |

| R17H     | R23D | Preset Actual Position (LSB) | INIT/IDLE                                    | 2's complement                | w <sup>[8]</sup>                   |

| R18H     | R24D | Commutator Ring              | All                                          | scalar <sup>[6,7]</sup>       | r/w                                |

| R19H     | R25D | Commutator Velocity Timer    | All                                          | scalar                        | W                                  |

| R1AH     | R26D | X                            | All                                          | scalar <sup>[6]</sup>         | r/w                                |

| R1BH     | R27D | Y Phase Overlap              | All                                          | scalar <sup>[6]</sup>         | r/w                                |

| R1CH     | R28D | Offset                       | All                                          | 2's complement <sup>[7]</sup> | r/w                                |

| R1FH     | R31D | Maximum Phase Advance        | All                                          | scalar <sup>[6,7]</sup>       | r/w                                |

| R20H     | R32D | Filter Zero, A               | All except Proportional Velocity             | scalar                        | r/w                                |

| R21H     | R33D | Filter Pole, B               | All except Proportional Velocity             | scalar                        | r/w                                |

| R22H     | R34D | Gain, K                      | All                                          | scalar                        | r/w                                |

| R23H     | R35D | Command Velocity (LSB)       | Proportional Velocity                        | 2's complement                | r/w                                |

| R24H     | R36D | Command Velocity (MSB)       | Proportional Velocity                        | 2's complement                | r/w                                |

| R26H     | R38D | Acceleration (LSB)           | Integral Velocity and<br>Trapezoidal Profile | scalar                        | r/w                                |

| R27H     | R39D | Acceleration (MSB)           | Integral Velocity and Trapezoidal Profile    | scalar <sup>[6]</sup>         | r/w                                |

| R28H     | R40D | Maximum Velocity             | Trapezoidal Profile                          | scalar <sup>[6]</sup>         | r/w                                |

| R29H     | R41D | Final Position (LSB)         | Trapezoidal Profile                          | 2's complement                | r/w                                |

| R2AH     | R42D | Final Position               | Trapezoidal Profile                          | 2's complement                | r/w                                |

| R2BH     | R43D | Final Position (MSB)         | Trapezoidal Profile                          | 2's complement                | r/w                                |

| R34H     | R52D | Actual Velocity (LSB)        | Proportional Velocity                        | 2's complement                | r                                  |

| R35H     | R53D | Actual Velocity (MSB)        | Proportional Velocity                        | 2's complement                | r                                  |

| R3CH     | R60D | Command Velocity             | Integral Velocity                            | 2's complement                | r/w                                |

- Consult appropriate section for data format and use.

Upper 4 bits are read only.

Writing to R0EH (LSB) latches all 24 bits.

Reading R14H (LSB) latches data in R12H and R13H.

- 5. Writing to R13H clears Actual Position Counter to zero.

6. The scalar data is limited to positive numbers (00H to 7FH).

7. The commutator registers (R18H, R1CH, R1FH) have further limits which are discussed in the Commutator section of this data sheet.

8. Writing to R17H (R23D) latches all 24 bits (only in INIT/IDLE mode).

Register Descriptions – General Control, Output, Filter, and Commutator

### Flag Register (R00H)

The Flag register contains flags F0 through F5. This register is a read/write register. Each flag is set and cleared by writing an 8-bit data word to R00H. When writing to R00H, the upper four bits are ignored by the HCTL-1100, bits 0,1,2 specify the flag address, and bit 3 specifies whether to set (bit=1) or clear (bit=0) the addressed flag.

### Flag Descriptions

**F0**-Trapezoidal Profile Flag – set by the user to execute Trapezoidal Profile Control. The flag is reset by the controller when the move is completed. The status of F0 can be monitored at the Profile pin and in Status register R07H bit 4.

F1-Initialization/Idle Flag – set/cleared by the HCTL-1100 to indicate execution of the Initialization/Idle mode. The status of F1 can be monitored at the Initialization/Idle pin and in bit 5 of the Status register (R07H). The user should not attempt to set or clear F1.

**F2**–Unipolar Flag – set/cleared by the user to specify Bipolar (clear) or Unipolar (set) mode for the Motor Command port.

**F3**–Proportional Velocity Control Flag – set by the user to specify Proportional Velocity control.

**F4**-Hold Commutator flag – set/ cleared by the user or automatically by the Align mode. When set, this flag inhibits the internal commutator counters to allow open loop stepping of a motor by using the commutator. (See "Offset register" description in the "Commutator section.")

**F5**-Integral Velocity Control – set by the user to specify Integral Velocity Control. Also set and cleared by the HCTL-1100 during execution of the Trapezoidal Profile mode. This is transparent to the user except when the Limit flag is set (see "Emergency Flags" section).

### Writing to the Flag Register

When writing to the flag register, only the lower four bits are used. Bit 3 indicates whether to set or clear a certain flag, and bits 0,1,and 2 indicate the desired flag. The following table shows the bit map of the Flag register:

| Bit Number | Function   |

|------------|------------|

| 7-4        | Don't Care |

| 3          | 1 = set    |

|            | 0 = clear  |

| 2          | AD2        |

| 1          | AD1        |

| 0          | AD0        |

The following table outlines the possible writes to the Flag Register:

| Flag | SET | CLEAR |

|------|-----|-------|

| F0   | 08H | 00H   |

| F1   | -   | -     |

| F2   | 0AH | 02H   |

| F3   | 0BH | 03H   |

| F4   | 0CH | 04H   |

| F5   | 0DH | 05H   |

### Reading the Flag Register

Reading register R00H returns the status of the flags in bits 0 to 5. For example, if bit 0 is set (logic 1), then flag F0 is set. If bit 4 is set, then flag F4 is set. If bits 0 and 5 are set, then both flags F0 and F5 are set.

The following table outlines the Flag Register Read:

| Bit<br>Number | Flag<br>(1 = set)<br>(0 = clear) |

|---------------|----------------------------------|

| 8-6           | Don't Care                       |

| 5             | F5                               |

| 4             | F4                               |

| 3             | F3                               |

| 2             | F2                               |

| 1             | F1                               |

| 0             | F0                               |

### Notes:

- 1. A soft reset (writing 00H to R05H) will not reset the flags in the flag register. A hard reset (RESET pin low) is required to reset all the flags. The flags can also be reset by writing the proper word to the Flag register as explained above.

- 2. While in Trapezoid Profile Mode, Flag F0 will be set, and Flag F5 may be set. F5 is used for internal purposes. Both flags will be cleared at the end of the profile.

### Program Counter Register (R05H)

The Program Counter, which is a write-only register, executes the preprogrammed functions of the controller. The program counter is used along with the control flags F0, F3, and F5 in the Flag register (R00H) to change control modes. The user can write any of the following four commands to the Program Counter.

| Value<br>written<br>to R05H | Action                                                                   |

|-----------------------------|--------------------------------------------------------------------------|

| 00H                         | Software Reset                                                           |

| 01H                         | Enter Init/Idle Mode                                                     |

| 02H<br>03H                  | Enter Align Mode<br>(only from INIT/<br>IDLE Mode)<br>Enter Control Mode |

| 0011                        | (only from INIT/<br>IDLE Mode)                                           |

These Commands are discussed in more detail in the "Operating Modes" section.

### Status Register (R07H)

The Status register indicates the status of the HCTL-1100. Each bit decodes into one signal. All 8 bits are user readable and are decoded as shown below. Only the lower 4 bits can be written to by the user to configure the HCTL-1100. To set or clear any of the lower 4 bits, the user writes an 8-bit word to R07H. The upper 4 bits are ignored. Each of the lower 4 bits directly sets/clears the corresponding bit of the Status register as shown below. For example, writing XXXX0101 to R07H sets the PWM Sign Reversal Inhibit, sets the Commutator Phase Configuration to "3 Phase," and sets the Commutator Count Configuration to "full."

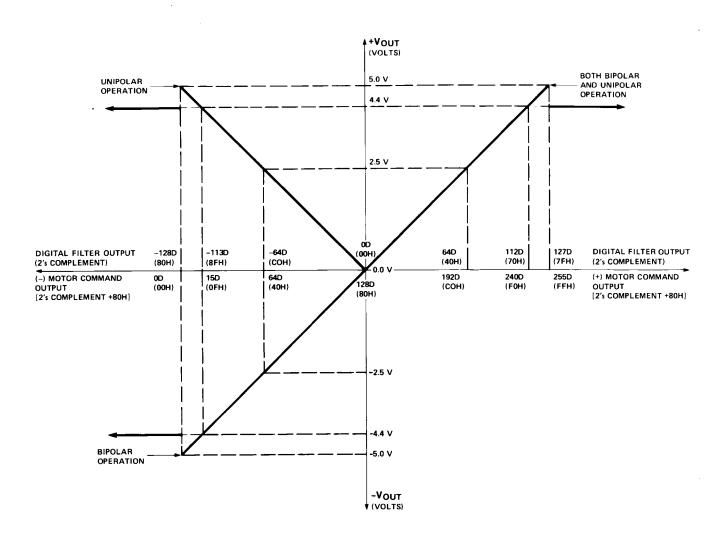

### Motor Command Register (R08H)

The 8-bit Motor Command Port consists of register R08H. The register is connected to external pins MC0-MC7. MC7 is the most significant bit. R08H can be read and written to; however, it should be written to only in the Initialization/Idle mode. During any of the four control modes, the HCTL-1100 writes values to register R08H.

The Motor Command Port operates in two modes, bipolar and unipolar, when under control of internal software. Bipolar mode allows the full range of values in R08H (-128D to +127D). The data written to the Motor Command Port by the control algorithms is the internally

computed 2's-complement motor command with an 80H offset added. This allows direct interfacing to a DAC. Connecting the Motor Command Port to a DAC, Bipolar mode allows the full voltage swing (positive and negative).

Unipolar mode functions such that with the same DAC circuit, the motor command output is restricted to positive values (80H to FFH) when in a control mode. Unipolar mode is used with multi-phase motors when the commutator controls the direction of movement. (If needed, the Sign pin could be used to indicate direction). In Unipolar mode, the user can still write a negative value to R08H in INIT/IDLE mode.

Unipolar mode or Bipolar mode is programmed by setting or clearing flag F2 in the Flag Register R00H.

Internally, the HCTL-1100 operates on data of 24, 16 and 8bit lengths to produce the 8-bit motor command, available externally. Many times the computed motor command will be greater than 8 bits. At this point, the motor command is saturated by the controller. The saturated value output by the controller is not the full scale value 00H (00D), or FFH (255D). The saturated value is adjusted to 0FH (15D) (negative saturation) and F0H (240D) (positive saturation). Saturation levels for the Motor Command port are in Figure 4.

Table 3. Status Register

| Status Bit | Function                                                                   |

|------------|----------------------------------------------------------------------------|

| 0          | PWM Sign Reversal Inhibit  0 = off  1 = on                                 |

| 1          | Commutator Phase Configuration $0 = 3 \text{ phase}$ $1 = 4 \text{ phase}$ |

| 2          | Commutator Count Configuration $0 = \text{quadrature}$ $1 = \text{full}$   |

| 3          | Should always be set to 0                                                  |

| 4          | Trapezoidal Profile Flag F0<br>1 = in Profile Control                      |

| 5          | Initialization/Idle Flag F1<br>1 = in Initialization/Idle Mode             |

| 6          | Stop Flag  0 = set (Stop triggered)  1 = cleared (no Stop)                 |

| 7          | Limit Flag  0 = set (Limit triggered)  1 = cleared (no Limit)              |

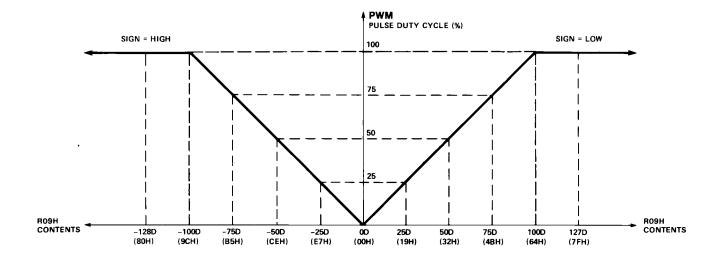

# PWM Motor Command Register (R09H)

The PWM port outputs the motor command as a pulse width modulated signal with the correct sign of polarity. The PWM port consists of the Pulse and Sign pins and R09H.

The PWM signal at the Pulse pin has a frequency of External Clock/100 and the duty cycle is

resolved into the 100 clocks. (For example, a 2 MHz clock gives a 20 KHz PWM frequency.)

The Sign pin gives the polarity of the command. Low output on Sign pin is positive polarity.

The 2's-complement contents of R09H determine the duty cycle and polarity of the PWM command. For example, D8H

(-40D) gives a 40% duty cycle signal at the Pulse pin and forces the Sign pin high. Data outside the 64H (+100D) to 9CH (-100D) linear range gives 100% duty cycle. R09H can be read and written to. However, the user should only write to R09H when the controller is in the Initialization/Idle mode. Figure 5 shows the PWM output versus the internal motor

command.

**Figure 4. Motor Command Port Output.**

When any Control mode is being executed, the unadjusted internal 2's-complement motor command is written to R09H. Because of the hardware limit on the linear range (64H to 9CH,  $\pm$  100D), the PWM port saturates sooner than the 8-bit Motor Command port (00H to FFH,  $\pm$  127D to  $\pm$  128D). When the internal motor command saturates above 8 bits, the PWM port is saturated to the full

$\pm$  100% duty cycle level. Figure 5 shows the actual values inside the PWM port. Note that the Unipolar flag, F2, does *not* affect the PWM port.

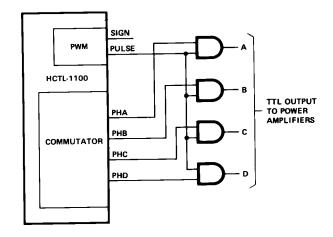

For commutation of brushless motors with the PWM port, only use the Pulse pin from the PWM port as the commutator already contains sign information. (See Figure 9.)

The PWM port has an option that can be used with H-bridge type amplifiers. The option is Sign Reversal Inhibit, which inhibits the Pulse output for one PWM period after a sign polarity reversal. This allows one pair of transistors to turn off before others are turned on and thereby avoids a short across the power supply. Bit 0 in the Status register (R07H) controls the Sign Reversal

Figure 5. PWM Port Output.

Figure 6. Sign Reversal Inhibit.

Inhibit option. Figure 6 shows the output of the PWM port when Bit 0 is set.

Actual Position Registers Read, Clear: R12H,R13H,R14H Preset: R15H,R16H,R17H

The Actual Position Register is accessed by two sets of registers in the HCTL-1100. When reading the Actual Position from the HCTL-1100, the host processor will read Registers R12H(MSB), R13H, and R14H(LSB). When presetting the Actual Position Register, the processor will write to Registers R15H(MSB), R16H, and R17H(LSB).

When reading the Actual Position registers, the order should be R14H, R13H, R12H. These registers are latched, such that, when reading Register R14H, all three bytes will be latched so that count data does not change while reading three separate bytes.

When presetting the Actual Position Register, write to R15H and R16H first. When R17H is written to, all three bytes are simultaneously loaded into the Actual Position Register.

Note that presetting the Actual Position Registers is only allowed while the HCTL-1100 is in INIT/IDLE mode.

The Actual Position Registers can be simultaneously cleared at any time by writing any value to R13H.

### **Digital Filter Registers**

Zero (A) R20H Pole (B) R21H Gain (K) R22H

All control modes use some part of the programmable digital filter D(z) to compensate for closed loop system stability. The compensation D(z) has the form:

$$D(z) = \frac{K\left(z - \frac{A}{256}\right)}{4\left(z + \frac{B}{256}\right)}$$

[1

where:

z = the digital domain operator

K = digital filter gain (R22H)

A = digital filter zero (R20H)

B = digital filter pole (R21H)

The compensation is a first-order lead filter which in combination with the Sample Timer T (R0FH) affects the dynamic step response and stability of the control system. The Sample Timer, T, determines the rate at which the control algorithm gets executed. All parameters, A, B, K, and T, are 8-bit scalars that can be changed by the user any time.

As shown in equations [2] and [3], the digital filter uses previously sampled data to calculate D(z). This old internally sampled data is cleared when the Initialization/Idle mode is executed.

In Position Control, Integral Velocity Control, and Trapezoidal Profile Control the digital filter is implemented in the time domain as shown below:

$$\begin{split} MC_{_{n}} = & (K/4) (X_{_{n}}) - \\ & [(A/256) (K/4) (X_{_{n-1}}) + \\ & (B/256) (MC_{_{n-1}})] \end{split}$$

where:

$$\begin{split} n &= \text{ current sample time} \\ n-1 &= \text{ previous sample time} \\ MC_n &= \text{ Motor Command Output} \\ \text{ at n} \\ MC_{n-1} &= \text{ Motor Command} \\ \text{ Output at n-1} \\ X_n &= \text{ (Command Position } - \\ \text{ Actual Position) at n} \\ X_{n-1} &= \text{ (Command Position } - \\ \text{ Actual Position) at n-1} \end{split}$$

In Proportional Velocity control the digital compensation filter is implemented in the time domain as:

$$MC_n = (K/4)(Y_n)$$

[3]

where:

Y<sub>n</sub> = (Command Velocity – Actual Velocity) at n

For more information on system sampling times, bandwidth, and stability, please consult Avago Application Note 1032, *Design of the HCTL-1000's Digital Filter Parameters by the Combination Method.*

### Sample Timer Register (R0FH)

The contents of this register set the sampling period of the HCTL-1100. The sampling period is:

t = 16(T+1)(1/frequency of theexternal clock) [4]

### where:

T = contents of register R0FH

The Sample Timer has a limit on the minimum allowable sample time depending on the control mode being executed. The limits are given in Table 4 below.

The minimum value limits are to make sure the internal programs have enough time to complete proper execution.

The maximum value of T (R0FH) is FFH (255D). With a 2 MHz clock, the sample time can vary from 64  $\mu$ sec to 2048  $\mu$ sec. With a 1 MHz clock, the sample time can vary from 128  $\mu$ sec to 4096  $\mu$ sec.

Digital closed-loop systems with slow sampling times have lower stability and a lower bandwidth than similar systems with faster sampling times. To keep the system stability and bandwidth as high as possible the HCTL-1100 should typically be programmed with the fastest sampling time

possible. This rule of thumb must be balanced by the needs of the velocity range to be controlled. Velocities are specified to the HCTL-1100 in terms of quadrature encoder counts per sample time. The faster the sampling time, the higher the slowest possible speed.

### **Hardware Description**

The Sample Timer consists of a buffer and a decrement counter. Each time the counter reaches 00H, the Sampler Timer Value T (value written to R0FH) is loaded from the buffer into the counter, which immediately begins to decrement from T.

### Writing to the Sample Timer Register

Data written to R0FH will be latched into the internal buffer and used by the counter after it completes the present sample time cycle by decrementing to 00H. The next sample time will use the newly written data.

Reading the Sample Timer Register Reading R0FH gives the values directly from the decrementing counter. Therefore, the data read from R0FH will have a value anywhere between T and 00H, depending where in the sample time cycle the counter is.

Table 4.

| Control Mode                  | R0FH Contents<br>Minimum Limit |

|-------------------------------|--------------------------------|

| Position Control              | 07H(07D)                       |

| Proportional Velocity Control | 07H(07D)                       |

| Trapezoidal Profile Control   | 0FH(15D)                       |

| Integral Velocity Control     | 0FH(15D)                       |

### Example -

- 1. On reset, the value of the timer is pre-set to 40H.

- 2. Reading R0FH shows 3EH . . . 2BH . . . 08H . . . 3CH . . .

### **Synchronizing Multiple Axes**

Synchronizing multiple axes with HCTL-1100s can be achieved by using the SYNC pin as explained in the Pin Discussion section. Some users may not only want to synchronize several HCTL-1100s but also follow custom profiles for each axis. To do this, the user may need to write a new command position or command velocity during each sample time for the duration of the profile. In this case, data written to the HCTL-1100 has to be coordinated with the Sample Timer. This is so that only one command position or velocity is received during any one sample period, and that it is written at the proper time within a sample period.

At the beginning of each sample period, the HCTL-1100 is performing calculations and executions. New command positions and velocities should not be written to the HCTL-1100 during this time. If they are, the calculations may be thrown off and cause unpredictable control.

The user can read the Sample Timer Register to avoid writing too early during a sample period. Since the Sample Timer Register continuously counts down from its programmed value, the user can check if enough time has passed in the sample period to insure the completion of the internal calculations. The length of time needed by the HCTL-1100

to do its calculations is given by the Minimum Limits of R0FH (Sample Timer Register) as shown in Table 4. For Position Control Mode, the user should wait for the Sample Timer to count down 07H from its programmed value before writing the next command position or velocity. If the programmed sample timer value is 39H, wait until the Sample Timer Register reads 32H. Writing between 32H and 00H will make the command information available for the next sample period.

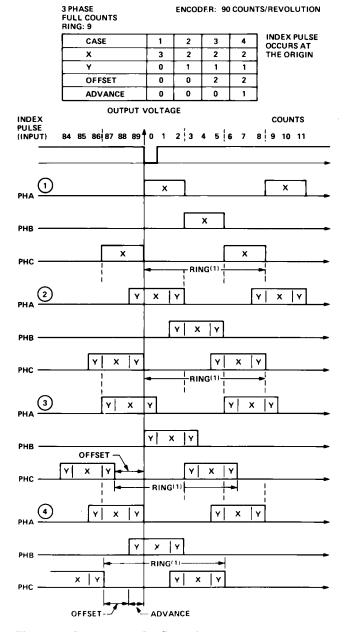

### Commutator

| Status Register    | (R07H) |

|--------------------|--------|

| Commutator Ring    | (R18H) |

| X Register         | (R1AH) |

| Y Phase Overlap    | (R1BH) |

| Offset             | (R1CH) |

| Max. Phase Advance | (R1FH) |

| Velocity Timer     | (R19H) |

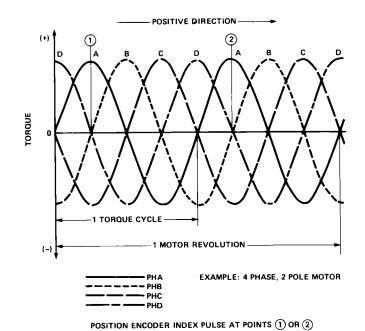

The commutator is a digital state machine that is configured by the user to properly select the phase sequence for electronic commutation of multiphase motors. The Commutator is designed to work with 2, 3, and 4-phase motors of various winding configurations and with various encoder counts. Along with providing the correct phase enable sequence, the Commutator provides programmable phase overlap, phase advance, and phase offset.

Phase overlap is used for better torque ripple control. It can also be used to generate unique state sequences which can be further decoded externally to drive more complex amplifiers and motors. Phase advance allows the user to compensate for the frequency characteristics of the motor/amplifier combination. By advancing the phase enable command (in position), the delay in reaction of the motor/amplifier combination can be offset and higher performance can be achieved.

Phase offset is used to adjust the alignment of the commutator output with the motor torque curves. By correctly aligning the HCTL-1100's commutator output with the motor's torque curves, maximum motor output torque can be achieved.

The inputs to the Commutator are the three encoder signals, Channel A, Channel B, and Index, and the configuration data stored in registers. The Commutator uses both channels and the index pulse of an incremental encoder. The index pulse of the encoder must be physically aligned to a known torque curve location because it is used as the reference point of the rotor position with respect to the Commutator phase enables.

The index pulse should be permanently aligned during motor encoder assembly to the last motor phase. This is done by energizing the last phase of the motor during assembly and permanently attaching the encoder codewheel to the motor shaft such that the index pulse is active as shown in Figures 7 and 8. Fine tuning of alignment for commutation purposes is done electronically by the Offset register (R1CH) once the complete control system is set up.

Figure 7. Index Pulse Alignment to Motor Torque Curves.

Each time an index pulse occurs, the internal commutator ring counter is reset to 0. The ring counter keeps track of the current position of the rotor based on the encoder feedback. When the ring counter is reset to 0, the Commutator is reset to its origin (last phase going low, Phase A going high) as shown in Figure 10.

The output of the Commutator is available as PHA, PHB, PHC, and PHD. The HCTL-1100's commutator acts as the electrical equivalent of the mechanical brushes in a motor. Therefore, the outputs of the commutator provide only proper phase sequencing for bidirectional operation. The magnitude information is provided to the

motor via the Motor Command and PWM ports. The outputs of the commutator must be combined with the outputs of one of the motor ports to provide proper DC brushless and stepper motor control. Figure 9 shows an example of circuitry which uses the outputs of the commutator with the Pulse output of the PWM port to control a DC brushless or

Figure 8. Codewheel Index Pulse Alignment.

Figure 9. PWM Interface to Brushless DC Motors.

Figure 10. Commutator Configuration.

stepper motor. A similar procedure could be used to combine the commutator outputs PHA-PHD with a linear amplifier interface output (Figure 16) to create a linear amplifier system.

The Commutator is programmed by the data in the following registers. Figure 10 shows an example of the relationship between all the parameters.

### Status Register (R07H)

Bit #1- 0 = 3-phase configuration, PHA, PHB, and PHC are active outputs.

> 1 = 4-phase configuration, PHA – PHD are active outputs.

Bit #2- 0 = Rotor position measured in quadrature counts (4x decoding).

> 1 = Rotor position measured in full counts (1 count = 1 codewheel bar and space.)

Bit #2 only affects the commutator's counting method. This includes the Ring register (R18H), the X and Y registers (R1AH & R1BH), the Offset register (R1CH), the Velocity Timer register (R19H), and the Maximum Advance register (R1FH).

Quadrature counts (4x decoding) are always used by the HCTL-1100 as a basis for position, velocity, and acceleration control.

### Ring Register (R18H)

The Ring register is defined as 1 electrical cycle of the commutator which corresponds to 1 torque cycle of the motor. The Ring register is scalar and determines the length of the commutation

cycle measured in full or quadrature counts as set by bit #2 in the Status register (R07H). The value of the ring must be limited to the range of 0 to 7FH.

### X Register (R1AH)

This register contains scalar data which sets the interval during which only one phase is active.

### Y Register (R1BH)

This register contains scalar data which set the interval during which two sequential phases are both active. Y is phase overlap. X and Y must be specified such that:

$$X + Y = Ring/(\# of phases)$$

[5]

These three parameters define the basic electrical commutation cycle.

### Offset Register (R1CH)

The Offset register contains two's-complement data which determines the relative start of the commutation cycle with respect to the index pulse. Since the index pulse must be physically referenced to the rotor, offset performs fine alignment between the electrical and mechanical torque cycles.

The Hold Commutator flag (F4) in the Status register (R07H) is used to decouple the internal commutator counters from the encoder input. Flag (F4) can be used in conjunction with the Offset register to allow the user to advance the commutator phases open loop. This technique may be used to create a custom commutator alignment procedure. For example, in Figure 10, case 1, for a three-phase motor where the ring = 9, X = 3, and Y = 0, the phases can be made to advance open loop by setting the Hold Commutator flag (F4) in the Flag register (R07H). When the values

0, 1, or 2 are written to the Offset register, phase A will be enabled. When the values 3, 4 or 5 are written to the Offset register, phase B will be enabled. And, when the values 6, 7, or 8 are written to the Offset register, phase C will be enabled. No values larger than the value programmed into the Ring register should be programmed into the Offset register.

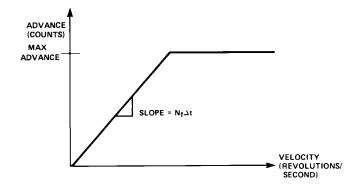

# Phase Advance Registers (R19H, R1FH)

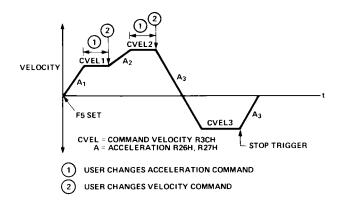

The Velocity Timer register and Maximum Advance register linearly increment the phase advance according to the measured speed for rotation up to a set maximum.

The Velocity Timer register (R19H) contains scalar data which determines the amount of phase advance at a given velocity. The phase advance is interpreted in the units set for the Ring counter by bit #2 in R07H. The velocity is measured in revolutions per second.

Advance =

$$N_t v \Delta t$$

[6]

where:

$$\Delta t = \frac{16 (R19H + 1)}{f \text{ external clk}}$$

[7]

$N_f$  = full encoder counts/ revolution.

v = velocity (revolutions/

second)

The Maximum Advance register (R1FH) contains scalar data which sets the upper limit for phase advance regardless of rotor speed.

Figure 11 shows the relationship between the Phase Advance registers. Note: If the phase advance feature is not used, set both R19H and R1FH to 0.

### **Commutator Constraints and Use**

When choosing a three-channel encoder to use with a DC brushless or stepper motor, the user should keep in mind that the number of quadrature encoder counts (4x the number of slots in the encoder's codewheel) must be an integer multiple (1x, 2x, 3x, 4x, 5x, etc.) of the number of pole pairs in the DC brushless motor or steps in a stepper motor. To take full advantage of the commutator's overlap feature, the number of quadrature counts should be at least 3 times the number of pole pairs in the DC brushless motor or steps in the stepper motor. For example, a 1.8°, (200 step/revolution) stepper motor should employ at least a 150 slot codewheel = 600 quadrature counts/revolution = 3 x 200 steps/revolution).

There are several numerical constraints the user should be aware of to use the Commutator.

The parameters of Ring, X, Y, and Max Advance must be positive numbers (00H to 7FH). Additionally, the following equation must be satisfied:

(-128D)

$$80H \le 3/2$$

Ring

+ Offset  $\pm$  Max Advance

$\le 7FH (127D)$  [8]

In order to utilize the greatest flexibility of the Commutator, it must be realized that the Commutator works on a circular ring counter principle, whose range is defined by the Ring register (R18H). This means that for a ring of 96 counts and a needed offset of 10 counts, numerically the Offset register

can be programmed as 0AH (10D) or AAH (-86D), the latter satisfying Equation 8.

If bit #2 in the Status register is set to allow the commutator to count in full counts, a higher resolution codewheel may be chosen for precise motor control without violating the commutator constraints equation (Equation 8).

Example: Suppose you want to commutate a 3-phase 15 deg/step Variable Reluctance Motor attached to a 192 count encoder.

- 1. Select 3-phase and quadrature mode for commutator by writing 0 to R07H.

- 2. With a 3-phase 15 degree/step Variable Reluctance motor the torque cycle repeats every 45 degrees or 8 times/revolution.

- 3. Ring register  $= \frac{(4)(192) \text{ counts/revolution}}{8/\text{revolution}}$

- = 96 quadrature counts

- 1 commutation cycle