# DS1707/DS1708 3.3 and 5.0-Volt MicroMonitor

#### www.maxim-ic.com

#### **FEATURES**

- Holds microprocessor in check during power transients

- Automatically restarts microprocessor after power failure

- Monitors pushbutton for external override

- Accurate 5%, 10% or 20% resets for 3.3V systems and 5% or 10% resets for 5.0V systems

- Eliminates the need for discrete components

- 20% tolerance compatible with 3.0V systems

- Pin compatible with the MAXIM MAX707/MAX708 in 8-pin DIP, 8-pin SOIC packages

- 8-pin DIP, 8-pin and μ-SOP SOIC and 8-pin μ-SOP packages available

- Industrial temperature range -40°C to +85°C

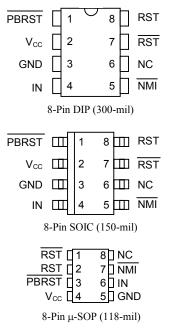

#### **PIN ASSIGNMENT**

See Mech. Drawings Section on website

DS1707 and DS1708 R/S/T

#### PIN DESCRIPTION

| PBRST    | <ul> <li>Pushbutton Reset Input</li> </ul> |

|----------|--------------------------------------------|

| $V_{CC}$ | - Power Supply                             |

| GND      | - Ground                                   |

| IN       | - Input                                    |

| NMI      | - Non-maskable Interrupt                   |

| NC       | - No Connect                               |

| RST      | - Active Low Reset Output                  |

| RST      | - Active High Reset Output                 |

#### DESCRIPTION

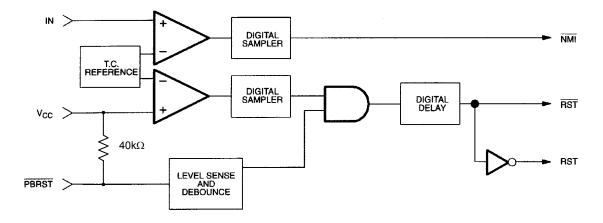

The DS1707/DS1708 3.3- or 5.0-Volt MicroMonitor monitors three vital conditions for a microprocessor: power supply, voltage sense, and external override. A precision temperature-compensated reference and comparator circuit monitor the status of  $V_{CC}$  at the device and at an upstream point for maximum protection. When the sense input detects an out-of-tolerance condition a non-maskable interrupt is generated. As the voltage at the device degrades an internal power fail signal is generated which forces the reset to an active state. When  $V_{CC}$  returns to an in-tolerance condition, the reset signal is kept in the active state for a minimum of 130 ms to allow the power supply and processor to stabilize.

1 of 10 041305

The third function the DS1707/DS1708 performs is pushbutton reset control. The DS1707/DS1708 debounces the pushbutton input and guarantees an active reset pulse width of 130 ms minimum.

#### **OPERATION**

## **Power Monitor**

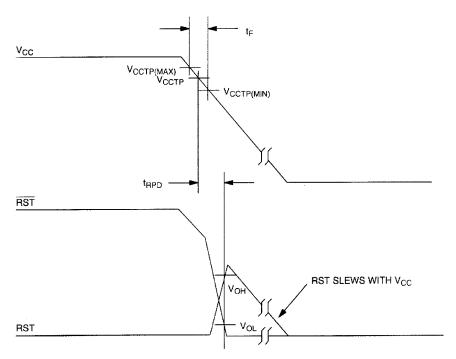

The DS1707/DS1708 detects out-of-tolerance power supply conditions and warns a processor-based system of impending power failure. When  $V_{CC}$  falls below the minimum  $V_{CC}$  tolerance, a comparator outputs the RST and  $\overline{RST}$  signals. RST and  $\overline{RST}$  are excellent control signals for a microprocessor, as processing is stopped at the last possible moment of valid  $V_{CC}$ . On power-up, RST and  $\overline{RST}$  are kept active for a minimum of 130 ms to allow the power supply and processor to stabilize.

## **Pushbutton Reset**

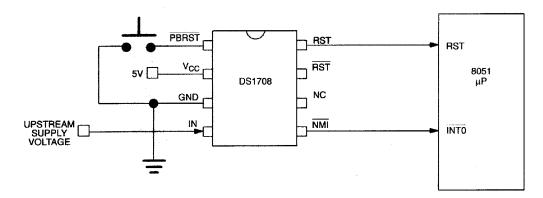

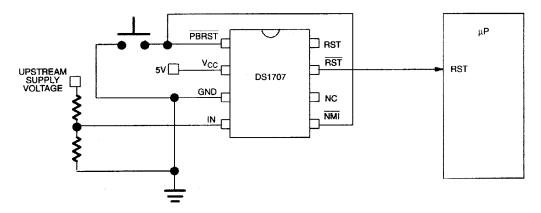

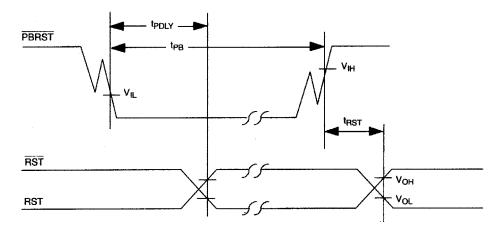

The DS1707/DS1708 provides an input pin for direct connection to a pushbutton reset (see Figure 2). The pushbutton reset input requires an active low signal. Internally, this input is debounced and timed such that RST and RST signals of at least 130 ms minimum will be generated. The 130 ms delay commences as the pushbutton reset input is released from the low level. The pushbutton can be initiated by connecting the NMI output to the PBRST input as shown in Figure 3.

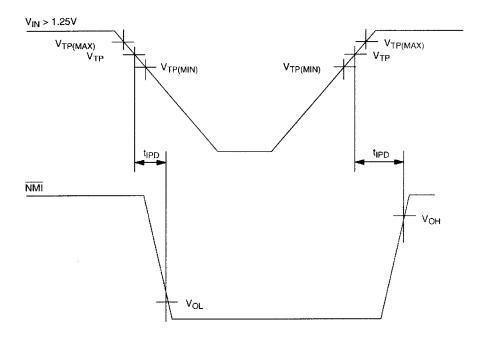

## Non-Maskable Interrupt

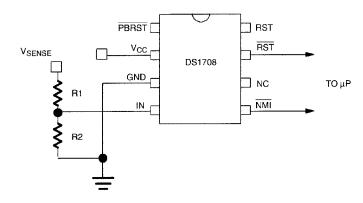

The DS1707/DS1708 generates a non-maskable interrupt (NMI) for early warning of a power failure. A precision comparator monitors the voltage level at the IN pin relative to an on-chip reference generated by an internal band gap. The IN pin is a high impedance input allowing for a user-defined sense point. An external resistor voltage divider network (Figure 5) is used to interface with high voltage signals. This sense point may be derived from a regulated supply or from a higher DC voltage level closer to the main system power input. Since the IN trip point  $V_{TP}$  is 1.25 volts, the proper values for R1 and R2 can be determined by the equation as shown in Figure 5. Proper operation of the DS1707/DS1708 requires that the voltage at the IN pin be limited to  $V_{CC}$ . Therefore, the maximum allowable voltage at the supply being monitored ( $V_{MAX}$ ) can also be derived as shown in Figure 5. A simple approach to solving the equation is to select a value for R2 high enough to keep power consumption low, and solve for R1. The flexibility of the IN input pin allows for detection of power loss at the earliest point in a power supply system, maximizing the amount of time for system shut-down between  $\overline{NMI}$  and RST/ $\overline{RST}$ .

When the supply being monitored decays to the voltage sense point, the DS1707/DS1708 pulses the NMI output to the active state for a minimum 200  $\mu$ s. The NMI power-fail detection circuitry also has built-in hysteresis of 100  $\mu$ V. The supply must be below the voltage sense point for approximately 5  $\mu$ s before a low NMI will be generated. In this way, power supply noise is removed from the monitoring function, preventing false interrupts. During a power-up, any detected IN pin levels below  $V_{TP}$  by the comparator are disabled from generating an interrupt until  $V_{CC}$  rises to  $V_{CCTP}$ . As a result, any potential NMI pulse will not be initiated until  $V_{CC}$  reaches  $V_{CCTP}$ .

Connecting NMI to PBRST would allow the non-maskable interrupt to generate an automatic reset when an out-of-tolerance condition occurred in a monitored supply. An example is shown in Figure 3.

# **MICROMONITOR BLOCK DIAGRAM** Figure 1

## **PUSHBUTTON RESET** Figure 2

# PUSHBUTTON RESET CONTROLLED BY NMI Figure 3

# TIMING DIAGRAM: PUSHBUTTON RESET Figure 4

## NON-MASKABLE INTERRUPT CIRCUIT EXAMPLE Figure 5

$$V_{SENSE} = \frac{R1+R2}{R2} \ X \ 1.25 \qquad \qquad V_{MAX} = \frac{V_{SENSE}}{V_{TP}} \ X \ V_{CC}$$

Example:  $V_{SENSE} = 4.50V$  at the trip point

$V_{CC} = 3.3V$  $10 \text{ k}\Omega = R2$

Therefore:  $\frac{4.50}{1.25}$  X 3.3 = 11.88V maximum

$$4.50 = \frac{R1 + 10k}{10k} \times 1.25$$

$R1 = 26 \text{ k}\Omega$

# TIMING DIAGRAM: NON-MASKABLE INTERRUPT Figure 6

# TIMING DIAGRAM: POWER-DOWN Figure 7

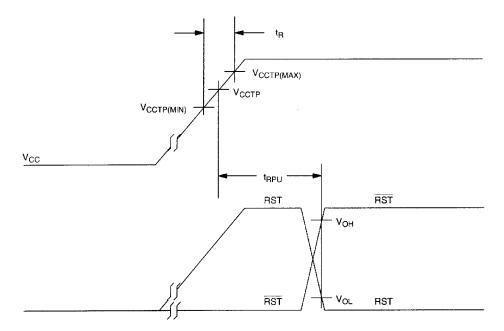

# TIMING DIAGRAM: POWER UP Figure 8

## **ABSOLUTE MAXIMUM RATINGS\***

Voltage on  $V_{CC}$  Pin Relative to Ground

Voltage on I/O Relative to Ground\*\*

Operating Temperature

Storage Temperature

Voltage on I/O Relative to Ground\*\*

-0.5V to +7.0V

-0.5V to  $V_{CC}$  + 0.5V

-40°C to +85°C

-55°C to +125°C

260°C for 10 seconds

## RECOMMENDED DC OPERATING CONDITIONS

(-40°C to +85°C)

| PARAMETER              | SYMBOL          | MIN           | TYP | MAX                  | UNITS | NOTES |

|------------------------|-----------------|---------------|-----|----------------------|-------|-------|

| Supply Voltage         | $V_{CC}$        | 1.2           |     | 5.5                  | V     | 1     |

| PBRST Input High Level | $V_{ m IH}$     | 2.0           |     | V <sub>CC</sub> +0.3 | V     | 1, 3  |

|                        |                 | $V_{CC}$ -0.5 |     |                      |       | 1, 4  |

| PBRST Input Low Level  | V <sub>IL</sub> | -0.03         |     | +0.5                 | V     | 1     |

## **DC ELECTRICAL CHARACTERISTICS** (-40°C to +85°C; $V_{CC}$ =1.2V to 5.5V)

| PARAMETER                           | SYMBOL            | MIN                  | TYP                  | MAX  | UNITS | NOTES |

|-------------------------------------|-------------------|----------------------|----------------------|------|-------|-------|

| V <sub>CC</sub> Trip Point DS1707   | $V_{CCTP}$        | 4.50                 | 4.65                 | 4.75 | V     | 1     |

| V <sub>CC</sub> Trip Point DS1708   | $V_{CCTP}$        | 4.25                 | 4.40                 | 4.50 | V     | 1     |

| V <sub>CC</sub> Trip Point DS1708T  | $V_{CCTP}$        | 3.00                 | 3.08                 | 3.15 | V     | 1     |

| V <sub>CC</sub> Trip Point DS1708S  | $V_{CCTP}$        | 2.85                 | 2.93                 | 3.00 | V     | 1     |

| V <sub>CC</sub> Trip Point DS1708R  | $V_{CCTP}$        | 2.55                 | 2.63                 | 2.70 | V     | 1     |

| Input Leakage                       | $I_{\mathrm{IL}}$ | -1.0                 |                      | +1.0 | μΑ    | 2     |

| Output Current @ 2.4V               | $I_{OH}$          |                      | 350                  |      | μΑ    | 3     |

| Output Current @ 0.4V               | $I_{OL}$          | 10                   |                      |      | mA    | 3     |

| Output Voltage @ -500μA             | $V_{OH}$          | V <sub>CC</sub> -0.3 | V <sub>CC</sub> -0.1 |      | V     | 3     |

| Operating Current @ $V_{CC} < 5.5V$ | $I_{CC}$          |                      |                      | 60   | μΑ    | 5     |

| Operating Current @ $V_{CC} < 3.6V$ | $I_{CC}$          |                      |                      | 50   | μΑ    | 5     |

| IN Input Trip Point                 | $V_{TP}$          | 1.20                 | 1.25                 | 1.30 | V     | 1     |

## **CAPACITANCE** $(t_A=25^{\circ}C)$

| PARAMETER          | SYMBOL           | MIN | TYP | MAX | UNITS | NOTES |

|--------------------|------------------|-----|-----|-----|-------|-------|

| Input Capacitance  | $C_{IN}$         |     |     | 5   | pF    |       |

| Output Capacitance | C <sub>OUT</sub> |     |     | 7   | pF    |       |

<sup>\*</sup> This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability.

<sup>\*\*</sup> The voltage input limits on IN and PBRST can be exceeded if the input current is less than 10 mA.

# AC ELECTRICAL CHARACTERISTICS (-40°C to +85°C; V<sub>CC</sub>=1.2V to 5.5V)

| PARAMETER                                                               | SYMBOL             | MIN | TYP | MAX | UNITS | NOTES |

|-------------------------------------------------------------------------|--------------------|-----|-----|-----|-------|-------|

| $\overline{PBRST} = V_{IL}$                                             | $t_{\mathrm{PB}}$  | 150 |     |     | ns    |       |

| Reset Active Time                                                       | $t_{RST}$          | 130 | 205 | 285 | ms    |       |

| $V_{CC}$ Detect to RST and $\overline{RST}$                             | $t_{ m RPD}$       |     | 5   | 8   | μs    | 7     |

| V <sub>CC</sub> Slew Rate                                               | $t_{\mathrm{F}}$   | 20  |     |     | μs    |       |

| V <sub>CC</sub> Detect to RST and RST                                   | $t_{ m RPU}$       | 130 | 205 | 285 | ms    | 6     |

| V <sub>CC</sub> Slew Rate                                               | $t_R$              | 0   |     |     | ns    |       |

| $\overline{\text{PBRST}}$ Stable Low to RST and $\overline{\text{RST}}$ | $t_{ m PDLY}$      |     |     | 250 | ns    |       |

| VIN Detect to NMI                                                       | $t_{\mathrm{IPD}}$ |     | 5   | 8   | μs    | 7     |

## **NOTES:**

- 1. All voltages are referenced to ground.

- 2. PBRST is internally pulled up to  $V_{CC}$  with an internal impedance of 40 k $\Omega$  typical.

- $3. \quad V_{CC} \geq 2.4V$

- 4.  $V_{CC} < 2.4V$

- 5. Measured with outputs open and all inputs at  $V_{\text{CC}}$  or ground.

- 6.  $t_R = 5 \mu s$

- 7. Noise immunity pulses  $\leq$  2  $\mu$ s at  $V_{CCTP}$  minimum will not cause a reset.

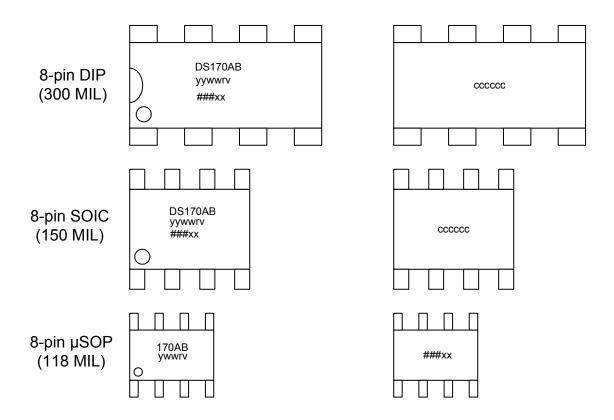

## **PART MARKING CODES**

| Brand Codes |                                    |                                           |  |  |  |

|-------------|------------------------------------|-------------------------------------------|--|--|--|

| Code        | Description                        | Values                                    |  |  |  |

| AB          | Device type and tolerance          | 7_, 8_, 8R, 8S, 8T (where'_' is a blank)  |  |  |  |

| yww or yyww | Date Code. Identifies the year and | y, the last digit of the year.            |  |  |  |

|             | work week the device was           | yy, the last two digits of the year.      |  |  |  |

|             | assembled.                         | ww, the work week (values 01 through 52). |  |  |  |

| rv          | Die Revision                       | A letter followed by a number (eg. B1)    |  |  |  |

| ###xx       | Lot Code                           | Three numbers followed by 2 letters       |  |  |  |

| ccccc       | Country of Assembly                | Abbreviation of country name.             |  |  |  |

## **ORDERING INFORMATION**

| ORDERING   | PACKAGE              | OPERATING      | VERSION                     |

|------------|----------------------|----------------|-----------------------------|

| NUMBER     |                      | TEMPERATURE    |                             |

| DS1707EPA  | 8-pin DIP (300mil)   | -40°C TO +85°C | 5V-5% MONITOR, /RST, RST    |

| DS1707ESA  | 8-pin SOIC (150 mil) | -40°C TO +85°C | 5V-5% MONITOR, /RST, RST    |

| DS1707EUA  | 8-pin μSOP (118 mil) | -40°C TO +85°C | 5V-5% MONITOR, /RST, RST    |

| DS1708EPA  | 8-pin DIP (300mil)   | -40°C TO +85°C | 5V-10% MONITOR, /RST, RST   |

| DS1708ESA  | 8-pin SOIC (150 mil) | -40°C TO +85°C | 5V-10% MONITOR, /RST, RST   |

| DS1708EUA  | 8-pin μSOP (118 mil) | -40°C TO +85°C | 5V-10% MONITOR, /RST, RST   |

| DS1708REPA | 8-pin DIP (300mil)   | -40°C TO +85°C | 3.3V-20% MONITOR, /RST, RST |

| DS1708RESA | 8-pin SOIC (150 mil) | -40°C TO +85°C | 3.3V-20% MONITOR, /RST, RST |

| DS1708REUA | 8-pin μSOP (118 mil) | -40°C TO +85°C | 3.3V-20% MONITOR, /RST, RST |

| DS1708SEPA | 8-pin DIP (300mil)   | -40°C TO +85°C | 3.3V-10% MONITOR, /RST, RST |

| DS1708SESA | 8-pin SOIC (150 mil) | -40°C TO +85°C | 3.3V-10% MONITOR, /RST, RST |

| DS1708SEUA | 8-pin μSOP (118 mil) | -40°C TO +85°C | 3.3V-10% MONITOR, /RST, RST |

| DS1708TEPA | 8-pin DIP (300mil)   | -40°C TO +85°C | 3.3V-5% MONITOR, /RST, RST  |

| DS1708TESA | 8-pin SOIC (150 mil) | -40°C TO +85°C | 3.3V-5% MONITOR, /RST, RST  |

| DS1708TEUA | 8-pin μSOP (118 mil) | -40°C TO +85°C | 3.3V-5% MONITOR, /RST, RST  |

<sup>\*</sup>Contact factory for availability of Pb-free versions.

E = -40°C to +85°C temperature range

A = 8 lead device

P = Plastic DIP (300 mil) S = SOIC (150 mil)

$U = \mu SOP (118 \text{ mil})$