# CD Digital Signal Processor with Built-in Digital Servo Preliminary

### Description

The CXD3068Q is a digital signal processor LSI for CD players. This LSI incorporates a digital servo.

### Features

- All digital signal processings during playback are performed with a single chip

- Highly integrated mounting possible due to a builtin RAM

### **Digital Signal Processor (DSP) Block**

- Playback mode supporting CAV (Constant Angular Velocity)

- Frame jitter free

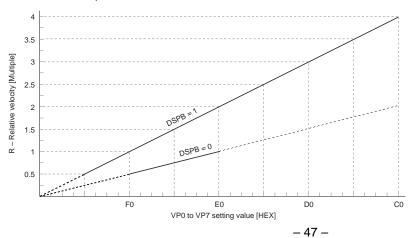

- $0.5 \times$  to  $4 \times$  continuous playback possible

- Allows relative rotational velocity readout

- Wide capture range playback mode

- Spindle rotational velocity following method

Supports 1× to 4× playback variable pitch

- Supports 1× to 4× playback variable pitch playback

- Bit clock, which strobes the EFM signal, is generated by the digital PLL.

- EFM data demodulation

- Enhanced EFM frame sync signal protection

- Refined super strategy-based powerful error correction

C1: double correction, C2: quadruple correction

- Supported during 4× playback

- Noise reduction during track jumps

- Auto zero-cross mute

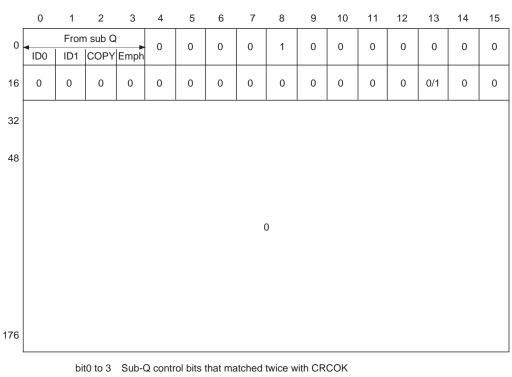

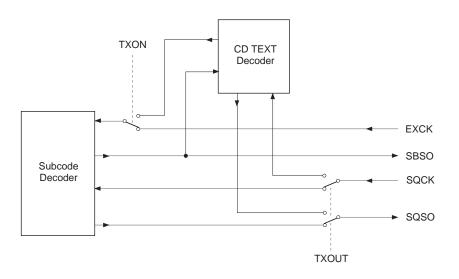

- Subcode demodulation and Sub-Q data error detection

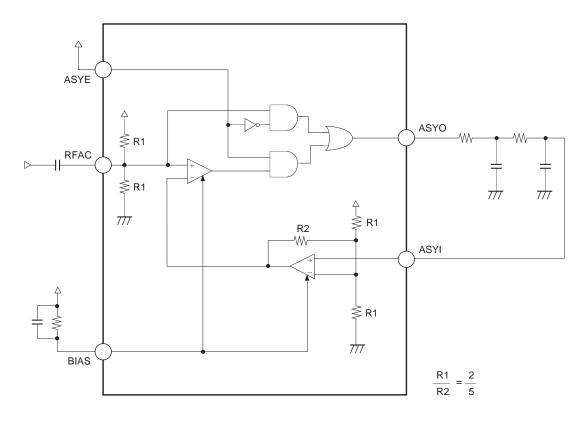

- Digital spindle servo

- 16-bit traverse counter

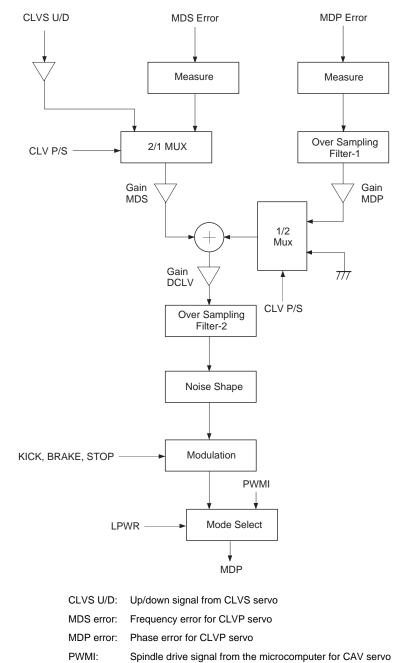

- Asymmetry correction circuit

- CPU interface on serial bus

- Error correction monitor signal, etc. output from a new CPU interface

- · Servo auto sequencer

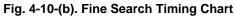

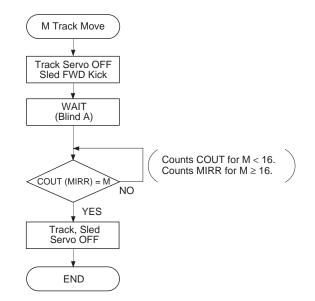

- Fine search performs track jumps with high accuracy

- Digital audio interface output

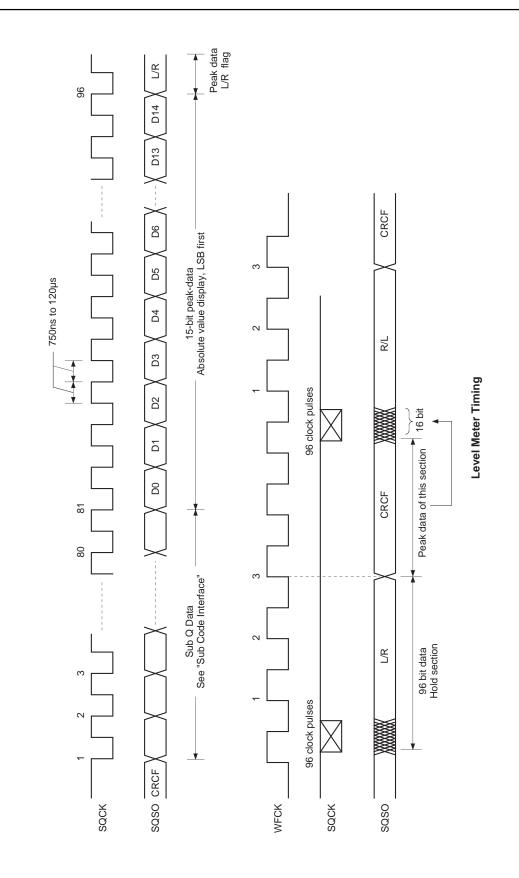

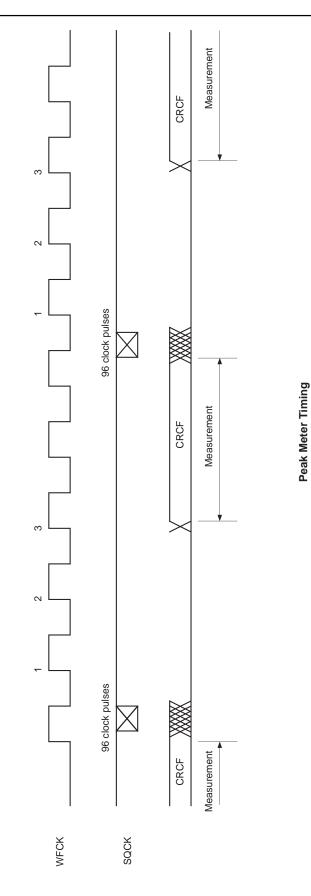

- Digital level meter, peak meter

- Bilingual supported

- VCO control mode

- CD TEXT data demodulation

- EFM playability reinforcement function

### Digital Servo (DSSP) Block

- Microcomputer software-based flexible servo control

- Offset cancel function for servo error signal

- Auto gain control function for servo loop

- E:F balance, focus bias adjustment function

- Surf jump function supporting micro two-axis

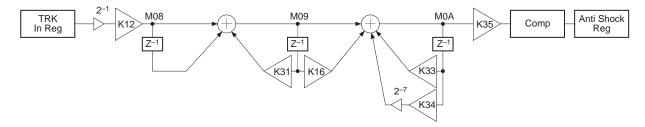

- Tracking filter: 6 stages

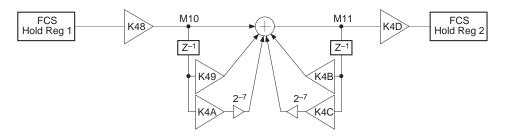

- Focus filter: 5 stages

### Applications

CD players

### Structure

Silicon gate CMOS IC

### **Absolute Maximum Ratings**

| <ul> <li>Supply voltage</li> </ul>           | VDD        | -0.5 to +4.6    | V     |

|----------------------------------------------|------------|-----------------|-------|

| <ul> <li>Input voltage</li> </ul>            | Vi         | -0.5 to +4.6    | V     |

|                                              | (Vss –     | 0.5V to VDD + ( | ).5V) |

| <ul> <li>Output voltage</li> </ul>           | Vo         | -0.5 to +4.6    | Ý     |

|                                              | (Vss –     | 0.5V to VDD + ( | ).5V) |

| • Storage temperature                        | Tstg       | -55 to +150     | °C    |

| <ul> <li>Supply voltage different</li> </ul> | ce         |                 |       |

|                                              | Vss-AVss   | -0.3 to +0.3    | V     |

|                                              | Vdd – AVdd | -0.3 to +0.3    | V     |

| Note) AVpp includes )                        |            | Vss includes X  | Vee   |

Note) AVDD includes XVDD and AVss includes XVss.

### Recommended Operating Conditions

| • | Supply voltage      | Vdd | 2.7 to 3.6 | V |

|---|---------------------|-----|------------|---|

| • | Operating temperate | ure |            |   |

Topr –20 to +75 ℃

### Input/Output Capacitance

| Input pin       | Cı             | 9 (Max.)      | pF |

|-----------------|----------------|---------------|----|

| Output pin      | Co             | 11 (Max.)     | рF |

| • I/O pin       | Ci/O           | 11 (Max.)     | pF |

| Note) Measureme | ent conditions | VDD = VI = 0V | •  |

| •               |                | fм = 1MHz     |    |

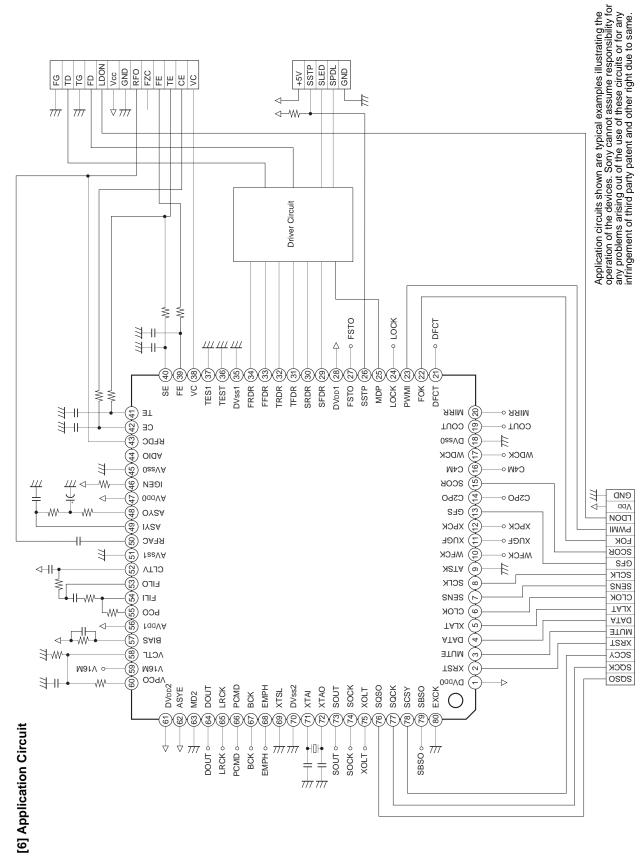

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

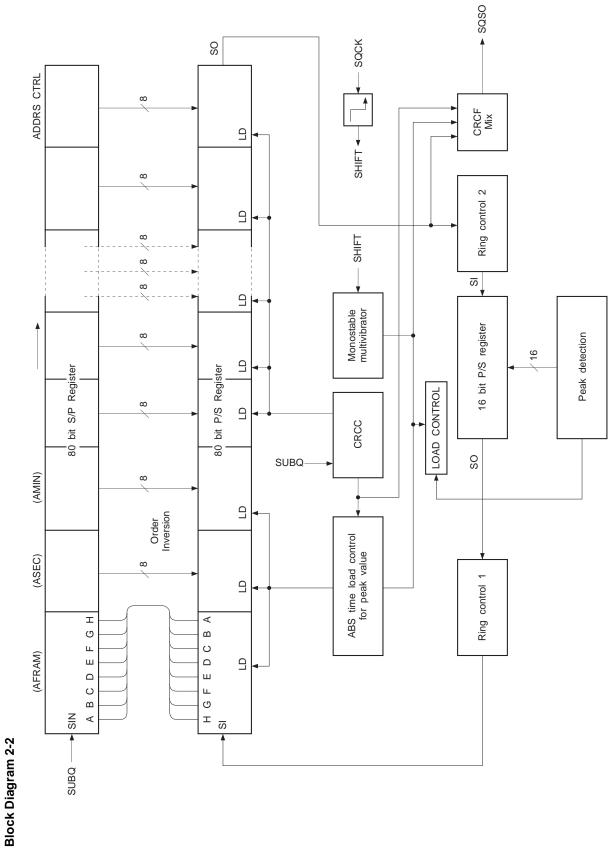

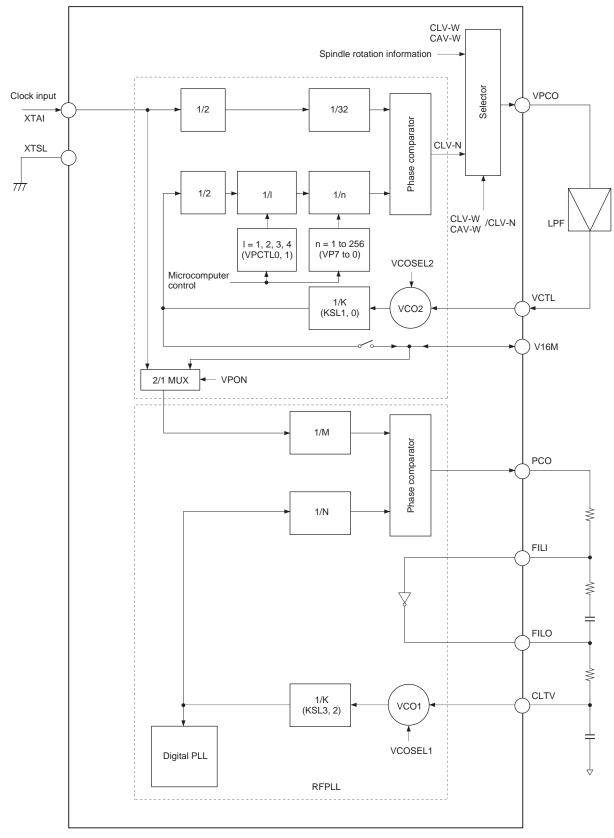

### **Block Diagram** XUGF GFS EMPH WFCK WDCK C2PO LLRCK PCMD BCK MUTE XTAO XTSL V16M VPCO VCTL XTAI 17 14 65 66 67 3 11)(13)(68)(10) (72)(69)(59)(60)(58) (37) TES1 (36) TEST FSTO (27) Clock Error (2) XRST (16)Generator Corrector C4M EFM D/A demodurator RFAC (50) Interface ASYI (49) Asymmetry ASYO (48) Corrector ASYE (62) 32K (63) MD2 Digital BIAS (57) RAM OUT ►64) DOUT XPCK (12) Sub Code FILO (53) Processor Digital FILI (54) PLL PCO (55) CLTV (52) MDP (25) Digital LOCK (24) CLV PWMI (23) SENS (7 DATA(4)XLAT (5 CLOK (6) SCOR (15) CPU SBSO (79) Interface EXCK (80) Servo SCSY (78) Auto Sequencer SQSO (76) SQCK (77) Signal processor block Servo block (73) SOUT ►(74) SOCK ►(75) XOLT SERVO (8) SCLK Interface ►(19) COUT -(26) SSTP ►(9) ATSK ►20) MIRR MIRR ►(21) DFCT DFCT RFDC (43) FOK ►(22) FOK CE (42) SERVO DSP PWM GENERATOR ΤE (41 ►(33) FFDR FOCUS PWM OPAmp A/D SE (40) FOCUS SERVO ►34) FRDR Analog SW Converter GENERATOR . . . . . . . . . . . FE (39) ►(31) TFDR TRACKING PWM TRACKING VC (38) GENERATOR SERVO •(32) TRDR IGEN (46 SLED PWM ►29 SFDR SLED SERVO GENERATOR ►(30) SRDR (44 ADIO

- 2 -

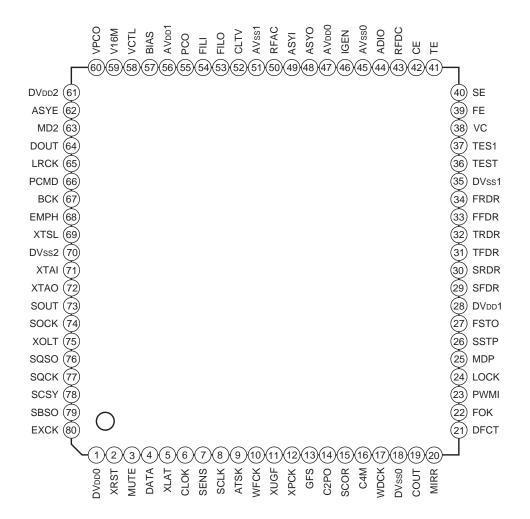

### **Pin Configuration**

### **Pin Description**

| Pin<br>No. | Symbol | I/O |         | Description                                                                                                                                                       |

|------------|--------|-----|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | DVdd0  | —   |         | Digital power supply.                                                                                                                                             |

| 2          | XRST   | Ι   |         | System reset. Reset when low.                                                                                                                                     |

| 3          | MUTE   | Ι   |         | Mute input (low: off, high: on)                                                                                                                                   |

| 4          | DATA   | Ι   |         | Serial data input from CPU.                                                                                                                                       |

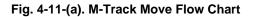

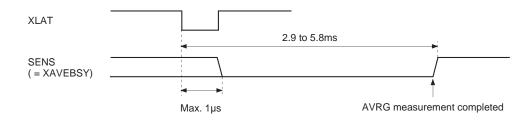

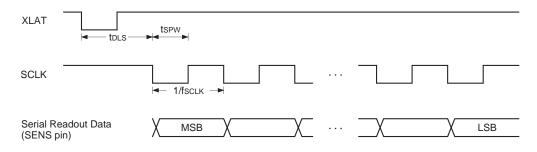

| 5          | XLAT   | Ι   |         | Latch input from CPU. Serial data is latched at the falling edge.                                                                                                 |

| 6          | CLOK   | Ι   |         | Serial data transfer clock input from CPU.                                                                                                                        |

| 7          | SENS   | 0   | 1, 0    | SENS output to CPU.                                                                                                                                               |

| 8          | SCLK   | I   |         | SENS serial data readout clock input.                                                                                                                             |

| 9          | ATSK   | I/O | 1, 0    | Anti-shock input/output.                                                                                                                                          |

| 10         | WFCK   | 0   | 1, 0    | WFCK output.                                                                                                                                                      |

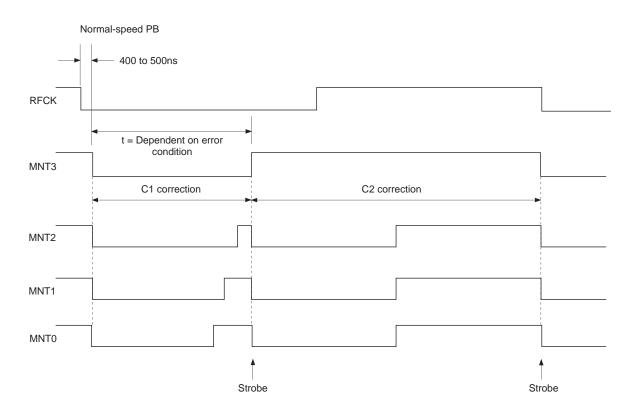

| 11         | XUGF   | 0   | 1, 0    | XUGF output. MNT0 or RFCK is output by switching with the command.                                                                                                |

| 12         | XPCK   | 0   | 1, 0    | XPCK output. MNT1 is output by switching with the command.                                                                                                        |

| 13         | GFS    | 0   | 1, 0    | GFS output. MNT2 or XROF is output by switching with the command.                                                                                                 |

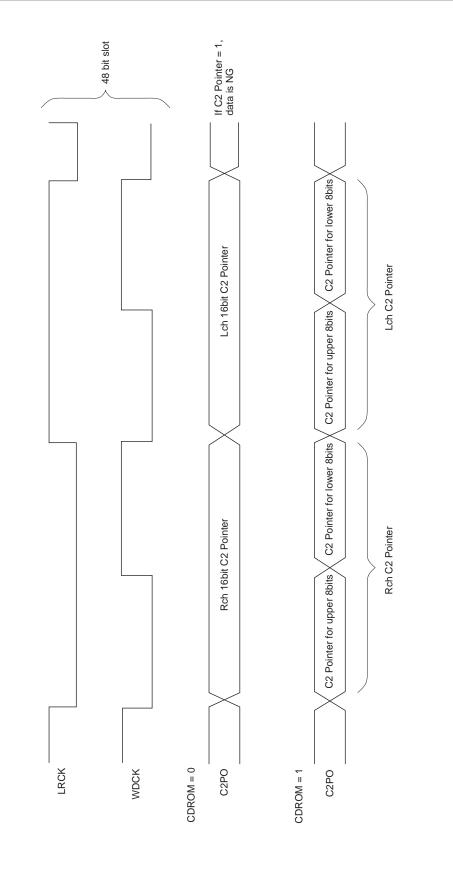

| 14         | C2PO   | 0   | 1, 0    | G2PO output. MNT3 or GTOP is output by switching with the command.                                                                                                |

| 15         | SCOR   | 0   | 1, 0    | Outputs a high signal when either subcode sync S0 or S1 is detected.                                                                                              |

| 16         | C4M    | 0   | 1, 0    | 4.2336MHz output. 1/4 frequency division output for V16M in CAV-W mode or variable pitch mode.                                                                    |

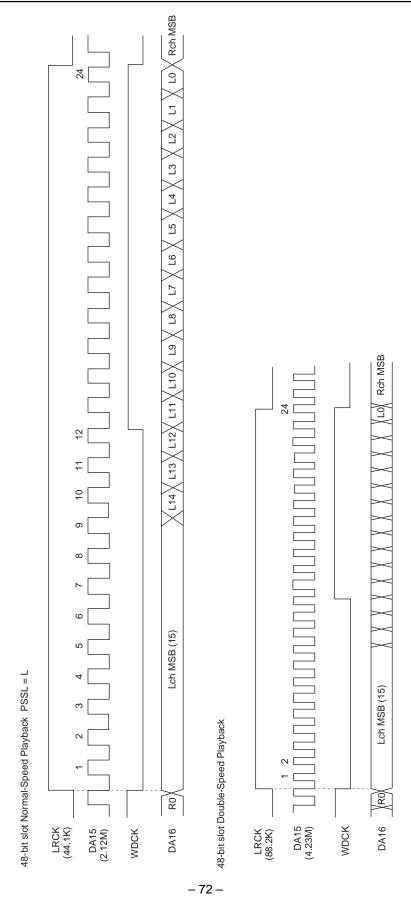

| 17         | WDCK   | 0   | 1, 0    | Word clock output. $f = 2Fs$ . GRSCOR is output by the command switching.                                                                                         |

| 18         | DVss0  | —   |         | Digital GND.                                                                                                                                                      |

| 19         | COUT   | I/O | 1, 0    | Track count signal I/O.                                                                                                                                           |

| 20         | MIRR   | I/O | 1, 0    | Mirror signal I/O.                                                                                                                                                |

| 21         | DFCT   | I/O | 1, 0    | Detect signal I/O.                                                                                                                                                |

| 22         | FOK    | I/O | 1, 0    | Focus OK signal I/O.                                                                                                                                              |

| 23         | PWMI   | Ι   |         | Spindle motor external control input.                                                                                                                             |

| 24         | LOCK   | 1/0 | 1, 0    | GFS is sampled at 460Hz; when GFS is high, this pin outputs a high signal.<br>If GFS is low eight consecutive samples, this pin outputs low. Input when LKIN = 1. |

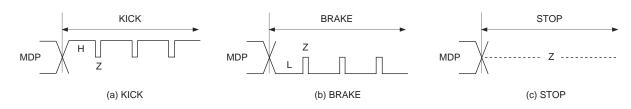

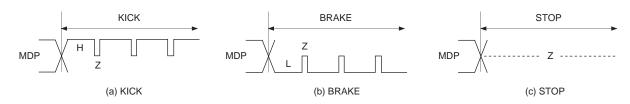

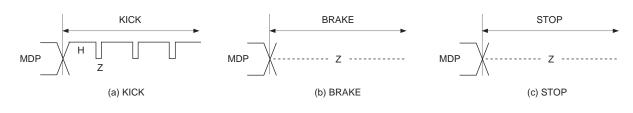

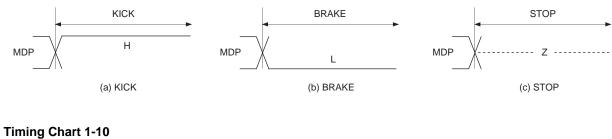

| 25         | MDP    | 0   | 1, Z, 0 | Spindle motor servo control output.                                                                                                                               |

| 26         | SSTP   | Ι   |         | Disc innermost track detection signal input.                                                                                                                      |

| 27         | FSTO   | 0   | 1, 0    | 2/3 frequency division output for XTAI pin.                                                                                                                       |

| 28         | DVDD1  | —   | —       | Digital power supply.                                                                                                                                             |

| 29         | SFDR   | 0   | 1, 0    | Sled drive output.                                                                                                                                                |

| 30         | SRDR   | 0   | 1, 0    | Sled drive output.                                                                                                                                                |

| 31         | TFDR   | 0   | 1, 0    | Tracking drive output.                                                                                                                                            |

| 32         | TRDR   | 0   | 1, 0    | Tracking drive output.                                                                                                                                            |

| 33         | FFDR   | 0   | 1, 0    | Focus drive output.                                                                                                                                               |

| Pin<br>No. | Symbol | I/O    |         | Description                                                                                                       |  |  |

|------------|--------|--------|---------|-------------------------------------------------------------------------------------------------------------------|--|--|

| 34         | FRDR   | 0      | 1, 0    | Focus drive output.                                                                                               |  |  |

| 35         | DVss1  | —      |         | Digital GND.                                                                                                      |  |  |

| 36         | TEST   | Ι      |         | Test. Normally, GND.                                                                                              |  |  |

| 37         | TES1   | Ι      |         | Test. Normally, GND.                                                                                              |  |  |

| 38         | VC     | Ι      |         | Center voltage input.                                                                                             |  |  |

| 39         | FE     | Ι      |         | Focus error signal input.                                                                                         |  |  |

| 40         | SE     | Т      |         | Sled error signal input.                                                                                          |  |  |

| 41         | TE     | Т      |         | Tracking error signal input.                                                                                      |  |  |

| 42         | CE     | Ι      |         | Center servo analog input.                                                                                        |  |  |

| 43         | RFDC   | Ι      |         | RF signal input.                                                                                                  |  |  |

| 44         | ADIO   | 0      | Analog  | Test. No connected.                                                                                               |  |  |

| 45         | AVss0  | —      |         | Analog GND.                                                                                                       |  |  |

| 46         | IGEN   | 1      |         | Constant current input for operational amplifier.                                                                 |  |  |

| 47         | AVdd0  | —      |         | Analog power supply.                                                                                              |  |  |

| 48         | ASYO   | O 1, 0 |         | EFM full-swing output. (low = Vss, high = VDD)                                                                    |  |  |

| 49         | ASYI   | Ι      |         | Asymmetry comparator voltage input.                                                                               |  |  |

| 50         | RFAC   | Ι      |         | EFM signal input.                                                                                                 |  |  |

| 51         | AVss1  | —      |         | Analog GND.                                                                                                       |  |  |

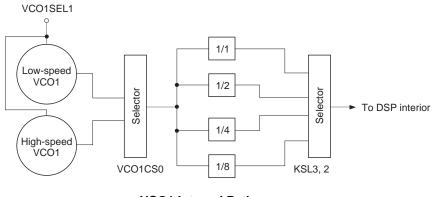

| 52         | CLTV   | Ι      |         | Multiplier VCO1 control voltage input.                                                                            |  |  |

| 53         | FILO   | 0      | Analog  | Master PLL filter output (slave = digital PLL).                                                                   |  |  |

| 54         | FILI   | 1      |         | Master PLL filter input.                                                                                          |  |  |

| 55         | PCO    | 0      | 1, Z, 0 | Master PLL charge pump output.                                                                                    |  |  |

| 56         | AVDD1  | —      |         | Analog power supply.                                                                                              |  |  |

| 57         | BIAS   | Ι      |         | Asymmetry circuit constant current input.                                                                         |  |  |

| 58         | VCTL   | Ι      |         | Wide-band EFM PLL VCO2 control voltage input.                                                                     |  |  |

| 59         | V16M   | I/O    | 1, 0    | Wide-band EFM PLL VCO2 oscillation output. Serves as wide-band EFM PLL clock input by switching with the command. |  |  |

| 60         | VPCO   | 0      | 1, Z, 0 | Wide-band EFM PLL charge pump output.                                                                             |  |  |

| 61         | DVdd2  | —      |         | Digital power supply.                                                                                             |  |  |

| 62         | ASYE   | Ι      |         | Asymmetry circuit on/off (low = off, high = on).                                                                  |  |  |

| 63         | MD2    | Ι      |         | Digital Out on/off control (low = off, high = on).                                                                |  |  |

| 64         | DOUT   | 0      | 1, 0    | Digital Out output.                                                                                               |  |  |

| 65         | LRCK   | 0      | 1, 0    | D/A interface. LR clock output. f = Fs                                                                            |  |  |

| 66         | PCMD   | 0      | 1, 0    | D/A interface. Serial data output (two's complement, MSB first).                                                  |  |  |

| 67         | ВСК    | 0      | 1, 0    | D/A interface. Bit clock output.                                                                                  |  |  |

| Pin<br>No. | Symbol | I/O |      | Description                                                                                            |

|------------|--------|-----|------|--------------------------------------------------------------------------------------------------------|

| 68         | EMPH   | 0   | 1, 0 | Outputs a high signal when the playback disc has emphasis, and a low signal when there is no emphasis. |

| 69         | XTSL   | I   |      | Crystal selection input. Low when the crystal is 16.9344MHz; high when it is 33.8688MHz.               |

| 70         | DVss2  | —   | —    | Digital GND.                                                                                           |

| 71         | ΧΤΑΙ   | I   |      | Crystal oscillation circuit input. When the master clock is input externally, input it from this pin.  |

| 72         | XTAO   | 0   |      | Crystal oscillation circuit output.                                                                    |

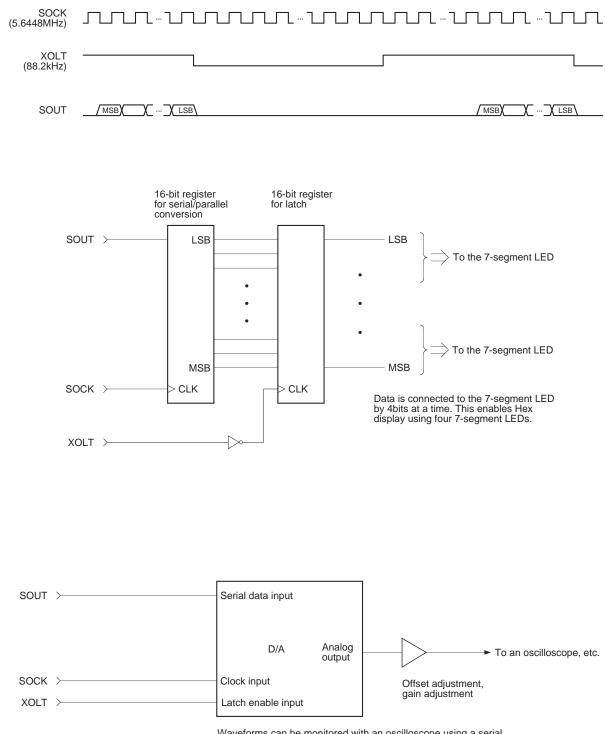

| 73         | SOUT   | 0   | 1, 0 | Serial data output in servo block.                                                                     |

| 74         | SOCK   | 0   | 1, 0 | Serial data readout clock output in servo block.                                                       |

| 75         | XOLT   | 0   | 1, 0 | Serial data latch output in servo block.                                                               |

| 76         | SQSO   | 0   | 1, 0 | Sub-Q 80-bit, PCM peak or level data outputs. CD TEXT data output.                                     |

| 77         | SQCK   | Ι   |      | SQSO readout clock input.                                                                              |

| 78         | SCSY   | Ι   |      | GRSCOR resynchronization input.                                                                        |

| 79         | SBSO   | 0   | 1, 0 | Sub-Q P to W serial output.                                                                            |

| 80         | EXCK   | Ι   |      | SBSO readout clock input.                                                                              |

### Notes)

- PCMD is a MSB first, two's complement output.

- GTOP is used to monitor the frame sync protection status. (High: sync protection window released.)

- XUGF is the frame sync obtained from the EFM signal, and is negative pulse. It is the signal before sync protection.

- XPCK is the inverse of the EFM PLL clock. The PLL is designed so that the falling edge and the EFM signal transition point coincide.

- The GFS signal goes high when the frame sync and the insertion protection timing match.

- RFCK is derived from the crystal accuracy, and has a cycle of 136µs. (during normal speed)

- C2PO represents the data error status.

- XROF is generated when the 32K RAM exceeds the ±28F jitter margin.

### **Combination of Monitor Pin Outputs**

| Comm  | and bit |             |      |      |      |  |  |  |

|-------|---------|-------------|------|------|------|--|--|--|

| MTSL1 | MTSL0   | Output data |      |      |      |  |  |  |

| 0     | 0       | XUGF        | XPCK | GFS  | C2PO |  |  |  |

| 0     | 1       | MNT0        | MNT1 | MNT2 | MNT3 |  |  |  |

| 1     | 0       | RFCK        | XPCK | XROF | GTOP |  |  |  |

### **Electrical Characteristics**

### 1. DC Characteristics

| $(V_{DD} = AV_{DD} = 3.3 \pm 0.3V, V_{SS} = AV_{SS} = 0V, T_{OPT}$ | $= -20$ to $+75^{\circ}$ C) |

|--------------------------------------------------------------------|-----------------------------|

|--------------------------------------------------------------------|-----------------------------|

|                         |             |      |                               |           |      | -      |      | Applicable    |

|-------------------------|-------------|------|-------------------------------|-----------|------|--------|------|---------------|

| ŀ                       | tem         |      | Conditions                    | Min.      | Тур. | Max.   | Unit | pins          |

| Input voltage (1)       | High level  | VIH1 |                               | 0.7Vdd    |      |        | V    | *1, *9        |

| input voltage (1)       | Low level   | VIL1 |                               |           |      | 0.2Vdd | V    | *1, *9        |

| Input voltage (2)       | High level  | VIH2 | Vı ≤ 5.5V                     | 0.8Vdd    |      |        | V    | *2            |

| input voltage (2)       | Low level   | VIL2 | VI <u>S</u> 3.3 V             |           |      | 0.2Vdd | V    | ** <b>Z</b>   |

| Input voltage (3)       | High level  | Vінз | $V_{I} \leq 5.5V$             | 0.8Vdd    |      |        | V    | *3            |

| input voltage (3)       | Low level   | VIL3 | Schmitt input                 |           |      | 0.2Vdd | V    | *5            |

| Input voltage (4)       |             | Vin4 | Analog input                  | Vss       |      | Vdd    | V    | *4, *5        |

|                         | High level  | Vон1 | Іон = −4mA<br>Іо∟ = 4mA       | Vdd - 0.4 |      | Vdd    | V    | *6, *8,<br>*9 |

| Output voltage (1)      | Low level   | Vol1 |                               | 0         |      | 0.4    | V    |               |

| Output voltage (2)      | High level  | Vон2 | Іон = –0.28mA<br>Іон = 0.36mA | Vdd - 0.5 |      | Vdd    | V    | *7            |

| Oulput voltage (2)      | Low level   | Vol2 |                               | 0         |      | 0.4    | V    | ~7            |

| Input leak current (1)  |             | IL11 | VI = Vss or<br>VDD            | -10       |      | 10     | μA   | *1, *4        |

| Input leak current (2)  |             | ILI2 | $V_{I} = 0$ to 5.5V           | -10       |      | 10     | μA   | *2, *3        |

| Input leak current (3)  |             | Ilis | VI = Vss or<br>VDD            | -40       |      | 40     | μA   | *9            |

| Input leak current (4)  |             | ILI4 | VI = 0.25VDD<br>to 0.75VDD    | -40       |      | 40     | μA   | *5            |

| Tri-state pin output le | eak current | Ilo  | VI = Vss or<br>VDD            | -40       |      | 40     | μA   | *8            |

### 1-1. Applicable pins and classification

\*1 CMOS level input pins: TEST, TES1 \*2 CMOS level input pins: MUTE, SCSY, PWMI, DATA, XLAT, SSTP, XTSL \*3 CMOS Schmitt input pins: ASYE, EXCK, V16M, SQCK, XRST, CLOK, SCLK \*4 Analog input pins (1): VCTL, ASYI, CLTV, FILI \*5 Analog input pins (2): VC, FE, SE, TE, CE, RFDC \*6 Normal output pins (1): V16M, SBSO, C4M, WDCK, FSTO, SOUT, SOCK, XOLT, SQSO, WFCK, XUGF, XPCK, GFS, C2PO, SCOR, SFDR, SRDR, TFDR, TRDR, FRDR, ASYO, DOUT, LRCK, PCMD, BCK, EMPH \*7 Normal output pin (2): FILO \*8 Tri-state output pins: VPCO, SENS, MDP, FFDR, PCO \*9 Normal input/output pins: ATSK, COUT, MIRR, DFCT, FOK, LOCK

**Note)** When the external pull-down resistors are connected to the pins  $^{*2}$  and  $^{*3}$ , the resistance applied to these pins should be  $5k\Omega$  or less in total.

### 2. AC Characteristics

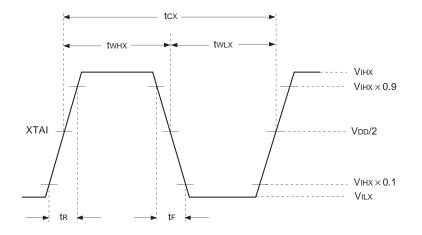

(1) XTAI pin

### (a) When using self-excited oscillation

$(V_{DD} = AV_{DD} = 3.3 \pm 0.3V, Topr = -20 \text{ to } +75^{\circ}C)$

| Item                     | Symbol | Min. | Тур. | Max. | Unit |

|--------------------------|--------|------|------|------|------|

| Oscillation<br>frequency | fмах   | 7    |      | 34   | MHz  |

### (b) When inputting pulses to XTAI pin

|                           | (VDD = AV) | $/DD = 3.3 \pm$ | 0.3V, Top | r = -20 to | +75°C) |

|---------------------------|------------|-----------------|-----------|------------|--------|

| Item                      | Symbol     | Min.            | Тур.      | Max.       | Unit   |

| High level pulse<br>width | twнx       | 13              |           | 500        | ns     |

| Low level pulse width     | twLx       | 13              |           | 500        | ns     |

| Pulse cycle               | tcx        | 26              |           | 1000       | ns     |

| Input high level          | Vінх       | Vdd - 1.0       |           |            | V      |

| Input low level           | VILX       |                 |           | 0.8        | V      |

| Rise time,<br>fall time   | tr, tr     |                 |           | 10         | ns     |

(c) When inputting sine waves to XTAI pin via a capacitor

$(V_{DD} = AV_{DD} = 3.3 \pm 0.3V, Topr = -20 \text{ to } +75^{\circ}C)$

| Item            | Symbol | Min. | Тур. | Max.      | Unit |

|-----------------|--------|------|------|-----------|------|

| Input amplitude | Vi     | 2.0  |      | Vdd + 0.3 | Vp-р |

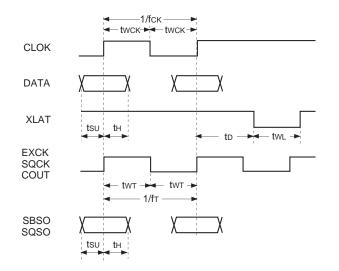

| (VDD = AVDD = 3)               | .3 ± 0.3V, ' | Vss = AVss | s = 0V, To | pr = -20 to | +75°C) |

|--------------------------------|--------------|------------|------------|-------------|--------|

| Item                           | Symbol       | Min.       | Тур.       | Max.        | Unit   |

| Clock frequency                | fcк          |            |            | 0.65        | MHz    |

| Clock pulse width              | twcк         | 750        |            |             | ns     |

| Setup time                     | ts∪          | 300        |            |             | ns     |

| Hold time                      | tн           | 300        |            |             | ns     |

| Delay time                     | to           | 300        |            |             | ns     |

| Latch pulse width              | tw∟          | 750        |            |             | ns     |

| EXCK SQCK frequency            | fт           |            |            | 0.65 Note)  | MHz    |

| EXCK SQCK pulse width          | twт          | 750 Note)  |            |             | ns     |

| COUT frequency (for input) *   | fт           |            |            | 65          | kHz    |

| COUT pulse width (for input) * | tw⊤          | 7.5        |            |             | μs     |

### (2) CLOK, DATA, XLAT, SQCK and EXCK pins

$^{\ast}$  Only when \$44 and \$45 are executed.

**Note)** In quasi double-speed playback mode, except when SQSO is Sub Q Read, the SQCK maximum operating frequency is 300kHz and its minimum pulse width is 1.5µs.

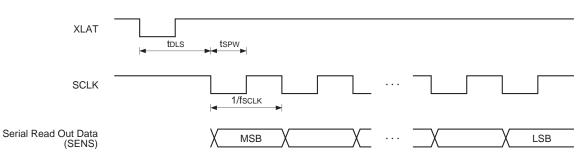

### (3) SCLK pin

| ltem             | Symbol | Min. | Тур. | Max. | Unit |

|------------------|--------|------|------|------|------|

| SCLK frequency   | fsclk  |      |      | 16   | MHz  |

| SCLK pulse width | tspw   | 31.3 |      |      | ns   |

| Delay time       | tDLS   | 15   |      |      | μs   |

### (4) COUT, MIRR and DFCT pins

| Operating frequency (V           | dd = AVdd     | $= 3.3 \pm 0.3$ | 3V, Vss = / | AVss = 0V | , Topr = | –20 to +75°C) |

|----------------------------------|---------------|-----------------|-------------|-----------|----------|---------------|

| Signal                           | Symbol        | Min.            | Тур.        | Max.      | Unit     | Conditions    |

| COUT maximum operating frequency | fcouт         | 40              |             |           | kHz      | *1            |

| MIRR maximum operating frequency | <b>f</b> MIRR | 40              |             |           | kHz      | *2            |

| DFCT maximum operating frequency | fdfcth        | 5               |             |           | kHz      | *3            |

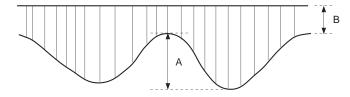

$^{\rm *1}$  When using a high-speed traverse TZC.

\*2

When the RF signal continuously satisfies the following conditions during the above traverse.

• A = 0.11VDD to 0.23VDD

•

$$\frac{\mathsf{B}}{\mathsf{A} + \mathsf{B}} \le 25\%$$

\*3 During complete RF signal omission.

When settings related to DFCT signal generation are Typ.

### Contents

| [1] CPU I  |                                 |                  |                        |     |

|------------|---------------------------------|------------------|------------------------|-----|

|            |                                 |                  |                        |     |

|            |                                 |                  |                        |     |

|            |                                 |                  |                        |     |

| § 1-4.     | Description of SENS Signals     |                  |                        | 30  |

|            |                                 |                  |                        |     |

|            | ode Interface                   |                  |                        |     |

|            |                                 |                  |                        |     |

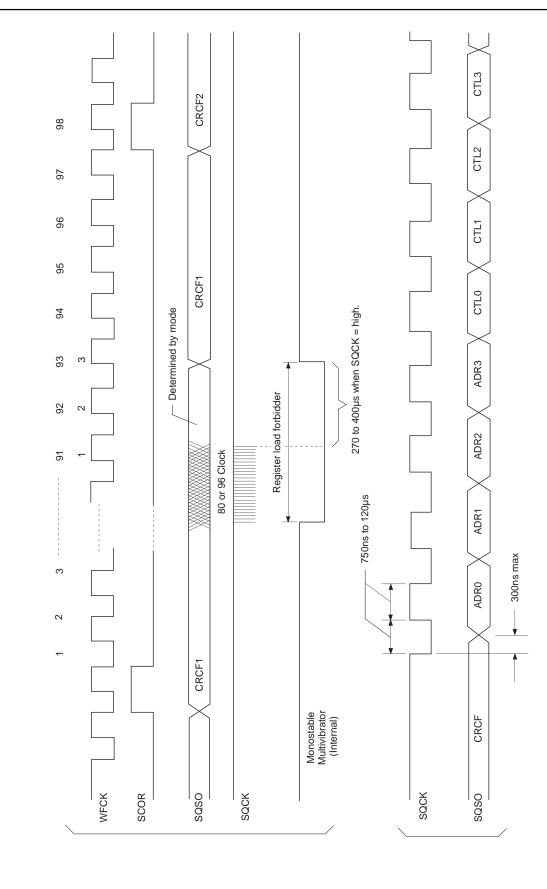

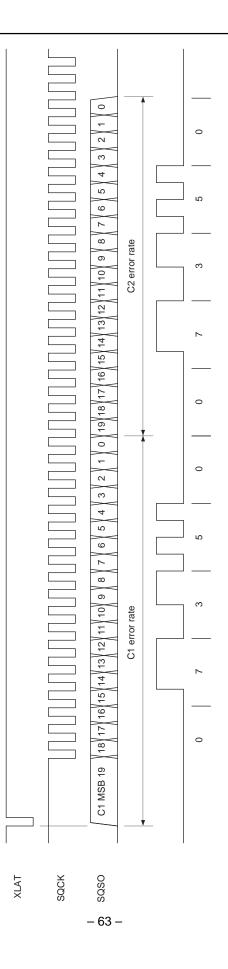

| § 2-2.     | 80-bit Sub-Q Readout            |                  |                        | 57  |

|            |                                 |                  |                        |     |

|            | iption of Modes                 |                  |                        | ~ 4 |

|            |                                 |                  |                        |     |

|            |                                 |                  |                        |     |

|            |                                 |                  |                        |     |

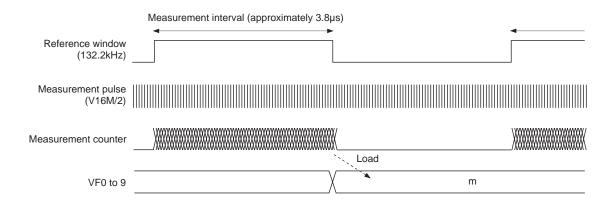

| § 3-4.     | VCO-C mode                      |                  |                        | 65  |

|            |                                 |                  |                        |     |

|            | iption of Other Functions       |                  |                        | ~~  |

|            |                                 |                  | Circuit                |     |

|            |                                 |                  |                        |     |

|            |                                 |                  |                        |     |

| § 4-4.     |                                 |                  |                        |     |

|            |                                 |                  |                        |     |

| § 4-6.     | Servo Auto Sequence             |                  |                        | 74  |

| § 4-7.     | Digital CLV                     |                  |                        | 82  |

| § 4-8.     | Playback Speed                  |                  |                        | 83  |

| § 4-9.     | Asymmetry Correction            |                  |                        | 84  |

|            |                                 |                  |                        |     |

| -          |                                 |                  |                        |     |

| [5] Descr  | iption of Servo Signal Processi | ing System I     | Functions and Commands |     |

|            |                                 |                  | ing System             | 87  |

|            |                                 |                  |                        |     |

| § 5-3.     |                                 |                  | Compensation]          |     |

|            |                                 |                  |                        |     |

|            |                                 |                  |                        |     |

|            |                                 |                  |                        |     |

|            |                                 |                  |                        |     |

|            |                                 |                  |                        |     |

|            |                                 |                  |                        |     |

|            |                                 |                  |                        |     |

|            |                                 |                  |                        |     |

|            |                                 |                  |                        |     |

| •          |                                 |                  |                        |     |

|            |                                 |                  |                        |     |

|            |                                 |                  |                        |     |

|            |                                 |                  |                        |     |

|            |                                 |                  | ignal                  |     |

|            |                                 |                  |                        |     |

|            |                                 |                  |                        |     |

|            |                                 |                  |                        |     |

|            |                                 |                  |                        |     |

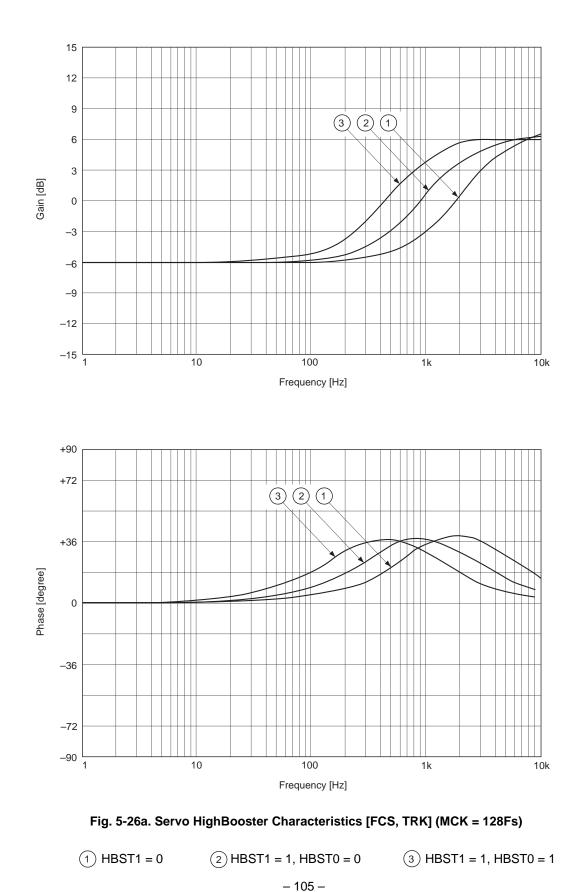

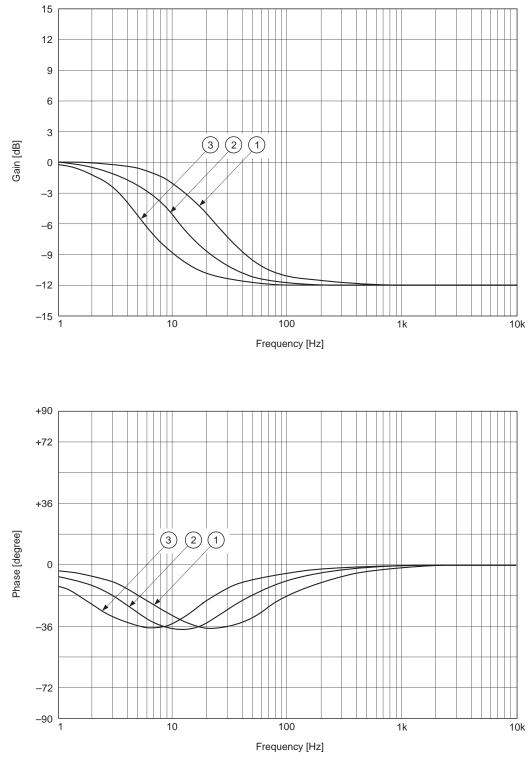

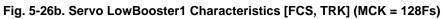

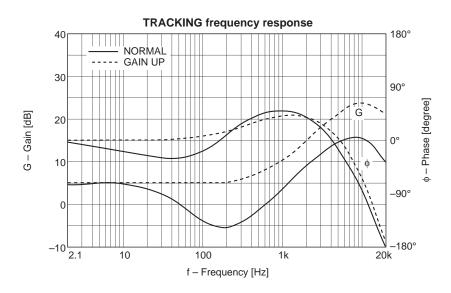

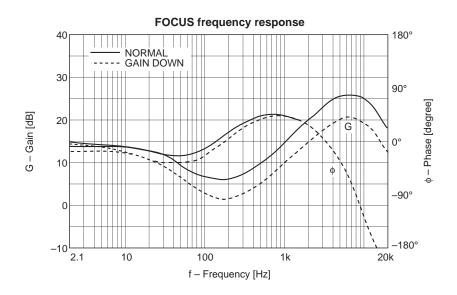

| 8 2-21     | . TRACKING and FOCUS Freque     | ency Respons     | se                     | 132 |

| [6] Annlia | action Circuit                  |                  |                        | 100 |

| fol Abbiid |                                 |                  |                        | 133 |

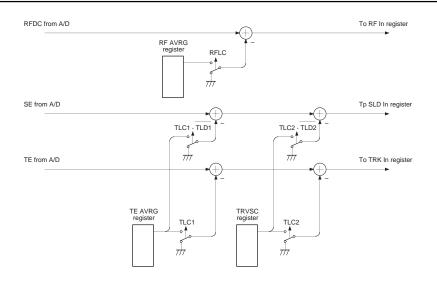

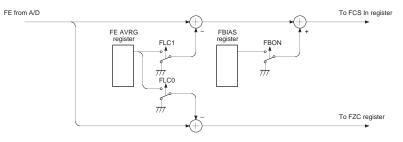

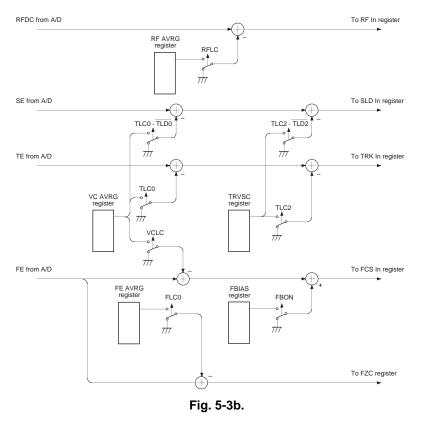

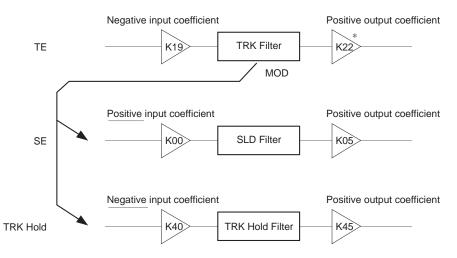

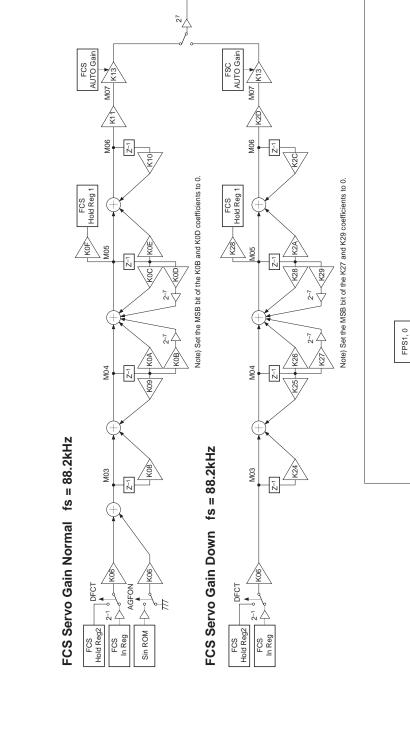

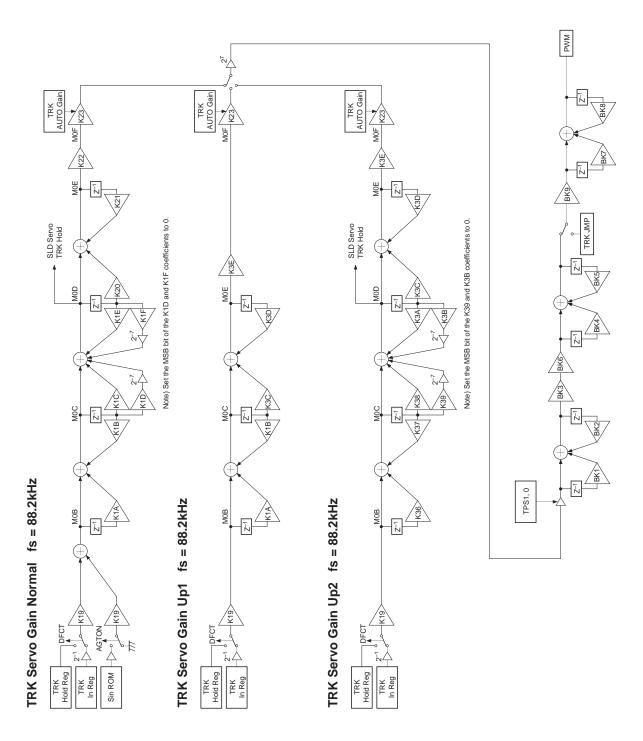

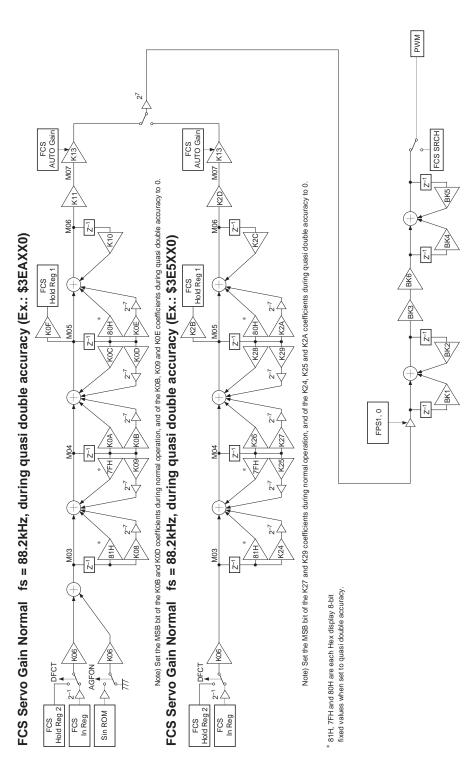

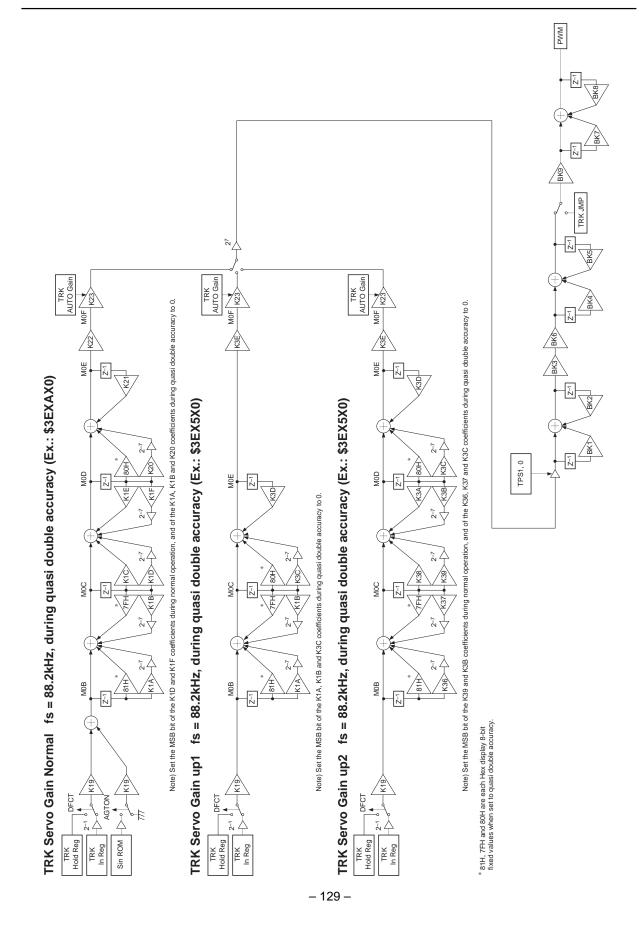

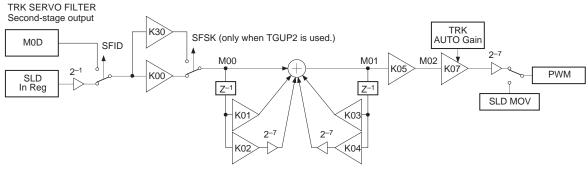

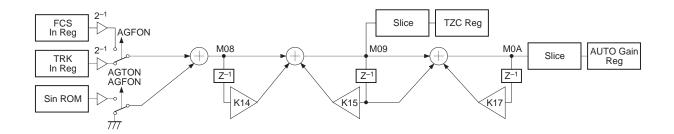

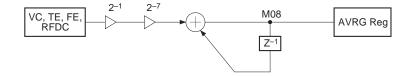

|            | Explanation of abbreviations    | AVRG:            | Average                |     |

|            |                                 | AVRG.<br>AGCNTL: |                        |     |

|            |                                 | AGCINTL:<br>FCS: | Auto gain control      |     |

|            |                                 | TRK:             | Focus                  |     |

|            |                                 | SLD:             | Tracking<br>Sled       |     |

|            |                                 | -                |                        |     |

|            |                                 | DFCT:            | Defect                 |     |

### [1] CPU Interface

### § 1-1. CPU Interface Timing

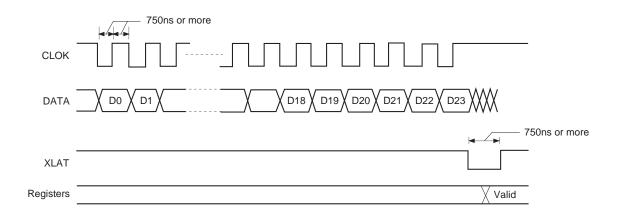

• CPU interface

This interface uses DATA, CLOK and XLAT to set the modes. The interface timing chart is shown below.

• The internal registers are initialized by a reset when XRST = 0. **Note)** Be sure to set SQCK to high when XLAT is low.

### § 1-2. CPU Interface Command Table

Total bit length for each register

| Register | Total bit length |

|----------|------------------|

| 0 to 2   | 8 bits           |

| 3        | 8 to 24 bits     |

| 4 to 6   | 16 bits          |

| 7        | 20 bits          |

| 8        | 28 bits          |

| 9        | 28 bits          |

| А        | 28 bits          |

| В        | 24 bits          |

| С        | 28 bits          |

| D        | 20 bits          |

| E        | 20 bits          |

– 13 –

## SONY

Downloaded from Elcodis.com electronic components distributor

--: Don't care

TRACKING GAIN UP FILTER SELECT 2

I

I

I

I

l

I

l

l

0

I

TRACKING GAIN UP FILTER SELECT 1

I

I

T

T

~

Ι

TRACKING GAIN UP

|

l

I

~

I

TRACKING GAIN NORMAL

0

0001

TRACKING CONTROL

~

**BRAKE OFF**

I

I

0

|

BRAKE ON

l

I

~

Τ

ANTI SHOCK OFF

0

|         |            | TRACKING SERVO OFF | TRACKING SERVO ON | FORWARD TRACK JUMP | REVERSE TRACK JUMP | SLED SERVO OFF | SLED SERVO ON | FORWARD SLED MOVE | REVERSE SLED MOVE |             |            | SLED KICK LEVEL<br>(±1 × basic value) (Default) | SLED KICK LEVEL<br>(±2 × basic value) | SLED KICK LEVEL<br>(±3 × basic value) | SLED KICK LEVEL<br>(±4 × basic value) |

|---------|------------|--------------------|-------------------|--------------------|--------------------|----------------|---------------|-------------------|-------------------|-------------|------------|-------------------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|

|         | D0         | Ι                  | Ι                 | I                  | Ι                  | I              |               | Ι                 |                   |             | DO         |                                                 |                                       |                                       |                                       |

| a 5     | D1         | Ι                  | -                 | I                  | I                  | I              | I             | I                 | I                 | a 5         | 5          | I                                               | I                                     | I                                     | I                                     |

| Data 5  | D2         | Ι                  | -                 | I                  | I                  | I              | I             | I                 | I                 | Data 5      | D2         | I                                               | I                                     | I                                     | I                                     |

|         | D3         | Ι                  | -                 | I                  | I                  | I              | I             | I                 | I                 |             | ß          | I                                               | I                                     | I                                     | I                                     |

|         | D4         | Ι                  | Ι                 | I                  | Ι                  | I              | 1             | I                 | I                 |             | D4         | 1                                               | I                                     | I                                     | I                                     |

| a 4     | D5         | Ι                  |                   | I                  | I                  | I              | I             | I                 | I                 | a 4         | D5         | I                                               | I                                     | I                                     | I                                     |

| Data 4  | D6         | Ι                  | Ι                 | I                  | Ι                  | I              | I             | I                 | I                 | Data 4      | D6         | I                                               | I                                     | I                                     | I                                     |

|         | D7         | Ι                  | -                 | I                  | I                  | I              | I             | I                 | I                 |             | D7         | I                                               | I                                     | I                                     | I                                     |

|         | D8         | I                  |                   | I                  | I                  | I              | 1             | I                 | I                 |             | D8         | 1                                               | I                                     | I                                     | I                                     |

| a 3     | D9         | I                  | -                 | I                  | I                  | I              | 1             | I                 | I                 | a 3         | D9         | 1                                               | I                                     | I                                     | I                                     |

| Data 3  | D10        | I                  | -                 | I                  | I                  | I              | 1             | I                 | I                 | Data 3      | D10        | 1                                               | I                                     | I                                     | I                                     |

|         | D11        | Ι                  | -                 | I                  | I                  | I              |               | I                 | I                 |             | D11        |                                                 | I                                     | I                                     | I                                     |

|         | D12        | Ι                  | Ι                 | I                  | I                  | I              | I             | I                 | I                 |             | D12        | I                                               | I                                     | I                                     | I                                     |

| a 2     | D13        | Ι                  | Ι                 | I                  | I                  | I              | I             | I                 | I                 | a 2         | D13        | I                                               | I                                     | I                                     | I                                     |

| Data 2  | D14        | Ι                  | Ι                 | I                  | I                  | I              | I             | I                 | I                 | Data 2      | D14        | I                                               | I                                     | I                                     | I                                     |

|         | D15        | Ι                  | Ι                 | I                  | I                  | I              | I             | I                 | I                 |             | D15        | I                                               | I                                     | I                                     | I                                     |

|         | D16        | Ι                  | I                 | I                  | I                  | 0              | ~             | 0                 | ~                 | a 1         | D16        | 0                                               | -                                     | 0                                     | -                                     |

| a 1     | D17        | Ι                  | -                 | I                  | I                  | 0              | 0             | -                 | ~                 | Data 1      | D17        | 0                                               | 0                                     | ~                                     | ~                                     |

| Data 1  | D18        | 0                  | 1                 | 0                  | ٢                  | I              | I             | Ι                 | I                 |             | D18        | 0                                               | 0                                     | 0                                     | 0                                     |

|         | D19        | 0                  | 0                 | ~                  | ٢                  | I              | I             | Ι                 | I                 | ess         | D19        | 0                                               | 0                                     | 0                                     | 0                                     |

| Address | D23 to D20 |                    |                   |                    |                    |                |               |                   |                   | Address     | D23 to D20 |                                                 | •<br>•                                | -                                     |                                       |

| Juemmo  |            |                    |                   |                    | TRACKING           | MODE           |               |                   |                   | ommand<br>O |            |                                                 | SEI EOT                               |                                       |                                       |

| Reg-    | ister      |                    |                   |                    | ~                  | 1              |               |                   |                   | Reg-        | ister      |                                                 | c                                     | 0                                     |                                       |

### Downloaded from <u>Elcodis.com</u> electronic components distributor

Command Table (\$2X to 3X)

|           |            |                                    | R A-H                                        | 3 A-L                                        | 3 B-H                                        | 3 B-L                                        |                                     |                                     |                                   | A                                          | В                                        | ER A-H                                        | ER A-L                                        | ER B-H                                        | ER B-L                                    | SATE FILTER A                                      | AIN                                       |

|-----------|------------|------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|-------------------------------------|-------------------------------------|-----------------------------------|--------------------------------------------|------------------------------------------|-----------------------------------------------|-----------------------------------------------|-----------------------------------------------|-------------------------------------------|----------------------------------------------------|-------------------------------------------|

|           |            | KRAM DATA (K00)<br>SLED INPUT GAIN | KRAM DATA (K01)<br>SLED LOW BOOST FILTER A-H | KRAM DATA (K02)<br>SLED LOW BOOST FILTER A-L | KRAM DATA (K03)<br>SLED LOW BOOST FILTER B-H | KRAM DATA (K04)<br>SLED LOW BOOST FILTER B-L | KRAM DATA (K05)<br>SLED OUTPUT GAIN | KRAM DATA (K06)<br>FOCUS INPUT GAIN | KRAM DATA (K07)<br>SLED AUTO GAIN | KRAM DATA (K08)<br>FOCUS HIGH CUT FILTER A | KRAM DATA (K09)<br>FOCUS HIGH CUT FILTER | KRAM DATA (K0A)<br>FOCUS LOW BOOST FILTER A-H | KRAM DATA (K0B)<br>FOCUS LOW BOOST FILTER A-L | KRAM DATA (K0C)<br>FOCUS LOW BOOST FILTER B-H | KRAM DATA (K0D)<br>FOCUS LOW BOOST FILTER | KRAM DATA (K0E)<br>FOCUS PHASE COMPENSATE FILTER A | KRAM DATA (K0F)<br>FOCUS DEFECT HOLD GAIN |

|           | DO         | KDO                                | KD0                                          | KD0                                          | KD0                                          | KD0                                          | KD0                                 | KD0                                 | KD0                               | KD0                                        | KD0                                      | KD0                                           | KD0                                           | KD0                                           | KD0                                       | KD0                                                | KD0                                       |

| ta 2      | Б          | KD1                                | KD1                                          | KD1                                          | KD1                                          | KD1                                          | KD1                                 | KD1                                 | KD1                               | KD1                                        | KD1                                      | KD1                                           | KD1                                           | KD1                                           | KD1                                       | KD1                                                | KD1                                       |

| Data      | D2         | KD2                                | KD2                                          | KD2                                          | KD2                                          | KD2                                          | KD2                                 | KD2                                 | KD2                               | KD2                                        | KD2                                      | KD2                                           | KD2                                           | KD2                                           | KD2                                       | KD2                                                | KD2                                       |

|           | D3         | KD3                                | KD3                                          | KD3                                          | KD3                                          | KD3                                          | KD3                                 | KD3                                 | KD3                               | KD3                                        | KD3                                      | KD3                                           | KD3                                           | KD3                                           | KD3                                       | KD3                                                | KD3                                       |

|           | D4         | KD4                                | KD4                                          | KD4                                          | KD4                                          | KD4                                          | KD4                                 | KD4                                 | KD4                               | KD4                                        | KD4                                      | KD4                                           | KD4                                           | KD4                                           | KD4                                       | KD4                                                | KD4                                       |

| a 1       | D5         | KD5                                | KD5                                          | KD5                                          | KD5                                          | KD5                                          | KD5                                 | KD5                                 | KD5                               | KD5                                        | KD5                                      | KD5                                           | KD5                                           | KD5                                           | KD5                                       | KD5                                                | KD5                                       |

| Data 1    | D6         | KD6                                | KD6                                          | KD6                                          | KD6                                          | KD6                                          | KD6                                 | KD6                                 | KD6                               | KD6                                        | KD6                                      | KD6                                           | KD6                                           | KD6                                           | KD6                                       | KD6                                                | KD6                                       |

|           | D7         | KD7                                | KD7                                          | KD7                                          | KD7                                          | KD7                                          | KD7                                 | KD7                                 | KD7                               | KD7                                        | KD7                                      | KD7                                           | KD7                                           | KD7                                           | KD7                                       | KD7                                                | KD7                                       |

|           | D8         | 0                                  | -                                            | 0                                            | ~                                            | 0                                            | -                                   | 0                                   | -                                 | 0                                          | ~                                        | 0                                             | ~                                             | 0                                             | -                                         | 0                                                  | -                                         |

| ess 4     | 60         | 0                                  | 0                                            | ~                                            | ~                                            | 0                                            | 0                                   | -                                   | -                                 | 0                                          | 0                                        | 1                                             | -                                             | 0                                             | 0                                         | -                                                  | -                                         |

| Address 4 | D10        | 0                                  | 0                                            | 0                                            | 0                                            | ~                                            | ~                                   | ~                                   | ~                                 | 0                                          | 0                                        | 0                                             | 0                                             | ~                                             | ~                                         | ~                                                  | -                                         |

|           | D11        | 0                                  | 0                                            | 0                                            | 0                                            | 0                                            | 0                                   | 0                                   | 0                                 | -                                          | -                                        | 1                                             | 1                                             | -                                             | -                                         | -                                                  | 1                                         |

| Address 3 | D15 to D12 |                                    |                                              |                                              |                                              |                                              |                                     |                                     |                                   |                                            |                                          |                                               |                                               |                                               |                                           |                                                    |                                           |

| Address 2 | D19 to D16 |                                    |                                              |                                              |                                              |                                              |                                     |                                     |                                   |                                            |                                          |                                               |                                               |                                               |                                           |                                                    |                                           |

| Address 1 | D23 to D20 |                                    |                                              |                                              |                                              |                                              |                                     |                                     | ,<br>,<br>,                       | -                                          |                                          |                                               |                                               |                                               |                                           |                                                    |                                           |

|           | Command    |                                    |                                              |                                              |                                              |                                              |                                     |                                     |                                   | 9E E E C -                                 |                                          |                                               |                                               |                                               |                                           |                                                    |                                           |

| Red-      | ister      |                                    |                                              |                                              |                                              |                                              |                                     |                                     | ç                                 | 0                                          |                                          |                                               |                                               |                                               |                                           |                                                    |                                           |

| L         |            | 1                                  |                                              |                                              |                                              |                                              |                                     |                                     |                                   |                                            |                                          |                                               |                                               |                                               |                                           |                                                    |                                           |

– 15 –

|           |            | KRAM DATA (K10)<br>FOCUS PHASE COMPENSATE FILTER B | JAIN                                 | T GAIN                                   | Z                                  | KRAM DATA (K14)<br>HPTZC / AUTO GAIN HIGH PASS FILTER A | KRAM DATA (K15)<br>HPTZC / AUTO GAIN HIGH PASS FILTER B | I PASS FILTER A                                | KRAM DATA (K17)<br>HPTZC / AUTO GAIN LOW PASS FILTER B |                                                                                                  | GAIN                                   | UT FILTER A                                 | UT FILTER B                                 | OOST FILTER A-H                                  | OOST FILTER A-L                                  | OOST FILTER B-H                              | KRAM DATA (K1F)<br>TRACKING LOW BOOST FILTER B-L |

|-----------|------------|----------------------------------------------------|--------------------------------------|------------------------------------------|------------------------------------|---------------------------------------------------------|---------------------------------------------------------|------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------------------------------------------------|----------------------------------------|---------------------------------------------|---------------------------------------------|--------------------------------------------------|--------------------------------------------------|----------------------------------------------|--------------------------------------------------|

|           |            |                                                    | KRAM DATA (K11)<br>FOCUS OUTPUT GAIN | KRAM DATA (K12)<br>ANTI SHOCK INPUT GAIN | KRAM DATA (K13)<br>FOCUS AUTO GAIN |                                                         |                                                         | KRAM DATA (K16)<br>ANTI SHOCK HIGH PASS FILTER |                                                        | KRAM DATA (K18)<br>FIX                                                                           | KRAM DATA (K19)<br>TRACKING INPUT GAIN | KRAM DATA (K1A)<br>TRACKING HIGH CUT FILTER | KRAM DATA (K1B)<br>TRACKING HIGH CUT FILTER | KRAM DATA (K1C)<br>TRACKING LOW BOOST FILTER A-H | KRAM DATA (K1D)<br>TRACKING LOW BOOST FILTER A-L | KRAM DATA (K1E)<br>TRACKING LOW BOOST FILTER |                                                  |

|           | DO         | KD0                                                | KD0                                  | KD0                                      | KD0                                | KD0                                                     | KD0                                                     | KD0                                            | KD0                                                    | KD0                                                                                              | KD0                                    | KD0                                         | KD0                                         | KD0                                              | KD0                                              | KD0                                          | KD0                                              |

| Data 2    | 5          | КD<br>Кр                                           | KD1                                  | ξ<br>Δ                                   | KD1                                | KD1                                                     | Б<br>Б                                                  | Б<br>Б                                         | KD<br>KD                                               | KD1                                                                                              | Б<br>Б                                 | KD1                                         | КD<br>Кр                                    | Б<br>Б                                           | КD<br>Кр                                         | KD1                                          | KD1                                              |

| Da        | D2         | KD2                                                | KD2                                  | KD2                                      | KD2                                | KD2                                                     | KD2                                                     | KD2                                            | KD2                                                    | KD2                                                                                              | KD2                                    | KD2                                         | KD2                                         | KD2                                              | KD2                                              | KD2                                          | KD2                                              |

|           | D3         | KD3                                                | KD3                                  | KD3                                      | KD3                                | KD3                                                     | KD3                                                     | KD3                                            | KD3                                                    | KD3                                                                                              | KD3                                    | KD3                                         | KD3                                         | KD3                                              | KD3                                              | KD3                                          | KD3                                              |

|           | D4         | KD4                                                | KD4                                  | KD4                                      | KD4                                | KD4                                                     | KD4                                                     | KD4                                            | KD4                                                    | KD4                                                                                              | KD4                                    | KD4                                         | KD4                                         | KD4                                              | KD4                                              | KD4                                          | KD4                                              |

| Data 1    | D5         | KD5                                                | KD5                                  | KD5                                      | KD5                                | KD5                                                     | KD5                                                     | KD5                                            | KD5                                                    | KD5                                                                                              | KD5                                    | KD5                                         | KD5                                         | KD5                                              | KD5                                              | KD5                                          | KD5                                              |

| Da        | D6         | KD6                                                | KD6                                  | KD6                                      | KD6                                | KD6                                                     | KD6                                                     | KD6                                            | KD6                                                    | KD6                                                                                              | KD6                                    | KD6                                         | KD6                                         | KD6                                              | KD6                                              | KD6                                          | KD6                                              |

|           | D7         | KD7                                                | KD7                                  | KD7                                      | KD7                                | KD7                                                     | KD7                                                     | KD7                                            | KD7                                                    | KD7                                                                                              | KD7                                    | KD7                                         | KD7                                         | KD7                                              | KD7                                              | KD7                                          | KD7                                              |

|           | D8         | 0                                                  | ~                                    | 0                                        | -                                  | 0                                                       | ~                                                       | 0                                              | ~                                                      | 0                                                                                                | ~                                      | 0                                           | ~                                           | 0                                                | -                                                | 0                                            | ~                                                |

| Address 4 | D9         | 0                                                  | 0                                    | ~                                        | -                                  | 0                                                       | 0                                                       | ~                                              | ~                                                      | 0                                                                                                | 0                                      | -                                           | ~                                           | 0                                                | 0                                                | ~                                            | ~                                                |

| Addr      | D10        | 0                                                  | 0                                    | 0                                        | 0                                  | ~                                                       | ~                                                       | ~                                              | ~                                                      | 0                                                                                                | 0                                      | 0                                           | 0                                           | ~                                                | ~                                                | ~                                            | ~                                                |

|           | D11        | 0                                                  | 0                                    | 0                                        | 0                                  | 0                                                       | 0                                                       | 0                                              | 0                                                      | ~                                                                                                | ~                                      | -                                           | ~                                           | ~                                                | ~                                                | ~                                            | ~                                                |

| Address 3 | D15 to D12 |                                                    |                                      |                                          |                                    |                                                         |                                                         |                                                |                                                        |                                                                                                  |                                        |                                             |                                             |                                                  |                                                  |                                              |                                                  |

| Address 2 | D19 to D16 |                                                    |                                      |                                          |                                    |                                                         |                                                         |                                                |                                                        |                                                                                                  |                                        |                                             |                                             |                                                  |                                                  |                                              |                                                  |

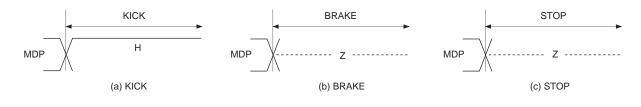

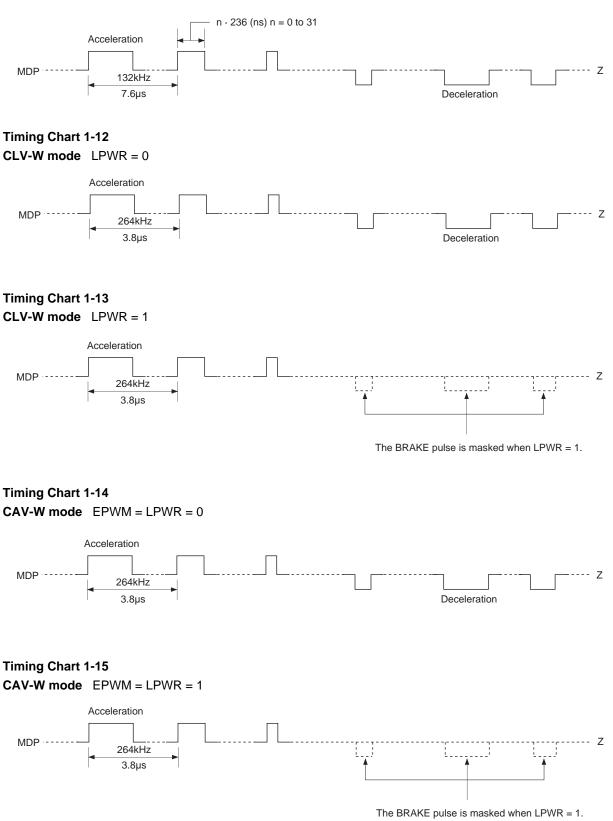

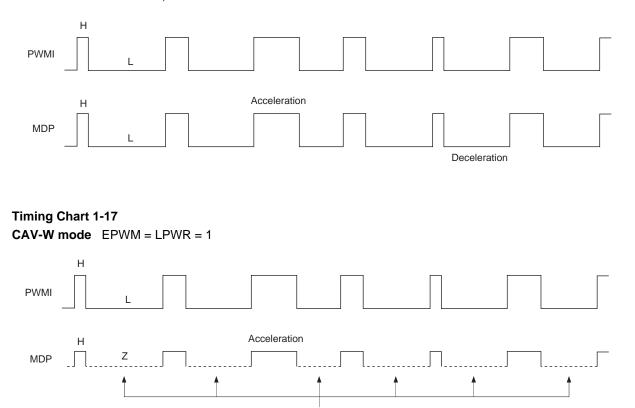

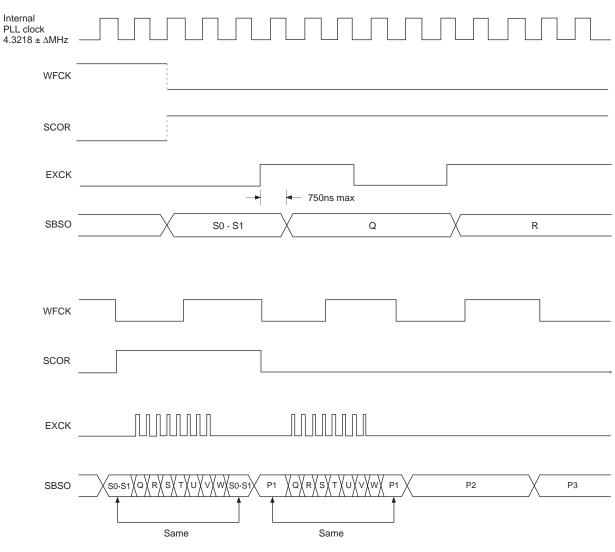

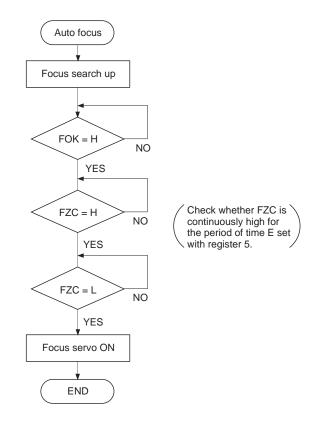

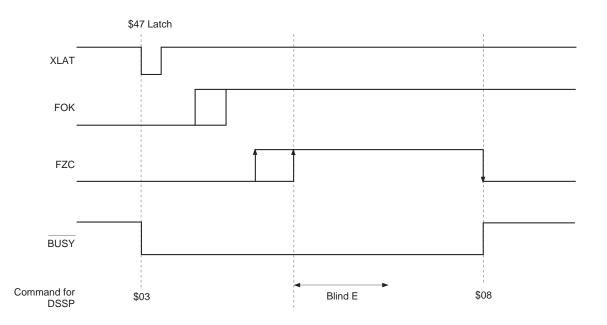

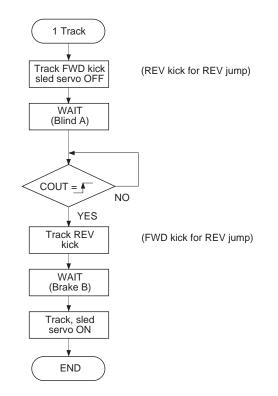

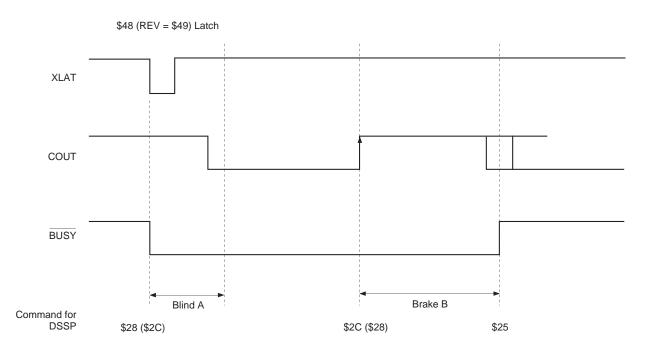

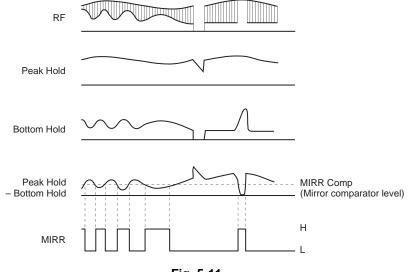

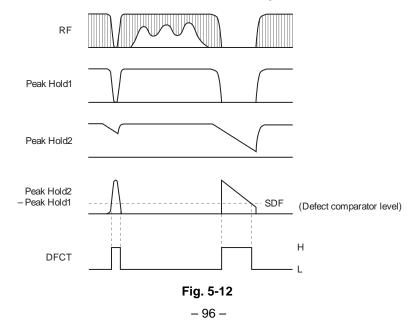

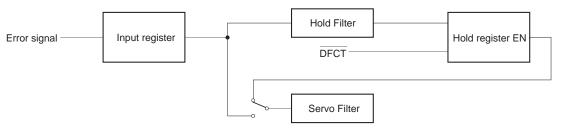

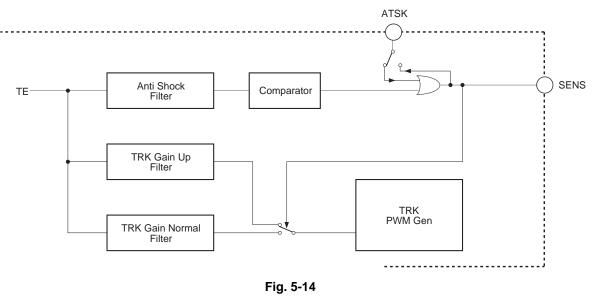

| Address 1 | D23 to D20 |                                                    |                                      |                                          |                                    |                                                         |                                                         |                                                |                                                        | -                                                                                                |                                        |                                             |                                             |                                                  |                                                  |                                              |                                                  |